カウント装置

【課題】 カウント入力回路への被カウント信号配線は変更することなく、その被カウント信号をカウントするカウンタを変更したり、あるいは1のカウンタ入力回路へ供給される被カウント信号を、複数のカウンタへ並列に供給することを可能とする。

【解決手段】 入力回路(11−1〜4)の各出力端とカウンタ(13−1〜4)の各入力端との間には分配切替回路(12)が介在され、分配切替回路は、入力回路の各出力端のそれぞれに接続される入力側端子(IN0〜IN1)と、カウンタの各入力端のそれぞれに接続される出力側端子(OUT1〜OUT4)とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされる。

【解決手段】 入力回路(11−1〜4)の各出力端とカウンタ(13−1〜4)の各入力端との間には分配切替回路(12)が介在され、分配切替回路は、入力回路の各出力端のそれぞれに接続される入力側端子(IN0〜IN1)と、カウンタの各入力端のそれぞれに接続される出力側端子(OUT1〜OUT4)とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、複数のカウンタを内蔵すると共に、それらのカウンタのカウント値又はそのカウント値に基づいて生成された状態信号を出力信号として外部へと出力するカウント装置に関する。

【背景技術】

【0002】

基本となる1つの動作部と、1若しくは2以上のその他の動作部とを互いに連動させることによって、目的を達するようにした自動処理装置の制御に当たっては、複数のカウンタを使用した制御システムがしばしば採用される。

【0003】

このような複数のカウンタを使用した制御システムの一例を示す説明図が図9に示されている。なお、図示の制御システムは、ガイドローラ駆動部、正極シートカット動作部、負極シートカット部、及びシート巻き取り動作部を有する二次電池電極製造装置に適用されるものである。

【0004】

同図(a)に示されるように、この二次電池電極製造装置は、絶縁シート、負極シート、絶縁シート、及び正極シートからなる4枚のシートを、ガイドローラにて適宜に供給経路をガイドしつつ1点に供給して、巻き取りローラ31に重ねて巻き取らせると共に、適当なインターバルで負極シートカッタ34及び正極シートカッタ35を作動させることにより、所望の積層構造を有する二次電池電極をロール体として完成するものである。

【0005】

シート巻き取りローラ31に連動する主軸32の回転は、主軸エンコーダ33を介してパルス列に変換される。こうして得られた主軸エンコーダ33からのパルス列は、第1カウンタ36−1、第2カウンタ36−2、第3カウンタ36−3へと並列に供給される。

【0006】

それらのカウンタ36−1〜3のそれぞれは、被カウント信号である主軸エンコーダ33からのパルス列をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウンタ部と、このリングカウンタ部のカウント値を、所定のONタイミング値及びOFFタイミング値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを含んでいる。

【0007】

ガイドローラ位置制御部37−1は、第1カウンタ36−1から得られる状態信号により起動され、ガイドローラ駆動部における所定の動作を制御する。正極シートカット制御部37−2は、第2カウンタ36−2から得られる状態信号により起動され、正極シートカッタ35における所定の動作を制御する。負極シートカット制御部37−3は、第3カウンタ36−3から得られる状態信号により起動され、負極シートカッタ34における所定の動作を制御する。

【0008】

同図(b)に示されるように、各カウンタ36−1〜3から得られる状態信号のON/OFFタイミングは、ガイドローラ駆動部、正極シートカッタ、負極シートカッタのそれぞれにおける動作タイミングに合わせて設定されている。

【0009】

そのため、このような制御システムによれば、シート巻き取り動作に連動して、ガイドローラの動作、正極シートカット動作、及び負極シートカット動作を適切に行わせることができる。しかも、3台のカウンタ36−1〜3におけるONカウント値、OFFカウント値を変更することで、各動作部間における動作関係の変更にも容易に対応することができる。

【0010】

この種の制御システムは、一般に、カウンタモジュールを含むビルディングブロック型のプログラマブルコントローラ(以下、PLCと言う)により実現することができる(例えば、特許文献1参照)。

【0011】

カウンタモジュールを含むPLCを用いた制御システムの一例を示す説明図が図10に示されている。

【0012】

同図に示されるように、この制御システムは、主軸モータM1と連動して主軸回転量情報(エンコーダパルス)を出力する主軸エンコーダEと、主軸回転量情報に基づいて所定のユーザプログラムを実行することにより、モータ動作指令を生成するPLC100と、PLC100から得られるモータ動作指令に基づいて従動モータM2を駆動するモータ駆動装置200とを含んで構成される。

【0013】

PLC100は、この例にあっては、PLC全体を統括制御するCPUモジュール2と、一般的な入出力信号のやりとりを外部と行うための入出力モジュール(図示せず)と、主軸回転量情報(エンコーダパルス)をカウントして、各従動軸に対応する主軸の状態信号をCPUモジュール2へ出力する複数のカウンタを備えたカウンタモジュール1と、CPUモジュール2から与えられる位置制御指令に応答して、モータ動作指令を生成する位置制御モジュール3とを含んで構成される。

【0014】

従来のカウンタモジュールの一例を示す構成図が図11に示されている。同図に示されるように、このカウンタモジュール1は、複数個(この例では4個)のカウンタ(第1カウンタ13−1、第2カウンタ13−2、第3カウンタ13−3、第4カウンタ13−4)と、外部から被カウント信号を取り込むための前記カウンタと同数の入力回路(第1カウンタ入力回路11−1、第2カウンタ入力回路11−2、第3カウンタ入力回路11−3、第4カウンタ入力回路11−4)とを有している。

【0015】

なお、第1〜第4カウンタ13−1〜4としては、ソフトウェアカウンタでもハードウェアカウンタでも良いが、高精度かつ高速カウント処理を実行するためには、ハードウェアカウンタのほうが好ましいことは言うまでもない。

【0016】

第1〜第4カウンタ13−1〜4のそれぞれは、図示を省略するが、被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウンタ部と、このリングカウンタ部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを含んでいる。

【0017】

内部メモリ16には、所定のカウンタ設定情報が格納されている。このカウンタ設定情報としては、各カウンタのそれぞれ毎に、上述のONカウント値、OFFカウント値、及び最大カウント値が含まれている。

【0018】

上位I/F回路(バスなど)14は、CPUモジュール2に繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュールとCPUモジュール2とで共有される共有メモリ(図示せず)を内蔵している。

【0019】

内部制御・演算用マイコン15は、所定のシステムプログラムを実行することによって、上位I/F回路14の共有メモリを介してCPUモジュール2からカウンタ設定情報に関する書替要求が到来したときには、当該要求に従って、内部メモリ16のカウンタ設定情報を書き替える動作を実行する。また、内部制御・演算用マイコン15は、上位I/F回路14の共有メモリを介してCPUモジュール2からカウンタ出力送信要求が到来したときには、当該要求に従って、複数のカウンタ13−1〜4のうちの該当するカウンタのカウント値、及び/又は、状態信号を読み込んで、CPUモジュール2へと受け渡すべく、共有メモリに書き込む動作を実行する。

【0020】

主軸と1又は2以上の従動軸とが連動する制御を実現するためには、主軸エンコーダEから得られるエンコーダパルス列を、第1〜第4カウンタ入力回路11−1〜4へと並列に供給する一方、第1〜第4カウンタ13−1〜4のそれぞれのONカウント値、OFFカウント値を適切に設定する。こうすることで、第1〜第4カウンタ13−1〜4からは、4系統の従動モータのそれぞれに対応する主軸の状態信号を得ることができる。

【0021】

CPUモジュール2の側では、ユーザ(エンドユーザ又はベンダー)が作成したユーザプログラムを実行しつつ、適当なタイミングで、カウンタモジュール1に対してカウンタ出力送信要求を与えることにより、カウンタモジュール側の動作を介して、第1〜第4カウンタ13−1〜4の状態信号を取得する。

【0022】

こうして得られた各カウンタの状態信号に基づいて、CPUモジュール2では、ユーザプログラムに従って、従動軸の動作量の演算を行うと共に、所定の位置制御指令を、モジュール間接続バスを介して位置制御モジュール3へと与える。

【0023】

すると、位置制御モジュール3は、CPUモジュール2から与えられた位置制御指令に基づき、所定の演算を実行することによって、モータ動作指令を生成し、これをモータ駆動装置200へと送信する。これにより、モータ駆動装置200が動作して、従動モータM2が駆動される。

【特許文献1】特開2001−249708号公報

【発明の開示】

【発明が解決しようとする課題】

【0024】

図11に示される従来のカウンタモジュールにあっては、第1〜4カウンタ13−1〜4とその前段に位置する第1〜4カウンタ入力回路11−1〜4とは直結されているため、常に1対1の関係にある。そのため、4個のカウンタ13−1〜4のいずれか1つにおいてカウント動作を行わせたい場合には、必ずそのカウンタの前段に位置するカウンタ入力回路へと、被カウント信号を供給せねばならない。

【0025】

そのため、前述の主軸と従動軸との連動制御を実現するためには、図8(a)に示されるように、主軸エンコーダEの出力パルス列を、外部配線を介して第1〜4カウンタ入力回路11−1〜4(図8(a)では図示せず)の各入力端へと分配するために、煩雑な配線作業を必要とするほか、主軸エンコーダEの出力駆動能力によっては、使用カウンタ数が制約を受けるという問題がある。

【0026】

また、第1〜4カウンタ入力回路11−1〜4又は第1〜4カウンタ13−1〜4のいずれか1つに故障が生じたり、それまで或るカウンタでカウントしていた被カウント入力を別のカウンタでカウントさせたいような場合には、その都度、外部配線の変更作業が必要となるといった問題点もあった。

【0027】

この発明は、このような従来の問題点に着目してなされたものであり、その目的とするところは、カウント入力回路への被カウント信号側配線は変更することなく、その被カウント信号をカウントするカウンタを変更したり、あるいは1のカウンタ入力回路へ供給される被カウント信号を、複数のカウンタへ並列に供給することを可能とするカウント装置を提供することにある。

【0028】

この発明のさらにほかの目的並びに作用効果については、明細書の以下の記述を参照することにより、当業者であれば容易に理解されるであろう。

【課題を解決するための手段】

【0029】

上述の「発明が解決しようとする課題」は、以下の構成を有するカウント装置によって解決できるものと考えられる。

【0030】

すなわち、このカウント装置は、複数個のカウンタと、外部から被カウント信号を取り込むための1若しくは2以上の入力回路と、1若しくは2以上の入力回路の各出力端と複数個のカウンタの各入力端との間に介在される分配切替回路とを包含し、複数個のカウンタのカウント値又はそのカウント値又はそのカウント値に基づいて生成された状態信号を出力信号として外部へと出力するように構成されている。

【0031】

ここで、分配切替回路は、1若しくは2以上の入力回路の各出力端のそれぞれに接続される入力側端子と、複数個のカウンタの各入力端のそれぞれに接続される出力側端子とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされ、それにより複数のカウンタのそれぞれは、分配切替回路を介して自己に供給される被カウント信号をカウントするように構成されている。

【0032】

このような構成によれば、入力回路の各出力端と複数個のカウンタの各入力端との間には分配切替回路が介在され、しかもこの分配切替回路は、入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通を任意に設定可能とされたものであるから、この端子間導通設定を適宜に行うことによって、1のカウンタ入力回路へ供給された被カウント入力を、複数のカウンタへと並列に供給することが可能となる。

【0033】

そして、この端子間導通設定の変更による複数カウンタへの被カウント信号分配方式によれば、分配それ自体はカウント装置の内部で行われるため、分配数がいくつに増加しようとも、主軸エンコーダは1個の入力回路を駆動すれば足り、そのため主軸エンコーダの駆動能力によって、被カウント信号の分配数に制約を受けることもない。

【0034】

また、このような構成によれば、複数のカウンタのいずれかが故障したり、あるいは設計上の都合などにより、それまで或るカウンタでカウントしていた被カウント信号を、別のカウンタでカウントさせる必要が生じたような場合には、これを外部配線を変更することなく、端子間導通設定の変更により実現することもできる。

【0035】

なお、分配切替回路としては、そのようなスイッチング機能を有する専用のワイヤードロジック回路で構成されたASIC、あるいはそのようなスイッチング機能を実現するようにプログラミングされたFPGA(Field Programable Gate Array)などで容易に実現することができる。

【0036】

また、複数のカウンタのそれぞれは、被カウント信号の周波数が低い場合にはソフトウェアカウンタでも差し支えないが、微細な制御を扱う高周波となった場合には、ハードウェアカウンタとすることが好ましいことは言うまでもない。

【0037】

上述のカウント装置において、分配切替回路における導通又は非導通の設定は、所定のメモリに格納された分配切替設定情報に基づいて自動的に行われるものであっても良い。ここで、「自動的に行われる」とは、当該メモリに格納された分配切替設定情報を読み出し、これに従って分配切替回路における導通/非導通設定を行うように組みこまれた専用回路、又はマイコンによるファームウェアを採用すれば良いことを意味している。

【0038】

また、上述のカウント装置において、複数個のカウンタのそれぞれは、被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウント部と、リングカウント部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを包含するものであっても良い。

【0039】

このような構成によれば、単に現在カウント値を出力するのみならず、制御サイクル上において、現在の状態信号を、直接的に出力させることができる。

【0040】

上述のカウント装置において、各カウンタのONカウント値及びOFFカウント値のそれぞれ、及び/又は各カウンタの最大カウント値は、所定のメモリに格納されたカウンタ設定情報に基づいて設定されるものであっても良い。

【0041】

ここで、「カウンタ設定情報に基づいて設定される」とは、所定のメモリに格納されたカウンタ設定情報を読み出すと共に、これに従って、各カウンタのONカウント値及びOFFカウント値のそれぞれ、及び/又は、各カウンタの最大カウント値を設定するように組みこまれたワイヤードロジック回路、又はそのような機能をソフトウェア的に実現するファームウェアを採用できることを意味している。

【0042】

このような構成によれば、各カウンタのカウント動作態様を、メモリに格納されたカウンタ設定情報の書替えを通じて、任意に変更可能となる。

【0043】

上述のカウント装置は、ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールとして構成することもできる。

【0044】

このようなカウント装置は、CPUモジュールに繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュールとCPUモジュールとで共有される共有メモリを内蔵する上位I/F回路と、この上位I/F回路の共有メモリを介してCPUモジュールからカウンタ設定情報に関する書替要求が到来したときには、当該要求に従って、メモリのカウンタ設定情報を書き替える動作を行うカウンタ設定情報書替手段と、上位I/F回路の共有メモリを介してCPUモジュールからカウンタ出力送信要求が到来したときには、当該要求に従って、複数のカウンタのうちの該当するカウンタのカウント値、及び/又は、状態信号を読み込んで、CPUモジュールへと受け渡すべく、共有メモリに書き込む動作を行うカウンタ出力送信手段とを含むものであっても良い。

【0045】

このような構成によれば、ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールに対して、上述の端子間導通設定操作を可能とすることで、カウンタモジュールの使い勝手を向上することができる。

【0046】

このとき、上述のカウンタ情報書替手段及びカウンタ出力送信手段の各機能は、内部制御演算用マイコンによりソフトウェア的に実現するようにしても良い。

【0047】

上述の端子間導通設定変更機能を有するカウント装置の使用方法としては、前記分配切替回路において、1の入力側端子と2以上の出力側端子とが導通するように端子間導通設定を行うと共に、前記1の入力側端子の前段に位置する入力回路には、主軸エンコーダの出力パルス列を供給し、さらに前記2以上の出力側端子の各後段に位置するカウンタのそれぞれから、従動軸制御用のカウンタ出力を取り出すといった方法が考えられる。

【0048】

このようなカウント装置の使用方法によれば、従来問題とされた、分配用外部配線や配線切替作業が不要となり、カウンタモジュールを使用する際の配線作業効率化を実現することができる。

【発明の効果】

【0049】

本発明のカウント装置によれば、入力回路の各出力端と複数個のカウンタの各入力端との間には分配切替回路が介在され、しかもこの分配切替回路は、入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通を任意に設定可能とされたものであるから、この端子間導通設定を適宜に行うことによって、1のカウンタ入力回路へ供給された被カウント入力を、複数のカウンタへと並列に供給することが可能となる。

【0050】

そして、この端子間導通設定の変更による複数カウンタへの被カウント信号分配方式によれば、分配それ自体はカウント装置の内部で行われるため、分配数がいくつに増加しようとも、主軸エンコーダは1個の入力回路を駆動すれば足り、そのため主軸エンコーダの駆動能力によって、被カウント信号の分配数に制約を受けることもない。

【0051】

また、このような構成によれば、複数のカウンタのいずれかが故障したり、あるいは設計上の都合などにより、それまで或るカウンタでカウントしていた被カウント信号を、別のカウンタでカウントさせる必要が生じたような場合には、これを外部配線を変更することなく、端子間導通設定の変更により実現することもできる。

【発明を実施するための最良の形態】

【0052】

以下に、本発明に係るカウント装置の好適な実施の一形態を添付図面に従って詳細に説明する。なお、本発明は特許請求の範囲の記載に基づいてその範囲が定義されるものであって、その範囲が以下の実施形態の構成により限定されることのないことは言うまでもない。

【0053】

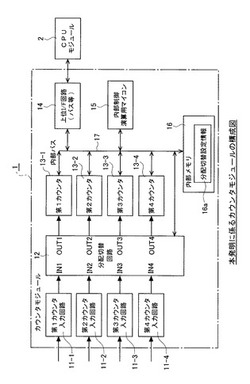

本発明に係るカウンタモジュールの構成図が図1に示されている。なお、図において、前述の従来例と同一構成部分については同符号を付している。

【0054】

同図に示されるように、このカウンタモジュール1は、複数個(この例では4個)のカウンタ(第1カウンタ13−1、第2カウンタ13−2、第3カウンタ13−3、第4カウンタ13−4)と、外部から被カウント信号を取り込むための1若しくは2以上(この例では4個)の入力回路(第1カウンタ入力回路11−1、第2カウンタ入力回路11−2、第3カウンタ入力回路11−3、第4カウンタ入力回路11−4)と、4個の入力回路11−1〜4の各出力端と4個のカウンタ13−1〜4の各入力端との間に介在される分配切替回路12とを包含している。

【0055】

分配切替回路12は、入力回路11−1〜4の各出力端のそれぞれに接続される入力側端子IN1〜IN4と、4個のカウンタ13−1〜4の各入力端のそれぞれに接続される出力側端子OUT1〜OUT4とを有し、かつ入力側端子IN1〜IN4のそれぞれと出力側端子OUT1〜OUT4のそれぞれとの間における導通又は非導通は、任意に設定可能とされ、それにより、複数のカウンタ13−1〜4のそれぞれは、分配切替回路12を介して自己に供給される被カウント信号をカウントするようになっている。

【0056】

なお、図3、図4、図5を参照して後に詳細に説明するように、分配切替回路12における導通又は非導通の設定は、内部メモリ16に格納された分配切替設定情報16aに基づいて自動的に行われるようになっている。

【0057】

4個のカウンタ13−1〜4のそれぞれは、図示を省略するが、被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値にリセットされるリングカウント部と、リングカウント部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを包含している。

【0058】

各カウンタ13−1〜4のONカウント値及びOFFカウント値のそれぞれ、及び/又は、各カウンタの最大カウント値は、後に図6を参照して説明するように、内部メモリ16に格納されたカウンタ設定情報に基づいて設定される。

【0059】

上位I/F回路(バスなど)14は、CPUモジュール2に繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュール1とCPUモジュール2とで共有される共有メモリ(図示せず)を内蔵している。

【0060】

内部制御演算用マイコン15は、図5に示される通常処理及び図7に示される割込処理を実行することによって、「カウンタ設定情報書替手段」及び「カウンタ出力送信手段」として機能を実現するものである。

【0061】

すなわち、内部制御演算用マイコンの通常処理全体を示すフローチャートが図5に示されている。同図において、電源投入などにより処理が開始されると、まず、イニシャライズ処理(ステップ101)を実行して、制御に必要な各種フラグやレジスタの初期化を行った後、共有メモリ参照処理(ステップ102)、CPUデータ有無判定処理(ステップ103)、システムサービス処理(ステップ110)、停止指令有無判定処理(ステップ111)を繰り返し実行する。

【0062】

共有メモリ参照処理(ステップ102)では、上位I/F回路14に内蔵される共有メモリの所定エリアに、CPUモジュール2から何らかのCPUデータが書き込まれているか否かの判定を行う。

【0063】

システムサービス処理(ステップ110)では、表示処理や故障診断処理といった一般的なシステムサービス処理のほかに、分配切替設定情報(図4参照)に従って、分配切替回路12を必要な導通/非導通状態に設定する処理、カウンタ設定情報(図6参照)に従って各カウンタ13−1〜4のONカウント値、OFFカウント値、最大カウント値を設定する処理などを実行する。

【0064】

停止指令有無判定処理(ステップ111)は、ユーザの操作又はCPUモジュールからの指令によって、停止指令が与えられたかどうかを判定する処理である。

【0065】

以上の処理を繰り返す間に、CPUデータありと判定されると(ステップ103YES)、そのCPUデータが共有メモリから読み出され(ステップ104)、こうして読み出されたCPUデータの内容が判定される。

【0066】

ここで、CPUデータの内容が、「カウンタ設定書替要求」であると判定されると(ステップ105YES)、該当カウンタの設定情報書替処理(ステップ106)が実行される。

【0067】

カウンタ設定情報の一例を示す説明図が図6に表にして示されている。同図に示されるように、カウンタ設定情報は、第1カウンタ〜第4カウンタのそれぞれに対応して、ONカウント値、OFFカウント値、最大カウント値を含んで構成されている。先に説明したように、これらのカウンタ設定情報は、システムサービス処理(ステップ110)において参照され、各カウンタ13−1〜4内に設定されて、リングカウント動作や状態信号生成動作に供される。

【0068】

一方、CPUデータが「分配切替設定書替要求」であると判定されると(ステップ107YES)、続いて分配切替設定書替処理(ステップ108)が実行されて、内部メモリ16内における分配切替設定情報16aの書替えが行われる。

【0069】

内部メモリ内の設定情報記憶領域の構成を示すメモリマップが図3に、分配切替設定情報の一例を示す説明図が図4にそれぞれ示されている。

【0070】

それらの図から明らかなように、この例にあっては、内部メモリ16内の設定情報記憶領域は、Bit00〜Bit15からなる16ビット(2バイト)構成とされている。そして、それらのビットBit00〜Bit15は、図4に示されるように、入力側端子IN1〜IN4と出力側端子OUT1〜OUT4とのマトリクスの交点に対応している。

【0071】

図4に示される分配切替設定情報は、図2に破線で示されるように、分配切替回路12において、1個の入力側端子IN1と4個の出力側端子OUT1〜OUT4とを導通状態とし、その他の入力側端子IN2〜IN4は出力側端子OUT1〜OUT4のいずれとも非導通状態とさせるための設定である。

【0072】

このようにBit00〜Bit03を全て“1”とすると共に、Bit04〜Bit15を全て“0”とすることによって、図2に示されるような端子間導通状態を実現することができる。なお、実際に分配切替回路12をそのように動作させるための処理は、システムサービス処理(ステップ110)において、分配切替設定情報に応じて、分配切替処理を実行することによって実現される。

【0073】

先に説明したように、分配切替回路12は、謂わば交換機の機能に相当するものであって、実際には、そのような機能が組みこまれたASIC又はそのような機能がプログラミングされたFPGAなどによって容易に実現することができる。

【0074】

一方、CPUデータがその他の意味内容を有するものと判定されれば(ステップ107NO)、該当するその他の処理が実行される(ステップ109)。そして、CPUモジュールから又は当該カウンタモジュールに設けられたスナップスイッチ等によって、停止指令が与えられると(ステップ111YES)、処理は終了する。

【0075】

次に、内部制御演算用マイコンのカウンタ出力読出処理を示すフローチャートが図7に示されている。このフローチャートに示される処理は、CPUモジュールからの割込処理によって実行される。

【0076】

同図において処理が開始されると、割込種別判定処理(ステップ201)が実行される。ここで、割込種別が、CPUモジュールからの「カウンタ出力送信要求」であると判定されると(ステップ202YES)、該当カウンタに関する出力読込の処理(ステップ203)が実行される。ここで言う「該当カウンタの出力」には、当該カウンタの現在カウント値、状態信号のON/OFF状態などが含まれている。

【0077】

そして、こうして読み込まれた該当カウンタの出力は、共有メモリの所定エリアにセットされ(ステップ204)、これによりCPUモジュール2からの読み出しを可能とする。すなわち、CPUモジュール2の側では、「カウンタ出力送信要求」を割込送信した後、共有メモリの該当エリアから所定データの読み出しを行うことによって、カウンタモジュール1が生成したカウント出力を取得することができるのである。

【0078】

なお、割込種別が「カウンタ出力送信要求」でなければ(ステップ202NO)、その他の処理が実行される(ステップ205)。

【0079】

最後に、従来と本発明とで使用例を比較して示す説明図が図8に示されている。同図(a)に示されるように、従来のカウンタモジュールの使用例の場合、主軸と1若しくは2以上の従動軸との連動処理を実現するためには、カウンタモジュールの外部において、主軸エンコーダEの出力を各カウンタに分配するために、分配用の外部配線が必要であった。

【0080】

これに対して、同図(b)に示されるように、本発明のカウンタモジュールの使用例の場合、図中破線で示されるように、主軸エンコーダEの出力パルスは、カウンタモジュールの内部において各カウンタに分配される。そのため、図から明らかなように、カウンタモジュールの外部には分配のための外部配線は不要となる。しかも、図2に示されるように、主軸エンコーダEにて駆動されるべきものは、1個の入力回路(第1カウンタ入力回路11−1)だけであるから、信号分配数が増大したとしても、主軸エンコーダの駆動能力には問題がなく、逆に、主軸エンコーダの駆動能力によって信号分配数に制限を受けるという問題を解決することができる。

【0081】

また、本発明のカウンタモジュールの使用例にあっては、各カウンタ13−1〜4は、分配切替回路12を介して送られてくる被カウント信号をカウントするものであるから、第1〜第4カウンタ13−1〜4のいずれかが故障したことにより、あるいは設計変更などによって、それまで或るカウンタがカウントしていた被カウント信号を、別のカウンタでカウントさせたいような場合には、入力側端子IN1〜IN4と出力側端子OUT1〜OUT4との導通/非導通の関係を変更するだけで、外部配線については何ら接続変更等を行うことなく、対応させることができ、煩わしい配線作業がなくなることで、この種のカウンタモジュールにおける使い勝手を格段に向上させることができる。

【0082】

なお、以上の実施形態においては、本発明に係るカウント装置を、ビルディングブロック型PLCのカウンタモジュールに応用したが、本発明のカウント装置は、それ自体で出力装置を内蔵することで、スタンドアローン形式のカウント装置として実現できることは勿論である。

【0083】

その際に、分配切替回路12については、入力側端子IN1〜IN4を出力側端子OUT1〜OUT4のいずれかに接続可能な多種切替スイッチ(手動又は自動)として単純化することもできる。

【産業上の利用可能性】

【0084】

本発明のカウント装置は、ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールとして応用することにより、外部配線の手間を省いて、その使い勝手を向上させることができる。

【図面の簡単な説明】

【0085】

【図1】本発明に係るカウンタモジュールの構成図である。

【図2】本発明に係るカウンタモジュールの使用例を示す説明図である。

【図3】内部メモリ内の設定情報記憶領域の構成を示すメモリマップである。

【図4】分配切り換え設定情報の一例を示す説明図である。

【図5】内部制御演算用マイコンの処理全体を示すフローチャートである。

【図6】カウンタ設定情報の一例を示す説明図である。

【図7】内部制御演算用マイコンのカウンタ出力読出処理を示すフローチャートである。

【図8】従来と本発明とで使用例を比較して示す説明図である。

【図9】複数のカウンタを使用した制御システムの一例を示す説明図である。

【図10】カウンタモジュールを含むPLCを用いた制御システムの一例を示す説明図である。

【図11】従来のカウンタモジュールの構成図である。

【符号の説明】

【0086】

1 カウンタモジュール

2 CPUモジュール

3 位置制御モジュール

11−1〜11−4 カウンタ入力回路

12 分配切替回路

13−1〜13−4 カウンタ

14 上位I/F回路(バスなど)

15 内部制御演算用マイコン

16 内部メモリ

16a 分配切替設定情報

17 内部バス

100 PLC

200 モータ駆動装置

31 巻き取りロール

32 主軸

33 主軸エンコーダ

34 負極シートカッタ

35 正極シートカッタ

36−1〜3 カウンタ

37−1 ガイドローラ位置制御部

37−2 正極シートカッタ制御部

37−3 負極シートカッタ制御部

E 主軸エンコーダ

M1 主軸モータ

M2 従動モータ

【技術分野】

【0001】

この発明は、複数のカウンタを内蔵すると共に、それらのカウンタのカウント値又はそのカウント値に基づいて生成された状態信号を出力信号として外部へと出力するカウント装置に関する。

【背景技術】

【0002】

基本となる1つの動作部と、1若しくは2以上のその他の動作部とを互いに連動させることによって、目的を達するようにした自動処理装置の制御に当たっては、複数のカウンタを使用した制御システムがしばしば採用される。

【0003】

このような複数のカウンタを使用した制御システムの一例を示す説明図が図9に示されている。なお、図示の制御システムは、ガイドローラ駆動部、正極シートカット動作部、負極シートカット部、及びシート巻き取り動作部を有する二次電池電極製造装置に適用されるものである。

【0004】

同図(a)に示されるように、この二次電池電極製造装置は、絶縁シート、負極シート、絶縁シート、及び正極シートからなる4枚のシートを、ガイドローラにて適宜に供給経路をガイドしつつ1点に供給して、巻き取りローラ31に重ねて巻き取らせると共に、適当なインターバルで負極シートカッタ34及び正極シートカッタ35を作動させることにより、所望の積層構造を有する二次電池電極をロール体として完成するものである。

【0005】

シート巻き取りローラ31に連動する主軸32の回転は、主軸エンコーダ33を介してパルス列に変換される。こうして得られた主軸エンコーダ33からのパルス列は、第1カウンタ36−1、第2カウンタ36−2、第3カウンタ36−3へと並列に供給される。

【0006】

それらのカウンタ36−1〜3のそれぞれは、被カウント信号である主軸エンコーダ33からのパルス列をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウンタ部と、このリングカウンタ部のカウント値を、所定のONタイミング値及びOFFタイミング値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを含んでいる。

【0007】

ガイドローラ位置制御部37−1は、第1カウンタ36−1から得られる状態信号により起動され、ガイドローラ駆動部における所定の動作を制御する。正極シートカット制御部37−2は、第2カウンタ36−2から得られる状態信号により起動され、正極シートカッタ35における所定の動作を制御する。負極シートカット制御部37−3は、第3カウンタ36−3から得られる状態信号により起動され、負極シートカッタ34における所定の動作を制御する。

【0008】

同図(b)に示されるように、各カウンタ36−1〜3から得られる状態信号のON/OFFタイミングは、ガイドローラ駆動部、正極シートカッタ、負極シートカッタのそれぞれにおける動作タイミングに合わせて設定されている。

【0009】

そのため、このような制御システムによれば、シート巻き取り動作に連動して、ガイドローラの動作、正極シートカット動作、及び負極シートカット動作を適切に行わせることができる。しかも、3台のカウンタ36−1〜3におけるONカウント値、OFFカウント値を変更することで、各動作部間における動作関係の変更にも容易に対応することができる。

【0010】

この種の制御システムは、一般に、カウンタモジュールを含むビルディングブロック型のプログラマブルコントローラ(以下、PLCと言う)により実現することができる(例えば、特許文献1参照)。

【0011】

カウンタモジュールを含むPLCを用いた制御システムの一例を示す説明図が図10に示されている。

【0012】

同図に示されるように、この制御システムは、主軸モータM1と連動して主軸回転量情報(エンコーダパルス)を出力する主軸エンコーダEと、主軸回転量情報に基づいて所定のユーザプログラムを実行することにより、モータ動作指令を生成するPLC100と、PLC100から得られるモータ動作指令に基づいて従動モータM2を駆動するモータ駆動装置200とを含んで構成される。

【0013】

PLC100は、この例にあっては、PLC全体を統括制御するCPUモジュール2と、一般的な入出力信号のやりとりを外部と行うための入出力モジュール(図示せず)と、主軸回転量情報(エンコーダパルス)をカウントして、各従動軸に対応する主軸の状態信号をCPUモジュール2へ出力する複数のカウンタを備えたカウンタモジュール1と、CPUモジュール2から与えられる位置制御指令に応答して、モータ動作指令を生成する位置制御モジュール3とを含んで構成される。

【0014】

従来のカウンタモジュールの一例を示す構成図が図11に示されている。同図に示されるように、このカウンタモジュール1は、複数個(この例では4個)のカウンタ(第1カウンタ13−1、第2カウンタ13−2、第3カウンタ13−3、第4カウンタ13−4)と、外部から被カウント信号を取り込むための前記カウンタと同数の入力回路(第1カウンタ入力回路11−1、第2カウンタ入力回路11−2、第3カウンタ入力回路11−3、第4カウンタ入力回路11−4)とを有している。

【0015】

なお、第1〜第4カウンタ13−1〜4としては、ソフトウェアカウンタでもハードウェアカウンタでも良いが、高精度かつ高速カウント処理を実行するためには、ハードウェアカウンタのほうが好ましいことは言うまでもない。

【0016】

第1〜第4カウンタ13−1〜4のそれぞれは、図示を省略するが、被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウンタ部と、このリングカウンタ部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを含んでいる。

【0017】

内部メモリ16には、所定のカウンタ設定情報が格納されている。このカウンタ設定情報としては、各カウンタのそれぞれ毎に、上述のONカウント値、OFFカウント値、及び最大カウント値が含まれている。

【0018】

上位I/F回路(バスなど)14は、CPUモジュール2に繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュールとCPUモジュール2とで共有される共有メモリ(図示せず)を内蔵している。

【0019】

内部制御・演算用マイコン15は、所定のシステムプログラムを実行することによって、上位I/F回路14の共有メモリを介してCPUモジュール2からカウンタ設定情報に関する書替要求が到来したときには、当該要求に従って、内部メモリ16のカウンタ設定情報を書き替える動作を実行する。また、内部制御・演算用マイコン15は、上位I/F回路14の共有メモリを介してCPUモジュール2からカウンタ出力送信要求が到来したときには、当該要求に従って、複数のカウンタ13−1〜4のうちの該当するカウンタのカウント値、及び/又は、状態信号を読み込んで、CPUモジュール2へと受け渡すべく、共有メモリに書き込む動作を実行する。

【0020】

主軸と1又は2以上の従動軸とが連動する制御を実現するためには、主軸エンコーダEから得られるエンコーダパルス列を、第1〜第4カウンタ入力回路11−1〜4へと並列に供給する一方、第1〜第4カウンタ13−1〜4のそれぞれのONカウント値、OFFカウント値を適切に設定する。こうすることで、第1〜第4カウンタ13−1〜4からは、4系統の従動モータのそれぞれに対応する主軸の状態信号を得ることができる。

【0021】

CPUモジュール2の側では、ユーザ(エンドユーザ又はベンダー)が作成したユーザプログラムを実行しつつ、適当なタイミングで、カウンタモジュール1に対してカウンタ出力送信要求を与えることにより、カウンタモジュール側の動作を介して、第1〜第4カウンタ13−1〜4の状態信号を取得する。

【0022】

こうして得られた各カウンタの状態信号に基づいて、CPUモジュール2では、ユーザプログラムに従って、従動軸の動作量の演算を行うと共に、所定の位置制御指令を、モジュール間接続バスを介して位置制御モジュール3へと与える。

【0023】

すると、位置制御モジュール3は、CPUモジュール2から与えられた位置制御指令に基づき、所定の演算を実行することによって、モータ動作指令を生成し、これをモータ駆動装置200へと送信する。これにより、モータ駆動装置200が動作して、従動モータM2が駆動される。

【特許文献1】特開2001−249708号公報

【発明の開示】

【発明が解決しようとする課題】

【0024】

図11に示される従来のカウンタモジュールにあっては、第1〜4カウンタ13−1〜4とその前段に位置する第1〜4カウンタ入力回路11−1〜4とは直結されているため、常に1対1の関係にある。そのため、4個のカウンタ13−1〜4のいずれか1つにおいてカウント動作を行わせたい場合には、必ずそのカウンタの前段に位置するカウンタ入力回路へと、被カウント信号を供給せねばならない。

【0025】

そのため、前述の主軸と従動軸との連動制御を実現するためには、図8(a)に示されるように、主軸エンコーダEの出力パルス列を、外部配線を介して第1〜4カウンタ入力回路11−1〜4(図8(a)では図示せず)の各入力端へと分配するために、煩雑な配線作業を必要とするほか、主軸エンコーダEの出力駆動能力によっては、使用カウンタ数が制約を受けるという問題がある。

【0026】

また、第1〜4カウンタ入力回路11−1〜4又は第1〜4カウンタ13−1〜4のいずれか1つに故障が生じたり、それまで或るカウンタでカウントしていた被カウント入力を別のカウンタでカウントさせたいような場合には、その都度、外部配線の変更作業が必要となるといった問題点もあった。

【0027】

この発明は、このような従来の問題点に着目してなされたものであり、その目的とするところは、カウント入力回路への被カウント信号側配線は変更することなく、その被カウント信号をカウントするカウンタを変更したり、あるいは1のカウンタ入力回路へ供給される被カウント信号を、複数のカウンタへ並列に供給することを可能とするカウント装置を提供することにある。

【0028】

この発明のさらにほかの目的並びに作用効果については、明細書の以下の記述を参照することにより、当業者であれば容易に理解されるであろう。

【課題を解決するための手段】

【0029】

上述の「発明が解決しようとする課題」は、以下の構成を有するカウント装置によって解決できるものと考えられる。

【0030】

すなわち、このカウント装置は、複数個のカウンタと、外部から被カウント信号を取り込むための1若しくは2以上の入力回路と、1若しくは2以上の入力回路の各出力端と複数個のカウンタの各入力端との間に介在される分配切替回路とを包含し、複数個のカウンタのカウント値又はそのカウント値又はそのカウント値に基づいて生成された状態信号を出力信号として外部へと出力するように構成されている。

【0031】

ここで、分配切替回路は、1若しくは2以上の入力回路の各出力端のそれぞれに接続される入力側端子と、複数個のカウンタの各入力端のそれぞれに接続される出力側端子とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされ、それにより複数のカウンタのそれぞれは、分配切替回路を介して自己に供給される被カウント信号をカウントするように構成されている。

【0032】

このような構成によれば、入力回路の各出力端と複数個のカウンタの各入力端との間には分配切替回路が介在され、しかもこの分配切替回路は、入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通を任意に設定可能とされたものであるから、この端子間導通設定を適宜に行うことによって、1のカウンタ入力回路へ供給された被カウント入力を、複数のカウンタへと並列に供給することが可能となる。

【0033】

そして、この端子間導通設定の変更による複数カウンタへの被カウント信号分配方式によれば、分配それ自体はカウント装置の内部で行われるため、分配数がいくつに増加しようとも、主軸エンコーダは1個の入力回路を駆動すれば足り、そのため主軸エンコーダの駆動能力によって、被カウント信号の分配数に制約を受けることもない。

【0034】

また、このような構成によれば、複数のカウンタのいずれかが故障したり、あるいは設計上の都合などにより、それまで或るカウンタでカウントしていた被カウント信号を、別のカウンタでカウントさせる必要が生じたような場合には、これを外部配線を変更することなく、端子間導通設定の変更により実現することもできる。

【0035】

なお、分配切替回路としては、そのようなスイッチング機能を有する専用のワイヤードロジック回路で構成されたASIC、あるいはそのようなスイッチング機能を実現するようにプログラミングされたFPGA(Field Programable Gate Array)などで容易に実現することができる。

【0036】

また、複数のカウンタのそれぞれは、被カウント信号の周波数が低い場合にはソフトウェアカウンタでも差し支えないが、微細な制御を扱う高周波となった場合には、ハードウェアカウンタとすることが好ましいことは言うまでもない。

【0037】

上述のカウント装置において、分配切替回路における導通又は非導通の設定は、所定のメモリに格納された分配切替設定情報に基づいて自動的に行われるものであっても良い。ここで、「自動的に行われる」とは、当該メモリに格納された分配切替設定情報を読み出し、これに従って分配切替回路における導通/非導通設定を行うように組みこまれた専用回路、又はマイコンによるファームウェアを採用すれば良いことを意味している。

【0038】

また、上述のカウント装置において、複数個のカウンタのそれぞれは、被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウント部と、リングカウント部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを包含するものであっても良い。

【0039】

このような構成によれば、単に現在カウント値を出力するのみならず、制御サイクル上において、現在の状態信号を、直接的に出力させることができる。

【0040】

上述のカウント装置において、各カウンタのONカウント値及びOFFカウント値のそれぞれ、及び/又は各カウンタの最大カウント値は、所定のメモリに格納されたカウンタ設定情報に基づいて設定されるものであっても良い。

【0041】

ここで、「カウンタ設定情報に基づいて設定される」とは、所定のメモリに格納されたカウンタ設定情報を読み出すと共に、これに従って、各カウンタのONカウント値及びOFFカウント値のそれぞれ、及び/又は、各カウンタの最大カウント値を設定するように組みこまれたワイヤードロジック回路、又はそのような機能をソフトウェア的に実現するファームウェアを採用できることを意味している。

【0042】

このような構成によれば、各カウンタのカウント動作態様を、メモリに格納されたカウンタ設定情報の書替えを通じて、任意に変更可能となる。

【0043】

上述のカウント装置は、ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールとして構成することもできる。

【0044】

このようなカウント装置は、CPUモジュールに繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュールとCPUモジュールとで共有される共有メモリを内蔵する上位I/F回路と、この上位I/F回路の共有メモリを介してCPUモジュールからカウンタ設定情報に関する書替要求が到来したときには、当該要求に従って、メモリのカウンタ設定情報を書き替える動作を行うカウンタ設定情報書替手段と、上位I/F回路の共有メモリを介してCPUモジュールからカウンタ出力送信要求が到来したときには、当該要求に従って、複数のカウンタのうちの該当するカウンタのカウント値、及び/又は、状態信号を読み込んで、CPUモジュールへと受け渡すべく、共有メモリに書き込む動作を行うカウンタ出力送信手段とを含むものであっても良い。

【0045】

このような構成によれば、ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールに対して、上述の端子間導通設定操作を可能とすることで、カウンタモジュールの使い勝手を向上することができる。

【0046】

このとき、上述のカウンタ情報書替手段及びカウンタ出力送信手段の各機能は、内部制御演算用マイコンによりソフトウェア的に実現するようにしても良い。

【0047】

上述の端子間導通設定変更機能を有するカウント装置の使用方法としては、前記分配切替回路において、1の入力側端子と2以上の出力側端子とが導通するように端子間導通設定を行うと共に、前記1の入力側端子の前段に位置する入力回路には、主軸エンコーダの出力パルス列を供給し、さらに前記2以上の出力側端子の各後段に位置するカウンタのそれぞれから、従動軸制御用のカウンタ出力を取り出すといった方法が考えられる。

【0048】

このようなカウント装置の使用方法によれば、従来問題とされた、分配用外部配線や配線切替作業が不要となり、カウンタモジュールを使用する際の配線作業効率化を実現することができる。

【発明の効果】

【0049】

本発明のカウント装置によれば、入力回路の各出力端と複数個のカウンタの各入力端との間には分配切替回路が介在され、しかもこの分配切替回路は、入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通を任意に設定可能とされたものであるから、この端子間導通設定を適宜に行うことによって、1のカウンタ入力回路へ供給された被カウント入力を、複数のカウンタへと並列に供給することが可能となる。

【0050】

そして、この端子間導通設定の変更による複数カウンタへの被カウント信号分配方式によれば、分配それ自体はカウント装置の内部で行われるため、分配数がいくつに増加しようとも、主軸エンコーダは1個の入力回路を駆動すれば足り、そのため主軸エンコーダの駆動能力によって、被カウント信号の分配数に制約を受けることもない。

【0051】

また、このような構成によれば、複数のカウンタのいずれかが故障したり、あるいは設計上の都合などにより、それまで或るカウンタでカウントしていた被カウント信号を、別のカウンタでカウントさせる必要が生じたような場合には、これを外部配線を変更することなく、端子間導通設定の変更により実現することもできる。

【発明を実施するための最良の形態】

【0052】

以下に、本発明に係るカウント装置の好適な実施の一形態を添付図面に従って詳細に説明する。なお、本発明は特許請求の範囲の記載に基づいてその範囲が定義されるものであって、その範囲が以下の実施形態の構成により限定されることのないことは言うまでもない。

【0053】

本発明に係るカウンタモジュールの構成図が図1に示されている。なお、図において、前述の従来例と同一構成部分については同符号を付している。

【0054】

同図に示されるように、このカウンタモジュール1は、複数個(この例では4個)のカウンタ(第1カウンタ13−1、第2カウンタ13−2、第3カウンタ13−3、第4カウンタ13−4)と、外部から被カウント信号を取り込むための1若しくは2以上(この例では4個)の入力回路(第1カウンタ入力回路11−1、第2カウンタ入力回路11−2、第3カウンタ入力回路11−3、第4カウンタ入力回路11−4)と、4個の入力回路11−1〜4の各出力端と4個のカウンタ13−1〜4の各入力端との間に介在される分配切替回路12とを包含している。

【0055】

分配切替回路12は、入力回路11−1〜4の各出力端のそれぞれに接続される入力側端子IN1〜IN4と、4個のカウンタ13−1〜4の各入力端のそれぞれに接続される出力側端子OUT1〜OUT4とを有し、かつ入力側端子IN1〜IN4のそれぞれと出力側端子OUT1〜OUT4のそれぞれとの間における導通又は非導通は、任意に設定可能とされ、それにより、複数のカウンタ13−1〜4のそれぞれは、分配切替回路12を介して自己に供給される被カウント信号をカウントするようになっている。

【0056】

なお、図3、図4、図5を参照して後に詳細に説明するように、分配切替回路12における導通又は非導通の設定は、内部メモリ16に格納された分配切替設定情報16aに基づいて自動的に行われるようになっている。

【0057】

4個のカウンタ13−1〜4のそれぞれは、図示を省略するが、被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値にリセットされるリングカウント部と、リングカウント部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、ONカウント値との一致タイミング及びOFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを包含している。

【0058】

各カウンタ13−1〜4のONカウント値及びOFFカウント値のそれぞれ、及び/又は、各カウンタの最大カウント値は、後に図6を参照して説明するように、内部メモリ16に格納されたカウンタ設定情報に基づいて設定される。

【0059】

上位I/F回路(バスなど)14は、CPUモジュール2に繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュール1とCPUモジュール2とで共有される共有メモリ(図示せず)を内蔵している。

【0060】

内部制御演算用マイコン15は、図5に示される通常処理及び図7に示される割込処理を実行することによって、「カウンタ設定情報書替手段」及び「カウンタ出力送信手段」として機能を実現するものである。

【0061】

すなわち、内部制御演算用マイコンの通常処理全体を示すフローチャートが図5に示されている。同図において、電源投入などにより処理が開始されると、まず、イニシャライズ処理(ステップ101)を実行して、制御に必要な各種フラグやレジスタの初期化を行った後、共有メモリ参照処理(ステップ102)、CPUデータ有無判定処理(ステップ103)、システムサービス処理(ステップ110)、停止指令有無判定処理(ステップ111)を繰り返し実行する。

【0062】

共有メモリ参照処理(ステップ102)では、上位I/F回路14に内蔵される共有メモリの所定エリアに、CPUモジュール2から何らかのCPUデータが書き込まれているか否かの判定を行う。

【0063】

システムサービス処理(ステップ110)では、表示処理や故障診断処理といった一般的なシステムサービス処理のほかに、分配切替設定情報(図4参照)に従って、分配切替回路12を必要な導通/非導通状態に設定する処理、カウンタ設定情報(図6参照)に従って各カウンタ13−1〜4のONカウント値、OFFカウント値、最大カウント値を設定する処理などを実行する。

【0064】

停止指令有無判定処理(ステップ111)は、ユーザの操作又はCPUモジュールからの指令によって、停止指令が与えられたかどうかを判定する処理である。

【0065】

以上の処理を繰り返す間に、CPUデータありと判定されると(ステップ103YES)、そのCPUデータが共有メモリから読み出され(ステップ104)、こうして読み出されたCPUデータの内容が判定される。

【0066】

ここで、CPUデータの内容が、「カウンタ設定書替要求」であると判定されると(ステップ105YES)、該当カウンタの設定情報書替処理(ステップ106)が実行される。

【0067】

カウンタ設定情報の一例を示す説明図が図6に表にして示されている。同図に示されるように、カウンタ設定情報は、第1カウンタ〜第4カウンタのそれぞれに対応して、ONカウント値、OFFカウント値、最大カウント値を含んで構成されている。先に説明したように、これらのカウンタ設定情報は、システムサービス処理(ステップ110)において参照され、各カウンタ13−1〜4内に設定されて、リングカウント動作や状態信号生成動作に供される。

【0068】

一方、CPUデータが「分配切替設定書替要求」であると判定されると(ステップ107YES)、続いて分配切替設定書替処理(ステップ108)が実行されて、内部メモリ16内における分配切替設定情報16aの書替えが行われる。

【0069】

内部メモリ内の設定情報記憶領域の構成を示すメモリマップが図3に、分配切替設定情報の一例を示す説明図が図4にそれぞれ示されている。

【0070】

それらの図から明らかなように、この例にあっては、内部メモリ16内の設定情報記憶領域は、Bit00〜Bit15からなる16ビット(2バイト)構成とされている。そして、それらのビットBit00〜Bit15は、図4に示されるように、入力側端子IN1〜IN4と出力側端子OUT1〜OUT4とのマトリクスの交点に対応している。

【0071】

図4に示される分配切替設定情報は、図2に破線で示されるように、分配切替回路12において、1個の入力側端子IN1と4個の出力側端子OUT1〜OUT4とを導通状態とし、その他の入力側端子IN2〜IN4は出力側端子OUT1〜OUT4のいずれとも非導通状態とさせるための設定である。

【0072】

このようにBit00〜Bit03を全て“1”とすると共に、Bit04〜Bit15を全て“0”とすることによって、図2に示されるような端子間導通状態を実現することができる。なお、実際に分配切替回路12をそのように動作させるための処理は、システムサービス処理(ステップ110)において、分配切替設定情報に応じて、分配切替処理を実行することによって実現される。

【0073】

先に説明したように、分配切替回路12は、謂わば交換機の機能に相当するものであって、実際には、そのような機能が組みこまれたASIC又はそのような機能がプログラミングされたFPGAなどによって容易に実現することができる。

【0074】

一方、CPUデータがその他の意味内容を有するものと判定されれば(ステップ107NO)、該当するその他の処理が実行される(ステップ109)。そして、CPUモジュールから又は当該カウンタモジュールに設けられたスナップスイッチ等によって、停止指令が与えられると(ステップ111YES)、処理は終了する。

【0075】

次に、内部制御演算用マイコンのカウンタ出力読出処理を示すフローチャートが図7に示されている。このフローチャートに示される処理は、CPUモジュールからの割込処理によって実行される。

【0076】

同図において処理が開始されると、割込種別判定処理(ステップ201)が実行される。ここで、割込種別が、CPUモジュールからの「カウンタ出力送信要求」であると判定されると(ステップ202YES)、該当カウンタに関する出力読込の処理(ステップ203)が実行される。ここで言う「該当カウンタの出力」には、当該カウンタの現在カウント値、状態信号のON/OFF状態などが含まれている。

【0077】

そして、こうして読み込まれた該当カウンタの出力は、共有メモリの所定エリアにセットされ(ステップ204)、これによりCPUモジュール2からの読み出しを可能とする。すなわち、CPUモジュール2の側では、「カウンタ出力送信要求」を割込送信した後、共有メモリの該当エリアから所定データの読み出しを行うことによって、カウンタモジュール1が生成したカウント出力を取得することができるのである。

【0078】

なお、割込種別が「カウンタ出力送信要求」でなければ(ステップ202NO)、その他の処理が実行される(ステップ205)。

【0079】

最後に、従来と本発明とで使用例を比較して示す説明図が図8に示されている。同図(a)に示されるように、従来のカウンタモジュールの使用例の場合、主軸と1若しくは2以上の従動軸との連動処理を実現するためには、カウンタモジュールの外部において、主軸エンコーダEの出力を各カウンタに分配するために、分配用の外部配線が必要であった。

【0080】

これに対して、同図(b)に示されるように、本発明のカウンタモジュールの使用例の場合、図中破線で示されるように、主軸エンコーダEの出力パルスは、カウンタモジュールの内部において各カウンタに分配される。そのため、図から明らかなように、カウンタモジュールの外部には分配のための外部配線は不要となる。しかも、図2に示されるように、主軸エンコーダEにて駆動されるべきものは、1個の入力回路(第1カウンタ入力回路11−1)だけであるから、信号分配数が増大したとしても、主軸エンコーダの駆動能力には問題がなく、逆に、主軸エンコーダの駆動能力によって信号分配数に制限を受けるという問題を解決することができる。

【0081】

また、本発明のカウンタモジュールの使用例にあっては、各カウンタ13−1〜4は、分配切替回路12を介して送られてくる被カウント信号をカウントするものであるから、第1〜第4カウンタ13−1〜4のいずれかが故障したことにより、あるいは設計変更などによって、それまで或るカウンタがカウントしていた被カウント信号を、別のカウンタでカウントさせたいような場合には、入力側端子IN1〜IN4と出力側端子OUT1〜OUT4との導通/非導通の関係を変更するだけで、外部配線については何ら接続変更等を行うことなく、対応させることができ、煩わしい配線作業がなくなることで、この種のカウンタモジュールにおける使い勝手を格段に向上させることができる。

【0082】

なお、以上の実施形態においては、本発明に係るカウント装置を、ビルディングブロック型PLCのカウンタモジュールに応用したが、本発明のカウント装置は、それ自体で出力装置を内蔵することで、スタンドアローン形式のカウント装置として実現できることは勿論である。

【0083】

その際に、分配切替回路12については、入力側端子IN1〜IN4を出力側端子OUT1〜OUT4のいずれかに接続可能な多種切替スイッチ(手動又は自動)として単純化することもできる。

【産業上の利用可能性】

【0084】

本発明のカウント装置は、ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールとして応用することにより、外部配線の手間を省いて、その使い勝手を向上させることができる。

【図面の簡単な説明】

【0085】

【図1】本発明に係るカウンタモジュールの構成図である。

【図2】本発明に係るカウンタモジュールの使用例を示す説明図である。

【図3】内部メモリ内の設定情報記憶領域の構成を示すメモリマップである。

【図4】分配切り換え設定情報の一例を示す説明図である。

【図5】内部制御演算用マイコンの処理全体を示すフローチャートである。

【図6】カウンタ設定情報の一例を示す説明図である。

【図7】内部制御演算用マイコンのカウンタ出力読出処理を示すフローチャートである。

【図8】従来と本発明とで使用例を比較して示す説明図である。

【図9】複数のカウンタを使用した制御システムの一例を示す説明図である。

【図10】カウンタモジュールを含むPLCを用いた制御システムの一例を示す説明図である。

【図11】従来のカウンタモジュールの構成図である。

【符号の説明】

【0086】

1 カウンタモジュール

2 CPUモジュール

3 位置制御モジュール

11−1〜11−4 カウンタ入力回路

12 分配切替回路

13−1〜13−4 カウンタ

14 上位I/F回路(バスなど)

15 内部制御演算用マイコン

16 内部メモリ

16a 分配切替設定情報

17 内部バス

100 PLC

200 モータ駆動装置

31 巻き取りロール

32 主軸

33 主軸エンコーダ

34 負極シートカッタ

35 正極シートカッタ

36−1〜3 カウンタ

37−1 ガイドローラ位置制御部

37−2 正極シートカッタ制御部

37−3 負極シートカッタ制御部

E 主軸エンコーダ

M1 主軸モータ

M2 従動モータ

【特許請求の範囲】

【請求項1】

複数個のカウンタと、

外部から被カウント信号を取り込むための1若しくは2以上の入力回路と、

前記1若しくは2以上の入力回路の各出力端と前記複数個のカウンタの各入力端との間に介在される分配切替回路とを包含し、

前記複数個のカウンタのカウント値又はそのカウント値に基づいて生成された状態信号を出力信号として外部へと出力するように構成されており、

前記分配切替回路は、

前記1若しくは2以上の入力回路の各出力端のそれぞれに接続される入力側端子と、前記複数個のカウンタの各入力端のそれぞれに接続される出力側端子とを有し、かつ

前記入力側端子のそれぞれと前記出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされ、

それにより、前記複数のカウンタのそれぞれは、前記分配切替回路を介して自己に供給される被カウント信号をカウントする、ことを特徴とするカウント装置。

【請求項2】

前記分配切替回路における導通又は非道通の設定は、所定のメモリに格納された分配切替設定情報に基づいて自動的に行われる、ことを特徴とする請求項1に記載のカウント装置。

【請求項3】

前記複数個のカウンタのそれぞれは、

前記被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウント部と、

前記リングカウント部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、前記ONカウント値との一致タイミング及び前記OFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを包含する、ことを特徴とする請求項1又は2に記載のカウント装置。

【請求項4】

前記各カウンタのONカウント値及びオフカウント値のそれぞれ、及び/又は、前記各カウンタの最大カウント値は、所定のメモリに格納されたカウンタ設定情報に基づいて設定される、ことを特徴とする請求項3に記載のカウント装置。

【請求項5】

ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールとして構成され、

CPUモジュールに繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュールと前記CPUモジュールとで共有される共有メモリを内蔵する上位I/F回路と、

前記上位I/F回路の共有メモリを介して前記CPUモジュールからカウンタ設定情報に関する書替要求が到来したときには、当該要求にしたがって、前記メモリのカウンタ設定情報を書き替える動作を行うカウンタ設定情報書替手段と、

前記上位I/F回路の共有メモリを介して前記CPUモジュールからカウンタ出力送信要求が到来したときには、当該要求にしたがって、前記複数のカウンタのうちの該当するカウンタの前記カウント値、及び/又は、前記状態信号を読み込んで、前記CPUモジュールへと受け渡すべく、前記共有メモリに書き込む動作を行うカウンタ出力送信手段とを包含する、ことを特徴とする請求項4に記載のカウント装置。

【請求項6】

前記カウンタ情報書替手段及び前記カウンタ出力送信手段の各機能は、内部制御演算用マイコンによりソフトウェア的に実現される、ことを特徴とする請求項5に記載のカウント装置。

【請求項7】

前記複数のカウンタのそれぞれは、ハードウェア・カウンタである、ことを特徴とする請求項1〜6のいずれかに記載のカウント装置。

【請求項8】

前記分配切替回路において、

1の入力側端子と2以上の出力側端子とが導通するように端子間導通設定が行われ、かつ前記1の入力側端子の前段に位置する入力回路には、主軸エンコーダの出力パルス列が供給され、さらに前記2以上の出力側端子の各後段に位置するカウンタのそれぞれから、従動軸制御用のカウンタ出力を取り出す、ことを特徴とする請求項1〜7のいずれかに記載されたカウント装置の使用方法。

【請求項1】

複数個のカウンタと、

外部から被カウント信号を取り込むための1若しくは2以上の入力回路と、

前記1若しくは2以上の入力回路の各出力端と前記複数個のカウンタの各入力端との間に介在される分配切替回路とを包含し、

前記複数個のカウンタのカウント値又はそのカウント値に基づいて生成された状態信号を出力信号として外部へと出力するように構成されており、

前記分配切替回路は、

前記1若しくは2以上の入力回路の各出力端のそれぞれに接続される入力側端子と、前記複数個のカウンタの各入力端のそれぞれに接続される出力側端子とを有し、かつ

前記入力側端子のそれぞれと前記出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされ、

それにより、前記複数のカウンタのそれぞれは、前記分配切替回路を介して自己に供給される被カウント信号をカウントする、ことを特徴とするカウント装置。

【請求項2】

前記分配切替回路における導通又は非道通の設定は、所定のメモリに格納された分配切替設定情報に基づいて自動的に行われる、ことを特徴とする請求項1に記載のカウント装置。

【請求項3】

前記複数個のカウンタのそれぞれは、

前記被カウント信号をカウントすると共に、カウント値が所定の最大カウント値に達する毎に、そのカウント値がリセットされるリングカウント部と、

前記リングカウント部のカウント値を、所定のONカウント値及びOFFカウント値と比較し、前記ONカウント値との一致タイミング及び前記OFFカウント値との一致タイミングに応答してON/OFFする状態信号を生成する状態信号生成部とを包含する、ことを特徴とする請求項1又は2に記載のカウント装置。

【請求項4】

前記各カウンタのONカウント値及びオフカウント値のそれぞれ、及び/又は、前記各カウンタの最大カウント値は、所定のメモリに格納されたカウンタ設定情報に基づいて設定される、ことを特徴とする請求項3に記載のカウント装置。

【請求項5】

ビルディングブロック型PLCの1要素モジュールであるカウンタモジュールとして構成され、

CPUモジュールに繋がるモジュール間接続バスとのインタフェースとして機能すると共に、当該カウンタモジュールと前記CPUモジュールとで共有される共有メモリを内蔵する上位I/F回路と、

前記上位I/F回路の共有メモリを介して前記CPUモジュールからカウンタ設定情報に関する書替要求が到来したときには、当該要求にしたがって、前記メモリのカウンタ設定情報を書き替える動作を行うカウンタ設定情報書替手段と、

前記上位I/F回路の共有メモリを介して前記CPUモジュールからカウンタ出力送信要求が到来したときには、当該要求にしたがって、前記複数のカウンタのうちの該当するカウンタの前記カウント値、及び/又は、前記状態信号を読み込んで、前記CPUモジュールへと受け渡すべく、前記共有メモリに書き込む動作を行うカウンタ出力送信手段とを包含する、ことを特徴とする請求項4に記載のカウント装置。

【請求項6】

前記カウンタ情報書替手段及び前記カウンタ出力送信手段の各機能は、内部制御演算用マイコンによりソフトウェア的に実現される、ことを特徴とする請求項5に記載のカウント装置。

【請求項7】

前記複数のカウンタのそれぞれは、ハードウェア・カウンタである、ことを特徴とする請求項1〜6のいずれかに記載のカウント装置。

【請求項8】

前記分配切替回路において、

1の入力側端子と2以上の出力側端子とが導通するように端子間導通設定が行われ、かつ前記1の入力側端子の前段に位置する入力回路には、主軸エンコーダの出力パルス列が供給され、さらに前記2以上の出力側端子の各後段に位置するカウンタのそれぞれから、従動軸制御用のカウンタ出力を取り出す、ことを特徴とする請求項1〜7のいずれかに記載されたカウント装置の使用方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−118981(P2010−118981A)

【公開日】平成22年5月27日(2010.5.27)

【国際特許分類】

【出願番号】特願2008−291856(P2008−291856)

【出願日】平成20年11月14日(2008.11.14)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

【公開日】平成22年5月27日(2010.5.27)

【国際特許分類】

【出願日】平成20年11月14日(2008.11.14)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

[ Back to top ]