ゲート駆動回路

【課題】印加可能なゲート電圧の制約条件を満たしながら、高速スイッチングによる低損失特性を満足させるとともに、誤オン動作等のインバータとしての不正動作を阻止することのできるゲート駆動回路を提供する。

【解決手段】SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3を設け、スイッチ5を介してゲート電源(Vsg)7と接続し、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11を設ける。

【解決手段】SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3を設け、スイッチ5を介してゲート電源(Vsg)7と接続し、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11を設ける。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、SiC(シリコンカーバイド)を材料としたJFET(Junction Field Effect Transistor:接合型電界効果トランジスタ)またはSIT

(Static Induction Transistor:静電誘導トランジスタ)等のスイッチングデバイスを駆動するゲート駆動回路に関する。

【背景技術】

【0002】

従来、ハイブリッド電気自動車のモータ可変速ドライブ用インバータや、太陽光発電用電力系統接続インバータ等においては、スイッチングデバイスとして、Si(シリコン)を材料としたIGBT(Insulated Gate Bipolar Transistor:絶縁ゲートバイポーラトランジスタ)やMOSFET

(Metal-Oxide-Semiconductor Field-Effect Transistor:MOS型電界効果トランジスタ)が用いられてきた。

【0003】

しかしながら、近年、SiC(シリコンカーバイド)を材料としたノーマリオフ型(Normally Off Type)JFETやノーマリオフ型SITが実用化されつつある。

【0004】

これは、SiCを用いることにより、Siと同一の厚さでも材料特性として高電圧を印加できるため、同一の電圧用スイッチングデバイスとして用いた時にSiよりも薄型化することが可能となり、結果として導通損失を小さくできるからである。

【0005】

この低導通損失特性とさらに高速低損失スイッチング特性から、SiCを用いたJFET(接合型電界効果トランジスタ)は、インバータの発熱損失を飛躍的に小さく出来るため、高パワー密度化が要求されるハイブリッド電気自動車や電気自動車、太陽光発電用インバータ等、省エネ・環境調和型インバータへの適用が期待されている。なお、スイッチングデバイスとして、JFET(接合型電界効果トランジスタ)のみならず、SIT(静電誘導トランジスタ)においても同様の機能が期待される。

【0006】

ところで、この種のJFETやSITなどのスイッチングデバイスを駆動するためのゲート駆動回路には特許文献1などに記載のものが従来から知られている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−174134号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来技術のゲート駆動回路をSiCを材料としたJFETに適用した場合には、以下の(1)〜(3)のような問題がある。

(1)JFETに正の電圧を一定値以上印加すると、ゲート電流が増加して回路の消費電力が増大する。

(2)逆に、JFETに印加する正の電圧が不足するとJFETのターンオンが遅くなり、ターンオン損失が増大する。

(3)JFETのオンオフ閾値電圧は、正ではあるがゼロに近い。このため、高速スイッチングにより発生する高い電圧時間変化率(dv/dt)により、ゲート・ドレイン間の浮遊容量を介してゲート・ソース間の電圧を上昇させ、オフとオンの閾値を容易に超過して誤オン動作してしまう場合がある。

【0009】

本発明の実施形態は、印加可能なゲート電圧の制約条件を満たしながら、高速スイッチングによる低損失特性を満足させるとともに、誤オン動作等の不正動作を阻止することのできるゲート駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

上述の目的を達成するため、本発明の実施形態は、SiCで形成され所定のオンオフ閾値電圧を有するスイッチングデバイスのゲート側に接続されるゲート駆動回路において、オンオフ動作するスイッチを介して前記スイッチングデバイスをゲート電源と接続し、前記スイッチングデバイスがオフの間に外乱により前記オンオフ閾値電圧を超えないように構成したことを特徴とする。

【図面の簡単な説明】

【0011】

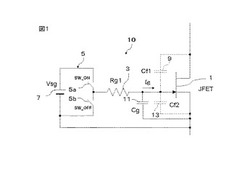

【図1】本発明の第1の実施形態を示す回路図である。

【図2】第1の実施形態の作用・効果を説明する回路図である。

【図3】本発明の第2の実施形態を示す回路図である。

【図4】本発明の第3の実施形態を示す回路図である。

【図5】本発明の第4の実施形態を示す回路図である。

【図6】本発明の第5の実施形態を示す回路図である。

【図7】本発明の第6の実施形態を示す回路図である。

【図8】本発明の第7の実施形態を示す回路図である。

【図9】本発明の第8の実施形態を示す回路図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について、図面を参照して具体的に説明する。

【0013】

[第1の実施形態]

(構成)

図1に示すように、本実施形態のゲート駆動回路10は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。スイッチ5は、図示しないゲート指令信号に従ってオンオフ動作するONスイッチ5a及びOFFスイッチ5bからなる。符号9は、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)であり、符号13は、JFET1のゲート・ソース間に生じる浮遊容量(Cf2)である。本実施形態では、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11が設けられている。

【0014】

(作用・効果)

図2に示すとおり、インバータのUVW各相は、2つの直列接続されたJFET1a,1bで構成されるのが一般的である。図2において直列上段に接続されたJFET1aが高速にオフからオンになると、直列下段に接続されたJFET1bの両端には主回路直流電圧Vmainが印加される。

【0015】

このとき、下式(1)のとおりドレイン・ゲート間の浮遊容量(Cf1)と、ゲート・ソース間の浮遊容量(Cf2)とで分圧された電圧VgsがJFET1bのゲート・ソース間に印加される。

【0016】

Vgs={Cf1/(Cf1+Cf2)}×Vmain・・・・・(1)

【0017】

式(1)において、Cf2がCf1に比較して十分に大きければ、Vgsは小さな値になり、JFET1bがオフの間に外乱によりオンオフ閾値を超過しないようにすることができる。このため、JFET1bのゲート・ソース間に大容量のコンデンサ11(容量Cg)を追加すると、ゲート・ソース間電圧Vgs’は下式(2)のとおり小さな値とすることができる。

【0018】

Vgs’={Cf1/(Cf1+Cf2+Cg)}×Vmain・・・(2)

【0019】

よって、JFET1bのオンオフ閾値がゼロに近くても、JFET1bがオフの間に外乱により誤オン動作をしないようにすることができる。従って、本実施形態によれば、印加可能なゲート電圧の制約条件を満たしながら、誤オン動作等のインバータとしての不正動作を阻止することができる。

【0020】

[第2の実施形態]

(構成)

図3に示すように、本実施形態のゲート駆動回路20は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。スイッチ5は、図示しないゲート指令信号に従ってオンオフ動作するONスイッチ5a及びOFFスイッチ5bからなる。

【0021】

本実施形態では、ゲート電源(Vsg)7の低電位側とJFET1のソースとの間に、ゲートオフセット電源(Vsg_ofst)21がマイナスにオフセットを印加するように接続されている。

【0022】

(作用・効果)

本実施形態では、ゲートオフ(OFFスイッチ5bがオンでONスイッチ5aがオフ)時のゲート・ソース間電圧は、−Vsg_ofst、ゲートオン(ONスイッチ5aがオンでOFFスイッチ5bがオフ)時のゲート・ソース間電圧は、Vsg−Vsg_ofstとなる。

【0023】

オンオフ閾値電圧をVthとした時、Vsg−Vsg_ofst−Vthの値と、Vth+Vsg_ofstの値とをほぼ同一とすることにより、オン・オフそれぞれの定常状態において閾値との差分電圧を大きくとることが可能になる。これより、ゲート電源の消費電力を必要以上に大きくすることなく、誤動作が発生しないための裕度を最大にすることができる。

【0024】

これより、本実施形態では、誤ったスイッチング動作を阻止するとともに、オンとオフの間の電位差を高くとることにより、オン状態でのゲート電圧をJFET1の正のゲート電圧制約よりも低い電位に制限することができる。

【0025】

[第3の実施形態]

(構成)

本実施形態は、前記第1の実施形態と第2の実施形態を組み合わせたものである。すなわち、図4に示すように、本実施形態のゲート駆動回路30は、ゲート電源7の低電位側とJFET1のソースとの間に、ゲートオフセット電源(電圧Vsg_ofst)21がマイナスにオフセットを印加するように接続されている。また、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11が設けられている。

【0026】

(作用・効果)

本実施形態では、以下の作用・効果を奏する。

【0027】

(1)コンデンサ(Cg)11を設けたことにより、JFET1のオンオフ閾値がゼロに近くても、誤オン動作しないようにすることができる。

【0028】

(2)ゲートオフセット電源(Vsg_ofst)21を用いたことにより、オン・オフそれぞれの定常状態において閾値との差分電圧を大きくとることが可能になる。これより、ゲート電源の消費電力を必要以上に大きくすることなく、誤動作が発生しないための裕度を最大にすることができる。

【0029】

(3)コンデンサ(Cg)11とゲートオフセット電源(Vsg_ofst)21を双方用いることにより、それぞれ単独で用いた場合と比較して、コンデンサ(Cg)11をより小容量化でき、かつ、ゲートオフセット電源(Vsg_ofst)21をより低電圧化することができる。

【0030】

これにより、ゲート駆動回路の消費電力をより低減できるとともに、JFET1の誤動作を確実に防止することができる。

【0031】

[第4の実施形態]

(構成)

図5に示すように、本実施形態のゲート駆動回路40は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。符号13は、JFET1のゲート・ソース間に生じる浮遊容量(Cf2)である。

【0032】

本実施形態では、ゲート抵抗(Rg1)3とスイッチ5との間に、第2のゲート抵抗(Rg2)31が直列に接続され、この第2のゲート抵抗(Rg2)31と並列に第2のコンデンサ(CgD)33が接続されている。

【0033】

(作用・効果)

本実施形態では、ターンオン動作時、OFFスイッチ5bが切れてONスイッチ5aがオンとなる。このため、JFET1には、第2のゲート抵抗(Rg2)31と第2のコンデンサ(CgD)33の並列回路、及びゲート抵抗(Rg1)3を通してゲート電源(Vsg)7からゲート電流が注入される。

【0034】

第2のコンデンサ(CgD)33はゲート電圧変化に対して微分動作するため、ターンオン動作において、ゲート抵抗(Rg1)3によって決まる高速スイッチングが可能になる。一方、定常動作時では、第2のゲート抵抗(Rg2)31で決まる小電流注入により、ゲート電源容量の低減が可能になる。これにより、JFET1のゲート・ソース間電圧を安定化させることができる。

【0035】

ターンオフ動作時では、ONスイッチ5aが切れてOFFスイッチ5bがオンとなる。このため、JFET1のゲートとソースは、ゲート抵抗(Rg1)3と、第2のゲート抵抗(Rg2)31及び第2のコンデンサ(CgD)33の並列回路とを通して短絡される。

【0036】

本実施形態では、第2のコンデンサ(CgD)33の存在によって、ゲート・ソース間の浮遊容量(Cf2)13の電荷の影響を取り除くことができる。このため、ターンオフ動作においては、ゲート抵抗3(Rg1)によって決まる高速スイッチングが可能になる。

【0037】

[第5の実施形態]

(構成)

図6に示すように、本実施形態のゲート駆動回路50は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。

【0038】

本実施形態は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0039】

(作用・効果)

本実施形態のゲート駆動回路50では、ターンオン動作時、OFFスイッチ5bが切れてONスイッチ5aがオンとなる。このため、JFET1には、ゲート抵抗(Rg1)3と並列に接続される順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を通して、ゲート電源(Vsg)7からゲート電流が注入される。

【0040】

第3のゲート抵抗(Rg_on)41の抵抗値をゲート抵抗(Rg1)3の抵抗値よりも低くなるように設定しておくと、順方向ダイオード(D_on)43を通して低い抵抗値の第3のゲート抵抗(Rg_on)41にゲート電流を多く注入できることから、高速のターンオン動作が可能になる。

【0041】

また、ゲート電源(Vsg)7を必要以上に高く設定する必要がなくなり、ゲート駆動回路の消費電力を小さくすることができる。

【0042】

よって、本実施形態では、印加可能なゲート電圧の制約条件を満たしながら、高速スイッチングによる低損失特性を満足させることができる。

【0043】

[第6の実施形態]

(構成)

本実施形態は、前記第4の実施形態と第5の実施形態を組み合わせたものである。すなわち、図7に示すように、本実施形態のゲート駆動回路60は、ゲート抵抗(Rg1)3とスイッチ5との間に、第2のゲート抵抗(Rg2)31が直列に接続され、この第2のゲート抵抗(Rg2)31と並列に第2のコンデンサ(CgD)33が接続されている。

【0044】

本実施形態は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0045】

(作用・効果)

本実施形態では、以下の作用・効果を奏する。

【0046】

(1)第2のコンデンサ(CgD)33の存在によって、ゲート・ソース間の浮遊容量(Cf2)13の電荷の影響を取り除くことができる。このため、ターンオフ動作においては、ゲート抵抗3(Rg1)によって決まる高速スイッチングが可能になる。

【0047】

(2)第3のゲート抵抗(Rg_on)41の抵抗値をゲート抵抗(Rg1)3の抵抗値よりも低くなるように設定しておくと、ダイオード(D_on)43を通して低い抵抗値の第3のゲート抵抗(Rg_on)41にゲート電流を多く注入できる。このため、高速のターンオン動作が可能になる。また、ゲート電源(Vsg)7を必要以上に高く設定する必要がなくなり、ゲート駆動回路の消費電力を小さくすることができる。

【0048】

(3)第2のコンデンサ(CgD)33、及び順方向ダイオード(D_on)43と第3のゲート抵抗(Rg_on)41との直列回路を併せて設けたので、それぞれ単独で用いた場合と比較して、ターンオンをより高速化できる。このため、ゲート電源(Vsg)7をより低電圧化することができ、ゲート駆動回路の消費電力を低減することができる。これと同時に、ターンオフ動作についても、ゲート抵抗(Rg1)3によって決まる高速スイッチングが可能になる。

【0049】

[第7の実施形態]

(構成)

本実施形態は、前記第6の実施形態に対して、さらに逆方向バイパスダイオード(D_by)53を付加したものである。すなわち、図8に示すように、本実施形態のゲート駆動回路70は、JFET1のゲート側からスイッチ5までの間に、順に、第1の回路61、第2の回路63を有している。

【0050】

第1の回路61は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0051】

第2の回路63は、第2のゲート抵抗(Rg2)31と、この第2のゲート抵抗(Rg2)31に対してそれぞれ並列に接続される第2のコンデンサ(CgD)33及び逆方向バイパスダイオード(D_by)53とからなる。

【0052】

(作用・効果)

たとえば、インバータ過電流状態からインバータを保護するために、各相すべてのゲート指令SwRefをオフして、各相すべてのJFET1をオフすることがある。この際、JFET1はアバランシェし、アバランシェ電流がJFET1のドレインからゲートに流れる。この時、第2のゲート抵抗(Rg2)31のみで逆方向バイパスダイオード(D_by)53がない場合、アバランシェ電流は第2のゲート抵抗(Rg2)31を通って流れる。その結果、第2のゲート抵抗(Rg2)31が損傷してゲート駆動回路が故障する場合がある。

【0053】

本実施形態では、逆方向バイパスダイオード(D_by)53を設けているので、第2のゲート抵抗(Rg2)31および第2のコンデンサ(CgD)33をバイパスしてアバランシェ電流を流すことができ、ゲート駆動回路をアバランシェ電流から保護することができる。

【0054】

また、本実施形態では、第6の実施形態の構成を全て備えているので、第6の実施形態と同様な作用・効果も奏することができる。

【0055】

[第8の実施形態]

本実施形態は、前記第3の実施形態と第7の実施形態を組み合わせたものである。すなわち、図9に示すように、本実施形態のゲート駆動回路80は、JFET1のゲート側からスイッチ5までの間に、順に、第1の回路61、第2の回路63を有している。

【0056】

第1の回路61は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0057】

第2の回路63は、第2のゲート抵抗(Rg2)31と、この第2のゲート抵抗(Rg2)31に対してそれぞれ並列に接続される第2のコンデンサ(CgD)33及び逆方向バイパスダイオード(D_by)53とからなる。

【0058】

本実施形態では、JFET1のゲート・ソース間にコンデンサ(Cg)11が接続される。また、ゲート電源7(Vsg)の低電位側とJFET1のソースとの間に、ゲートオフセット電源21(電圧Vsg_ofst)が接続されている。このゲートオフセット電源21は、ゲート電源7に対してマイナスにオフセットを印加するように接続されている。

【0059】

(作用・効果)

本実施形態では、以下の作用・効果を奏する。

【0060】

(1)コンデンサ(Cg)11を設けたことにより、JFET1のオンオフ閾値がゼロに近くても、誤オン動作しないようにすることができる。

【0061】

(2)ゲートオフセット電源(Vsg_ofst)21を用いたことにより、オン・オフそれぞれの定常状態において閾値との差分電圧を大きくとることが可能になる。これより、ゲート電源の消費電力を必要以上に大きくすることなく、誤動作が発生しないための裕度を最大にすることができる。

【0062】

(3)コンデンサ(Cg)11とゲートオフセット電源(Vsg_ofst)21を双方用いることにより、それぞれ単独で用いた場合と比較して、コンデンサ(Cg)11をより小容量化でき、かつ、ゲートオフセット電源(Vsg_ofst)21をより低電圧化することができる。

【0063】

(4)逆方向バイパスダイオード(D_by)53を設けているので、第2のゲート抵抗(Rg2)31および第2のコンデンサ(CgD)33をバイパスしてアバランシェ電流を流すことができ、ゲート駆動回路をアバランシェ電流から保護することができる。

【0064】

(5)第2のコンデンサ(CgD)33の存在によって、ゲート・ソース間の浮遊容量(Cf2)13の電荷の影響を取り除くことができる。このため、ターンオフ動作においては、ゲート抵抗3(Rg1)によって決まる高速スイッチングが可能になる。

【0065】

(6)第3のゲート抵抗(Rg_on)41の抵抗値をゲート抵抗(Rg1)3の抵抗値よりも低くなるように設定しておくと、ダイオード(D_on)43を通して低い抵抗値の第3のゲート抵抗(Rg_on)41にゲート電流を多く注入できる。このため、高速のターンオン動作が可能になる。また、ゲート電源(Vsg)7を必要以上に高く設定する必要がなくなり、ゲート駆動回路の消費電力を小さくすることができる。

【0066】

(7)第2のコンデンサ(CgD)33、及び順方向ダイオード(D_on)43と第3のゲート抵抗(Rg_on)41との直列回路を併せて設けたので、それぞれ単独で用いた場合と比較して、ターンオンをより高速化できる。このため、ゲート電源(Vsg)7をより低電圧化することができ、ゲート駆動回路の消費電力を低減することができる。これと同時に、ターンオフ動作についても、ゲート抵抗(Rg1)3によって決まる高速スイッチングが可能になる。

【0067】

[他の実施形態]

(1)上記の各実施形態では、スイッチングデバイスとしてJFETを用いた例を説明したが、SITに置き換えても良く、この場合も同様の作用効果を得ることができる。

【0068】

(2)上記の各実施形態では、ゲート抵抗(Rg1)3を配置した回路を示したが、必要に応じて省略することもできる。

【0069】

(3)上記の各実施形態では、スイッチ5として、ONスイッチ5a及びOFFスイッチ5bの2個のスイッチからなる例を示したが、同様の機能を果たすものであれば、他の構成のスイッチの使用も可能である。

【0070】

(4)以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0071】

1…接合型電界効果トランジスタ(JFET)(スイッチングデバイス)

3…ゲート抵抗(Rg1)(第1のゲート抵抗)

5…スイッチ

7…ゲート電源(Vsg)

10…ゲート駆動回路

11…コンデンサ(Cg)

20…ゲート駆動回路

21…ゲートオフセット電源(Vsg_ofst)

30…ゲート駆動回路

31…第2のゲート抵抗(Rg2)

33…第2のコンデンサ(CgD)

40…ゲート駆動回路

41…第3のゲート抵抗(Rg_on)

43…順方向ダイオード(D_on)

50…ゲート駆動回路

53…逆方向バイパスダイオード(D_by)

60…ゲート駆動回路

61…第1の回路

63…第2の回路

70…ゲート駆動回路

80…ゲート駆動回路

90…ゲート駆動回路

【技術分野】

【0001】

本発明の実施形態は、SiC(シリコンカーバイド)を材料としたJFET(Junction Field Effect Transistor:接合型電界効果トランジスタ)またはSIT

(Static Induction Transistor:静電誘導トランジスタ)等のスイッチングデバイスを駆動するゲート駆動回路に関する。

【背景技術】

【0002】

従来、ハイブリッド電気自動車のモータ可変速ドライブ用インバータや、太陽光発電用電力系統接続インバータ等においては、スイッチングデバイスとして、Si(シリコン)を材料としたIGBT(Insulated Gate Bipolar Transistor:絶縁ゲートバイポーラトランジスタ)やMOSFET

(Metal-Oxide-Semiconductor Field-Effect Transistor:MOS型電界効果トランジスタ)が用いられてきた。

【0003】

しかしながら、近年、SiC(シリコンカーバイド)を材料としたノーマリオフ型(Normally Off Type)JFETやノーマリオフ型SITが実用化されつつある。

【0004】

これは、SiCを用いることにより、Siと同一の厚さでも材料特性として高電圧を印加できるため、同一の電圧用スイッチングデバイスとして用いた時にSiよりも薄型化することが可能となり、結果として導通損失を小さくできるからである。

【0005】

この低導通損失特性とさらに高速低損失スイッチング特性から、SiCを用いたJFET(接合型電界効果トランジスタ)は、インバータの発熱損失を飛躍的に小さく出来るため、高パワー密度化が要求されるハイブリッド電気自動車や電気自動車、太陽光発電用インバータ等、省エネ・環境調和型インバータへの適用が期待されている。なお、スイッチングデバイスとして、JFET(接合型電界効果トランジスタ)のみならず、SIT(静電誘導トランジスタ)においても同様の機能が期待される。

【0006】

ところで、この種のJFETやSITなどのスイッチングデバイスを駆動するためのゲート駆動回路には特許文献1などに記載のものが従来から知られている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−174134号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来技術のゲート駆動回路をSiCを材料としたJFETに適用した場合には、以下の(1)〜(3)のような問題がある。

(1)JFETに正の電圧を一定値以上印加すると、ゲート電流が増加して回路の消費電力が増大する。

(2)逆に、JFETに印加する正の電圧が不足するとJFETのターンオンが遅くなり、ターンオン損失が増大する。

(3)JFETのオンオフ閾値電圧は、正ではあるがゼロに近い。このため、高速スイッチングにより発生する高い電圧時間変化率(dv/dt)により、ゲート・ドレイン間の浮遊容量を介してゲート・ソース間の電圧を上昇させ、オフとオンの閾値を容易に超過して誤オン動作してしまう場合がある。

【0009】

本発明の実施形態は、印加可能なゲート電圧の制約条件を満たしながら、高速スイッチングによる低損失特性を満足させるとともに、誤オン動作等の不正動作を阻止することのできるゲート駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

上述の目的を達成するため、本発明の実施形態は、SiCで形成され所定のオンオフ閾値電圧を有するスイッチングデバイスのゲート側に接続されるゲート駆動回路において、オンオフ動作するスイッチを介して前記スイッチングデバイスをゲート電源と接続し、前記スイッチングデバイスがオフの間に外乱により前記オンオフ閾値電圧を超えないように構成したことを特徴とする。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施形態を示す回路図である。

【図2】第1の実施形態の作用・効果を説明する回路図である。

【図3】本発明の第2の実施形態を示す回路図である。

【図4】本発明の第3の実施形態を示す回路図である。

【図5】本発明の第4の実施形態を示す回路図である。

【図6】本発明の第5の実施形態を示す回路図である。

【図7】本発明の第6の実施形態を示す回路図である。

【図8】本発明の第7の実施形態を示す回路図である。

【図9】本発明の第8の実施形態を示す回路図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について、図面を参照して具体的に説明する。

【0013】

[第1の実施形態]

(構成)

図1に示すように、本実施形態のゲート駆動回路10は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。スイッチ5は、図示しないゲート指令信号に従ってオンオフ動作するONスイッチ5a及びOFFスイッチ5bからなる。符号9は、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)であり、符号13は、JFET1のゲート・ソース間に生じる浮遊容量(Cf2)である。本実施形態では、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11が設けられている。

【0014】

(作用・効果)

図2に示すとおり、インバータのUVW各相は、2つの直列接続されたJFET1a,1bで構成されるのが一般的である。図2において直列上段に接続されたJFET1aが高速にオフからオンになると、直列下段に接続されたJFET1bの両端には主回路直流電圧Vmainが印加される。

【0015】

このとき、下式(1)のとおりドレイン・ゲート間の浮遊容量(Cf1)と、ゲート・ソース間の浮遊容量(Cf2)とで分圧された電圧VgsがJFET1bのゲート・ソース間に印加される。

【0016】

Vgs={Cf1/(Cf1+Cf2)}×Vmain・・・・・(1)

【0017】

式(1)において、Cf2がCf1に比較して十分に大きければ、Vgsは小さな値になり、JFET1bがオフの間に外乱によりオンオフ閾値を超過しないようにすることができる。このため、JFET1bのゲート・ソース間に大容量のコンデンサ11(容量Cg)を追加すると、ゲート・ソース間電圧Vgs’は下式(2)のとおり小さな値とすることができる。

【0018】

Vgs’={Cf1/(Cf1+Cf2+Cg)}×Vmain・・・(2)

【0019】

よって、JFET1bのオンオフ閾値がゼロに近くても、JFET1bがオフの間に外乱により誤オン動作をしないようにすることができる。従って、本実施形態によれば、印加可能なゲート電圧の制約条件を満たしながら、誤オン動作等のインバータとしての不正動作を阻止することができる。

【0020】

[第2の実施形態]

(構成)

図3に示すように、本実施形態のゲート駆動回路20は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。スイッチ5は、図示しないゲート指令信号に従ってオンオフ動作するONスイッチ5a及びOFFスイッチ5bからなる。

【0021】

本実施形態では、ゲート電源(Vsg)7の低電位側とJFET1のソースとの間に、ゲートオフセット電源(Vsg_ofst)21がマイナスにオフセットを印加するように接続されている。

【0022】

(作用・効果)

本実施形態では、ゲートオフ(OFFスイッチ5bがオンでONスイッチ5aがオフ)時のゲート・ソース間電圧は、−Vsg_ofst、ゲートオン(ONスイッチ5aがオンでOFFスイッチ5bがオフ)時のゲート・ソース間電圧は、Vsg−Vsg_ofstとなる。

【0023】

オンオフ閾値電圧をVthとした時、Vsg−Vsg_ofst−Vthの値と、Vth+Vsg_ofstの値とをほぼ同一とすることにより、オン・オフそれぞれの定常状態において閾値との差分電圧を大きくとることが可能になる。これより、ゲート電源の消費電力を必要以上に大きくすることなく、誤動作が発生しないための裕度を最大にすることができる。

【0024】

これより、本実施形態では、誤ったスイッチング動作を阻止するとともに、オンとオフの間の電位差を高くとることにより、オン状態でのゲート電圧をJFET1の正のゲート電圧制約よりも低い電位に制限することができる。

【0025】

[第3の実施形態]

(構成)

本実施形態は、前記第1の実施形態と第2の実施形態を組み合わせたものである。すなわち、図4に示すように、本実施形態のゲート駆動回路30は、ゲート電源7の低電位側とJFET1のソースとの間に、ゲートオフセット電源(電圧Vsg_ofst)21がマイナスにオフセットを印加するように接続されている。また、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11が設けられている。

【0026】

(作用・効果)

本実施形態では、以下の作用・効果を奏する。

【0027】

(1)コンデンサ(Cg)11を設けたことにより、JFET1のオンオフ閾値がゼロに近くても、誤オン動作しないようにすることができる。

【0028】

(2)ゲートオフセット電源(Vsg_ofst)21を用いたことにより、オン・オフそれぞれの定常状態において閾値との差分電圧を大きくとることが可能になる。これより、ゲート電源の消費電力を必要以上に大きくすることなく、誤動作が発生しないための裕度を最大にすることができる。

【0029】

(3)コンデンサ(Cg)11とゲートオフセット電源(Vsg_ofst)21を双方用いることにより、それぞれ単独で用いた場合と比較して、コンデンサ(Cg)11をより小容量化でき、かつ、ゲートオフセット電源(Vsg_ofst)21をより低電圧化することができる。

【0030】

これにより、ゲート駆動回路の消費電力をより低減できるとともに、JFET1の誤動作を確実に防止することができる。

【0031】

[第4の実施形態]

(構成)

図5に示すように、本実施形態のゲート駆動回路40は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。符号13は、JFET1のゲート・ソース間に生じる浮遊容量(Cf2)である。

【0032】

本実施形態では、ゲート抵抗(Rg1)3とスイッチ5との間に、第2のゲート抵抗(Rg2)31が直列に接続され、この第2のゲート抵抗(Rg2)31と並列に第2のコンデンサ(CgD)33が接続されている。

【0033】

(作用・効果)

本実施形態では、ターンオン動作時、OFFスイッチ5bが切れてONスイッチ5aがオンとなる。このため、JFET1には、第2のゲート抵抗(Rg2)31と第2のコンデンサ(CgD)33の並列回路、及びゲート抵抗(Rg1)3を通してゲート電源(Vsg)7からゲート電流が注入される。

【0034】

第2のコンデンサ(CgD)33はゲート電圧変化に対して微分動作するため、ターンオン動作において、ゲート抵抗(Rg1)3によって決まる高速スイッチングが可能になる。一方、定常動作時では、第2のゲート抵抗(Rg2)31で決まる小電流注入により、ゲート電源容量の低減が可能になる。これにより、JFET1のゲート・ソース間電圧を安定化させることができる。

【0035】

ターンオフ動作時では、ONスイッチ5aが切れてOFFスイッチ5bがオンとなる。このため、JFET1のゲートとソースは、ゲート抵抗(Rg1)3と、第2のゲート抵抗(Rg2)31及び第2のコンデンサ(CgD)33の並列回路とを通して短絡される。

【0036】

本実施形態では、第2のコンデンサ(CgD)33の存在によって、ゲート・ソース間の浮遊容量(Cf2)13の電荷の影響を取り除くことができる。このため、ターンオフ動作においては、ゲート抵抗3(Rg1)によって決まる高速スイッチングが可能になる。

【0037】

[第5の実施形態]

(構成)

図6に示すように、本実施形態のゲート駆動回路50は、SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3が設けられ、スイッチ5を介してゲート電源(Vsg)7と接続されている。

【0038】

本実施形態は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0039】

(作用・効果)

本実施形態のゲート駆動回路50では、ターンオン動作時、OFFスイッチ5bが切れてONスイッチ5aがオンとなる。このため、JFET1には、ゲート抵抗(Rg1)3と並列に接続される順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を通して、ゲート電源(Vsg)7からゲート電流が注入される。

【0040】

第3のゲート抵抗(Rg_on)41の抵抗値をゲート抵抗(Rg1)3の抵抗値よりも低くなるように設定しておくと、順方向ダイオード(D_on)43を通して低い抵抗値の第3のゲート抵抗(Rg_on)41にゲート電流を多く注入できることから、高速のターンオン動作が可能になる。

【0041】

また、ゲート電源(Vsg)7を必要以上に高く設定する必要がなくなり、ゲート駆動回路の消費電力を小さくすることができる。

【0042】

よって、本実施形態では、印加可能なゲート電圧の制約条件を満たしながら、高速スイッチングによる低損失特性を満足させることができる。

【0043】

[第6の実施形態]

(構成)

本実施形態は、前記第4の実施形態と第5の実施形態を組み合わせたものである。すなわち、図7に示すように、本実施形態のゲート駆動回路60は、ゲート抵抗(Rg1)3とスイッチ5との間に、第2のゲート抵抗(Rg2)31が直列に接続され、この第2のゲート抵抗(Rg2)31と並列に第2のコンデンサ(CgD)33が接続されている。

【0044】

本実施形態は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0045】

(作用・効果)

本実施形態では、以下の作用・効果を奏する。

【0046】

(1)第2のコンデンサ(CgD)33の存在によって、ゲート・ソース間の浮遊容量(Cf2)13の電荷の影響を取り除くことができる。このため、ターンオフ動作においては、ゲート抵抗3(Rg1)によって決まる高速スイッチングが可能になる。

【0047】

(2)第3のゲート抵抗(Rg_on)41の抵抗値をゲート抵抗(Rg1)3の抵抗値よりも低くなるように設定しておくと、ダイオード(D_on)43を通して低い抵抗値の第3のゲート抵抗(Rg_on)41にゲート電流を多く注入できる。このため、高速のターンオン動作が可能になる。また、ゲート電源(Vsg)7を必要以上に高く設定する必要がなくなり、ゲート駆動回路の消費電力を小さくすることができる。

【0048】

(3)第2のコンデンサ(CgD)33、及び順方向ダイオード(D_on)43と第3のゲート抵抗(Rg_on)41との直列回路を併せて設けたので、それぞれ単独で用いた場合と比較して、ターンオンをより高速化できる。このため、ゲート電源(Vsg)7をより低電圧化することができ、ゲート駆動回路の消費電力を低減することができる。これと同時に、ターンオフ動作についても、ゲート抵抗(Rg1)3によって決まる高速スイッチングが可能になる。

【0049】

[第7の実施形態]

(構成)

本実施形態は、前記第6の実施形態に対して、さらに逆方向バイパスダイオード(D_by)53を付加したものである。すなわち、図8に示すように、本実施形態のゲート駆動回路70は、JFET1のゲート側からスイッチ5までの間に、順に、第1の回路61、第2の回路63を有している。

【0050】

第1の回路61は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0051】

第2の回路63は、第2のゲート抵抗(Rg2)31と、この第2のゲート抵抗(Rg2)31に対してそれぞれ並列に接続される第2のコンデンサ(CgD)33及び逆方向バイパスダイオード(D_by)53とからなる。

【0052】

(作用・効果)

たとえば、インバータ過電流状態からインバータを保護するために、各相すべてのゲート指令SwRefをオフして、各相すべてのJFET1をオフすることがある。この際、JFET1はアバランシェし、アバランシェ電流がJFET1のドレインからゲートに流れる。この時、第2のゲート抵抗(Rg2)31のみで逆方向バイパスダイオード(D_by)53がない場合、アバランシェ電流は第2のゲート抵抗(Rg2)31を通って流れる。その結果、第2のゲート抵抗(Rg2)31が損傷してゲート駆動回路が故障する場合がある。

【0053】

本実施形態では、逆方向バイパスダイオード(D_by)53を設けているので、第2のゲート抵抗(Rg2)31および第2のコンデンサ(CgD)33をバイパスしてアバランシェ電流を流すことができ、ゲート駆動回路をアバランシェ電流から保護することができる。

【0054】

また、本実施形態では、第6の実施形態の構成を全て備えているので、第6の実施形態と同様な作用・効果も奏することができる。

【0055】

[第8の実施形態]

本実施形態は、前記第3の実施形態と第7の実施形態を組み合わせたものである。すなわち、図9に示すように、本実施形態のゲート駆動回路80は、JFET1のゲート側からスイッチ5までの間に、順に、第1の回路61、第2の回路63を有している。

【0056】

第1の回路61は、順方向ダイオード(D_on)43及び第3のゲート抵抗(Rg_on)41を直列に接続し、これらをゲート抵抗(Rg1)3と並列に配置してなる。

【0057】

第2の回路63は、第2のゲート抵抗(Rg2)31と、この第2のゲート抵抗(Rg2)31に対してそれぞれ並列に接続される第2のコンデンサ(CgD)33及び逆方向バイパスダイオード(D_by)53とからなる。

【0058】

本実施形態では、JFET1のゲート・ソース間にコンデンサ(Cg)11が接続される。また、ゲート電源7(Vsg)の低電位側とJFET1のソースとの間に、ゲートオフセット電源21(電圧Vsg_ofst)が接続されている。このゲートオフセット電源21は、ゲート電源7に対してマイナスにオフセットを印加するように接続されている。

【0059】

(作用・効果)

本実施形態では、以下の作用・効果を奏する。

【0060】

(1)コンデンサ(Cg)11を設けたことにより、JFET1のオンオフ閾値がゼロに近くても、誤オン動作しないようにすることができる。

【0061】

(2)ゲートオフセット電源(Vsg_ofst)21を用いたことにより、オン・オフそれぞれの定常状態において閾値との差分電圧を大きくとることが可能になる。これより、ゲート電源の消費電力を必要以上に大きくすることなく、誤動作が発生しないための裕度を最大にすることができる。

【0062】

(3)コンデンサ(Cg)11とゲートオフセット電源(Vsg_ofst)21を双方用いることにより、それぞれ単独で用いた場合と比較して、コンデンサ(Cg)11をより小容量化でき、かつ、ゲートオフセット電源(Vsg_ofst)21をより低電圧化することができる。

【0063】

(4)逆方向バイパスダイオード(D_by)53を設けているので、第2のゲート抵抗(Rg2)31および第2のコンデンサ(CgD)33をバイパスしてアバランシェ電流を流すことができ、ゲート駆動回路をアバランシェ電流から保護することができる。

【0064】

(5)第2のコンデンサ(CgD)33の存在によって、ゲート・ソース間の浮遊容量(Cf2)13の電荷の影響を取り除くことができる。このため、ターンオフ動作においては、ゲート抵抗3(Rg1)によって決まる高速スイッチングが可能になる。

【0065】

(6)第3のゲート抵抗(Rg_on)41の抵抗値をゲート抵抗(Rg1)3の抵抗値よりも低くなるように設定しておくと、ダイオード(D_on)43を通して低い抵抗値の第3のゲート抵抗(Rg_on)41にゲート電流を多く注入できる。このため、高速のターンオン動作が可能になる。また、ゲート電源(Vsg)7を必要以上に高く設定する必要がなくなり、ゲート駆動回路の消費電力を小さくすることができる。

【0066】

(7)第2のコンデンサ(CgD)33、及び順方向ダイオード(D_on)43と第3のゲート抵抗(Rg_on)41との直列回路を併せて設けたので、それぞれ単独で用いた場合と比較して、ターンオンをより高速化できる。このため、ゲート電源(Vsg)7をより低電圧化することができ、ゲート駆動回路の消費電力を低減することができる。これと同時に、ターンオフ動作についても、ゲート抵抗(Rg1)3によって決まる高速スイッチングが可能になる。

【0067】

[他の実施形態]

(1)上記の各実施形態では、スイッチングデバイスとしてJFETを用いた例を説明したが、SITに置き換えても良く、この場合も同様の作用効果を得ることができる。

【0068】

(2)上記の各実施形態では、ゲート抵抗(Rg1)3を配置した回路を示したが、必要に応じて省略することもできる。

【0069】

(3)上記の各実施形態では、スイッチ5として、ONスイッチ5a及びOFFスイッチ5bの2個のスイッチからなる例を示したが、同様の機能を果たすものであれば、他の構成のスイッチの使用も可能である。

【0070】

(4)以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0071】

1…接合型電界効果トランジスタ(JFET)(スイッチングデバイス)

3…ゲート抵抗(Rg1)(第1のゲート抵抗)

5…スイッチ

7…ゲート電源(Vsg)

10…ゲート駆動回路

11…コンデンサ(Cg)

20…ゲート駆動回路

21…ゲートオフセット電源(Vsg_ofst)

30…ゲート駆動回路

31…第2のゲート抵抗(Rg2)

33…第2のコンデンサ(CgD)

40…ゲート駆動回路

41…第3のゲート抵抗(Rg_on)

43…順方向ダイオード(D_on)

50…ゲート駆動回路

53…逆方向バイパスダイオード(D_by)

60…ゲート駆動回路

61…第1の回路

63…第2の回路

70…ゲート駆動回路

80…ゲート駆動回路

90…ゲート駆動回路

【特許請求の範囲】

【請求項1】

SiCで形成され所定のオンオフ閾値電圧を有するスイッチングデバイスのゲート側に接続されるゲート駆動回路において、

オンオフ動作するスイッチを介して前記スイッチングデバイスをゲート電源と接続し、前記スイッチングデバイスがオフの間に外乱により前記オンオフ閾値電圧を超えないように構成したことを特徴とするゲート駆動回路。

【請求項2】

前記スイッチングデバイスのドレイン・ゲート間に生じる浮遊容量よりも大きな容量を有するコンデンサを前記スイッチングデバイスのゲート・ソース間に設けたことを特徴とする請求項1記載のゲート駆動回路。

【請求項3】

前記ゲート電源の低電位側と前記スイッチングデバイスのソースとの間に、ゲートオフセット電源をマイナスにオフセットを印加するように接続したことを特徴とする請求項1または2記載のゲート駆動回路。

【請求項4】

前記スイッチングデバイスのゲート側と前記スイッチとの間の回路に対して並列に第2のコンデンサを接続したことを特徴とする請求項1乃至3のいずれか1項記載のゲート駆動回路。

【請求項5】

前記スイッチングデバイスのゲート側と前記スイッチとの間に第1のゲート抵抗を接続するとともに、当該第1のゲート抵抗と前記スイッチとの間に、第2のゲート抵抗を直列に接続し、さらに当該第2のゲート抵抗と並列に第2のコンデンサを接続したことを特徴とする請求項1乃至4のいずれか1項記載のゲート駆動回路。

【請求項6】

前記第2のゲート抵抗及び前記第2のコンデンサのそれぞれに対して並列になるようにバイパスダイオードを逆方向に接続したことを特徴とする請求項5記載のゲート駆動回路。

【請求項7】

前記スイッチングデバイスのゲート側と前記スイッチとの間の回路に対して並列に、ダイオードを順方向に接続したことを特徴とする請求項1乃至6のいずれか1項記載のゲート駆動回路。

【請求項8】

前記第1のゲート抵抗と並列に、ダイオードを順方向に接続したことを特徴とする請求項5乃至7のいずれか1項記載のゲート駆動回路。

【請求項9】

前記順方向に接続したダイオードと直列に、第3のゲート抵抗を接続したことを特徴とする請求項8記載のゲート駆動回路。

【請求項1】

SiCで形成され所定のオンオフ閾値電圧を有するスイッチングデバイスのゲート側に接続されるゲート駆動回路において、

オンオフ動作するスイッチを介して前記スイッチングデバイスをゲート電源と接続し、前記スイッチングデバイスがオフの間に外乱により前記オンオフ閾値電圧を超えないように構成したことを特徴とするゲート駆動回路。

【請求項2】

前記スイッチングデバイスのドレイン・ゲート間に生じる浮遊容量よりも大きな容量を有するコンデンサを前記スイッチングデバイスのゲート・ソース間に設けたことを特徴とする請求項1記載のゲート駆動回路。

【請求項3】

前記ゲート電源の低電位側と前記スイッチングデバイスのソースとの間に、ゲートオフセット電源をマイナスにオフセットを印加するように接続したことを特徴とする請求項1または2記載のゲート駆動回路。

【請求項4】

前記スイッチングデバイスのゲート側と前記スイッチとの間の回路に対して並列に第2のコンデンサを接続したことを特徴とする請求項1乃至3のいずれか1項記載のゲート駆動回路。

【請求項5】

前記スイッチングデバイスのゲート側と前記スイッチとの間に第1のゲート抵抗を接続するとともに、当該第1のゲート抵抗と前記スイッチとの間に、第2のゲート抵抗を直列に接続し、さらに当該第2のゲート抵抗と並列に第2のコンデンサを接続したことを特徴とする請求項1乃至4のいずれか1項記載のゲート駆動回路。

【請求項6】

前記第2のゲート抵抗及び前記第2のコンデンサのそれぞれに対して並列になるようにバイパスダイオードを逆方向に接続したことを特徴とする請求項5記載のゲート駆動回路。

【請求項7】

前記スイッチングデバイスのゲート側と前記スイッチとの間の回路に対して並列に、ダイオードを順方向に接続したことを特徴とする請求項1乃至6のいずれか1項記載のゲート駆動回路。

【請求項8】

前記第1のゲート抵抗と並列に、ダイオードを順方向に接続したことを特徴とする請求項5乃至7のいずれか1項記載のゲート駆動回路。

【請求項9】

前記順方向に接続したダイオードと直列に、第3のゲート抵抗を接続したことを特徴とする請求項8記載のゲート駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−99133(P2013−99133A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−240371(P2011−240371)

【出願日】平成23年11月1日(2011.11.1)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(000173809)一般財団法人電力中央研究所 (1,040)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月1日(2011.11.1)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(000173809)一般財団法人電力中央研究所 (1,040)

【Fターム(参考)】

[ Back to top ]