スイッチング素子の駆動回路

【課題】電力損失が少なく、低コストなスイッチング素子の駆動回路を提供する。

【解決手段】スイッチング素子の駆動回路は、電源と、前記電源の正極性端子とスイッチング素子の制御端子との間に挿入される第1スイッチと、前記電源の負極性端子と前記スイッチング素子の制御端子との間に挿入される第2スイッチと、前記スイッチング素子の電流出力端子に一端が接続される第3スイッチと、前記スイッチング素子の前記電流出力端子に一端が接続される第4スイッチと、前記第3スイッチの他端に高電位側の端子が接続され、前記第4スイッチの他端に低電位側の端子が接続される電圧出力部とを含む。

【解決手段】スイッチング素子の駆動回路は、電源と、前記電源の正極性端子とスイッチング素子の制御端子との間に挿入される第1スイッチと、前記電源の負極性端子と前記スイッチング素子の制御端子との間に挿入される第2スイッチと、前記スイッチング素子の電流出力端子に一端が接続される第3スイッチと、前記スイッチング素子の前記電流出力端子に一端が接続される第4スイッチと、前記第3スイッチの他端に高電位側の端子が接続され、前記第4スイッチの他端に低電位側の端子が接続される電圧出力部とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング素子の駆動回路に関する。

【背景技術】

【0002】

従来より、IGBT(Insulated Gate Bipolar Transistor)のゲートにオントランジスタとオフトランジスタを接続し、IGBTをオフになるときに、オントランジスタをオフにしてゲートへの正電圧の印加を遮断するとともに、オフトランジスタをオンにしてゲートに逆バイアス電圧を印加することにより、IGBTのオフ時にIGBTが誤オンすることを防止したゲート駆動回路があった(例えば、特許文献1参照)。

【0003】

また、正電源のみでIGBTのオフ時にIGBTが誤オンすることを防止するために、HブリッジでIGBTのゲートを駆動する方法があった(例えば、特許文献2参照)。

【0004】

また、IGBTのゲート電圧が第1の設定値に達した時点で、オン電圧のレベルを低下させ、ゲート電圧が第2の設定値(>第1の設定値)に達した時点で、オン電圧のレベルを元の状態に復帰させるゲート駆動回路があった(例えば、特許文献3参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平07−131971号公報

【特許文献2】国際公開第2009/004715号

【特許文献3】特開2001−352748号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、従来のゲート駆動装置等は、電力損失が大きい、又は、部品点数が多いため、電力損失が少なく、簡素な構成で低コストな駆動回路等は実現されていなかった。

【0007】

そこで、本発明は、電力損失が少なく、低コストなスイッチング素子の駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一局面のスイッチング素子の駆動回路は、電源と、前記電源の正極性端子とスイッチング素子の制御端子との間に挿入される第1スイッチと、前記電源の負極性端子と前記スイッチング素子の制御端子との間に挿入される第2スイッチと、前記スイッチング素子の電流出力端子に一端が接続される第3スイッチと、前記スイッチング素子の前記電流出力端子に一端が接続される第4スイッチと、前記第3スイッチの他端に高電位側の端子が接続され、前記第4スイッチの他端に低電位側の端子が接続される電圧出力部とを含む。

【発明の効果】

【0009】

本発明によれば、電力損失が少なく、低コストなスイッチング素子の駆動回路を提供できるという効果が得られる。

【図面の簡単な説明】

【0010】

【図1】比較例1のスイッチング素子の駆動回路を示す図である。

【図2】比較例2のスイッチング素子の駆動回路を示す図である。

【図3】比較例2のスイッチング素子の駆動回路の駆動方法を示すタイミングチャートである。

【図4】比較例2のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【図5】比較例2の変形例のスイッチング素子の駆動回路を示す図である。

【図6】比較例2の変形例のスイッチング素子の駆動回路の駆動方法を示すタイミングチャートである。

【図7】比較例2の変形例のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【図8】比較例3のスイッチング素子の駆動回路を示す図である。

【図9】比較例3のスイッチング素子の駆動回路の駆動方法を示すタイミングチャートである。

【図10】比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【図11】実施の形態のスイッチング素子の駆動回路を含む電気自動車用駆動装置300の一実施例の概略構成を示す図である。

【図12】実施の形態のスイッチング素子の駆動回路を示す図である。

【図13】実施の形態のスイッチング素子の駆動回路の変形例を示す図である。

【図14】実施の形態のスイッチング素子の駆動回路100の駆動方法を示すタイミングチャートである。

【図15】実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。

【図16】実施の形態のスイッチング素子の駆動回路100の他の駆動方法を示すタイミングチャートである。

【図17】実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。

【図18】比較例3のスイッチング素子の駆動回路30の駆動方法を示すタイミングチャートである。

【図19】比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【発明を実施するための形態】

【0011】

本発明のスイッチング素子の駆動回路を適用した実施の形態について説明する前に、図1乃至図10を用いて、比較例のスイッチング素子の駆動回路に生じうる問題点について説明する。

【0012】

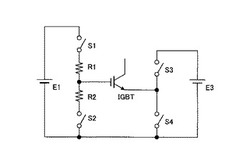

図1は、比較例1のスイッチング素子の駆動回路を示す図である。

【0013】

図1に示すように、比較例1のスイッチング素子の駆動回路10は、電源E1、スイッチS1、S2、S3、S4、及び抵抗器R1、R2を含み、スイッチング素子としてのIGBTを駆動する。

【0014】

ここでは、一例として、比較例1のスイッチング素子の駆動回路がインバータに用いられるIGBTを駆動する場合について説明する。

【0015】

IGBTのゲートは、抵抗器R1及びスイッチS1を介して、電源E1の正極性端子とスイッチS3に接続されるとともに、抵抗器R2及びスイッチS2を介して、電源E1の負極性端子とスイッチS4に接続されている。

【0016】

IGBTのエミッタは、スイッチS3とスイッチS4の中点に接続されている。

【0017】

IGBTのコレクタは、IGBTがインバータの上アームに含まれる場合は、コレクタはDC−DCコンバータを介して電源に接続され、IGBTがインバータの下アームに含まれる場合は、コレクタは上アームと下アームの中点に接続される。

【0018】

上述のように、図1に示す比較例1のスイッチング素子の駆動回路10では、スイッチS1〜S4は、IGBTを中心として、ブリッジ接続されている。

【0019】

IGBTをオンにするときには、スイッチS1及びスイッチS4をオンにするとともに、スイッチS2及びスイッチS3をオフにする。また、IGBTをオフにするときには、スイッチS1及びスイッチS4をオフにするとともに、スイッチS2及びスイッチS3をオンにする。

【0020】

図2は、比較例2のスイッチング素子の駆動回路を示す図である。

【0021】

図2に示すように、比較例2のスイッチング素子の駆動回路20は、電源E11、E12、E2、スイッチS1、S2、S11、S12、及び抵抗器R1、R2を含み、スイッチング素子としてのIGBTを駆動する。

【0022】

IGBTのゲートは、抵抗器R1及びスイッチS1を介して、スイッチS11及びスイッチS12の出力側の接続点Aに接続されている。また、IGBTのゲートは、抵抗器R2及びスイッチS2を介して電源E2の負極性端子に接続されている。

【0023】

スイッチS11の入力側(図2中左側の端子)は、電源E11の正極性端子に接続されており、スイッチS12の入力側(図2中左側の端子)は、電源E12の正極性端子に接続されている。

【0024】

電源E11と電源E12の負極性端子は、接続点B1、B2で接続されている。接続点B1には電源E2の正極性端子が接続され、電源E2の負極性端子はスイッチS2に接続されている。接続点B2はIGBTのエミッタに接続されている。

【0025】

図3は、比較例2のスイッチング素子の駆動回路20の駆動方法を示すタイミングチャートである。

【0026】

図3(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0027】

図3(B)のタイミングチャートは、各スイッチS1、S11、S12、S2のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。

【0028】

図3(B)に示すように、時刻t1より前では、スイッチS1、S11、S12はオフであり、スイッチS2がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図3(A)に示すように電源E2の電圧が負バイアス(Vge=−E2)として印加されており、IGBTはオフである。

【0029】

図3(B)に示すように、時刻t1で、スイッチS1、S11がオンにされるとともに、スイッチS2がオフにされると、図3(A)に示すように、IGBTのゲート・エミッタ間には、電源E11の出力電圧(E11)が印加されるため、IGBTはオンする。

【0030】

また、時刻t2でスイッチS12がオンされるとともに、スイッチS11がオフされると、IGBTのゲートには電源E12が印加されるため、ゲート・エミッタ間電圧はE12に上昇する。

【0031】

その後、時刻t3でスイッチS2がオンされるとともに、スイッチS1、S12がオフされると、IGBTのゲートには電源E2の電圧が負バイアス(Vge=−E2)として印加されるため、ゲート・エミッタ間電圧は−E2に低下する。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0032】

図4は、比較例2のスイッチング素子の駆動回路20による1スイッチングあたりの消費エネルギを示す図である。比較例2のスイッチング素子の駆動回路20で図3に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0033】

IGBTのオン時の電源E11の消費エネルギは{E11×Cg×(E11+E2)}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTのオンにするときの電圧変動幅{E11−(−E2)}(=E11+E2)を乗じて得る値である。

【0034】

IGBTのオン時の電源E12の消費エネルギは{E12×Cg×(E12−E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、電源E11から電源E12に切り替えたときの電圧変動幅(E12−E11)を乗じて得る値である。

【0035】

また、IGBTのオン時の消費エネルギは、電源E2では0である。これは、オン時には電源E2は無関係だからである。

【0036】

また、IGBTのオフ時の電源E11、E12の消費エネルギは0である。これは、オフ時には電源E11、E12は無関係だからである。

【0037】

また、IGBTのオフ時のE2の消費エネルギは{E2×Cg×(E12+E2)}である。これは、電源E2の出力電圧E2に、ゲート容量Cgと、IGBTのオフにするときの電圧変動幅{E12−(−E2)}(=E12+E2)を乗じて得る値である。

【0038】

ここで、E11=13V、E12=18V、E2=5V、IGBTのゲート容量Cg=0.1μFの場合には、IGBTのオン時の電源E11の消費エネルギ{E11×Cg×(E11+E2)}は23.4μJである。また、IGBTのオン時の電源E12の消費エネルギ{E12×Cg×(E12−E11)}は、9μJである。また、IGBTのオフ時のE2の消費エネルギ{E2×Cg×(E12+E2)}は、11.5μJである。

【0039】

これらを合計すると、比較例2のスイッチング素子の駆動回路20で図3に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギの具体値は43.9μJとなる。

【0040】

次に、図5乃至図7を用いて、比較例2の変形例のスイッチング素子の駆動回路及びその動作について説明する。

【0041】

図5は、比較例2の変形例のスイッチング素子の駆動回路を示す図である。

【0042】

図5に示すように、比較例2の変形例のスイッチング素子の駆動回路20Aは、図2に示す比較例2のスイッチング素子の駆動回路20において、接続点B2とIGBTのゲートとの間に、スイッチS5及び抵抗器R3を挿入した回路構成を有する。その他の構成は比較例2のスイッチング素子の駆動回路20(図3参照)と同様であるため、重複説明は省略する。

【0043】

図6は、比較例2の変形例のスイッチング素子の駆動回路20Aの駆動方法を示すタイミングチャートである。

【0044】

図6(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0045】

図6(B)のタイミングチャートは、各スイッチS1、S11、S12、S2、S5のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t5は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、比較例2の時刻t1〜t3とは無関係である。

【0046】

図6(B)に示すように、時刻t1より前では、スイッチS1、S11、S12、S5はオフであり、スイッチS2がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図6(A)に示すように電源E2の電圧が負バイアス(Vge=−E2)として印加されており、IGBTはオフである。

【0047】

図6(B)に示すように、時刻t1で、スイッチS2がオフされるとともに、スイッチS5がオンされると、IGBTのゲートは接地されるため、IGBTのゲート・エミッタ間電圧は0Vとなる。

【0048】

次に、図6(B)に示すように、時刻t2で、スイッチS1、S11がオンにされるとともに、スイッチS5がオフにされると、図6(A)に示すように、IGBTのゲート・エミッタ間には、電源E11の出力電圧(E11)が印加されるため、IGBTはオンする。

【0049】

また、時刻t3でスイッチS12がオンされるとともに、スイッチS11がオフされると、IGBTのゲートには電源E12が印加されるため、ゲート・エミッタ間電圧はE12に上昇する。

【0050】

その後、時刻t4でスイッチS5がオンされるとともに、スイッチS1、S12がオフされると、IGBTのゲートは接地されるため、IGBTのゲート・エミッタ間電圧は0Vとなり、IGBTはオフになる。

【0051】

さらに、時刻t5でスイッチS2がオンになるとともに、スイッチS5がオフになると、IGBTのゲートには電源E2の電圧が負バイアス(Vge=−E2)として印加されるため、ゲート・エミッタ間電圧は−E2に低下する。これで時刻t1以前の状態と同様の状態になる。

【0052】

図7は、比較例2の変形例のスイッチング素子の駆動回路20Aによる1スイッチングあたりの消費エネルギを示す図である。比較例2の変形例のスイッチング素子の駆動回路20Aで図6に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0053】

IGBTのオン時の電源E11の消費エネルギは{E11×Cg×E11}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTのオンにするときの電圧変動幅E11を乗じて得る値である。

【0054】

IGBTのオン時の電源E12の消費エネルギは{E12×Cg×(E12−E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、電源E11から電源E12に切り替えたときの電圧変動幅(E12−E11)を乗じて得る値である。

【0055】

また、IGBTのオン時の消費エネルギは、電源E2では0である。これは、オン時には電源E2は無関係だからである。

【0056】

また、IGBTのオフ時の電源E11、E12の消費エネルギは0である。これは、オフ時には電源E11、E12は無関係だからである。

【0057】

また、IGBTのオフ時のE2の消費エネルギは{E2×Cg×E2}である。これは、電源E2の出力電圧E2に、ゲート容量Cgと、IGBTのオフにするときの電圧変動幅E2を乗じて得る値である。

【0058】

ここで、E11=13V、E12=18V、E2=5V、IGBTのゲート容量Cg=0.1μFの場合には、IGBTのオン時の電源E11の消費エネルギ{E11×Cg×E11}は16.9μJである。また、IGBTのオン時の電源E12の消費エネルギ{E12×Cg×(E12−E11)}は、9μJである。また、IGBTのオフ時のE2の消費エネルギ{E2×Cg×E2}は、2.5μJである。

【0059】

これらを合計すると、比較例2の変形例のスイッチング素子の駆動回路20Aで図6に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギの具体値は28.4μJとなる。この値は、比較例2のスイッチング素子の駆動回路20で図3に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギ(43.9μJ)よりも低減されている。これは、図3と図6に示す駆動方法における差であり、図6に示すように、IGBTをオン/オフする際に、ゲートの電位を0V(接地)にする期間を設けたことによって得られたものである。

【0060】

図8は、比較例3のスイッチング素子の駆動回路を示す図である。

【0061】

比較例3のスイッチング素子の駆動回路30は、図1に示す比較例1のスイッチング素子の駆動回路10と、図2に示す比較例2のスイッチング素子の駆動回路20とを組み合わせた構成を有する。

【0062】

図8に示すように、比較例3のスイッチング素子の駆動回路30は、スイッチS1、S2、S3、S4、S11、S12、抵抗器R1、R2、及び電源E11、E12を有する。

【0063】

スイッチS1〜S4と抵抗器R1、R2は、図1に示す比較例1のスイッチング素子の駆動回路10と同様に、IGBTに対してブリッジ接続されている。

【0064】

また、スイッチS1の入力端子側には、スイッチS11とS12の出力側の接続点Aが接続されている。

【0065】

スイッチS11は、接続点Aと電源E11との正極性端子との間に挿入され、スイッチS12は、接続点Aと電源E12の正極性端子との間に挿入されている。

【0066】

図9は、比較例3のスイッチング素子の駆動回路30の駆動方法を示すタイミングチャートである。

【0067】

図9(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0068】

図9(B)のタイミングチャートは、各スイッチS1、S2、S3、S4、S11、S12のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t4は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、比較例3以外における時刻(t1〜t5等)とは無関係である。

【0069】

図9(B)に示すように、時刻t1より前では、スイッチS1、S4、S12、S11はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図9(A)に示すように電源E11の電圧が負バイアス(Vge=−E11)として印加されており、IGBTはオフである。

【0070】

図9(B)に示すように、時刻t1で、スイッチS1、S4、S12がオンにされるとともに、スイッチS2、S3がオフにされると、図9(A)に示すように、IGBTのゲート・エミッタ間には、電源E12の出力電圧(E12)が印加されるため、IGBTはオンする。

【0071】

また、時刻t2でスイッチS12がオフされるとともに、スイッチS11がオンされると、IGBTのゲートには電源E11が印加されるため、ゲート・エミッタ間電圧はE11に低下する。

【0072】

その後、時刻t3でスイッチS12がオンされるとともに、スイッチS11がオフされると、IGBTのゲートには電源E12が印加されるため、ゲート・エミッタ間電圧はE12に上昇する。

【0073】

時刻t4では、スイッチS1、S4、S12はオフにされ、スイッチS2、S3がオンにされる。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0074】

図10は、比較例3のスイッチング素子の駆動回路30による1スイッチングあたりの消費エネルギを示す図である。比較例3のスイッチング素子の駆動回路30で図9に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0075】

IGBTのオン時の電源E12の消費エネルギは{E12×Cg×(E12+E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、IGBTのオンにするときの電圧変動幅{E12−(−E11)}(=E12+E11)を乗じて得る値である。

【0076】

また、IGBTのオン時の消費エネルギは、電源E11では0である。これは、オン時には電源E11は無関係だからである。

【0077】

また、IGBTのオフ時のE12の消費エネルギは0である。これは、オフ時には電源E12は無関係だからである。

【0078】

また、IGBTのオフ時のE11の消費エネルギは{E11×Cg×(E12+E11)}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTのオフにするときの電圧変動幅{E12−(−E11)}(=E12+E11)を乗じて得る値である。

【0079】

従って、比較例3のスイッチング素子の駆動回路でIGBTを図9に示す駆動方法で駆動した場合の1スイッチングあたりの合計の消費エネルギは、{Cg×(E12+E11)2}となる。

【0080】

ここで、E12=18V、E11=13V、IGBTのゲート容量Cg=0.1μFの場合に、これらの値を{Cg×(E12+E11)2}に代入すると、具体値は96.1μJとなる。なお、電源E12の出力電圧は、IGBTのゲート耐圧(例えば、20V)より少し低い値であり、電源E11の出力電圧は、飽和電流を制限するための値に設定である。

【0081】

<実施の形態>

実施の形態のスイッチング素子の駆動回路について説明する前に、実施の形態のスイッチング素子の駆動回路を含む電気自動車用駆動装置について説明する。

【0082】

図11は、実施の形態のスイッチング素子の駆動回路を含む電気自動車用駆動装置300の一実施例の概略構成を示す図である。

【0083】

電気自動車用駆動装置300は、バッテリ301の電力を用いて走行用モータ304を駆動することにより車両を駆動させる装置である。尚、電気自動車は、電力を用いて走行用モータ304を駆動して走行するものであれば、その方式や構成の詳細は任意である。電気自動車は、典型的には、動力源がエンジンと走行用モータ304であるハイブリッド自動車(HV),動力源が走行用モータ304のみである電気自動車を含む。

【0084】

電気自動車用駆動装置300は、図11に示すように、バッテリ301、DC/DCコンバータ302、インバータ303、走行用モータ304、及び、制御装置305を備える。

【0085】

バッテリ301は、電力を蓄積して直流電圧を出力する任意の蓄電装置であり、ニッケル水素バッテリ、リチウムイオンバッテリや電気2重層キャパシタ等の容量性負荷から構成されてもよい。

【0086】

DC/DCコンバータ302は、双方向のDC/DCコンバータ(可逆チョッパ方式の昇圧DC/DCコンバータ)であり、例えば14Vから42Vへの昇圧変換、及び、42Vから14Vへの降圧変換が可能である。DC/DCコンバータ302は、スイッチング素子Q1,Q2,ダイオードD1,D2、リアクトルL1を含む。

【0087】

スイッチング素子Q1,Q2は、本例ではIGBT(Insulated Gate Bipolar Transistor)であるが、MOSFET(Metal Oxide Semiconductor Field-Effect Transistor)のような他のスイッチング素子が用いられてもよい。

【0088】

スイッチング素子Q1,Q2は、インバータ303の正極ラインと負極ラインとの間に直列に接続される。上アームのスイッチング素子Q1のコレクタは正極ラインに接続され、下アームのスイッチング素子Q2のエミッタは負極ラインに接続される。スイッチング素子Q1,Q2の中間点、即ちスイッチング素子Q1のエミッタとスイッチング素子Q2のコレクタの接続点にはリアクトルL1の一端が接続される。このリアクトルL1の他端は、正極ラインを介してバッテリ301の正極に接続される。また、スイッチング素子Q2のエミッタは、負極ラインを介してバッテリ301の負極に接続される。また、各スイッチング素子Q1,Q2のコレクタ−エミッタ間には、エミッタ側からコレクタ側に電流を流すようにダイオード(フライホイルダイオード)D1,D2が配置される。また、リアクトルL1の他端と負極ラインとの間には平滑用コンデンサC1が接続され、スイッチング素子Q1のコレクタと負極ラインとの間には平滑用コンデンサC2が接続される。

【0089】

インバータ303は、正極ラインと負極ラインとの間に互いに並列に配置されるU相、V相、W相の各アームから構成される。U相はスイッチング素子(本例ではIGBT)Q3,Q4の直列接続からなり、V相はスイッチング素子(本例ではIGBT)Q5,Q6の直列接続からなり、W相はスイッチング素子(本例ではIGBT)Q7,Q8の直列接続からなる。また、各スイッチング素子Q3〜Q8のコレクタ−エミッタ間には、それぞれ、エミッタ側からコレクタ側に電流を流すようにダイオード(フライホイルダイオード)D3〜D8が配置される。尚、インバータ303の上アーム(高電位側のアーム)は、各スイッチング素子Q3,Q5,Q7及びダイオードD3,D5,D7から構成され、インバータ303の下アーム(低電位側のアーム)は、各スイッチング素子Q4,Q6,Q8及びダイオードD4,D6,D8から構成される。

【0090】

走行用モータ304は、三相の永久磁石モータであり、U,V,W相の3つのコイルの一端が中点で共通接続されている。U相コイルの他端は、スイッチング素子Q3,Q4の中間点に接続され、V相コイルの他端は、スイッチング素子Q5,Q6の中間点に接続され、W相コイルの他端は、スイッチング素子Q7,Q8の中間点に接続される。

【0091】

制御装置305は、DC/DCコンバータ302及びインバータ303を制御する。制御装置305は、例えばCPU,ROM、メインメモリなどを含み、制御装置305の各種機能は、ROM等に記録された制御プログラムがメインメモリに読み出されてCPUにより実行されることによって実現される。但し、制御装置305の一部又は全部は、ハードウェアのみにより実現されてもよい。また、制御装置305は、物理的に複数の装置により構成されてもよい。

【0092】

実施の形態のスイッチング素子の駆動回路は、例えば、インバータ303のスイッチング素子Q3〜Q8を駆動する駆動回路として用いられる。スイッチング素子Q3〜Q8は、一例として、IGBTで構成される。

【0093】

図11に示す構成では、実施の形態のスイッチング素子の駆動回路は、制御装置305に含まれる。

【0094】

次に、実施の形態のスイッチング素子の駆動回路について説明する。

【0095】

図12は、実施の形態のスイッチング素子の駆動回路を示す図である。

【0096】

実施の形態のスイッチング素子の駆動回路100は、電源E1、E3、スイッチS1、S2、S3、S4、及び抵抗器R1、R2を含み、スイッチング素子としてのIGBTを駆動する。

【0097】

ここでは、一例として、比較例1のスイッチング素子の駆動回路がインバータに含まれるIGBTを駆動する場合について説明する。

【0098】

IGBTのゲートは、抵抗器R1及びスイッチS1を介して、電源E1の正極性端子に接続されるとともに、抵抗器R2及びスイッチS2を介して、電源E1の負極性端子、スイッチS4、及び電源E3の負極性端子に接続されている。

【0099】

IGBTのエミッタは、スイッチS3とスイッチS4の中点に接続されている。

【0100】

IGBTのコレクタは、IGBTがインバータの上アームに含まれる場合は、コレクタはインバータに接続される電源に接続され、IGBTがインバータの下アームに含まれる場合は、コレクタは上アームと下アームの中点に接続される。

【0101】

スイッチS3は、電源E3の正極性端子とIGBTのエミッタとの間に接続されており、スイッチS4は、電源E3の負極性端子とIGBTのエミッタとの間に接続されている。なお、電源E3の出力電圧(E3)は、電源E1の出力電圧(E1)よりも低く設定されている。

【0102】

スイッチS1〜S4としては、例えば、トランジスタを用いることができる。スイッチS1〜S4の駆動は、図11に示す制御装置305で行えばよい。

【0103】

図13は、実施の形態のスイッチング素子の駆動回路の変形例を示す図である。

【0104】

図13に示す実施の形態の変形例のスイッチング素子の駆動回路100Aでは、図12に示す電源E3の代わりに、ダイオードZD1、キャパシタC1、及び抵抗器R4が接続されている。

【0105】

ここで、電源E3と、ダイオードZD1、キャパシタC1、及び抵抗器R4とは、それぞれ、電圧出力部の一例である。電源E3と、ダイオードZD1、キャパシタC1、及び抵抗器R4とは等価であるため、以下では、ダイオードZD1、キャパシタC1、及び抵抗器R4をまとめて電源E3として取り扱う場合がある。

【0106】

ダイオードZD1は、例えば、ツェナーダイオードで構成される整流素子であり、スイッチS3及びS4の両端間に並列に接続される。ダイオードZD1の入力端子はスイッチS4に接続されており、出力端子はスイッチS3に接続されている。すなわち、ダイオードZD1は、図13中において、下側(低電位側)から上側(高電位側)に向かう方向の整流方向を有する。

【0107】

キャパシタC1は、ダイオードZD1に並列に接続される。

【0108】

抵抗器R4は、一端がダイオードZD1の出力端子、キャパシタC1の一端(高電位側の端子)及びスイッチS3の一端(高電位側の端子)に接続されるとともに、他端が電源E1とスイッチS1の一端(高電位側の端子)に接続されている。

【0109】

ここで、例えば、IGBTの閾値電圧は6Vであり、ゲート耐圧は20Vであるとする。また、飽和電流を所定値(例えば、ノイズ等の生じない適切な電流値)に抑えるためのゲート・エミッタ間電圧Vgeは13Vであり、オフ時に誤ってオンにないためのゲート・エミッタ間電圧Vgeは逆バイアスで3V以上(−3V以下)であることが必要である。

【0110】

このため、一例として、電源E1の出力電圧E1を18V、電源E3の出力電圧E3を5Vに設定する。

【0111】

ここで、実施の形態のスイッチング素子の駆動回路100、100Aによって駆動されるIGBTは、例えば、インバータの一対のアーム(上アームと下アーム(図11参照))のうちの一方のアームに含まれており、IBGTのエミッタ・コレクタ間には、図示しないFWD(Free Wheel Diode)が接続されている。インバータの一対のアームには、それぞれ、IGBTとFWDが含まれており(図11参照)、一方のアームのIGBTと、他方のアームのIGBTとは、交互に(互い違いに)オンにされる。

【0112】

すなわち、他方のアームのIGBTがオンのときには、一方のアームのIGBTはオフにされることが必要であり、誤ってオンになることはインバータの効率低下に繋がる虞があるため、好ましくない。このため、スイッチング素子の駆動回路100、100Aには、IGBTを確実にオフにされることが求められる。

【0113】

また、IGBTのオン/オフのスイッチングに伴い、エネルギ損失が生じるため、スイッチング素子の駆動回路100、100Aには、エネルギ損失が低減されていることが求められる。

【0114】

図14は、実施の形態のスイッチング素子の駆動回路100の駆動方法を示すタイミングチャートである。

【0115】

図14(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0116】

図14(B)のタイミングチャートは、各スイッチS1、S2、S3、S4のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t4は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、図14以外における時刻(t1〜t5等)とは無関係である。

【0117】

図14(B)に示すように、時刻t1より前では、スイッチS1、S4はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図14(A)に示すように電源E3の電圧が負バイアス(Vge=−E3)として印加されており、IGBTはオフである。

【0118】

図14(B)に示すように、時刻t1で、スイッチS1、S4がオンにされるとともに、スイッチS2、S3がオンにされると、図14(A)に示すように、IGBTのゲート・エミッタ間には、電源E1の出力電圧(E1)が印加されるため、IGBTはオンする。

【0119】

このようにIGBTのゲート・エミッタ間に時刻t2以降よりも大きな電圧を印加するのは、オフからオンへのスイッチング速度を速くするためである。

【0120】

また、時刻t2でスイッチS3がオンされるとともに、スイッチS4がオフされると、IGBTのゲートには電源E1が接続されるとともに、IGBTのエミッタに電源E3が接続されるため、ゲート・エミッタ間電圧は(E1−E3)に低下する。

【0121】

時刻t2から時刻t3の間では、ゲート・エミッタ間電圧は(E1−E3)に低下させることにより、IGBTの飽和電流を抑えることで、インバータの対向アーム(他方のアーム)でのダイオードのリカバリーノイズの発生を抑制する。

【0122】

その後、時刻t3でスイッチS3がオフされるとともに、スイッチS4がオンされると、IGBTのゲートには電源E1が接続されるため、ゲート・エミッタ間電圧はE1に上昇する。時刻t3からt4の間でゲート・エミッタ間電圧はE1に上昇させるのは、IGBTのオン電圧を下げることにより、IGBTの損失を低下させるためである。

【0123】

時刻t4では、スイッチS1、S4はオフにされ、スイッチS2、S3がオンにされる。これで時刻t1以前の状態と同様の状態になり、IGBTのゲート・エミッタ間電圧には図14(A)に示すように電源E3の電圧が負バイアス(Vge=−E3)として印加されており、IGBTはオフになる。

【0124】

このようにIGBTのゲート・エミッタ間電圧に負バイアス(Vge=−E3)を印加するのは、対向アームに含まれるIGBTがオンにされたときに、当該アームのIGBTが誤ってオンになることを抑制するためである。

【0125】

図15は、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。実施の形態のスイッチング素子の駆動回路100で図14に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0126】

IGBTのオン時の電源E1の消費エネルギは{E1×Cg×(E1+E3)}である。これは、電源E1の出力電圧E1に、ゲート容量Cgと、IGBTをオンにするときの電圧変動幅{E1−(−E3)}(=E1+E3)を乗じて得る値である。

【0127】

また、IGBTのオン時の電源E3では0である。これは、IGBTをオンにする際に、電源E3は仕事をしないからである。

【0128】

また、IGBTをオフにするときは、電源E1では0である。これは、IGBTをオフにする際に、電源E1は無関係だからである。

【0129】

また、IGBTをオフにするときは、電源E3では{E3×Cg×(E1+E3)}である。これは、電源E3の出力電圧E3に、ゲート容量Cgと、IGBTをオフにするときの電圧変動幅{E1−(−E3)}(=E1+E3)を乗じて得る値である。

【0130】

すなわち、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギは、オン時における電源E1の{E1×Cg×(E1+E3)}と、オフ時における電源E3の{E3×Cg×(E1+E3)}との合計であり、{Cg×(E1+E3)2}となる。

【0131】

ここで、E1=18V、E3=5V、IGBTのゲート容量Cg=0.1μFの場合に、これらの値を{Cg×(E1+E3)2}に値を代入すると、具体値は52.9μJであり、これは、本実施の形態の図14に示す駆動方法と同様の図9に示す駆動方法を用いて、比較例3のスイッチング素子の駆動回路30でIGBTを駆動した場合の96.1μJに比べて大幅に低減された値である。

【0132】

以上のように、実施の形態のスイッチング素子の駆動回路100によれば、IBGTを確実にオフできるとともに、スイッチングに伴うエネルギ損失を低減することができる。

【0133】

このようにエネルギ損失が低減されたのは、主に、比較例3に比べて、スイッチング(オン/オフ)を行う際の電圧の変動幅が小さくなったためである。

【0134】

また、4つのスイッチング素子(S1〜S4)と、2つの電源(E1、E2)とを含むスイッチング素子の駆動回路100で、IBGTの確実なオフと、エネルギ損失の低減とを実現できる。このため、スイッチング素子の駆動回路100を低コストで提供することができる。

【0135】

図16は、実施の形態のスイッチング素子の駆動回路100の他の駆動方法を示すタイミングチャートである。

【0136】

図16(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0137】

図16(B)のタイミングチャートは、各スイッチS1、S2、S3、S4のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t5は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、図16以外における時刻(t1〜t5等)とは無関係である。

【0138】

図16(B)に示すように、時刻t1より前では、スイッチS1、S4はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図16(A)に示すように電源E3の電圧が負バイアス(Vge=−E3)として印加されており、IGBTはオフである。

【0139】

図16(B)に示すように、時刻t1でスイッチS3がオフにされるとともに、スイッチS4がオンにされると、エミッタが接地されるため、ゲート・エミッタ間電圧Vgeは0Vになる。このとき、エミッタが接地されることにより、IGBTのゲートに蓄積されている電荷が放出される。

【0140】

次に、時刻t2で、スイッチS1、S3がオンにされるとともに、S2、S4がオフにされると、ゲート・エミッタ間電圧Vgeは、(E1−E3)になる。この状態では、IGBTのゲートが充電されてIGBTがオンするとともに、キャパシタC1に高電位側の端子から低電位側の端子に向けて電流が流れ込むことにより、キャパシタC1が充電される。

【0141】

次に、時刻t3でスイッチS3がオフされるとともに、スイッチS4がオンにされると、電源E1の出力電圧(E1)が印加されるため、IGBTはオン状態を維持する。

【0142】

次に、時刻t4でスイッチS1がオフされるとともに、スイッチS2がオンされると、ゲIGBTのゲートが接地されるため、IGBTはオフになる。

【0143】

その後、時刻t5でスイッチS3がオンにされるとともに、スイッチS4がオフにされると、IGBTのゲート・エミッタ間電圧Vgeは−E3に設定される。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0144】

時刻t5以降は、他のアームのIGBT(図示せず)がオンされるが、ゲート・エミッタ間電圧Vgeは−E3に設定されるため、当該アームのIGBTが誤ってオンにされることが抑制される。

【0145】

図17は、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。図17に示すように、実施の形態のスイッチング素子の駆動回路100を図16に示す駆動方法で駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0146】

IGBTのオン時の電源E1の{E1×Cg×E1}である。これは、電源E1の出力電圧E1に、ゲート容量Cgと、IGBTをオンにするときの電圧変動幅E1を乗じて得る値である。

【0147】

また、IGBTのオン時の電源E3では−{E3(Cg(E1−E3))}である。この電源E3の{E3(−Cg(E1−E3))は、図16に示す時刻t2〜t3の間にキャパシタC1が充電されることによってエネルギが回生されたものである。このため、これは、電源E3の出力電圧に、ゲート容量Cgと、電源E1と電源E3との出力電圧の差(E1−E3)を乗じて得る値に負の符号“−”を乗じた値になる。

【0148】

また、IGBTのオフ時の電源E1の消費エネルギは0である。これは、IGBTをオフにするときは、電源E1は無関係であるからである。

【0149】

また、IGBTのオフ時の電源E3の消費エネルギは{E3×Cg×E3}である。これは、電源E3の出力電圧E3に、ゲート容量Cgと、IGBTをオフにするときの電圧変動幅E3を乗じて得る値である。

【0150】

すなわち、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギは、電源E1ではオン時における{E1×Cg×E1}と、オフ時における0との合計(Cg×E12)となる。

【0151】

ここで、E1=18V、E3=5V、IGBTのゲート容量Cg=0.1μFであるとし、これらの値を(Cg×E12)に代入すると、具体値は32.4μJである。

【0152】

また、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギは、電源E3では、IGBTのオフ時の{E3(−Cg(E1−E3))}と、IGBTのオフ時の{E3×Cg×E3}との合計{Cg×E3(2E3−E1)}である。{Cg×E3(2E3−E1)}に上述の値を代入すると、具体値は−4μJである。

【0153】

従って、実施の形態のスイッチング素子の駆動回路100で図16に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、電源E1側と電源E3側との合計として、28.4μJである。

【0154】

ここで、実施の形態のスイッチング素子の駆動回路100で図16に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギ(28.4μJ)は、比較例2の変形例のスイッチング素子の駆動回路20Aで図6に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギ(28.4μJ)と同一である。

【0155】

しかしながら、比較例2の変形例のスイッチング素子の駆動回路20A(図5参照)は、3つの電源E11、E12、E2、及び、5つのスイッチS1〜S5を用いており、本実施の形態のスイッチング素子の駆動回路100(図13参照)に比べて部品点数が多く、回路構成が複雑である。

【0156】

従って、本実施の形態では、電力損失が少なく、低コストなスイッチング素子の駆動回路100を提供できる。

【0157】

また、実施の形態のスイッチング素子の駆動回路100で図16に示す駆動方法でIGBTを駆動した場合に電力損失を少なくできたことには、時刻t2〜t3の間にキャパシタC1が充電されることによってIGBTに蓄積されたエネルギエネルギが回生されたことも寄与している。

【0158】

このようにキャパシタC1は動作中に充電されるため、抵抗器R4は無くても電源E3を得ることができる。インバータの動作開始時に電源E3が必要な場合に抵抗器R4を設けることで予めキャパシタC1を充電しておくことができる。なお、インバータの高圧電源投入前に図16の駆動方法でIGBTのゲート・エミッタ間に電圧を与えることで、キャパシタC1を充電しておくことが可能であり、その場合も抵抗器R4を省略することができる。

【0159】

最後に、図18及び図19を用いて、比較例3のスイッチング素子の駆動回路30を実施の形態のスイッチング素子の駆動回路100と同様に、オン/オフの際にゲート・エミッタ間電圧Vgeを一端0Vにする駆動方法で駆動した場合の消費エネルギについて説明する。

【0160】

図18は、比較例3のスイッチング素子の駆動回路30(図8参照)の駆動方法を示すタイミングチャートである。

【0161】

図18(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0162】

図18(B)のタイミングチャートは、各スイッチS1、S2、S3、S4、S12、S11のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。

【0163】

図18(B)に示すように、時刻t1より前では、スイッチS1、S4、S12、S11はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図18(A)に示すように電源E11の電圧が負バイアス(Vge=−E11)として印加されており、IGBTはオフである。

【0164】

図18(B)に示すように、時刻t1でスイッチS3がオフにされるとともに、スイッチS4がオンにされると、エミッタが接地されるため、ゲート・エミッタ間電圧Vgeは0Vになる。

【0165】

次に、時刻t2で、スイッチS1、S11がオンにされるとともに、S2がオフにされると、ゲート・エミッタ間電圧Vgeは、E11になる。

【0166】

次に、時刻t3でスイッチS12がオンにされるとともに、スイッチS11がオフにされると、電源E12の出力電圧(E12)が印加されるため、IGBTはオン状態を維持する。

【0167】

次に、時刻t4でスイッチS1、S12がオフされるとともに、スイッチS2がオンされると、IGBTのゲートが接地されるため、IGBTはオフになる。

【0168】

その後、時刻t5でスイッチS3がオンにされるとともに、スイッチS4がオフにされると、IGBTのゲート・エミッタ間電圧Vgeは−E11に設定される。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0169】

図19は、比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。図19に示すように、比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギは、次の通りである。

【0170】

IGBTのオン時の電源E12側で消費エネルギの{E12×Cg×(E12−E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、電源E12と電源E11との出力電圧の差(E12−E11)を乗じて得る値である。

【0171】

また、IGBTのオン時の電源E11の消費エネルギは{E11×Cg×E11}である。これは、電源E11の出力電圧E1に、ゲート容量Cgと、IGBTをオンにするときの電圧変動幅E1を乗じて得る値である。

【0172】

また、IGBTをオフ時の電源E12の消費エネルギは0である。これは、IGBTがオフのときには、電源E12は無関係だからである。

【0173】

また、IGBTをオフ時の電源E11の消費エネルギは{E11×Cg×E11}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTをオフにするときの電圧変動幅E11を乗じて得る値である。

【0174】

すなわち、比較例3のスイッチング素子の駆動回路によって図18のようにIGBTを駆動した場合の1スイッチングあたりの消費エネルギは、電源E12の{E12×Cg×(E12−E11)}と、電源E11の{2×Cg×E112}となる。

【0175】

ここで、E12=18V、E11=13V、IGBTのゲート容量Cg=0.1μFである場合に、電源E12の{E12×Cg×(E12−E11)}に上述の値を代入すると、具体値は9μJであり、電源E11の{2×Cg×E112}に上述の値を代入すると、具体値は33.8μJである。

【0176】

従って、比較例3のスイッチング素子の駆動回路30によって図18のようにIGBTを駆動した場合の1スイッチングあたりの消費エネルギは、42.8μJである。

【0177】

これは、実施の形態のスイッチング素子の駆動回路100を図16に示す駆動方法で駆動した場合(28.4μJ)に比べて、約37%程大きな値である。

【0178】

このように消費電力が大きいのは、主に、比較例3のスイッチング素子の駆動回路30では、エネルギの回生が行われていないことが原因と考えられる。

【0179】

以上のように、実施の形態によれば、電力損失が少なく、低コストなスイッチング素子の駆動回路100を提供することができる。

【0180】

また、本実施の形態のスイッチング素子の駆動回路100は、IGBTを駆動する際の消費エネルギが比較例のスイッチング素子の駆動回路よりも小さいので、IGBTを駆動する際の発熱量が低減される。また、電源(特にE3)を小型化することができる。

【0181】

なお、以上では、本実施の形態のスイッチング素子の駆動回路をインバータに適用する場合について説明したが、本実施の形態のスイッチング素子の駆動回路は、インバータ以外の機器にも適用することができる。

【0182】

以上、本発明の例示的な実施の形態のスイッチング素子の駆動回路について説明したが、本発明は、具体的に開示された実施の形態に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【符号の説明】

【0183】

100、100A スイッチング素子の駆動回路

E1、E3 電源

S1、S2、S3、S4 スイッチ

R1、R2、R4 抵抗器

ZD1 ダイオード

C1 キャパシタ

【技術分野】

【0001】

本発明は、スイッチング素子の駆動回路に関する。

【背景技術】

【0002】

従来より、IGBT(Insulated Gate Bipolar Transistor)のゲートにオントランジスタとオフトランジスタを接続し、IGBTをオフになるときに、オントランジスタをオフにしてゲートへの正電圧の印加を遮断するとともに、オフトランジスタをオンにしてゲートに逆バイアス電圧を印加することにより、IGBTのオフ時にIGBTが誤オンすることを防止したゲート駆動回路があった(例えば、特許文献1参照)。

【0003】

また、正電源のみでIGBTのオフ時にIGBTが誤オンすることを防止するために、HブリッジでIGBTのゲートを駆動する方法があった(例えば、特許文献2参照)。

【0004】

また、IGBTのゲート電圧が第1の設定値に達した時点で、オン電圧のレベルを低下させ、ゲート電圧が第2の設定値(>第1の設定値)に達した時点で、オン電圧のレベルを元の状態に復帰させるゲート駆動回路があった(例えば、特許文献3参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平07−131971号公報

【特許文献2】国際公開第2009/004715号

【特許文献3】特開2001−352748号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、従来のゲート駆動装置等は、電力損失が大きい、又は、部品点数が多いため、電力損失が少なく、簡素な構成で低コストな駆動回路等は実現されていなかった。

【0007】

そこで、本発明は、電力損失が少なく、低コストなスイッチング素子の駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一局面のスイッチング素子の駆動回路は、電源と、前記電源の正極性端子とスイッチング素子の制御端子との間に挿入される第1スイッチと、前記電源の負極性端子と前記スイッチング素子の制御端子との間に挿入される第2スイッチと、前記スイッチング素子の電流出力端子に一端が接続される第3スイッチと、前記スイッチング素子の前記電流出力端子に一端が接続される第4スイッチと、前記第3スイッチの他端に高電位側の端子が接続され、前記第4スイッチの他端に低電位側の端子が接続される電圧出力部とを含む。

【発明の効果】

【0009】

本発明によれば、電力損失が少なく、低コストなスイッチング素子の駆動回路を提供できるという効果が得られる。

【図面の簡単な説明】

【0010】

【図1】比較例1のスイッチング素子の駆動回路を示す図である。

【図2】比較例2のスイッチング素子の駆動回路を示す図である。

【図3】比較例2のスイッチング素子の駆動回路の駆動方法を示すタイミングチャートである。

【図4】比較例2のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【図5】比較例2の変形例のスイッチング素子の駆動回路を示す図である。

【図6】比較例2の変形例のスイッチング素子の駆動回路の駆動方法を示すタイミングチャートである。

【図7】比較例2の変形例のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【図8】比較例3のスイッチング素子の駆動回路を示す図である。

【図9】比較例3のスイッチング素子の駆動回路の駆動方法を示すタイミングチャートである。

【図10】比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【図11】実施の形態のスイッチング素子の駆動回路を含む電気自動車用駆動装置300の一実施例の概略構成を示す図である。

【図12】実施の形態のスイッチング素子の駆動回路を示す図である。

【図13】実施の形態のスイッチング素子の駆動回路の変形例を示す図である。

【図14】実施の形態のスイッチング素子の駆動回路100の駆動方法を示すタイミングチャートである。

【図15】実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。

【図16】実施の形態のスイッチング素子の駆動回路100の他の駆動方法を示すタイミングチャートである。

【図17】実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。

【図18】比較例3のスイッチング素子の駆動回路30の駆動方法を示すタイミングチャートである。

【図19】比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。

【発明を実施するための形態】

【0011】

本発明のスイッチング素子の駆動回路を適用した実施の形態について説明する前に、図1乃至図10を用いて、比較例のスイッチング素子の駆動回路に生じうる問題点について説明する。

【0012】

図1は、比較例1のスイッチング素子の駆動回路を示す図である。

【0013】

図1に示すように、比較例1のスイッチング素子の駆動回路10は、電源E1、スイッチS1、S2、S3、S4、及び抵抗器R1、R2を含み、スイッチング素子としてのIGBTを駆動する。

【0014】

ここでは、一例として、比較例1のスイッチング素子の駆動回路がインバータに用いられるIGBTを駆動する場合について説明する。

【0015】

IGBTのゲートは、抵抗器R1及びスイッチS1を介して、電源E1の正極性端子とスイッチS3に接続されるとともに、抵抗器R2及びスイッチS2を介して、電源E1の負極性端子とスイッチS4に接続されている。

【0016】

IGBTのエミッタは、スイッチS3とスイッチS4の中点に接続されている。

【0017】

IGBTのコレクタは、IGBTがインバータの上アームに含まれる場合は、コレクタはDC−DCコンバータを介して電源に接続され、IGBTがインバータの下アームに含まれる場合は、コレクタは上アームと下アームの中点に接続される。

【0018】

上述のように、図1に示す比較例1のスイッチング素子の駆動回路10では、スイッチS1〜S4は、IGBTを中心として、ブリッジ接続されている。

【0019】

IGBTをオンにするときには、スイッチS1及びスイッチS4をオンにするとともに、スイッチS2及びスイッチS3をオフにする。また、IGBTをオフにするときには、スイッチS1及びスイッチS4をオフにするとともに、スイッチS2及びスイッチS3をオンにする。

【0020】

図2は、比較例2のスイッチング素子の駆動回路を示す図である。

【0021】

図2に示すように、比較例2のスイッチング素子の駆動回路20は、電源E11、E12、E2、スイッチS1、S2、S11、S12、及び抵抗器R1、R2を含み、スイッチング素子としてのIGBTを駆動する。

【0022】

IGBTのゲートは、抵抗器R1及びスイッチS1を介して、スイッチS11及びスイッチS12の出力側の接続点Aに接続されている。また、IGBTのゲートは、抵抗器R2及びスイッチS2を介して電源E2の負極性端子に接続されている。

【0023】

スイッチS11の入力側(図2中左側の端子)は、電源E11の正極性端子に接続されており、スイッチS12の入力側(図2中左側の端子)は、電源E12の正極性端子に接続されている。

【0024】

電源E11と電源E12の負極性端子は、接続点B1、B2で接続されている。接続点B1には電源E2の正極性端子が接続され、電源E2の負極性端子はスイッチS2に接続されている。接続点B2はIGBTのエミッタに接続されている。

【0025】

図3は、比較例2のスイッチング素子の駆動回路20の駆動方法を示すタイミングチャートである。

【0026】

図3(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0027】

図3(B)のタイミングチャートは、各スイッチS1、S11、S12、S2のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。

【0028】

図3(B)に示すように、時刻t1より前では、スイッチS1、S11、S12はオフであり、スイッチS2がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図3(A)に示すように電源E2の電圧が負バイアス(Vge=−E2)として印加されており、IGBTはオフである。

【0029】

図3(B)に示すように、時刻t1で、スイッチS1、S11がオンにされるとともに、スイッチS2がオフにされると、図3(A)に示すように、IGBTのゲート・エミッタ間には、電源E11の出力電圧(E11)が印加されるため、IGBTはオンする。

【0030】

また、時刻t2でスイッチS12がオンされるとともに、スイッチS11がオフされると、IGBTのゲートには電源E12が印加されるため、ゲート・エミッタ間電圧はE12に上昇する。

【0031】

その後、時刻t3でスイッチS2がオンされるとともに、スイッチS1、S12がオフされると、IGBTのゲートには電源E2の電圧が負バイアス(Vge=−E2)として印加されるため、ゲート・エミッタ間電圧は−E2に低下する。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0032】

図4は、比較例2のスイッチング素子の駆動回路20による1スイッチングあたりの消費エネルギを示す図である。比較例2のスイッチング素子の駆動回路20で図3に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0033】

IGBTのオン時の電源E11の消費エネルギは{E11×Cg×(E11+E2)}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTのオンにするときの電圧変動幅{E11−(−E2)}(=E11+E2)を乗じて得る値である。

【0034】

IGBTのオン時の電源E12の消費エネルギは{E12×Cg×(E12−E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、電源E11から電源E12に切り替えたときの電圧変動幅(E12−E11)を乗じて得る値である。

【0035】

また、IGBTのオン時の消費エネルギは、電源E2では0である。これは、オン時には電源E2は無関係だからである。

【0036】

また、IGBTのオフ時の電源E11、E12の消費エネルギは0である。これは、オフ時には電源E11、E12は無関係だからである。

【0037】

また、IGBTのオフ時のE2の消費エネルギは{E2×Cg×(E12+E2)}である。これは、電源E2の出力電圧E2に、ゲート容量Cgと、IGBTのオフにするときの電圧変動幅{E12−(−E2)}(=E12+E2)を乗じて得る値である。

【0038】

ここで、E11=13V、E12=18V、E2=5V、IGBTのゲート容量Cg=0.1μFの場合には、IGBTのオン時の電源E11の消費エネルギ{E11×Cg×(E11+E2)}は23.4μJである。また、IGBTのオン時の電源E12の消費エネルギ{E12×Cg×(E12−E11)}は、9μJである。また、IGBTのオフ時のE2の消費エネルギ{E2×Cg×(E12+E2)}は、11.5μJである。

【0039】

これらを合計すると、比較例2のスイッチング素子の駆動回路20で図3に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギの具体値は43.9μJとなる。

【0040】

次に、図5乃至図7を用いて、比較例2の変形例のスイッチング素子の駆動回路及びその動作について説明する。

【0041】

図5は、比較例2の変形例のスイッチング素子の駆動回路を示す図である。

【0042】

図5に示すように、比較例2の変形例のスイッチング素子の駆動回路20Aは、図2に示す比較例2のスイッチング素子の駆動回路20において、接続点B2とIGBTのゲートとの間に、スイッチS5及び抵抗器R3を挿入した回路構成を有する。その他の構成は比較例2のスイッチング素子の駆動回路20(図3参照)と同様であるため、重複説明は省略する。

【0043】

図6は、比較例2の変形例のスイッチング素子の駆動回路20Aの駆動方法を示すタイミングチャートである。

【0044】

図6(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0045】

図6(B)のタイミングチャートは、各スイッチS1、S11、S12、S2、S5のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t5は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、比較例2の時刻t1〜t3とは無関係である。

【0046】

図6(B)に示すように、時刻t1より前では、スイッチS1、S11、S12、S5はオフであり、スイッチS2がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図6(A)に示すように電源E2の電圧が負バイアス(Vge=−E2)として印加されており、IGBTはオフである。

【0047】

図6(B)に示すように、時刻t1で、スイッチS2がオフされるとともに、スイッチS5がオンされると、IGBTのゲートは接地されるため、IGBTのゲート・エミッタ間電圧は0Vとなる。

【0048】

次に、図6(B)に示すように、時刻t2で、スイッチS1、S11がオンにされるとともに、スイッチS5がオフにされると、図6(A)に示すように、IGBTのゲート・エミッタ間には、電源E11の出力電圧(E11)が印加されるため、IGBTはオンする。

【0049】

また、時刻t3でスイッチS12がオンされるとともに、スイッチS11がオフされると、IGBTのゲートには電源E12が印加されるため、ゲート・エミッタ間電圧はE12に上昇する。

【0050】

その後、時刻t4でスイッチS5がオンされるとともに、スイッチS1、S12がオフされると、IGBTのゲートは接地されるため、IGBTのゲート・エミッタ間電圧は0Vとなり、IGBTはオフになる。

【0051】

さらに、時刻t5でスイッチS2がオンになるとともに、スイッチS5がオフになると、IGBTのゲートには電源E2の電圧が負バイアス(Vge=−E2)として印加されるため、ゲート・エミッタ間電圧は−E2に低下する。これで時刻t1以前の状態と同様の状態になる。

【0052】

図7は、比較例2の変形例のスイッチング素子の駆動回路20Aによる1スイッチングあたりの消費エネルギを示す図である。比較例2の変形例のスイッチング素子の駆動回路20Aで図6に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0053】

IGBTのオン時の電源E11の消費エネルギは{E11×Cg×E11}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTのオンにするときの電圧変動幅E11を乗じて得る値である。

【0054】

IGBTのオン時の電源E12の消費エネルギは{E12×Cg×(E12−E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、電源E11から電源E12に切り替えたときの電圧変動幅(E12−E11)を乗じて得る値である。

【0055】

また、IGBTのオン時の消費エネルギは、電源E2では0である。これは、オン時には電源E2は無関係だからである。

【0056】

また、IGBTのオフ時の電源E11、E12の消費エネルギは0である。これは、オフ時には電源E11、E12は無関係だからである。

【0057】

また、IGBTのオフ時のE2の消費エネルギは{E2×Cg×E2}である。これは、電源E2の出力電圧E2に、ゲート容量Cgと、IGBTのオフにするときの電圧変動幅E2を乗じて得る値である。

【0058】

ここで、E11=13V、E12=18V、E2=5V、IGBTのゲート容量Cg=0.1μFの場合には、IGBTのオン時の電源E11の消費エネルギ{E11×Cg×E11}は16.9μJである。また、IGBTのオン時の電源E12の消費エネルギ{E12×Cg×(E12−E11)}は、9μJである。また、IGBTのオフ時のE2の消費エネルギ{E2×Cg×E2}は、2.5μJである。

【0059】

これらを合計すると、比較例2の変形例のスイッチング素子の駆動回路20Aで図6に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギの具体値は28.4μJとなる。この値は、比較例2のスイッチング素子の駆動回路20で図3に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギ(43.9μJ)よりも低減されている。これは、図3と図6に示す駆動方法における差であり、図6に示すように、IGBTをオン/オフする際に、ゲートの電位を0V(接地)にする期間を設けたことによって得られたものである。

【0060】

図8は、比較例3のスイッチング素子の駆動回路を示す図である。

【0061】

比較例3のスイッチング素子の駆動回路30は、図1に示す比較例1のスイッチング素子の駆動回路10と、図2に示す比較例2のスイッチング素子の駆動回路20とを組み合わせた構成を有する。

【0062】

図8に示すように、比較例3のスイッチング素子の駆動回路30は、スイッチS1、S2、S3、S4、S11、S12、抵抗器R1、R2、及び電源E11、E12を有する。

【0063】

スイッチS1〜S4と抵抗器R1、R2は、図1に示す比較例1のスイッチング素子の駆動回路10と同様に、IGBTに対してブリッジ接続されている。

【0064】

また、スイッチS1の入力端子側には、スイッチS11とS12の出力側の接続点Aが接続されている。

【0065】

スイッチS11は、接続点Aと電源E11との正極性端子との間に挿入され、スイッチS12は、接続点Aと電源E12の正極性端子との間に挿入されている。

【0066】

図9は、比較例3のスイッチング素子の駆動回路30の駆動方法を示すタイミングチャートである。

【0067】

図9(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0068】

図9(B)のタイミングチャートは、各スイッチS1、S2、S3、S4、S11、S12のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t4は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、比較例3以外における時刻(t1〜t5等)とは無関係である。

【0069】

図9(B)に示すように、時刻t1より前では、スイッチS1、S4、S12、S11はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図9(A)に示すように電源E11の電圧が負バイアス(Vge=−E11)として印加されており、IGBTはオフである。

【0070】

図9(B)に示すように、時刻t1で、スイッチS1、S4、S12がオンにされるとともに、スイッチS2、S3がオフにされると、図9(A)に示すように、IGBTのゲート・エミッタ間には、電源E12の出力電圧(E12)が印加されるため、IGBTはオンする。

【0071】

また、時刻t2でスイッチS12がオフされるとともに、スイッチS11がオンされると、IGBTのゲートには電源E11が印加されるため、ゲート・エミッタ間電圧はE11に低下する。

【0072】

その後、時刻t3でスイッチS12がオンされるとともに、スイッチS11がオフされると、IGBTのゲートには電源E12が印加されるため、ゲート・エミッタ間電圧はE12に上昇する。

【0073】

時刻t4では、スイッチS1、S4、S12はオフにされ、スイッチS2、S3がオンにされる。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0074】

図10は、比較例3のスイッチング素子の駆動回路30による1スイッチングあたりの消費エネルギを示す図である。比較例3のスイッチング素子の駆動回路30で図9に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0075】

IGBTのオン時の電源E12の消費エネルギは{E12×Cg×(E12+E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、IGBTのオンにするときの電圧変動幅{E12−(−E11)}(=E12+E11)を乗じて得る値である。

【0076】

また、IGBTのオン時の消費エネルギは、電源E11では0である。これは、オン時には電源E11は無関係だからである。

【0077】

また、IGBTのオフ時のE12の消費エネルギは0である。これは、オフ時には電源E12は無関係だからである。

【0078】

また、IGBTのオフ時のE11の消費エネルギは{E11×Cg×(E12+E11)}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTのオフにするときの電圧変動幅{E12−(−E11)}(=E12+E11)を乗じて得る値である。

【0079】

従って、比較例3のスイッチング素子の駆動回路でIGBTを図9に示す駆動方法で駆動した場合の1スイッチングあたりの合計の消費エネルギは、{Cg×(E12+E11)2}となる。

【0080】

ここで、E12=18V、E11=13V、IGBTのゲート容量Cg=0.1μFの場合に、これらの値を{Cg×(E12+E11)2}に代入すると、具体値は96.1μJとなる。なお、電源E12の出力電圧は、IGBTのゲート耐圧(例えば、20V)より少し低い値であり、電源E11の出力電圧は、飽和電流を制限するための値に設定である。

【0081】

<実施の形態>

実施の形態のスイッチング素子の駆動回路について説明する前に、実施の形態のスイッチング素子の駆動回路を含む電気自動車用駆動装置について説明する。

【0082】

図11は、実施の形態のスイッチング素子の駆動回路を含む電気自動車用駆動装置300の一実施例の概略構成を示す図である。

【0083】

電気自動車用駆動装置300は、バッテリ301の電力を用いて走行用モータ304を駆動することにより車両を駆動させる装置である。尚、電気自動車は、電力を用いて走行用モータ304を駆動して走行するものであれば、その方式や構成の詳細は任意である。電気自動車は、典型的には、動力源がエンジンと走行用モータ304であるハイブリッド自動車(HV),動力源が走行用モータ304のみである電気自動車を含む。

【0084】

電気自動車用駆動装置300は、図11に示すように、バッテリ301、DC/DCコンバータ302、インバータ303、走行用モータ304、及び、制御装置305を備える。

【0085】

バッテリ301は、電力を蓄積して直流電圧を出力する任意の蓄電装置であり、ニッケル水素バッテリ、リチウムイオンバッテリや電気2重層キャパシタ等の容量性負荷から構成されてもよい。

【0086】

DC/DCコンバータ302は、双方向のDC/DCコンバータ(可逆チョッパ方式の昇圧DC/DCコンバータ)であり、例えば14Vから42Vへの昇圧変換、及び、42Vから14Vへの降圧変換が可能である。DC/DCコンバータ302は、スイッチング素子Q1,Q2,ダイオードD1,D2、リアクトルL1を含む。

【0087】

スイッチング素子Q1,Q2は、本例ではIGBT(Insulated Gate Bipolar Transistor)であるが、MOSFET(Metal Oxide Semiconductor Field-Effect Transistor)のような他のスイッチング素子が用いられてもよい。

【0088】

スイッチング素子Q1,Q2は、インバータ303の正極ラインと負極ラインとの間に直列に接続される。上アームのスイッチング素子Q1のコレクタは正極ラインに接続され、下アームのスイッチング素子Q2のエミッタは負極ラインに接続される。スイッチング素子Q1,Q2の中間点、即ちスイッチング素子Q1のエミッタとスイッチング素子Q2のコレクタの接続点にはリアクトルL1の一端が接続される。このリアクトルL1の他端は、正極ラインを介してバッテリ301の正極に接続される。また、スイッチング素子Q2のエミッタは、負極ラインを介してバッテリ301の負極に接続される。また、各スイッチング素子Q1,Q2のコレクタ−エミッタ間には、エミッタ側からコレクタ側に電流を流すようにダイオード(フライホイルダイオード)D1,D2が配置される。また、リアクトルL1の他端と負極ラインとの間には平滑用コンデンサC1が接続され、スイッチング素子Q1のコレクタと負極ラインとの間には平滑用コンデンサC2が接続される。

【0089】

インバータ303は、正極ラインと負極ラインとの間に互いに並列に配置されるU相、V相、W相の各アームから構成される。U相はスイッチング素子(本例ではIGBT)Q3,Q4の直列接続からなり、V相はスイッチング素子(本例ではIGBT)Q5,Q6の直列接続からなり、W相はスイッチング素子(本例ではIGBT)Q7,Q8の直列接続からなる。また、各スイッチング素子Q3〜Q8のコレクタ−エミッタ間には、それぞれ、エミッタ側からコレクタ側に電流を流すようにダイオード(フライホイルダイオード)D3〜D8が配置される。尚、インバータ303の上アーム(高電位側のアーム)は、各スイッチング素子Q3,Q5,Q7及びダイオードD3,D5,D7から構成され、インバータ303の下アーム(低電位側のアーム)は、各スイッチング素子Q4,Q6,Q8及びダイオードD4,D6,D8から構成される。

【0090】

走行用モータ304は、三相の永久磁石モータであり、U,V,W相の3つのコイルの一端が中点で共通接続されている。U相コイルの他端は、スイッチング素子Q3,Q4の中間点に接続され、V相コイルの他端は、スイッチング素子Q5,Q6の中間点に接続され、W相コイルの他端は、スイッチング素子Q7,Q8の中間点に接続される。

【0091】

制御装置305は、DC/DCコンバータ302及びインバータ303を制御する。制御装置305は、例えばCPU,ROM、メインメモリなどを含み、制御装置305の各種機能は、ROM等に記録された制御プログラムがメインメモリに読み出されてCPUにより実行されることによって実現される。但し、制御装置305の一部又は全部は、ハードウェアのみにより実現されてもよい。また、制御装置305は、物理的に複数の装置により構成されてもよい。

【0092】

実施の形態のスイッチング素子の駆動回路は、例えば、インバータ303のスイッチング素子Q3〜Q8を駆動する駆動回路として用いられる。スイッチング素子Q3〜Q8は、一例として、IGBTで構成される。

【0093】

図11に示す構成では、実施の形態のスイッチング素子の駆動回路は、制御装置305に含まれる。

【0094】

次に、実施の形態のスイッチング素子の駆動回路について説明する。

【0095】

図12は、実施の形態のスイッチング素子の駆動回路を示す図である。

【0096】

実施の形態のスイッチング素子の駆動回路100は、電源E1、E3、スイッチS1、S2、S3、S4、及び抵抗器R1、R2を含み、スイッチング素子としてのIGBTを駆動する。

【0097】

ここでは、一例として、比較例1のスイッチング素子の駆動回路がインバータに含まれるIGBTを駆動する場合について説明する。

【0098】

IGBTのゲートは、抵抗器R1及びスイッチS1を介して、電源E1の正極性端子に接続されるとともに、抵抗器R2及びスイッチS2を介して、電源E1の負極性端子、スイッチS4、及び電源E3の負極性端子に接続されている。

【0099】

IGBTのエミッタは、スイッチS3とスイッチS4の中点に接続されている。

【0100】

IGBTのコレクタは、IGBTがインバータの上アームに含まれる場合は、コレクタはインバータに接続される電源に接続され、IGBTがインバータの下アームに含まれる場合は、コレクタは上アームと下アームの中点に接続される。

【0101】

スイッチS3は、電源E3の正極性端子とIGBTのエミッタとの間に接続されており、スイッチS4は、電源E3の負極性端子とIGBTのエミッタとの間に接続されている。なお、電源E3の出力電圧(E3)は、電源E1の出力電圧(E1)よりも低く設定されている。

【0102】

スイッチS1〜S4としては、例えば、トランジスタを用いることができる。スイッチS1〜S4の駆動は、図11に示す制御装置305で行えばよい。

【0103】

図13は、実施の形態のスイッチング素子の駆動回路の変形例を示す図である。

【0104】

図13に示す実施の形態の変形例のスイッチング素子の駆動回路100Aでは、図12に示す電源E3の代わりに、ダイオードZD1、キャパシタC1、及び抵抗器R4が接続されている。

【0105】

ここで、電源E3と、ダイオードZD1、キャパシタC1、及び抵抗器R4とは、それぞれ、電圧出力部の一例である。電源E3と、ダイオードZD1、キャパシタC1、及び抵抗器R4とは等価であるため、以下では、ダイオードZD1、キャパシタC1、及び抵抗器R4をまとめて電源E3として取り扱う場合がある。

【0106】

ダイオードZD1は、例えば、ツェナーダイオードで構成される整流素子であり、スイッチS3及びS4の両端間に並列に接続される。ダイオードZD1の入力端子はスイッチS4に接続されており、出力端子はスイッチS3に接続されている。すなわち、ダイオードZD1は、図13中において、下側(低電位側)から上側(高電位側)に向かう方向の整流方向を有する。

【0107】

キャパシタC1は、ダイオードZD1に並列に接続される。

【0108】

抵抗器R4は、一端がダイオードZD1の出力端子、キャパシタC1の一端(高電位側の端子)及びスイッチS3の一端(高電位側の端子)に接続されるとともに、他端が電源E1とスイッチS1の一端(高電位側の端子)に接続されている。

【0109】

ここで、例えば、IGBTの閾値電圧は6Vであり、ゲート耐圧は20Vであるとする。また、飽和電流を所定値(例えば、ノイズ等の生じない適切な電流値)に抑えるためのゲート・エミッタ間電圧Vgeは13Vであり、オフ時に誤ってオンにないためのゲート・エミッタ間電圧Vgeは逆バイアスで3V以上(−3V以下)であることが必要である。

【0110】

このため、一例として、電源E1の出力電圧E1を18V、電源E3の出力電圧E3を5Vに設定する。

【0111】

ここで、実施の形態のスイッチング素子の駆動回路100、100Aによって駆動されるIGBTは、例えば、インバータの一対のアーム(上アームと下アーム(図11参照))のうちの一方のアームに含まれており、IBGTのエミッタ・コレクタ間には、図示しないFWD(Free Wheel Diode)が接続されている。インバータの一対のアームには、それぞれ、IGBTとFWDが含まれており(図11参照)、一方のアームのIGBTと、他方のアームのIGBTとは、交互に(互い違いに)オンにされる。

【0112】

すなわち、他方のアームのIGBTがオンのときには、一方のアームのIGBTはオフにされることが必要であり、誤ってオンになることはインバータの効率低下に繋がる虞があるため、好ましくない。このため、スイッチング素子の駆動回路100、100Aには、IGBTを確実にオフにされることが求められる。

【0113】

また、IGBTのオン/オフのスイッチングに伴い、エネルギ損失が生じるため、スイッチング素子の駆動回路100、100Aには、エネルギ損失が低減されていることが求められる。

【0114】

図14は、実施の形態のスイッチング素子の駆動回路100の駆動方法を示すタイミングチャートである。

【0115】

図14(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0116】

図14(B)のタイミングチャートは、各スイッチS1、S2、S3、S4のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t4は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、図14以外における時刻(t1〜t5等)とは無関係である。

【0117】

図14(B)に示すように、時刻t1より前では、スイッチS1、S4はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図14(A)に示すように電源E3の電圧が負バイアス(Vge=−E3)として印加されており、IGBTはオフである。

【0118】

図14(B)に示すように、時刻t1で、スイッチS1、S4がオンにされるとともに、スイッチS2、S3がオンにされると、図14(A)に示すように、IGBTのゲート・エミッタ間には、電源E1の出力電圧(E1)が印加されるため、IGBTはオンする。

【0119】

このようにIGBTのゲート・エミッタ間に時刻t2以降よりも大きな電圧を印加するのは、オフからオンへのスイッチング速度を速くするためである。

【0120】

また、時刻t2でスイッチS3がオンされるとともに、スイッチS4がオフされると、IGBTのゲートには電源E1が接続されるとともに、IGBTのエミッタに電源E3が接続されるため、ゲート・エミッタ間電圧は(E1−E3)に低下する。

【0121】

時刻t2から時刻t3の間では、ゲート・エミッタ間電圧は(E1−E3)に低下させることにより、IGBTの飽和電流を抑えることで、インバータの対向アーム(他方のアーム)でのダイオードのリカバリーノイズの発生を抑制する。

【0122】

その後、時刻t3でスイッチS3がオフされるとともに、スイッチS4がオンされると、IGBTのゲートには電源E1が接続されるため、ゲート・エミッタ間電圧はE1に上昇する。時刻t3からt4の間でゲート・エミッタ間電圧はE1に上昇させるのは、IGBTのオン電圧を下げることにより、IGBTの損失を低下させるためである。

【0123】

時刻t4では、スイッチS1、S4はオフにされ、スイッチS2、S3がオンにされる。これで時刻t1以前の状態と同様の状態になり、IGBTのゲート・エミッタ間電圧には図14(A)に示すように電源E3の電圧が負バイアス(Vge=−E3)として印加されており、IGBTはオフになる。

【0124】

このようにIGBTのゲート・エミッタ間電圧に負バイアス(Vge=−E3)を印加するのは、対向アームに含まれるIGBTがオンにされたときに、当該アームのIGBTが誤ってオンになることを抑制するためである。

【0125】

図15は、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。実施の形態のスイッチング素子の駆動回路100で図14に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0126】

IGBTのオン時の電源E1の消費エネルギは{E1×Cg×(E1+E3)}である。これは、電源E1の出力電圧E1に、ゲート容量Cgと、IGBTをオンにするときの電圧変動幅{E1−(−E3)}(=E1+E3)を乗じて得る値である。

【0127】

また、IGBTのオン時の電源E3では0である。これは、IGBTをオンにする際に、電源E3は仕事をしないからである。

【0128】

また、IGBTをオフにするときは、電源E1では0である。これは、IGBTをオフにする際に、電源E1は無関係だからである。

【0129】

また、IGBTをオフにするときは、電源E3では{E3×Cg×(E1+E3)}である。これは、電源E3の出力電圧E3に、ゲート容量Cgと、IGBTをオフにするときの電圧変動幅{E1−(−E3)}(=E1+E3)を乗じて得る値である。

【0130】

すなわち、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギは、オン時における電源E1の{E1×Cg×(E1+E3)}と、オフ時における電源E3の{E3×Cg×(E1+E3)}との合計であり、{Cg×(E1+E3)2}となる。

【0131】

ここで、E1=18V、E3=5V、IGBTのゲート容量Cg=0.1μFの場合に、これらの値を{Cg×(E1+E3)2}に値を代入すると、具体値は52.9μJであり、これは、本実施の形態の図14に示す駆動方法と同様の図9に示す駆動方法を用いて、比較例3のスイッチング素子の駆動回路30でIGBTを駆動した場合の96.1μJに比べて大幅に低減された値である。

【0132】

以上のように、実施の形態のスイッチング素子の駆動回路100によれば、IBGTを確実にオフできるとともに、スイッチングに伴うエネルギ損失を低減することができる。

【0133】

このようにエネルギ損失が低減されたのは、主に、比較例3に比べて、スイッチング(オン/オフ)を行う際の電圧の変動幅が小さくなったためである。

【0134】

また、4つのスイッチング素子(S1〜S4)と、2つの電源(E1、E2)とを含むスイッチング素子の駆動回路100で、IBGTの確実なオフと、エネルギ損失の低減とを実現できる。このため、スイッチング素子の駆動回路100を低コストで提供することができる。

【0135】

図16は、実施の形態のスイッチング素子の駆動回路100の他の駆動方法を示すタイミングチャートである。

【0136】

図16(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0137】

図16(B)のタイミングチャートは、各スイッチS1、S2、S3、S4のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。また、以下で示す時刻t1〜t5は、時間軸における時刻を表すために説明の便宜上用いている記号に過ぎず、図16以外における時刻(t1〜t5等)とは無関係である。

【0138】

図16(B)に示すように、時刻t1より前では、スイッチS1、S4はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図16(A)に示すように電源E3の電圧が負バイアス(Vge=−E3)として印加されており、IGBTはオフである。

【0139】

図16(B)に示すように、時刻t1でスイッチS3がオフにされるとともに、スイッチS4がオンにされると、エミッタが接地されるため、ゲート・エミッタ間電圧Vgeは0Vになる。このとき、エミッタが接地されることにより、IGBTのゲートに蓄積されている電荷が放出される。

【0140】

次に、時刻t2で、スイッチS1、S3がオンにされるとともに、S2、S4がオフにされると、ゲート・エミッタ間電圧Vgeは、(E1−E3)になる。この状態では、IGBTのゲートが充電されてIGBTがオンするとともに、キャパシタC1に高電位側の端子から低電位側の端子に向けて電流が流れ込むことにより、キャパシタC1が充電される。

【0141】

次に、時刻t3でスイッチS3がオフされるとともに、スイッチS4がオンにされると、電源E1の出力電圧(E1)が印加されるため、IGBTはオン状態を維持する。

【0142】

次に、時刻t4でスイッチS1がオフされるとともに、スイッチS2がオンされると、ゲIGBTのゲートが接地されるため、IGBTはオフになる。

【0143】

その後、時刻t5でスイッチS3がオンにされるとともに、スイッチS4がオフにされると、IGBTのゲート・エミッタ間電圧Vgeは−E3に設定される。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0144】

時刻t5以降は、他のアームのIGBT(図示せず)がオンされるが、ゲート・エミッタ間電圧Vgeは−E3に設定されるため、当該アームのIGBTが誤ってオンにされることが抑制される。

【0145】

図17は、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギを示す図である。図17に示すように、実施の形態のスイッチング素子の駆動回路100を図16に示す駆動方法で駆動した場合における1スイッチングあたりの消費エネルギは、次の通りである。

【0146】

IGBTのオン時の電源E1の{E1×Cg×E1}である。これは、電源E1の出力電圧E1に、ゲート容量Cgと、IGBTをオンにするときの電圧変動幅E1を乗じて得る値である。

【0147】

また、IGBTのオン時の電源E3では−{E3(Cg(E1−E3))}である。この電源E3の{E3(−Cg(E1−E3))は、図16に示す時刻t2〜t3の間にキャパシタC1が充電されることによってエネルギが回生されたものである。このため、これは、電源E3の出力電圧に、ゲート容量Cgと、電源E1と電源E3との出力電圧の差(E1−E3)を乗じて得る値に負の符号“−”を乗じた値になる。

【0148】

また、IGBTのオフ時の電源E1の消費エネルギは0である。これは、IGBTをオフにするときは、電源E1は無関係であるからである。

【0149】

また、IGBTのオフ時の電源E3の消費エネルギは{E3×Cg×E3}である。これは、電源E3の出力電圧E3に、ゲート容量Cgと、IGBTをオフにするときの電圧変動幅E3を乗じて得る値である。

【0150】

すなわち、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギは、電源E1ではオン時における{E1×Cg×E1}と、オフ時における0との合計(Cg×E12)となる。

【0151】

ここで、E1=18V、E3=5V、IGBTのゲート容量Cg=0.1μFであるとし、これらの値を(Cg×E12)に代入すると、具体値は32.4μJである。

【0152】

また、実施の形態のスイッチング素子の駆動回路100による1スイッチングあたりの消費エネルギは、電源E3では、IGBTのオフ時の{E3(−Cg(E1−E3))}と、IGBTのオフ時の{E3×Cg×E3}との合計{Cg×E3(2E3−E1)}である。{Cg×E3(2E3−E1)}に上述の値を代入すると、具体値は−4μJである。

【0153】

従って、実施の形態のスイッチング素子の駆動回路100で図16に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギは、電源E1側と電源E3側との合計として、28.4μJである。

【0154】

ここで、実施の形態のスイッチング素子の駆動回路100で図16に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギ(28.4μJ)は、比較例2の変形例のスイッチング素子の駆動回路20Aで図6に示す駆動方法でIGBTを駆動した場合における1スイッチングあたりの消費エネルギ(28.4μJ)と同一である。

【0155】

しかしながら、比較例2の変形例のスイッチング素子の駆動回路20A(図5参照)は、3つの電源E11、E12、E2、及び、5つのスイッチS1〜S5を用いており、本実施の形態のスイッチング素子の駆動回路100(図13参照)に比べて部品点数が多く、回路構成が複雑である。

【0156】

従って、本実施の形態では、電力損失が少なく、低コストなスイッチング素子の駆動回路100を提供できる。

【0157】

また、実施の形態のスイッチング素子の駆動回路100で図16に示す駆動方法でIGBTを駆動した場合に電力損失を少なくできたことには、時刻t2〜t3の間にキャパシタC1が充電されることによってIGBTに蓄積されたエネルギエネルギが回生されたことも寄与している。

【0158】

このようにキャパシタC1は動作中に充電されるため、抵抗器R4は無くても電源E3を得ることができる。インバータの動作開始時に電源E3が必要な場合に抵抗器R4を設けることで予めキャパシタC1を充電しておくことができる。なお、インバータの高圧電源投入前に図16の駆動方法でIGBTのゲート・エミッタ間に電圧を与えることで、キャパシタC1を充電しておくことが可能であり、その場合も抵抗器R4を省略することができる。

【0159】

最後に、図18及び図19を用いて、比較例3のスイッチング素子の駆動回路30を実施の形態のスイッチング素子の駆動回路100と同様に、オン/オフの際にゲート・エミッタ間電圧Vgeを一端0Vにする駆動方法で駆動した場合の消費エネルギについて説明する。

【0160】

図18は、比較例3のスイッチング素子の駆動回路30(図8参照)の駆動方法を示すタイミングチャートである。

【0161】

図18(A)では、IGBTのゲート・エミッタ間電圧Vgeの目標値を実線で示し、実際のゲート・エミッタ間電圧Vgeを破線で示す。

【0162】

図18(B)のタイミングチャートは、各スイッチS1、S2、S3、S4、S12、S11のオン/オフの状況を示す。レベルが高い区間(H)はオンを表し、レベルが低い区間(L)はオフを表す。

【0163】

図18(B)に示すように、時刻t1より前では、スイッチS1、S4、S12、S11はオフであり、スイッチS2、S3がオンである。すなわち、IGBTのゲート・エミッタ間電圧には、図18(A)に示すように電源E11の電圧が負バイアス(Vge=−E11)として印加されており、IGBTはオフである。

【0164】

図18(B)に示すように、時刻t1でスイッチS3がオフにされるとともに、スイッチS4がオンにされると、エミッタが接地されるため、ゲート・エミッタ間電圧Vgeは0Vになる。

【0165】

次に、時刻t2で、スイッチS1、S11がオンにされるとともに、S2がオフにされると、ゲート・エミッタ間電圧Vgeは、E11になる。

【0166】

次に、時刻t3でスイッチS12がオンにされるとともに、スイッチS11がオフにされると、電源E12の出力電圧(E12)が印加されるため、IGBTはオン状態を維持する。

【0167】

次に、時刻t4でスイッチS1、S12がオフされるとともに、スイッチS2がオンされると、IGBTのゲートが接地されるため、IGBTはオフになる。

【0168】

その後、時刻t5でスイッチS3がオンにされるとともに、スイッチS4がオフにされると、IGBTのゲート・エミッタ間電圧Vgeは−E11に設定される。これで時刻t1以前の状態と同様の状態になり、IGBTはオフになる。

【0169】

図19は、比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギを示す図である。図19に示すように、比較例3のスイッチング素子の駆動回路による1スイッチングあたりの消費エネルギは、次の通りである。

【0170】

IGBTのオン時の電源E12側で消費エネルギの{E12×Cg×(E12−E11)}である。これは、電源E12の出力電圧E12に、ゲート容量Cgと、電源E12と電源E11との出力電圧の差(E12−E11)を乗じて得る値である。

【0171】

また、IGBTのオン時の電源E11の消費エネルギは{E11×Cg×E11}である。これは、電源E11の出力電圧E1に、ゲート容量Cgと、IGBTをオンにするときの電圧変動幅E1を乗じて得る値である。

【0172】

また、IGBTをオフ時の電源E12の消費エネルギは0である。これは、IGBTがオフのときには、電源E12は無関係だからである。

【0173】

また、IGBTをオフ時の電源E11の消費エネルギは{E11×Cg×E11}である。これは、電源E11の出力電圧E11に、ゲート容量Cgと、IGBTをオフにするときの電圧変動幅E11を乗じて得る値である。

【0174】

すなわち、比較例3のスイッチング素子の駆動回路によって図18のようにIGBTを駆動した場合の1スイッチングあたりの消費エネルギは、電源E12の{E12×Cg×(E12−E11)}と、電源E11の{2×Cg×E112}となる。

【0175】

ここで、E12=18V、E11=13V、IGBTのゲート容量Cg=0.1μFである場合に、電源E12の{E12×Cg×(E12−E11)}に上述の値を代入すると、具体値は9μJであり、電源E11の{2×Cg×E112}に上述の値を代入すると、具体値は33.8μJである。

【0176】

従って、比較例3のスイッチング素子の駆動回路30によって図18のようにIGBTを駆動した場合の1スイッチングあたりの消費エネルギは、42.8μJである。

【0177】

これは、実施の形態のスイッチング素子の駆動回路100を図16に示す駆動方法で駆動した場合(28.4μJ)に比べて、約37%程大きな値である。

【0178】

このように消費電力が大きいのは、主に、比較例3のスイッチング素子の駆動回路30では、エネルギの回生が行われていないことが原因と考えられる。

【0179】

以上のように、実施の形態によれば、電力損失が少なく、低コストなスイッチング素子の駆動回路100を提供することができる。

【0180】

また、本実施の形態のスイッチング素子の駆動回路100は、IGBTを駆動する際の消費エネルギが比較例のスイッチング素子の駆動回路よりも小さいので、IGBTを駆動する際の発熱量が低減される。また、電源(特にE3)を小型化することができる。

【0181】

なお、以上では、本実施の形態のスイッチング素子の駆動回路をインバータに適用する場合について説明したが、本実施の形態のスイッチング素子の駆動回路は、インバータ以外の機器にも適用することができる。

【0182】

以上、本発明の例示的な実施の形態のスイッチング素子の駆動回路について説明したが、本発明は、具体的に開示された実施の形態に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【符号の説明】

【0183】

100、100A スイッチング素子の駆動回路

E1、E3 電源

S1、S2、S3、S4 スイッチ

R1、R2、R4 抵抗器

ZD1 ダイオード

C1 キャパシタ

【特許請求の範囲】

【請求項1】

電源と、

前記電源の正極性端子とスイッチング素子の制御端子との間に挿入される第1スイッチと、

前記電源の負極性端子と前記スイッチング素子の制御端子との間に挿入される第2スイッチと、

前記スイッチング素子の電流出力端子に一端が接続される第3スイッチと、

前記スイッチング素子の前記電流出力端子に一端が接続される第4スイッチと、

前記第3スイッチの他端に高電位側の端子が接続され、前記第4スイッチの他端に低電位側の端子が接続される電圧出力部と

を含む、スイッチング素子の駆動回路。

【請求項2】

前記電圧出力部は、前記電源が出力する第1電圧よりも低い第2電圧を出力する、請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記電圧出力部は、前記低電位側の端子から前記高電位側の端子の方向に整流方向を有するダイオードと、前記ダイオードと並列に接続されるキャパシタとで構成される、請求項1又は2記載のスイッチング素子の駆動回路。

【請求項4】

前記スイッチング素子をオンにする際に、前記第1スイッチ及び前記第3スイッチをともにオンにするとともに、前記第2スイッチ及び前記第4スイッチをともにオフにする、請求項1乃至3のいずれか一項記載のスイッチング素子の駆動回路。

【請求項5】

前記スイッチング素子をオンにする際に、前記第1スイッチ及び前記第3スイッチをともにオンにするとともに、前記第2スイッチ及び前記第4スイッチをともにオフにする前に、

前記第1スイッチをオフにするとともに前記第2スイッチをオンにした状態で、前記第3スイッチをオフにするとともに前記第4スイッチをオンにする準備期間を有する、請求項4に記載のスイッチング素子の駆動回路。

【請求項1】

電源と、

前記電源の正極性端子とスイッチング素子の制御端子との間に挿入される第1スイッチと、

前記電源の負極性端子と前記スイッチング素子の制御端子との間に挿入される第2スイッチと、

前記スイッチング素子の電流出力端子に一端が接続される第3スイッチと、

前記スイッチング素子の前記電流出力端子に一端が接続される第4スイッチと、

前記第3スイッチの他端に高電位側の端子が接続され、前記第4スイッチの他端に低電位側の端子が接続される電圧出力部と

を含む、スイッチング素子の駆動回路。

【請求項2】

前記電圧出力部は、前記電源が出力する第1電圧よりも低い第2電圧を出力する、請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記電圧出力部は、前記低電位側の端子から前記高電位側の端子の方向に整流方向を有するダイオードと、前記ダイオードと並列に接続されるキャパシタとで構成される、請求項1又は2記載のスイッチング素子の駆動回路。

【請求項4】

前記スイッチング素子をオンにする際に、前記第1スイッチ及び前記第3スイッチをともにオンにするとともに、前記第2スイッチ及び前記第4スイッチをともにオフにする、請求項1乃至3のいずれか一項記載のスイッチング素子の駆動回路。

【請求項5】

前記スイッチング素子をオンにする際に、前記第1スイッチ及び前記第3スイッチをともにオンにするとともに、前記第2スイッチ及び前記第4スイッチをともにオフにする前に、

前記第1スイッチをオフにするとともに前記第2スイッチをオンにした状態で、前記第3スイッチをオフにするとともに前記第4スイッチをオンにする準備期間を有する、請求項4に記載のスイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−110924(P2013−110924A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−256108(P2011−256108)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]