スイッチング装置及びその制御方法

【課題】出力端子の数よりもコイルの数の少ないスイッチング装置を提供する。

【解決手段】メインスイッチング素子24のオンオフに伴って整流回路30に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路30から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路30を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。

【解決手段】メインスイッチング素子24のオンオフに伴って整流回路30に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路30から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路30を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング装置及びその制御方法に関する。

【背景技術】

【0002】

従来より、スイッチング装置として、入力した直流電源電圧を変圧して出力するDC−DCコンバータが知られている。例えば特許文献1には、スイッチング素子としてのトランジスタと、ダイオードやコイルを有する整流回路とを備え、電源電圧を降圧して出力するDC−DCコンバーターが記載されている。また、特許文献2には、スイッチング素子とコイルを有する整流回路とを並列に接続することで1つの直流電源入力から複数の電圧を出力するDC−DCコンバーターが記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平05−83939号公報

【特許文献2】特開2000−116127号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、電子機器の回路では、スイッチング装置により変圧された複数の電圧が必要となる場合があるが、このような場合に必要な電圧の数だけスイッチング装置を用意するとスイッチング装置を含む回路全体の大きさが大きくなってしまうという問題があった。特に、コイルについては半導体と異なり素子の小型化が進んでおらず、必要な電圧の数だけスイッチング装置を用意すると各スイッチング装置がそれぞれコイルを有するため、回路全体の小型化にとって問題となっていた。また、1つのスイッチング装置で1つの直流電源入力から複数の電圧を出力するものは上述した特許文献2に記載があるが、このスイッチング装置においても出力端子と同じ数だけコイルを有しており、やはり回路全体の小型化にとって問題があった。

【0005】

本発明は、上述した課題に鑑みなされたものであり、出力端子の数よりもコイルの数の少ないスイッチング装置及びその制御方法を提供することを主目的とする。

【課題を解決するための手段】

【0006】

本発明のスイッチング装置は、

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、

前記メインスイッチング素子に接続され、コイルを有する整流回路と、

一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、

一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、

を備えたものである。

【0007】

この本発明のスイッチング装置では、メインスイッチング素子のオンオフに伴って整流回路に電流が流れ、第1サブスイッチング素子及び第2サブスイッチング素子のうちオンである方に整流回路から電流が流れる。そして、第1サブスイッチング素子及び第2サブスイッチング素子のオンオフを制御して第1出力回路及び第2出力回路のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路を流れる電流に応じて直流電源を変圧した電圧が第1出力端子から出力され、第2出力回路を流れる電流に応じて直流電源を変圧した電圧が第2出力端子から出力される。したがって、1つの整流回路を共用することにより、出力端子の数よりもコイルの数の少ないスイッチング装置を提供することができる。この場合において、前記整流回路は、前記コイルが蓄えた電力を放出する際に流れる電流の向きが順方向となるように該コイルに接続されたダイオードを有する回路としてもよい。また、前記第1出力回路は、前記第1出力端子に出力される電圧を平滑化する第1コンデンサーを有する回路であり、前記第2出力回路は、前記第2出力端子に出力される電圧を平滑化する第2コンデンサーを有する回路であるものとしてもよい。こうすれば、出力端子から出力される電圧の値を安定化することができる。また、本発明のスイッチング装置は、一端が前記整流回路側に接続されると共に他端が第3出力端子側に接続され、該整流回路と該第3出力端子との間でスイッチングを行う第3サブスイッチング素子を有する第3出力回路をさらに備えるなど、3つ以上の出力端子に電圧を出力する装置としてもよい。

【0008】

本発明のスイッチング装置は、制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させる制御回路、を備えたものとしてもよい。こうすれば、スイッチング装置において出力端子の数よりもコイルの数を少なくするに際して、メインスイッチング素子,第1サブスイッチング素子及び第2サブスイッチング素子のオンオフを制御することで、第1出力端子及び第2出力端子から出力させる電圧を制御することができる。なお、前記制御回路は、前記第1出力端子から出力させる電圧と前記第2出力端子から出力させる電圧とが異なる電圧となるように前記メインスイッチング素子,前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御するものとしてもよい。

【0009】

本発明のスイッチング装置において、前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオフからオンへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路としてもよい。こうすれば、サブスイッチング素子をオフからオンへ切り替える際にスイッチングロスが生じるのを防止できる。

【0010】

本発明のスイッチング装置において、前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオンからオフへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路としてもよい。こうすれば、サブスイッチング素子をオンからオフへ切り替える際にスイッチングロスが生じるのを防止できる。

【0011】

本発明のスイッチング装置において、前記制御回路は、前記メインスイッチング素子がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、該切替期間が前記第1出力回路又は前記第2出力回路に対応し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のうち該切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、前記整流回路から前記切替期間に対応する出力回路に電流が流れるよう切り替える回路としてもよい。こうすれば、第1出力回路及び第2出力回路のいずれに整流回路から電流が流れるかの切り替えを簡易な処理で行うことができる。

【0012】

この場合において、前記制御回路は、前記切替期間における前記メインスイッチング素子のオンオフのデューティー比を制御することにより、該切替期間に対応する出力回路に流れる電流を調整して、該切替期間に対応する出力回路に接続された前記出力端子から出力される電圧を調整する回路としてもよい。こうすれば、メインスイッチング素子のオンオフのデューティー比を制御するという簡易な処理で出力端子から出力される電圧を調整することができる。また、前記制御回路は、前記第1出力回路に対応する前記切替期間の頻度を変更することにより該第1出力回路に流れる電流を調整して前記第1出力端子から出力される電圧を調整し、前記第2出力回路に対応する前記切替期間の頻度を変更することにより該第2出力回路に流れる電流を調整して前記第2出力端子から出力される電圧を調整する回路としてもよい。こうすれば、出力回路に対応する切替期間の頻度を変更するという簡易な処理で出力端子から出力される電圧を調整することができる。

【0013】

上述した出力端子から出力される電圧を調整する態様の本発明のスイッチング装置において、前記制御回路は、検出した前記第1出力端子の電圧が所定の第1電圧範囲に収まり、検出した前記第2出力端子の電圧が所定の第2電圧範囲に収まるように、該第1出力端子の電圧及び該第2出力端子の電圧を調整するフィードバック制御を行う回路としてもよい。こうすれば、出力端子の電圧をより適切に調整することができる。ここで、メインスイッチング素子のオンオフのデューティー比を制御することで出力端子の電圧を調整する場合には、例えば、前記検出した出力端子の電圧が所定の高電圧領域に含まれるときには前記メインスイッチング素子のオン時間とオフ時間との合計に対するオン時間の割合を小さくする、すなわちデューティー比を低くし、前記検出した出力端子の電圧が所定の低電圧領域に含まれる場合には、前記メインスイッチング素子のオン時間とオフ時間との合計に対するオン時間の割合を大きくする、すなわちデューティー比を高くすることで、該出力端子の電圧を前記所定の電圧範囲に収めるようフィードバック制御を行うものとしてもよい。また、出力回路に対応する前記切替期間の頻度を変更することで該出力端子の電圧を調整する場合には、例えば、前記検出した出力端子の電圧が所定の低電圧領域に含まれるときには該出力端子に接続された出力回路に対応する前記切替期間の頻度を高くし、前記検出した出力端子の電圧が所定の高電圧領域に含まれるときには該出力端子に接続された出力回路に対応する前記切替期間の頻度を低くすることで該出力端子の電圧を前記所定の電圧範囲に納めるようフィードバック制御を行うものとしてもよい。

【0014】

本発明のスイッチング装置において、前記メインスイッチング素子は、一端が前記直流電源側に接続されると共に他端が前記整流回路に接続された素子であり、前記整流回路は、一端が前記メインスイッチング素子に接続され他端が前記第1出力回路及び前記第2出力回路に接続されたコイルと、一端が該メインスイッチング素子及び該コイルに接続され他端が基準電位であり他端側から一端側へ向かう方向が順方向であるダイオードとを有する回路であり、前記第1出力端子及び前記第2出力端子は、前記直流電源を降圧した電圧を出力する端子であるものとしてもよい。こうすれば、本発明のスイッチング装置を、直流電源を降圧した電圧を出力端子から出力するステップダウンコンバーターとして機能させることができる。この場合において、前記メインスイッチング素子は、ベースが前記制御回路に接続されエミッタが前記直流電源側に接続されコレクタが前記整流回路側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路に接続されドレインが前記直流電源側に接続されソースが前記整流回路側に接続されたNチャネルMOSFETであるものとしてもよい。こうすれば、スイッチング素子としてトランジスタ又はMOSFETを利用することにより比較的小さな駆動電流でスイッチングを行うことができる。

【0015】

本発明のスイッチング装置において、前記整流回路は、一端が前記直流電源側に接続されると共に他端が前記ダイオード及び前記メインスイッチング素子に接続されたコイルと、一端が該コイル及び該メインスイッチング素子に接続されると共に他端が前記第1出力回路及び前記第2出力回路に接続され一端側から他端側へ向かう方向が順方向であるダイオードとを有する回路であり、前記メインスイッチング素子は、一端が前記コイル及び前記ダイオードに接続され他端が基準電位である素子であり、前記第1出力端子及び前記第2出力端子は、前記直流電源を昇圧した電圧を出力する端子であるものとしてもよい。こうすれば、本発明のスイッチング装置を、直流電源を昇圧した電圧を出力端子から出力するステップアップコンバーターとして機能させることができる。この場合において、前記メインスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが基準電位であるNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが基準電位であるNチャネルMOSFETであるものとしてもよい。こうすれば、スイッチング素子としてトランジスタ又はMOSFETを利用することにより比較的小さな駆動電流でスイッチングを行うことができる。なお、基準電位は、グランド電位としてもよい。

【0016】

本発明のスイッチング装置の制御方法は、

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、前記メインスイッチング素子に接続され、コイルを有する整流回路と、一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、を備えたスイッチング装置の制御方法であって、

制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させるステップ、

を含むものである。

【0017】

この本発明のスイッチング装置の制御方法によれば、上述した本発明のスイッチング装置と同様に1つの整流回路を共用することにより出力端子の数よりもコイルの数を少なくすることができる。そして、その際にメインスイッチング素子,第1サブスイッチング素子及び第2サブスイッチング素子のオンオフを制御することで、第1出力端子及び第2出力端子から出力させる電圧を制御することができる。なお、このスイッチング装置の制御方法において、上述したスイッチング装置の種々の態様を採用してもよいし、上述したスイッチング装置の各機能を実現するようなステップを追加してもよい。

【図面の簡単な説明】

【0018】

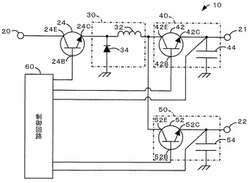

【図1】第1実施形態であるスイッチング装置10の構成の概略を示す構成図。

【図2】スイッチング装置10の動作の様子を示すタイムチャート。

【図3】第1サブスイッチング素子42がオンのときの様子を示す説明図。

【図4】第2サブスイッチング素子52がオンのときの様子を示す説明図。

【図5】第2実施形態であるスイッチング装置110の構成の概略を示す構成図。

【図6】スイッチング装置110の動作の様子を示すタイムチャート。

【図7】第1サブスイッチング素子42がオンのときの様子を示す説明図。

【図8】第2サブスイッチング素子52がオンのときの様子を示す説明図。

【図9】切替期間の頻度を変更する制御を行った様子を示すタイムチャート。

【発明を実施するための形態】

【0019】

[第1実施形態]

図1は、第1実施形態であるスイッチング装置10の構成の概略を示す構成図である。本実施形態のスイッチング装置10は、例えば複合機やプリンターなどの電子機器において直流電圧を入力してこれを変圧した電圧を出力するDC−DCコンバーターとして構成されており、入力端子20と、第1出力端子21と、第2出力端子22と、メインスイッチング素子24と、整流回路30と、第1出力回路40と、第2出力回路50と、制御回路60とを備えている。なお、スイッチング装置10は、直流電源を降圧した電圧を第1出力端子21及び第2出力端子22からそれぞれ出力するステップダウンコンバーターとして構成されている。

【0020】

入力端子20は、図示しない所定の電圧(例えば42V)の直流電源に接続されており、直流電源から電力が入力される端子である。なお、直流電源は、例えばグランド電位としての基準電位と入力端子20との間に所定の電圧を印加する。第1出力端子21は、直流電源を降圧した電圧V1(例えば5V)が出力される端子である。第2出力端子22は、直流電源を降圧した電圧V2(例えば3.3V)が出力される端子である。第1出力端子21は、例えばスキャナーのCISセンサーに用いるLEDを発光させる回路など、電圧V1で動作する回路に接続されている。第2出力端子22は、直流電源を降圧した電圧であり電圧V1とは異なる電圧V2が出力される端子である。第2出力端子22は、例えばCPUやメモリーなど、電圧V2で動作する回路に接続されている。

【0021】

メインスイッチング素子24は、入力端子20を介して直流電源から入力した電力をスイッチング可能な素子であり、一端が直流電源側に接続されると共に他端が整流回路30に接続されている。より具体的には、メインスイッチング素子24は、ベース24Bが制御回路60側に接続されエミッタ24Eが直流電源側に接続されコレクタ24Cが整流回路側に接続されたNPNトランジスタである。このメインスイッチング素子24は、制御回路60からベース24Bに電圧が印加されるとオンとなり、エミッタ24Eとコレクタ24Cとが導通して入力端子20からの電力が整流回路30に出力される。一方、制御回路60からベース24Bに電圧が印加されないとオフとなり、入力端子20からの電力は整流回路30に出力されない。

【0022】

整流回路30は、メインスイッチング素子24に接続された回路であり、コイル32と、ダイオード34とを備えている。コイル32は、一端がメインスイッチング素子24のコレクタ24Cに接続され他端が第1出力回路40及び第2出力回路50に接続されている。コイル32のリアクタンスLは、例えば数10μFであり、68μFとしてもよい。このコイル32は、メインスイッチング素子24やダイオード34などの半導体素子に比して素子のサイズが大きい。ダイオード34は、一端がメインスイッチング素子24のコレクタ24C及び該コイル32に接続され他端が基準電位であり、他端側から一端側へ向かう方向が順方向となっている。この整流回路30は、メインスイッチング素子24がオンのときにはメインスイッチング素子24を介して直流電源からコイル32に電流が流れ、整流回路30から第1出力回路40又は第1サブスイッチング素子42に電流が流れると共にコイル32が電力を蓄える。一方、メインスイッチング素子24がオフのときには、ダイオード34はコイル32が蓄えた電力を放出するときの電流の向きが順方向となるように接続されているため、コイル32の蓄えた電力が第1出力回路40又は第2出力回路50に放出される。

【0023】

第1出力回路40は、一端が整流回路30側に接続されると共に他端が第1出力端子21側に接続された回路であり、第1サブスイッチング素子42と、第1コンデンサー44とを備えている。第1サブスイッチング素子42は、ベース42Bが制御回路60側に接続されエミッタ42Eが整流回路30のコイル32の他端に接続されコレクタ42Cが第1出力端子21及び第1コンデンサー44に接続されたNPNトランジスタである。この第1サブスイッチング素子42は、整流回路30と第1出力端子21との間でスイッチングを行う。第1コンデンサー44は、一端が第1サブスイッチング素子42のコレクタ42C及び第1出力端子21に接続され、他端が基準電位に接続されており、第1出力端子21に出力される電圧を平滑化する。第1コンデンサー44の静電容量Cは、例えば数10μF〜数100μFであり、100μFや220μFとしてもよい。この第1出力回路40は、制御回路60からベース42Bに電圧が印加されると第1サブスイッチング素子42がオンとなり、エミッタ42Eとコレクタ42Cとが接続されて整流回路30からの電力が第1出力端子21に出力される。一方、制御回路60からベース42Bに電圧が印加されないとオフとなり、整流回路30からの電力は第1出力端子21に出力されない。

【0024】

第2出力回路50は、一端が整流回路30側に接続されると共に他端が第2出力端子22側に接続された回路であり、第2サブスイッチング素子52と、第2コンデンサー54とを備えている。第2サブスイッチング素子52は、ベース52Bが制御回路60側に接続されエミッタ52Eが整流回路30のコイル32の他端に接続されコレクタ52Cが第2出力端子22及び第2コンデンサー54に接続されたNPNトランジスタである。この第2サブスイッチング素子52は、整流回路30と第2出力端子22との間でスイッチングを行う。第2コンデンサー54は、一端が第2サブスイッチング素子52のコレクタ52C及び第2出力端子22に接続され、他端が基準電位に接続されており、第2出力端子22に出力される電圧を平滑化する。第2コンデンサー54の静電容量Cは、例えば数10μF〜数100μFであり、100μFや220μFとしてもよい。この第2出力回路50は、制御回路60からベース52Bに電圧が印加されると第2サブスイッチング素子52がオンとなり、エミッタ52Eとコレクタ52Cとが接続されて整流回路30からの電力が第2出力端子22に出力される。一方、制御回路60からベース52Bに電圧が印加されないとオフとなり、整流回路30からの電力は第2出力端子22に出力されない。

【0025】

制御回路60は、メインスイッチング素子24,第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを制御するASIC(Application Specific Integrated Circuit)として構成された回路である。この制御回路60は、メインスイッチング素子24のベース24B,第1サブスイッチング素子42のベース42B,及び第2サブスイッチング素子52のベース52Bに接続されてこれらに制御信号を出力する。また、制御回路60は、第1サブスイッチング素子42と第1コンデンサー44との接続点に接続されてこの接続点の電圧を第1出力端子21の電圧V1として検出し、第2サブスイッチング素子52と第2コンデンサー54との接続点に接続されてこの接続点の電圧を第2出力端子22の電圧V2として検出する。この制御回路60は、制御信号をメインスイッチング素子24に出力してメインスイッチング素子24にオンオフを繰り返させることで、メインスイッチング素子24のオンオフに伴って整流回路30に電流を流し、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力回路40及び第2出力回路50のいずれに整流回路30から電流が流れるかを切り替えて、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧を第1出力端子21から出力させ、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧を第2出力端子22から出力させる機能を有する。また、制御回路60は、検出した第1出力端子21の電圧V1が目標値としての第1電圧範囲(例えば5V±5%の範囲)に収まり、検出した第2出力端子22の電圧V2が目標値としての第2電圧範囲(例えば3.3V±5%の範囲)に収まるように、第1出力端子21の電圧V1及び第2出力端子22の電圧V2を調整するフィードバック制御を行う機能を有する。

【0026】

次に、こうして構成された本実施形態のスイッチング装置10の動作について説明する。図2は、スイッチング装置10の動作の様子を示すタイムチャートである。図3は、第1サブスイッチング素子42がオンのときの様子を示す説明図である。図3(a)は、メインスイッチング素子24がオン且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図3(b)は、メインスイッチング素子24がオフ且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図4は、第2サブスイッチング素子52がオンのときの様子を示す説明図である。図4(a)は、メインスイッチング素子24がオン且つ第2サブスイッチング素子52がオンのときの様子を示す説明図である。図4(b)は、メインスイッチング素子24がオフ且つ第2サブスイッチング素子52がオンのときの様子を示す説明図である。

【0027】

まず、制御回路60によるメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52の制御の概略について説明する。制御回路60は、ベース24Bに制御信号として所定の周波数f(例えば100kHz)のパルス信号を出力する。これにより、メインスイッチング素子24は図2に示すようにオンとオフとを繰り返す。また、制御回路60は、メインスイッチング素子24のオン時間Tonとオフ時間Toffとの和であるオン時間Ton+オフ時間Toffの長さを周期T(=1/f)で固定とし、メインスイッチング素子24のオン時間Tonを変更することで、オン時間Ton+オフ時間Toffに対するオン時間Tonの比であるデューティー比を変更するようになっている。なお、オン時間Ton+オフ時間Toffで表される期間、すなわちメインスイッチング素子24がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの期間を切替期間と称する。それぞれの切替期間は、第1出力回路40又は第2出力回路50のいずれかに対応している。本実施形態では、最初の切替期間(図2の時刻t2〜時刻t7)が第1出力回路40に対応し、2番目の切替期間(図2の時刻t7〜時刻t12)が第2出力回路50に対応し、以降この切替期間は第1出力回路40及び第2出力回路50に交互に対応する。そして、制御回路60は、第1サブスイッチング素子42及び第2サブスイッチング素子52のうち、切替期間に対応するサブスイッチング素子のみをオンとすることで、整流回路から切替期間に対応する出力回路に電流が流れるよう切り替えを行う。

【0028】

次に、図2の時系列に沿ってスイッチング装置10の動作の様子について具体的に説明する。まず、制御回路60は、第1出力回路40に対応している最初の切替期間では、第1出力回路40の第1サブスイッチング素子42をオンする。具体的には、メインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52がオフの状態から、時刻t1において第1出力回路40の第1サブスイッチング素子42をオンする。続いて時刻t2においてメインスイッチング素子24をオンする。これにより、時刻t2ではメインスイッチング素子24及び第1サブスイッチング素子42が共にオンで第2サブスイッチング素子52がオフの状態となり、図3(a)に示すように直流電源から入力端子20,メインスイッチング素子24,整流回路30,第1出力回路40,第1出力端子21の順に電流が流れる状態となる。そして、この電流に応じた電圧が第1出力端子21に出力されると共に、第1コンデンサー44にも電流が流れ込み電荷が蓄えられる。

【0029】

ここで、時刻t1は、メインスイッチング素子24をオンする時刻t2から時間T1(T1は正の値)だけ前の時刻である。この時間T1は、第1サブスイッチング素子42のオフからオンへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路30から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。例えば、時刻t2でメインスイッチング素子24がオンとなるため、時刻t2以降に第1サブスイッチング素子42をオンとすると、第1サブスイッチング素子42がオンとなった瞬間に整流回路30(コイル32)から電流が第1サブスイッチング素子42に流れ込む。これにより、第1サブスイッチング素子42においてスイッチングロスが生じる。そこで、時刻t2より時間T1だけ前の時刻に第1サブスイッチング素子42をオンすることで、このスイッチングロスが生じるのを防止しているのである。時間T1は、例えば第1サブスイッチング素子42のターンオン時間などを考慮して、時刻t2より前に第1サブスイッチング素子42がオンの状態となるように例えば実験により定めることができる。

【0030】

次に、制御回路60は、時刻t2からオン時間Tonが経過した時刻t3においてメインスイッチング素子24をオフとする。このため、時刻t2〜時刻t3の間は、メインスイッチング素子24及び第1サブスイッチング素子42がオンの状態となる。これにより、時刻t2〜時刻t3の間はコイル32を流れる電流は徐々に増加していく。また、コイル32を流れる電流に応じた電圧が第1出力端子21に出力されると共に、第1コンデンサー44にも電流が流れ込み電荷が蓄えられる。

【0031】

時刻t3において制御回路60がメインスイッチング素子24をオフすると、図3(b)に示すように、メインスイッチング素子24及び第2サブスイッチング素子52がオフ且つ第1サブスイッチング素子42がオンの状態となる。この状態では、メインスイッチング素子24がオフであるため入力端子20から整流回路30へは電流が流れ込まない。そして、コイル32は電流を流し続けようとして電気エネルギーを放出しようとするため、図3(b)に示すように基準電位からダイオード34,コイル32,第1出力回路40,第1出力端子21の順に電流が流れる。また、第1コンデンサー44からも電荷が放出されて第1出力端子21に電流が流れる。そして、これらの電流に応じた電圧が第1出力端子21に出力される。このとき、コイル32は電気エネルギーを放出するため、図2に示すように時刻t3からコイル32を流れる電流は徐々に減少していき、時刻t4でゼロとなる。そのため、時刻t4を過ぎると、図3(b)に示したコイル32を流れる電流はなくなり、第1出力端子21に流れるのは第1コンデンサー44からの電流のみとなる。なお、第1コンデンサー44からの電流も徐々に減少していくため、時刻t3から次にメインスイッチング素子24及び第1サブスイッチング素子42が共にオンとなる時刻t12までの期間では、第1出力端子21に流れる電流は徐々に減少していく。

【0032】

次に、制御回路60は、時刻t5において第1サブスイッチング素子42をオフする。ここで、時刻t5は、次にメインスイッチング素子24をオンする時刻t7から時間T2(T2は正の値)だけ前の時刻である。この時間T2は、第1サブスイッチング素子42のオンからオフへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路30から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。上述したように時刻t4以降はコイル32を流れる電流がないため、次にメインスイッチング素子24がオンとなるまでの時刻t4〜時刻t7の間は、第1サブスイッチング素子42がオンであっても整流回路30から第1サブスイッチング素子42には電流が流れ込まない。そこで、この時刻t4〜t7の期間中に第1サブスイッチング素子42をオフするように、時間T2が定められている。こうすることで、第1サブスイッチング素子42をオフする時のスイッチングロスが無くなる。時間T2は、例えば、時刻t3から時刻t4までの時間を予め実験により求めておき、時刻t5が時刻t4より後になるように定めることができる。また、時間T2は、第1サブスイッチング素子42のターンオフ時間などを考慮して、時刻t7より前に第1サブスイッチング素子42がオフの状態となるように定めることができる。

【0033】

次に、制御回路60は、第2出力回路50に対応している次の切替期間(時刻t7〜時刻t12)では、第2出力回路50の第2サブスイッチング素子52をオンする。具体的には、時刻t6において第2出力回路50の第2サブスイッチング素子52をオンし、時刻t3からオフ時間Toff経過後の時刻t7においてメインスイッチング素子24をオンする。これにより、時刻t7ではメインスイッチング素子24及び第2サブスイッチング素子52が共にオンで第1サブスイッチング素子42がオフの状態となり、図4(a)に示すように直流電源から入力端子20,メインスイッチング素子24,整流回路30,第2出力回路50,第2出力端子22の順に電流が流れる状態となる。そして、この電流に応じた電圧が第2出力端子22に出力されると共に、第2コンデンサー54にも電流が流れ込み電荷が蓄えられる。

【0034】

ここで、時刻t6は、メインスイッチング素子24をオンする時刻t7から時間T3(T3は正の値)だけ前の時刻である。この時間T3は、第2サブスイッチング素子52のオフからオンへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路30から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。これにより、時刻t1における第1サブスイッチング素子42のオンと同様に、第2サブスイッチング素子52をオンするときにスイッチングロスが生じるのを防止している。時間T3は、本実施形態では時間T1と同じ値とした。なお、時刻t5と時刻t6との順序が逆になることがないよう、すなわち、第1サブスイッチング素子42がオフしたあとで第2サブスイッチング素子52をオンするよう、時間T3は時間T2よりも小さい値に設定されている。

【0035】

続いて、制御回路60は、時刻t7からオン時間Tonが経過した時刻t8においてメインスイッチング素子24をオフとする。このため、時刻t7〜時刻t8の間は、メインスイッチング素子24及び第2サブスイッチング素子52がオンの状態となる。これにより、時刻t7〜時刻t8の間はコイル32を流れる電流は徐々に増加していく。また、コイル32を流れる電流に応じた電圧が第2出力端子22に出力されると共に、第2コンデンサー54にも電流が流れ込み電荷が蓄えられる。

【0036】

時刻t8において制御回路60がメインスイッチング素子24をオフすると、図4(b)に示すように、メインスイッチング素子24及び第1サブスイッチング素子42がオフ且つ第2サブスイッチング素子52がオンの状態となる。この状態では、メインスイッチング素子24がオフであるため入力端子20から整流回路30へは電流が流れ込まない。そして、コイル32は電流を流し続けようとして電気エネルギーを放出しようとするため、図4(b)に示すように基準電位からダイオード34,コイル32,第2出力回路50,第2出力端子22の順に電流が流れる。また、第2コンデンサー54からも電荷が放出されて第2出力端子22に電流が流れる。そして、これらの電流に応じた電圧が第2出力端子22に出力される。このとき、コイル32は電気エネルギーを放出するため、図2に示すように時刻t8からコイル32を流れる電流は徐々に減少していき、時刻t9でゼロとなる。そのため、時刻t9を過ぎると、図4(b)に示したコイル32を流れる電流はなくなり、第2出力端子22に流れるのは第2コンデンサー54からの電流のみとなる。なお、第2コンデンサー54からの電流も徐々に減少していくため、時刻t8から次にメインスイッチング素子24及び第2サブスイッチング素子52が共にオンとなる時刻t17までの期間では、第2出力端子22に流れる電流は徐々に減少していく。

【0037】

続いて、制御回路60は、時刻t10において第2サブスイッチング素子52をオフする。ここで、時刻t10は、次にメインスイッチング素子24をオンする時刻t12から時間T4(T4は正の値)だけ前の時刻である。この時間T4は、第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路30から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。上述したように時刻t9以降はコイル32を流れる電流がないため、次にメインスイッチング素子24がオンとなるまでの時刻t9〜時刻t12の間は、第2サブスイッチング素子52がオンであっても整流回路30から第2サブスイッチング素子52には電流が流れ込まない。そこで、この時刻t9〜t12の期間中に第2サブスイッチング素子52をオフするように、時間T4が定められている。こうすることで、第2サブスイッチング素子52をオフする時のスイッチングロスが無くなる。時間T4は、例えば、時刻t8から時刻t9までの時間を予め実験により求めておき、時刻t10が時刻t9より後になるように定めることができる。本実施形態では、時間T4は時間T2と同じ値とした。

【0038】

次に、制御回路60は、第1出力回路40に対応している次の切替期間(時刻t12〜時刻t17)では、第1出力回路40の第1サブスイッチング素子42をオンする。具体的には、時刻t11において第1出力回路40の第1サブスイッチング素子42をオンし、時刻t12においてメインスイッチング素子24をオンする。これにより、時刻t7では上述した時刻t2と同様の状態となる。なお、時刻t11は、時刻t1と同様、メインスイッチング素子24をオンする時刻t12から時間T1だけ前の時刻である。なお、時刻t10と時刻t11との順序が逆になることがないよう、すなわち、第2サブスイッチング素子52がオフしたあとで第1サブスイッチング素子42をオンするよう、時間T1は、時間T4よりも小さい値に設定されている。

【0039】

以降は、切替期間に対応するサブスイッチング素子に応じて、制御回路60は上述した処理と同様の処理を行う。例えば、時刻t12〜時刻t17までの切替期間は第1サブスイッチング素子42に対応しているため、制御回路60は時刻t11〜t17において時刻t1〜t7と同様にしてメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。また、時刻t17〜時刻t22までの切替期間は第2サブスイッチング素子52に対応しているため、制御回路60は時刻t16〜t22において時刻t6〜t12と同様にしてメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。

【0040】

ここで、電圧V1,V2の変動範囲について説明する。時刻t2〜時刻t3や時刻t12〜時刻t13の期間では第1出力端子21に流れる電流が徐々に増加するため、これに応じて電圧V1が上昇していく。時刻t3〜時刻t12や時刻t13〜時刻t22では第1出力端子21に流れる電流が徐々に減少するため、これに応じて電圧V1が下降していく。また、時刻t7〜時刻t8や時刻t17〜時刻t18の期間では第2出力端子22に流れる電流が徐々に増加するため、これに応じて電圧V2が上昇していく。時刻t8〜時刻t17や時刻t18から次にメインスイッチング素子24及び第2サブスイッチング素子52が共にオンとなる時刻までの期間では第2出力端子22に流れる電流が徐々に減少するため、これに応じて電圧V2が下降していく。このように、電圧V1,V2はそれぞれ上昇と下降とを繰り返す。制御回路60は、上述したデューティ比を調整するフィードバック制御を行うことで、このような上昇及び下降による電圧V1,V2の変動範囲がそれぞれ第1電圧範囲,第2電圧範囲に収まるようにしている。例えば、制御回路60は時刻t2より前の所定タイミングで第1出力端子21の電圧V1を検出し、検出した電圧V1が第1電圧範囲に収まるように、フィードバック制御により時刻t2から時刻t3までのメインスイッチング素子24のオン時間Tonの長さすなわちデューティ比を設定する。具体的には、検出した電圧V1が所定の高電圧領域に含まれるときにはオン時間Tonを短くしてデューティー比を低くし、検出した電圧V1が所定の低電圧領域に含まれる場合には、メインスイッチング素子24のオン時間Tonを長くしてデューティー比を高くする。ここで、所定の高電圧領域は、例えば第1電圧範囲のうち5V以上5V+5%以下の間で予め定められた閾値以上の領域としてもよい。また、所定の低電圧領域は、例えば第1電圧範囲のうち5V−5%以上5V以下の間で予め定められた閾値以下の領域としてもよい。電圧V2についても同様にフィードバック制御を行う。例えば、時刻t7より前の所定タイミングで第2出力端子22の電圧V2を検出し、検出した電圧V2が第2電圧範囲に収まるように、フィードバック制御により時刻t7から時刻t8までのオン時間Tonの長さすなわちデューティ比を設定する。

【0041】

このように、本実施形態のスイッチング装置10では、制御回路60がメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52を制御することで、第1出力端子21と第2出力端子22とに対して整流回路30のコイル32を共用としつつ、第1出力端子及び第2出力端子から出力させる電圧V1,V2をそれぞれ異なる値になるよう制御するのである。

【0042】

以上説明した本実施形態のスイッチング装置10によれば、メインスイッチング素子24のオンオフに伴って整流回路30に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路30から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路30を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。コイル32は、メインスイッチング素子24やダイオード34などの半導体素子に比して素子のサイズが大きいが、出力端子の数よりもコイルの数を少なくすることで、スイッチング装置10全体をより小型化することができる。

【0043】

また、スイッチング装置において出力端子の数よりもコイルの数を少なくするに際して、制御回路60がメインスイッチング素子24,第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力端子21及び第2出力端子22から出力させる電圧を制御することができる。

【0044】

さらに、制御回路60は、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオフからオンへの切り替えや、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路からサブスイッチング素子に流れ込まない所定の期間中に行う。このため、サブスイッチング素子を切り替える際にスイッチングロスが生じるのを防止できる。また、サブスイッチング素子を消費電力のより小さいものとすることができる。

【0045】

さらにまた、制御回路60は、メインスイッチング素子24がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、切替期間が第1出力回路40又は第2出力回路50に対応し、第1サブスイッチング素子42及び第2サブスイッチング素子44のうち切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、整流回路30から切替期間に対応する出力回路に電流が流れるよう切り替える。このため、第1出力回路40及び第2出力回路50のいずれに整流回路30から電流が流れるかの切り替えを簡易な処理で行うことができる。

【0046】

そしてまた、制御回路60は、切替期間におけるメインスイッチング素子24のオンオフのデューティー比を制御することにより、切替期間に対応する出力回路に流れる電流を調整して、切替期間に対応する出力回路に接続された出力端子から出力される電圧を調整する。このため、メインスイッチング素子24のオンオフのデューティー比を制御するという簡易な処理で第1出力端子21や第2出力端子22から出力される電圧V1,V2を調整することができる。

【0047】

そしてまた、制御回路60は、検出した第1出力端子21の電圧V1が所定の第1電圧範囲に収まり、検出した第2出力端子22の電圧V2が所定の第2電圧範囲に収まるように、メインスイッチング素子24のオンオフのデューティー比を制御して第1出力端子21の電圧V1及び第2出力端子の電圧V2を調整するフィードバック制御を行う。このため、第1出力端子21や第2出力端子22の電圧V1,V2をより適切に調整することができる。

【0048】

[第2実施形態]

図5は、第2実施形態であるスイッチング装置110の構成の概略を示す構成図である。なお、第2実施形態のスイッチング装置110のうち、スイッチング装置10と同様の構成要素については、スイッチング装置10の構成要素と同じ符号を付してその説明を省略する。

【0049】

本実施形態のスイッチング装置110は、入力端子20と、第1出力端子21と、第2出力端子22と、メインスイッチング素子124と、整流回路130と、第1出力回路40と、第2出力回路50と、制御回路60とを備えている。このスイッチング装置110は、直流電源を昇圧した電圧を第1出力端子21及び第2出力端子22からそれぞれ出力するステップアップコンバーターとして構成されている。

【0050】

入力端子20は、図示しない所定の電圧(例えば20V)の直流電源に接続されており、直流電源から電力が入力される端子である。第1出力端子21は、入力端子20に接続された直流電源を昇圧した電圧V3(例えば30V)が出力される端子である。第2出力端子22は、入力端子20に接続された直流電源を昇圧した電圧V4(例えば25V)が出力される端子である。

【0051】

メインスイッチング素子124は、入力端子20を介して直流電源から入力した電力をスイッチング可能な素子であり、一端が整流回路130のコイル132及びダイオード134に接続され他端が基準電位となっている。より具体的には、メインスイッチング素子124は、ベース124Bが制御回路60側に接続されエミッタ124Eが整流回路130のコイル132及びダイオード134に接続されコレクタ124Cが基準電位であるNPNトランジスタである。このメインスイッチング素子124は、制御回路60からベース124Bに電圧が印加されるとオンとなり、エミッタ124Eとコレクタ124Cとが導通して入力端子20及びコイル132を介して入力される電力が基準電位に出力される。一方、制御回路60からベース124Bに電圧が印加されないとオフとなり、入力端子20及びコイル132からの電力は基準電位にに出力されない。

【0052】

整流回路130は、入力端子20,メインスイッチング素子124,第1出力回路40及び第2出力回路50に接続された回路であり、コイル132と、ダイオード134とを備えている。コイル132は、一端が入力端子20に接続されると共に他端がダイオード134及びメインスイッチング素子のエミッタ124Eに接続されている。このコイル132は、メインスイッチング素子124やダイオード134などの半導体素子に比して素子のサイズが大きい。ダイオード134は、一端がコイル132及びメインスイッチング素子124のエミッタ124Eに接続されると共に他端が第1出力回路40及び第2出力回路50に接続され一端側から他端側へ向かう方向が順方向となっている。この整流回路130は、メインスイッチング素子124がオンのときには直流電源からコイル132を介してメインスイッチング素子124に電流が流れると共にコイル132が電力を蓄える。一方、メインスイッチング素子124がオフのときには、直流電源からコイル132及びダイオード134を介して第1出力回路40又は第2出力回路50に電流が流れる。また、ダイオード134はコイル132が蓄えた電力を放出するときの電流の向きが順方向となるように接続されているため、コイル132の蓄えた電力もダイオード134を介して第1出力回路40又は第2出力回路50に放出される。

【0053】

第1出力回路40は、第1サブスイッチング素子42と第1コンデンサー44とを備えている。第1サブスイッチング素子42は、エミッタ42Eが整流回路130のダイオード134に接続されている。

【0054】

第2出力回路50は、第2サブスイッチング素子52と第2コンデンサー54とを備えている。第2サブスイッチング素子52は、エミッタ52Eが整流回路130のダイオード134に接続されている。

【0055】

制御回路60は、メインスイッチング素子124,第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを制御するASIC(Application Specific Integrated Circuit)として構成された回路である。この制御回路60は、メインスイッチング素子124のベース124B,第1サブスイッチング素子42のベース42B,及び第2サブスイッチング素子52のベース52Bに接続されてこれらに制御信号を出力する。また、制御回路60は、第1サブスイッチング素子42と第1コンデンサー44との接続点に接続されてこの接続点の電圧を第1出力端子21の電圧V3として検出し、第2サブスイッチング素子52と第2コンデンサー54との接続点に接続されてこの接続点の電圧を第2出力端子22の電圧V4として検出する。この制御回路60は、制御信号をメインスイッチング素子124に出力してメインスイッチング素子124にオンオフを繰り返させることで、メインスイッチング素子124のオンオフに伴って整流回路130に電流を流し、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力回路40及び第2出力回路50のいずれに整流回路130から電流が流れるかを切り替えて、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧を第1出力端子21から出力させ、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧を第2出力端子22から出力させる機能を有する。また、制御回路60は、検出した第1出力端子21の電圧V3が目標値としての第3電圧範囲(例えば30V±5%の範囲)に収まり、検出した第2出力端子22の電圧V4が目標値としての第4電圧範囲(例えば25V±5%の範囲)に収まるように、第1出力端子21の電圧V3及び第2出力端子22の電圧V4を調整するフィードバック制御を行う機能を有する。

【0056】

次に、こうして構成された本実施形態のスイッチング装置110の動作について説明する。図6は、スイッチング装置110の動作の様子を示すタイムチャートである。図7は、第1サブスイッチング素子42がオンのときの様子を示す説明図である。図7(a)は、メインスイッチング素子124がオン且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図7(b)は、メインスイッチング素子124がオフ且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図8は、メインスイッチング素子124がオフ且つ第2サブスイッチング素子52がオンのときの様子を示す説明図である。なお、制御回路60は、第1実施形態と同様に、ベース124Bに所定の周波数f(例えば100kHz)のパルス信号を出力することでメインスイッチング素子124にオンとオフとを繰り返させる。また、メインスイッチング素子124がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの期間を切替期間として、最初の切替期間(図6の時刻t1〜時刻t4)が第1出力回路40に対応し、2番目の切替期間(図6の時刻t4〜時刻t8)が第2出力回路50に対応し、以降この切替期間が第1出力回路40及び第2出力回路50に交互に対応している。

【0057】

図6の時系列に沿ってスイッチング装置110の動作の様子について具体的に説明する。まず、制御回路60は、メインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52がオフの状態から、時刻t1においてメインスイッチング素子124をオンする。これにより、図7(a)に示すように直流電源から入力端子20,メインスイッチング素子124を通って基準電位に電流が流れ込む。このとき、コイル132は電気エネルギーを蓄えるため、図6に示すように時刻t1からコイル132を流れる電流は徐々に増加していく。

【0058】

次に、制御回路60は、第1出力回路40に対応している最初の切替期間では、時刻t2において第1出力回路40の第1サブスイッチング素子42をオンする。また、時刻t1からオン時間Tonが経過した時刻t3においてメインスイッチング素子124をオフとする。なお、制御回路60は、例えば時刻t2より前の所定タイミングで第1出力端子21の電圧V3を検出し、検出した電圧V3が第3電圧範囲に収まるように、フィードバック制御により時刻t1から時刻t3までのオン時間Tonの長さすなわちデューティ比を設定する。また、時刻t2は、メインスイッチング素子124をオフする時刻t3から時間T5(T5は正の値)だけ前の時刻である。この時間T5は、第1サブスイッチング素子42のオンからオフへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路130から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。メインスイッチング素子124がオンとなっている間は、エミッタ124Eが基準電位と導通するため、第1サブスイッチング素子42がオンであっても整流回路130から第1出力回路40には電流が流れない。そこで、メインスイッチング素子124がオフとなる時刻t3より時間T5だけ前の時刻に第1サブスイッチング素子42をオンすることで、第1サブスイッチング素子42でスイッチングロスが生じるのを防止しているのである。時間T5は、例えば第1サブスイッチング素子42のターンオン時間などを考慮して、時刻t3より前に第1サブスイッチング素子42がオンの状態となるように例えば実験により定めることができる。

【0059】

時刻t2で第1サブスイッチング素子42がオンとなり、時刻t3でメインスイッチング素子124がオフの状態となると、図7(b)に示すように直流電源から入力端子20,整流回路130,第1出力回路40,第1出力端子21の順に電流が流れる状態となる。また、時刻t1〜t3の間にコイル132が蓄えた電力もダイオード134を介して第1出力回路40に放出され、これによっても第1出力端子21に電流が流れる。そして、これらの電流の和に応じた電圧が第1出力端子21に出力される。また、第1コンデンサー44にも電流が流れ込み電荷が蓄えられる。そして、コイル132が電気エネルギーを放出するため、コイル132を流れる電流は、図6に示すように時刻t3から徐々に減少していく。

【0060】

次に、制御回路60は、時刻t3からオフ時間Toff経過後の時刻t4においてメインスイッチング素子124をオンし、時刻t5において第1サブスイッチング素子42をオフする。そして、第2出力回路50に対応している次の切替期間(時刻t4〜t8)で、時刻t6において第2出力回路50の第2サブスイッチング素子52をオンし、時刻t4からオン時間Tonが経過した時刻t7においてメインスイッチング素子124をオフとする。時刻t4においてメインスイッチング素子124がオンとなることで、時刻t4〜時刻t7の間は、スイッチング装置110は図7(a)に示した状態となり、整流回路130から第1出力回路40や第2出力回路50には電流が流れ込まない状態となる。この状態では、第1コンデンサー44から電荷が放出されて第1出力端子21に電流が流れ、この電流に応じた電圧が第1出力端子21に出力される。

【0061】

ここで、時刻t5は、メインスイッチング素子124をオフする時刻t7から時間T6(T6は正の値)だけ前の時刻である。また、時刻t6は、メインスイッチング素子124をオフする時刻t7から時間T7(T7は正の値)だけ前の時刻である。時間T6は、第1サブスイッチング素子42のオンからオフへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路130から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。時間T7は、第2サブスイッチング素子52のオフからオンへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路130から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。上述したようにメインスイッチング素子124がオンの間は図7(a)に示した状態となり、第1サブスイッチング素子42や第2サブスイッチング素子52がオンであっても電流が整流回路130から第1サブスイッチング素子42や第2サブスイッチング素子52に流れ込まない。そこで、メインスイッチング素子124がオンとなる時刻t4からオフとなる時刻t7までの間に第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを行うように時間T6,T7を定めることで、第1サブスイッチング素子42でスイッチングロスが生じるのを防止しているのである。なお、本実施形態では、第1出力端子21の第3電圧範囲と第2出力端子22の第4電圧範囲とが異なるため、図6に示すように時間T6>時間T7として、第1サブスイッチング素子42と第2サブスイッチング素子52とが同時にオンとなることがないようにしている。時間T6は、例えば第1サブスイッチング素子42のターンオフ時間などを考慮して、第1サブスイッチング素子42がオンの状態となるのが時刻t6より前のタイミングとなるように例えば実験により定めることができる。また、時間T7は時間T5と同じ値とした。

【0062】

時刻t6で第2サブスイッチング素子52がオンとなり、時刻t7でメインスイッチング素子124がオフの状態となると、図8に示すように直流電源から入力端子20,整流回路130,第2出力回路50,第2出力端子22の順に電流が流れる状態となる。また、時刻t4〜t7の間にコイル132が蓄えた電力もダイオード134を介して第2出力回路50に放出され、これによっても第2出力端子22に電流が流れる。そして、これらの電流の和に応じた電圧が第2出力端子22に出力される。また、第2コンデンサー54にも電流が流れ込み電荷が蓄えられる。そして、コイル132が電気エネルギーを放出するため、コイル132を流れる電流は、図6に示すように時刻t7から徐々に減少していく。

【0063】

続いて、制御回路60は、時刻t7からオフ時間Toff経過後の時刻t8においてメインスイッチング素子124をオンし、時刻t9において第2サブスイッチング素子52をオフする。ここで、時刻t9は、次にメインスイッチング素子124をオフする時刻t11から時間T8(T8は正の値)だけ前の時刻である。時間T8は、第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路130から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。メインスイッチング素子124がオンとなる時刻t8からオフとなる時刻t11までの間は図7(a)に示した状態となり、上述したように整流回路130から第2サブスイッチング素子52には電流が流れ込まない。そこで、この期間に第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを行うように時間T8を定めることで、第2サブスイッチング素子52でスイッチングロスが生じるのを防止しているのである。なお、本実施形態では、時間T6>時間T7としたのと同様の理由により、時間T8>時間T5としている。また、時間T7は時間T5と同じ値とした。

【0064】

以降は、切替期間に対応するサブスイッチング素子に応じて、制御回路60は上述した処理と同様の処理を行う。例えば、時刻t8〜時刻t12までの切替期間は第1サブスイッチング素子42に対応しているため、制御回路60は時刻t8〜t13において時刻t1〜時刻t5と同様にしてメインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。また、時刻t12〜時刻t16までの切替期間は第2サブスイッチング素子52に対応しているため、制御回路60は時刻t12〜t17において時刻t4〜t9と同様にしてメインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。

【0065】

ここで、電圧V3,V4の変動範囲について説明する。時刻t1〜時刻t3の期間では、第1出力端子21には電流が流れず、時刻t3以降は第1出力端子21に電流が流れるため、これに応じた電圧V3が生じる。また、時刻t3で電流が流れ始めるため、これに応じて電圧V3が上昇し、時刻t3〜時刻t4の期間でコイル132からの電気エネルギーが徐々に減少するため、これに応じて電圧V3が下降していく。時刻t4〜時刻t11の期間では、第1コンデンサー44から放出される電荷による電流が徐々に減少するため、これに応じて電圧V3がさらに下降していく。そして、時刻t11で再び直流電源及びコイル132からの電流が第1出力端子21に流れるため、これに応じて電圧V3が上昇し、時刻t11〜時刻t19は時刻t3〜時刻t11と同様に電圧V3が下降する。また、時刻t1〜時刻t7の期間では、第2出力端子22には電流が流れず、時刻t7以降は第2出力端子22に電流が流れるため、これに応じた電圧V4が生じる。また、時刻t7で電流が流れ始めるため、これに応じて電圧V4が上昇し、時刻t7〜時刻t8の期間でコイル132からの電気エネルギーが徐々に減少するため、これに応じて電圧V4が下降していく。時刻t8〜時刻t15の期間では、第2コンデンサー54から放出される電荷による電流が徐々に減少するため、これに応じて電圧V4がさらに下降していく。そして、時刻t15で再び直流電源及びコイル132からの電流が第2出力端子22に流れるため、これに応じて電圧V4が上昇し、時刻t15から次に第1出力回路40に対応する来切替期間においてメインスイッチング素子124がオフする時刻までは、時刻t7〜時刻t15と同様に電圧V4が下降する。このように、電圧V3,V4はそれぞれ上昇と下降とを繰り返す。制御回路60は、上述したデューティ比を調整するフィードバック制御を行うことで、このような上昇及び下降による電圧V3,V4の変動範囲がそれぞれ第3電圧範囲,第4電圧範囲に収まるようにしている。例えば、制御回路60は、時刻t1より前の所定タイミングで第1出力端子21の電圧V3を検出し、検出した電圧V3が第3電圧範囲に収まるように、フィードバック制御により時刻t1から時刻t3までのオン時間Tonの長さすなわちデューティ比を設定する。また、制御回路60は、時刻t4より前の所定タイミングで第2出力端子22の電圧V4を検出し、検出した電圧V4が第4電圧範囲に収まるように、フィードバック制御により時刻t4から時刻t7までのオン時間Tonの長さすなわちデューティ比を設定する。

【0066】

このように、本実施形態のスイッチング装置110では、制御回路60がメインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52を制御することで、第1出力端子21と第2出力端子22とに対して整流回路130のコイル132を共用としつつ、第1出力端子21及び第2出力端子22から出力させる電圧V3,V4をそれぞれ異なる値になるよう制御するのである。

【0067】

以上説明した本実施形態のスイッチング装置110によれば、メインスイッチング素子124のオンオフに伴って整流回路130に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路130から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路130を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。コイル132は、メインスイッチング素子124やダイオード134などの半導体素子に比して素子のサイズが大きいが、出力端子の数よりもコイルの数を少なくすることで、スイッチング装置110全体をより小型化することができる。

【0068】

また、スイッチング装置において出力端子の数よりもコイルの数を少なくするに際して、制御回路60がメインスイッチング素子124,第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力端子21及び第2出力端子22から出力させる電圧を制御することができる。

【0069】

さらに、制御回路60は、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオフからオンへの切り替えや、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路からサブスイッチング素子に流れ込まない所定の期間中に行う。このため、サブスイッチング素子を切り替える際にスイッチングロスが生じるのを防止できる。また、サブスイッチング素子を消費電力のより小さいものとすることができる。

【0070】

さらにまた、制御回路60は、メインスイッチング素子124がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、切替期間が第1出力回路40又は第2出力回路50に対応し、第1サブスイッチング素子42及び第2サブスイッチング素子44のうち切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、整流回路130から切替期間に対応する出力回路に電流が流れるよう切り替える。このため、第1出力回路40及び第2出力回路50のいずれに整流回路130から電流が流れるかの切り替えを簡易な処理で行うことができる。

【0071】

そしてまた、制御回路60は、切替期間におけるメインスイッチング素子124のオンオフのデューティー比を制御することにより、切替期間に対応する出力回路に流れる電流を調整して、切替期間に対応する出力回路に接続された出力端子から出力される電圧を調整する。このため、メインスイッチング素子124のオンオフのデューティー比を制御するという簡易な処理で第1出力端子21や第2出力端子22から出力される電圧V3,V4を調整することができる。

【0072】

そしてまた、制御回路60は、検出した第1出力端子21の電圧V3が所定の第3電圧範囲に収まり、検出した第2出力端子22の電圧V4が所定の第4電圧範囲に収まるように、メインスイッチング素子124のオンオフのデューティー比を制御して第1出力端子21の電圧V3及び第2出力端子の電圧V4を調整するフィードバック制御を行う。このため、第1出力端子21や第2出力端子22の電圧V3,V4をより適切に調整することができる。

【0073】

ここで、第1,第2実施形態の構成要素と本発明の構成要素との対応関係を明らかにする。本実施形態のメインスイッチング素子24,124が本発明のメインスイッチング素子に相当し、コイル32,132がコイルに相当し、整流回路30,130が整流回路に相当し、第1出力端子21が第1出力回路に相当し、第1出力回路40が第1出力回路に相当し、第1サブスイッチング素子が第1サブスイッチング素子に相当し、第2出力端子22が第2出力端子に相当し、第2出力回路50が第2出力回路に相当し、第2サブスイッチング素子52が第2サブスイッチング素子に相当する。なお、本実施形態では、スイッチング装置10,110の動作を説明することにより本発明のスイッチング装置の制御方法の一例も明らかにしている。

【0074】

なお、本発明は上述した実施形態に何ら限定されることはなく、本発明の技術的範囲に属する限り種々の態様で実施し得ることはいうまでもない。

【0075】

例えば、上述した実施形態では、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52はいずれもNPNトランジスタであるものとしたが、メインスイッチング素子は直流電源から入力した電力をスイッチング可能であればどのようなものであってもよく、第1サブスイッチング素子42は整流回路と第1出力端子21との間でスイッチングを行うものであればどのようなものであってもよく、第2サブスイッチング素子52は整流回路と第2出力端子22との間でスイッチングを行うものであればどのようなものであってもよい。例えば、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52いずれか1つ以上をPNPトランジスタとしてもよい。この場合、上述した実施形態におけるNPNトランジスタのエミッタに代えてPNPトランジスタのコレクタを接続し、コレクタに代えてエミッタを接続し、ベースはNPNトランジスタと同様に接続すればよい。また、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52のいずれか1つ以上をNチャネルMOS−FETとしてもよい。この場合、上述した実施形態におけるNPNトランジスタのベースに代えてNチャネルMOS−FETのゲートを接続し、エミッタに代えてソースを接続し,コレクタに代えてドレインを接続すればよい。また、また、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52のいずれか1つ以上をPチャネルMOS−FETとしてもよい。この場合、上述した実施形態におけるNPNトランジスタのベースに代えてPチャネルMOS−FETのゲートを接続し、エミッタに代えてドレインを接続し,コレクタに代えてゲートを接続すればよい。

【0076】

上述した実施形態では、整流回路30,130はそれぞれ図1,5に示す回路としたが、メインスイッチング素子に接続され、コイルを有する回路であれば、これに限られない。

【0077】

上述した実施形態では、第1出力回路40は図1,5に示す回路としたが、第1出力回路40は一端が整流回路側に接続されると共に他端が第1出力端子側に接続され、整流回路と第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有するものであればこれに限られない。同様に、第2出力回路50は図1,5に示す回路としたが、第2出力回路50は一端が整流回路側に接続されると共に他端が第2出力端子側に接続され、整流回路と第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有するものであればこれに限られない。

【0078】

上述した実施形態では、制御回路60はフィードバック制御を行うものとしたが、フィードバック制御を行わなくともよい。また、制御回路60はデューティ比を調整する制御を行うものとしたが、デューティ比は予め定められた固定値とするなど、デューティ比の調整を行わないものとしてもよい。

【0079】

上述した実施形態では、時間T1と時間T3,時間T2と時間T4,時間T5と時間T7,時間T6と時間T8とはそれぞれ同じ値としたが、これに限らず異なる値としてもよい。また、時間T1〜T8の少なくともいずれかを値0とするなど、切替対象のサブスイッチング素子がオンであると電流が整流回路からそのサブスイッチング素子に流れ込む期間中に、サブスイッチング素子の切替を行うものとしてもよい。また、時間T1〜T8はそれぞれ可変の値としてもよい。例えば第1出力端子21の電圧や第2出力端子22の電圧に応じて可変の値としてもよい。

【0080】

上述した実施形態では、スイッチング装置10,110は制御回路60を備えている物としたが、制御回路60を備えない構成としてもよい。この場合、例えば他の制御回路にスイッチング装置10,110を接続するものとしてもよい。

【0081】

上述した実施形態では、スイッチング装置10,110は2つの出力端子を有するものとしたが、3つ以上の出力端子を有していてもよい。例えば、第3出力端子を有する場合には、整流回路30,130は共用として、一端が整流回路30,130側に接続されると共に他端が第3出力端子側に接続された第1出力回路40と同様の構成の出力回路をさらに備えるものとすればよい。

【0082】

上述した実施形態では、切替期間は第1出力回路40及び第2出力回路50に交互に対応するものとしたが、これに限られない。例えば、2回連続で切替期間と第1出力回路40とが対応し、次の1回の切替期間が第2出力回路50に対応するものとするなど、切替え期間と第1出力回路40及び第2出力回路50との対応関係はどのようにしてもよい。また、制御回路60は、第1出力回路40に対応する切替期間の頻度を変更することにより第1出力回路40に流れる電流を調整して第1出力端子21から出力される電圧を調整し、第2出力回路50に対応する切替期間の頻度を変更することにより第2出力回路50流れる電流を調整して第2出力端子22から出力される電圧を調整するものとしてもよい。例えば、制御回路60は、電圧V1が所定の低電圧領域に含まれるときには、第1出力端子21に接続された第1出力回路40に対応する切替期間の頻度を高くし、電圧V1が所定の高電圧領域に含まれるときには、第1出力回路40に対応する切替期間の頻度を低くするものとしてもよい。図9は、上述したスイッチング装置10において、第1出力回路40の切替期間の頻度を高くする制御を行った場合のスイッチング装置10の動作の様子を示すタイムチャートである。図9において、時刻t1〜時刻t15までは図2と同じであり、切替期間は第1出力回路40及び第2出力回路50に交互に対応している。そして、制御回路60が、例えば時刻t12の前の所定のタイミングで検出した電圧V1が所定の低電圧領域に含まれると判定すると、第1出力回路40の切替期間の頻度を高くする。具体的には、次の切替期間(時刻t12〜時刻t17)及びその次の切替期間(時刻t17〜時刻t22)を連続で第1出力回路40に対応させ、その次の切替期間(時刻t22から始まる切替期間)を第2出力回路50に対応させる。これにより、時刻t17〜t22の切替期間が第2出力回路50ではなく第1出力回路40に割り当てられるため、図2とは異なり時刻t17より時間T1だけ前の時刻t16において第1サブスイッチング素子42をオンし、時刻t22より時間T2だけ前の時刻t20において第1サブスイッチング素子42をオフする。そして、時刻t22から始まる切替期間は第2出力回路50に対応するため、時刻t22より時間T3だけ前の時刻t21において第2サブスイッチング素子52をオンする。このようにすると、第1サブスイッチング素子42が2回の切替期間にわたって連続でオンするため、切替期間を第1出力回路40及び第2出力回路50に交互に対応させる場合と比較して第1出力端子21により多くの電流を流すことができ、第1出力端子21の電圧V1をより高い値にすることができる。このように、検出した出力端子の電圧が所定の低電圧領域に含まれるときにはその出力端子に接続された出力回路に対応する切替期間の頻度を高くするようフィードバック制御を行うことでも、出力端子の電圧を調整することができる。こうすれば、出力回路に対応する切替期間の頻度を変更するという簡易な処理で出力端子から出力される電圧を調整することができる。同様に、検出した出力端子の電圧が所定の高電圧領域に含まれるときにはその出力端子に接続された出力回路に対応する切替期間の頻度を低くすることで出力端子の電圧を所定の電圧範囲に納めるようフィードバック制御を行うものとしてもよい。なお、図9において第1サブスイッチング素子42を時刻t15でオフし時刻t16でオンしているが、これを省略して時刻t15〜時刻t17の間もオンのままとしてもよい。すなわち、切替期間が連続して同じ出力回路に対応するときにはその連続する切替期間の間におけるサブスイッチング素子のオンからオフへの切替とその切替に連続したオフからオンへの切替とを省略してもよい。また、デューティー比を調整するフィードバック制御と、切替期間の頻度を調整するフィードバック制御との両方を行って、出力端子の電圧を調整してもよい。例えば、通常はデューティー比の調整によって出力端子の電圧を調整し、デューティ比が所定の上限値(例えば50%)であってもなお出力端子の電圧が所定の低電圧領域に含まれるときに、その出力端子に接続された出力回路の切替期間の頻度を高くすることとしたり、デューティ比が所定の下限値(例えば10%)であってもなお出力端子の電圧が所定の高電圧領域に含まれるときに、その出力端子に接続された出力回路の切替期間の頻度を低くすることとしたりしてもよい。また、第1出力回路40に対応する切替期間の頻度を高くすると、その分第2出力回路50の切替期間の頻度が低くなり、第2出力端子21の電圧V2が低下する場合があるため、第1出力回路40の切替期間の頻度を高くするときには、第2出力回路50の切替期間におけるデューティー比をその分だけ高くして電圧V2の低下を抑制することとしてもよい。

【0083】

上述した実施形態では、切替期間は第1出力回路40及び第2出力回路50に交互に対応するものとしたが、第1出力回路40と第2出力回路50とのいずれにも対応しない切替期間があってもよい。その場合、第1出力回路40と第2出力回路50とのいずれにも対応しない切替期間では、第1サブスイッチング素子42と第2サブスイッチング素子52とをいずれもオフとすればよい。また、例えば第1出力端子21に接続された負荷が休止モードとなり電圧V1の出力が不要となった場合には、切替期間が第2出力回路50に1回おきに対応し、その間の切替期間は第1出力回路40と第2出力回路50とのいずれにも対応しないものとするなどとしてもよい。すなわち、電圧の出力が不要となった出力端子があるときには、その出力端子に接続された出力回路に対応していた切替期間をいずれの出力回路にも対応しないものとしてもよい。

【0084】

上述した実施形態では、スイッチング装置10,110は複合機やプリンターなどの電子機器において直流電圧を入力してこれを変圧した電圧を出力するDC−DCコンバーターとして構成されているものとしたが、複合機やプリンターに限らずどのような機器におけるDC−DCコンバーターとしてもよい。

【符号の説明】

【0085】

10,110 スイッチング装置、20 入力端子、21 第1出力端子、22 第2出力端子、24,124 メインスイッチング素子、24B,124B ベース、24C,124C コレクタ、24E,124E エミッタ24E、30,130 整流回路、32,132 コイル、34,134 ダイオード、40 第1出力回路、42 第1サブスイッチング素子、42B ベース、42C コレクタ、42E エミッタ、44 第1コンデンサー、50 第2出力回路、52 第2サブスイッチング素子、52B ベース、52C コレクタ、52E エミッタ、54 第2コンデンサー、60 制御回路。

【技術分野】

【0001】

本発明は、スイッチング装置及びその制御方法に関する。

【背景技術】

【0002】

従来より、スイッチング装置として、入力した直流電源電圧を変圧して出力するDC−DCコンバータが知られている。例えば特許文献1には、スイッチング素子としてのトランジスタと、ダイオードやコイルを有する整流回路とを備え、電源電圧を降圧して出力するDC−DCコンバーターが記載されている。また、特許文献2には、スイッチング素子とコイルを有する整流回路とを並列に接続することで1つの直流電源入力から複数の電圧を出力するDC−DCコンバーターが記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平05−83939号公報

【特許文献2】特開2000−116127号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、電子機器の回路では、スイッチング装置により変圧された複数の電圧が必要となる場合があるが、このような場合に必要な電圧の数だけスイッチング装置を用意するとスイッチング装置を含む回路全体の大きさが大きくなってしまうという問題があった。特に、コイルについては半導体と異なり素子の小型化が進んでおらず、必要な電圧の数だけスイッチング装置を用意すると各スイッチング装置がそれぞれコイルを有するため、回路全体の小型化にとって問題となっていた。また、1つのスイッチング装置で1つの直流電源入力から複数の電圧を出力するものは上述した特許文献2に記載があるが、このスイッチング装置においても出力端子と同じ数だけコイルを有しており、やはり回路全体の小型化にとって問題があった。

【0005】

本発明は、上述した課題に鑑みなされたものであり、出力端子の数よりもコイルの数の少ないスイッチング装置及びその制御方法を提供することを主目的とする。

【課題を解決するための手段】

【0006】

本発明のスイッチング装置は、

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、

前記メインスイッチング素子に接続され、コイルを有する整流回路と、

一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、

一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、

を備えたものである。

【0007】

この本発明のスイッチング装置では、メインスイッチング素子のオンオフに伴って整流回路に電流が流れ、第1サブスイッチング素子及び第2サブスイッチング素子のうちオンである方に整流回路から電流が流れる。そして、第1サブスイッチング素子及び第2サブスイッチング素子のオンオフを制御して第1出力回路及び第2出力回路のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路を流れる電流に応じて直流電源を変圧した電圧が第1出力端子から出力され、第2出力回路を流れる電流に応じて直流電源を変圧した電圧が第2出力端子から出力される。したがって、1つの整流回路を共用することにより、出力端子の数よりもコイルの数の少ないスイッチング装置を提供することができる。この場合において、前記整流回路は、前記コイルが蓄えた電力を放出する際に流れる電流の向きが順方向となるように該コイルに接続されたダイオードを有する回路としてもよい。また、前記第1出力回路は、前記第1出力端子に出力される電圧を平滑化する第1コンデンサーを有する回路であり、前記第2出力回路は、前記第2出力端子に出力される電圧を平滑化する第2コンデンサーを有する回路であるものとしてもよい。こうすれば、出力端子から出力される電圧の値を安定化することができる。また、本発明のスイッチング装置は、一端が前記整流回路側に接続されると共に他端が第3出力端子側に接続され、該整流回路と該第3出力端子との間でスイッチングを行う第3サブスイッチング素子を有する第3出力回路をさらに備えるなど、3つ以上の出力端子に電圧を出力する装置としてもよい。

【0008】

本発明のスイッチング装置は、制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させる制御回路、を備えたものとしてもよい。こうすれば、スイッチング装置において出力端子の数よりもコイルの数を少なくするに際して、メインスイッチング素子,第1サブスイッチング素子及び第2サブスイッチング素子のオンオフを制御することで、第1出力端子及び第2出力端子から出力させる電圧を制御することができる。なお、前記制御回路は、前記第1出力端子から出力させる電圧と前記第2出力端子から出力させる電圧とが異なる電圧となるように前記メインスイッチング素子,前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御するものとしてもよい。

【0009】

本発明のスイッチング装置において、前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオフからオンへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路としてもよい。こうすれば、サブスイッチング素子をオフからオンへ切り替える際にスイッチングロスが生じるのを防止できる。

【0010】

本発明のスイッチング装置において、前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオンからオフへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路としてもよい。こうすれば、サブスイッチング素子をオンからオフへ切り替える際にスイッチングロスが生じるのを防止できる。

【0011】

本発明のスイッチング装置において、前記制御回路は、前記メインスイッチング素子がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、該切替期間が前記第1出力回路又は前記第2出力回路に対応し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のうち該切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、前記整流回路から前記切替期間に対応する出力回路に電流が流れるよう切り替える回路としてもよい。こうすれば、第1出力回路及び第2出力回路のいずれに整流回路から電流が流れるかの切り替えを簡易な処理で行うことができる。

【0012】

この場合において、前記制御回路は、前記切替期間における前記メインスイッチング素子のオンオフのデューティー比を制御することにより、該切替期間に対応する出力回路に流れる電流を調整して、該切替期間に対応する出力回路に接続された前記出力端子から出力される電圧を調整する回路としてもよい。こうすれば、メインスイッチング素子のオンオフのデューティー比を制御するという簡易な処理で出力端子から出力される電圧を調整することができる。また、前記制御回路は、前記第1出力回路に対応する前記切替期間の頻度を変更することにより該第1出力回路に流れる電流を調整して前記第1出力端子から出力される電圧を調整し、前記第2出力回路に対応する前記切替期間の頻度を変更することにより該第2出力回路に流れる電流を調整して前記第2出力端子から出力される電圧を調整する回路としてもよい。こうすれば、出力回路に対応する切替期間の頻度を変更するという簡易な処理で出力端子から出力される電圧を調整することができる。

【0013】

上述した出力端子から出力される電圧を調整する態様の本発明のスイッチング装置において、前記制御回路は、検出した前記第1出力端子の電圧が所定の第1電圧範囲に収まり、検出した前記第2出力端子の電圧が所定の第2電圧範囲に収まるように、該第1出力端子の電圧及び該第2出力端子の電圧を調整するフィードバック制御を行う回路としてもよい。こうすれば、出力端子の電圧をより適切に調整することができる。ここで、メインスイッチング素子のオンオフのデューティー比を制御することで出力端子の電圧を調整する場合には、例えば、前記検出した出力端子の電圧が所定の高電圧領域に含まれるときには前記メインスイッチング素子のオン時間とオフ時間との合計に対するオン時間の割合を小さくする、すなわちデューティー比を低くし、前記検出した出力端子の電圧が所定の低電圧領域に含まれる場合には、前記メインスイッチング素子のオン時間とオフ時間との合計に対するオン時間の割合を大きくする、すなわちデューティー比を高くすることで、該出力端子の電圧を前記所定の電圧範囲に収めるようフィードバック制御を行うものとしてもよい。また、出力回路に対応する前記切替期間の頻度を変更することで該出力端子の電圧を調整する場合には、例えば、前記検出した出力端子の電圧が所定の低電圧領域に含まれるときには該出力端子に接続された出力回路に対応する前記切替期間の頻度を高くし、前記検出した出力端子の電圧が所定の高電圧領域に含まれるときには該出力端子に接続された出力回路に対応する前記切替期間の頻度を低くすることで該出力端子の電圧を前記所定の電圧範囲に納めるようフィードバック制御を行うものとしてもよい。

【0014】

本発明のスイッチング装置において、前記メインスイッチング素子は、一端が前記直流電源側に接続されると共に他端が前記整流回路に接続された素子であり、前記整流回路は、一端が前記メインスイッチング素子に接続され他端が前記第1出力回路及び前記第2出力回路に接続されたコイルと、一端が該メインスイッチング素子及び該コイルに接続され他端が基準電位であり他端側から一端側へ向かう方向が順方向であるダイオードとを有する回路であり、前記第1出力端子及び前記第2出力端子は、前記直流電源を降圧した電圧を出力する端子であるものとしてもよい。こうすれば、本発明のスイッチング装置を、直流電源を降圧した電圧を出力端子から出力するステップダウンコンバーターとして機能させることができる。この場合において、前記メインスイッチング素子は、ベースが前記制御回路に接続されエミッタが前記直流電源側に接続されコレクタが前記整流回路側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路に接続されドレインが前記直流電源側に接続されソースが前記整流回路側に接続されたNチャネルMOSFETであるものとしてもよい。こうすれば、スイッチング素子としてトランジスタ又はMOSFETを利用することにより比較的小さな駆動電流でスイッチングを行うことができる。

【0015】

本発明のスイッチング装置において、前記整流回路は、一端が前記直流電源側に接続されると共に他端が前記ダイオード及び前記メインスイッチング素子に接続されたコイルと、一端が該コイル及び該メインスイッチング素子に接続されると共に他端が前記第1出力回路及び前記第2出力回路に接続され一端側から他端側へ向かう方向が順方向であるダイオードとを有する回路であり、前記メインスイッチング素子は、一端が前記コイル及び前記ダイオードに接続され他端が基準電位である素子であり、前記第1出力端子及び前記第2出力端子は、前記直流電源を昇圧した電圧を出力する端子であるものとしてもよい。こうすれば、本発明のスイッチング装置を、直流電源を昇圧した電圧を出力端子から出力するステップアップコンバーターとして機能させることができる。この場合において、前記メインスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが基準電位であるNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが基準電位であるNチャネルMOSFETであるものとしてもよい。こうすれば、スイッチング素子としてトランジスタ又はMOSFETを利用することにより比較的小さな駆動電流でスイッチングを行うことができる。なお、基準電位は、グランド電位としてもよい。

【0016】

本発明のスイッチング装置の制御方法は、

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、前記メインスイッチング素子に接続され、コイルを有する整流回路と、一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、を備えたスイッチング装置の制御方法であって、

制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させるステップ、

を含むものである。

【0017】

この本発明のスイッチング装置の制御方法によれば、上述した本発明のスイッチング装置と同様に1つの整流回路を共用することにより出力端子の数よりもコイルの数を少なくすることができる。そして、その際にメインスイッチング素子,第1サブスイッチング素子及び第2サブスイッチング素子のオンオフを制御することで、第1出力端子及び第2出力端子から出力させる電圧を制御することができる。なお、このスイッチング装置の制御方法において、上述したスイッチング装置の種々の態様を採用してもよいし、上述したスイッチング装置の各機能を実現するようなステップを追加してもよい。

【図面の簡単な説明】

【0018】

【図1】第1実施形態であるスイッチング装置10の構成の概略を示す構成図。

【図2】スイッチング装置10の動作の様子を示すタイムチャート。

【図3】第1サブスイッチング素子42がオンのときの様子を示す説明図。

【図4】第2サブスイッチング素子52がオンのときの様子を示す説明図。

【図5】第2実施形態であるスイッチング装置110の構成の概略を示す構成図。

【図6】スイッチング装置110の動作の様子を示すタイムチャート。

【図7】第1サブスイッチング素子42がオンのときの様子を示す説明図。

【図8】第2サブスイッチング素子52がオンのときの様子を示す説明図。

【図9】切替期間の頻度を変更する制御を行った様子を示すタイムチャート。

【発明を実施するための形態】

【0019】

[第1実施形態]

図1は、第1実施形態であるスイッチング装置10の構成の概略を示す構成図である。本実施形態のスイッチング装置10は、例えば複合機やプリンターなどの電子機器において直流電圧を入力してこれを変圧した電圧を出力するDC−DCコンバーターとして構成されており、入力端子20と、第1出力端子21と、第2出力端子22と、メインスイッチング素子24と、整流回路30と、第1出力回路40と、第2出力回路50と、制御回路60とを備えている。なお、スイッチング装置10は、直流電源を降圧した電圧を第1出力端子21及び第2出力端子22からそれぞれ出力するステップダウンコンバーターとして構成されている。

【0020】

入力端子20は、図示しない所定の電圧(例えば42V)の直流電源に接続されており、直流電源から電力が入力される端子である。なお、直流電源は、例えばグランド電位としての基準電位と入力端子20との間に所定の電圧を印加する。第1出力端子21は、直流電源を降圧した電圧V1(例えば5V)が出力される端子である。第2出力端子22は、直流電源を降圧した電圧V2(例えば3.3V)が出力される端子である。第1出力端子21は、例えばスキャナーのCISセンサーに用いるLEDを発光させる回路など、電圧V1で動作する回路に接続されている。第2出力端子22は、直流電源を降圧した電圧であり電圧V1とは異なる電圧V2が出力される端子である。第2出力端子22は、例えばCPUやメモリーなど、電圧V2で動作する回路に接続されている。

【0021】

メインスイッチング素子24は、入力端子20を介して直流電源から入力した電力をスイッチング可能な素子であり、一端が直流電源側に接続されると共に他端が整流回路30に接続されている。より具体的には、メインスイッチング素子24は、ベース24Bが制御回路60側に接続されエミッタ24Eが直流電源側に接続されコレクタ24Cが整流回路側に接続されたNPNトランジスタである。このメインスイッチング素子24は、制御回路60からベース24Bに電圧が印加されるとオンとなり、エミッタ24Eとコレクタ24Cとが導通して入力端子20からの電力が整流回路30に出力される。一方、制御回路60からベース24Bに電圧が印加されないとオフとなり、入力端子20からの電力は整流回路30に出力されない。

【0022】

整流回路30は、メインスイッチング素子24に接続された回路であり、コイル32と、ダイオード34とを備えている。コイル32は、一端がメインスイッチング素子24のコレクタ24Cに接続され他端が第1出力回路40及び第2出力回路50に接続されている。コイル32のリアクタンスLは、例えば数10μFであり、68μFとしてもよい。このコイル32は、メインスイッチング素子24やダイオード34などの半導体素子に比して素子のサイズが大きい。ダイオード34は、一端がメインスイッチング素子24のコレクタ24C及び該コイル32に接続され他端が基準電位であり、他端側から一端側へ向かう方向が順方向となっている。この整流回路30は、メインスイッチング素子24がオンのときにはメインスイッチング素子24を介して直流電源からコイル32に電流が流れ、整流回路30から第1出力回路40又は第1サブスイッチング素子42に電流が流れると共にコイル32が電力を蓄える。一方、メインスイッチング素子24がオフのときには、ダイオード34はコイル32が蓄えた電力を放出するときの電流の向きが順方向となるように接続されているため、コイル32の蓄えた電力が第1出力回路40又は第2出力回路50に放出される。

【0023】

第1出力回路40は、一端が整流回路30側に接続されると共に他端が第1出力端子21側に接続された回路であり、第1サブスイッチング素子42と、第1コンデンサー44とを備えている。第1サブスイッチング素子42は、ベース42Bが制御回路60側に接続されエミッタ42Eが整流回路30のコイル32の他端に接続されコレクタ42Cが第1出力端子21及び第1コンデンサー44に接続されたNPNトランジスタである。この第1サブスイッチング素子42は、整流回路30と第1出力端子21との間でスイッチングを行う。第1コンデンサー44は、一端が第1サブスイッチング素子42のコレクタ42C及び第1出力端子21に接続され、他端が基準電位に接続されており、第1出力端子21に出力される電圧を平滑化する。第1コンデンサー44の静電容量Cは、例えば数10μF〜数100μFであり、100μFや220μFとしてもよい。この第1出力回路40は、制御回路60からベース42Bに電圧が印加されると第1サブスイッチング素子42がオンとなり、エミッタ42Eとコレクタ42Cとが接続されて整流回路30からの電力が第1出力端子21に出力される。一方、制御回路60からベース42Bに電圧が印加されないとオフとなり、整流回路30からの電力は第1出力端子21に出力されない。

【0024】

第2出力回路50は、一端が整流回路30側に接続されると共に他端が第2出力端子22側に接続された回路であり、第2サブスイッチング素子52と、第2コンデンサー54とを備えている。第2サブスイッチング素子52は、ベース52Bが制御回路60側に接続されエミッタ52Eが整流回路30のコイル32の他端に接続されコレクタ52Cが第2出力端子22及び第2コンデンサー54に接続されたNPNトランジスタである。この第2サブスイッチング素子52は、整流回路30と第2出力端子22との間でスイッチングを行う。第2コンデンサー54は、一端が第2サブスイッチング素子52のコレクタ52C及び第2出力端子22に接続され、他端が基準電位に接続されており、第2出力端子22に出力される電圧を平滑化する。第2コンデンサー54の静電容量Cは、例えば数10μF〜数100μFであり、100μFや220μFとしてもよい。この第2出力回路50は、制御回路60からベース52Bに電圧が印加されると第2サブスイッチング素子52がオンとなり、エミッタ52Eとコレクタ52Cとが接続されて整流回路30からの電力が第2出力端子22に出力される。一方、制御回路60からベース52Bに電圧が印加されないとオフとなり、整流回路30からの電力は第2出力端子22に出力されない。

【0025】

制御回路60は、メインスイッチング素子24,第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを制御するASIC(Application Specific Integrated Circuit)として構成された回路である。この制御回路60は、メインスイッチング素子24のベース24B,第1サブスイッチング素子42のベース42B,及び第2サブスイッチング素子52のベース52Bに接続されてこれらに制御信号を出力する。また、制御回路60は、第1サブスイッチング素子42と第1コンデンサー44との接続点に接続されてこの接続点の電圧を第1出力端子21の電圧V1として検出し、第2サブスイッチング素子52と第2コンデンサー54との接続点に接続されてこの接続点の電圧を第2出力端子22の電圧V2として検出する。この制御回路60は、制御信号をメインスイッチング素子24に出力してメインスイッチング素子24にオンオフを繰り返させることで、メインスイッチング素子24のオンオフに伴って整流回路30に電流を流し、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力回路40及び第2出力回路50のいずれに整流回路30から電流が流れるかを切り替えて、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧を第1出力端子21から出力させ、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧を第2出力端子22から出力させる機能を有する。また、制御回路60は、検出した第1出力端子21の電圧V1が目標値としての第1電圧範囲(例えば5V±5%の範囲)に収まり、検出した第2出力端子22の電圧V2が目標値としての第2電圧範囲(例えば3.3V±5%の範囲)に収まるように、第1出力端子21の電圧V1及び第2出力端子22の電圧V2を調整するフィードバック制御を行う機能を有する。

【0026】

次に、こうして構成された本実施形態のスイッチング装置10の動作について説明する。図2は、スイッチング装置10の動作の様子を示すタイムチャートである。図3は、第1サブスイッチング素子42がオンのときの様子を示す説明図である。図3(a)は、メインスイッチング素子24がオン且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図3(b)は、メインスイッチング素子24がオフ且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図4は、第2サブスイッチング素子52がオンのときの様子を示す説明図である。図4(a)は、メインスイッチング素子24がオン且つ第2サブスイッチング素子52がオンのときの様子を示す説明図である。図4(b)は、メインスイッチング素子24がオフ且つ第2サブスイッチング素子52がオンのときの様子を示す説明図である。

【0027】

まず、制御回路60によるメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52の制御の概略について説明する。制御回路60は、ベース24Bに制御信号として所定の周波数f(例えば100kHz)のパルス信号を出力する。これにより、メインスイッチング素子24は図2に示すようにオンとオフとを繰り返す。また、制御回路60は、メインスイッチング素子24のオン時間Tonとオフ時間Toffとの和であるオン時間Ton+オフ時間Toffの長さを周期T(=1/f)で固定とし、メインスイッチング素子24のオン時間Tonを変更することで、オン時間Ton+オフ時間Toffに対するオン時間Tonの比であるデューティー比を変更するようになっている。なお、オン時間Ton+オフ時間Toffで表される期間、すなわちメインスイッチング素子24がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの期間を切替期間と称する。それぞれの切替期間は、第1出力回路40又は第2出力回路50のいずれかに対応している。本実施形態では、最初の切替期間(図2の時刻t2〜時刻t7)が第1出力回路40に対応し、2番目の切替期間(図2の時刻t7〜時刻t12)が第2出力回路50に対応し、以降この切替期間は第1出力回路40及び第2出力回路50に交互に対応する。そして、制御回路60は、第1サブスイッチング素子42及び第2サブスイッチング素子52のうち、切替期間に対応するサブスイッチング素子のみをオンとすることで、整流回路から切替期間に対応する出力回路に電流が流れるよう切り替えを行う。

【0028】

次に、図2の時系列に沿ってスイッチング装置10の動作の様子について具体的に説明する。まず、制御回路60は、第1出力回路40に対応している最初の切替期間では、第1出力回路40の第1サブスイッチング素子42をオンする。具体的には、メインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52がオフの状態から、時刻t1において第1出力回路40の第1サブスイッチング素子42をオンする。続いて時刻t2においてメインスイッチング素子24をオンする。これにより、時刻t2ではメインスイッチング素子24及び第1サブスイッチング素子42が共にオンで第2サブスイッチング素子52がオフの状態となり、図3(a)に示すように直流電源から入力端子20,メインスイッチング素子24,整流回路30,第1出力回路40,第1出力端子21の順に電流が流れる状態となる。そして、この電流に応じた電圧が第1出力端子21に出力されると共に、第1コンデンサー44にも電流が流れ込み電荷が蓄えられる。

【0029】

ここで、時刻t1は、メインスイッチング素子24をオンする時刻t2から時間T1(T1は正の値)だけ前の時刻である。この時間T1は、第1サブスイッチング素子42のオフからオンへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路30から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。例えば、時刻t2でメインスイッチング素子24がオンとなるため、時刻t2以降に第1サブスイッチング素子42をオンとすると、第1サブスイッチング素子42がオンとなった瞬間に整流回路30(コイル32)から電流が第1サブスイッチング素子42に流れ込む。これにより、第1サブスイッチング素子42においてスイッチングロスが生じる。そこで、時刻t2より時間T1だけ前の時刻に第1サブスイッチング素子42をオンすることで、このスイッチングロスが生じるのを防止しているのである。時間T1は、例えば第1サブスイッチング素子42のターンオン時間などを考慮して、時刻t2より前に第1サブスイッチング素子42がオンの状態となるように例えば実験により定めることができる。

【0030】

次に、制御回路60は、時刻t2からオン時間Tonが経過した時刻t3においてメインスイッチング素子24をオフとする。このため、時刻t2〜時刻t3の間は、メインスイッチング素子24及び第1サブスイッチング素子42がオンの状態となる。これにより、時刻t2〜時刻t3の間はコイル32を流れる電流は徐々に増加していく。また、コイル32を流れる電流に応じた電圧が第1出力端子21に出力されると共に、第1コンデンサー44にも電流が流れ込み電荷が蓄えられる。

【0031】

時刻t3において制御回路60がメインスイッチング素子24をオフすると、図3(b)に示すように、メインスイッチング素子24及び第2サブスイッチング素子52がオフ且つ第1サブスイッチング素子42がオンの状態となる。この状態では、メインスイッチング素子24がオフであるため入力端子20から整流回路30へは電流が流れ込まない。そして、コイル32は電流を流し続けようとして電気エネルギーを放出しようとするため、図3(b)に示すように基準電位からダイオード34,コイル32,第1出力回路40,第1出力端子21の順に電流が流れる。また、第1コンデンサー44からも電荷が放出されて第1出力端子21に電流が流れる。そして、これらの電流に応じた電圧が第1出力端子21に出力される。このとき、コイル32は電気エネルギーを放出するため、図2に示すように時刻t3からコイル32を流れる電流は徐々に減少していき、時刻t4でゼロとなる。そのため、時刻t4を過ぎると、図3(b)に示したコイル32を流れる電流はなくなり、第1出力端子21に流れるのは第1コンデンサー44からの電流のみとなる。なお、第1コンデンサー44からの電流も徐々に減少していくため、時刻t3から次にメインスイッチング素子24及び第1サブスイッチング素子42が共にオンとなる時刻t12までの期間では、第1出力端子21に流れる電流は徐々に減少していく。

【0032】

次に、制御回路60は、時刻t5において第1サブスイッチング素子42をオフする。ここで、時刻t5は、次にメインスイッチング素子24をオンする時刻t7から時間T2(T2は正の値)だけ前の時刻である。この時間T2は、第1サブスイッチング素子42のオンからオフへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路30から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。上述したように時刻t4以降はコイル32を流れる電流がないため、次にメインスイッチング素子24がオンとなるまでの時刻t4〜時刻t7の間は、第1サブスイッチング素子42がオンであっても整流回路30から第1サブスイッチング素子42には電流が流れ込まない。そこで、この時刻t4〜t7の期間中に第1サブスイッチング素子42をオフするように、時間T2が定められている。こうすることで、第1サブスイッチング素子42をオフする時のスイッチングロスが無くなる。時間T2は、例えば、時刻t3から時刻t4までの時間を予め実験により求めておき、時刻t5が時刻t4より後になるように定めることができる。また、時間T2は、第1サブスイッチング素子42のターンオフ時間などを考慮して、時刻t7より前に第1サブスイッチング素子42がオフの状態となるように定めることができる。

【0033】

次に、制御回路60は、第2出力回路50に対応している次の切替期間(時刻t7〜時刻t12)では、第2出力回路50の第2サブスイッチング素子52をオンする。具体的には、時刻t6において第2出力回路50の第2サブスイッチング素子52をオンし、時刻t3からオフ時間Toff経過後の時刻t7においてメインスイッチング素子24をオンする。これにより、時刻t7ではメインスイッチング素子24及び第2サブスイッチング素子52が共にオンで第1サブスイッチング素子42がオフの状態となり、図4(a)に示すように直流電源から入力端子20,メインスイッチング素子24,整流回路30,第2出力回路50,第2出力端子22の順に電流が流れる状態となる。そして、この電流に応じた電圧が第2出力端子22に出力されると共に、第2コンデンサー54にも電流が流れ込み電荷が蓄えられる。

【0034】

ここで、時刻t6は、メインスイッチング素子24をオンする時刻t7から時間T3(T3は正の値)だけ前の時刻である。この時間T3は、第2サブスイッチング素子52のオフからオンへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路30から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。これにより、時刻t1における第1サブスイッチング素子42のオンと同様に、第2サブスイッチング素子52をオンするときにスイッチングロスが生じるのを防止している。時間T3は、本実施形態では時間T1と同じ値とした。なお、時刻t5と時刻t6との順序が逆になることがないよう、すなわち、第1サブスイッチング素子42がオフしたあとで第2サブスイッチング素子52をオンするよう、時間T3は時間T2よりも小さい値に設定されている。

【0035】

続いて、制御回路60は、時刻t7からオン時間Tonが経過した時刻t8においてメインスイッチング素子24をオフとする。このため、時刻t7〜時刻t8の間は、メインスイッチング素子24及び第2サブスイッチング素子52がオンの状態となる。これにより、時刻t7〜時刻t8の間はコイル32を流れる電流は徐々に増加していく。また、コイル32を流れる電流に応じた電圧が第2出力端子22に出力されると共に、第2コンデンサー54にも電流が流れ込み電荷が蓄えられる。

【0036】

時刻t8において制御回路60がメインスイッチング素子24をオフすると、図4(b)に示すように、メインスイッチング素子24及び第1サブスイッチング素子42がオフ且つ第2サブスイッチング素子52がオンの状態となる。この状態では、メインスイッチング素子24がオフであるため入力端子20から整流回路30へは電流が流れ込まない。そして、コイル32は電流を流し続けようとして電気エネルギーを放出しようとするため、図4(b)に示すように基準電位からダイオード34,コイル32,第2出力回路50,第2出力端子22の順に電流が流れる。また、第2コンデンサー54からも電荷が放出されて第2出力端子22に電流が流れる。そして、これらの電流に応じた電圧が第2出力端子22に出力される。このとき、コイル32は電気エネルギーを放出するため、図2に示すように時刻t8からコイル32を流れる電流は徐々に減少していき、時刻t9でゼロとなる。そのため、時刻t9を過ぎると、図4(b)に示したコイル32を流れる電流はなくなり、第2出力端子22に流れるのは第2コンデンサー54からの電流のみとなる。なお、第2コンデンサー54からの電流も徐々に減少していくため、時刻t8から次にメインスイッチング素子24及び第2サブスイッチング素子52が共にオンとなる時刻t17までの期間では、第2出力端子22に流れる電流は徐々に減少していく。

【0037】

続いて、制御回路60は、時刻t10において第2サブスイッチング素子52をオフする。ここで、時刻t10は、次にメインスイッチング素子24をオンする時刻t12から時間T4(T4は正の値)だけ前の時刻である。この時間T4は、第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路30から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。上述したように時刻t9以降はコイル32を流れる電流がないため、次にメインスイッチング素子24がオンとなるまでの時刻t9〜時刻t12の間は、第2サブスイッチング素子52がオンであっても整流回路30から第2サブスイッチング素子52には電流が流れ込まない。そこで、この時刻t9〜t12の期間中に第2サブスイッチング素子52をオフするように、時間T4が定められている。こうすることで、第2サブスイッチング素子52をオフする時のスイッチングロスが無くなる。時間T4は、例えば、時刻t8から時刻t9までの時間を予め実験により求めておき、時刻t10が時刻t9より後になるように定めることができる。本実施形態では、時間T4は時間T2と同じ値とした。

【0038】

次に、制御回路60は、第1出力回路40に対応している次の切替期間(時刻t12〜時刻t17)では、第1出力回路40の第1サブスイッチング素子42をオンする。具体的には、時刻t11において第1出力回路40の第1サブスイッチング素子42をオンし、時刻t12においてメインスイッチング素子24をオンする。これにより、時刻t7では上述した時刻t2と同様の状態となる。なお、時刻t11は、時刻t1と同様、メインスイッチング素子24をオンする時刻t12から時間T1だけ前の時刻である。なお、時刻t10と時刻t11との順序が逆になることがないよう、すなわち、第2サブスイッチング素子52がオフしたあとで第1サブスイッチング素子42をオンするよう、時間T1は、時間T4よりも小さい値に設定されている。

【0039】

以降は、切替期間に対応するサブスイッチング素子に応じて、制御回路60は上述した処理と同様の処理を行う。例えば、時刻t12〜時刻t17までの切替期間は第1サブスイッチング素子42に対応しているため、制御回路60は時刻t11〜t17において時刻t1〜t7と同様にしてメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。また、時刻t17〜時刻t22までの切替期間は第2サブスイッチング素子52に対応しているため、制御回路60は時刻t16〜t22において時刻t6〜t12と同様にしてメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。

【0040】

ここで、電圧V1,V2の変動範囲について説明する。時刻t2〜時刻t3や時刻t12〜時刻t13の期間では第1出力端子21に流れる電流が徐々に増加するため、これに応じて電圧V1が上昇していく。時刻t3〜時刻t12や時刻t13〜時刻t22では第1出力端子21に流れる電流が徐々に減少するため、これに応じて電圧V1が下降していく。また、時刻t7〜時刻t8や時刻t17〜時刻t18の期間では第2出力端子22に流れる電流が徐々に増加するため、これに応じて電圧V2が上昇していく。時刻t8〜時刻t17や時刻t18から次にメインスイッチング素子24及び第2サブスイッチング素子52が共にオンとなる時刻までの期間では第2出力端子22に流れる電流が徐々に減少するため、これに応じて電圧V2が下降していく。このように、電圧V1,V2はそれぞれ上昇と下降とを繰り返す。制御回路60は、上述したデューティ比を調整するフィードバック制御を行うことで、このような上昇及び下降による電圧V1,V2の変動範囲がそれぞれ第1電圧範囲,第2電圧範囲に収まるようにしている。例えば、制御回路60は時刻t2より前の所定タイミングで第1出力端子21の電圧V1を検出し、検出した電圧V1が第1電圧範囲に収まるように、フィードバック制御により時刻t2から時刻t3までのメインスイッチング素子24のオン時間Tonの長さすなわちデューティ比を設定する。具体的には、検出した電圧V1が所定の高電圧領域に含まれるときにはオン時間Tonを短くしてデューティー比を低くし、検出した電圧V1が所定の低電圧領域に含まれる場合には、メインスイッチング素子24のオン時間Tonを長くしてデューティー比を高くする。ここで、所定の高電圧領域は、例えば第1電圧範囲のうち5V以上5V+5%以下の間で予め定められた閾値以上の領域としてもよい。また、所定の低電圧領域は、例えば第1電圧範囲のうち5V−5%以上5V以下の間で予め定められた閾値以下の領域としてもよい。電圧V2についても同様にフィードバック制御を行う。例えば、時刻t7より前の所定タイミングで第2出力端子22の電圧V2を検出し、検出した電圧V2が第2電圧範囲に収まるように、フィードバック制御により時刻t7から時刻t8までのオン時間Tonの長さすなわちデューティ比を設定する。

【0041】

このように、本実施形態のスイッチング装置10では、制御回路60がメインスイッチング素子24,第1サブスイッチング素子42,第2サブスイッチング素子52を制御することで、第1出力端子21と第2出力端子22とに対して整流回路30のコイル32を共用としつつ、第1出力端子及び第2出力端子から出力させる電圧V1,V2をそれぞれ異なる値になるよう制御するのである。

【0042】

以上説明した本実施形態のスイッチング装置10によれば、メインスイッチング素子24のオンオフに伴って整流回路30に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路30から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路30を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。コイル32は、メインスイッチング素子24やダイオード34などの半導体素子に比して素子のサイズが大きいが、出力端子の数よりもコイルの数を少なくすることで、スイッチング装置10全体をより小型化することができる。

【0043】

また、スイッチング装置において出力端子の数よりもコイルの数を少なくするに際して、制御回路60がメインスイッチング素子24,第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力端子21及び第2出力端子22から出力させる電圧を制御することができる。

【0044】

さらに、制御回路60は、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオフからオンへの切り替えや、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路からサブスイッチング素子に流れ込まない所定の期間中に行う。このため、サブスイッチング素子を切り替える際にスイッチングロスが生じるのを防止できる。また、サブスイッチング素子を消費電力のより小さいものとすることができる。

【0045】

さらにまた、制御回路60は、メインスイッチング素子24がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、切替期間が第1出力回路40又は第2出力回路50に対応し、第1サブスイッチング素子42及び第2サブスイッチング素子44のうち切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、整流回路30から切替期間に対応する出力回路に電流が流れるよう切り替える。このため、第1出力回路40及び第2出力回路50のいずれに整流回路30から電流が流れるかの切り替えを簡易な処理で行うことができる。

【0046】

そしてまた、制御回路60は、切替期間におけるメインスイッチング素子24のオンオフのデューティー比を制御することにより、切替期間に対応する出力回路に流れる電流を調整して、切替期間に対応する出力回路に接続された出力端子から出力される電圧を調整する。このため、メインスイッチング素子24のオンオフのデューティー比を制御するという簡易な処理で第1出力端子21や第2出力端子22から出力される電圧V1,V2を調整することができる。

【0047】

そしてまた、制御回路60は、検出した第1出力端子21の電圧V1が所定の第1電圧範囲に収まり、検出した第2出力端子22の電圧V2が所定の第2電圧範囲に収まるように、メインスイッチング素子24のオンオフのデューティー比を制御して第1出力端子21の電圧V1及び第2出力端子の電圧V2を調整するフィードバック制御を行う。このため、第1出力端子21や第2出力端子22の電圧V1,V2をより適切に調整することができる。

【0048】

[第2実施形態]

図5は、第2実施形態であるスイッチング装置110の構成の概略を示す構成図である。なお、第2実施形態のスイッチング装置110のうち、スイッチング装置10と同様の構成要素については、スイッチング装置10の構成要素と同じ符号を付してその説明を省略する。

【0049】

本実施形態のスイッチング装置110は、入力端子20と、第1出力端子21と、第2出力端子22と、メインスイッチング素子124と、整流回路130と、第1出力回路40と、第2出力回路50と、制御回路60とを備えている。このスイッチング装置110は、直流電源を昇圧した電圧を第1出力端子21及び第2出力端子22からそれぞれ出力するステップアップコンバーターとして構成されている。

【0050】

入力端子20は、図示しない所定の電圧(例えば20V)の直流電源に接続されており、直流電源から電力が入力される端子である。第1出力端子21は、入力端子20に接続された直流電源を昇圧した電圧V3(例えば30V)が出力される端子である。第2出力端子22は、入力端子20に接続された直流電源を昇圧した電圧V4(例えば25V)が出力される端子である。

【0051】

メインスイッチング素子124は、入力端子20を介して直流電源から入力した電力をスイッチング可能な素子であり、一端が整流回路130のコイル132及びダイオード134に接続され他端が基準電位となっている。より具体的には、メインスイッチング素子124は、ベース124Bが制御回路60側に接続されエミッタ124Eが整流回路130のコイル132及びダイオード134に接続されコレクタ124Cが基準電位であるNPNトランジスタである。このメインスイッチング素子124は、制御回路60からベース124Bに電圧が印加されるとオンとなり、エミッタ124Eとコレクタ124Cとが導通して入力端子20及びコイル132を介して入力される電力が基準電位に出力される。一方、制御回路60からベース124Bに電圧が印加されないとオフとなり、入力端子20及びコイル132からの電力は基準電位にに出力されない。

【0052】

整流回路130は、入力端子20,メインスイッチング素子124,第1出力回路40及び第2出力回路50に接続された回路であり、コイル132と、ダイオード134とを備えている。コイル132は、一端が入力端子20に接続されると共に他端がダイオード134及びメインスイッチング素子のエミッタ124Eに接続されている。このコイル132は、メインスイッチング素子124やダイオード134などの半導体素子に比して素子のサイズが大きい。ダイオード134は、一端がコイル132及びメインスイッチング素子124のエミッタ124Eに接続されると共に他端が第1出力回路40及び第2出力回路50に接続され一端側から他端側へ向かう方向が順方向となっている。この整流回路130は、メインスイッチング素子124がオンのときには直流電源からコイル132を介してメインスイッチング素子124に電流が流れると共にコイル132が電力を蓄える。一方、メインスイッチング素子124がオフのときには、直流電源からコイル132及びダイオード134を介して第1出力回路40又は第2出力回路50に電流が流れる。また、ダイオード134はコイル132が蓄えた電力を放出するときの電流の向きが順方向となるように接続されているため、コイル132の蓄えた電力もダイオード134を介して第1出力回路40又は第2出力回路50に放出される。

【0053】

第1出力回路40は、第1サブスイッチング素子42と第1コンデンサー44とを備えている。第1サブスイッチング素子42は、エミッタ42Eが整流回路130のダイオード134に接続されている。

【0054】

第2出力回路50は、第2サブスイッチング素子52と第2コンデンサー54とを備えている。第2サブスイッチング素子52は、エミッタ52Eが整流回路130のダイオード134に接続されている。

【0055】

制御回路60は、メインスイッチング素子124,第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを制御するASIC(Application Specific Integrated Circuit)として構成された回路である。この制御回路60は、メインスイッチング素子124のベース124B,第1サブスイッチング素子42のベース42B,及び第2サブスイッチング素子52のベース52Bに接続されてこれらに制御信号を出力する。また、制御回路60は、第1サブスイッチング素子42と第1コンデンサー44との接続点に接続されてこの接続点の電圧を第1出力端子21の電圧V3として検出し、第2サブスイッチング素子52と第2コンデンサー54との接続点に接続されてこの接続点の電圧を第2出力端子22の電圧V4として検出する。この制御回路60は、制御信号をメインスイッチング素子124に出力してメインスイッチング素子124にオンオフを繰り返させることで、メインスイッチング素子124のオンオフに伴って整流回路130に電流を流し、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力回路40及び第2出力回路50のいずれに整流回路130から電流が流れるかを切り替えて、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧を第1出力端子21から出力させ、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧を第2出力端子22から出力させる機能を有する。また、制御回路60は、検出した第1出力端子21の電圧V3が目標値としての第3電圧範囲(例えば30V±5%の範囲)に収まり、検出した第2出力端子22の電圧V4が目標値としての第4電圧範囲(例えば25V±5%の範囲)に収まるように、第1出力端子21の電圧V3及び第2出力端子22の電圧V4を調整するフィードバック制御を行う機能を有する。

【0056】

次に、こうして構成された本実施形態のスイッチング装置110の動作について説明する。図6は、スイッチング装置110の動作の様子を示すタイムチャートである。図7は、第1サブスイッチング素子42がオンのときの様子を示す説明図である。図7(a)は、メインスイッチング素子124がオン且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図7(b)は、メインスイッチング素子124がオフ且つ第1サブスイッチング素子42がオンのときの様子を示す説明図である。図8は、メインスイッチング素子124がオフ且つ第2サブスイッチング素子52がオンのときの様子を示す説明図である。なお、制御回路60は、第1実施形態と同様に、ベース124Bに所定の周波数f(例えば100kHz)のパルス信号を出力することでメインスイッチング素子124にオンとオフとを繰り返させる。また、メインスイッチング素子124がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの期間を切替期間として、最初の切替期間(図6の時刻t1〜時刻t4)が第1出力回路40に対応し、2番目の切替期間(図6の時刻t4〜時刻t8)が第2出力回路50に対応し、以降この切替期間が第1出力回路40及び第2出力回路50に交互に対応している。

【0057】

図6の時系列に沿ってスイッチング装置110の動作の様子について具体的に説明する。まず、制御回路60は、メインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52がオフの状態から、時刻t1においてメインスイッチング素子124をオンする。これにより、図7(a)に示すように直流電源から入力端子20,メインスイッチング素子124を通って基準電位に電流が流れ込む。このとき、コイル132は電気エネルギーを蓄えるため、図6に示すように時刻t1からコイル132を流れる電流は徐々に増加していく。

【0058】

次に、制御回路60は、第1出力回路40に対応している最初の切替期間では、時刻t2において第1出力回路40の第1サブスイッチング素子42をオンする。また、時刻t1からオン時間Tonが経過した時刻t3においてメインスイッチング素子124をオフとする。なお、制御回路60は、例えば時刻t2より前の所定タイミングで第1出力端子21の電圧V3を検出し、検出した電圧V3が第3電圧範囲に収まるように、フィードバック制御により時刻t1から時刻t3までのオン時間Tonの長さすなわちデューティ比を設定する。また、時刻t2は、メインスイッチング素子124をオフする時刻t3から時間T5(T5は正の値)だけ前の時刻である。この時間T5は、第1サブスイッチング素子42のオンからオフへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路130から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。メインスイッチング素子124がオンとなっている間は、エミッタ124Eが基準電位と導通するため、第1サブスイッチング素子42がオンであっても整流回路130から第1出力回路40には電流が流れない。そこで、メインスイッチング素子124がオフとなる時刻t3より時間T5だけ前の時刻に第1サブスイッチング素子42をオンすることで、第1サブスイッチング素子42でスイッチングロスが生じるのを防止しているのである。時間T5は、例えば第1サブスイッチング素子42のターンオン時間などを考慮して、時刻t3より前に第1サブスイッチング素子42がオンの状態となるように例えば実験により定めることができる。

【0059】

時刻t2で第1サブスイッチング素子42がオンとなり、時刻t3でメインスイッチング素子124がオフの状態となると、図7(b)に示すように直流電源から入力端子20,整流回路130,第1出力回路40,第1出力端子21の順に電流が流れる状態となる。また、時刻t1〜t3の間にコイル132が蓄えた電力もダイオード134を介して第1出力回路40に放出され、これによっても第1出力端子21に電流が流れる。そして、これらの電流の和に応じた電圧が第1出力端子21に出力される。また、第1コンデンサー44にも電流が流れ込み電荷が蓄えられる。そして、コイル132が電気エネルギーを放出するため、コイル132を流れる電流は、図6に示すように時刻t3から徐々に減少していく。

【0060】

次に、制御回路60は、時刻t3からオフ時間Toff経過後の時刻t4においてメインスイッチング素子124をオンし、時刻t5において第1サブスイッチング素子42をオフする。そして、第2出力回路50に対応している次の切替期間(時刻t4〜t8)で、時刻t6において第2出力回路50の第2サブスイッチング素子52をオンし、時刻t4からオン時間Tonが経過した時刻t7においてメインスイッチング素子124をオフとする。時刻t4においてメインスイッチング素子124がオンとなることで、時刻t4〜時刻t7の間は、スイッチング装置110は図7(a)に示した状態となり、整流回路130から第1出力回路40や第2出力回路50には電流が流れ込まない状態となる。この状態では、第1コンデンサー44から電荷が放出されて第1出力端子21に電流が流れ、この電流に応じた電圧が第1出力端子21に出力される。

【0061】

ここで、時刻t5は、メインスイッチング素子124をオフする時刻t7から時間T6(T6は正の値)だけ前の時刻である。また、時刻t6は、メインスイッチング素子124をオフする時刻t7から時間T7(T7は正の値)だけ前の時刻である。時間T6は、第1サブスイッチング素子42のオンからオフへの切り替えを、切り替え対象である第1サブスイッチング素子42がオンであっても電流が整流回路130から第1サブスイッチング素子42に流れ込まない期間中に行うことができるように、予め定められた値である。時間T7は、第2サブスイッチング素子52のオフからオンへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路130から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。上述したようにメインスイッチング素子124がオンの間は図7(a)に示した状態となり、第1サブスイッチング素子42や第2サブスイッチング素子52がオンであっても電流が整流回路130から第1サブスイッチング素子42や第2サブスイッチング素子52に流れ込まない。そこで、メインスイッチング素子124がオンとなる時刻t4からオフとなる時刻t7までの間に第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを行うように時間T6,T7を定めることで、第1サブスイッチング素子42でスイッチングロスが生じるのを防止しているのである。なお、本実施形態では、第1出力端子21の第3電圧範囲と第2出力端子22の第4電圧範囲とが異なるため、図6に示すように時間T6>時間T7として、第1サブスイッチング素子42と第2サブスイッチング素子52とが同時にオンとなることがないようにしている。時間T6は、例えば第1サブスイッチング素子42のターンオフ時間などを考慮して、第1サブスイッチング素子42がオンの状態となるのが時刻t6より前のタイミングとなるように例えば実験により定めることができる。また、時間T7は時間T5と同じ値とした。

【0062】

時刻t6で第2サブスイッチング素子52がオンとなり、時刻t7でメインスイッチング素子124がオフの状態となると、図8に示すように直流電源から入力端子20,整流回路130,第2出力回路50,第2出力端子22の順に電流が流れる状態となる。また、時刻t4〜t7の間にコイル132が蓄えた電力もダイオード134を介して第2出力回路50に放出され、これによっても第2出力端子22に電流が流れる。そして、これらの電流の和に応じた電圧が第2出力端子22に出力される。また、第2コンデンサー54にも電流が流れ込み電荷が蓄えられる。そして、コイル132が電気エネルギーを放出するため、コイル132を流れる電流は、図6に示すように時刻t7から徐々に減少していく。

【0063】

続いて、制御回路60は、時刻t7からオフ時間Toff経過後の時刻t8においてメインスイッチング素子124をオンし、時刻t9において第2サブスイッチング素子52をオフする。ここで、時刻t9は、次にメインスイッチング素子124をオフする時刻t11から時間T8(T8は正の値)だけ前の時刻である。時間T8は、第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象である第2サブスイッチング素子52がオンであっても電流が整流回路130から第2サブスイッチング素子52に流れ込まない期間中に行うことができるように、予め定められた値である。メインスイッチング素子124がオンとなる時刻t8からオフとなる時刻t11までの間は図7(a)に示した状態となり、上述したように整流回路130から第2サブスイッチング素子52には電流が流れ込まない。そこで、この期間に第1サブスイッチング素子42及び第2サブスイッチング素子52のスイッチングを行うように時間T8を定めることで、第2サブスイッチング素子52でスイッチングロスが生じるのを防止しているのである。なお、本実施形態では、時間T6>時間T7としたのと同様の理由により、時間T8>時間T5としている。また、時間T7は時間T5と同じ値とした。

【0064】

以降は、切替期間に対応するサブスイッチング素子に応じて、制御回路60は上述した処理と同様の処理を行う。例えば、時刻t8〜時刻t12までの切替期間は第1サブスイッチング素子42に対応しているため、制御回路60は時刻t8〜t13において時刻t1〜時刻t5と同様にしてメインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。また、時刻t12〜時刻t16までの切替期間は第2サブスイッチング素子52に対応しているため、制御回路60は時刻t12〜t17において時刻t4〜t9と同様にしてメインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52のオンオフを制御する。

【0065】

ここで、電圧V3,V4の変動範囲について説明する。時刻t1〜時刻t3の期間では、第1出力端子21には電流が流れず、時刻t3以降は第1出力端子21に電流が流れるため、これに応じた電圧V3が生じる。また、時刻t3で電流が流れ始めるため、これに応じて電圧V3が上昇し、時刻t3〜時刻t4の期間でコイル132からの電気エネルギーが徐々に減少するため、これに応じて電圧V3が下降していく。時刻t4〜時刻t11の期間では、第1コンデンサー44から放出される電荷による電流が徐々に減少するため、これに応じて電圧V3がさらに下降していく。そして、時刻t11で再び直流電源及びコイル132からの電流が第1出力端子21に流れるため、これに応じて電圧V3が上昇し、時刻t11〜時刻t19は時刻t3〜時刻t11と同様に電圧V3が下降する。また、時刻t1〜時刻t7の期間では、第2出力端子22には電流が流れず、時刻t7以降は第2出力端子22に電流が流れるため、これに応じた電圧V4が生じる。また、時刻t7で電流が流れ始めるため、これに応じて電圧V4が上昇し、時刻t7〜時刻t8の期間でコイル132からの電気エネルギーが徐々に減少するため、これに応じて電圧V4が下降していく。時刻t8〜時刻t15の期間では、第2コンデンサー54から放出される電荷による電流が徐々に減少するため、これに応じて電圧V4がさらに下降していく。そして、時刻t15で再び直流電源及びコイル132からの電流が第2出力端子22に流れるため、これに応じて電圧V4が上昇し、時刻t15から次に第1出力回路40に対応する来切替期間においてメインスイッチング素子124がオフする時刻までは、時刻t7〜時刻t15と同様に電圧V4が下降する。このように、電圧V3,V4はそれぞれ上昇と下降とを繰り返す。制御回路60は、上述したデューティ比を調整するフィードバック制御を行うことで、このような上昇及び下降による電圧V3,V4の変動範囲がそれぞれ第3電圧範囲,第4電圧範囲に収まるようにしている。例えば、制御回路60は、時刻t1より前の所定タイミングで第1出力端子21の電圧V3を検出し、検出した電圧V3が第3電圧範囲に収まるように、フィードバック制御により時刻t1から時刻t3までのオン時間Tonの長さすなわちデューティ比を設定する。また、制御回路60は、時刻t4より前の所定タイミングで第2出力端子22の電圧V4を検出し、検出した電圧V4が第4電圧範囲に収まるように、フィードバック制御により時刻t4から時刻t7までのオン時間Tonの長さすなわちデューティ比を設定する。

【0066】

このように、本実施形態のスイッチング装置110では、制御回路60がメインスイッチング素子124,第1サブスイッチング素子42,第2サブスイッチング素子52を制御することで、第1出力端子21と第2出力端子22とに対して整流回路130のコイル132を共用としつつ、第1出力端子21及び第2出力端子22から出力させる電圧V3,V4をそれぞれ異なる値になるよう制御するのである。

【0067】

以上説明した本実施形態のスイッチング装置110によれば、メインスイッチング素子124のオンオフに伴って整流回路130に電流が流れ、第1サブスイッチング素子42及び第2サブスイッチング素子52のうちオンである方に整流回路130から電流が流れる。そして、第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御して第1出力回路40及び第2出力回路40のいずれに整流回路から電流が流れるかを切り替えることで、第1出力回路40を流れる電流に応じて直流電源を変圧した電圧が第1出力端子21から出力され、第2出力回路50を流れる電流に応じて直流電源を変圧した電圧が第2出力端子22から出力される。したがって、1つの整流回路130を共用することにより、出力端子の数よりもコイルの数を少なくすることができる。コイル132は、メインスイッチング素子124やダイオード134などの半導体素子に比して素子のサイズが大きいが、出力端子の数よりもコイルの数を少なくすることで、スイッチング装置110全体をより小型化することができる。

【0068】

また、スイッチング装置において出力端子の数よりもコイルの数を少なくするに際して、制御回路60がメインスイッチング素子124,第1サブスイッチング素子42及び第2サブスイッチング素子52のオンオフを制御することで、第1出力端子21及び第2出力端子22から出力させる電圧を制御することができる。

【0069】

さらに、制御回路60は、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオフからオンへの切り替えや、第1サブスイッチング素子42及び前記第2サブスイッチング素子52のオンからオフへの切り替えを、切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路からサブスイッチング素子に流れ込まない所定の期間中に行う。このため、サブスイッチング素子を切り替える際にスイッチングロスが生じるのを防止できる。また、サブスイッチング素子を消費電力のより小さいものとすることができる。

【0070】

さらにまた、制御回路60は、メインスイッチング素子124がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、切替期間が第1出力回路40又は第2出力回路50に対応し、第1サブスイッチング素子42及び第2サブスイッチング素子44のうち切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、整流回路130から切替期間に対応する出力回路に電流が流れるよう切り替える。このため、第1出力回路40及び第2出力回路50のいずれに整流回路130から電流が流れるかの切り替えを簡易な処理で行うことができる。

【0071】

そしてまた、制御回路60は、切替期間におけるメインスイッチング素子124のオンオフのデューティー比を制御することにより、切替期間に対応する出力回路に流れる電流を調整して、切替期間に対応する出力回路に接続された出力端子から出力される電圧を調整する。このため、メインスイッチング素子124のオンオフのデューティー比を制御するという簡易な処理で第1出力端子21や第2出力端子22から出力される電圧V3,V4を調整することができる。

【0072】

そしてまた、制御回路60は、検出した第1出力端子21の電圧V3が所定の第3電圧範囲に収まり、検出した第2出力端子22の電圧V4が所定の第4電圧範囲に収まるように、メインスイッチング素子124のオンオフのデューティー比を制御して第1出力端子21の電圧V3及び第2出力端子の電圧V4を調整するフィードバック制御を行う。このため、第1出力端子21や第2出力端子22の電圧V3,V4をより適切に調整することができる。

【0073】

ここで、第1,第2実施形態の構成要素と本発明の構成要素との対応関係を明らかにする。本実施形態のメインスイッチング素子24,124が本発明のメインスイッチング素子に相当し、コイル32,132がコイルに相当し、整流回路30,130が整流回路に相当し、第1出力端子21が第1出力回路に相当し、第1出力回路40が第1出力回路に相当し、第1サブスイッチング素子が第1サブスイッチング素子に相当し、第2出力端子22が第2出力端子に相当し、第2出力回路50が第2出力回路に相当し、第2サブスイッチング素子52が第2サブスイッチング素子に相当する。なお、本実施形態では、スイッチング装置10,110の動作を説明することにより本発明のスイッチング装置の制御方法の一例も明らかにしている。

【0074】

なお、本発明は上述した実施形態に何ら限定されることはなく、本発明の技術的範囲に属する限り種々の態様で実施し得ることはいうまでもない。

【0075】

例えば、上述した実施形態では、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52はいずれもNPNトランジスタであるものとしたが、メインスイッチング素子は直流電源から入力した電力をスイッチング可能であればどのようなものであってもよく、第1サブスイッチング素子42は整流回路と第1出力端子21との間でスイッチングを行うものであればどのようなものであってもよく、第2サブスイッチング素子52は整流回路と第2出力端子22との間でスイッチングを行うものであればどのようなものであってもよい。例えば、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52いずれか1つ以上をPNPトランジスタとしてもよい。この場合、上述した実施形態におけるNPNトランジスタのエミッタに代えてPNPトランジスタのコレクタを接続し、コレクタに代えてエミッタを接続し、ベースはNPNトランジスタと同様に接続すればよい。また、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52のいずれか1つ以上をNチャネルMOS−FETとしてもよい。この場合、上述した実施形態におけるNPNトランジスタのベースに代えてNチャネルMOS−FETのゲートを接続し、エミッタに代えてソースを接続し,コレクタに代えてドレインを接続すればよい。また、また、メインスイッチング素子24,124,第1サブスイッチング素子42,第2サブスイッチング素子52のいずれか1つ以上をPチャネルMOS−FETとしてもよい。この場合、上述した実施形態におけるNPNトランジスタのベースに代えてPチャネルMOS−FETのゲートを接続し、エミッタに代えてドレインを接続し,コレクタに代えてゲートを接続すればよい。

【0076】

上述した実施形態では、整流回路30,130はそれぞれ図1,5に示す回路としたが、メインスイッチング素子に接続され、コイルを有する回路であれば、これに限られない。

【0077】

上述した実施形態では、第1出力回路40は図1,5に示す回路としたが、第1出力回路40は一端が整流回路側に接続されると共に他端が第1出力端子側に接続され、整流回路と第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有するものであればこれに限られない。同様に、第2出力回路50は図1,5に示す回路としたが、第2出力回路50は一端が整流回路側に接続されると共に他端が第2出力端子側に接続され、整流回路と第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有するものであればこれに限られない。

【0078】

上述した実施形態では、制御回路60はフィードバック制御を行うものとしたが、フィードバック制御を行わなくともよい。また、制御回路60はデューティ比を調整する制御を行うものとしたが、デューティ比は予め定められた固定値とするなど、デューティ比の調整を行わないものとしてもよい。

【0079】

上述した実施形態では、時間T1と時間T3,時間T2と時間T4,時間T5と時間T7,時間T6と時間T8とはそれぞれ同じ値としたが、これに限らず異なる値としてもよい。また、時間T1〜T8の少なくともいずれかを値0とするなど、切替対象のサブスイッチング素子がオンであると電流が整流回路からそのサブスイッチング素子に流れ込む期間中に、サブスイッチング素子の切替を行うものとしてもよい。また、時間T1〜T8はそれぞれ可変の値としてもよい。例えば第1出力端子21の電圧や第2出力端子22の電圧に応じて可変の値としてもよい。

【0080】

上述した実施形態では、スイッチング装置10,110は制御回路60を備えている物としたが、制御回路60を備えない構成としてもよい。この場合、例えば他の制御回路にスイッチング装置10,110を接続するものとしてもよい。

【0081】

上述した実施形態では、スイッチング装置10,110は2つの出力端子を有するものとしたが、3つ以上の出力端子を有していてもよい。例えば、第3出力端子を有する場合には、整流回路30,130は共用として、一端が整流回路30,130側に接続されると共に他端が第3出力端子側に接続された第1出力回路40と同様の構成の出力回路をさらに備えるものとすればよい。

【0082】

上述した実施形態では、切替期間は第1出力回路40及び第2出力回路50に交互に対応するものとしたが、これに限られない。例えば、2回連続で切替期間と第1出力回路40とが対応し、次の1回の切替期間が第2出力回路50に対応するものとするなど、切替え期間と第1出力回路40及び第2出力回路50との対応関係はどのようにしてもよい。また、制御回路60は、第1出力回路40に対応する切替期間の頻度を変更することにより第1出力回路40に流れる電流を調整して第1出力端子21から出力される電圧を調整し、第2出力回路50に対応する切替期間の頻度を変更することにより第2出力回路50流れる電流を調整して第2出力端子22から出力される電圧を調整するものとしてもよい。例えば、制御回路60は、電圧V1が所定の低電圧領域に含まれるときには、第1出力端子21に接続された第1出力回路40に対応する切替期間の頻度を高くし、電圧V1が所定の高電圧領域に含まれるときには、第1出力回路40に対応する切替期間の頻度を低くするものとしてもよい。図9は、上述したスイッチング装置10において、第1出力回路40の切替期間の頻度を高くする制御を行った場合のスイッチング装置10の動作の様子を示すタイムチャートである。図9において、時刻t1〜時刻t15までは図2と同じであり、切替期間は第1出力回路40及び第2出力回路50に交互に対応している。そして、制御回路60が、例えば時刻t12の前の所定のタイミングで検出した電圧V1が所定の低電圧領域に含まれると判定すると、第1出力回路40の切替期間の頻度を高くする。具体的には、次の切替期間(時刻t12〜時刻t17)及びその次の切替期間(時刻t17〜時刻t22)を連続で第1出力回路40に対応させ、その次の切替期間(時刻t22から始まる切替期間)を第2出力回路50に対応させる。これにより、時刻t17〜t22の切替期間が第2出力回路50ではなく第1出力回路40に割り当てられるため、図2とは異なり時刻t17より時間T1だけ前の時刻t16において第1サブスイッチング素子42をオンし、時刻t22より時間T2だけ前の時刻t20において第1サブスイッチング素子42をオフする。そして、時刻t22から始まる切替期間は第2出力回路50に対応するため、時刻t22より時間T3だけ前の時刻t21において第2サブスイッチング素子52をオンする。このようにすると、第1サブスイッチング素子42が2回の切替期間にわたって連続でオンするため、切替期間を第1出力回路40及び第2出力回路50に交互に対応させる場合と比較して第1出力端子21により多くの電流を流すことができ、第1出力端子21の電圧V1をより高い値にすることができる。このように、検出した出力端子の電圧が所定の低電圧領域に含まれるときにはその出力端子に接続された出力回路に対応する切替期間の頻度を高くするようフィードバック制御を行うことでも、出力端子の電圧を調整することができる。こうすれば、出力回路に対応する切替期間の頻度を変更するという簡易な処理で出力端子から出力される電圧を調整することができる。同様に、検出した出力端子の電圧が所定の高電圧領域に含まれるときにはその出力端子に接続された出力回路に対応する切替期間の頻度を低くすることで出力端子の電圧を所定の電圧範囲に納めるようフィードバック制御を行うものとしてもよい。なお、図9において第1サブスイッチング素子42を時刻t15でオフし時刻t16でオンしているが、これを省略して時刻t15〜時刻t17の間もオンのままとしてもよい。すなわち、切替期間が連続して同じ出力回路に対応するときにはその連続する切替期間の間におけるサブスイッチング素子のオンからオフへの切替とその切替に連続したオフからオンへの切替とを省略してもよい。また、デューティー比を調整するフィードバック制御と、切替期間の頻度を調整するフィードバック制御との両方を行って、出力端子の電圧を調整してもよい。例えば、通常はデューティー比の調整によって出力端子の電圧を調整し、デューティ比が所定の上限値(例えば50%)であってもなお出力端子の電圧が所定の低電圧領域に含まれるときに、その出力端子に接続された出力回路の切替期間の頻度を高くすることとしたり、デューティ比が所定の下限値(例えば10%)であってもなお出力端子の電圧が所定の高電圧領域に含まれるときに、その出力端子に接続された出力回路の切替期間の頻度を低くすることとしたりしてもよい。また、第1出力回路40に対応する切替期間の頻度を高くすると、その分第2出力回路50の切替期間の頻度が低くなり、第2出力端子21の電圧V2が低下する場合があるため、第1出力回路40の切替期間の頻度を高くするときには、第2出力回路50の切替期間におけるデューティー比をその分だけ高くして電圧V2の低下を抑制することとしてもよい。

【0083】

上述した実施形態では、切替期間は第1出力回路40及び第2出力回路50に交互に対応するものとしたが、第1出力回路40と第2出力回路50とのいずれにも対応しない切替期間があってもよい。その場合、第1出力回路40と第2出力回路50とのいずれにも対応しない切替期間では、第1サブスイッチング素子42と第2サブスイッチング素子52とをいずれもオフとすればよい。また、例えば第1出力端子21に接続された負荷が休止モードとなり電圧V1の出力が不要となった場合には、切替期間が第2出力回路50に1回おきに対応し、その間の切替期間は第1出力回路40と第2出力回路50とのいずれにも対応しないものとするなどとしてもよい。すなわち、電圧の出力が不要となった出力端子があるときには、その出力端子に接続された出力回路に対応していた切替期間をいずれの出力回路にも対応しないものとしてもよい。

【0084】

上述した実施形態では、スイッチング装置10,110は複合機やプリンターなどの電子機器において直流電圧を入力してこれを変圧した電圧を出力するDC−DCコンバーターとして構成されているものとしたが、複合機やプリンターに限らずどのような機器におけるDC−DCコンバーターとしてもよい。

【符号の説明】

【0085】

10,110 スイッチング装置、20 入力端子、21 第1出力端子、22 第2出力端子、24,124 メインスイッチング素子、24B,124B ベース、24C,124C コレクタ、24E,124E エミッタ24E、30,130 整流回路、32,132 コイル、34,134 ダイオード、40 第1出力回路、42 第1サブスイッチング素子、42B ベース、42C コレクタ、42E エミッタ、44 第1コンデンサー、50 第2出力回路、52 第2サブスイッチング素子、52B ベース、52C コレクタ、52E エミッタ、54 第2コンデンサー、60 制御回路。

【特許請求の範囲】

【請求項1】

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、

前記メインスイッチング素子に接続され、コイルを有する整流回路と、

一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、

一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、

を備えたスイッチング装置。

【請求項2】

請求項1に記載のスイッチング装置であって、

制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させる制御回路、

を備えたスイッチング装置。

【請求項3】

前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオフからオンへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路である、

請求項2に記載のスイッチング装置。

【請求項4】

前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオンからオフへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路である、

請求項2又は3に記載のスイッチング装置。

【請求項5】

前記制御回路は、前記メインスイッチング素子がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、該切替期間が前記第1出力回路又は前記第2出力回路に対応し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のうち該切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、前記整流回路から前記切替期間に対応する出力回路に電流が流れるよう切り替える回路である、

請求項2〜4のいずれか1項に記載のスイッチング装置。

【請求項6】

前記制御回路は、前記切替期間における前記メインスイッチング素子のオンオフのデューティー比を制御することにより、該切替期間に対応する出力回路に流れる電流を調整して、該切替期間に対応する出力回路に接続された前記出力端子から出力される電圧を調整する回路である、

請求項5に記載のスイッチング装置。

【請求項7】

前記制御回路は、前記第1出力回路に対応する前記切替期間の頻度を変更することにより該第1出力回路に流れる電流を調整して前記第1出力端子から出力される電圧を調整し、前記第2出力回路に対応する前記切替期間の頻度を変更することにより該第2出力回路に流れる電流を調整して前記第2出力端子から出力される電圧を調整する回路である、

請求項5又は6に記載のスイッチング装置。

【請求項8】

前記制御回路は、検出した前記第1出力端子の電圧が所定の第1電圧範囲に収まり、検出した前記第2出力端子の電圧が所定の第2電圧範囲に収まるように、該第1出力端子の電圧及び該第2出力端子の電圧を調整するフィードバック制御を行う回路である、

請求項6又は7に記載のスイッチング装置。

【請求項9】

前記第1サブスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが前記第1出力端子側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが前記第1出力端子側に接続されたNチャネルMOSFETであり、

前記第2サブスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが前記第2出力端子側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが前記第2出力端子側に接続されたNチャネルMOSFETである、

請求項1〜8のいずれか1項に記載のスイッチング装置。

【請求項10】

前記メインスイッチング素子は、一端が前記直流電源側に接続されると共に他端が前記整流回路に接続された素子であり、

前記整流回路は、一端が前記メインスイッチング素子に接続され他端が前記第1出力回路及び前記第2出力回路に接続されたコイルと、一端が該メインスイッチング素子及び該コイルに接続され他端が基準電位であり他端側から一端側へ向かう方向が順方向であるダイオードとを有する回路であり、

前記第1出力端子及び前記第2出力端子は、前記直流電源を降圧した電圧を出力する端子である、

請求項1〜9のいずれか1項に記載のスイッチング装置。

【請求項11】

前記メインスイッチング素子は、ベースが前記制御回路に接続されエミッタが前記直流電源側に接続されコレクタが前記整流回路側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路に接続されドレインが前記直流電源側に接続されソースが前記整流回路側に接続されたNチャネルMOSFETである、

請求項10に記載のスイッチング装置。

【請求項12】

前記整流回路は、一端が前記直流電源側に接続されると共に他端が前記ダイオード及び前記メインスイッチング素子に接続されたコイルと、一端が該コイル及び該メインスイッチング素子に接続されると共に他端が前記第1出力回路及び前記第2出力回路に接続され一端側から他端側へ向かう方向が順方向であるダイオードとを有する回路であり、

前記メインスイッチング素子は、一端が前記コイル及び前記ダイオードに接続され他端が基準電位である素子であり、

前記第1出力端子及び前記第2出力端子は、前記直流電源を昇圧した電圧を出力する端子である、

請求項1〜9のいずれか1項に記載のスイッチング装置。

【請求項13】

前記メインスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが基準電位であるNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが基準電位であるNチャネルMOSFETである、

請求項12に記載のスイッチング装置。

【請求項14】

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、前記メインスイッチング素子に接続され、コイルを有する整流回路と、一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、を備えたスイッチング装置の制御方法であって、

制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させるステップ、

を含むスイッチング装置の制御方法。

【請求項1】

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、

前記メインスイッチング素子に接続され、コイルを有する整流回路と、

一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、

一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、

を備えたスイッチング装置。

【請求項2】

請求項1に記載のスイッチング装置であって、

制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させる制御回路、

を備えたスイッチング装置。

【請求項3】

前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオフからオンへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路である、

請求項2に記載のスイッチング装置。

【請求項4】

前記制御回路は、前記第1サブスイッチング素子又は前記第2サブスイッチング素子のオンからオフへの切り替えを、該切り替え対象のサブスイッチング素子がオンであっても電流が前記整流回路から該サブスイッチング素子に流れ込まない所定の期間中に行う回路である、

請求項2又は3に記載のスイッチング装置。

【請求項5】

前記制御回路は、前記メインスイッチング素子がオフからオンに切り替わるときから次にオフからオンに切り替わるときまでの切替期間毎に、該切替期間が前記第1出力回路又は前記第2出力回路に対応し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のうち該切替期間に対応する出力回路のサブスイッチング素子のみをオンとすることで、前記整流回路から前記切替期間に対応する出力回路に電流が流れるよう切り替える回路である、

請求項2〜4のいずれか1項に記載のスイッチング装置。

【請求項6】

前記制御回路は、前記切替期間における前記メインスイッチング素子のオンオフのデューティー比を制御することにより、該切替期間に対応する出力回路に流れる電流を調整して、該切替期間に対応する出力回路に接続された前記出力端子から出力される電圧を調整する回路である、

請求項5に記載のスイッチング装置。

【請求項7】

前記制御回路は、前記第1出力回路に対応する前記切替期間の頻度を変更することにより該第1出力回路に流れる電流を調整して前記第1出力端子から出力される電圧を調整し、前記第2出力回路に対応する前記切替期間の頻度を変更することにより該第2出力回路に流れる電流を調整して前記第2出力端子から出力される電圧を調整する回路である、

請求項5又は6に記載のスイッチング装置。

【請求項8】

前記制御回路は、検出した前記第1出力端子の電圧が所定の第1電圧範囲に収まり、検出した前記第2出力端子の電圧が所定の第2電圧範囲に収まるように、該第1出力端子の電圧及び該第2出力端子の電圧を調整するフィードバック制御を行う回路である、

請求項6又は7に記載のスイッチング装置。

【請求項9】

前記第1サブスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが前記第1出力端子側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが前記第1出力端子側に接続されたNチャネルMOSFETであり、

前記第2サブスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが前記第2出力端子側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが前記第2出力端子側に接続されたNチャネルMOSFETである、

請求項1〜8のいずれか1項に記載のスイッチング装置。

【請求項10】

前記メインスイッチング素子は、一端が前記直流電源側に接続されると共に他端が前記整流回路に接続された素子であり、

前記整流回路は、一端が前記メインスイッチング素子に接続され他端が前記第1出力回路及び前記第2出力回路に接続されたコイルと、一端が該メインスイッチング素子及び該コイルに接続され他端が基準電位であり他端側から一端側へ向かう方向が順方向であるダイオードとを有する回路であり、

前記第1出力端子及び前記第2出力端子は、前記直流電源を降圧した電圧を出力する端子である、

請求項1〜9のいずれか1項に記載のスイッチング装置。

【請求項11】

前記メインスイッチング素子は、ベースが前記制御回路に接続されエミッタが前記直流電源側に接続されコレクタが前記整流回路側に接続されたNPNトランジスタであるか、又はゲートが前記制御回路に接続されドレインが前記直流電源側に接続されソースが前記整流回路側に接続されたNチャネルMOSFETである、

請求項10に記載のスイッチング装置。

【請求項12】

前記整流回路は、一端が前記直流電源側に接続されると共に他端が前記ダイオード及び前記メインスイッチング素子に接続されたコイルと、一端が該コイル及び該メインスイッチング素子に接続されると共に他端が前記第1出力回路及び前記第2出力回路に接続され一端側から他端側へ向かう方向が順方向であるダイオードとを有する回路であり、

前記メインスイッチング素子は、一端が前記コイル及び前記ダイオードに接続され他端が基準電位である素子であり、

前記第1出力端子及び前記第2出力端子は、前記直流電源を昇圧した電圧を出力する端子である、

請求項1〜9のいずれか1項に記載のスイッチング装置。

【請求項13】

前記メインスイッチング素子は、ベースが前記制御回路側に接続されエミッタが前記整流回路側に接続されコレクタが基準電位であるNPNトランジスタであるか、又はゲートが前記制御回路側に接続されドレインが前記整流回路側に接続されソースが基準電位であるNチャネルMOSFETである、

請求項12に記載のスイッチング装置。

【請求項14】

直流電源から入力した電力をスイッチング可能なメインスイッチング素子と、前記メインスイッチング素子に接続され、コイルを有する整流回路と、一端が前記整流回路側に接続されると共に他端が第1出力端子側に接続され、該整流回路と該第1出力端子との間でスイッチングを行う第1サブスイッチング素子を有する第1出力回路と、一端が前記整流回路側に接続されると共に他端が第2出力端子側に接続され、該整流回路と該第2出力端子との間でスイッチングを行う第2サブスイッチング素子を有する第2出力回路と、を備えたスイッチング装置の制御方法であって、

制御信号を前記メインスイッチング素子に出力して該メインスイッチング素子にオンオフを繰り返させることで、該メインスイッチング素子のオンオフに伴って前記整流回路に電流を流し、前記第1サブスイッチング素子及び前記第2サブスイッチング素子のオンオフを制御することで、前記第1出力回路及び第2出力回路のいずれに前記整流回路から電流が流れるかを切り替えて、該第1出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第1出力端子から出力させ、該第2出力回路を流れる電流に応じて前記直流電源を変圧した電圧を前記第2出力端子から出力させるステップ、

を含むスイッチング装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−70499(P2013−70499A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−206801(P2011−206801)

【出願日】平成23年9月22日(2011.9.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月22日(2011.9.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]