スイッチング電源回路

【課題】ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現し、かつクロスレギュレーションの影響を小さくするスイッチング電源回路を得ること。

【解決手段】入力電圧が単一インダクタ2出力DC/DC変換回路150に入力されると、その出力電圧が第1及び第2のエラーアンプ151,152と第1及び第2のΔΣ変調回路153,154とドライブ回路155を介してΔΣ変調制御され、単一インダクタ2出力DC/DC変換回路150から出力電圧を得る。このΔΣ変調制御の特徴は、入力信号に比例して出力のパルス密度が変化することである。

【解決手段】入力電圧が単一インダクタ2出力DC/DC変換回路150に入力されると、その出力電圧が第1及び第2のエラーアンプ151,152と第1及び第2のΔΣ変調回路153,154とドライブ回路155を介してΔΣ変調制御され、単一インダクタ2出力DC/DC変換回路150から出力電圧を得る。このΔΣ変調制御の特徴は、入力信号に比例して出力のパルス密度が変化することである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング電源回路に関し、より詳細には、ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現し、かつクロスレギュレーションの影響を小さくするようにしたスイッチング電源回路に関する。

【背景技術】

【0002】

近年の電子機器は、小型でありながらも高性能化や多機能化が進んでおり、これらの電子機器の電源は、入力電圧変動及び負荷変動などの外乱に対する高い出力電圧安定性や高速な電圧変調などといった高い性能が求められている。

【0003】

また、家庭用電源からAC/DCパワーサプライを用いてパソコンなどのDC入力機器を用いる場合には、交流電源から平滑回路を用いてAC整流を行なうが、非安定な直流電流しか得られないので、DC/DCコンバータを用いて安定な直流電流を得る必要がある。そのためには、DC入力機器に各ICの駆動電圧を生成するためのDC/DCコンバータが組み込まれている。これらのDC/DCコンバータの求められる性能としては、高効率化や高速過渡応答などがある。これらを要求に答えるためには、DC/DCコンバータの制御部から改善しなければならない。また、DC/DCコンバータには小型化や低コスト化が求められている。そのためには、DC/DCコンバータのパワーステージから改善しなければならない。

【0004】

従来から知られているスイッチング電源装置として、PWM制御によるDC/DCコンバータがある。このPWM制御によるDC/DCコンバータは、入力電圧を降圧又は昇圧するためのスイッチング素子やインダクタを含み、パルス幅が入力信号に比例したPWM信号によりスイッチング素子のオンオフを制御するPWM変調器を備えている。

【0005】

このPWM制御によるDC/DCコンバータは、入力信号が変化したとき、出力電圧が所望の電圧に到達するまでの時間が長く、つまり、応答速度が遅いことが知られている。また、この種のPWM制御に代えて、応答速度が速いスイッチング電源装置として、ΔΣ(デルタ・シグマ)変調信号によりスイッチング素子のオンオフを制御するΔΣ変調器を備えたDC/DCコンバータが知られている(例えば、特許文献1参照)。

【0006】

また、近年、携帯電話を始め、電子機器の多機能化が進み、一つの電子機器に多くの電子部品が搭載されている。また、電子機器の小型化の要求もあり、単一のバッテリーで駆動される電子機器が普及しつつある。

【0007】

ところで、電子機器における各電子部品は、駆動するための電源電圧が異なるので、単一のバッテリーで電力を供給するためには、単一のバッテリーの電圧から各電子部品を駆動するための電源電圧を生成するDC/DCコンバータが、電子部品ごとに必要となる。ところが、電子部品ごとにDC/DCコンバータを用意することは、部品数の増加を招くという問題がある。そこで、電子部品ごとにDC/DCコンバータを用意するのではなく、インダクタを共有化、つまり、単一のインダクタで構成し、複数の電源電圧を生成する多出力電源装置が知られている(例えば、特許文献2参照)。

【0008】

ΔΣ変調は、アナログ信号をデジタル符号に変換する際に、高速で標本化した量子化雑音のパワースペクトル密度(PSD)分布の形状を整形して通過帯域のダイナミックレンジを向上させるようにしたものである。

【0009】

ΔΣ変調を用いたDC/DCコンバータは、電源の出力に応じてスイッチング周波数が変化する性質があり、この特徴を生かして電源の設計をすることで、スイッチング電源の出力状態に変化のない定常状態のときには、スイッチング電源のスイッチング周波数が低くなってスイッチングロスが低減される。一方、電源の出力が変化する過渡状態のとき、スイッチング電源のスイッチング周波数が高くなって負荷や出力電圧の急激な変化に対して高速な応答が可能となるといった動作が可能となる。

【0010】

また、特に軽負荷時にスイッチング周波数が低下して電源効率が高くなる特徴がある。近年の電子機器・装置、例えば、ファクシミリ、電話機、コピー機、その他OA機器や家電製品などは、本来の動作時以外の待機時にも電源を供給する必要のあるものが多くなってきている。このような電子機器の低消費電力化に対してもΔΣ変調方式のスイッチング電源回路は有効である。

【0011】

図1(a),(b)は、従来の多出力DC/DCコンバータを示す構成回路図で、図1(a)は、多出力DC/DCコンバータの構成回路図で、図1(b)は、図1(a)に示された制御回路の具体的な回路構成図である。この図1(a),(b)は、特許文献2に記載されたもので、単一インダクタとPWM制御を用いた多出力DC/DCコンバータである。

【0012】

図1(a)に示された多出力DC/DCコンバータは、入力直流電源1に接続され入力直流電圧Eiが入力されている。この多出力DC/DCコンバータには、NチャネルMOSFETの第1の主スイッチ21、PチャネルMOSFETの第2の主スイッチ22、インダクタ31、ダイオードの第1の整流手段51、コンデンサの第1の平滑手段61、ダイオードの第2の整流手段52、コンデンサの第2の平滑手段62、及び第1の主スイッチ21と第2の主スイッチ22をそれぞれ所定のオン期間とオフ期間で駆動する制御回路81が設けられている。第1の平滑手段61の両端には第1の負荷71が接続され、昇圧出力電圧Vo1が第1の負荷71へ出力される。第2の平滑手段62の両端には第2の負荷72が接続され、反転出力電圧Vo2が第2の負荷72へ出力される。入出力条件は、Vo1>Ei>0>Vo2 である。第2の主スイッチ22がオン状態の時、第1の主スイッチ21とインダクタ31と第1の整流手段51と第1の平滑手段61が、昇圧コンバータとして動作する。一方、第1の主スイッチ21がオン状態の時は、第2の主スイッチ22とインダクタ31と第2の整流手段52と第2の平滑手段62が反転コンバータとして動作する。

【0013】

図1(b)において、抵抗801と抵抗802は昇圧出力電圧Vo1を検出し、抵抗803と抵抗804は反転出力電圧Vo2を検出する。各検出電圧は、誤差増幅器805及び誤差増幅器806によって基準電圧源807の基準電圧とそれぞれ比較され、昇圧出力用誤差信号Ve1と反転出力用誤差信号Ve2がそれぞれ出力される。抵抗801〜804、誤差増幅器805、誤差増幅器806及び基準電圧源807により、検出回路90が構成されている。発振回路808は、所定の周期で電位が増減する三角波電圧Vtと、三角波電圧Vtが増加している時に“H”となり、減少している時に“L”となる信号Vt1を出力する。比較器809は昇圧出力用誤差信号Ve1と三角波電圧Vtとを比較する。比較器810は反転出力用誤差信号Ve2と三角波電圧Vtとを比較する。各比較器809,810の出力信号は、それぞれAND回路811及び812によって信号Vt1との論理積を示す信号V1及び信号V2として出力される。ここで、信号V1は昇圧出力用パルス信号であり、信号V2は反転出力用パルス信号である。比較器809,810とAND回路811,812とによりPWM回路91が構成されている。分周回路であるTフリップフロップ813には信号Vt1が入力され、信号Vt2を出力する。OR回路814には信号V1と信号Vt2が入力され、駆動信号Vg21を出力する。駆動信号Vg21はNチャネルMOSFETである第1の主スイッチ21を駆動し、“H”で第1の主スイッチ21をオン状態にする。NOR回路815は信号V2と信号Vt2の反転信号が入力され、駆動信号Vg22を出力する。駆動信号Vg22はPチャネルMOSFETである第2の主スイッチ22を駆動し、“L”で第2の主スイッチ22をオン状態にする。駆動信号Vg21と駆動信号Vg22が主スイッチ駆動信号である。OR回路814及びNOR回路815により論理回路92が構成されている。

【0014】

また、ΔΣ変調器を用いたスイッチング電源については、例えば、特許文献3に記載されている。この特許文献3に記載のものは、ΔΣ変調器のサンプリング信号の周波数を電源の出力に応じて制御することが可能なスイッチング電源に関するものである。

【0015】

また、ΔΣ変調器については、例えば、特許文献4及び5に記載されている。この特許文献4及び5に記載のものは、乗算器が不要で回路規模が小さく、高速動作や多チャンネル・タイムシェア使用の可能な高次のデジタルΔΣ変調器に関するものである。また、例えば、特許文献6及び7にもΔΣ変調器について開示されている。また、特許文献8のものは、バックブースト動作の可能な正負の出力を備えた単一インダクタバックブーストコンバータに関するものである。また、非特許文献1及び2には、単一インダクタ正負2出力DC−DCコンバータが記載されている。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2008−99362号公報

【特許文献2】特開2003−164143号公報

【特許文献3】特開2002−300772号公報

【特許文献4】特開平7−22952号公報

【特許文献5】特開2002−9624号公報

【特許文献6】再表2007/66431号公報

【特許文献7】特開2008−99035号公報

【特許文献8】特開2010−45966号公報

【非特許文献】

【0017】

【非特許文献1】電気情報通信学会論文「擬似連続モードを用いた単一インダクタ正負2出力DC−DCコンバータの検討」(津志田健吾他8名 第22回 回路とシステム(軽井沢)ワークショップ)

【非特許文献2】第22回 回路とシステム軽井沢ワークショップ「単一インダクタンス2出力DC−DCコンバータの検討」(津志田健吾他13名 4.19〜20、2010)

【発明の概要】

【発明が解決しようとする課題】

【0018】

しかしながら、上述した特許文献1に記載のDC/DCコンバータは、単一インダクタ多出力DC/DCコンバータではない。また、特許文献2に記載の単一インダクタ多出力電源装置は、PWM信号によりスイッチング素子のオンオフを制御しており、入力信号や負荷に変動があったとき、定常状態に収束するまでの応答速度が遅いという問題があった。

【0019】

また、多出力DC/DCコンバータにおいて、時分割で行っている複数の出力の昇降圧動作を一つの出力端子の出力電圧の昇降圧動作から他の出力端子の出力電圧の昇降圧動作に切り替えたとき、前の昇降圧動作時にインダクタに充電した充電電流が、他の出力端子に漏れるという問題がある。すなわち、一つの出力端子に転送すべき充電電流が、他の出力端子に転送されるクロスレギュレーションの影響が大きいという問題がある。

【0020】

また、上述した特許文献3に記載のΔΣ変調器を用いたスイッチング電源は、単一インダクタ多出力DC/DCコンバータではない。また、上述した特許文献4乃至7に記載のΔΣ変調器は、DC/DC変換回路を備えたスイッチング電源回路に適用することについては何ら開示されていない。

【0021】

つまり、上述した各特許文献のいずれにもΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてなるスイッチング電源回路については何ら開示されていない。

【0022】

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現し、かつクロスレギュレーションの影響を小さくするようにしたスイッチング電源回路を提供することにある。

【課題を解決するための手段】

【0023】

本発明は、このような目的を達成するためになされたもので、請求項1に記載の発明は、単一インダクタ多出力DC/DC変換回路を制御するスイッチング電源回路において、入力信号を出力信号に変換する単一インダクタ多出力DC/DC変換回路と、該単一インダクタ多出力DC/DC変換回路の前記出力信号を入力し、該単一インダクタ多出力DC/DC変換回路を制御するΔΣ変調回路とを備えていることを特徴とする。

【0024】

また、請求項2に記載の発明は、請求項1に記載の発明において、前記ΔΣ変調回路が、フィードフォワード型ΔΣ変調回路であることを特徴とする。

【0025】

また、請求項3に記載の発明は、請求項2に記載の発明において、前記フィードフォワード型ΔΣ変調回路の信号伝達関数が1であり、該フィードフォワード型ΔΣ変調回路より出力されるパルス密度変調信号に遅延がなく、該遅延に起因する出力電圧波形のリップルが低減されることを特徴とする。

【0026】

また、請求項4に記載の発明は、請求項2又は3に記載の発明において、前記単一インダクタ多出力DC/DC変換回路が、単一インダクタn出力DC/DC変換回路であって、該単一インダクタn出力DC/DC変換回路の出力電圧に対応する分圧電圧との差分を増幅した誤差信号をn個の前記フィードフォワード型ΔΣ変調回路に出力するn個のエラーアンプと、前記n個のフィードフォワード型ΔΣ変調回路より出力されたパルス密度変調信号が入力されるドライブ回路とを備えていることを特徴とする。

【0027】

また、請求項5に記載の発明は、請求項2,3又は4に記載の発明において、前記フィードフォワード型ΔΣ変調回路の次数が1次であることを特徴とする。

【0028】

また、請求項6に記載の発明は、請求項5に記載の発明において、前記フィードフォワード型ΔΣ変調回路が、低い周波数の入力アナログ信号を通過させる積分器と、該積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路から出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させるフィードフォワードパスとを備えていることを特徴とする。

【0029】

また、請求項7に記載の発明は、請求項6に記載の発明において、前記減算器が、第1のスイッチを備え、前記入力アナログ信号と前記出力デジタル信号をデジタル/アナログ変換した信号との差分をとり、前記積分器が、第2のスイッチと容量と第1の演算増幅器とを備え、前記差分を積分した差分積分信号を出力し、前記加算器が、前記入力アナログ信号がフィードフォワードパスにより入力される第1の抵抗と前記積分器の出力が入力される第2の抵抗と第2の演算増幅器と帰還抵抗とを備え、前記量子化器が、コンパレータとフリップフロップとを備え、量子化基準信号と前記加算器の信号レベルを大小比較して量子化信号を出力し、前記デジタル/アナログ変換回路が、2つの基準信号を選択する2つの第3のスイッチを備え、前記量子化信号である前記出力デジタル信号を帰還して前記量子化信号に同期して、前記出力デジタル信号の論理値に応じた基準信号を前記第3のスイッチにより選択し、前記出力デジタル信号をデジタル/アナログ変換した信号を生成するものであることを特徴とする。

【0030】

また、請求項8に記載の発明は、請求項2,3又は4に記載の発明において、前記フィードフォワード型ΔΣ変調回路の次数が2次であることを特徴とする。

【0031】

また、請求項9に記載の発明は、請求項8に記載の発明において、前記フィードフォワード型ΔΣ変調回路が、低い周波数の入力アナログ信号を通過させる1段目の積分器と、該1段目の積分器の出力側に接続された2段目の積分器と、該2段目の積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記1段目の積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路より出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させる第1のフィードフォワードパスと、前記1段目の積分器からの出力信号を前記加算器に直接入力する第2のフィードフォワードパスとを備えていることを特徴とする。

【0032】

また、請求項10に記載の発明は、請求項9に記載の発明において、前記減算器が、第1のスイッチを備え、前記入力アナログ信号と前記出力デジタル信号をデジタル/アナログ変換した信号との差分をとり、前記1段目の積分器が、第2のスイッチと第1の容量と第1の演算増幅器とを備え、前記差分を積分した差分積分信号を出力し、前記1段目の積分器が、第3のスイッチと第2の容量と第2の演算増幅器とを備え、前記1段目の積分器の出力を積分し、前記加算器が、前記入力アナログ信号が第1のフィードフォワードパスより入力される第1の抵抗と前記1段目の積分器の出力が第2のフィードフォワードパスより入力される第2の抵抗と前記2段目の積分器の出力が入力される第3の抵抗と第3の演算増幅器と帰還抵抗とを備え、前記量子化器が、コンパレータとフリップフロップとを備え、量子化基準信号と前記加算器の信号レベルを大小比較して量子化信号を出力し、

前記デジタル/アナログ変換回路が、2つの基準信号を選択する2つの第4のスイッチを備え、前記量子化信号である前記出力デジタル信号を帰還して前記量子化信号に同期して、前記出力デジタル信号の論理値に応じた基準信号を前記第4のスイッチにより選択し、前記出力デジタル信号をデジタル/アナログ変換した信号を生成することを特徴とする。

【0033】

また、請求項11に記載の発明は、請求項2,3又は4に記載の発明において、前記フィードフォワード型ΔΣ変調回路の次数がN次(Nは3以上の整数)あることを特徴とする。

【0034】

また、請求項12に記載の発明は、請求項11に記載の発明において、前記フィードフォワード型ΔΣ変調回路が、1段目からN段目までカスケード接続される1段目乃至N段目の積分器と、該N段目の積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記1段目の積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路より出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させる第1のフィードフォワードパスと、前記1段目の積分器から前記N−1段目までの出力信号を前記加算器に直接入力する第1乃至第N−1のフィードフォワードパスとを備えていることを特徴とする。

【発明の効果】

【0035】

本発明によれば、ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現するようにしたスイッチング電源回路を得ることができる。

【0036】

また、時分割で行っている複数の出力の昇降圧動作を一つの出力端子の出力電圧の昇降圧動作から他の出力端子の出力電圧の昇降圧動作に切り替えたとき、クロスレギュレーションにより他の出力端子の出力電圧に変動があっても、パルス密度変調信号により、高速で応答できるためクロスレギュレーションの影響が小さいという効果を奏する。

【図面の簡単な説明】

【0037】

【図1】従来のフィードバック(FB)型ΔΣ変調器を用いたスイッチング電源を示す構成回路図で、(a)は、多出力DC/DCコンバータの構成回路図で、(b)は、(a)に示された制御回路の具体的な回路構成図である。

【図2】従来から用いられていたPWM制御によるスイッチング電源回路の構成ブロック図で、(a)はスイッチング電源回路の全体構成図、b)は、ノコギリ波とエラーアンプ(誤差増幅器)の出力の関係を示す図、(c)は、PWM回路の出力信号を示す図である。

【図3】DC/DC変換回路に対する制御回路の動作を説明するための図で、(a)は、過渡状態の高速化を図るための昇圧(boost;ブースト)コンバータの回路構成図で、(b)は、過渡状態と定常状態における出力電圧の関係を示す図で、(c)は、スイッチング動作を示す図である。

【図4】PWM制御とFB型ΔΣ変調制御との特徴を比較するための構成ブロック図で、(a)はPWM制御を用いたスイッチング電源回路の構成図、(b)はFB型ΔΣ変調制御を用いたスイッチング電源回路の構成図である。

【図5】FB型ΔΣ変調制御についての説明図で、(a)はFB型ΔΣ変調回路を用いたスイッチング電源回路における制御回路の概略構成ブロック図、(b)はFB型ΔΣ変調回路の出力信号を示す図である。

【図6】FB型ΔΣ変調回路の回路構成とその入出力特性を示す図で、(a)はFB型ΔΣ変調回路の回路構成図、(b)は入力信号に対する出力信号を示す図、(c)は積分器出力を示す図である。

【図7】FB型ΔΣAD変調回路の構成ブロック図と伝達特性を説明するための図で、(a)はFB型ΔΣAD変調回路のブロック図、(b)は伝達特性を示す図、(c)は信号伝達関数とノイズ伝達関数の関係式を示している。

【図8】2次フィードバック型ΔΣ変調回路を説明するための構成ブロック図である。

【図9】単一インダクタ2出力DC/DC変換回路を説明するための図で、(a)は従来の2出力DC/DC変換回路、(b)は単一インダクタ2出力DC/DC変換回路を示している。

【図10】単一インダクタ2出力DC/DC変換回路の原理図で、(a)は、2出力昇圧コンバータの回路構成図、(b)はそのインダクタ電流波形を示している。

【図11】多出力DC/DC変換回路におけるクロスレギュレーションを説明するための図で、(a)はPWM制御方式の場合、(b)はΔΣ変調方式の場合を示している。

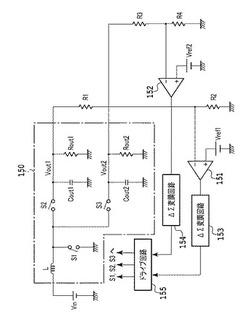

【図12】本発明に係るΔΣ変調制御を用いた多出力DC/DC変換回路を備えたスイッチング電源回路を説明するための回路構成図である。

【図13】図12におけるドライブ回路の具体的な回路構成図で、(a)はΔΣ変調回路の出力を受けて各スイッチ操作をする概念図、(b)はドライブ回路の回路構成図、(c)は真理値表を示している。

【図14】図13に示したドライブ回路を介して得られた本発明のスイッチング電源回路の出力のシミュレーション結果を示す図である。

【図15】本発明に係るスイッチング電源回路に用いられる1次フィードフォワード(FF)型ΔΣ変調回路を説明するための図で、(a)は1次フィードフォワード型ΔΣ変調回路の構成ブロック図、(b)は伝達特性を示す図、(c)は信号伝達関数とノイズ伝達関数の関係式を示している。

【図16】図15(a)に示した1次フィードフォワード型(FF型)ΔΣ変調回路の具体的な回路構成図である。

【図17】従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、1次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図である。

【図18】図17(a),(b)に示した出力電圧波形の拡大図である。

【図19】本発明に係るスイッチング電源回路に用いられる2次フィードフォワード(FF)型ΔΣ変調回路を説明するための構成ブロック図である。

【図20】図19に示した2次フィードフォワード型ΔΣ変調回路の具体的な回路構成図である。

【図21】従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、2次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図である。

【図22】図21(a),(b)に示した出力電圧波形の拡大図である。

【発明を実施するための形態】

【0038】

本発明に係るスイッチング電源回路の実施例について説明する前に、まず従来から用いられていたPWM制御によるスイッチング電源回路について以下に説明する。

【0039】

図2(a)乃至(c)は、従来から用いられていたPWM制御によるスイッチング電源回路を説明するための図で、図2(a)はスイッチング電源回路の全体構成図、図2(b)は、ノコギリ波とエラーアンプ(誤差増幅器)の関係を示す図、図2(c)は、PWM回路の出力信号を示す図である。PWM制御は、スイッチング周波数がノコギリ波の周波数で決定され、パルス幅はエラーアンプの出力の大きさにより決定され、パルスの数はスイッチング周波数で決定される。

【0040】

図2(a)において、入力電圧がDC/DC変換回路(DC/DCコンバータ)101に入力されると、入力電圧が昇圧もしくは降圧されて、出力電圧が出力される。その出力電圧がエラーアンプ102に入力され、所望の出力電圧からの誤差に対応する出力信号がPWM回路105に出力される。そして、PWM回路105を構成するコンパレータ103によってノコギリ波発生回路104からのノコギリ波とエラーアンプ102からの出力信号とが比較される。ここで、ノコギリ波とエラーアンプの出力の関係は、例えば、図2(b)のようになる。つまり、スイッチング周期ごとにエラーアンプ102の出力信号は変化し、PWM回路105の出力信号は、図2(c)のような、パルス幅の異なる信号が出力される。ここで、パルス幅はスイッチング電源回路の出力電圧の所望の出力電圧からの誤差に対応する。ドライブ回路106を介して、DC/DC変換回路101でパルス幅に応じたスイッチング動作が行われ、入力電圧を昇圧もしくは降圧した出力電圧が、スイッチング電源回路の出力電圧として得られる。

【0041】

このような構成のスイッチング電源回路を高いスイッチング周波数で動作させた場合には、PWM回路105の出力信号のパルス数が多くなり、スイッチングによる損失(スイッチングロス)が生じて、高効率化は図れないが、高速過渡応答が得られる。これに対して、低いスイッチング周波数で動作させた場合には、PWM回路105の出力信号のパルス数が少なくなり、高効率化は図れるが、高速過渡応答が得られない。このように、従来のPWM制御によるスイッチング電源回路では、高効率化と高速過渡応答とをスイッチング周波数で解決することは困難であった。

【0042】

スイッチング電源回路の要求される高効率化と高速過渡応答についてさらに具体的に動作説明する。

【0043】

図3(a)乃至(c)は、DC/DC変換回路に対する制御回路の動作を説明するための図で、図3(a)は、DC/DC変換回路の一例である昇圧(boost;ブースト)コンバータの回路構成図で、図3(b)は、過渡状態と定常状態における出力電圧の関係を示す図で、図3(c)は、DC/DC変換回路のスイッチング動作を行うためのスイッチング信号を示す図である。

【0044】

まず、図3(a)を参照して、昇圧コンバータの構成と動作を説明する。

昇圧コンバータは、DC/DC変換回路101と制御回路107とで構成されている。制御回路107は、図2(a)におけるエラーアンプ102とPWM回路105とドライブ回路106を含んでいる。また、制御回路107及び入力電圧Vin以外はDC/DC変換回路101を示している。

【0045】

DC/DC変換回路101におけるスイッチS1,S2は、MOSトランジスタ等で構成される。本説明では、スイッチS1,S2はNチャネルMOSトランジスタで構成されているものとする。つまり、スイッチS1,S2はハイレベルの制御信号が入力されると、オン(導通)して、ローレベルの制御信号が入力されると、オフ(遮断)される。また、スイッチS1,S2にはそれぞれ互いに極性が異なるスイッチング信号が制御回路107より与えられる。出力電圧の所望の値からの誤差に対応するPWM信号がスイッチS1に与えられ、反転したPWM信号がスイッチS2に与えられる。

【0046】

PWM信号がハイレベルのとき、スイッチS1はオンし、スイッチS2はオフする。スイッチS1がオンすることで、インダクタLに入力電圧Vinが印加され、インダクタLに充電電流が充電される。

【0047】

次に、PWM信号がローレベルになったとき、スイッチS1はオフし、スイッチS2はオンする。スイッチS2がオンすることで、インダクタLに充電された充電電流が容量Coutに流れ、容量Coutに電荷が蓄えられ、昇圧された出力電圧Voutが出力される。

【0048】

ここで、PWM信号のパルス幅が小さい程、インダクタLに充電される充電電流が小さくなるので、昇圧電圧は低くなる。一方、PWM信号のパルス幅が大きい程、インダクタLに充電される充電電流が大きくなるので、昇圧電圧は高くなる。パルス幅は、出力電圧Voutに応じて決まる。つまり、過渡状態である電源投入直後は、パルス幅が相対的に大きくなり、定常時は、パルス幅が相対的に小さくなる。

【0049】

上述のように、出力電圧Voutから所望の出力電圧の誤差に応じて制御回路107は、誤差に対応したパルス幅のPWM信号を生成して、スイッチS1、S2に出力する。

【0050】

次に、図3(b),(c)を参照して、高効率化と高速過渡応答について以下に説明する。

【0051】

図3(b)は、DC/DC変換回路が昇圧動作を開始して、出力電圧Voutが一定値(所望の出力電圧)に収束するまでの様子を表す図である。出力電圧Voutは、一定値に収束するまでの過渡状態、一定値に収束してからの定常状態の2つの状態がある。図3(c)は、周波数が低いときと、高いときのPWM信号を例示した図である。

【0052】

昇圧コンバータが、昇圧動作を開始して、一定値に収束するまでの過渡状態を短くするためには、周波数が高いPWM信号でスイッチングする必要がある。つまり、周波数が高いほど、スイッチS1,S2におけるスイッチング回数が多くなり、インダクタLから容量Coutへの充電回数が多くなるので、高速で定常状態に収束する。よって、高速で定常状態に収束するためには、PWM信号の周波数を高くすればよい。ところが、PWM信号の周波数を高くすると、スイッチS1,S2での損失が大きくなる。つまり、高効率化が図れなくなる。

【0053】

一方、スイッチS1,S2での損失を小さくし、高効率化を図るためには、PWM信号の周波数を低くする必要がある。すなわち、スイッチS1,S2におけるスイッチング回数を少なくすることで、損失が小さくなる。つまり、高効率化が図れる。

【0054】

ところが、PWM信号の周波数を低くすると、スイッチS1,S2におけるスイッチング回数が少なくなり、インダクタLから容量Coutへの充電回数が少なくなるので、定常状態に収束するまでの時間が長くなる。つまり、過渡状態が長くなる。

【0055】

このように、スイッチング電源回路の高速過渡応答と高効率化はトレードオフの関係にあり、周波数が固定であると、いずれか一方の要求しか達成できない。また、これらの要求に対して、高いスイッチング周波数での動作(高速過渡応答の改善)や低いスイッチング周波数での動作(高効率化の改善)は、周波数を可変にして行なう必要があった。つまり、従来では、高速過渡応答と高効率化をスイッチング周波数のみで解決しており、これでは回路規模増大を招き、大変困難を伴うものであった。そこで、ΔΣ変調方式の採用が検討されてきた。

【0056】

本発明に係るフィードフォワード(FF)型ΔΣ変調回路を用いたDC/DC変換回路を備えたスイッチング電源回路を説明する前に、PWM制御によるDC/DC変換回路とフィードバック(FB)型ΔΣ変調制御によるDC/DC変換回路を用いたスイッチング電源回路について以下に説明する。

【0057】

図4(a),(b)は、PWM制御とFB型ΔΣ変調制御との特徴を比較するための構成ブロック図で、図4(a)は、PWM制御を用いたスイッチング電源回路の構成図、図4(b)は、FB型ΔΣ変調制御を用いたスイッチング電源回路の構成図である。なお、制御回路112は、エラーアンプ102とFB型ΔΣ変調回路111とドライブ回路106を含んでいる。

【0058】

図4(a)において、入力電圧がDC/DC変換回路101に入力されると、その出力電圧がエラーアンプ102とPWM回路105とドライブ回路106を介してPWM制御され、DC/DC変換回路101から出力電圧を得る。このPWM制御の特徴は、上述のように、出力電圧から所望の出力電圧までの誤差に比例して、パルス幅が変化するPWM信号をPWM回路105からドライブ回路106を介してDC/DC変換回路101に出力することである。

【0059】

一方、図4(b)において、入力電圧がDC/DC変換回路101に入力されると、その出力電圧がエラーアンプ102とFB型ΔΣ変調制御回路111とドライブ回路106を介してFB型ΔΣ変調制御され、DC/DC変換回路101から出力電圧を得る。このFB型ΔΣ変調制御の特徴は、出力電圧から所望の出力電圧までの誤差に比例して、パルス密度が変化するパルス密度変調信号(ΔΣ変調信号)をFB型ΔΣ変調回路111からドライブ回路106を介してDC/DC変換回路101に出力することである。

【0060】

次に、フィードバック(FB)型ΔΣ変調制御の特徴について説明する。

【0061】

図5(a),(b)は、FB型ΔΣ変調制御についての説明図で、図5(a)は、FB型ΔΣ変調回路を用いたスイッチング電源回路の制御回路における概略構成ブロック図、図5(b)は、FB型ΔΣ変調回路の出力信号を示す図である。

【0062】

図5(a)において、エラーアンプ102の出力信号はDC/DC変換回路101の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号であり、FB型ΔΣ変調回路111に出力される。そして、FB型ΔΣ変調回路111は、誤差信号の大きさに応じたパルス密度のパルス密度変調信号を出力する。つまり、FB型ΔΣ変調回路111の出力信号は、図5(b)のように示される。FB型ΔΣ変調回路111の入力信号、すなわち、誤差信号が常に小さいとき(定常状態)では、パルス密度が相対的に薄くなり(低いスイッチング周波数)、高効率化が図れる。一方、FB型ΔΣ変調回路111の入力信号が常に大きいとき(過渡状態)では、パルス密度が相対的に濃くなり(高いスイッチング周波数)、高速過渡応答が図れる。

【0063】

次に、フィードバック(FB)型ΔΣ変調回路111の回路構成とその入出力特性について以下に説明する。

【0064】

図6(a)乃至(c)は、FB型ΔΣ変調回路の回路構成とその入出力特性を示す図で、図6(a)はFB型ΔΣ変調回路の回路構成図、図6(b)は、入力信号に対する出力信号を示す図、図6(c)は、積分器出力を示す図である。

【0065】

まず、図6(a)を参照して、FB型ΔΣ変調回路111の回路構成について説明する。

【0066】

FB型ΔΣ変調回路111は、減算器121と積分器122と量子化器(A/Dコンバータ;ADC)123とDAC(D/Aコンバータ)124とから構成されている。

【0067】

FB型ΔΣ変調回路111は、スイッチを含み入力信号と出力信号をD/A変換した信号との差分をとる減算器121と、スイッチ、容量、演算増幅器を含み、差分を積分した差分積分信号を出力する積分器122と、コンパレータ、フリップフロップを含み、量子化基準信号(しきい値)とで差分積分信号の信号レベルを大小比較し1ビットの量子化信号を出力する量子化器123と、2つの基準信号Vref、−Vrefを選択する2つのスイッチを含み、量子化信号である出力信号を帰還して1ビットの量子化信号に同期して、出力信号の論理値に応じた基準信号をスイッチにより選択し、出力信号をD/A変換した信号を生成するDAC124を備える構成とすることで、パルス密度変調信号を生成する。

【0068】

また、このような構成により、FB型ΔΣ変調回路111を備えたスイッチング電源回路は、従来のPWM回路を備えたスイッチング電源回路と比べて、サンプリング周波数が固定であるので、回路規模が小さくできるとともに、高速過渡応答と高効率化を可能としている。

【0069】

FB型ΔΣ変調回路111は、スイッチをオンオフし、電荷を転送するための2つのフェーズ、Ph1(フェーズ1)とPh2(フェーズ2)がある。図6(a)において、Ph1と図示したスイッチは、Ph1においてオンし、Ph2と図示したスイッチは、Ph2においてオンする。各フェーズの周波数は、サンプリング周波数に等しく、Ph1とPh2は、交互に繰り返される。つまり、一つのサンプリング周期において、一つのPh1と一つのPh2が存在する。

【0070】

次に、図6(b)、(c)を参照して、FB型ΔΣ変調回路111の動作を説明する。

【0071】

まず、FB型ΔΣ変調回路111は、上述のように、エラーアンプ102が出力するDC/DC変換回路101の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号を入力する。

【0072】

Ph1において、入力信号が積分器122の入力側容量に印加され、入力信号に応じた電荷が蓄えられる。Ph2において、DAC124の出力信号が積分器122の入力側容量に印加され、DAC124の出力信号に応じた電荷が転送される。ここで、減算器121は、入力側とDAC124の出力は結線されているので、Ph1で入力信号により蓄えた電荷から、Ph2でDAC124の出力信号に応じた電荷を減算した電荷が、積分器122の入力側容量に蓄えられる。つまり、FB型ΔΣ変調回路111の入力信号と出力信号との減算が行われ、差分信号が生成される。

【0073】

積分器122の入力側容量の電荷は、Ph2において、演算増幅器の出力端子から非反転入力端子との間の帰還容量に転送される。つまり、差分信号が積分され、差分積分信号が出力される。

【0074】

図6(b)は、FB型ΔΣ変調回路111の入力信号と出力信号を例示した波形で、図6(c)は、差分積分信号を例示した波形である。また、入力信号が0より小さいときの波形を表している。まず、図6(b)に示す様に、最初のサンプリング周期において、出力信号は、ローレベルであり、その出力信号に対応するDAC124の出力信号は、−Vrefであり、入力信号との差分は正の値となる。よって、図6(c)に示す様に、差分積分信号は、正の傾きをもつ一次関数波形となる。

【0075】

次に、差分積分信号は、量子化器123のコンパレータに入力され、量子化基準信号と差分積分信号が大小比較されて、フリップフロップに入力される。図6(a)において、量子化基準信号は、0V(グラウンド)である。そして、Ph1になったとき、フリップフロップは、差分積分信号と量子化基準信号(しきい値)との大小比較結果を1ビットの量子化信号として出力する。つまり、量子化器123は、差分積分信号が0V以上のとき、ハイレベルを出力し、0Vより小さいとき、ローレベルを出力する。図6(c)において、最初のサンプリング周期の最後の時点で、差分積分信号は、量子化基準信号と等しくなるので、コンパレータはハイレベルを出力し、次のサンプリング周期(次のPh1)になったとき、量子化器123は、ハイレベルの量子化信号を出力する。

【0076】

量子化信号は、DAC124のスイッチに入力される。DAC124において、量子化信号がハイレベルのとき、基準信号Vrefが選択され、量子化信号がローレベルのとき、基準信号−Vrefが選択される。

【0077】

そして、次のサンプリング周期において、量子化信号は、ハイレベルであるので、入力信号との差分は負の値となる。よって、図6(c)に示す様に、差分積分信号は、負の傾きをもつ一次関数波形となる。

【0078】

したがって、量子化器123におけるコンパレータの出力はローレベルとなり、さらに次のサンプリング周期になったとき、量子化信号はローレベルとなる。

【0079】

このような動作を繰り返すことで、入力信号に応じたパルス密度変調信号が生成される。図6(b)に例示した波形において、7サンプリング周期に3つのパルスが存在する。FB型ΔΣ変調回路111の入力信号が図示した値よりも小さくなる(誤差が大きくなる)と、パルス密度は濃くなり(パルスの数が増え)、図示した値よりも大きくなる(誤差が小さくなる)と、パルス密度は薄くなる(パルスの数が減る)。

【0080】

また、上述した動作により、入力信号が0Vより小さいとき、パルス密度変調信号は、一回ハイレベルになった後、必ずローレベルになる。このとき、ハイレベルの期間は、サンプリング周期であり固定である。一方、入力信号が0Vより大きいとき、パルス密度変調信号は、一回ローレベルになった後、必ずハイレベルになる。このとき、ローレベルの期間は、サンプリング周期であり固定である。

【0081】

このようにして、FB型ΔΣ変調回路111を備えたスイッチング電源回路は、従来のPWM回路を備えたスイッチング電源回路と比べて、回路規模が小さくなるとともに、高速過渡応答と高効率化を可能としている。

以上が、FB型ΔΣ変調回路111の動作説明である。

【0082】

図7(a)乃至(c)は、FB型ΔΣAD変調回路の構成ブロック図と伝達特性を説明するための図で、図7(a)は、FB型ΔΣAD変調回路のブロック図、図7(b)は、伝達特性を示す図、図7(c)は、信号伝達関数(STF;Signal Transfer Function)とノイズ伝達関数(NTF;Noise Transfer Function)の関係式を示している。

【0083】

図7(a)に示すように、低い周波数の信号を通過させる積分器(LPF)122と、量子化器(ADC;アナログ/デジタル変換回路)123と、DAC(デジタル/アナログ変換回路)124と、アナログ信号を減算して出力する減算器121とを備えている。

【0084】

減算器121の出力は、積分器122に入力され、積分器122の出力は、量子化器123に入力されている。また、DAC124は、量子化器123の出力をアナログ信号に変換して積分器122にフィードバックするように、量子化器123と減算器121との間に設けられている。減算器121は、FB型ΔΣAD変調器の入力信号から、DAC124の出力を減算して出力する。すなわち、図7(a)の積分器122、量子化器123、DAC124、減算器121はそれぞれ、図6(a)の積分器122、量子化器123、DAC124、減算器121に対応する。

【0085】

次に、FB型ΔΣAD変調回路の動作について説明する。まず、アナログ信号が入力されると、積分器122によって、低い周波数のアナログ信号が出力され、量子化器123によって、積分器122から出力されたアナログ信号がデジタル信号に変換され、減算器121で入力信号との差分をとるために、フィードバックするために、デジタル信号がDAC124に入力される。

【0086】

DAC124では、入力された量子化器123の出力を、アナログ信号に変換して、減算器121に入力し、入力となるアナログ信号から、DAC124の出力を減算して、積分器122にフィードバックする。そして、積分器122の出力が、量子化器123によってデジタル信号に変換されて、FB型ΔΣAD変調器の出力としてデジタル信号(パルス密度変調信号)が出力される。

【0087】

なお、FB型ΔΣ変調回路の出力信号により、図4(b)に示したDC/DC変換回路101でスイッチング動作を行ったときのDC/DC変換回路101の出力電圧波形は図17(a)に示され、その拡大図は図18(a)に示されている。

【0088】

FB型ΔΣ変調回路は、積分器の出力を量子化器で量子化するため、量子化器において量子化ノイズE(Z)が加わる。すなわち、図7(a)の入力から出力までの伝達特性は、図7(b)に示すようになる。図7(b)より伝達関数を求めると、図7(c)のようになる。

【0089】

図7(c)に示すように、Z変換した出力デジタル信号Y(Z)は、Y(Z)=H(Z)・X(Z)/(1+H(Z))+1・E(Z)/(1+H(Z))となる。信号伝達関数STF(Signal Transfer Function)は、STF(Z)=H(Z)/(1+H(Z))であり、ノイズ伝達関数NTF(Noise Transfer Function)は、NTF(Z)=1/(1+H(Z))である。なお、X(Z)はZ変換した入力アナログ信号であり、H(Z)は積分器の伝達関数である。

【0090】

また、オーバーサンプリングとノイズ伝達関数により量子化ノイズE(Z)はノイズシャイプされ高SNDR(Signal to Noise plus Distortion Ratio;信号対雑音+歪電力比)を実現する。

【0091】

しかしながら、積分器122の伝達関数は、1次の場合には、H(Z)=Z-1/(1−Z-1)であるので、信号伝達関数は、STF(Z)=Z-1となって1クロック(1サンプリング周期)遅れる。また、ノイズ伝達関数は、NTF(Z)=1−Z-1となり、1次の微分特性となる。

【0092】

ここで示されているフィルタ回路の次数は1次である。フィルタの次数は、その伝達関数の遅延演算子Z-1の最大のべき数である。

【0093】

図8は、2次フィードバック型ΔΣ変調回路を説明するための構成ブロック図である。減算器131の出力は、1段目の積分器132に入力され、1段目の積分器132の出力は、減算器133及び2段目の積分器134を介して量子化器135に入力されている。また、DAC136は、量子化器135の出力をアナログ信号に変換して2段目の積分器134にフィードバックするとともに、DAC137は、量子化器135の出力をアナログ信号に変換して1段目の積分器132にフィードバックする。減算器131は、ΔΣAD変調回路の入力となるアナログ信号から、DAC137の出力を減算して出力し、減算器133は、ΔΣAD変調回路の入力となるアナログ信号から、DAC136の出力を減算して出力する。

【0094】

1段目の積分器132の出力をZ変換すると、y1(Z)=Z-1X(Z)+Z-1(1−Z-1)E(Z)で示される。また、量子化器135の出力をZ変換すると、Y(Z)=Z-1X(Z)+(1−Z-1)2E(Z)で示される。

【0095】

すなわち、2次フィードバック型ΔΣ変調回路の信号伝達関数は、STF(Z)=Z-1であり、1クロック(1サンプリング周期)遅れる。ノイズ伝達関数は、NTF(Z)=(1−Z-1)2となり、2次の微分特性となる。

【0096】

以上、本発明に係るフィードフォワード型ΔΣ変調回路を用いたスイッチング電源回路を説明する前に、従来から用いられていたPWM回路を用いたスイッチング電源回路及び従来から用いられていたフィードバック型ΔΣ変調回路を用いたスイッチング電源回路について説明した。

【0097】

図9(a),(b)は、単一インダクタ2出力DC/DC変換回路を説明するための図で、図9(a)は、従来の2出力DC/DC変換回路、図9(b)は、単一インダクタ2出力DC/DC変換回路を示している。

【0098】

従来の2出力DC/DC変換回路141a,141bは、インダクタLが2個必要であり、サイズもコストも大きい。これに対して、単一インダクタ2出力DC/DC変換回路142は、インダクタLが1個であり、サイズもコストも小さい。

【0099】

図9(a)に示すように、電子機器における各電子部品は、駆動するための電源電圧が異なるので、単一のバッテリーで電力を供給するためには、単一のバッテリーの電圧から各電子部品を駆動するための電源電圧を生成するDC/DC変換回路が、電子部品ごとに必要となる。ところが、電子部品ごとにDC/DC変換回路を用意することは、部品数の増加を招くという問題がある。そこで、電子部品ごとにDC/DC変換回路を用意するのではなく、図9(b)に示すように、インダクタを共有化、つまり、単一のインダクタで構成し、複数の電源電圧を生成する多出力電源装置が必要になる。つまり、単一インダクタ多出力(SI−SIMO(Single Inductor−Single Input, Multiple Output)DC/DC変換回路が有用である。

【0100】

図10(a),(b)は、単一インダクタ2出力DC/DC変換回路の原理図で、図10(a)は、2出力昇圧コンバータの回路構成図、図10(b)は、そのインダクタ電流波形を示している。

【0101】

まず、図10(a)に示した2出力昇圧コンバータの構成を説明する。

図10(a)に示した2出力昇圧コンバータは、インダクタLとスイッチS1〜S3と容量C1,C2と負荷抵抗R1,R2とを備えている。インダクタLの一端には、入力電圧Vinが与えられ、インダクタの他端はスイッチS1〜S3の一端に共通接続される。スイッチS1の他端は、グラウンドに接地されている。スイッチS2は、容量C1と抵抗R1の一端に接続され、2出力のうち第1の出力電圧Vout1が得られる。スイッチS3の他端は、容量C2と抵抗R2の一端に接続され、2出力のうち第2の出力電圧Vout2が得られる。そして、容量C1,C2と抵抗R1,R2の他端は、それぞれグラウンドに接地されている。

【0102】

次に、図10(a)に示した2出力昇圧コンバータの動作を説明する。

2出力昇圧コンバータは、2つの出力電圧Vout1,Vout2を得るために、容量C1,C2に電荷を充電する期間を2つ設けて、インダクタを時分割して利用することで、充電を行う。すなわち、2つの期間のうち1つ目の期間(第1の期間)では、第1の出力電圧Vout1を得るための昇圧動作を行い、2つの期間のうち2つ目の期間(第2の期間)では、第2の出力電圧Vout2を得るための昇圧動作を行う。

【0103】

まず、第1の期間において、スイッチS3はオフし、スイッチS1,S2のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS2がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS2がオンして、インダクタLに充電された充電電流が容量C1に放電され、容量C1は充電される。そして、第1の出力電圧Vout1が得られる。

【0104】

次に、第2の期間において、スイッチS2はオフし、スイッチS1,S3のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS3がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS3がオンして、インダクタLに充電された充電電流が容量C2に放電され、容量C2は充電される。そして、第2の出力電圧Vout2が得られる。

【0105】

このときのインダクタLに流れる充電電流ILの波形を図10(b)に例示する。例示した波形は、スイッチS1〜S3をPWM信号によりスイッチング動作を行ったときの波形であり、安定した定常状態における波形である。このような回路によってインダクタを時分割して利用することで、2つの出力を得ることができる。

【0106】

図11(a),(b)は、多出力DC/DC変換回路におけるクロスレギュレーションの影響を説明するための図で、図11(a)は、PWM制御方式の場合、図11(b)は、ΔΣ変調方式の場合を示している。

【0107】

多出力電源において、片方の出力で負荷変動が生じると、他方の出力電圧が変動する現象をクロスレギュレーションという。つまり、複数の出力を取り出す場合、ある出力が他の出力に与える影響である。例えば、PWM制御を使うフライバック方式のコンバータの場合、軽負荷時には1次側FETのオン期間の幅を狭めて出力を制御する。そのため、2次巻き線に電圧が発生する期間も短くなる。複数の2次巻き線から巻き数に応じた異なる電圧を取り出す場合、電圧制御を行っている出力の負荷に応じて他の出力電圧が大きく変動してしまう。2次側にレギュレータ回路を追加すれば、システム全体としてのクロスレギュレーション特性の改善が可能だが、部品点数が増えるのでコストが上がってしまうという問題がある。

【0108】

また、図10(a)に示す非絶縁型の2出力DC/DCコンバータについても、同様に、片方の出力で負荷変動が生じると、スイッチに与えるPWM信号のパルス幅が変動する。例えば、第1の出力電圧側の負荷が重負荷になったとき、第1の期間において、スイッチS1,S2に与えられるPWM信号のパルス幅は大きくなる。すなわち、インダクタに充電される充電電流ILは大きくなる。そして、充電電流ILが容量C1に全て放電される前に、第2の期間に移行するため、第2の期間において、放電されなかった充電電流ILが容量C2に一部充電され、第2の出力電圧Vout2に変動が生じるという問題がある。

【0109】

第1の出力電圧Vout1側の負荷が重負荷になり、第2の出力電圧Vout2が定常状態のときのクロスレギュレーションの様子を図11(a),(b)に示す。

【0110】

図11(a)に示すように、PWM制御方式の場合には、図10(a)に示したS1からS3のスイッチ操作に対してVout1とVout2とのクロスレギュレーションが大である。これに対して、図11(b)に示すように、ΔΣ変調方式の場合には、Vout1とVout2とのクロスレギュレーションが小である。したがって、この種のクロスレギュレーションを良好にするためには、ΔΣ変調方式を用いることが有効であることが分かる。

【0111】

以下、図面を参照して本発明の実施例について説明する。

図12は、本発明に係るΔΣ変調制御を用いた単一インダクタ2出力DC/DC変換回路を備えたスイッチング電源回路を説明するための回路構成図で、ΔΣ変調制御を2出力昇圧コンバータに適用した場合の回路構成図である。

【0112】

図中符号150は単一インダクタ2出力DC/DC変換回路(デュアル昇圧コンバータ)、151は第1のエラーアンプ(誤差増幅器)、152は第2のエラーアンプ(誤差増幅器)、153は第1のΔΣ変調回路、154は第2のΔΣ変調回路、155はドライブ回路を示している。なお、2出力昇圧コンバータ150については、図10(a)に示した2出力昇圧コンバータと同様である。

【0113】

本発明に係るスイッチング電源回路は、単一インダクタ2出力DC/DC変換回路150と、第1出力を入力する第1のエラーアンプ151と、この第1のエラーアンプ151に接続された第1のΔΣ変調回路153と、第2出力を入力する第2のエラーアンプ152と、この第2のエラーアンプ152に接続された第2のΔΣ変調回路154と、第1のΔΣ変調回路153の出力と第2のΔΣ変調回路154の出力が接続されたドライバ回路155とから構成されている。

【0114】

つまり、本発明に係るスイッチング電源回路は、ΔΣ変調制御を用いた単一インダクタ2出力DC/DC変換回路150を備えたもので、入力信号を2つの出力信号に変換する単一インダクタ2出力DC/DC変換回路150と、この単一インダクタ2出力DC/DC変換回路150に接続されて出力信号をΔΣ変調制御する2つのΔΣ変調回路153,154とを備えている。

【0115】

入力電圧が単一インダクタ2出力DC/DC変換回路150に入力されると、その出力電圧が第1及び第2のエラーアンプ151,152と第1及び第2のΔΣ変調回路153,154とドライブ回路155を介してΔΣ変調制御され、単一インダクタ2出力DC/DC変換回路150から出力電圧を得る。このΔΣ変調制御の特徴は、パルス密度変調信号が、出力信号の所望の電圧からの誤差に比例してパルス密度が変化することである。

【0116】

図12に示した本発明のスイッチング電源回路の動作を以下に説明する。

本発明のスイッチング電源回路は、2つの出力電圧Vout1,Vout2を得るために、容量Cout1,Cout2に電荷を充電する期間を2つ設けて、インダクタを時分割して利用することで、充電を行う。すなわち、2つの期間のうち1つ目の期間(第1の期間)では、第1の出力電圧Vout1を得るための昇圧動作を行い、2つの期間のうち2つ目の期間(第2の期間)では、第2の出力電圧Vout2を得るための昇圧動作を行う。

【0117】

まず、第1の期間において、スイッチS3はオフし、スイッチS1,S2のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS2がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS2がオンして、インダクタLに充電された充電電流が容量Cout1に放電され、容量Cout1は充電される。そして、インダクタLの充放電の動作を1つの期間の間、繰り返すことで、第1の出力電圧Vout1が得られる。つまり、1つの期間の間、複数のパルスがスイッチS1,S2に入力されて、昇圧動作が行われる。

【0118】

次に、第2の期間において、スイッチS2はオフし、スイッチS1,S3のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS3がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS3がオンして、インダクタLに充電された充電電流が容量Cout2に放電され、容量Cout2は充電される。そして、インダクタLに充電された充電電流が容量Cout2に放電され、第2の出力電圧Vout2が得られる。つまり、1つの期間の間、複数のパルスがスイッチS1,S2に入力されて、昇圧動作が行われる。

【0119】

このときの第1及び第2の期間におけるインダクタLに流れる充電電流ILの波形、スイッチS1〜S3に与えられるパルス密度変調信号の波形を図11(b)に例示する。例示した波形は、スイッチS1〜S3をパルス密度変調信号によりスイッチング動作を行ったときの波形であり、第1の出力が重負荷になり、第2の出力が定常状態における波形である。

【0120】

図11(b)に示すように、第1の期間において、重負荷であるので、スイッチS1,S2のパルス密度は濃くなり、昇圧される。第2の期間において、第1の期間の残留した充電電流ILが第2出力にクロスレギュレーションされ、余分に容量Cout2に充電が行われるが、本発明のスイッチング電源回路は、ΔΣ変調制御であり、パルス密度変調信号によりスイッチングを行っているため、第2の出力電圧Vout2がクロスレギュレーションにより変動してもすぐに、パルス密度を調整して、所定の電圧にすることができる。

【0121】

つまり、PWM制御の場合、第1出力において負荷変動が生じ、第2出力が定常状態のとき、1つの期間において1つのパルスしかないので、クロスレギュレーションの影響に対して、パルス幅を調整して所定の電圧にするのに、次の第2の期間まで待たなければならないので、クロスレギュレーションの影響が大きくなる。それに対して、ΔΣ制御の場合、パルス密度、すなわち、一定期間におけるパルスの数で出力電圧を制御するので、変動が生じても、次の第2の期間を待たずに、その変動量に応じてパルス密度を調整することができる。図11(b)では、第2の期間において、第2の出力電圧Vout2の変動に応じてパルス密度が薄くなる様子を示している。したがって、本発明のスイッチング電源回路は、クロスレギュレーションの影響が小さくすることができる。

【0122】

以上が、本発明のスイッチング電源回路の動作説明である。なお、S2とS3が同時にオンすると、出力電圧が短絡してしまうのでドライブ回路155の構成は注意が必要である。

【0123】

図13(a)乃至(c)は、図12におけるドライブ回路の具体的な回路構成図で、図13(a)は、ΔΣ変調回路の出力を受けて各スイッチ操作をする概念図、図13(b)は、ドライブ回路の回路構成図、図13(c)は、真理値表を示している。

【0124】

ドライブ回路は、第1のΔΣ変調回路153の出力信号MO1、第2のΔΣ変調回路154の出力信号MO2、選択信号SELを入力し、スイッチS1〜S3にパルス密度変調信号を出力する。選択信号SELは、第1の期間、第2の期間を決める信号である。第1の期間は、論理値が0(ローレベル)のときで、第2の期間は、論理値が1(ハイレベル)のときである。

【0125】

選択信号SELが0のとき、第1のΔΣ変調回路153の出力信号MO1はイネーブルされ、第2のΔΣ変調回路154の出力信号MO2はディスイネーブルされる。そして、スイッチS1には、第1のΔΣ変調回路153の出力信号MO1が出力され、スイッチS2には、第1のΔΣ変調回路153の出力信号MO1を反転した信号が出力され、スイッチS3には、0が出力される。

【0126】

選択信号SELが1のとき、第1のΔΣ変調回路153の出力信号MO1はディスイネーブルされ、第2のΔΣ変調回路154の出力信号MO2はイネーブルされる。そして、スイッチS1には、第2のΔΣ変調回路154の出力信号MO2が出力され、スイッチS2には、0が出力され、スイッチS3には、第2のΔΣ変調回路154の出力信号MO2を反転した信号が出力される。

【0127】

このようにして、S2とS3が同時にオンすることなく、第1のΔΣ変調回路153の出力信号MO1と第1のΔΣ変調回路154の出力信号MO2とを時分割して、スイッチS1〜S3に与えることができる。

【0128】

このように、位相差を持ったサンプリング周波数のパルス(選択信号SEL)により、Vout1とVout2の制御を行う。なお、図14は、図13(b)に示したドライブ回路を介して得られた本発明のスイッチング電源回路の出力のシミュレーション結果を示す図である。

【0129】

以上は、単一インダクタ2出力DC/DC変換回路を用いた場合について説明したが、単一インダクタ多出力DC/DC変換回路を用いることも可能である。つまり、単一インダクタ多出力DC/DC変換回路として、単一インダクタn出力DC/DC変換回路を用いる場合には、この単一インダクタn出力DC/DC変換回路の出力電圧に対応する分圧電圧との差分を増幅した誤差信号をn個のΔΣ変調回路に出力するn個のエラーアンプと、n個のΔΣ変調回路より出力されたパルス密度変調信号が入力されるドライブ回路が必要になる。

【0130】

以下に、本発明に用いられるΔΣ変調回路として、1次フィードフォワード(FF)型ΔΣ変調回路及び2次フィードフォワード(FF)型ΔΣ変調回路について説明する。

【0131】

図15(a)乃至(c)は、本発明に係るスイッチング電源回路に用いられる1次フィードフォワード(FF)型ΔΣ変調回路を説明するための図で、図15(a)は、1次フィードフォワード型ΔΣ変調回路の構成ブロック図、図15(b)は、伝達特性を示す図、図15(c)は、信号伝達関数(STF;Signal Transfer Function)とノイズ伝達関数(NTF;Noise Transfer Function)の関係式を示している。

【0132】

図15(a)に示すように、特定の周波数のアナログ信号を通過させる積分器(LPF)162と加算器163とADC(アナログ/デジタル変換回路)164とDAC(デジタル/アナログ変換回路)165とアナログ信号を減算して出力する減算器161とを備えている。

【0133】

つまり、図15(a)に示すように、フィードフォワード型ΔΣ変調回路は、特定の周波数の入力アナログ信号を通過させる積分器162と、この積分器162に接続された加算器163と、この加算器163に接続された量子化器(ADC;アナログ/デジタル変換回路)164と、この量子化器164に接続され、この量子化器164のデジタル信号をアナログ信号に変換して積分器162にフィードバックするDAC(デジタル/アナログ変換回路)165と、入力アナログ信号からDAC165から出力されたアナログ信号を減算する減算器161と、入力アナログ信号を直接加算器163に入力させるフィードフォワードパスaとを備えている。

【0134】

FF型ΔΣ変調回路は、積分器162の出力を量子化器で量子化するため、量子化器において量子化ノイズE(Z)が加わる。すなわち、図15(a)の入力から出力までの伝達特性は、図15(b)に示すようになる。図15(b)より伝達関数を求めると、図15(c)のようになる。

【0135】

図15(c)に示すように、Z変換した出力デジタル信号Y(Z)は、Y(Z)=X(Z)+1・E(Z)/(1+H(Z))となり、積分器の伝達関数H(Z)は、1次の場合には、H(Z)=Z-1/(1−Z-1)であるので、信号伝達関数は、STF(Z)=1となり、パルス密度変調信号は遅延しない。また、ノイズ伝達関数は、NTF(Z)=1−Z-1となり、1次の微分特性となる。つまり、図7(c)に示した信号伝達関数は、STF(Z)=Z-1となり1クロック(1サンプリング周期)遅れるのに対して、図15(c)に示した信号伝達関数は、STF(Z)=1となり、パルス密度変調信号は遅延しない。つまり、FB型ΔΣAD変調回路よりもFF型ΔΣ変調回路の方が、パルス密度変調信号に遅延が生じないので、応答速度が改善されていることが分かる。

【0136】

つまり、フィードフォワード型ΔΣ変調回路の信号伝達関数が1であり、このフィードフォワード型ΔΣ変調回路より出力されるパルス密度変調信号に遅延がなく、該遅延に起因する出力電圧波形のリップルが低減されるという効果を奏する。

【0137】

図16は、図15(a)に示した1次フィードフォワード型(FF型)ΔΣ変調回路の具体的な回路構成図である。

【0138】

1次FF型ΔΣ変調回路は、減算器161と積分器162と加算器163と量子化器(A/Dコンバータ;ADC)164とDAC(D/Aコンバータ)165とから構成されている。

【0139】

1次FF型ΔΣ変調回路は、第1のスイッチを含み入力信号と出力信号をD/A変換した信号との差分をとる減算器161と、第2のスイッチと容量と第1の演算増幅器を備え、差分を積分した差分積分信号を出力する積分器162と、入力信号がフィードフォワードパスaより入力される第1の抵抗と積分器162の出力が入力される第2の抵抗と第2の演算増幅器と帰還抵抗とを備えた加算器163と、コンパレータとフリップフロップとを備え、量子化基準信号(しきい値)と加算器163の信号レベルを大小比較し1ビットの量子化信号を出力する量子化器164と、2つの基準信号Vref、−Vrefを選択する2つの第3のスイッチを備え、量子化信号である出力信号を帰還して1ビットの量子化信号に同期して、出力信号の論理値に応じた基準信号を第3のスイッチにより選択し、出力信号をD/A変換した信号を生成するDAC165を備える構成とすることで、パルス密度変調信号を生成する。

【0140】

1次FF型ΔΣ変調回路は、FB型ΔΣ変調回路の場合と同様に、スイッチをオンオフし、電荷を転送するための2つのフェーズ、Ph1(フェーズ1)とPh2(フェーズ2)がある。図16において、Ph1と図示したスイッチは、Ph1においてオンし、Ph2と図示したスイッチは、Ph2においてオンする。各フェーズの周波数は、サンプリング周波数に等しく、Ph1とPh2は、交互に繰り返される。つまり、一つのサンプリング周期において、一つのPh1と一つのPh2が存在する。

【0141】

まず、1次FF型ΔΣ変調回路は、上述のように、エラーアンプ151,152が出力するDC/DC変換回路150の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号を入力する。

【0142】

Ph1において、入力信号が積分器162の入力側容量に印加され、入力信号に応じた電荷が蓄えられる。また、フィードフォワードパスaにより直接加算器163に入力される。

【0143】

Ph2において、DAC165の出力信号が積分器162の入力側容量に印加され、DAC165の出力信号に応じた電荷が転送される。ここで、減算器161は、入力側とDAC165の出力が結線されているので、Ph1で入力信号により蓄えた電荷から、Ph2でDAC165の出力信号に応じた電荷を減算した電荷が、積分器162の入力側容量に蓄えられる。つまり、1次FF型ΔΣ変調回路の入力信号と出力信号との減算が行われ、差分信号が生成される。

【0144】

積分器162の入力側容量の電荷は、Ph2において、演算増幅器の出力端子から非反転入力端子との間の帰還容量に転送される。つまり、差分信号が積分され、差分積分信号が出力される。次に、差分積分信号は、加算器163において、フィードフォワードパスより伝達された入力信号と加算されて、加算信号が出力される。

【0145】

そして、加算信号は、量子化器164のコンパレータに入力され、量子化基準信号と加算信号が大小比較されて、フリップフロップに出力される。ここで、量子化基準信号は、0V(グラウンド)である。そして、Ph1になったとき、フリップフロップは、差分積分信号と量子化基準信号(しきい値)との大小比較結果を1ビットの量子化信号として出力する。つまり、量子化器164は、差分積分信号が0V以上のとき、ハイレベルを出力し、0Vより小さいとき、ローレベルを出力する。

【0146】

量子化信号は、DAC165のスイッチに入力される。DAC165において、量子化信号がハイレベルのとき、基準信号Vrefが選択され、量子化信号がローレベルのとき、基準信号−Vrefが選択される。そして、次のサンプリング周期において、量子化信号をD/A変換した信号は、入力信号から減算器161により減算される。

【0147】

このような動作を繰り返すことで、入力信号に応じたパルス密度変調信号が生成される。1次FF型ΔΣ変調回路の入力信号が小さくなる(誤差が大きくなる)と、パルス密度は濃くなり(パルスの数が増え)、大きくなる(誤差が小さくなる)と、パルス密度は薄くなる(パルスの数が減る)。

【0148】

また、上述した動作により、入力信号が0Vより小さいとき、パルス密度変調信号は、1回ハイレベルになった後、必ずローレベルになる。このとき、ハイレベルの期間は、サンプリング周期であり固定である。一方、入力信号が0Vより大きいとき、パルス密度変調信号は、1回ローレベルになった後、必ずハイレベルになる。このとき、ローレベルの期間は、サンプリング周期であり固定である。

以上が、1次FF型ΔΣ変調回路の動作説明である。

【0149】

FF型ΔΣ変調回路を用いたスイッチング電源回路は、上述のように、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、さらなる早い応答速度を実現することができる。

【0150】

さらに、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、スイッチング電源回路において遅延に起因する発振ループが形成されず、リップルが小さくなるという効果を奏する。

【0151】

つまり、エラーアンプの出力信号に対応し、スイッチング電源回路の所望の出力電圧からの誤差が0になるような量子化信号、すなわち、パルス密度信号が遅延することなくDC/DC変換回路(電圧コンバータ部)に反映されるので、量子化信号が反映されるまでの間、DC/DC変換回路が余分に昇圧もしくは降圧することがない。したがって、所望の出力電圧からの誤差が小さくなる。つまり、遅延に起因する誤差がエラーアンプに伝達されない。結果、スイッチング電源回路の出力信号にリップルは小さくなる。

【0152】

図17(a),(b)は、従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、1次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図で、図18(a),(b)は、その拡大図である。図18(a)に示したFB型ΔΣ変調回路の出力電圧波形のリップル(ripple;脈動成分)が大きいのに対して、図18(b)に示した1次FF型ΔΣ変調回路の出力電圧波形のリップルが小さいことがわかる。

【0153】

図19は、本発明に係るスイッチング電源回路に用いられる2次フィードフォワード(FF)型ΔΣ変調回路を説明するための構成ブロック図である。特定の周波数のアナログ信号を通過させる1段目の積分器172と2段目の積分器173と加算器174と量子化器(ADC)175とDAC176とアナログ信号を減算して出力する減算器171とを備えている。

【0154】

つまり、2次フィードフォワード型ΔΣ変調回路は、低い周波数の入力アナログ信号を通過させる1段目の積分器172と、この1段目の積分器172に接続された2段目の積分器173と、この2段目の積分器173に接続された加算器174と、この加算器174に接続された量子化器(ADC;アナログ/デジタル変換回路)175と、この量子化器175に接続され、この量子化器175のデジタル信号をアナログ信号に変換して1段目の積分器172にフィードバックするDAC(デジタル/アナログ変換回路)176と、入力アナログ信号からDAC176より出力されたアナログ信号を減算する減算器171と、入力アナログ信号を直接加算器174に入力させる第1のフィードフォワードパスaと、1段目の積分器172からの出力信号を加算器174に直接入力する第2のフィードフォワードパスbとを備えている。

【0155】

1段目の積分器172をZ変換した出力は、y1(Z)=Z-1(1−Z-1)E(Z)で示される。また、量子化器175をZ変換した出力は、Y(Z)=X(Z)+(1−Z-1)2E(Z)で示される。つまり、信号伝達関数は、STF(Z)=1で遅延がなく、ノイズ伝達関数は、NTF(Z)=(1−Z-1)2で2次の微分特性である。

【0156】

図20は、図19に示した2次フィードフォワード型ΔΣ変調回路の具体的な回路構成図である。

【0157】

2次FF型ΔΣ変調回路は、減算器171と積分器172と積分器173と加算器174と量子化器(A/Dコンバータ;ADC)175とDAC(D/Aコンバータ)176とから構成されている。

【0158】

2次FF型ΔΣ変調回路は、第1のスイッチを含み入力信号と出力信号をD/A変換した信号との差分をとる減算器171と、第2のスイッチと第1の容量と第1の演算増幅器とを備え、差分を積分した差分積分信号を出力する積分器172と、第3のスイッチと第2の容量と第3の演算増幅器とを備え、積分器172の出力を積分する積分器173と、入力信号がフィードフォワードパスaより入力される第1の抵抗と積分器172の出力がフィードフォワードパスbより入力される第2の抵抗と積分器173の出力が入力される第3の抵抗と第3の演算増幅器と帰還抵抗とを備えた加算器174と、コンパレータとフリップフロップとを備え、量子化基準信号(しきい値)と加算器174の信号レベルを大小比較し1ビットの量子化信号を出力する量子化器175と、2つの基準信号Vref、−Vrefを選択する2つの第4のスイッチを備え、量子化信号である出力信号を帰還して1ビットの量子化信号に同期して、出力信号の論理値に応じた基準信号を第4のスイッチにより選択し、出力信号をD/A変換した信号を生成するDAC176を備える構成とすることで、パルス密度変調信号を生成する。

【0159】

2次FF型ΔΣ変調回路は、1次FF型ΔΣ変調回路の場合と同様に、スイッチをオンオフし、電荷を転送するための2つのフェーズ、Ph1(フェーズ1)とPh2(フェーズ2)がある。図20において、Ph1と図示したスイッチは、Ph1においてオンし、Ph2と図示したスイッチは、Ph2においてオンする。各フェーズの周波数は、サンプリング周波数に等しく、Ph1とPh2は、交互に繰り返される。つまり、一つのサンプリング周期において、一つのPh1と一つのPh2が存在する。

【0160】

まず、2次FF型ΔΣ変調回路は、上述のように、エラーアンプ151,152が出力するDC/DC変換回路150の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号を入力する。

【0161】

Ph1において、入力信号が積分器172の入力側容量に印加され、入力信号に応じた電荷が蓄えられる。また、フィードフォワードパスaにより直接加算器174に入力される。

【0162】

Ph2において、DAC176の出力信号が積分器172の入力側容量に印加され、DAC176の出力信号に応じた電荷が転送される。ここで、減算器171は、入力側とDAC176の出力が結線されているので、Ph1で入力信号により蓄えた電荷から、Ph2でDAC176の出力信号に応じた電荷を減算した電荷が、積分器172の入力側容量に蓄えられる。つまり、2次FF型ΔΣ変調回路の入力信号と出力信号との減算が行われ、差分信号が生成される。

【0163】

積分器172の入力側容量の電荷は、Ph2において、演算増幅器の出力端子から非反転入力端子との間の帰還容量に転送される。つまり、差分信号が積分され、差分積分信号が出力される。

【0164】

次に、差分積分信号は、積分器173に入力され、さらに積分される。また、差分積分信号は、フィードフォワードパスbにより直接加算器174に入力される。加算器174において、フィードフォワードパスa及びbより伝達された信号と積分器173の出力信号とが加算されて、加算信号が出力される。

【0165】

そして、加算信号は、量子化器175のコンパレータに入力され、量子化基準信号と加算信号が大小比較されて、フリップフロップに出力される。ここで、量子化基準信号は、0V(グラウンド)である。そして、Ph1になったとき、フリップフロップは、差分積分信号と量子化基準信号(しきい値)との大小比較結果を1ビットの量子化信号として出力する。つまり、量子化器175は、差分積分信号が0V以上のとき、ハイレベルを出力し、0Vより小さいとき、ローレベルを出力する。

【0166】

量子化信号は、DAC176のスイッチに入力される。DAC176において、量子化信号がハイレベルのとき、基準信号Vrefが選択され、量子化信号がローレベルのとき、基準信号−Vrefが選択される。そして、次のサンプリング周期において、量子化信号をD/A変換した信号は、入力信号から減算器171により減算される。このような動作を繰り返すことで、入力信号に応じたパルス密度変調信号が生成される。

【0167】

2次FF型ΔΣ変調回路の入力信号が小さくなる(誤差が大きくなる)と、パルス密度は濃くなり(パルスの数が増え)、大きくなる(誤差が小さくなる)と、パルス密度は薄くなる(パルスの数が減る)。

【0168】

また、上述した動作により、入力信号が0Vより小さいとき、パルス密度変調信号は、一回ハイレベルになった後、必ずローレベルになる。このとき、ハイレベルの期間は、サンプリング周期であり固定である。一方、入力信号が0Vより大きいとき、パルス密度変調信号は、一回ローレベルになった後、必ずハイレベルになる。このとき、ローレベルの期間は、サンプリング周期であり固定である。

以上が、2次FF型ΔΣ変調回路の動作説明である。

【0169】

2次FF型ΔΣ変調回路を用いたスイッチング電源回路は、上述のように、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、さらなる早い応答速度を実現することができる。また、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、スイッチング電源回路においてパルス密度変調信号の遅延に起因する発振ループが形成されない。

【0170】

つまり、エラーアンプの出力信号に対応し、スイッチング電源回路の所望の出力電圧からの誤差が0になるような量子化信号、すなわち、パルス密度信号が遅延することなくDC/DC変換回路(電圧コンバータ部)に反映されるので、量子化信号が反映されるまでの間、DC/DC変換回路が余分に昇圧もしくは降圧することがない。よって、所望の出力電圧からの誤差が小さくなる。つまり、遅延に起因する誤差がエラーアンプに伝達されない。

【0171】

さらに、ノイズ伝達関数が2次の微分特性を有するので、信号帯域(低周波帯域)におけるSNDRがさらに高くなるので、1次FF型ΔΣ変調器を用いたスイッチング電源回路よりもリップルが小さくなるという効果を奏する。すなわち、量子化ノイズがより高周波帯域にシェーピングされるため、DC/DC変換回路におけるインダクタと容量とで形成されるリアクタンスフィルタによって、量子化ノイズを減衰させることができる。したがって、スイッチング電源回路の出力信号にリップルはさらに小さくなる。

【0172】

図21(a),(b)は、従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、2次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図で、図22(a),(b)は、その拡大図である。図22(a)に示したFB型ΔΣ変調回路の出力電圧波形のリップル(ripple;脈動成分)が大きいのに対して、図22(b)に示した2次FF型ΔΣ変調回路の出力電圧波形のリップルが極めて小さいことがわかる。また、図18(b)に示した1次FF型ΔΣ変調回路の出力電圧波形のリップリよりも、図22(b)に示した2次FF型ΔΣ変調回路の出力電圧波形のリップルの方が小さいことはわかる。つまり、1次FF型ΔΣ変調回路よりも2次FF型ΔΣ変調回路のリップルの方が改善されていることが分かる。

【0173】

以上は、2次FF型ΔΣ変調回路について説明したが、N次FF型ΔΣ変調回路について、図示していないが以下に説明する。

【0174】

フィードフォワード型ΔΣ変調回路が、1段目からN段目までカスケード接続される1段目乃至N段目の積分器と、このN段目の積分器の出力側に接続された加算器と、この加算器の出力側に接続された量子化器と、この量子化器の出力側に接続され、この量子化器の出力デジタル信号をアナログ信号に変換して1段目の積分器にフィードバックするデジタル/アナログ変換回路と、入力アナログ信号からデジタル/アナログ変換回路より出力されたアナログ信号を減算する減算器と、入力アナログ信号を直接加算器に入力させる第1のフィードフォワードパスと、1段目の積分器からN−1段目までの出力信号を加算器に直接入力する第1乃至第N−1のフィードフォワードパスとを備えている。

【0175】

このように、N次の場合も、1次や2次の場合と同様に、フィードフォワードパスがN個あり、積分器が初段からN段まで、N個カスケード接続されている。そして、各積分器の出力が加算器により加算され、量子化器にて、量子化される。量子化された量子化信号は、DACに入力され、アナログ信号に変換される。そして、入力信号と減算されて、初段の積分器に入力される。

【0176】

伝達関数は、1次と2次の場合と同様に導かれ、次式となる。

【0177】

Y(Z)=X(Z)+(1−Z-1)NE(Z)

すなわち、STFとNTFはそれぞれ以下の式で表される。

【0178】

STF=1

NTF=(1−Z-1)N

この式から分かるように、STFは、遅延がなく、NTFはN次の微分特性を有する。したがって、信号帯域の中心周波数付近で量子化ノイズが著しく減少していることが分かる。つまり、リップルをさらに低減できるという効果を奏する。

【0179】

以上のように、スイッチング電源回路の高性能化の要求に対して高効率化及び高速過渡応答をΔΣ変調制御により実現でき、小型化及び低コスト化を図るようにし、クロスレギュレーションの影響を小さくした単一インダクタ多出力DC/DC変換回路を備えたスイッチング電源回路を実現することが可能になった。

【符号の説明】

【0180】

1 入力直流電源

21 第1の主スイッチ

22 第2の主スイッチ

31 インダクタ

51 第1の整流手段

52 第2の整流手段

61 第1の平滑手段

62 第2の平滑手段

71 第1の負荷

72 第2の負荷

81 制御回路

90 検出回路

91 PWM回路

92 論理回路

101 DC/DC変換回路(DC/DCコンバータ)

102 エラーアンプ

103 コンパレータ

104 のこぎり発生回路

105 PWM回路

106 ドライブ回路

107,112 制御回路

111 FB型ΔΣ変調回路

121,131,133 減算器

122 積分器(ローパスフィルタ回路:LPF)

123 量子化器(A/Dコンバータ;ADC)

124,136,137 DAC(D/Aコンバータ)

132 1段目の積分器

134 2段目の積分器

135 ADC

141a,141b 2出力DC/DC変換回路

142 単一インダクタ2出力DC/DC変換回路

150 単一インダクタ2出力DC/DC変換回路(デュアル昇圧コンバータ)

151 第1のエラーアンプ(誤差増幅器)

152 第2のエラーアンプ(誤差増幅器)

153 第1のΔΣ変調回路

154 第2のΔΣ変調回路

155 ドライブ回路

161,171 減算器

162 積分器(LPF)

163,174 加算器

164,175 ADC(アナログ/デジタル変換回路)

165,176 DAC(デジタル/アナログ変換回路)

172 1段目の積分器

173 2段目の積分器

801,802,803,804 抵抗

805,806 誤差増幅器

807 基準電圧源

808 発振回路

809,810 比較器

811,812 AND回路

813 Tフリップフロップ

814 OR回路

815 NOR回路

【技術分野】

【0001】

本発明は、スイッチング電源回路に関し、より詳細には、ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現し、かつクロスレギュレーションの影響を小さくするようにしたスイッチング電源回路に関する。

【背景技術】

【0002】

近年の電子機器は、小型でありながらも高性能化や多機能化が進んでおり、これらの電子機器の電源は、入力電圧変動及び負荷変動などの外乱に対する高い出力電圧安定性や高速な電圧変調などといった高い性能が求められている。

【0003】

また、家庭用電源からAC/DCパワーサプライを用いてパソコンなどのDC入力機器を用いる場合には、交流電源から平滑回路を用いてAC整流を行なうが、非安定な直流電流しか得られないので、DC/DCコンバータを用いて安定な直流電流を得る必要がある。そのためには、DC入力機器に各ICの駆動電圧を生成するためのDC/DCコンバータが組み込まれている。これらのDC/DCコンバータの求められる性能としては、高効率化や高速過渡応答などがある。これらを要求に答えるためには、DC/DCコンバータの制御部から改善しなければならない。また、DC/DCコンバータには小型化や低コスト化が求められている。そのためには、DC/DCコンバータのパワーステージから改善しなければならない。

【0004】

従来から知られているスイッチング電源装置として、PWM制御によるDC/DCコンバータがある。このPWM制御によるDC/DCコンバータは、入力電圧を降圧又は昇圧するためのスイッチング素子やインダクタを含み、パルス幅が入力信号に比例したPWM信号によりスイッチング素子のオンオフを制御するPWM変調器を備えている。

【0005】

このPWM制御によるDC/DCコンバータは、入力信号が変化したとき、出力電圧が所望の電圧に到達するまでの時間が長く、つまり、応答速度が遅いことが知られている。また、この種のPWM制御に代えて、応答速度が速いスイッチング電源装置として、ΔΣ(デルタ・シグマ)変調信号によりスイッチング素子のオンオフを制御するΔΣ変調器を備えたDC/DCコンバータが知られている(例えば、特許文献1参照)。

【0006】

また、近年、携帯電話を始め、電子機器の多機能化が進み、一つの電子機器に多くの電子部品が搭載されている。また、電子機器の小型化の要求もあり、単一のバッテリーで駆動される電子機器が普及しつつある。

【0007】

ところで、電子機器における各電子部品は、駆動するための電源電圧が異なるので、単一のバッテリーで電力を供給するためには、単一のバッテリーの電圧から各電子部品を駆動するための電源電圧を生成するDC/DCコンバータが、電子部品ごとに必要となる。ところが、電子部品ごとにDC/DCコンバータを用意することは、部品数の増加を招くという問題がある。そこで、電子部品ごとにDC/DCコンバータを用意するのではなく、インダクタを共有化、つまり、単一のインダクタで構成し、複数の電源電圧を生成する多出力電源装置が知られている(例えば、特許文献2参照)。

【0008】

ΔΣ変調は、アナログ信号をデジタル符号に変換する際に、高速で標本化した量子化雑音のパワースペクトル密度(PSD)分布の形状を整形して通過帯域のダイナミックレンジを向上させるようにしたものである。

【0009】

ΔΣ変調を用いたDC/DCコンバータは、電源の出力に応じてスイッチング周波数が変化する性質があり、この特徴を生かして電源の設計をすることで、スイッチング電源の出力状態に変化のない定常状態のときには、スイッチング電源のスイッチング周波数が低くなってスイッチングロスが低減される。一方、電源の出力が変化する過渡状態のとき、スイッチング電源のスイッチング周波数が高くなって負荷や出力電圧の急激な変化に対して高速な応答が可能となるといった動作が可能となる。

【0010】

また、特に軽負荷時にスイッチング周波数が低下して電源効率が高くなる特徴がある。近年の電子機器・装置、例えば、ファクシミリ、電話機、コピー機、その他OA機器や家電製品などは、本来の動作時以外の待機時にも電源を供給する必要のあるものが多くなってきている。このような電子機器の低消費電力化に対してもΔΣ変調方式のスイッチング電源回路は有効である。

【0011】

図1(a),(b)は、従来の多出力DC/DCコンバータを示す構成回路図で、図1(a)は、多出力DC/DCコンバータの構成回路図で、図1(b)は、図1(a)に示された制御回路の具体的な回路構成図である。この図1(a),(b)は、特許文献2に記載されたもので、単一インダクタとPWM制御を用いた多出力DC/DCコンバータである。

【0012】

図1(a)に示された多出力DC/DCコンバータは、入力直流電源1に接続され入力直流電圧Eiが入力されている。この多出力DC/DCコンバータには、NチャネルMOSFETの第1の主スイッチ21、PチャネルMOSFETの第2の主スイッチ22、インダクタ31、ダイオードの第1の整流手段51、コンデンサの第1の平滑手段61、ダイオードの第2の整流手段52、コンデンサの第2の平滑手段62、及び第1の主スイッチ21と第2の主スイッチ22をそれぞれ所定のオン期間とオフ期間で駆動する制御回路81が設けられている。第1の平滑手段61の両端には第1の負荷71が接続され、昇圧出力電圧Vo1が第1の負荷71へ出力される。第2の平滑手段62の両端には第2の負荷72が接続され、反転出力電圧Vo2が第2の負荷72へ出力される。入出力条件は、Vo1>Ei>0>Vo2 である。第2の主スイッチ22がオン状態の時、第1の主スイッチ21とインダクタ31と第1の整流手段51と第1の平滑手段61が、昇圧コンバータとして動作する。一方、第1の主スイッチ21がオン状態の時は、第2の主スイッチ22とインダクタ31と第2の整流手段52と第2の平滑手段62が反転コンバータとして動作する。

【0013】

図1(b)において、抵抗801と抵抗802は昇圧出力電圧Vo1を検出し、抵抗803と抵抗804は反転出力電圧Vo2を検出する。各検出電圧は、誤差増幅器805及び誤差増幅器806によって基準電圧源807の基準電圧とそれぞれ比較され、昇圧出力用誤差信号Ve1と反転出力用誤差信号Ve2がそれぞれ出力される。抵抗801〜804、誤差増幅器805、誤差増幅器806及び基準電圧源807により、検出回路90が構成されている。発振回路808は、所定の周期で電位が増減する三角波電圧Vtと、三角波電圧Vtが増加している時に“H”となり、減少している時に“L”となる信号Vt1を出力する。比較器809は昇圧出力用誤差信号Ve1と三角波電圧Vtとを比較する。比較器810は反転出力用誤差信号Ve2と三角波電圧Vtとを比較する。各比較器809,810の出力信号は、それぞれAND回路811及び812によって信号Vt1との論理積を示す信号V1及び信号V2として出力される。ここで、信号V1は昇圧出力用パルス信号であり、信号V2は反転出力用パルス信号である。比較器809,810とAND回路811,812とによりPWM回路91が構成されている。分周回路であるTフリップフロップ813には信号Vt1が入力され、信号Vt2を出力する。OR回路814には信号V1と信号Vt2が入力され、駆動信号Vg21を出力する。駆動信号Vg21はNチャネルMOSFETである第1の主スイッチ21を駆動し、“H”で第1の主スイッチ21をオン状態にする。NOR回路815は信号V2と信号Vt2の反転信号が入力され、駆動信号Vg22を出力する。駆動信号Vg22はPチャネルMOSFETである第2の主スイッチ22を駆動し、“L”で第2の主スイッチ22をオン状態にする。駆動信号Vg21と駆動信号Vg22が主スイッチ駆動信号である。OR回路814及びNOR回路815により論理回路92が構成されている。

【0014】

また、ΔΣ変調器を用いたスイッチング電源については、例えば、特許文献3に記載されている。この特許文献3に記載のものは、ΔΣ変調器のサンプリング信号の周波数を電源の出力に応じて制御することが可能なスイッチング電源に関するものである。

【0015】

また、ΔΣ変調器については、例えば、特許文献4及び5に記載されている。この特許文献4及び5に記載のものは、乗算器が不要で回路規模が小さく、高速動作や多チャンネル・タイムシェア使用の可能な高次のデジタルΔΣ変調器に関するものである。また、例えば、特許文献6及び7にもΔΣ変調器について開示されている。また、特許文献8のものは、バックブースト動作の可能な正負の出力を備えた単一インダクタバックブーストコンバータに関するものである。また、非特許文献1及び2には、単一インダクタ正負2出力DC−DCコンバータが記載されている。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2008−99362号公報

【特許文献2】特開2003−164143号公報

【特許文献3】特開2002−300772号公報

【特許文献4】特開平7−22952号公報

【特許文献5】特開2002−9624号公報

【特許文献6】再表2007/66431号公報

【特許文献7】特開2008−99035号公報

【特許文献8】特開2010−45966号公報

【非特許文献】

【0017】

【非特許文献1】電気情報通信学会論文「擬似連続モードを用いた単一インダクタ正負2出力DC−DCコンバータの検討」(津志田健吾他8名 第22回 回路とシステム(軽井沢)ワークショップ)

【非特許文献2】第22回 回路とシステム軽井沢ワークショップ「単一インダクタンス2出力DC−DCコンバータの検討」(津志田健吾他13名 4.19〜20、2010)

【発明の概要】

【発明が解決しようとする課題】

【0018】

しかしながら、上述した特許文献1に記載のDC/DCコンバータは、単一インダクタ多出力DC/DCコンバータではない。また、特許文献2に記載の単一インダクタ多出力電源装置は、PWM信号によりスイッチング素子のオンオフを制御しており、入力信号や負荷に変動があったとき、定常状態に収束するまでの応答速度が遅いという問題があった。

【0019】

また、多出力DC/DCコンバータにおいて、時分割で行っている複数の出力の昇降圧動作を一つの出力端子の出力電圧の昇降圧動作から他の出力端子の出力電圧の昇降圧動作に切り替えたとき、前の昇降圧動作時にインダクタに充電した充電電流が、他の出力端子に漏れるという問題がある。すなわち、一つの出力端子に転送すべき充電電流が、他の出力端子に転送されるクロスレギュレーションの影響が大きいという問題がある。

【0020】

また、上述した特許文献3に記載のΔΣ変調器を用いたスイッチング電源は、単一インダクタ多出力DC/DCコンバータではない。また、上述した特許文献4乃至7に記載のΔΣ変調器は、DC/DC変換回路を備えたスイッチング電源回路に適用することについては何ら開示されていない。

【0021】

つまり、上述した各特許文献のいずれにもΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてなるスイッチング電源回路については何ら開示されていない。

【0022】

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現し、かつクロスレギュレーションの影響を小さくするようにしたスイッチング電源回路を提供することにある。

【課題を解決するための手段】

【0023】

本発明は、このような目的を達成するためになされたもので、請求項1に記載の発明は、単一インダクタ多出力DC/DC変換回路を制御するスイッチング電源回路において、入力信号を出力信号に変換する単一インダクタ多出力DC/DC変換回路と、該単一インダクタ多出力DC/DC変換回路の前記出力信号を入力し、該単一インダクタ多出力DC/DC変換回路を制御するΔΣ変調回路とを備えていることを特徴とする。

【0024】

また、請求項2に記載の発明は、請求項1に記載の発明において、前記ΔΣ変調回路が、フィードフォワード型ΔΣ変調回路であることを特徴とする。

【0025】

また、請求項3に記載の発明は、請求項2に記載の発明において、前記フィードフォワード型ΔΣ変調回路の信号伝達関数が1であり、該フィードフォワード型ΔΣ変調回路より出力されるパルス密度変調信号に遅延がなく、該遅延に起因する出力電圧波形のリップルが低減されることを特徴とする。

【0026】

また、請求項4に記載の発明は、請求項2又は3に記載の発明において、前記単一インダクタ多出力DC/DC変換回路が、単一インダクタn出力DC/DC変換回路であって、該単一インダクタn出力DC/DC変換回路の出力電圧に対応する分圧電圧との差分を増幅した誤差信号をn個の前記フィードフォワード型ΔΣ変調回路に出力するn個のエラーアンプと、前記n個のフィードフォワード型ΔΣ変調回路より出力されたパルス密度変調信号が入力されるドライブ回路とを備えていることを特徴とする。

【0027】

また、請求項5に記載の発明は、請求項2,3又は4に記載の発明において、前記フィードフォワード型ΔΣ変調回路の次数が1次であることを特徴とする。

【0028】

また、請求項6に記載の発明は、請求項5に記載の発明において、前記フィードフォワード型ΔΣ変調回路が、低い周波数の入力アナログ信号を通過させる積分器と、該積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路から出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させるフィードフォワードパスとを備えていることを特徴とする。

【0029】

また、請求項7に記載の発明は、請求項6に記載の発明において、前記減算器が、第1のスイッチを備え、前記入力アナログ信号と前記出力デジタル信号をデジタル/アナログ変換した信号との差分をとり、前記積分器が、第2のスイッチと容量と第1の演算増幅器とを備え、前記差分を積分した差分積分信号を出力し、前記加算器が、前記入力アナログ信号がフィードフォワードパスにより入力される第1の抵抗と前記積分器の出力が入力される第2の抵抗と第2の演算増幅器と帰還抵抗とを備え、前記量子化器が、コンパレータとフリップフロップとを備え、量子化基準信号と前記加算器の信号レベルを大小比較して量子化信号を出力し、前記デジタル/アナログ変換回路が、2つの基準信号を選択する2つの第3のスイッチを備え、前記量子化信号である前記出力デジタル信号を帰還して前記量子化信号に同期して、前記出力デジタル信号の論理値に応じた基準信号を前記第3のスイッチにより選択し、前記出力デジタル信号をデジタル/アナログ変換した信号を生成するものであることを特徴とする。

【0030】

また、請求項8に記載の発明は、請求項2,3又は4に記載の発明において、前記フィードフォワード型ΔΣ変調回路の次数が2次であることを特徴とする。

【0031】

また、請求項9に記載の発明は、請求項8に記載の発明において、前記フィードフォワード型ΔΣ変調回路が、低い周波数の入力アナログ信号を通過させる1段目の積分器と、該1段目の積分器の出力側に接続された2段目の積分器と、該2段目の積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記1段目の積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路より出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させる第1のフィードフォワードパスと、前記1段目の積分器からの出力信号を前記加算器に直接入力する第2のフィードフォワードパスとを備えていることを特徴とする。

【0032】

また、請求項10に記載の発明は、請求項9に記載の発明において、前記減算器が、第1のスイッチを備え、前記入力アナログ信号と前記出力デジタル信号をデジタル/アナログ変換した信号との差分をとり、前記1段目の積分器が、第2のスイッチと第1の容量と第1の演算増幅器とを備え、前記差分を積分した差分積分信号を出力し、前記1段目の積分器が、第3のスイッチと第2の容量と第2の演算増幅器とを備え、前記1段目の積分器の出力を積分し、前記加算器が、前記入力アナログ信号が第1のフィードフォワードパスより入力される第1の抵抗と前記1段目の積分器の出力が第2のフィードフォワードパスより入力される第2の抵抗と前記2段目の積分器の出力が入力される第3の抵抗と第3の演算増幅器と帰還抵抗とを備え、前記量子化器が、コンパレータとフリップフロップとを備え、量子化基準信号と前記加算器の信号レベルを大小比較して量子化信号を出力し、

前記デジタル/アナログ変換回路が、2つの基準信号を選択する2つの第4のスイッチを備え、前記量子化信号である前記出力デジタル信号を帰還して前記量子化信号に同期して、前記出力デジタル信号の論理値に応じた基準信号を前記第4のスイッチにより選択し、前記出力デジタル信号をデジタル/アナログ変換した信号を生成することを特徴とする。

【0033】

また、請求項11に記載の発明は、請求項2,3又は4に記載の発明において、前記フィードフォワード型ΔΣ変調回路の次数がN次(Nは3以上の整数)あることを特徴とする。

【0034】

また、請求項12に記載の発明は、請求項11に記載の発明において、前記フィードフォワード型ΔΣ変調回路が、1段目からN段目までカスケード接続される1段目乃至N段目の積分器と、該N段目の積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記1段目の積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路より出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させる第1のフィードフォワードパスと、前記1段目の積分器から前記N−1段目までの出力信号を前記加算器に直接入力する第1乃至第N−1のフィードフォワードパスとを備えていることを特徴とする。

【発明の効果】

【0035】

本発明によれば、ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現するようにしたスイッチング電源回路を得ることができる。

【0036】

また、時分割で行っている複数の出力の昇降圧動作を一つの出力端子の出力電圧の昇降圧動作から他の出力端子の出力電圧の昇降圧動作に切り替えたとき、クロスレギュレーションにより他の出力端子の出力電圧に変動があっても、パルス密度変調信号により、高速で応答できるためクロスレギュレーションの影響が小さいという効果を奏する。

【図面の簡単な説明】

【0037】

【図1】従来のフィードバック(FB)型ΔΣ変調器を用いたスイッチング電源を示す構成回路図で、(a)は、多出力DC/DCコンバータの構成回路図で、(b)は、(a)に示された制御回路の具体的な回路構成図である。

【図2】従来から用いられていたPWM制御によるスイッチング電源回路の構成ブロック図で、(a)はスイッチング電源回路の全体構成図、b)は、ノコギリ波とエラーアンプ(誤差増幅器)の出力の関係を示す図、(c)は、PWM回路の出力信号を示す図である。

【図3】DC/DC変換回路に対する制御回路の動作を説明するための図で、(a)は、過渡状態の高速化を図るための昇圧(boost;ブースト)コンバータの回路構成図で、(b)は、過渡状態と定常状態における出力電圧の関係を示す図で、(c)は、スイッチング動作を示す図である。

【図4】PWM制御とFB型ΔΣ変調制御との特徴を比較するための構成ブロック図で、(a)はPWM制御を用いたスイッチング電源回路の構成図、(b)はFB型ΔΣ変調制御を用いたスイッチング電源回路の構成図である。

【図5】FB型ΔΣ変調制御についての説明図で、(a)はFB型ΔΣ変調回路を用いたスイッチング電源回路における制御回路の概略構成ブロック図、(b)はFB型ΔΣ変調回路の出力信号を示す図である。

【図6】FB型ΔΣ変調回路の回路構成とその入出力特性を示す図で、(a)はFB型ΔΣ変調回路の回路構成図、(b)は入力信号に対する出力信号を示す図、(c)は積分器出力を示す図である。

【図7】FB型ΔΣAD変調回路の構成ブロック図と伝達特性を説明するための図で、(a)はFB型ΔΣAD変調回路のブロック図、(b)は伝達特性を示す図、(c)は信号伝達関数とノイズ伝達関数の関係式を示している。

【図8】2次フィードバック型ΔΣ変調回路を説明するための構成ブロック図である。

【図9】単一インダクタ2出力DC/DC変換回路を説明するための図で、(a)は従来の2出力DC/DC変換回路、(b)は単一インダクタ2出力DC/DC変換回路を示している。

【図10】単一インダクタ2出力DC/DC変換回路の原理図で、(a)は、2出力昇圧コンバータの回路構成図、(b)はそのインダクタ電流波形を示している。

【図11】多出力DC/DC変換回路におけるクロスレギュレーションを説明するための図で、(a)はPWM制御方式の場合、(b)はΔΣ変調方式の場合を示している。

【図12】本発明に係るΔΣ変調制御を用いた多出力DC/DC変換回路を備えたスイッチング電源回路を説明するための回路構成図である。

【図13】図12におけるドライブ回路の具体的な回路構成図で、(a)はΔΣ変調回路の出力を受けて各スイッチ操作をする概念図、(b)はドライブ回路の回路構成図、(c)は真理値表を示している。

【図14】図13に示したドライブ回路を介して得られた本発明のスイッチング電源回路の出力のシミュレーション結果を示す図である。

【図15】本発明に係るスイッチング電源回路に用いられる1次フィードフォワード(FF)型ΔΣ変調回路を説明するための図で、(a)は1次フィードフォワード型ΔΣ変調回路の構成ブロック図、(b)は伝達特性を示す図、(c)は信号伝達関数とノイズ伝達関数の関係式を示している。

【図16】図15(a)に示した1次フィードフォワード型(FF型)ΔΣ変調回路の具体的な回路構成図である。

【図17】従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、1次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図である。

【図18】図17(a),(b)に示した出力電圧波形の拡大図である。

【図19】本発明に係るスイッチング電源回路に用いられる2次フィードフォワード(FF)型ΔΣ変調回路を説明するための構成ブロック図である。

【図20】図19に示した2次フィードフォワード型ΔΣ変調回路の具体的な回路構成図である。

【図21】従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、2次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図である。

【図22】図21(a),(b)に示した出力電圧波形の拡大図である。

【発明を実施するための形態】

【0038】

本発明に係るスイッチング電源回路の実施例について説明する前に、まず従来から用いられていたPWM制御によるスイッチング電源回路について以下に説明する。

【0039】

図2(a)乃至(c)は、従来から用いられていたPWM制御によるスイッチング電源回路を説明するための図で、図2(a)はスイッチング電源回路の全体構成図、図2(b)は、ノコギリ波とエラーアンプ(誤差増幅器)の関係を示す図、図2(c)は、PWM回路の出力信号を示す図である。PWM制御は、スイッチング周波数がノコギリ波の周波数で決定され、パルス幅はエラーアンプの出力の大きさにより決定され、パルスの数はスイッチング周波数で決定される。

【0040】

図2(a)において、入力電圧がDC/DC変換回路(DC/DCコンバータ)101に入力されると、入力電圧が昇圧もしくは降圧されて、出力電圧が出力される。その出力電圧がエラーアンプ102に入力され、所望の出力電圧からの誤差に対応する出力信号がPWM回路105に出力される。そして、PWM回路105を構成するコンパレータ103によってノコギリ波発生回路104からのノコギリ波とエラーアンプ102からの出力信号とが比較される。ここで、ノコギリ波とエラーアンプの出力の関係は、例えば、図2(b)のようになる。つまり、スイッチング周期ごとにエラーアンプ102の出力信号は変化し、PWM回路105の出力信号は、図2(c)のような、パルス幅の異なる信号が出力される。ここで、パルス幅はスイッチング電源回路の出力電圧の所望の出力電圧からの誤差に対応する。ドライブ回路106を介して、DC/DC変換回路101でパルス幅に応じたスイッチング動作が行われ、入力電圧を昇圧もしくは降圧した出力電圧が、スイッチング電源回路の出力電圧として得られる。

【0041】

このような構成のスイッチング電源回路を高いスイッチング周波数で動作させた場合には、PWM回路105の出力信号のパルス数が多くなり、スイッチングによる損失(スイッチングロス)が生じて、高効率化は図れないが、高速過渡応答が得られる。これに対して、低いスイッチング周波数で動作させた場合には、PWM回路105の出力信号のパルス数が少なくなり、高効率化は図れるが、高速過渡応答が得られない。このように、従来のPWM制御によるスイッチング電源回路では、高効率化と高速過渡応答とをスイッチング周波数で解決することは困難であった。

【0042】

スイッチング電源回路の要求される高効率化と高速過渡応答についてさらに具体的に動作説明する。

【0043】

図3(a)乃至(c)は、DC/DC変換回路に対する制御回路の動作を説明するための図で、図3(a)は、DC/DC変換回路の一例である昇圧(boost;ブースト)コンバータの回路構成図で、図3(b)は、過渡状態と定常状態における出力電圧の関係を示す図で、図3(c)は、DC/DC変換回路のスイッチング動作を行うためのスイッチング信号を示す図である。

【0044】

まず、図3(a)を参照して、昇圧コンバータの構成と動作を説明する。

昇圧コンバータは、DC/DC変換回路101と制御回路107とで構成されている。制御回路107は、図2(a)におけるエラーアンプ102とPWM回路105とドライブ回路106を含んでいる。また、制御回路107及び入力電圧Vin以外はDC/DC変換回路101を示している。

【0045】

DC/DC変換回路101におけるスイッチS1,S2は、MOSトランジスタ等で構成される。本説明では、スイッチS1,S2はNチャネルMOSトランジスタで構成されているものとする。つまり、スイッチS1,S2はハイレベルの制御信号が入力されると、オン(導通)して、ローレベルの制御信号が入力されると、オフ(遮断)される。また、スイッチS1,S2にはそれぞれ互いに極性が異なるスイッチング信号が制御回路107より与えられる。出力電圧の所望の値からの誤差に対応するPWM信号がスイッチS1に与えられ、反転したPWM信号がスイッチS2に与えられる。

【0046】

PWM信号がハイレベルのとき、スイッチS1はオンし、スイッチS2はオフする。スイッチS1がオンすることで、インダクタLに入力電圧Vinが印加され、インダクタLに充電電流が充電される。

【0047】

次に、PWM信号がローレベルになったとき、スイッチS1はオフし、スイッチS2はオンする。スイッチS2がオンすることで、インダクタLに充電された充電電流が容量Coutに流れ、容量Coutに電荷が蓄えられ、昇圧された出力電圧Voutが出力される。

【0048】

ここで、PWM信号のパルス幅が小さい程、インダクタLに充電される充電電流が小さくなるので、昇圧電圧は低くなる。一方、PWM信号のパルス幅が大きい程、インダクタLに充電される充電電流が大きくなるので、昇圧電圧は高くなる。パルス幅は、出力電圧Voutに応じて決まる。つまり、過渡状態である電源投入直後は、パルス幅が相対的に大きくなり、定常時は、パルス幅が相対的に小さくなる。

【0049】

上述のように、出力電圧Voutから所望の出力電圧の誤差に応じて制御回路107は、誤差に対応したパルス幅のPWM信号を生成して、スイッチS1、S2に出力する。

【0050】

次に、図3(b),(c)を参照して、高効率化と高速過渡応答について以下に説明する。

【0051】

図3(b)は、DC/DC変換回路が昇圧動作を開始して、出力電圧Voutが一定値(所望の出力電圧)に収束するまでの様子を表す図である。出力電圧Voutは、一定値に収束するまでの過渡状態、一定値に収束してからの定常状態の2つの状態がある。図3(c)は、周波数が低いときと、高いときのPWM信号を例示した図である。

【0052】

昇圧コンバータが、昇圧動作を開始して、一定値に収束するまでの過渡状態を短くするためには、周波数が高いPWM信号でスイッチングする必要がある。つまり、周波数が高いほど、スイッチS1,S2におけるスイッチング回数が多くなり、インダクタLから容量Coutへの充電回数が多くなるので、高速で定常状態に収束する。よって、高速で定常状態に収束するためには、PWM信号の周波数を高くすればよい。ところが、PWM信号の周波数を高くすると、スイッチS1,S2での損失が大きくなる。つまり、高効率化が図れなくなる。

【0053】

一方、スイッチS1,S2での損失を小さくし、高効率化を図るためには、PWM信号の周波数を低くする必要がある。すなわち、スイッチS1,S2におけるスイッチング回数を少なくすることで、損失が小さくなる。つまり、高効率化が図れる。

【0054】

ところが、PWM信号の周波数を低くすると、スイッチS1,S2におけるスイッチング回数が少なくなり、インダクタLから容量Coutへの充電回数が少なくなるので、定常状態に収束するまでの時間が長くなる。つまり、過渡状態が長くなる。

【0055】

このように、スイッチング電源回路の高速過渡応答と高効率化はトレードオフの関係にあり、周波数が固定であると、いずれか一方の要求しか達成できない。また、これらの要求に対して、高いスイッチング周波数での動作(高速過渡応答の改善)や低いスイッチング周波数での動作(高効率化の改善)は、周波数を可変にして行なう必要があった。つまり、従来では、高速過渡応答と高効率化をスイッチング周波数のみで解決しており、これでは回路規模増大を招き、大変困難を伴うものであった。そこで、ΔΣ変調方式の採用が検討されてきた。

【0056】

本発明に係るフィードフォワード(FF)型ΔΣ変調回路を用いたDC/DC変換回路を備えたスイッチング電源回路を説明する前に、PWM制御によるDC/DC変換回路とフィードバック(FB)型ΔΣ変調制御によるDC/DC変換回路を用いたスイッチング電源回路について以下に説明する。

【0057】

図4(a),(b)は、PWM制御とFB型ΔΣ変調制御との特徴を比較するための構成ブロック図で、図4(a)は、PWM制御を用いたスイッチング電源回路の構成図、図4(b)は、FB型ΔΣ変調制御を用いたスイッチング電源回路の構成図である。なお、制御回路112は、エラーアンプ102とFB型ΔΣ変調回路111とドライブ回路106を含んでいる。

【0058】

図4(a)において、入力電圧がDC/DC変換回路101に入力されると、その出力電圧がエラーアンプ102とPWM回路105とドライブ回路106を介してPWM制御され、DC/DC変換回路101から出力電圧を得る。このPWM制御の特徴は、上述のように、出力電圧から所望の出力電圧までの誤差に比例して、パルス幅が変化するPWM信号をPWM回路105からドライブ回路106を介してDC/DC変換回路101に出力することである。

【0059】

一方、図4(b)において、入力電圧がDC/DC変換回路101に入力されると、その出力電圧がエラーアンプ102とFB型ΔΣ変調制御回路111とドライブ回路106を介してFB型ΔΣ変調制御され、DC/DC変換回路101から出力電圧を得る。このFB型ΔΣ変調制御の特徴は、出力電圧から所望の出力電圧までの誤差に比例して、パルス密度が変化するパルス密度変調信号(ΔΣ変調信号)をFB型ΔΣ変調回路111からドライブ回路106を介してDC/DC変換回路101に出力することである。

【0060】

次に、フィードバック(FB)型ΔΣ変調制御の特徴について説明する。

【0061】

図5(a),(b)は、FB型ΔΣ変調制御についての説明図で、図5(a)は、FB型ΔΣ変調回路を用いたスイッチング電源回路の制御回路における概略構成ブロック図、図5(b)は、FB型ΔΣ変調回路の出力信号を示す図である。

【0062】

図5(a)において、エラーアンプ102の出力信号はDC/DC変換回路101の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号であり、FB型ΔΣ変調回路111に出力される。そして、FB型ΔΣ変調回路111は、誤差信号の大きさに応じたパルス密度のパルス密度変調信号を出力する。つまり、FB型ΔΣ変調回路111の出力信号は、図5(b)のように示される。FB型ΔΣ変調回路111の入力信号、すなわち、誤差信号が常に小さいとき(定常状態)では、パルス密度が相対的に薄くなり(低いスイッチング周波数)、高効率化が図れる。一方、FB型ΔΣ変調回路111の入力信号が常に大きいとき(過渡状態)では、パルス密度が相対的に濃くなり(高いスイッチング周波数)、高速過渡応答が図れる。

【0063】

次に、フィードバック(FB)型ΔΣ変調回路111の回路構成とその入出力特性について以下に説明する。

【0064】

図6(a)乃至(c)は、FB型ΔΣ変調回路の回路構成とその入出力特性を示す図で、図6(a)はFB型ΔΣ変調回路の回路構成図、図6(b)は、入力信号に対する出力信号を示す図、図6(c)は、積分器出力を示す図である。

【0065】

まず、図6(a)を参照して、FB型ΔΣ変調回路111の回路構成について説明する。

【0066】

FB型ΔΣ変調回路111は、減算器121と積分器122と量子化器(A/Dコンバータ;ADC)123とDAC(D/Aコンバータ)124とから構成されている。

【0067】

FB型ΔΣ変調回路111は、スイッチを含み入力信号と出力信号をD/A変換した信号との差分をとる減算器121と、スイッチ、容量、演算増幅器を含み、差分を積分した差分積分信号を出力する積分器122と、コンパレータ、フリップフロップを含み、量子化基準信号(しきい値)とで差分積分信号の信号レベルを大小比較し1ビットの量子化信号を出力する量子化器123と、2つの基準信号Vref、−Vrefを選択する2つのスイッチを含み、量子化信号である出力信号を帰還して1ビットの量子化信号に同期して、出力信号の論理値に応じた基準信号をスイッチにより選択し、出力信号をD/A変換した信号を生成するDAC124を備える構成とすることで、パルス密度変調信号を生成する。

【0068】

また、このような構成により、FB型ΔΣ変調回路111を備えたスイッチング電源回路は、従来のPWM回路を備えたスイッチング電源回路と比べて、サンプリング周波数が固定であるので、回路規模が小さくできるとともに、高速過渡応答と高効率化を可能としている。

【0069】

FB型ΔΣ変調回路111は、スイッチをオンオフし、電荷を転送するための2つのフェーズ、Ph1(フェーズ1)とPh2(フェーズ2)がある。図6(a)において、Ph1と図示したスイッチは、Ph1においてオンし、Ph2と図示したスイッチは、Ph2においてオンする。各フェーズの周波数は、サンプリング周波数に等しく、Ph1とPh2は、交互に繰り返される。つまり、一つのサンプリング周期において、一つのPh1と一つのPh2が存在する。

【0070】

次に、図6(b)、(c)を参照して、FB型ΔΣ変調回路111の動作を説明する。

【0071】

まず、FB型ΔΣ変調回路111は、上述のように、エラーアンプ102が出力するDC/DC変換回路101の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号を入力する。

【0072】

Ph1において、入力信号が積分器122の入力側容量に印加され、入力信号に応じた電荷が蓄えられる。Ph2において、DAC124の出力信号が積分器122の入力側容量に印加され、DAC124の出力信号に応じた電荷が転送される。ここで、減算器121は、入力側とDAC124の出力は結線されているので、Ph1で入力信号により蓄えた電荷から、Ph2でDAC124の出力信号に応じた電荷を減算した電荷が、積分器122の入力側容量に蓄えられる。つまり、FB型ΔΣ変調回路111の入力信号と出力信号との減算が行われ、差分信号が生成される。

【0073】

積分器122の入力側容量の電荷は、Ph2において、演算増幅器の出力端子から非反転入力端子との間の帰還容量に転送される。つまり、差分信号が積分され、差分積分信号が出力される。

【0074】

図6(b)は、FB型ΔΣ変調回路111の入力信号と出力信号を例示した波形で、図6(c)は、差分積分信号を例示した波形である。また、入力信号が0より小さいときの波形を表している。まず、図6(b)に示す様に、最初のサンプリング周期において、出力信号は、ローレベルであり、その出力信号に対応するDAC124の出力信号は、−Vrefであり、入力信号との差分は正の値となる。よって、図6(c)に示す様に、差分積分信号は、正の傾きをもつ一次関数波形となる。

【0075】

次に、差分積分信号は、量子化器123のコンパレータに入力され、量子化基準信号と差分積分信号が大小比較されて、フリップフロップに入力される。図6(a)において、量子化基準信号は、0V(グラウンド)である。そして、Ph1になったとき、フリップフロップは、差分積分信号と量子化基準信号(しきい値)との大小比較結果を1ビットの量子化信号として出力する。つまり、量子化器123は、差分積分信号が0V以上のとき、ハイレベルを出力し、0Vより小さいとき、ローレベルを出力する。図6(c)において、最初のサンプリング周期の最後の時点で、差分積分信号は、量子化基準信号と等しくなるので、コンパレータはハイレベルを出力し、次のサンプリング周期(次のPh1)になったとき、量子化器123は、ハイレベルの量子化信号を出力する。

【0076】

量子化信号は、DAC124のスイッチに入力される。DAC124において、量子化信号がハイレベルのとき、基準信号Vrefが選択され、量子化信号がローレベルのとき、基準信号−Vrefが選択される。

【0077】

そして、次のサンプリング周期において、量子化信号は、ハイレベルであるので、入力信号との差分は負の値となる。よって、図6(c)に示す様に、差分積分信号は、負の傾きをもつ一次関数波形となる。

【0078】

したがって、量子化器123におけるコンパレータの出力はローレベルとなり、さらに次のサンプリング周期になったとき、量子化信号はローレベルとなる。

【0079】

このような動作を繰り返すことで、入力信号に応じたパルス密度変調信号が生成される。図6(b)に例示した波形において、7サンプリング周期に3つのパルスが存在する。FB型ΔΣ変調回路111の入力信号が図示した値よりも小さくなる(誤差が大きくなる)と、パルス密度は濃くなり(パルスの数が増え)、図示した値よりも大きくなる(誤差が小さくなる)と、パルス密度は薄くなる(パルスの数が減る)。

【0080】

また、上述した動作により、入力信号が0Vより小さいとき、パルス密度変調信号は、一回ハイレベルになった後、必ずローレベルになる。このとき、ハイレベルの期間は、サンプリング周期であり固定である。一方、入力信号が0Vより大きいとき、パルス密度変調信号は、一回ローレベルになった後、必ずハイレベルになる。このとき、ローレベルの期間は、サンプリング周期であり固定である。

【0081】

このようにして、FB型ΔΣ変調回路111を備えたスイッチング電源回路は、従来のPWM回路を備えたスイッチング電源回路と比べて、回路規模が小さくなるとともに、高速過渡応答と高効率化を可能としている。

以上が、FB型ΔΣ変調回路111の動作説明である。

【0082】

図7(a)乃至(c)は、FB型ΔΣAD変調回路の構成ブロック図と伝達特性を説明するための図で、図7(a)は、FB型ΔΣAD変調回路のブロック図、図7(b)は、伝達特性を示す図、図7(c)は、信号伝達関数(STF;Signal Transfer Function)とノイズ伝達関数(NTF;Noise Transfer Function)の関係式を示している。

【0083】

図7(a)に示すように、低い周波数の信号を通過させる積分器(LPF)122と、量子化器(ADC;アナログ/デジタル変換回路)123と、DAC(デジタル/アナログ変換回路)124と、アナログ信号を減算して出力する減算器121とを備えている。

【0084】

減算器121の出力は、積分器122に入力され、積分器122の出力は、量子化器123に入力されている。また、DAC124は、量子化器123の出力をアナログ信号に変換して積分器122にフィードバックするように、量子化器123と減算器121との間に設けられている。減算器121は、FB型ΔΣAD変調器の入力信号から、DAC124の出力を減算して出力する。すなわち、図7(a)の積分器122、量子化器123、DAC124、減算器121はそれぞれ、図6(a)の積分器122、量子化器123、DAC124、減算器121に対応する。

【0085】

次に、FB型ΔΣAD変調回路の動作について説明する。まず、アナログ信号が入力されると、積分器122によって、低い周波数のアナログ信号が出力され、量子化器123によって、積分器122から出力されたアナログ信号がデジタル信号に変換され、減算器121で入力信号との差分をとるために、フィードバックするために、デジタル信号がDAC124に入力される。

【0086】

DAC124では、入力された量子化器123の出力を、アナログ信号に変換して、減算器121に入力し、入力となるアナログ信号から、DAC124の出力を減算して、積分器122にフィードバックする。そして、積分器122の出力が、量子化器123によってデジタル信号に変換されて、FB型ΔΣAD変調器の出力としてデジタル信号(パルス密度変調信号)が出力される。

【0087】

なお、FB型ΔΣ変調回路の出力信号により、図4(b)に示したDC/DC変換回路101でスイッチング動作を行ったときのDC/DC変換回路101の出力電圧波形は図17(a)に示され、その拡大図は図18(a)に示されている。

【0088】

FB型ΔΣ変調回路は、積分器の出力を量子化器で量子化するため、量子化器において量子化ノイズE(Z)が加わる。すなわち、図7(a)の入力から出力までの伝達特性は、図7(b)に示すようになる。図7(b)より伝達関数を求めると、図7(c)のようになる。

【0089】

図7(c)に示すように、Z変換した出力デジタル信号Y(Z)は、Y(Z)=H(Z)・X(Z)/(1+H(Z))+1・E(Z)/(1+H(Z))となる。信号伝達関数STF(Signal Transfer Function)は、STF(Z)=H(Z)/(1+H(Z))であり、ノイズ伝達関数NTF(Noise Transfer Function)は、NTF(Z)=1/(1+H(Z))である。なお、X(Z)はZ変換した入力アナログ信号であり、H(Z)は積分器の伝達関数である。

【0090】

また、オーバーサンプリングとノイズ伝達関数により量子化ノイズE(Z)はノイズシャイプされ高SNDR(Signal to Noise plus Distortion Ratio;信号対雑音+歪電力比)を実現する。

【0091】

しかしながら、積分器122の伝達関数は、1次の場合には、H(Z)=Z-1/(1−Z-1)であるので、信号伝達関数は、STF(Z)=Z-1となって1クロック(1サンプリング周期)遅れる。また、ノイズ伝達関数は、NTF(Z)=1−Z-1となり、1次の微分特性となる。

【0092】

ここで示されているフィルタ回路の次数は1次である。フィルタの次数は、その伝達関数の遅延演算子Z-1の最大のべき数である。

【0093】

図8は、2次フィードバック型ΔΣ変調回路を説明するための構成ブロック図である。減算器131の出力は、1段目の積分器132に入力され、1段目の積分器132の出力は、減算器133及び2段目の積分器134を介して量子化器135に入力されている。また、DAC136は、量子化器135の出力をアナログ信号に変換して2段目の積分器134にフィードバックするとともに、DAC137は、量子化器135の出力をアナログ信号に変換して1段目の積分器132にフィードバックする。減算器131は、ΔΣAD変調回路の入力となるアナログ信号から、DAC137の出力を減算して出力し、減算器133は、ΔΣAD変調回路の入力となるアナログ信号から、DAC136の出力を減算して出力する。

【0094】

1段目の積分器132の出力をZ変換すると、y1(Z)=Z-1X(Z)+Z-1(1−Z-1)E(Z)で示される。また、量子化器135の出力をZ変換すると、Y(Z)=Z-1X(Z)+(1−Z-1)2E(Z)で示される。

【0095】

すなわち、2次フィードバック型ΔΣ変調回路の信号伝達関数は、STF(Z)=Z-1であり、1クロック(1サンプリング周期)遅れる。ノイズ伝達関数は、NTF(Z)=(1−Z-1)2となり、2次の微分特性となる。

【0096】

以上、本発明に係るフィードフォワード型ΔΣ変調回路を用いたスイッチング電源回路を説明する前に、従来から用いられていたPWM回路を用いたスイッチング電源回路及び従来から用いられていたフィードバック型ΔΣ変調回路を用いたスイッチング電源回路について説明した。

【0097】

図9(a),(b)は、単一インダクタ2出力DC/DC変換回路を説明するための図で、図9(a)は、従来の2出力DC/DC変換回路、図9(b)は、単一インダクタ2出力DC/DC変換回路を示している。

【0098】

従来の2出力DC/DC変換回路141a,141bは、インダクタLが2個必要であり、サイズもコストも大きい。これに対して、単一インダクタ2出力DC/DC変換回路142は、インダクタLが1個であり、サイズもコストも小さい。

【0099】

図9(a)に示すように、電子機器における各電子部品は、駆動するための電源電圧が異なるので、単一のバッテリーで電力を供給するためには、単一のバッテリーの電圧から各電子部品を駆動するための電源電圧を生成するDC/DC変換回路が、電子部品ごとに必要となる。ところが、電子部品ごとにDC/DC変換回路を用意することは、部品数の増加を招くという問題がある。そこで、電子部品ごとにDC/DC変換回路を用意するのではなく、図9(b)に示すように、インダクタを共有化、つまり、単一のインダクタで構成し、複数の電源電圧を生成する多出力電源装置が必要になる。つまり、単一インダクタ多出力(SI−SIMO(Single Inductor−Single Input, Multiple Output)DC/DC変換回路が有用である。

【0100】

図10(a),(b)は、単一インダクタ2出力DC/DC変換回路の原理図で、図10(a)は、2出力昇圧コンバータの回路構成図、図10(b)は、そのインダクタ電流波形を示している。

【0101】

まず、図10(a)に示した2出力昇圧コンバータの構成を説明する。

図10(a)に示した2出力昇圧コンバータは、インダクタLとスイッチS1〜S3と容量C1,C2と負荷抵抗R1,R2とを備えている。インダクタLの一端には、入力電圧Vinが与えられ、インダクタの他端はスイッチS1〜S3の一端に共通接続される。スイッチS1の他端は、グラウンドに接地されている。スイッチS2は、容量C1と抵抗R1の一端に接続され、2出力のうち第1の出力電圧Vout1が得られる。スイッチS3の他端は、容量C2と抵抗R2の一端に接続され、2出力のうち第2の出力電圧Vout2が得られる。そして、容量C1,C2と抵抗R1,R2の他端は、それぞれグラウンドに接地されている。

【0102】

次に、図10(a)に示した2出力昇圧コンバータの動作を説明する。

2出力昇圧コンバータは、2つの出力電圧Vout1,Vout2を得るために、容量C1,C2に電荷を充電する期間を2つ設けて、インダクタを時分割して利用することで、充電を行う。すなわち、2つの期間のうち1つ目の期間(第1の期間)では、第1の出力電圧Vout1を得るための昇圧動作を行い、2つの期間のうち2つ目の期間(第2の期間)では、第2の出力電圧Vout2を得るための昇圧動作を行う。

【0103】

まず、第1の期間において、スイッチS3はオフし、スイッチS1,S2のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS2がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS2がオンして、インダクタLに充電された充電電流が容量C1に放電され、容量C1は充電される。そして、第1の出力電圧Vout1が得られる。

【0104】

次に、第2の期間において、スイッチS2はオフし、スイッチS1,S3のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS3がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS3がオンして、インダクタLに充電された充電電流が容量C2に放電され、容量C2は充電される。そして、第2の出力電圧Vout2が得られる。

【0105】

このときのインダクタLに流れる充電電流ILの波形を図10(b)に例示する。例示した波形は、スイッチS1〜S3をPWM信号によりスイッチング動作を行ったときの波形であり、安定した定常状態における波形である。このような回路によってインダクタを時分割して利用することで、2つの出力を得ることができる。

【0106】

図11(a),(b)は、多出力DC/DC変換回路におけるクロスレギュレーションの影響を説明するための図で、図11(a)は、PWM制御方式の場合、図11(b)は、ΔΣ変調方式の場合を示している。

【0107】

多出力電源において、片方の出力で負荷変動が生じると、他方の出力電圧が変動する現象をクロスレギュレーションという。つまり、複数の出力を取り出す場合、ある出力が他の出力に与える影響である。例えば、PWM制御を使うフライバック方式のコンバータの場合、軽負荷時には1次側FETのオン期間の幅を狭めて出力を制御する。そのため、2次巻き線に電圧が発生する期間も短くなる。複数の2次巻き線から巻き数に応じた異なる電圧を取り出す場合、電圧制御を行っている出力の負荷に応じて他の出力電圧が大きく変動してしまう。2次側にレギュレータ回路を追加すれば、システム全体としてのクロスレギュレーション特性の改善が可能だが、部品点数が増えるのでコストが上がってしまうという問題がある。

【0108】

また、図10(a)に示す非絶縁型の2出力DC/DCコンバータについても、同様に、片方の出力で負荷変動が生じると、スイッチに与えるPWM信号のパルス幅が変動する。例えば、第1の出力電圧側の負荷が重負荷になったとき、第1の期間において、スイッチS1,S2に与えられるPWM信号のパルス幅は大きくなる。すなわち、インダクタに充電される充電電流ILは大きくなる。そして、充電電流ILが容量C1に全て放電される前に、第2の期間に移行するため、第2の期間において、放電されなかった充電電流ILが容量C2に一部充電され、第2の出力電圧Vout2に変動が生じるという問題がある。

【0109】

第1の出力電圧Vout1側の負荷が重負荷になり、第2の出力電圧Vout2が定常状態のときのクロスレギュレーションの様子を図11(a),(b)に示す。

【0110】

図11(a)に示すように、PWM制御方式の場合には、図10(a)に示したS1からS3のスイッチ操作に対してVout1とVout2とのクロスレギュレーションが大である。これに対して、図11(b)に示すように、ΔΣ変調方式の場合には、Vout1とVout2とのクロスレギュレーションが小である。したがって、この種のクロスレギュレーションを良好にするためには、ΔΣ変調方式を用いることが有効であることが分かる。

【0111】

以下、図面を参照して本発明の実施例について説明する。

図12は、本発明に係るΔΣ変調制御を用いた単一インダクタ2出力DC/DC変換回路を備えたスイッチング電源回路を説明するための回路構成図で、ΔΣ変調制御を2出力昇圧コンバータに適用した場合の回路構成図である。

【0112】

図中符号150は単一インダクタ2出力DC/DC変換回路(デュアル昇圧コンバータ)、151は第1のエラーアンプ(誤差増幅器)、152は第2のエラーアンプ(誤差増幅器)、153は第1のΔΣ変調回路、154は第2のΔΣ変調回路、155はドライブ回路を示している。なお、2出力昇圧コンバータ150については、図10(a)に示した2出力昇圧コンバータと同様である。

【0113】

本発明に係るスイッチング電源回路は、単一インダクタ2出力DC/DC変換回路150と、第1出力を入力する第1のエラーアンプ151と、この第1のエラーアンプ151に接続された第1のΔΣ変調回路153と、第2出力を入力する第2のエラーアンプ152と、この第2のエラーアンプ152に接続された第2のΔΣ変調回路154と、第1のΔΣ変調回路153の出力と第2のΔΣ変調回路154の出力が接続されたドライバ回路155とから構成されている。

【0114】

つまり、本発明に係るスイッチング電源回路は、ΔΣ変調制御を用いた単一インダクタ2出力DC/DC変換回路150を備えたもので、入力信号を2つの出力信号に変換する単一インダクタ2出力DC/DC変換回路150と、この単一インダクタ2出力DC/DC変換回路150に接続されて出力信号をΔΣ変調制御する2つのΔΣ変調回路153,154とを備えている。

【0115】

入力電圧が単一インダクタ2出力DC/DC変換回路150に入力されると、その出力電圧が第1及び第2のエラーアンプ151,152と第1及び第2のΔΣ変調回路153,154とドライブ回路155を介してΔΣ変調制御され、単一インダクタ2出力DC/DC変換回路150から出力電圧を得る。このΔΣ変調制御の特徴は、パルス密度変調信号が、出力信号の所望の電圧からの誤差に比例してパルス密度が変化することである。

【0116】

図12に示した本発明のスイッチング電源回路の動作を以下に説明する。

本発明のスイッチング電源回路は、2つの出力電圧Vout1,Vout2を得るために、容量Cout1,Cout2に電荷を充電する期間を2つ設けて、インダクタを時分割して利用することで、充電を行う。すなわち、2つの期間のうち1つ目の期間(第1の期間)では、第1の出力電圧Vout1を得るための昇圧動作を行い、2つの期間のうち2つ目の期間(第2の期間)では、第2の出力電圧Vout2を得るための昇圧動作を行う。

【0117】

まず、第1の期間において、スイッチS3はオフし、スイッチS1,S2のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS2がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS2がオンして、インダクタLに充電された充電電流が容量Cout1に放電され、容量Cout1は充電される。そして、インダクタLの充放電の動作を1つの期間の間、繰り返すことで、第1の出力電圧Vout1が得られる。つまり、1つの期間の間、複数のパルスがスイッチS1,S2に入力されて、昇圧動作が行われる。

【0118】

次に、第2の期間において、スイッチS2はオフし、スイッチS1,S3のオンオフで昇圧動作を行う。最初にスイッチS1がオンし、スイッチS3がオフして、インダクタLに充電電流が充電される。次に、スイッチS1がオフし、スイッチS3がオンして、インダクタLに充電された充電電流が容量Cout2に放電され、容量Cout2は充電される。そして、インダクタLに充電された充電電流が容量Cout2に放電され、第2の出力電圧Vout2が得られる。つまり、1つの期間の間、複数のパルスがスイッチS1,S2に入力されて、昇圧動作が行われる。

【0119】

このときの第1及び第2の期間におけるインダクタLに流れる充電電流ILの波形、スイッチS1〜S3に与えられるパルス密度変調信号の波形を図11(b)に例示する。例示した波形は、スイッチS1〜S3をパルス密度変調信号によりスイッチング動作を行ったときの波形であり、第1の出力が重負荷になり、第2の出力が定常状態における波形である。

【0120】

図11(b)に示すように、第1の期間において、重負荷であるので、スイッチS1,S2のパルス密度は濃くなり、昇圧される。第2の期間において、第1の期間の残留した充電電流ILが第2出力にクロスレギュレーションされ、余分に容量Cout2に充電が行われるが、本発明のスイッチング電源回路は、ΔΣ変調制御であり、パルス密度変調信号によりスイッチングを行っているため、第2の出力電圧Vout2がクロスレギュレーションにより変動してもすぐに、パルス密度を調整して、所定の電圧にすることができる。

【0121】

つまり、PWM制御の場合、第1出力において負荷変動が生じ、第2出力が定常状態のとき、1つの期間において1つのパルスしかないので、クロスレギュレーションの影響に対して、パルス幅を調整して所定の電圧にするのに、次の第2の期間まで待たなければならないので、クロスレギュレーションの影響が大きくなる。それに対して、ΔΣ制御の場合、パルス密度、すなわち、一定期間におけるパルスの数で出力電圧を制御するので、変動が生じても、次の第2の期間を待たずに、その変動量に応じてパルス密度を調整することができる。図11(b)では、第2の期間において、第2の出力電圧Vout2の変動に応じてパルス密度が薄くなる様子を示している。したがって、本発明のスイッチング電源回路は、クロスレギュレーションの影響が小さくすることができる。

【0122】

以上が、本発明のスイッチング電源回路の動作説明である。なお、S2とS3が同時にオンすると、出力電圧が短絡してしまうのでドライブ回路155の構成は注意が必要である。

【0123】

図13(a)乃至(c)は、図12におけるドライブ回路の具体的な回路構成図で、図13(a)は、ΔΣ変調回路の出力を受けて各スイッチ操作をする概念図、図13(b)は、ドライブ回路の回路構成図、図13(c)は、真理値表を示している。

【0124】

ドライブ回路は、第1のΔΣ変調回路153の出力信号MO1、第2のΔΣ変調回路154の出力信号MO2、選択信号SELを入力し、スイッチS1〜S3にパルス密度変調信号を出力する。選択信号SELは、第1の期間、第2の期間を決める信号である。第1の期間は、論理値が0(ローレベル)のときで、第2の期間は、論理値が1(ハイレベル)のときである。

【0125】

選択信号SELが0のとき、第1のΔΣ変調回路153の出力信号MO1はイネーブルされ、第2のΔΣ変調回路154の出力信号MO2はディスイネーブルされる。そして、スイッチS1には、第1のΔΣ変調回路153の出力信号MO1が出力され、スイッチS2には、第1のΔΣ変調回路153の出力信号MO1を反転した信号が出力され、スイッチS3には、0が出力される。

【0126】

選択信号SELが1のとき、第1のΔΣ変調回路153の出力信号MO1はディスイネーブルされ、第2のΔΣ変調回路154の出力信号MO2はイネーブルされる。そして、スイッチS1には、第2のΔΣ変調回路154の出力信号MO2が出力され、スイッチS2には、0が出力され、スイッチS3には、第2のΔΣ変調回路154の出力信号MO2を反転した信号が出力される。

【0127】

このようにして、S2とS3が同時にオンすることなく、第1のΔΣ変調回路153の出力信号MO1と第1のΔΣ変調回路154の出力信号MO2とを時分割して、スイッチS1〜S3に与えることができる。

【0128】

このように、位相差を持ったサンプリング周波数のパルス(選択信号SEL)により、Vout1とVout2の制御を行う。なお、図14は、図13(b)に示したドライブ回路を介して得られた本発明のスイッチング電源回路の出力のシミュレーション結果を示す図である。

【0129】

以上は、単一インダクタ2出力DC/DC変換回路を用いた場合について説明したが、単一インダクタ多出力DC/DC変換回路を用いることも可能である。つまり、単一インダクタ多出力DC/DC変換回路として、単一インダクタn出力DC/DC変換回路を用いる場合には、この単一インダクタn出力DC/DC変換回路の出力電圧に対応する分圧電圧との差分を増幅した誤差信号をn個のΔΣ変調回路に出力するn個のエラーアンプと、n個のΔΣ変調回路より出力されたパルス密度変調信号が入力されるドライブ回路が必要になる。

【0130】

以下に、本発明に用いられるΔΣ変調回路として、1次フィードフォワード(FF)型ΔΣ変調回路及び2次フィードフォワード(FF)型ΔΣ変調回路について説明する。

【0131】

図15(a)乃至(c)は、本発明に係るスイッチング電源回路に用いられる1次フィードフォワード(FF)型ΔΣ変調回路を説明するための図で、図15(a)は、1次フィードフォワード型ΔΣ変調回路の構成ブロック図、図15(b)は、伝達特性を示す図、図15(c)は、信号伝達関数(STF;Signal Transfer Function)とノイズ伝達関数(NTF;Noise Transfer Function)の関係式を示している。

【0132】

図15(a)に示すように、特定の周波数のアナログ信号を通過させる積分器(LPF)162と加算器163とADC(アナログ/デジタル変換回路)164とDAC(デジタル/アナログ変換回路)165とアナログ信号を減算して出力する減算器161とを備えている。

【0133】

つまり、図15(a)に示すように、フィードフォワード型ΔΣ変調回路は、特定の周波数の入力アナログ信号を通過させる積分器162と、この積分器162に接続された加算器163と、この加算器163に接続された量子化器(ADC;アナログ/デジタル変換回路)164と、この量子化器164に接続され、この量子化器164のデジタル信号をアナログ信号に変換して積分器162にフィードバックするDAC(デジタル/アナログ変換回路)165と、入力アナログ信号からDAC165から出力されたアナログ信号を減算する減算器161と、入力アナログ信号を直接加算器163に入力させるフィードフォワードパスaとを備えている。

【0134】

FF型ΔΣ変調回路は、積分器162の出力を量子化器で量子化するため、量子化器において量子化ノイズE(Z)が加わる。すなわち、図15(a)の入力から出力までの伝達特性は、図15(b)に示すようになる。図15(b)より伝達関数を求めると、図15(c)のようになる。

【0135】

図15(c)に示すように、Z変換した出力デジタル信号Y(Z)は、Y(Z)=X(Z)+1・E(Z)/(1+H(Z))となり、積分器の伝達関数H(Z)は、1次の場合には、H(Z)=Z-1/(1−Z-1)であるので、信号伝達関数は、STF(Z)=1となり、パルス密度変調信号は遅延しない。また、ノイズ伝達関数は、NTF(Z)=1−Z-1となり、1次の微分特性となる。つまり、図7(c)に示した信号伝達関数は、STF(Z)=Z-1となり1クロック(1サンプリング周期)遅れるのに対して、図15(c)に示した信号伝達関数は、STF(Z)=1となり、パルス密度変調信号は遅延しない。つまり、FB型ΔΣAD変調回路よりもFF型ΔΣ変調回路の方が、パルス密度変調信号に遅延が生じないので、応答速度が改善されていることが分かる。

【0136】

つまり、フィードフォワード型ΔΣ変調回路の信号伝達関数が1であり、このフィードフォワード型ΔΣ変調回路より出力されるパルス密度変調信号に遅延がなく、該遅延に起因する出力電圧波形のリップルが低減されるという効果を奏する。

【0137】

図16は、図15(a)に示した1次フィードフォワード型(FF型)ΔΣ変調回路の具体的な回路構成図である。

【0138】

1次FF型ΔΣ変調回路は、減算器161と積分器162と加算器163と量子化器(A/Dコンバータ;ADC)164とDAC(D/Aコンバータ)165とから構成されている。

【0139】

1次FF型ΔΣ変調回路は、第1のスイッチを含み入力信号と出力信号をD/A変換した信号との差分をとる減算器161と、第2のスイッチと容量と第1の演算増幅器を備え、差分を積分した差分積分信号を出力する積分器162と、入力信号がフィードフォワードパスaより入力される第1の抵抗と積分器162の出力が入力される第2の抵抗と第2の演算増幅器と帰還抵抗とを備えた加算器163と、コンパレータとフリップフロップとを備え、量子化基準信号(しきい値)と加算器163の信号レベルを大小比較し1ビットの量子化信号を出力する量子化器164と、2つの基準信号Vref、−Vrefを選択する2つの第3のスイッチを備え、量子化信号である出力信号を帰還して1ビットの量子化信号に同期して、出力信号の論理値に応じた基準信号を第3のスイッチにより選択し、出力信号をD/A変換した信号を生成するDAC165を備える構成とすることで、パルス密度変調信号を生成する。

【0140】

1次FF型ΔΣ変調回路は、FB型ΔΣ変調回路の場合と同様に、スイッチをオンオフし、電荷を転送するための2つのフェーズ、Ph1(フェーズ1)とPh2(フェーズ2)がある。図16において、Ph1と図示したスイッチは、Ph1においてオンし、Ph2と図示したスイッチは、Ph2においてオンする。各フェーズの周波数は、サンプリング周波数に等しく、Ph1とPh2は、交互に繰り返される。つまり、一つのサンプリング周期において、一つのPh1と一つのPh2が存在する。

【0141】

まず、1次FF型ΔΣ変調回路は、上述のように、エラーアンプ151,152が出力するDC/DC変換回路150の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号を入力する。

【0142】

Ph1において、入力信号が積分器162の入力側容量に印加され、入力信号に応じた電荷が蓄えられる。また、フィードフォワードパスaにより直接加算器163に入力される。

【0143】

Ph2において、DAC165の出力信号が積分器162の入力側容量に印加され、DAC165の出力信号に応じた電荷が転送される。ここで、減算器161は、入力側とDAC165の出力が結線されているので、Ph1で入力信号により蓄えた電荷から、Ph2でDAC165の出力信号に応じた電荷を減算した電荷が、積分器162の入力側容量に蓄えられる。つまり、1次FF型ΔΣ変調回路の入力信号と出力信号との減算が行われ、差分信号が生成される。

【0144】

積分器162の入力側容量の電荷は、Ph2において、演算増幅器の出力端子から非反転入力端子との間の帰還容量に転送される。つまり、差分信号が積分され、差分積分信号が出力される。次に、差分積分信号は、加算器163において、フィードフォワードパスより伝達された入力信号と加算されて、加算信号が出力される。

【0145】

そして、加算信号は、量子化器164のコンパレータに入力され、量子化基準信号と加算信号が大小比較されて、フリップフロップに出力される。ここで、量子化基準信号は、0V(グラウンド)である。そして、Ph1になったとき、フリップフロップは、差分積分信号と量子化基準信号(しきい値)との大小比較結果を1ビットの量子化信号として出力する。つまり、量子化器164は、差分積分信号が0V以上のとき、ハイレベルを出力し、0Vより小さいとき、ローレベルを出力する。

【0146】

量子化信号は、DAC165のスイッチに入力される。DAC165において、量子化信号がハイレベルのとき、基準信号Vrefが選択され、量子化信号がローレベルのとき、基準信号−Vrefが選択される。そして、次のサンプリング周期において、量子化信号をD/A変換した信号は、入力信号から減算器161により減算される。

【0147】

このような動作を繰り返すことで、入力信号に応じたパルス密度変調信号が生成される。1次FF型ΔΣ変調回路の入力信号が小さくなる(誤差が大きくなる)と、パルス密度は濃くなり(パルスの数が増え)、大きくなる(誤差が小さくなる)と、パルス密度は薄くなる(パルスの数が減る)。

【0148】

また、上述した動作により、入力信号が0Vより小さいとき、パルス密度変調信号は、1回ハイレベルになった後、必ずローレベルになる。このとき、ハイレベルの期間は、サンプリング周期であり固定である。一方、入力信号が0Vより大きいとき、パルス密度変調信号は、1回ローレベルになった後、必ずハイレベルになる。このとき、ローレベルの期間は、サンプリング周期であり固定である。

以上が、1次FF型ΔΣ変調回路の動作説明である。

【0149】

FF型ΔΣ変調回路を用いたスイッチング電源回路は、上述のように、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、さらなる早い応答速度を実現することができる。

【0150】

さらに、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、スイッチング電源回路において遅延に起因する発振ループが形成されず、リップルが小さくなるという効果を奏する。

【0151】

つまり、エラーアンプの出力信号に対応し、スイッチング電源回路の所望の出力電圧からの誤差が0になるような量子化信号、すなわち、パルス密度信号が遅延することなくDC/DC変換回路(電圧コンバータ部)に反映されるので、量子化信号が反映されるまでの間、DC/DC変換回路が余分に昇圧もしくは降圧することがない。したがって、所望の出力電圧からの誤差が小さくなる。つまり、遅延に起因する誤差がエラーアンプに伝達されない。結果、スイッチング電源回路の出力信号にリップルは小さくなる。

【0152】

図17(a),(b)は、従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、1次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図で、図18(a),(b)は、その拡大図である。図18(a)に示したFB型ΔΣ変調回路の出力電圧波形のリップル(ripple;脈動成分)が大きいのに対して、図18(b)に示した1次FF型ΔΣ変調回路の出力電圧波形のリップルが小さいことがわかる。

【0153】

図19は、本発明に係るスイッチング電源回路に用いられる2次フィードフォワード(FF)型ΔΣ変調回路を説明するための構成ブロック図である。特定の周波数のアナログ信号を通過させる1段目の積分器172と2段目の積分器173と加算器174と量子化器(ADC)175とDAC176とアナログ信号を減算して出力する減算器171とを備えている。

【0154】

つまり、2次フィードフォワード型ΔΣ変調回路は、低い周波数の入力アナログ信号を通過させる1段目の積分器172と、この1段目の積分器172に接続された2段目の積分器173と、この2段目の積分器173に接続された加算器174と、この加算器174に接続された量子化器(ADC;アナログ/デジタル変換回路)175と、この量子化器175に接続され、この量子化器175のデジタル信号をアナログ信号に変換して1段目の積分器172にフィードバックするDAC(デジタル/アナログ変換回路)176と、入力アナログ信号からDAC176より出力されたアナログ信号を減算する減算器171と、入力アナログ信号を直接加算器174に入力させる第1のフィードフォワードパスaと、1段目の積分器172からの出力信号を加算器174に直接入力する第2のフィードフォワードパスbとを備えている。

【0155】

1段目の積分器172をZ変換した出力は、y1(Z)=Z-1(1−Z-1)E(Z)で示される。また、量子化器175をZ変換した出力は、Y(Z)=X(Z)+(1−Z-1)2E(Z)で示される。つまり、信号伝達関数は、STF(Z)=1で遅延がなく、ノイズ伝達関数は、NTF(Z)=(1−Z-1)2で2次の微分特性である。

【0156】

図20は、図19に示した2次フィードフォワード型ΔΣ変調回路の具体的な回路構成図である。

【0157】

2次FF型ΔΣ変調回路は、減算器171と積分器172と積分器173と加算器174と量子化器(A/Dコンバータ;ADC)175とDAC(D/Aコンバータ)176とから構成されている。

【0158】

2次FF型ΔΣ変調回路は、第1のスイッチを含み入力信号と出力信号をD/A変換した信号との差分をとる減算器171と、第2のスイッチと第1の容量と第1の演算増幅器とを備え、差分を積分した差分積分信号を出力する積分器172と、第3のスイッチと第2の容量と第3の演算増幅器とを備え、積分器172の出力を積分する積分器173と、入力信号がフィードフォワードパスaより入力される第1の抵抗と積分器172の出力がフィードフォワードパスbより入力される第2の抵抗と積分器173の出力が入力される第3の抵抗と第3の演算増幅器と帰還抵抗とを備えた加算器174と、コンパレータとフリップフロップとを備え、量子化基準信号(しきい値)と加算器174の信号レベルを大小比較し1ビットの量子化信号を出力する量子化器175と、2つの基準信号Vref、−Vrefを選択する2つの第4のスイッチを備え、量子化信号である出力信号を帰還して1ビットの量子化信号に同期して、出力信号の論理値に応じた基準信号を第4のスイッチにより選択し、出力信号をD/A変換した信号を生成するDAC176を備える構成とすることで、パルス密度変調信号を生成する。

【0159】

2次FF型ΔΣ変調回路は、1次FF型ΔΣ変調回路の場合と同様に、スイッチをオンオフし、電荷を転送するための2つのフェーズ、Ph1(フェーズ1)とPh2(フェーズ2)がある。図20において、Ph1と図示したスイッチは、Ph1においてオンし、Ph2と図示したスイッチは、Ph2においてオンする。各フェーズの周波数は、サンプリング周波数に等しく、Ph1とPh2は、交互に繰り返される。つまり、一つのサンプリング周期において、一つのPh1と一つのPh2が存在する。

【0160】

まず、2次FF型ΔΣ変調回路は、上述のように、エラーアンプ151,152が出力するDC/DC変換回路150の出力信号から所望の出力電圧に対応する基準電圧Vrefからの誤差信号を入力する。

【0161】

Ph1において、入力信号が積分器172の入力側容量に印加され、入力信号に応じた電荷が蓄えられる。また、フィードフォワードパスaにより直接加算器174に入力される。

【0162】

Ph2において、DAC176の出力信号が積分器172の入力側容量に印加され、DAC176の出力信号に応じた電荷が転送される。ここで、減算器171は、入力側とDAC176の出力が結線されているので、Ph1で入力信号により蓄えた電荷から、Ph2でDAC176の出力信号に応じた電荷を減算した電荷が、積分器172の入力側容量に蓄えられる。つまり、2次FF型ΔΣ変調回路の入力信号と出力信号との減算が行われ、差分信号が生成される。

【0163】

積分器172の入力側容量の電荷は、Ph2において、演算増幅器の出力端子から非反転入力端子との間の帰還容量に転送される。つまり、差分信号が積分され、差分積分信号が出力される。

【0164】

次に、差分積分信号は、積分器173に入力され、さらに積分される。また、差分積分信号は、フィードフォワードパスbにより直接加算器174に入力される。加算器174において、フィードフォワードパスa及びbより伝達された信号と積分器173の出力信号とが加算されて、加算信号が出力される。

【0165】

そして、加算信号は、量子化器175のコンパレータに入力され、量子化基準信号と加算信号が大小比較されて、フリップフロップに出力される。ここで、量子化基準信号は、0V(グラウンド)である。そして、Ph1になったとき、フリップフロップは、差分積分信号と量子化基準信号(しきい値)との大小比較結果を1ビットの量子化信号として出力する。つまり、量子化器175は、差分積分信号が0V以上のとき、ハイレベルを出力し、0Vより小さいとき、ローレベルを出力する。

【0166】

量子化信号は、DAC176のスイッチに入力される。DAC176において、量子化信号がハイレベルのとき、基準信号Vrefが選択され、量子化信号がローレベルのとき、基準信号−Vrefが選択される。そして、次のサンプリング周期において、量子化信号をD/A変換した信号は、入力信号から減算器171により減算される。このような動作を繰り返すことで、入力信号に応じたパルス密度変調信号が生成される。

【0167】

2次FF型ΔΣ変調回路の入力信号が小さくなる(誤差が大きくなる)と、パルス密度は濃くなり(パルスの数が増え)、大きくなる(誤差が小さくなる)と、パルス密度は薄くなる(パルスの数が減る)。

【0168】

また、上述した動作により、入力信号が0Vより小さいとき、パルス密度変調信号は、一回ハイレベルになった後、必ずローレベルになる。このとき、ハイレベルの期間は、サンプリング周期であり固定である。一方、入力信号が0Vより大きいとき、パルス密度変調信号は、一回ローレベルになった後、必ずハイレベルになる。このとき、ローレベルの期間は、サンプリング周期であり固定である。

以上が、2次FF型ΔΣ変調回路の動作説明である。

【0169】

2次FF型ΔΣ変調回路を用いたスイッチング電源回路は、上述のように、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、さらなる早い応答速度を実現することができる。また、信号伝達関数が1であり、パルス密度変調信号に遅延が生じないので、スイッチング電源回路においてパルス密度変調信号の遅延に起因する発振ループが形成されない。

【0170】

つまり、エラーアンプの出力信号に対応し、スイッチング電源回路の所望の出力電圧からの誤差が0になるような量子化信号、すなわち、パルス密度信号が遅延することなくDC/DC変換回路(電圧コンバータ部)に反映されるので、量子化信号が反映されるまでの間、DC/DC変換回路が余分に昇圧もしくは降圧することがない。よって、所望の出力電圧からの誤差が小さくなる。つまり、遅延に起因する誤差がエラーアンプに伝達されない。

【0171】

さらに、ノイズ伝達関数が2次の微分特性を有するので、信号帯域(低周波帯域)におけるSNDRがさらに高くなるので、1次FF型ΔΣ変調器を用いたスイッチング電源回路よりもリップルが小さくなるという効果を奏する。すなわち、量子化ノイズがより高周波帯域にシェーピングされるため、DC/DC変換回路におけるインダクタと容量とで形成されるリアクタンスフィルタによって、量子化ノイズを減衰させることができる。したがって、スイッチング電源回路の出力信号にリップルはさらに小さくなる。

【0172】

図21(a),(b)は、従来のフィードバック(FB)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形と、2次フィードフォワード(FF)型ΔΣ変調回路を用いたスイッチング電源回路の出力電圧波形とを比較するための図で、図22(a),(b)は、その拡大図である。図22(a)に示したFB型ΔΣ変調回路の出力電圧波形のリップル(ripple;脈動成分)が大きいのに対して、図22(b)に示した2次FF型ΔΣ変調回路の出力電圧波形のリップルが極めて小さいことがわかる。また、図18(b)に示した1次FF型ΔΣ変調回路の出力電圧波形のリップリよりも、図22(b)に示した2次FF型ΔΣ変調回路の出力電圧波形のリップルの方が小さいことはわかる。つまり、1次FF型ΔΣ変調回路よりも2次FF型ΔΣ変調回路のリップルの方が改善されていることが分かる。

【0173】

以上は、2次FF型ΔΣ変調回路について説明したが、N次FF型ΔΣ変調回路について、図示していないが以下に説明する。

【0174】

フィードフォワード型ΔΣ変調回路が、1段目からN段目までカスケード接続される1段目乃至N段目の積分器と、このN段目の積分器の出力側に接続された加算器と、この加算器の出力側に接続された量子化器と、この量子化器の出力側に接続され、この量子化器の出力デジタル信号をアナログ信号に変換して1段目の積分器にフィードバックするデジタル/アナログ変換回路と、入力アナログ信号からデジタル/アナログ変換回路より出力されたアナログ信号を減算する減算器と、入力アナログ信号を直接加算器に入力させる第1のフィードフォワードパスと、1段目の積分器からN−1段目までの出力信号を加算器に直接入力する第1乃至第N−1のフィードフォワードパスとを備えている。

【0175】

このように、N次の場合も、1次や2次の場合と同様に、フィードフォワードパスがN個あり、積分器が初段からN段まで、N個カスケード接続されている。そして、各積分器の出力が加算器により加算され、量子化器にて、量子化される。量子化された量子化信号は、DACに入力され、アナログ信号に変換される。そして、入力信号と減算されて、初段の積分器に入力される。

【0176】

伝達関数は、1次と2次の場合と同様に導かれ、次式となる。

【0177】

Y(Z)=X(Z)+(1−Z-1)NE(Z)

すなわち、STFとNTFはそれぞれ以下の式で表される。

【0178】

STF=1

NTF=(1−Z-1)N

この式から分かるように、STFは、遅延がなく、NTFはN次の微分特性を有する。したがって、信号帯域の中心周波数付近で量子化ノイズが著しく減少していることが分かる。つまり、リップルをさらに低減できるという効果を奏する。

【0179】

以上のように、スイッチング電源回路の高性能化の要求に対して高効率化及び高速過渡応答をΔΣ変調制御により実現でき、小型化及び低コスト化を図るようにし、クロスレギュレーションの影響を小さくした単一インダクタ多出力DC/DC変換回路を備えたスイッチング電源回路を実現することが可能になった。

【符号の説明】

【0180】

1 入力直流電源

21 第1の主スイッチ

22 第2の主スイッチ

31 インダクタ

51 第1の整流手段

52 第2の整流手段

61 第1の平滑手段

62 第2の平滑手段

71 第1の負荷

72 第2の負荷

81 制御回路

90 検出回路

91 PWM回路

92 論理回路

101 DC/DC変換回路(DC/DCコンバータ)

102 エラーアンプ

103 コンパレータ

104 のこぎり発生回路

105 PWM回路

106 ドライブ回路

107,112 制御回路

111 FB型ΔΣ変調回路

121,131,133 減算器

122 積分器(ローパスフィルタ回路:LPF)

123 量子化器(A/Dコンバータ;ADC)

124,136,137 DAC(D/Aコンバータ)

132 1段目の積分器

134 2段目の積分器

135 ADC

141a,141b 2出力DC/DC変換回路

142 単一インダクタ2出力DC/DC変換回路

150 単一インダクタ2出力DC/DC変換回路(デュアル昇圧コンバータ)

151 第1のエラーアンプ(誤差増幅器)

152 第2のエラーアンプ(誤差増幅器)

153 第1のΔΣ変調回路

154 第2のΔΣ変調回路

155 ドライブ回路

161,171 減算器

162 積分器(LPF)

163,174 加算器

164,175 ADC(アナログ/デジタル変換回路)

165,176 DAC(デジタル/アナログ変換回路)

172 1段目の積分器

173 2段目の積分器

801,802,803,804 抵抗

805,806 誤差増幅器

807 基準電圧源

808 発振回路

809,810 比較器

811,812 AND回路

813 Tフリップフロップ

814 OR回路

815 NOR回路

【特許請求の範囲】

【請求項1】

単一インダクタ多出力DC/DC変換回路を制御するスイッチング電源回路において、

入力信号を出力信号に変換する単一インダクタ多出力DC/DC変換回路と、

該単一インダクタ多出力DC/DC変換回路の前記出力信号を入力し、該単一インダクタ多出力DC/DC変換回路を制御するΔΣ変調回路と

を備えていることを特徴とするスイッチング電源回路。

【請求項2】

前記ΔΣ変調回路が、フィードフォワード型ΔΣ変調回路であることを特徴とする請求項1に記載のスイッチング電源回路。

【請求項3】

前記フィードフォワード型ΔΣ変調回路の信号伝達関数が1であり、該フィードフォワード型ΔΣ変調回路より出力されるパルス密度変調信号に遅延がなく、該遅延に起因する出力電圧波形のリップルが低減されることを特徴とする請求項2に記載のスイッチング電源回路。

【請求項4】

前記単一インダクタ多出力DC/DC変換回路が、単一インダクタn出力DC/DC変換回路であって、該単一インダクタn出力DC/DC変換回路の出力電圧に対応する分圧電圧との差分を増幅した誤差信号をn個の前記フィードフォワード型ΔΣ変調回路に出力するn個のエラーアンプと、前記n個のフィードフォワード型ΔΣ変調回路より出力されたパルス密度変調信号が入力されるドライブ回路とを備えていることを特徴とする請求項2又は3に記載のスイッチング電源回路。

【請求項5】

前記フィードフォワード型ΔΣ変調回路の次数が1次であることを特徴とする請求項2,3又は4に記載のスイッチング電源回路。

【請求項6】

前記フィードフォワード型ΔΣ変調回路が、低い周波数の入力アナログ信号を通過させる積分器と、該積分器の出力側に接続された加算器と、該加算器の出力側に接続された量子化器と、該量子化器の出力側に接続され、該量子化器の出力デジタル信号をアナログ信号に変換して前記積分器にフィードバックするデジタル/アナログ変換回路と、前記入力アナログ信号から前記デジタル/アナログ変換回路から出力されたアナログ信号を減算する減算器と、前記入力アナログ信号を直接前記加算器に入力させるフィードフォワードパスとを備えていることを特徴とする請求項5に記載のスイッチング電源回路。

【請求項7】

前記減算器が、第1のスイッチを備え、前記入力アナログ信号と前記出力デジタル信号をデジタル/アナログ変換した信号との差分をとり、

前記積分器が、第2のスイッチと容量と第1の演算増幅器とを備え、前記差分を積分した差分積分信号を出力し、

前記加算器が、前記入力アナログ信号がフィードフォワードパスにより入力される第1の抵抗と前記積分器の出力が入力される第2の抵抗と第2の演算増幅器と帰還抵抗とを備え、

前記量子化器が、コンパレータとフリップフロップとを備え、量子化基準信号と前記加算器の信号レベルを大小比較して量子化信号を出力し、