フリップチップ実装基板及びフリップチップ実装方法

【課題】本発明はバンプを用いて半導体素子をフリップチップ実装を行うフリップチップ実装基板及びフリップチップ実装方法に関し、ボイドの発生を抑制することにより実装信頼性を高めることを課題とする。

【解決手段】基板本体26上に、ソルダーレジスト30と、半導体チップ1に設けられた中央バンプ3がフリップチップ接合される中央パッド28とを有しており、前記半導体チップ1が実装された後にアンダーフィルレジン35が配設されるフリップチップ実装基板において、前記ソルダーレジスト30に中央パッド28を露出させる中央開口部32を形成すると共に、このソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の外周部において一部重なった構成とする。

【解決手段】基板本体26上に、ソルダーレジスト30と、半導体チップ1に設けられた中央バンプ3がフリップチップ接合される中央パッド28とを有しており、前記半導体チップ1が実装された後にアンダーフィルレジン35が配設されるフリップチップ実装基板において、前記ソルダーレジスト30に中央パッド28を露出させる中央開口部32を形成すると共に、このソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の外周部において一部重なった構成とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はフリップチップ実装基板及びフリップチップ実装方法に係り、特にバンプを用いて半導体素子をフリップチップ実装を行うフリップチップ実装基板及びフリップチップ実装方法に関する。

【背景技術】

【0002】

例えば特許文献1に開示されているように、電子素子(例えば半導体素子)に外部接続端子としてスタッドバンプ(登録商標)といわれるワイヤーボンディングにより形成されるバンプ(以下、単にバンプという)を用い、これを接合材を用いてフリップチップ実装基板に形成された接続パッドにフリップチップ接合する実装構造が近年多用されるようになってきている(このバンプについては、「半導体用語大辞典」、株式会社日刊工業新聞社、第1版、1999年3月20日発行、第891頁左欄9行目〜13行目参照)。

【0003】

図1はフリップチップ実装される半導体チップの一例を示しており、図2はこの半導体チップ1がフリップチップ実装されるフリップチップ実装基板5の一例を示している。図1は半導体チップ1の回路形成面1aを示しており、フリップチップ実装時にはこの回路形成面1aがフリップチップ実装基板5と対向するようフェイスダウンで実装される。

【0004】

この半導体チップ1の回路形成面1aには、金バンプよりなる外周バンプ2と中央バンプ3とが形成されている。外周バンプ2は回路形成面1aにペリフェラル状に配設されている。また、中央バンプ3は、回路形成面1aの中央位置に形成されている。従来では、バンプを外部接続端子とする半導体素子では、バンプをペリフェラル状に配置する構成が一般的であった。しかしながら、近年の半導体素子の高密度に伴い端子数が増大し、よって回路形成面1aの中央位置にも中央バンプ3を配置することが行われるようになってきている。

【0005】

これに伴い、半導体チップ1をフリップチップ実装するフリップチップ実装基板5も、外周バンプ2に対応する外周パッド7と中央バンプ3に対応する中央パッド8を設けた構成とされている。また、半導体チップ1の上面にはソルダーレジスト10(梨地で示す)が設けられているが、各パッド7,8の形成位置においては、ソルダーレジスト10に開口が設けられ、各パッド7,8が露出した構成となっている。

【0006】

従来、ペリフェラル状に配設された外周バンプ2がフリップチップ実装される外周パッド7については、ソルダーレジスト10に枠状の枠状開口部11を形成することが行われている。よって、全ての外周パッド7は、この枠状開口部11内に位置した構成となっている。これに対し、中央に位置する中央パッド8は、各々についてソルダーレジスト10に中央開口部12が設けられた構成とされていた。

【0007】

上記構成とされた半導体チップ1は、各パッド7,8に接合材(例えば、はんだ)を配設した上で、フリップチップ実装基板5にフリップチップ実装される。そして、フリップチップ実装が終了した後、半導体チップ1とフリップチップ実装基板5との離間部分にはアンダーフィルレジンが配設される。このアンダーフィルレジンは、半導体チップ1とフリップチップ実装基板5との熱膨張差に起因した応力が各バンプ2,3と各パッド7,8との間に印加されるのを防止するために配設される。このアンダーフィルレジンを設けることにより、半導体チップ1とフリップチップ実装基板5との実装信頼性を高めることができる。

【特許文献1】特開2001−332584号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

図3は、半導体チップ1がフリップチップ実装基板5に実装された後でアンダーフィルレジンが配設される前の状態を示す断面図であり、特に外周バンプ2が外周パッド7にフリップチップ実装された近傍を拡大して示している。同図に示すように、外周バンプ2は外周パッド7にはんだ14を介してフリップチップ実装されており、また外周パッド7はソルダーレジスト10に形成された枠状開口部11の内部に位置している。

【0009】

外周バンプ2と外周パッド7とのフリップチップ実装位置にアンダーフィルレジン15を配設するには、図3に破線で示す矢印のように、半導体チップ1の外周縁1bとフリップチップ実装基板5との隙間から外周バンプ2と外周パッド7との接合位置(即ちの枠状開口部11内)にアンダーフィルレジン15を装填する。

【0010】

外周バンプ2と外周パッド7との接合位置は、半導体チップ1の外周縁1bに近い位置である。このため、アンダーフィルレジン15を外周バンプ2と外周パッド7との接合位置(即ちの枠状開口部11内)に装填する処理は、円滑かつ容易に行うことができた。また、枠状開口部11内に入り込んだアンダーフィルレジン15は枠状開口部11に沿って進行するため、枠状開口部11内に存在する外周バンプ2と外周パッド7との接合位置を確実にアンダーフィルレジン15で封止することができた。

【0011】

しかしながら、近年のように半導体チップ1の回路形成面1aの中央位置に中央バンプ3が設けられ、この中央バンプ3を中央パッド8に接合することにより、アンダーフィルレジン15の配設位置にボイド16(図7参照)が多発する問題点が生じるようになった。以下、図4乃至図7を用いて、従来において中央バンプ3と中央パッド8とのフリップチップ接合位置近傍にボイド16が発生する理由について説明する。

【0012】

図4は、半導体チップ1が実装される前のフリップチップ実装基板5を示しており、特に中央パッド8の近傍を拡大して示している。尚、図4(A)は、図4(B)の矢印A−A線に沿う断面図である。

【0013】

前記したように、中央パッド8は各々について中央開口部12が設けられた構成とされている。また、中央パッド8は、幅広部8aと幅狭部8bとを有した形状とされている。従来においては、中央開口部12は中央パッド8に対して大きく形成されており、中央パッド8と中央開口部12の縁部との間には離間部分6a(図4(A)に矢印W2で示す部分)があった。この離間部分6aにおいては、基板本体6(フリップチップ実装基板5)の表面が露出した状態となっている。従って、中央開口部12の深さは、ソルダーレジスト10の上面から基板本体6上面までの距離(即ち、ソルダーレジスト10の厚さ。図4(A)に矢印H2で示す)となる。

【0014】

図5は、中央パッド8の上面に接合材としてのはんだ14が配設された状態を示している。このはんだ14は、中央パッド8の上部にのみ配設されており、よって離間部分6aは依然として中央開口部12内に存在している。

【0015】

また図6は、中央バンプ3が中央パッド8にはんだ14を介してフリップチップ接合され、これにより半導体チップ1がフリップチップ実装基板5にフリップチップ実装された状態を示している。このフリップチップ実装状態においても、離間部分6aは中央開口部12内に存在している。

【0016】

また図7は、フリップチップ実装された半導体チップ1とフリップチップ実装基板5との間にアンダーフィルレジン15を配設した状態を示している。

図3を用いて説明したように、外周バンプ2と外周パッド7との接合位置をアンダーフィルレジン15で封止する処理は、外周バンプ2が半導体チップ1の外周位置に配設されているため外周縁1bから半導体チップ1とフリップチップ実装基板5との離間部分に充填することができ、よって容易かつ確実に行うことができた。

【0017】

これに対して、半導体チップ1の中央位置に形成された中央バンプ3と中央パッド8との接合位置は、半導体チップ1の外周縁1bから充填されたアンダーフィルレジン15が中央バンプ3と中央パッド8との接合位置まで流れることにより封止される。

【0018】

しかしながら、アンダーフィルレジン15が中央バンプ3と中央パッド8との接合位置(即ち、ソルダーレジスト10の中央開口部12の形成位置)まで流れた際、図7(B)に矢印で示すように、アンダーフィルレジン15は中央開口部12の内部に流れ落ちることなく、その前に中央開口部12の周囲を先回りして流れる現象が発生した。

【0019】

このように中央開口部12の内部にアンダーフィルレジン15が流れ込まないと、中央バンプ3と中央パッド8はアンダーフィルレジン15に保持されない構成となり、半導体チップ1とフリップチップ実装基板5との熱膨張差に起因する応力が直接接合位置に印加されることとなり、実装信頼性が低下してしまう。

【0020】

また、中央バンプ3と中央パッド8との接合位置の周りにボイド(空隙)16が形成されることとなり、後に加熱処理等がされた場合にはボイド16が熱膨張し、中央バンプ3と中央パッド8との接合が破損したり、ソルダーレジスト10やアンダーフィルレジン15等にクラックが発生したりするおそれがあるという問題点があった。

【0021】

本発明は上記の点に鑑みてなされたものであり、ボイドの発生を抑制することにより実装信頼性を高めることができるフリップチップ実装基板及びフリップチップ実装方法を提供することを目的とする。

【課題を解決するための手段】

【0022】

上記の課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とするものである。

【0023】

請求項1記載の発明は、

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周部において一部重なった構成としたことを特徴とするものである。

【0024】

また、請求項2記載の発明は、

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周縁と一致する構成としたことを特徴とするものである。

【0025】

また、請求項3記載の発明は、

請求項1又は2記載のフリップチップ実装基板において、

前記バンプと前記接続パッドとを接続する接合部材が、前記バンプと前記接続パッドとを接続した際に前記ソルダーレジストに形成された開口部を塞ぐよう構成されていることを特徴とするものである。

【0026】

また、請求項4記載の発明は、

請求項1又は3記載のフリップチップ実装基板において、

前記ソルダーレジストの開口部の縁部が外周部において一部重なった構成とされた前記接続パッドが、前記電子素子が実装される領域の中央位置に設けられていることを特徴とするものである。

【0027】

また、請求項5記載の発明は、

ワイヤーボンディングにより形成されるバンプが配設された電子素子をフリップチップ実装するフリップチップ実装方法において、

請求項1乃至4のいずれか1項に記載のフリップチップ実装基板のソルダーレジストに形成された開口部から露出した接続パッド上に、接合部材を配設する工程と、

前記接合部材を介して前記バンプを前記接続パッドに接合することにより、前記電子素子を前記フリップチップ実装基板に搭載すると共に、前記開口部を前記接合部材で塞ぐ工程と、

前記電子素子と前記フリップチップ実装基板との間の離間部分にアンダーフィルレジンを配設する工程とを有することを特徴とするものである。

【発明の効果】

【0028】

本発明によれば、アンダーフィルレジンの流れが円滑化し、アンダーフィルレジン内にボイドが発生することを防止することができる。

【発明を実施するための最良の形態】

【0029】

次に、本発明を実施するための最良の形態について図面と共に説明する。

【0030】

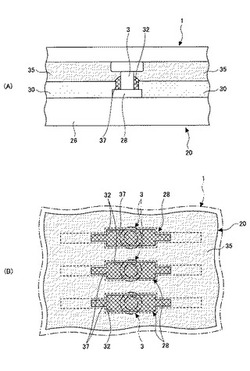

図8は本発明の第1実施例であるフリップチップ実装基板20を示している。このフリップチップ実装基板20は、図1に示した、回路形成面1aに外周バンプ2及び中央バンプ3を形成した高密度化された半導体チップ1をフリップチップ実装する基板である。この外周バンプ2及び中央バンプ3は、ワイヤーボンディングにより形成されるバンプである。

【0031】

尚、図8(A)は図8(B)のA−A線に沿う断面図である。また、フリップチップ実装基板20の平面視した外観は、図2に示したフリップチップ実装基板5の外観と略等しいため、フリップチップ実装基板20の外観の図示は省略する。

【0032】

本実施例に係るフリップチップ実装基板20は、大略すると基板本体26、中央パッド28、及びソルダーレジスト30等により構成されている。基板本体26は樹脂材料よりなり、その上部には配線パターンが形成されている。図では便宜上、配線パターンの内、中央バンプ3とフリップチップ接合される中央パッド28のみを示している。

【0033】

ソルダーレジスト30は、基板本体26上に形成された配線パターンの内、はんだ付け処理が実施されない部分を保護するために設けられている。このソルダーレジスト30には、中央開口部32が形成されている。

【0034】

この中央開口部32は、中央バンプ3がフリップチップ実装される中央パッド28の配設位置に形成されている。従って、中央パッド28は、中央開口部32の形成位置では外部に露出した状態となっている。後述するように半導体チップ1の中央バンプ3は、この中央開口部32から露出した中央パッド28にフリップチップ実装される。尚、中央パッド28は、幅広部28aと幅狭部28bとにより構成されている。

【0035】

本実施例に係るフリップチップ実装基板20は、ソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の外周部において一部重なった構成としたことを特徴としている。具体的には、図8(A)に示すように、本実施例ではソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の上部に乗り上げるように延出することにより、中央パッド28とソルダーレジスト30は図中矢印W1で示す範囲だけ両者が重なった状態となっている(平面視状態で重なっている)。

【0036】

この構成とすることにより、中央開口部32の深さ(図8(A)中、矢印H1で示す)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のようなソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0037】

次に、上記の構成とされたフリップチップ実装基板20を用い、半導体チップ1をフリップチップ実装基板20にフリップチップ実装する方法について説明する。図9乃至図11は、半導体チップ1をフリップチップ実装基板20にフリップチップ実装する方法を実装手順に沿って示している。尚、図9乃至図11において、図1及び図8に示した構成と同一構成については、同一符号を付してその説明を一部省略する。

【0038】

半導体チップ1をフリップチップ実装基板20にフリップチップ実装するには、先ず中央パッド28の上面に接合材としてのはんだ34を配設する。このはんだ34は、中央パッド28の全面(幅広部28a及び幅狭部28bを含む)に配設される。このはんだ34を配設した状態において、本実施例では中央開口部32がはんだ34で完全に塞がれた構成(埋められた構成)となっている。尚、はんだ34は必ずしも中央パッド28の全面を覆う必要はない。

【0039】

上記のようにはんだ34が中央パッド28上に配設されると、続いて中央バンプ3が中央パッド28上に位置決めされる。続いて、半導体チップ1の背面から加熱・加圧を行い、中央バンプ3を介して熱をはんだ34に熱伝達してこれを溶融させる。そして、このはんだ34を介して中央バンプ3を中央パッド28にフリップチップ接合する。尚、中央バンプ3と中央パッド28のフリップチップ接合は、はんだペーストを利用してリフロー処理により行うこととしてもよい。

【0040】

これにより、図10に示すように、半導体チップ1はフリップチップ実装基板20にフリップチップ実装された状態となる。この状態において、はんだ34は中央開口部32を覆っており、その一部はソルダーレジスト30の上部に位置した状態となっている。

【0041】

上記のように半導体チップ1がフリップチップ実装基板20にフリップチップ実装されると、続いて半導体チップ1とフリップチップ実装基板20との離間部分にアンダーフィルレジン35が配設される。本実施例では、中央バンプ3と中央パッド28との接合位置に対するアンダーフィルレジン35の配設が特徴となるため、この接合位置におけるアンダーフィルレジン35の配設についてのみ説明するものとする。

【0042】

前記したように、中央バンプ3と中央パッド28との接合位置は、アンダーフィルレジン35が充填される半導体チップ1の外周縁1bから離間した半導体チップ1の中央位置である。よって、外周縁1bから充填されたアンダーフィルレジン15は、半導体チップ1の中央位置まで流れた後に中央バンプ3と中央パッド28との接合位置を封止する。

【0043】

図7を用いて説明したように、従来のフリップチップ実装基板5を用いたフリップチップ実装方法では、中央パッド8とソルダーレジスト10との間に離間部分6aが形成されているため、中央開口部12の深さはソルダーレジスト10の厚さと同じ深さH2であった。このため、アンダーフィルレジン15が中央バンプ3と中央パッド8との接合位置に到達しても、アンダーフィルレジン15が中央開口部12の内部に流れ込まず、よってボイド16が発生してしまうことは前述した通りである。

【0044】

これに対して本実施例に係るフリップチップ実装基板20は、中央開口部32の形成位置においてソルダーレジスト30の縁部が中央パッド28の外周部に一部重なった構成とされている。よって、中央開口部32の深さH1(図8(A)参照)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のようなソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0045】

よって、はんだ34により中央開口部32を塞ぐことができ、ソルダーレジスト30の中央バンプ3と中央パッド28との接合位置の周囲に窪み(開口した部分)が発生することを防止できる。これにより、半導体チップ1の外周縁1bから充填し、中央バンプ3と中央パッド28との接合位置まで流れてきたアンダーフィルレジン35は、中央バンプ3と中央パッド28との接合位置を完全に封止する。

【0046】

続いて、本発明の第2実施例であるフリップチップ実装基板40について説明する。

【0047】

図12は、本発明の第2実施例であるフリップチップ実装基板40を示している。このフリップチップ実装基板40も第1実施例で示したフリップチップ実装基板20と同様に、回路形成面1aに外周バンプ2及び中央バンプ3を形成した高密度化された半導体チップ1をフリップチップ実装する基板である。

【0048】

尚、図12(A)は図12(B)のA−A線に沿う断面図である。また、図12に示す構成において、図8に示した第1実施例に係るフリップチップ実装基板20の構成と対応する構成については、同一符号を付してその説明を一部省略するものとする。

【0049】

本実施例に係るフリップチップ実装基板40は、基本的には第1実施例に係るフリップチップ実装基板20と同様の構成とされている。即ち、フリップチップ実装基板40は、基板本体26、中央パッド28、ソルダーレジスト30等により構成されている。

【0050】

基板本体26は樹脂材料よりなり、その上部には中央パッド28を含む配線パターンが形成されている。ソルダーレジスト30は基板本体26の上面に形成されており、その中央位置には複数の中央開口部32が形成されている。中央パッド28は、この中央開口部32の形成位置では外部に露出した状態となっている。

【0051】

ここで、第1実施例に係るフリップチップ実装基板20と、本実施例に係るフリップチップ実装基板40との相違点である、中央パッド28と、ソルダーレジスト30の中央開口部32を形成する縁部との位置関係について説明する。

【0052】

前記した第1実施例に係るフリップチップ実装基板40では、ソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の外周部において一部重なるよう構成した(図8(A)参照)。これに対して本実施例に係るフリップチップ実装基板40は、中央開口部32を形成する縁部が中央パッド28上に位置する構成では同一であるが、特にソルダーレジスト30の中央開口部32の縁部が、中央パッド28の外周縁と一致するよう構成したことを特徴としている。

【0053】

この構成とすることにより、ソルダーレジスト30の中央開口部32の縁部と、中央パッド28の外周縁は側面視で一直線状となる(図12(A)参照)。また本実施例においても、中央開口部32の深さ(図12(A)中、矢印H1で示す)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0054】

次に、本実施例のフリップチップ実装基板40を用い、フリップチップ実装基板40の製造方法、及び半導体チップ1をフリップチップ実装基板40にフリップチップ実装する方法について説明する。

【0055】

図13乃至図15は、フリップチップ実装基板40の製造方法、及び半導体チップ1をフリップチップ実装基板40にフリップチップ実装する方法を説明するための図である。尚、図13乃至図15において、図9乃至図11に示した構成と同一構成については、同一符号を付してその説明を一部省略する。

【0056】

フリップチップ実装基板40の製造工程において、ソルダーレジスト30に中央パッド28の外周縁とが一致した縁部を有する中央開口部32を形成するには、基板本体26上にソルダーレジスト30を形成する工程においてスクリーン印刷法或いは写真法等を用いる。

【0057】

スクリーン印刷法は、中央開口部32と対応するパターンが形成されたマスクを用いてソルダーレジスト材を基板本体26上に印刷形成することによりソルダーレジスト30を形成する。一方、写真法では、基板本体26の全面に感光性ソルダーレジスト材を配設し、これを中央開口部32と対応するパターンが形成されたマスクを用いて露光・現像することによりソルダーレジスト30を形成する。

【0058】

これらのソルダーレジスト30の形成方法は、高精度にソルダーレジスト30のパターニングができるため、ソルダーレジスト30の中央開口部32の縁部と、中央パッド28の外周縁とを一致させることができる。また、これらの形成方法は、半導体製造技術として一般に用いられるものであり、よってソルダーレジスト30に中央パッド28の外周縁とが一致した縁部を有する中央開口部32を形成する処理は、容易かつ安価に行うことができる。

【0059】

上記のように製造されたフリップチップ実装基板40に対して半導体チップ1をフリップチップ実装するには、先ず中央パッド28の上面にはんだ34を配設する。この際、はんだ34は、中央パッド28の全面(幅広部28a及び幅狭部28bを含む)に配設される。

【0060】

このはんだ34を配設した状態において、本実施例では中央開口部32がはんだ34で完全に塞がれた構成(埋められた構成)となっている。この際、本実施例に係るフリップチップ実装基板40は、ソルダーレジスト30の中央開口部32の縁部と、中央パッド28の外周縁とが一致した構成とされている。

【0061】

このため、中央パッド28の形状が第1及び第2実施例に係るフリップチップ実装基板20,40で同一面積であったとしても、中央開口部32から露出した中央パッド28の面積は本実施例の方が広くなる。このため、本実施例の構成とすることにより、第1実施例に比べてはんだ34の配設量を多くすることができる。

【0062】

続いて、半導体チップ1の背面から加熱・加圧を行い、中央バンプ3を介して熱をはんだ34に熱伝達してこれを溶融させる。そして、このはんだ34を介して中央バンプ3を中央パッド28にフリップチップ接合する。

【0063】

これにより、図14に示すように、半導体チップ1はフリップチップ実装基板20にフリップチップ実装された状態となる。尚、中央バンプ3と中央パッド28のフリップチップ接合は、はんだペーストを利用してリフロー処理により行うこととしてもよい。

【0064】

前記のように、本実施例では中央パッド28の露出面積を増大できるため、はんだ34の配設量が増大されている。このため、中央バンプ3と中央パッド28とを接合するはんだ34の体積も増大し、よって中央バンプ3と中央パッド28とを確実にはんだ接合することができる。

【0065】

上記のように半導体チップ1がフリップチップ実装基板40にフリップチップ実装されると、続いて半導体チップ1とフリップチップ実装基板40との離間部分にアンダーフィルレジン35が配設される。

【0066】

本実施例においても、中央バンプ3と中央パッド28との接合位置は半導体チップ1の中央位置であり、よって半導体チップ1の外周縁1bから充填されたアンダーフィルレジン15は、その中央位置まで流れた後に中央バンプ3と中央パッド28との接合位置を封止する。

【0067】

しかしながら、本実施例に係るフリップチップ実装基板40は、ソルダーレジスト30の中央開口部32の縁部が、中央パッド28の外周縁と一致するよう構成されておいる。よって本実施例に係るフリップチップ実装基板40も、第1実施例に係るフリップチップ実装基板20と同様に、中央開口部32の深さH1(図12(A)参照)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のようなソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0068】

これにより本実施例においても、はんだ34により中央開口部32を塞ぐことができ、ソルダーレジスト30の中央バンプ3と中央パッド28との接合位置の周囲に窪み(開口した部分)が発生することを防止できる。よって、半導体チップ1の外周縁1bから充填した際、中央バンプ3と中央パッド28との接合位置まで流れてきたアンダーフィルレジン35は、中央バンプ3と中央パッド28との接合位置を完全に封止する。

【0069】

上記のように、第1及び第2の本実施例に係るフリップチップ実装基板20,40を用いてフリップチップ実装を行うことにより、特に半導体チップ1の中央に位置している中央バンプ3と中央パッド28との接合位置においてボイドが発生することを防止できる。

【0070】

またボイトの発生が抑制されることにより、フリップチップ実装後に熱の印加が行われたような場合であっても、従来のようにボイドが膨張して中央バンプ3と中央パッド28との接合が損傷したり、ソルダーレジスト30やアンダーフィルレジン35にクラックが発生したりすることを防止でき、実装信頼性を高めることができる。

【図面の簡単な説明】

【0071】

【図1】図1は、半導体チップのバンプの配設位置を説明するための底面図である。

【図2】図2は、図1に示す半導体チップが実装されるフリップチップ実装基板の一例を示す平面図である。

【図3】図3は、外周バンプ2のフリップチップ接合位置に対するアンダーフィルレジンの充填を説明するための断面図である。

【図4】図4は、従来の一例であるフリップチップ実装基板の構造を説明するための図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図5】図5は、従来の一例であるフリップチップ実装基板の中央パッドにはんだを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図6】図6は、従来の一例であるフリップチップ実装基板に中央バンプが接合された状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図7】図7は、従来の一例であるフリップチップ実装基板にアンダーフィルレジンを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図8】図8は、本発明の第1実施例であるフリップチップ実装基板の構造を説明するための図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図9】図9は、本発明の第1実施例であるフリップチップ実装基板の中央パッドにはんだを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図10】図10は、本発明の第1実施例であるフリップチップ実装基板に中央バンプが接合された状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図11】図11は、本発明の第1実施例であるフリップチップ実装基板にアンダーフィルレジンを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図12】図12は、本発明の第2実施例であるフリップチップ実装基板の構造を説明するための図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図13】図13は、本発明の第2実施例であるフリップチップ実装基板の中央パッドにはんだを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図14】図14は、本発明の第2実施例であるフリップチップ実装基板に中央バンプが接合された状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図15】図15は、本発明の第2実施例であるフリップチップ実装基板にアンダーフィルレジンを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【符号の説明】

【0072】

1 半導体チップ

2 外周バンプ

3 中央バンプ

20,40 フリップチップ実装基板

26 基板本体

27 外周パッド

28 中央パッド

30 ソルダーレジスト

31 枠状開口部

32 中央開口部

34 はんだ

35 アンダーフィルレジン

【技術分野】

【0001】

本発明はフリップチップ実装基板及びフリップチップ実装方法に係り、特にバンプを用いて半導体素子をフリップチップ実装を行うフリップチップ実装基板及びフリップチップ実装方法に関する。

【背景技術】

【0002】

例えば特許文献1に開示されているように、電子素子(例えば半導体素子)に外部接続端子としてスタッドバンプ(登録商標)といわれるワイヤーボンディングにより形成されるバンプ(以下、単にバンプという)を用い、これを接合材を用いてフリップチップ実装基板に形成された接続パッドにフリップチップ接合する実装構造が近年多用されるようになってきている(このバンプについては、「半導体用語大辞典」、株式会社日刊工業新聞社、第1版、1999年3月20日発行、第891頁左欄9行目〜13行目参照)。

【0003】

図1はフリップチップ実装される半導体チップの一例を示しており、図2はこの半導体チップ1がフリップチップ実装されるフリップチップ実装基板5の一例を示している。図1は半導体チップ1の回路形成面1aを示しており、フリップチップ実装時にはこの回路形成面1aがフリップチップ実装基板5と対向するようフェイスダウンで実装される。

【0004】

この半導体チップ1の回路形成面1aには、金バンプよりなる外周バンプ2と中央バンプ3とが形成されている。外周バンプ2は回路形成面1aにペリフェラル状に配設されている。また、中央バンプ3は、回路形成面1aの中央位置に形成されている。従来では、バンプを外部接続端子とする半導体素子では、バンプをペリフェラル状に配置する構成が一般的であった。しかしながら、近年の半導体素子の高密度に伴い端子数が増大し、よって回路形成面1aの中央位置にも中央バンプ3を配置することが行われるようになってきている。

【0005】

これに伴い、半導体チップ1をフリップチップ実装するフリップチップ実装基板5も、外周バンプ2に対応する外周パッド7と中央バンプ3に対応する中央パッド8を設けた構成とされている。また、半導体チップ1の上面にはソルダーレジスト10(梨地で示す)が設けられているが、各パッド7,8の形成位置においては、ソルダーレジスト10に開口が設けられ、各パッド7,8が露出した構成となっている。

【0006】

従来、ペリフェラル状に配設された外周バンプ2がフリップチップ実装される外周パッド7については、ソルダーレジスト10に枠状の枠状開口部11を形成することが行われている。よって、全ての外周パッド7は、この枠状開口部11内に位置した構成となっている。これに対し、中央に位置する中央パッド8は、各々についてソルダーレジスト10に中央開口部12が設けられた構成とされていた。

【0007】

上記構成とされた半導体チップ1は、各パッド7,8に接合材(例えば、はんだ)を配設した上で、フリップチップ実装基板5にフリップチップ実装される。そして、フリップチップ実装が終了した後、半導体チップ1とフリップチップ実装基板5との離間部分にはアンダーフィルレジンが配設される。このアンダーフィルレジンは、半導体チップ1とフリップチップ実装基板5との熱膨張差に起因した応力が各バンプ2,3と各パッド7,8との間に印加されるのを防止するために配設される。このアンダーフィルレジンを設けることにより、半導体チップ1とフリップチップ実装基板5との実装信頼性を高めることができる。

【特許文献1】特開2001−332584号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

図3は、半導体チップ1がフリップチップ実装基板5に実装された後でアンダーフィルレジンが配設される前の状態を示す断面図であり、特に外周バンプ2が外周パッド7にフリップチップ実装された近傍を拡大して示している。同図に示すように、外周バンプ2は外周パッド7にはんだ14を介してフリップチップ実装されており、また外周パッド7はソルダーレジスト10に形成された枠状開口部11の内部に位置している。

【0009】

外周バンプ2と外周パッド7とのフリップチップ実装位置にアンダーフィルレジン15を配設するには、図3に破線で示す矢印のように、半導体チップ1の外周縁1bとフリップチップ実装基板5との隙間から外周バンプ2と外周パッド7との接合位置(即ちの枠状開口部11内)にアンダーフィルレジン15を装填する。

【0010】

外周バンプ2と外周パッド7との接合位置は、半導体チップ1の外周縁1bに近い位置である。このため、アンダーフィルレジン15を外周バンプ2と外周パッド7との接合位置(即ちの枠状開口部11内)に装填する処理は、円滑かつ容易に行うことができた。また、枠状開口部11内に入り込んだアンダーフィルレジン15は枠状開口部11に沿って進行するため、枠状開口部11内に存在する外周バンプ2と外周パッド7との接合位置を確実にアンダーフィルレジン15で封止することができた。

【0011】

しかしながら、近年のように半導体チップ1の回路形成面1aの中央位置に中央バンプ3が設けられ、この中央バンプ3を中央パッド8に接合することにより、アンダーフィルレジン15の配設位置にボイド16(図7参照)が多発する問題点が生じるようになった。以下、図4乃至図7を用いて、従来において中央バンプ3と中央パッド8とのフリップチップ接合位置近傍にボイド16が発生する理由について説明する。

【0012】

図4は、半導体チップ1が実装される前のフリップチップ実装基板5を示しており、特に中央パッド8の近傍を拡大して示している。尚、図4(A)は、図4(B)の矢印A−A線に沿う断面図である。

【0013】

前記したように、中央パッド8は各々について中央開口部12が設けられた構成とされている。また、中央パッド8は、幅広部8aと幅狭部8bとを有した形状とされている。従来においては、中央開口部12は中央パッド8に対して大きく形成されており、中央パッド8と中央開口部12の縁部との間には離間部分6a(図4(A)に矢印W2で示す部分)があった。この離間部分6aにおいては、基板本体6(フリップチップ実装基板5)の表面が露出した状態となっている。従って、中央開口部12の深さは、ソルダーレジスト10の上面から基板本体6上面までの距離(即ち、ソルダーレジスト10の厚さ。図4(A)に矢印H2で示す)となる。

【0014】

図5は、中央パッド8の上面に接合材としてのはんだ14が配設された状態を示している。このはんだ14は、中央パッド8の上部にのみ配設されており、よって離間部分6aは依然として中央開口部12内に存在している。

【0015】

また図6は、中央バンプ3が中央パッド8にはんだ14を介してフリップチップ接合され、これにより半導体チップ1がフリップチップ実装基板5にフリップチップ実装された状態を示している。このフリップチップ実装状態においても、離間部分6aは中央開口部12内に存在している。

【0016】

また図7は、フリップチップ実装された半導体チップ1とフリップチップ実装基板5との間にアンダーフィルレジン15を配設した状態を示している。

図3を用いて説明したように、外周バンプ2と外周パッド7との接合位置をアンダーフィルレジン15で封止する処理は、外周バンプ2が半導体チップ1の外周位置に配設されているため外周縁1bから半導体チップ1とフリップチップ実装基板5との離間部分に充填することができ、よって容易かつ確実に行うことができた。

【0017】

これに対して、半導体チップ1の中央位置に形成された中央バンプ3と中央パッド8との接合位置は、半導体チップ1の外周縁1bから充填されたアンダーフィルレジン15が中央バンプ3と中央パッド8との接合位置まで流れることにより封止される。

【0018】

しかしながら、アンダーフィルレジン15が中央バンプ3と中央パッド8との接合位置(即ち、ソルダーレジスト10の中央開口部12の形成位置)まで流れた際、図7(B)に矢印で示すように、アンダーフィルレジン15は中央開口部12の内部に流れ落ちることなく、その前に中央開口部12の周囲を先回りして流れる現象が発生した。

【0019】

このように中央開口部12の内部にアンダーフィルレジン15が流れ込まないと、中央バンプ3と中央パッド8はアンダーフィルレジン15に保持されない構成となり、半導体チップ1とフリップチップ実装基板5との熱膨張差に起因する応力が直接接合位置に印加されることとなり、実装信頼性が低下してしまう。

【0020】

また、中央バンプ3と中央パッド8との接合位置の周りにボイド(空隙)16が形成されることとなり、後に加熱処理等がされた場合にはボイド16が熱膨張し、中央バンプ3と中央パッド8との接合が破損したり、ソルダーレジスト10やアンダーフィルレジン15等にクラックが発生したりするおそれがあるという問題点があった。

【0021】

本発明は上記の点に鑑みてなされたものであり、ボイドの発生を抑制することにより実装信頼性を高めることができるフリップチップ実装基板及びフリップチップ実装方法を提供することを目的とする。

【課題を解決するための手段】

【0022】

上記の課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とするものである。

【0023】

請求項1記載の発明は、

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周部において一部重なった構成としたことを特徴とするものである。

【0024】

また、請求項2記載の発明は、

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周縁と一致する構成としたことを特徴とするものである。

【0025】

また、請求項3記載の発明は、

請求項1又は2記載のフリップチップ実装基板において、

前記バンプと前記接続パッドとを接続する接合部材が、前記バンプと前記接続パッドとを接続した際に前記ソルダーレジストに形成された開口部を塞ぐよう構成されていることを特徴とするものである。

【0026】

また、請求項4記載の発明は、

請求項1又は3記載のフリップチップ実装基板において、

前記ソルダーレジストの開口部の縁部が外周部において一部重なった構成とされた前記接続パッドが、前記電子素子が実装される領域の中央位置に設けられていることを特徴とするものである。

【0027】

また、請求項5記載の発明は、

ワイヤーボンディングにより形成されるバンプが配設された電子素子をフリップチップ実装するフリップチップ実装方法において、

請求項1乃至4のいずれか1項に記載のフリップチップ実装基板のソルダーレジストに形成された開口部から露出した接続パッド上に、接合部材を配設する工程と、

前記接合部材を介して前記バンプを前記接続パッドに接合することにより、前記電子素子を前記フリップチップ実装基板に搭載すると共に、前記開口部を前記接合部材で塞ぐ工程と、

前記電子素子と前記フリップチップ実装基板との間の離間部分にアンダーフィルレジンを配設する工程とを有することを特徴とするものである。

【発明の効果】

【0028】

本発明によれば、アンダーフィルレジンの流れが円滑化し、アンダーフィルレジン内にボイドが発生することを防止することができる。

【発明を実施するための最良の形態】

【0029】

次に、本発明を実施するための最良の形態について図面と共に説明する。

【0030】

図8は本発明の第1実施例であるフリップチップ実装基板20を示している。このフリップチップ実装基板20は、図1に示した、回路形成面1aに外周バンプ2及び中央バンプ3を形成した高密度化された半導体チップ1をフリップチップ実装する基板である。この外周バンプ2及び中央バンプ3は、ワイヤーボンディングにより形成されるバンプである。

【0031】

尚、図8(A)は図8(B)のA−A線に沿う断面図である。また、フリップチップ実装基板20の平面視した外観は、図2に示したフリップチップ実装基板5の外観と略等しいため、フリップチップ実装基板20の外観の図示は省略する。

【0032】

本実施例に係るフリップチップ実装基板20は、大略すると基板本体26、中央パッド28、及びソルダーレジスト30等により構成されている。基板本体26は樹脂材料よりなり、その上部には配線パターンが形成されている。図では便宜上、配線パターンの内、中央バンプ3とフリップチップ接合される中央パッド28のみを示している。

【0033】

ソルダーレジスト30は、基板本体26上に形成された配線パターンの内、はんだ付け処理が実施されない部分を保護するために設けられている。このソルダーレジスト30には、中央開口部32が形成されている。

【0034】

この中央開口部32は、中央バンプ3がフリップチップ実装される中央パッド28の配設位置に形成されている。従って、中央パッド28は、中央開口部32の形成位置では外部に露出した状態となっている。後述するように半導体チップ1の中央バンプ3は、この中央開口部32から露出した中央パッド28にフリップチップ実装される。尚、中央パッド28は、幅広部28aと幅狭部28bとにより構成されている。

【0035】

本実施例に係るフリップチップ実装基板20は、ソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の外周部において一部重なった構成としたことを特徴としている。具体的には、図8(A)に示すように、本実施例ではソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の上部に乗り上げるように延出することにより、中央パッド28とソルダーレジスト30は図中矢印W1で示す範囲だけ両者が重なった状態となっている(平面視状態で重なっている)。

【0036】

この構成とすることにより、中央開口部32の深さ(図8(A)中、矢印H1で示す)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のようなソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0037】

次に、上記の構成とされたフリップチップ実装基板20を用い、半導体チップ1をフリップチップ実装基板20にフリップチップ実装する方法について説明する。図9乃至図11は、半導体チップ1をフリップチップ実装基板20にフリップチップ実装する方法を実装手順に沿って示している。尚、図9乃至図11において、図1及び図8に示した構成と同一構成については、同一符号を付してその説明を一部省略する。

【0038】

半導体チップ1をフリップチップ実装基板20にフリップチップ実装するには、先ず中央パッド28の上面に接合材としてのはんだ34を配設する。このはんだ34は、中央パッド28の全面(幅広部28a及び幅狭部28bを含む)に配設される。このはんだ34を配設した状態において、本実施例では中央開口部32がはんだ34で完全に塞がれた構成(埋められた構成)となっている。尚、はんだ34は必ずしも中央パッド28の全面を覆う必要はない。

【0039】

上記のようにはんだ34が中央パッド28上に配設されると、続いて中央バンプ3が中央パッド28上に位置決めされる。続いて、半導体チップ1の背面から加熱・加圧を行い、中央バンプ3を介して熱をはんだ34に熱伝達してこれを溶融させる。そして、このはんだ34を介して中央バンプ3を中央パッド28にフリップチップ接合する。尚、中央バンプ3と中央パッド28のフリップチップ接合は、はんだペーストを利用してリフロー処理により行うこととしてもよい。

【0040】

これにより、図10に示すように、半導体チップ1はフリップチップ実装基板20にフリップチップ実装された状態となる。この状態において、はんだ34は中央開口部32を覆っており、その一部はソルダーレジスト30の上部に位置した状態となっている。

【0041】

上記のように半導体チップ1がフリップチップ実装基板20にフリップチップ実装されると、続いて半導体チップ1とフリップチップ実装基板20との離間部分にアンダーフィルレジン35が配設される。本実施例では、中央バンプ3と中央パッド28との接合位置に対するアンダーフィルレジン35の配設が特徴となるため、この接合位置におけるアンダーフィルレジン35の配設についてのみ説明するものとする。

【0042】

前記したように、中央バンプ3と中央パッド28との接合位置は、アンダーフィルレジン35が充填される半導体チップ1の外周縁1bから離間した半導体チップ1の中央位置である。よって、外周縁1bから充填されたアンダーフィルレジン15は、半導体チップ1の中央位置まで流れた後に中央バンプ3と中央パッド28との接合位置を封止する。

【0043】

図7を用いて説明したように、従来のフリップチップ実装基板5を用いたフリップチップ実装方法では、中央パッド8とソルダーレジスト10との間に離間部分6aが形成されているため、中央開口部12の深さはソルダーレジスト10の厚さと同じ深さH2であった。このため、アンダーフィルレジン15が中央バンプ3と中央パッド8との接合位置に到達しても、アンダーフィルレジン15が中央開口部12の内部に流れ込まず、よってボイド16が発生してしまうことは前述した通りである。

【0044】

これに対して本実施例に係るフリップチップ実装基板20は、中央開口部32の形成位置においてソルダーレジスト30の縁部が中央パッド28の外周部に一部重なった構成とされている。よって、中央開口部32の深さH1(図8(A)参照)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のようなソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0045】

よって、はんだ34により中央開口部32を塞ぐことができ、ソルダーレジスト30の中央バンプ3と中央パッド28との接合位置の周囲に窪み(開口した部分)が発生することを防止できる。これにより、半導体チップ1の外周縁1bから充填し、中央バンプ3と中央パッド28との接合位置まで流れてきたアンダーフィルレジン35は、中央バンプ3と中央パッド28との接合位置を完全に封止する。

【0046】

続いて、本発明の第2実施例であるフリップチップ実装基板40について説明する。

【0047】

図12は、本発明の第2実施例であるフリップチップ実装基板40を示している。このフリップチップ実装基板40も第1実施例で示したフリップチップ実装基板20と同様に、回路形成面1aに外周バンプ2及び中央バンプ3を形成した高密度化された半導体チップ1をフリップチップ実装する基板である。

【0048】

尚、図12(A)は図12(B)のA−A線に沿う断面図である。また、図12に示す構成において、図8に示した第1実施例に係るフリップチップ実装基板20の構成と対応する構成については、同一符号を付してその説明を一部省略するものとする。

【0049】

本実施例に係るフリップチップ実装基板40は、基本的には第1実施例に係るフリップチップ実装基板20と同様の構成とされている。即ち、フリップチップ実装基板40は、基板本体26、中央パッド28、ソルダーレジスト30等により構成されている。

【0050】

基板本体26は樹脂材料よりなり、その上部には中央パッド28を含む配線パターンが形成されている。ソルダーレジスト30は基板本体26の上面に形成されており、その中央位置には複数の中央開口部32が形成されている。中央パッド28は、この中央開口部32の形成位置では外部に露出した状態となっている。

【0051】

ここで、第1実施例に係るフリップチップ実装基板20と、本実施例に係るフリップチップ実装基板40との相違点である、中央パッド28と、ソルダーレジスト30の中央開口部32を形成する縁部との位置関係について説明する。

【0052】

前記した第1実施例に係るフリップチップ実装基板40では、ソルダーレジスト30の中央開口部32を形成する縁部が中央パッド28の外周部において一部重なるよう構成した(図8(A)参照)。これに対して本実施例に係るフリップチップ実装基板40は、中央開口部32を形成する縁部が中央パッド28上に位置する構成では同一であるが、特にソルダーレジスト30の中央開口部32の縁部が、中央パッド28の外周縁と一致するよう構成したことを特徴としている。

【0053】

この構成とすることにより、ソルダーレジスト30の中央開口部32の縁部と、中央パッド28の外周縁は側面視で一直線状となる(図12(A)参照)。また本実施例においても、中央開口部32の深さ(図12(A)中、矢印H1で示す)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0054】

次に、本実施例のフリップチップ実装基板40を用い、フリップチップ実装基板40の製造方法、及び半導体チップ1をフリップチップ実装基板40にフリップチップ実装する方法について説明する。

【0055】

図13乃至図15は、フリップチップ実装基板40の製造方法、及び半導体チップ1をフリップチップ実装基板40にフリップチップ実装する方法を説明するための図である。尚、図13乃至図15において、図9乃至図11に示した構成と同一構成については、同一符号を付してその説明を一部省略する。

【0056】

フリップチップ実装基板40の製造工程において、ソルダーレジスト30に中央パッド28の外周縁とが一致した縁部を有する中央開口部32を形成するには、基板本体26上にソルダーレジスト30を形成する工程においてスクリーン印刷法或いは写真法等を用いる。

【0057】

スクリーン印刷法は、中央開口部32と対応するパターンが形成されたマスクを用いてソルダーレジスト材を基板本体26上に印刷形成することによりソルダーレジスト30を形成する。一方、写真法では、基板本体26の全面に感光性ソルダーレジスト材を配設し、これを中央開口部32と対応するパターンが形成されたマスクを用いて露光・現像することによりソルダーレジスト30を形成する。

【0058】

これらのソルダーレジスト30の形成方法は、高精度にソルダーレジスト30のパターニングができるため、ソルダーレジスト30の中央開口部32の縁部と、中央パッド28の外周縁とを一致させることができる。また、これらの形成方法は、半導体製造技術として一般に用いられるものであり、よってソルダーレジスト30に中央パッド28の外周縁とが一致した縁部を有する中央開口部32を形成する処理は、容易かつ安価に行うことができる。

【0059】

上記のように製造されたフリップチップ実装基板40に対して半導体チップ1をフリップチップ実装するには、先ず中央パッド28の上面にはんだ34を配設する。この際、はんだ34は、中央パッド28の全面(幅広部28a及び幅狭部28bを含む)に配設される。

【0060】

このはんだ34を配設した状態において、本実施例では中央開口部32がはんだ34で完全に塞がれた構成(埋められた構成)となっている。この際、本実施例に係るフリップチップ実装基板40は、ソルダーレジスト30の中央開口部32の縁部と、中央パッド28の外周縁とが一致した構成とされている。

【0061】

このため、中央パッド28の形状が第1及び第2実施例に係るフリップチップ実装基板20,40で同一面積であったとしても、中央開口部32から露出した中央パッド28の面積は本実施例の方が広くなる。このため、本実施例の構成とすることにより、第1実施例に比べてはんだ34の配設量を多くすることができる。

【0062】

続いて、半導体チップ1の背面から加熱・加圧を行い、中央バンプ3を介して熱をはんだ34に熱伝達してこれを溶融させる。そして、このはんだ34を介して中央バンプ3を中央パッド28にフリップチップ接合する。

【0063】

これにより、図14に示すように、半導体チップ1はフリップチップ実装基板20にフリップチップ実装された状態となる。尚、中央バンプ3と中央パッド28のフリップチップ接合は、はんだペーストを利用してリフロー処理により行うこととしてもよい。

【0064】

前記のように、本実施例では中央パッド28の露出面積を増大できるため、はんだ34の配設量が増大されている。このため、中央バンプ3と中央パッド28とを接合するはんだ34の体積も増大し、よって中央バンプ3と中央パッド28とを確実にはんだ接合することができる。

【0065】

上記のように半導体チップ1がフリップチップ実装基板40にフリップチップ実装されると、続いて半導体チップ1とフリップチップ実装基板40との離間部分にアンダーフィルレジン35が配設される。

【0066】

本実施例においても、中央バンプ3と中央パッド28との接合位置は半導体チップ1の中央位置であり、よって半導体チップ1の外周縁1bから充填されたアンダーフィルレジン15は、その中央位置まで流れた後に中央バンプ3と中央パッド28との接合位置を封止する。

【0067】

しかしながら、本実施例に係るフリップチップ実装基板40は、ソルダーレジスト30の中央開口部32の縁部が、中央パッド28の外周縁と一致するよう構成されておいる。よって本実施例に係るフリップチップ実装基板40も、第1実施例に係るフリップチップ実装基板20と同様に、中央開口部32の深さH1(図12(A)参照)はソルダーレジスト30の上面から中央パッド28の上面までの深さとなり、従来のようなソルダーレジスト10の上面から基板本体6の表面までの深さH2(図4(A)参照)に比べて浅くすることができる(H1<H2)。

【0068】

これにより本実施例においても、はんだ34により中央開口部32を塞ぐことができ、ソルダーレジスト30の中央バンプ3と中央パッド28との接合位置の周囲に窪み(開口した部分)が発生することを防止できる。よって、半導体チップ1の外周縁1bから充填した際、中央バンプ3と中央パッド28との接合位置まで流れてきたアンダーフィルレジン35は、中央バンプ3と中央パッド28との接合位置を完全に封止する。

【0069】

上記のように、第1及び第2の本実施例に係るフリップチップ実装基板20,40を用いてフリップチップ実装を行うことにより、特に半導体チップ1の中央に位置している中央バンプ3と中央パッド28との接合位置においてボイドが発生することを防止できる。

【0070】

またボイトの発生が抑制されることにより、フリップチップ実装後に熱の印加が行われたような場合であっても、従来のようにボイドが膨張して中央バンプ3と中央パッド28との接合が損傷したり、ソルダーレジスト30やアンダーフィルレジン35にクラックが発生したりすることを防止でき、実装信頼性を高めることができる。

【図面の簡単な説明】

【0071】

【図1】図1は、半導体チップのバンプの配設位置を説明するための底面図である。

【図2】図2は、図1に示す半導体チップが実装されるフリップチップ実装基板の一例を示す平面図である。

【図3】図3は、外周バンプ2のフリップチップ接合位置に対するアンダーフィルレジンの充填を説明するための断面図である。

【図4】図4は、従来の一例であるフリップチップ実装基板の構造を説明するための図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図5】図5は、従来の一例であるフリップチップ実装基板の中央パッドにはんだを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図6】図6は、従来の一例であるフリップチップ実装基板に中央バンプが接合された状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図7】図7は、従来の一例であるフリップチップ実装基板にアンダーフィルレジンを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図8】図8は、本発明の第1実施例であるフリップチップ実装基板の構造を説明するための図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図9】図9は、本発明の第1実施例であるフリップチップ実装基板の中央パッドにはんだを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図10】図10は、本発明の第1実施例であるフリップチップ実装基板に中央バンプが接合された状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図11】図11は、本発明の第1実施例であるフリップチップ実装基板にアンダーフィルレジンを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図12】図12は、本発明の第2実施例であるフリップチップ実装基板の構造を説明するための図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図13】図13は、本発明の第2実施例であるフリップチップ実装基板の中央パッドにはんだを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図14】図14は、本発明の第2実施例であるフリップチップ実装基板に中央バンプが接合された状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【図15】図15は、本発明の第2実施例であるフリップチップ実装基板にアンダーフィルレジンを配設した状態を示す図であり、(A)は中央パッド近傍の断面図、(B)は中央パッド近傍の平面図である。

【符号の説明】

【0072】

1 半導体チップ

2 外周バンプ

3 中央バンプ

20,40 フリップチップ実装基板

26 基板本体

27 外周パッド

28 中央パッド

30 ソルダーレジスト

31 枠状開口部

32 中央開口部

34 はんだ

35 アンダーフィルレジン

【特許請求の範囲】

【請求項1】

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周部において一部重なった構成としたことを特徴とするフリップチップ実装基板。

【請求項2】

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周縁と一致する構成としたことを特徴とするフリップチップ実装基板。

【請求項3】

前記バンプと前記接続パッドとを接続する接合部材が、前記バンプと前記接続パッドとを接続した際に前記ソルダーレジストに形成された開口部を塞ぐよう構成されていることを特徴とする請求項1又は2記載のフリップチップ実装基板。

【請求項4】

前記ソルダーレジストの開口部の縁部が外周部において一部重なった構成とされた前記接続パッドが、前記電子素子が実装される領域の中央位置に設けられていることを特徴とする請求項1又は3記載のフリップチップ実装基板。

【請求項5】

ワイヤーボンディングにより形成されるバンプが配設された電子素子をフリップチップ実装するフリップチップ実装方法において、

請求項1乃至4のいずれか1項に記載のフリップチップ実装基板のソルダーレジストに形成された開口部から露出した接続パッド上に、接合部材を配設する工程と、

前記接合部材を介して前記バンプを前記接続パッドに接合することにより、前記電子素子を前記フリップチップ実装基板に搭載すると共に、前記開口部を前記接合部材で塞ぐ工程と、

前記電子素子と前記フリップチップ実装基板との間の離間部分にアンダーフィルレジンを配設する工程と

を有することを特徴とするフリップチップ実装方法。

【請求項1】

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周部において一部重なった構成としたことを特徴とするフリップチップ実装基板。

【請求項2】

基板本体上に、ソルダーレジストと、電子素子に設けられワイヤーボンディングにより形成されるバンプがフリップチップ接合される接続パッドとを有しており、前記電子素子が実装された後にアンダーフィルレジンが配設されるフリップチップ実装基板において、

前記ソルダーレジストに前記接続パッドを露出させる開口部を形成すると共に、該ソルダーレジストの開口部を形成する縁部が前記接続パッドの外周縁と一致する構成としたことを特徴とするフリップチップ実装基板。

【請求項3】

前記バンプと前記接続パッドとを接続する接合部材が、前記バンプと前記接続パッドとを接続した際に前記ソルダーレジストに形成された開口部を塞ぐよう構成されていることを特徴とする請求項1又は2記載のフリップチップ実装基板。

【請求項4】

前記ソルダーレジストの開口部の縁部が外周部において一部重なった構成とされた前記接続パッドが、前記電子素子が実装される領域の中央位置に設けられていることを特徴とする請求項1又は3記載のフリップチップ実装基板。

【請求項5】

ワイヤーボンディングにより形成されるバンプが配設された電子素子をフリップチップ実装するフリップチップ実装方法において、

請求項1乃至4のいずれか1項に記載のフリップチップ実装基板のソルダーレジストに形成された開口部から露出した接続パッド上に、接合部材を配設する工程と、

前記接合部材を介して前記バンプを前記接続パッドに接合することにより、前記電子素子を前記フリップチップ実装基板に搭載すると共に、前記開口部を前記接合部材で塞ぐ工程と、

前記電子素子と前記フリップチップ実装基板との間の離間部分にアンダーフィルレジンを配設する工程と

を有することを特徴とするフリップチップ実装方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2007−194598(P2007−194598A)

【公開日】平成19年8月2日(2007.8.2)

【国際特許分類】

【出願番号】特願2006−332444(P2006−332444)

【出願日】平成18年12月8日(2006.12.8)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

【公開日】平成19年8月2日(2007.8.2)

【国際特許分類】

【出願日】平成18年12月8日(2006.12.8)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

[ Back to top ]