マイクロコンピュータ

【課題】セキュリティの向上を実現可能なマイクロコンピュータを提供する。

【解決手段】例えば、マイクロコンピュータに含まれる不揮発性メモリNVMEMにおいて、そのメモリアレイNVARY内にデータ保持寿命が10年以上となる第1メモリセル領域ARY1と、データ保持寿命が1〜365日となる第2メモリセル領域ARY2を設ける。このデータ保持寿命の違いを実現するため、ARY1に消去・書き込みを行う際には、基準電圧生成回路VRFGEN1に基づく消去・書き込み電圧を用い、ARY2に消去・書き込みを行う際には、基準電圧生成回路VRFGEN2に基づき、ARY1よりも絶対値が小さい消去・書き込み電圧を用いる。

【解決手段】例えば、マイクロコンピュータに含まれる不揮発性メモリNVMEMにおいて、そのメモリアレイNVARY内にデータ保持寿命が10年以上となる第1メモリセル領域ARY1と、データ保持寿命が1〜365日となる第2メモリセル領域ARY2を設ける。このデータ保持寿命の違いを実現するため、ARY1に消去・書き込みを行う際には、基準電圧生成回路VRFGEN1に基づく消去・書き込み電圧を用い、ARY2に消去・書き込みを行う際には、基準電圧生成回路VRFGEN2に基づき、ARY1よりも絶対値が小さい消去・書き込み電圧を用いる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロコンピュータに関し、特にICカード等を代表にセキュリティが必要な各種装置に搭載されるマイクロコンピュータに適用して有効な技術に関するものである。

【背景技術】

【0002】

例えば、キャッシュカード、クレジットカード、SIM(Subscriber Identity Module)カード等を代表とする接触型のICカードや、FeliCa(登録商標)などで知られている非接触型のICカードが広く流通している。このようなICカードには、通常、プロセッサ、不揮発性メモリおよび各種セキュリティ機能等を備えたマイクロコンピュータが搭載されている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

例えば、前述したようなICカード用マイクロコンピュータの不揮発性メモリには、個人情報データや、暗証番号、暗号鍵といったセキュリティ管理データなどのように重要性が高いデータが記憶されている。その中には、性質上、期限付きのアプリケーションやデータといったように一定期間が経過したら消えた方が都合がよいデータも含まれている。従来において、このようなデータは、例えばライセンスによる認証処理等によって期限管理が行われているが、データ自体が実際に消去される訳ではないため、認証処理の改竄によって不正アクセスが行われる可能性がある。

【0004】

そこで、本発明の目的の一つは、セキュリティの向上を実現可能なマイクロコンピュータを提供することにある。本発明の前記ならびにそれ以外の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0005】

本願において開示される発明の代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

【0006】

本発明の一実施の形態によるマイクロコンピュータは、不揮発性メモリを含み、この不揮発性メモリが、例えば10年以上のデータ保持寿命に設定される第1メモリセル領域と、例えば1〜365日のデータ保持寿命に設定される第2メモリセル領域とを備えたものとなっている。このデータ保持寿命の違いは、消去および/または書き込みの際に、第1メモリセル領域で使用する消去・書き込み電圧(絶対値)よりも第2メモリセル領域で使用する消去・書き込み電圧(絶対値)を小さくすることで実現する。この第2メモリセル領域に、有効期限が決められたデータなどを格納することで、セキュリティの向上が実現可能となる。

【発明の効果】

【0007】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すると、ICカード用のマイクロコンピュータ等において、セキュリティの向上が実現可能になる。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0009】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0010】

(実施の形態1)

図1は、本発明の実施の形態1によるマイクロコンピュータにおいて、その構成の一例を示すブロック図である。図1のマイクロコンピュータMCUは、単結晶シリコンのような1個の半導体基板にCMOS等の集積回路製造技術によって形成され、例えば、ICカードのプラスチック基板中に埋め込んで用いられる。MCUは、例えば、中央処理装置CPU、揮発性メモリRAM、不揮発性メモリNVMEM、コプロセッサCPRO、マスクロムMROM、システムコントロールロジックCTLLOG、入出力バッファBF、無線通信処理部RF、電源回路PW、アドレスバスBS_A、データバスBS_D等を備えている。

【0011】

データバスBS_Dは、CTLLOG、CPU、NVMEM、RAM、MROM、CPRO、およびRFに接続される。アドレスバスBS_Aは、CPU、NVMEM、RAM、MROM、CPRO、およびRFに接続される。RAMは、CPUのワーク領域若しくはデータの一時記憶領域として用いられる。コプロセッサCPROは、暗号処理等で用いられ、CPUの制御に従ってRSA等における剰余演算処理などを行う。MROMは、CPUの動作プログラムなどが格納される。不揮発性メモリNVMEMは、電気的に消去処理及び書き込み処理が可能とされ、例えば、EEPROM(Electrically Erasable and Programmable Read Only Memory)、フラッシュメモリ、強誘電体メモリ等である。NVMEMには、例えば、個人情報、認証証明書などの各種データや、あるいはアプリケーションプログラム等が格納される。

【0012】

ここで、MCUは、外部端子として、信号入出力端子IO、クロック端子CLK、リセット端子RES、電源端子VCC、接地端子VSS、アンテナ端子LA,LBを備えている。入出力バッファBFは、IO、CLK、RESに接続される。CLKからのクロック信号は、BFを介して全体に供給される。RESからのリセット信号は、BFを介してCPUに供給される。CPUは、リセット信号が入力されると、MROMに格納された動作プログラムを最初から実行する。IOから入力された信号は、BFを介してシステムコントロールロジックCTLLOGに入力される。CTLLOGは、この信号をデコードし、このデコード結果に応じた処理プログラムをCPUに実行させる。また、CTLLOGは、CPU等からのデータ信号をBFを介してIOに出力する。電源回路PWは、VCCおよびVSSに接続され、全体に電力を供給する。

【0013】

また、図1のMCUは、前述したようなIO、CLK、VCC、VSSを用いた有線通信処理(接触型処理)の他に、アンテナ端子LA,LBを用いた無線通信処理(非接触型処理)も可能な構成となっている。無線通信処理を行う場合、LA,LBから受信した搬送波を無線通信処理部RFを介して電源回路PWに供給し、PW内で整流処理や平滑処理等を行うことで電力を生成する。また、RFは、LA,LBからの無線受信信号を復調して信号成分を検出し、この結果をBS_Dを介してCTLLOGに伝送し、逆に、CTLLOGからBS_Dを介して得られた送信データで変調を行うことで無線送信信号を生成する。この際のCTLLOGの処理内容に関しては、前述した有線通信処理の場合と同様である。なお、図1のMCUは、有線通信処理と無線通信処理の両方を備えるものとしたが、勿論、一方のみを備える構成であってもよい。また、MCU内の各回路ブロック構成は、それに限定されるものではなく、必要に応じて適宜変更可能である。

【0014】

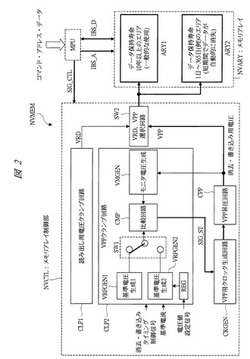

図2は、図1のマイクロプロセッサにおいて、その不揮発性メモリNVMEMの詳細な構成例を示すブロック図である。図2に示す不揮発性メモリNVMEMは、メモリアレイNVARYと、NVARYに対して動作に必要な各種電圧を供給するメモリアレイ制御部NVCTLと、制御プロセッサMPUなどによって構成される。MPUは、外部からの読み出し・書き込み・消去命令(コマンド、アドレス、データ)に応じて制御信号SIG_CTLによりNVCTLを制御すると共に、内部アドレスバスIBS_Aおよび内部データバスIBS_Dを介してNVARY内の所定のメモリセルにアクセスする。

【0015】

メモリアレイ制御部NVCTLは、読み出し用電圧VRD(例えば−2V程度)を設定するクランプ回路CLP1、書き込み及び消去用電圧VPP(例えば−10Vなど)を設定するクランプ回路CLP2、クロック生成回路CKGEN、昇圧回路(チャージポンプ回路)CPP、VRD・VPP選択回路SW2を備えている。CLP2は、2個の基準電圧生成回路VRFGEN1,VRFGEN2と、選択回路SW1と、比較回路CMPと、モニタ電圧生成回路VMGENと、設定レジスタREGを備えている。VRFGEN1,VRFGEN2のそれぞれは、基準電流を用いてそれぞれ異なる電圧を生成する。この際、VRFGEN2の生成電圧は、設定レジスタREGによって任意に設定される。

【0016】

図3は、図2における基準電圧生成回路VRFGEN1,VRFGEN2の動作例を示す説明図である。図3に示すように、VRFGEN2は、VRFGEN1と比較して絶対値が小さい電圧を生成する。すなわち、VRFGEN1は、メモリアレイNVARY内のメモリセルの消去(ここでは‘1’レベルとする)や書き込み(ここでは‘0’レベルとする)を十分に行うために必要な電圧(消去用:VPPE1、書き込み用:VPPW1)を生成する。一方、VRFGEN2は、メモリセルの消去および書き込みを十分に行えない程度の電圧(消去用:VPPE2、書き込み用:VPPW2)を生成する。

【0017】

図2の選択回路SW1は、このVRFGEN1かVRFGEN2の一方の電圧を選択し、比較回路CMPに出力する。CMPは、このSW1からの電圧と、昇圧回路CPPの出力電圧を反映して生成されたモニタ電圧生成回路VMGENからのモニタ電圧とを比較して、クロック生成回路CKGENに対して制御信号SIG_STを出力する。特に限定はされないが、例えば、SW1からの電圧よりもVMGENからのモニタ電圧の方が高かった場合には、SIG_STによってCKGENからCPPに向けたクロック供給が停止するように制御され、これに伴いCPPは、昇圧動作を停止してその出力電圧が低下していく。逆に、SW1からの電圧よりもVMGENからのモニタ電圧の方が低かった場合には、SIG_STによってCKGENからCPPに向けたクロック供給が行われるように制御され、これに伴いCPPは、昇圧動作を行ってその出力電圧が上昇していく。

【0018】

選択回路SW2は、この昇圧回路CPPからの出力電圧(消去・書き込み用電圧)VPPかクランプ回路CLP1からの出力電圧(読み出し用電圧)VRDかを選択して、メモリアレイNVARYに供給する。この出力電圧を供給するタイミングや、SW1およびSW2の選択や、設定レジスタREGの設定値などは、MPUによって制御される。メモリアレイNVARYは、第1メモリセル領域ARY1と、第2メモリセル領域ARY2を備えている。ARY1は、例えばデータ保持寿命が10年以上といった一般的な記憶領域であり、ARY2は、例えばデータ保持寿命が1〜365日といった本実施の形態の特徴となる記憶領域である。ここでは、ARY1とARY2内のメモリセル構成自体には差異はなく、前述したデータ保持寿命の違いは、ARY1においてVRFGEN1からの基準電圧を用い、ARY2においてVRFGEN2からの基準電圧を用いることで実現する。

【0019】

図4は、図2のメモリアレイNVARYにおいて、そのデータ保持特性の一例を示す説明図である。一般的に、不揮発性メモリのデータ保持寿命は、消去・書き込みに伴うしきい値電圧Vthの大きさに左右され、消去・書き込み時の絶対値電圧(VPP)が低くなるほど、消去・書き込みが浅くなり、データ保持寿命が短くなる。本実施の形態では、この特性を利用して、図2の第2メモリセル領域ARY2におけるデータ保持寿命を制御する。図4に示すように、例えば、書き込み時に図3のVPPW1を用いた場合にはしきい値電圧Vth0aとなり、10年以上のデータ保持寿命を実現することができる。一方、書き込み時に図3のVPPW2を用い、その絶対値電圧を相対的に高めに設定した場合にはしきい値電圧Vth0bとなり、相対的に低めに設定した場合にはしきい値電圧Vth0cとなり、このVth0b〜Vth0cの間で365日〜1日といったデータ保持寿命を実現することができる。

【0020】

同様にして、例えば、消去時に図3のVPPE1を用いた場合にはしきい値電圧Vth1aとなり、10年以上のデータ保持寿命を実現することができる。一方、消去時に図3のVPPE2を用い、その絶対値電圧を相対的に高めに設定した場合にはしきい値電圧Vth1bとなり、相対的に低めに設定した場合にはしきい値電圧Vth1cとなり、このVth1b〜Vth1cの間で365日〜1日といったデータ保持寿命を実現することができる。なお、特に限定はされないが、メモリアレイNVARY内の各メモリセル(図示せず)を消去する場合には、例えばゲート:VPP(−10V等)、ソース:2V、ドレイン:オープンとし、フローティングゲート内の電子をソース側に引き抜けばよい。逆に、各メモリセル(図示せず)に書き込みを行う場合には、例えばゲート:2V、ソース:VPP(−10V等)、ドレイン:オープンとし、フローティングゲート内に電子を蓄えればよい。また、読み出しを行う場合には、例えばソース:0V、ドレイン:1V、ゲート:−2Vとすればよい。これらの電圧条件は、通常、メモリセルの構造や仕様によって異なるが、いずれにしても、消去および書き込みを行う際には高電圧(VPP)が必要とされ、この高電圧の電圧値を制御することで、メモリセルのデータ保持寿命を制御することができる。

【0021】

なお、第2メモリセル領域ARY2では、理想的には、図4に示すように、消去状態および書き込み状態ともにしきい値電圧が浅くなるように電圧調整を行うことが望ましいが、制御の複雑化を避けるため、場合によっては消去時か書き込み時のいずれか一方のみの電圧を変更することも可能である。この場合、例えば、通常通りの深い消去を行った上で浅い書き込みを行うこととなるが、仮に浅い書き込み状態のメモリセルのしきい値が判定不能レベルとなっても、その判定不能状態を書き込み状態として取り扱えば原理的にはデータを復元できることになり、セキュリティは若干低下する。ただし、データを復元しない限り当該不揮発性メモリのデータを用いてCPU等が処理を行うことはできないため、実使用上は、ある程度のセキュリティは確保できる。

【0022】

以上、本実施の形態1のマイクロコンピュータを用いることで、期限付きのアプリケーションやデータといったように一定期間が経過したら消えた方が都合がよい情報に関して、その期限を確実に管理することが可能となる。これによって、セキュリティの向上が実現可能になる。なお、この際の期限の長さは、例えば、予め設定コマンド等によってMPUを介して設定レジスタREGに所定値を設定すればよい。また、図2においては、2個の基準電圧生成回路VRFGEN1,VRFGEN2を設け、いずれかの出力電圧を選択する構成例としたが、1個の基準電圧生成回路を設け、その出力電圧を適宜変更する構成例とすることも可能である。ただし、この場合、出力電圧を変更する毎に、その電圧が安定するまで待ち時間を設ける必要がある。

【0023】

(実施の形態2)

本実施の形態2では、図2で述べた第1メモリセル領域ARY1および第2メモリセル領域ARY2の別の実現方法について述べる。前述した実施の形態1では、消去・書き込み電圧を変更することでARY1,ARY2を実現したが、本実施の形態2では、図示はしないが、ARY1と比較して、意図的にARY2内の各メモリセルを予め劣化させておくことでARY1,ARY2を実現する。具体的には、例えば予め製造段階で、ARY2内のみに消去と書き込みを繰り返し行うことなどでストレスを印可し、メモリセルのデータ保持特性を劣化させておく。ただし、この場合、データ保持寿命はある程度固定として取り扱う必要がある。

【0024】

(実施の形態3)

本実施の形態3では、実施の形態1,2で説明したマイクロコンピュータの適用例について説明を行う。図5は、本発明の実施の形態3によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。図5(a)においては、前述したマイクロコンピュータMCUが搭載された非接触型ICカードICCD1が示されている。ICCD1は、周辺にループ状のアンテナATNが形成され、このATNの一端と他端がMCUのアンテナ端子LA,LBにそれぞれ接続される。ICCD1は、例えば電子入場券などである。電子入場券には、通常、有効期限が定まっており、有効期限が過ぎた際にデータが消滅するとセキュリティの向上が図れる。

【0025】

そこで、図5(b)に示すように、電子入場券を提供する側(メーカー側)が、データ属性を判別して(S501)、短時間で消したくないデータを格納したい場合には基準電圧生成回路VRFGEN1が選択されるように操作を行い(S502)、短時間で消したいデータを格納したい場合にはVRFGEN2が選択されるように操作を行う(S505)。短時間で消したいデータは、例えば、入場のアクセス権限を示すデータであったり、何らかの試用プログラムであったりする。また、この基準電圧生成回路の選択は、特に限定はされないが、例えば、VRFGEN2を用いた消去動作や書き込み動作に対応して、予め不揮発性メモリNVMEMに特殊コマンド等を設け、ユーザがこの特殊コマンドを用いる操作を行えばよい。

【0026】

VRFGEN1が選択されると、ユーザの指示に基づいて、マイクロコンピュータMCUは、必要なデータをメモリアレイNVARYの第1メモリセル領域ARY1に書き込む(S503)。なお、図示は省略しているが、この書き込み動作の前に、ARY1は、予めVRFGEN1を用いて消去動作が行われている。このような動作を経て、ARY1のデータは、データ保持特性が10年以上のデータとなる(S504)。一方、VRFGEN2が選択されると、ユーザの指示に基づいて、MCUは、必要なデータをNVARYの第2メモリセル領域ARY2に書き込む(S506)。なお、図示は省略しているが、この書き込み動作の前に、ARY2は、予めVRFGEN2(あるいはVRFGEN1)を用いて消去動作が行われている。このような動作を経て、ARY2のデータは、データ保持特性が例えば1日〜365日のデータとなる(S507)。

【0027】

(実施の形態4)

本実施の形態4では、実施の形態1,2で説明したマイクロコンピュータの他の適用例について説明を行う。図6は、本発明の実施の形態4によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。図6(a)においては、接触型ICカードICCD2が挿入された携帯電話機MPHが示され、このICCD2に前述したマイクロコンピュータMCUが搭載されている。ICCD2は、例えばSIMカードなどである。携帯電話機MPHでは、音楽データや試用のアプリケーションデータなど有効期限が定まったデータがダウンロードされる場合が数多くあり、有効期限が過ぎた際にデータが消滅するとセキュリティの向上が図れる。

【0028】

そこで、図6(b)に示すように、携帯電話機MPHの使用者の操作に基づいて、MPHにデータがダウンロードされると(S601)、マイクロコンピュータMCUは、当該データの付属情報等を参照してデータ属性を判別する(S602)。その結果、MCUは、当該データが短時間で消したくないデータであった場合は基準電圧生成回路VRFGEN1が選択されるように制御を行い(S603)、短時間で消したいデータであった場合はVRFGEN2が選択されるように制御を行う(S606)。この基準電圧生成回路の選択制御は、特に限定はされないが、例えば、VRFGEN2を用いた消去動作や書き込み動作に対応して、予め不揮発性メモリNVMEMに特殊コマンド等を設けておけばよい。

【0029】

VRFGEN1が選択されると、MCUは、必要なデータをメモリアレイNVARYの第1メモリセル領域ARY1に書き込む(S604)。なお、図示は省略しているが、この書き込み動作の前に、ARY1は、予めVRFGEN1を用いて消去動作が行われている。このような動作を経て、ARY1のデータは、データ保持特性が10年以上のデータとなる(S605)。一方、VRFGEN2が選択されると、MCUは、必要なデータをNVARYの第2メモリセル領域ARY2に書き込む(S607)。なお、図示は省略しているが、この書き込み動作の前に、ARY2は、予めVRFGEN2(あるいはVRFGEN1)を用いて消去動作が行われている。このような動作を経て、ARY2のデータは、データ保持特性が例えば1日〜365日のデータとなる(S608)。

【0030】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【0031】

例えば、前述した実施の形態では、基準電圧生成回路VRFGEN1,VRFGEN2共に、消去時と書き込み時で同一の高電圧(VPP)を用いる構成としたが、勿論、同一値である必要はなく、消去時と書き込み時で若干異なる電圧値であってもよい。すなわち、|VRFGEN1での書き込み電圧|>|VRFGEN2での書き込み電圧|で、かつ|VRFGEN1での消去電圧|>|VRFGEN2での消去電圧|の関係が満たされていればよい。

【産業上の利用可能性】

【0032】

本発明の一実施の形態によるマイクロコンピュータは、特に、ICカード等に搭載される不揮発性メモリ内蔵のマイクロコンピュータに適用して有益な技術であり、これに限らず、不揮発性メモリ内蔵のマイクロコンピュータ全般に対して広く適用可能である。

【図面の簡単な説明】

【0033】

【図1】本発明の実施の形態1によるマイクロコンピュータにおいて、その構成の一例を示すブロック図である。

【図2】図1のマイクロプロセッサにおいて、その不揮発性メモリの詳細な構成例を示すブロック図である。

【図3】図2における基準電圧生成回路の動作例を示す説明図である。

【図4】図2のメモリアレイにおいて、そのデータ保持特性の一例を示す説明図である。

【図5】本発明の実施の形態3によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。

【図6】本発明の実施の形態4によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。

【符号の説明】

【0034】

MCU マイクロコンピュータ

BF 入出力バッファ

CPU 中央処理装置

NVMEM 不揮発性メモリ

RAM 揮発性メモリ

MROM マスクロム

CPRO コプロセッサ

BS,IBS バス

RF 無線通信処理部

PW 電源回路

CTLLOG システムコントロールロジック

IO 信号入出力端子

CLK クロック端子

RES リセット端子

LA,LB アンテナ端子

VCC 電源端子

VSS 接地端子

NVCTL メモリアレイ制御部

NVARY メモリアレイ

ARY1,ARY2 メモリセル領域

MPU 制御プロセッサ

CLP クランプ回路

VRFGEN 基準電圧生成回路

REG 設定レジスタ

SW 選択回路

CMP 比較回路

VMGEN モニタ電圧生成回路

CKGEN クロック生成回路

CPP 昇圧回路

ATN アンテナ

ICCD ICカード

MPH 携帯電話機

【技術分野】

【0001】

本発明は、マイクロコンピュータに関し、特にICカード等を代表にセキュリティが必要な各種装置に搭載されるマイクロコンピュータに適用して有効な技術に関するものである。

【背景技術】

【0002】

例えば、キャッシュカード、クレジットカード、SIM(Subscriber Identity Module)カード等を代表とする接触型のICカードや、FeliCa(登録商標)などで知られている非接触型のICカードが広く流通している。このようなICカードには、通常、プロセッサ、不揮発性メモリおよび各種セキュリティ機能等を備えたマイクロコンピュータが搭載されている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

例えば、前述したようなICカード用マイクロコンピュータの不揮発性メモリには、個人情報データや、暗証番号、暗号鍵といったセキュリティ管理データなどのように重要性が高いデータが記憶されている。その中には、性質上、期限付きのアプリケーションやデータといったように一定期間が経過したら消えた方が都合がよいデータも含まれている。従来において、このようなデータは、例えばライセンスによる認証処理等によって期限管理が行われているが、データ自体が実際に消去される訳ではないため、認証処理の改竄によって不正アクセスが行われる可能性がある。

【0004】

そこで、本発明の目的の一つは、セキュリティの向上を実現可能なマイクロコンピュータを提供することにある。本発明の前記ならびにそれ以外の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0005】

本願において開示される発明の代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

【0006】

本発明の一実施の形態によるマイクロコンピュータは、不揮発性メモリを含み、この不揮発性メモリが、例えば10年以上のデータ保持寿命に設定される第1メモリセル領域と、例えば1〜365日のデータ保持寿命に設定される第2メモリセル領域とを備えたものとなっている。このデータ保持寿命の違いは、消去および/または書き込みの際に、第1メモリセル領域で使用する消去・書き込み電圧(絶対値)よりも第2メモリセル領域で使用する消去・書き込み電圧(絶対値)を小さくすることで実現する。この第2メモリセル領域に、有効期限が決められたデータなどを格納することで、セキュリティの向上が実現可能となる。

【発明の効果】

【0007】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すると、ICカード用のマイクロコンピュータ等において、セキュリティの向上が実現可能になる。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0009】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0010】

(実施の形態1)

図1は、本発明の実施の形態1によるマイクロコンピュータにおいて、その構成の一例を示すブロック図である。図1のマイクロコンピュータMCUは、単結晶シリコンのような1個の半導体基板にCMOS等の集積回路製造技術によって形成され、例えば、ICカードのプラスチック基板中に埋め込んで用いられる。MCUは、例えば、中央処理装置CPU、揮発性メモリRAM、不揮発性メモリNVMEM、コプロセッサCPRO、マスクロムMROM、システムコントロールロジックCTLLOG、入出力バッファBF、無線通信処理部RF、電源回路PW、アドレスバスBS_A、データバスBS_D等を備えている。

【0011】

データバスBS_Dは、CTLLOG、CPU、NVMEM、RAM、MROM、CPRO、およびRFに接続される。アドレスバスBS_Aは、CPU、NVMEM、RAM、MROM、CPRO、およびRFに接続される。RAMは、CPUのワーク領域若しくはデータの一時記憶領域として用いられる。コプロセッサCPROは、暗号処理等で用いられ、CPUの制御に従ってRSA等における剰余演算処理などを行う。MROMは、CPUの動作プログラムなどが格納される。不揮発性メモリNVMEMは、電気的に消去処理及び書き込み処理が可能とされ、例えば、EEPROM(Electrically Erasable and Programmable Read Only Memory)、フラッシュメモリ、強誘電体メモリ等である。NVMEMには、例えば、個人情報、認証証明書などの各種データや、あるいはアプリケーションプログラム等が格納される。

【0012】

ここで、MCUは、外部端子として、信号入出力端子IO、クロック端子CLK、リセット端子RES、電源端子VCC、接地端子VSS、アンテナ端子LA,LBを備えている。入出力バッファBFは、IO、CLK、RESに接続される。CLKからのクロック信号は、BFを介して全体に供給される。RESからのリセット信号は、BFを介してCPUに供給される。CPUは、リセット信号が入力されると、MROMに格納された動作プログラムを最初から実行する。IOから入力された信号は、BFを介してシステムコントロールロジックCTLLOGに入力される。CTLLOGは、この信号をデコードし、このデコード結果に応じた処理プログラムをCPUに実行させる。また、CTLLOGは、CPU等からのデータ信号をBFを介してIOに出力する。電源回路PWは、VCCおよびVSSに接続され、全体に電力を供給する。

【0013】

また、図1のMCUは、前述したようなIO、CLK、VCC、VSSを用いた有線通信処理(接触型処理)の他に、アンテナ端子LA,LBを用いた無線通信処理(非接触型処理)も可能な構成となっている。無線通信処理を行う場合、LA,LBから受信した搬送波を無線通信処理部RFを介して電源回路PWに供給し、PW内で整流処理や平滑処理等を行うことで電力を生成する。また、RFは、LA,LBからの無線受信信号を復調して信号成分を検出し、この結果をBS_Dを介してCTLLOGに伝送し、逆に、CTLLOGからBS_Dを介して得られた送信データで変調を行うことで無線送信信号を生成する。この際のCTLLOGの処理内容に関しては、前述した有線通信処理の場合と同様である。なお、図1のMCUは、有線通信処理と無線通信処理の両方を備えるものとしたが、勿論、一方のみを備える構成であってもよい。また、MCU内の各回路ブロック構成は、それに限定されるものではなく、必要に応じて適宜変更可能である。

【0014】

図2は、図1のマイクロプロセッサにおいて、その不揮発性メモリNVMEMの詳細な構成例を示すブロック図である。図2に示す不揮発性メモリNVMEMは、メモリアレイNVARYと、NVARYに対して動作に必要な各種電圧を供給するメモリアレイ制御部NVCTLと、制御プロセッサMPUなどによって構成される。MPUは、外部からの読み出し・書き込み・消去命令(コマンド、アドレス、データ)に応じて制御信号SIG_CTLによりNVCTLを制御すると共に、内部アドレスバスIBS_Aおよび内部データバスIBS_Dを介してNVARY内の所定のメモリセルにアクセスする。

【0015】

メモリアレイ制御部NVCTLは、読み出し用電圧VRD(例えば−2V程度)を設定するクランプ回路CLP1、書き込み及び消去用電圧VPP(例えば−10Vなど)を設定するクランプ回路CLP2、クロック生成回路CKGEN、昇圧回路(チャージポンプ回路)CPP、VRD・VPP選択回路SW2を備えている。CLP2は、2個の基準電圧生成回路VRFGEN1,VRFGEN2と、選択回路SW1と、比較回路CMPと、モニタ電圧生成回路VMGENと、設定レジスタREGを備えている。VRFGEN1,VRFGEN2のそれぞれは、基準電流を用いてそれぞれ異なる電圧を生成する。この際、VRFGEN2の生成電圧は、設定レジスタREGによって任意に設定される。

【0016】

図3は、図2における基準電圧生成回路VRFGEN1,VRFGEN2の動作例を示す説明図である。図3に示すように、VRFGEN2は、VRFGEN1と比較して絶対値が小さい電圧を生成する。すなわち、VRFGEN1は、メモリアレイNVARY内のメモリセルの消去(ここでは‘1’レベルとする)や書き込み(ここでは‘0’レベルとする)を十分に行うために必要な電圧(消去用:VPPE1、書き込み用:VPPW1)を生成する。一方、VRFGEN2は、メモリセルの消去および書き込みを十分に行えない程度の電圧(消去用:VPPE2、書き込み用:VPPW2)を生成する。

【0017】

図2の選択回路SW1は、このVRFGEN1かVRFGEN2の一方の電圧を選択し、比較回路CMPに出力する。CMPは、このSW1からの電圧と、昇圧回路CPPの出力電圧を反映して生成されたモニタ電圧生成回路VMGENからのモニタ電圧とを比較して、クロック生成回路CKGENに対して制御信号SIG_STを出力する。特に限定はされないが、例えば、SW1からの電圧よりもVMGENからのモニタ電圧の方が高かった場合には、SIG_STによってCKGENからCPPに向けたクロック供給が停止するように制御され、これに伴いCPPは、昇圧動作を停止してその出力電圧が低下していく。逆に、SW1からの電圧よりもVMGENからのモニタ電圧の方が低かった場合には、SIG_STによってCKGENからCPPに向けたクロック供給が行われるように制御され、これに伴いCPPは、昇圧動作を行ってその出力電圧が上昇していく。

【0018】

選択回路SW2は、この昇圧回路CPPからの出力電圧(消去・書き込み用電圧)VPPかクランプ回路CLP1からの出力電圧(読み出し用電圧)VRDかを選択して、メモリアレイNVARYに供給する。この出力電圧を供給するタイミングや、SW1およびSW2の選択や、設定レジスタREGの設定値などは、MPUによって制御される。メモリアレイNVARYは、第1メモリセル領域ARY1と、第2メモリセル領域ARY2を備えている。ARY1は、例えばデータ保持寿命が10年以上といった一般的な記憶領域であり、ARY2は、例えばデータ保持寿命が1〜365日といった本実施の形態の特徴となる記憶領域である。ここでは、ARY1とARY2内のメモリセル構成自体には差異はなく、前述したデータ保持寿命の違いは、ARY1においてVRFGEN1からの基準電圧を用い、ARY2においてVRFGEN2からの基準電圧を用いることで実現する。

【0019】

図4は、図2のメモリアレイNVARYにおいて、そのデータ保持特性の一例を示す説明図である。一般的に、不揮発性メモリのデータ保持寿命は、消去・書き込みに伴うしきい値電圧Vthの大きさに左右され、消去・書き込み時の絶対値電圧(VPP)が低くなるほど、消去・書き込みが浅くなり、データ保持寿命が短くなる。本実施の形態では、この特性を利用して、図2の第2メモリセル領域ARY2におけるデータ保持寿命を制御する。図4に示すように、例えば、書き込み時に図3のVPPW1を用いた場合にはしきい値電圧Vth0aとなり、10年以上のデータ保持寿命を実現することができる。一方、書き込み時に図3のVPPW2を用い、その絶対値電圧を相対的に高めに設定した場合にはしきい値電圧Vth0bとなり、相対的に低めに設定した場合にはしきい値電圧Vth0cとなり、このVth0b〜Vth0cの間で365日〜1日といったデータ保持寿命を実現することができる。

【0020】

同様にして、例えば、消去時に図3のVPPE1を用いた場合にはしきい値電圧Vth1aとなり、10年以上のデータ保持寿命を実現することができる。一方、消去時に図3のVPPE2を用い、その絶対値電圧を相対的に高めに設定した場合にはしきい値電圧Vth1bとなり、相対的に低めに設定した場合にはしきい値電圧Vth1cとなり、このVth1b〜Vth1cの間で365日〜1日といったデータ保持寿命を実現することができる。なお、特に限定はされないが、メモリアレイNVARY内の各メモリセル(図示せず)を消去する場合には、例えばゲート:VPP(−10V等)、ソース:2V、ドレイン:オープンとし、フローティングゲート内の電子をソース側に引き抜けばよい。逆に、各メモリセル(図示せず)に書き込みを行う場合には、例えばゲート:2V、ソース:VPP(−10V等)、ドレイン:オープンとし、フローティングゲート内に電子を蓄えればよい。また、読み出しを行う場合には、例えばソース:0V、ドレイン:1V、ゲート:−2Vとすればよい。これらの電圧条件は、通常、メモリセルの構造や仕様によって異なるが、いずれにしても、消去および書き込みを行う際には高電圧(VPP)が必要とされ、この高電圧の電圧値を制御することで、メモリセルのデータ保持寿命を制御することができる。

【0021】

なお、第2メモリセル領域ARY2では、理想的には、図4に示すように、消去状態および書き込み状態ともにしきい値電圧が浅くなるように電圧調整を行うことが望ましいが、制御の複雑化を避けるため、場合によっては消去時か書き込み時のいずれか一方のみの電圧を変更することも可能である。この場合、例えば、通常通りの深い消去を行った上で浅い書き込みを行うこととなるが、仮に浅い書き込み状態のメモリセルのしきい値が判定不能レベルとなっても、その判定不能状態を書き込み状態として取り扱えば原理的にはデータを復元できることになり、セキュリティは若干低下する。ただし、データを復元しない限り当該不揮発性メモリのデータを用いてCPU等が処理を行うことはできないため、実使用上は、ある程度のセキュリティは確保できる。

【0022】

以上、本実施の形態1のマイクロコンピュータを用いることで、期限付きのアプリケーションやデータといったように一定期間が経過したら消えた方が都合がよい情報に関して、その期限を確実に管理することが可能となる。これによって、セキュリティの向上が実現可能になる。なお、この際の期限の長さは、例えば、予め設定コマンド等によってMPUを介して設定レジスタREGに所定値を設定すればよい。また、図2においては、2個の基準電圧生成回路VRFGEN1,VRFGEN2を設け、いずれかの出力電圧を選択する構成例としたが、1個の基準電圧生成回路を設け、その出力電圧を適宜変更する構成例とすることも可能である。ただし、この場合、出力電圧を変更する毎に、その電圧が安定するまで待ち時間を設ける必要がある。

【0023】

(実施の形態2)

本実施の形態2では、図2で述べた第1メモリセル領域ARY1および第2メモリセル領域ARY2の別の実現方法について述べる。前述した実施の形態1では、消去・書き込み電圧を変更することでARY1,ARY2を実現したが、本実施の形態2では、図示はしないが、ARY1と比較して、意図的にARY2内の各メモリセルを予め劣化させておくことでARY1,ARY2を実現する。具体的には、例えば予め製造段階で、ARY2内のみに消去と書き込みを繰り返し行うことなどでストレスを印可し、メモリセルのデータ保持特性を劣化させておく。ただし、この場合、データ保持寿命はある程度固定として取り扱う必要がある。

【0024】

(実施の形態3)

本実施の形態3では、実施の形態1,2で説明したマイクロコンピュータの適用例について説明を行う。図5は、本発明の実施の形態3によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。図5(a)においては、前述したマイクロコンピュータMCUが搭載された非接触型ICカードICCD1が示されている。ICCD1は、周辺にループ状のアンテナATNが形成され、このATNの一端と他端がMCUのアンテナ端子LA,LBにそれぞれ接続される。ICCD1は、例えば電子入場券などである。電子入場券には、通常、有効期限が定まっており、有効期限が過ぎた際にデータが消滅するとセキュリティの向上が図れる。

【0025】

そこで、図5(b)に示すように、電子入場券を提供する側(メーカー側)が、データ属性を判別して(S501)、短時間で消したくないデータを格納したい場合には基準電圧生成回路VRFGEN1が選択されるように操作を行い(S502)、短時間で消したいデータを格納したい場合にはVRFGEN2が選択されるように操作を行う(S505)。短時間で消したいデータは、例えば、入場のアクセス権限を示すデータであったり、何らかの試用プログラムであったりする。また、この基準電圧生成回路の選択は、特に限定はされないが、例えば、VRFGEN2を用いた消去動作や書き込み動作に対応して、予め不揮発性メモリNVMEMに特殊コマンド等を設け、ユーザがこの特殊コマンドを用いる操作を行えばよい。

【0026】

VRFGEN1が選択されると、ユーザの指示に基づいて、マイクロコンピュータMCUは、必要なデータをメモリアレイNVARYの第1メモリセル領域ARY1に書き込む(S503)。なお、図示は省略しているが、この書き込み動作の前に、ARY1は、予めVRFGEN1を用いて消去動作が行われている。このような動作を経て、ARY1のデータは、データ保持特性が10年以上のデータとなる(S504)。一方、VRFGEN2が選択されると、ユーザの指示に基づいて、MCUは、必要なデータをNVARYの第2メモリセル領域ARY2に書き込む(S506)。なお、図示は省略しているが、この書き込み動作の前に、ARY2は、予めVRFGEN2(あるいはVRFGEN1)を用いて消去動作が行われている。このような動作を経て、ARY2のデータは、データ保持特性が例えば1日〜365日のデータとなる(S507)。

【0027】

(実施の形態4)

本実施の形態4では、実施の形態1,2で説明したマイクロコンピュータの他の適用例について説明を行う。図6は、本発明の実施の形態4によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。図6(a)においては、接触型ICカードICCD2が挿入された携帯電話機MPHが示され、このICCD2に前述したマイクロコンピュータMCUが搭載されている。ICCD2は、例えばSIMカードなどである。携帯電話機MPHでは、音楽データや試用のアプリケーションデータなど有効期限が定まったデータがダウンロードされる場合が数多くあり、有効期限が過ぎた際にデータが消滅するとセキュリティの向上が図れる。

【0028】

そこで、図6(b)に示すように、携帯電話機MPHの使用者の操作に基づいて、MPHにデータがダウンロードされると(S601)、マイクロコンピュータMCUは、当該データの付属情報等を参照してデータ属性を判別する(S602)。その結果、MCUは、当該データが短時間で消したくないデータであった場合は基準電圧生成回路VRFGEN1が選択されるように制御を行い(S603)、短時間で消したいデータであった場合はVRFGEN2が選択されるように制御を行う(S606)。この基準電圧生成回路の選択制御は、特に限定はされないが、例えば、VRFGEN2を用いた消去動作や書き込み動作に対応して、予め不揮発性メモリNVMEMに特殊コマンド等を設けておけばよい。

【0029】

VRFGEN1が選択されると、MCUは、必要なデータをメモリアレイNVARYの第1メモリセル領域ARY1に書き込む(S604)。なお、図示は省略しているが、この書き込み動作の前に、ARY1は、予めVRFGEN1を用いて消去動作が行われている。このような動作を経て、ARY1のデータは、データ保持特性が10年以上のデータとなる(S605)。一方、VRFGEN2が選択されると、MCUは、必要なデータをNVARYの第2メモリセル領域ARY2に書き込む(S607)。なお、図示は省略しているが、この書き込み動作の前に、ARY2は、予めVRFGEN2(あるいはVRFGEN1)を用いて消去動作が行われている。このような動作を経て、ARY2のデータは、データ保持特性が例えば1日〜365日のデータとなる(S608)。

【0030】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【0031】

例えば、前述した実施の形態では、基準電圧生成回路VRFGEN1,VRFGEN2共に、消去時と書き込み時で同一の高電圧(VPP)を用いる構成としたが、勿論、同一値である必要はなく、消去時と書き込み時で若干異なる電圧値であってもよい。すなわち、|VRFGEN1での書き込み電圧|>|VRFGEN2での書き込み電圧|で、かつ|VRFGEN1での消去電圧|>|VRFGEN2での消去電圧|の関係が満たされていればよい。

【産業上の利用可能性】

【0032】

本発明の一実施の形態によるマイクロコンピュータは、特に、ICカード等に搭載される不揮発性メモリ内蔵のマイクロコンピュータに適用して有益な技術であり、これに限らず、不揮発性メモリ内蔵のマイクロコンピュータ全般に対して広く適用可能である。

【図面の簡単な説明】

【0033】

【図1】本発明の実施の形態1によるマイクロコンピュータにおいて、その構成の一例を示すブロック図である。

【図2】図1のマイクロプロセッサにおいて、その不揮発性メモリの詳細な構成例を示すブロック図である。

【図3】図2における基準電圧生成回路の動作例を示す説明図である。

【図4】図2のメモリアレイにおいて、そのデータ保持特性の一例を示す説明図である。

【図5】本発明の実施の形態3によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。

【図6】本発明の実施の形態4によるマイクロコンピュータの適用例を示すものであり、(a)はそれを適用した構成例を示す概略図、(b)は(a)の動作例を示す説明図である。

【符号の説明】

【0034】

MCU マイクロコンピュータ

BF 入出力バッファ

CPU 中央処理装置

NVMEM 不揮発性メモリ

RAM 揮発性メモリ

MROM マスクロム

CPRO コプロセッサ

BS,IBS バス

RF 無線通信処理部

PW 電源回路

CTLLOG システムコントロールロジック

IO 信号入出力端子

CLK クロック端子

RES リセット端子

LA,LB アンテナ端子

VCC 電源端子

VSS 接地端子

NVCTL メモリアレイ制御部

NVARY メモリアレイ

ARY1,ARY2 メモリセル領域

MPU 制御プロセッサ

CLP クランプ回路

VRFGEN 基準電圧生成回路

REG 設定レジスタ

SW 選択回路

CMP 比較回路

VMGEN モニタ電圧生成回路

CKGEN クロック生成回路

CPP 昇圧回路

ATN アンテナ

ICCD ICカード

MPH 携帯電話機

【特許請求の範囲】

【請求項1】

プロセッサと、

バスを介して前記プロセッサに接続される不揮発性メモリとを備え、

前記不揮発性メモリは、

データ保持寿命が第1期間以上に設定される第1メモリセル領域と、

データ保持寿命が前記第1期間よりも短い第2期間以内に設定される第2メモリセル領域と、

消去時および/または書き込み時に前記第1期間に対応して前記第1メモリセル領域内の各メモリセルに印加される第1電圧と、前記第1電圧よりも絶対値が小さく、消去時および/または書き込み時に前記第2期間に対応して前記第2メモリセル領域内の各メモリセルに印加される第2電圧とを生成する電圧生成手段とを有することを特徴とするマイクロコンピュータ。

【請求項2】

請求項1記載のマイクロコンピュータにおいて、

前記電圧生成手段は、

前記第1電圧の基準となる第1基準電圧を生成する第1基準電圧生成回路と、

前記第2電圧の基準となる第2基準電圧を生成する第2基準電圧生成回路と、

前記第1基準電圧か前記第2基準電圧かを選択して出力する選択回路と、

昇圧によって前記第1電圧または前記第2電圧を生成する昇圧回路と、

前記昇圧回路の出力電圧を反映したモニタ電圧を生成するモニタ電圧生成回路と、

前記モニタ電圧と前記選択回路の出力電圧とを比較し、その比較結果に応じて前記昇圧回路での昇圧動作を制御する比較回路とを有することを特徴とするマイクロコンピュータ。

【請求項3】

請求項1記載のマイクロコンピュータにおいて、さらに、

前記第2電圧の電圧値を任意に設定可能にする設定手段を有することを特徴とするマイクロコンピュータ。

【請求項4】

請求項1〜3のいずれか1項に記載のマイクロコンピュータにおいて、

前記第2期間は、1年以内であることを特徴とするマイクロコンピュータ。

【請求項5】

請求項1〜3のいずれか1項に記載のマイクロコンピュータにおいて、

前記マイクロコンピュータは、ICカードに搭載されることを特徴とするマイクロコンピュータ。

【請求項1】

プロセッサと、

バスを介して前記プロセッサに接続される不揮発性メモリとを備え、

前記不揮発性メモリは、

データ保持寿命が第1期間以上に設定される第1メモリセル領域と、

データ保持寿命が前記第1期間よりも短い第2期間以内に設定される第2メモリセル領域と、

消去時および/または書き込み時に前記第1期間に対応して前記第1メモリセル領域内の各メモリセルに印加される第1電圧と、前記第1電圧よりも絶対値が小さく、消去時および/または書き込み時に前記第2期間に対応して前記第2メモリセル領域内の各メモリセルに印加される第2電圧とを生成する電圧生成手段とを有することを特徴とするマイクロコンピュータ。

【請求項2】

請求項1記載のマイクロコンピュータにおいて、

前記電圧生成手段は、

前記第1電圧の基準となる第1基準電圧を生成する第1基準電圧生成回路と、

前記第2電圧の基準となる第2基準電圧を生成する第2基準電圧生成回路と、

前記第1基準電圧か前記第2基準電圧かを選択して出力する選択回路と、

昇圧によって前記第1電圧または前記第2電圧を生成する昇圧回路と、

前記昇圧回路の出力電圧を反映したモニタ電圧を生成するモニタ電圧生成回路と、

前記モニタ電圧と前記選択回路の出力電圧とを比較し、その比較結果に応じて前記昇圧回路での昇圧動作を制御する比較回路とを有することを特徴とするマイクロコンピュータ。

【請求項3】

請求項1記載のマイクロコンピュータにおいて、さらに、

前記第2電圧の電圧値を任意に設定可能にする設定手段を有することを特徴とするマイクロコンピュータ。

【請求項4】

請求項1〜3のいずれか1項に記載のマイクロコンピュータにおいて、

前記第2期間は、1年以内であることを特徴とするマイクロコンピュータ。

【請求項5】

請求項1〜3のいずれか1項に記載のマイクロコンピュータにおいて、

前記マイクロコンピュータは、ICカードに搭載されることを特徴とするマイクロコンピュータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2010−9190(P2010−9190A)

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願番号】特願2008−165786(P2008−165786)

【出願日】平成20年6月25日(2008.6.25)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願日】平成20年6月25日(2008.6.25)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]