メモリカード

【課題】 ATAホストに対しても正常な動作を行うことができるメモリカードを提供すること。

【解決手段】 ホスト機器1に接続される端子22と、フラッシュメモリ部23と、端子22とフラッシュメモリ部23に接続されるとともに動作モードが変更可能なモードレジスタ部32とMPU31とを有するデバイスコントローラ24と、モードレジスタ部32の初期動作モードを設定する初期動作モード設定部25とを有する。

【解決手段】 ホスト機器1に接続される端子22と、フラッシュメモリ部23と、端子22とフラッシュメモリ部23に接続されるとともに動作モードが変更可能なモードレジスタ部32とMPU31とを有するデバイスコントローラ24と、モードレジスタ部32の初期動作モードを設定する初期動作モード設定部25とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリカードに関する。

【背景技術】

【0002】

コンピュータのメモリの拡張や、他の機器とのデータ交換・データ通信等のためにカード型媒体が用いられている。カード型媒体の規格としては、例えばPCカード、コンパクトフラッシュ(登録商標)カード(以下、「CFカード」)、スマートメディア等がある。CFカードは、サンディスク社が提唱しているメモリカードの規格である。

【0003】

CFカード、スマートメディア等の小型のメモリカードは、デジタルカメラ、パームトップパーソナルコンピュータ、PDA(Personal Digital Assistant)等の携帯機器に使用されている。

【0004】

また、CFカードスロットにそのまま装着できるカード型ハードディスクが開発されている。このハードディスクは、CF+TypeIIと呼ばれる規格に準拠している。

【0005】

ところで、このようなカード型媒体の規格の中には、複数の動作モードで動作を許容しているものがある。例えば、下記の特許文献1には、PCカードのピンの割り当てを変更してカスタムインターフェースとして一般化し、PCカードをZVポート(Zoomed Video port)対応カード等として使用することが記載されている。

【0006】

同様に、CFカードの規格においては、メモリモード(memory momde)、プライマリI/Oモード(primary I/O mode)、セカンダリI/Oモード(secondary I/O mode)、コンティギュアスI/Oモード(contiguous I/O mode)、True IDE モード(True Integrated Device Electronics mode)の5つの動作モードが定義されている。

【0007】

これらのモードのうち、メモリモードと3つのI/OモードはPCカード互換モードであり、PCカードコントローラから見ればPCカードとの区別はない。一方、True IDEモードは、一般的なハードディスクと同じインターフェースであり、PCカードと互換性はない。

【0008】

True IDEモードは、CF+V1.4と呼ばれる規格の策定時に追加された仕様で、CFカードの50ピンコネクタにIDEインターフェースの40本の信号ラインを割り当てたものである。このTrue IDEモードで動作するCFカードはIDEで接続した場合と同じ機能、性能が得られる。

【0009】

また、メモリモードは通信カードに対応する動作モードであり、さらに、I/OモードとTrue IDEモードはストレージカードに対応する動作モードである。ただし、I/OモードとTrue IDEモードではデータの転送速度に違いがある。すなわち、I/Oモードは、PCカードの16ビットI/Oカードとして扱われるので、16ビットI/Oカードで規定される転送速度、すなわちISA(Industrial Standard Architecture)バス相当のスピードが限界となる。これに対し、True IDEモードはPCカードの限界以上の転送速度でデータを転送することができる。

【0010】

CFカードのホストは、通常、上記の5つのモードのいずれか1つの動作モードを選択してCFカードにアクセスする。動作モードの選択は、ホストからCFカードに出力されるアウトプットイネーブル信号OE♯によって行われる。ホストがTrue IDEモードでの動作を選択する場合にはアウトプットイネーブル信号OE#を定常的に低レベル(Lレベル)にしてCFカードのコンフィギュレーション・オプション・レジスタ(Configuration Option Resister)をTrue IDEモードで動作させる。また、ホストが他のモードでの動作を選択する場合には、アウトプットイネーブル信号OE#を高レベル(Hレベル)にしてCFカードのコンフィギュレーション・オプション・レジスタに希望のモードを示す値を書き込むと、コンフィギュレーション・オプション・レジスタは書き換えられて希望のモードで動作するようになる。

【0011】

CFカードでは、電源電圧Vccの印加当初(電源投入後の初期)は、アウトプットイネーブル信号OE#のレベルが不安定となることにかんがみ、図9に示すタイミングチャートのように、最初にPCMCIA(Personal Computer Memory Card International Association)規格のメモリモードで動作するように設定されている。その後、アウトプットイネーブル信号OE#のレベルが安定してから、CFカードは、アウトプットイネーブル信号OE#のレベルに基づいてTrue IDEモードで動作すべきかどうかを判断する。そのため、True IDEモードでCFカードを動作させるシステムでも、コンピュータ等の機器からCFカードへの電源投入後の初期の段階で、CFカードは一時的にメモリモードで動作している。もし、CFカードがアウトプットイネーブル信号OE#のレベルを検知するタイミングが早すぎると、誤ってTrue IDEモードに切り替わってしまう。

【特許文献1】特開2001−319209号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

CFカードが暫くの時間、メモリモードで動作することについて、CFカード用のホストはモード切り換えまでの時間に配慮するように構成されているので問題はない。

【0013】

しかし、上記切り替え時間に対応していないATA(AT Attachment)(IDE)ホスト(以下、非対応ATAホストと呼ぶ)とCFカードとの組み合わせでは問題が起きてしまう。

【0014】

例えば、CFカードの43番ピンをLレベルとする信号は、True IDEモードで動作している場合には、DMA(Direct Memory Access)リクエスト信号を意味するが、メモリモードで動作している場合には異なる信号(INPACK#信号)を意味する。このため、モード切り替え前にメモリモードで動作している間、CFカードがINPACK#信号を出力すると、非対応ATAホストは、True IDE モードのDMAリクエスト信号と誤認してそのための処理を開始してしまう。

【0015】

なお、DMAリクエスト信号は、DMA転送のためにCFカードがホスト側へと出力する信号であり、INPACK#信号は、アドレスデコーダの出力信号である。

【0016】

このように非対応ATAホストのためには、電源投入直後からTrue IDE モードで動作する特別な仕様に変更したCFカードを用意しなければならない。この場合、CFカードを容易かつ安価に実現するために、通常仕様のCFカードと特別仕様のCFカードとで、なるべく多くの部品を共通にすることが好ましい。

【0017】

また、ファームウェアの違いのみで両方の仕様を実現できればよいが、上述したように、電源投入後にはファームウェアのモードを直ぐに変更してもファームウェアが実行されるまでの間はメモリモードになるので、例えばCFカードからのINPACK#信号を、非対応ATAホストがDMAリクエストであると誤認するなどの問題は解決されない。

【0018】

本発明の目的の一つは、非対応ATAホストに対応したモード切り替えを行うことができるメモリカードを提供することにある。

【課題を解決するための手段】

【0019】

上記の課題を解決するための本発明は、メモリカードであって、ホスト機器に接続される端子、メモリ部、前記端子と前記メモリ部に接続されるとともに動作モードが変更可能なモードレジスタと制御回路とを有するデバイスコントローラ、及び、前記モードレジスタの初期動作モードを設定する初期動作モード設定部を有することを特徴としている。

【発明を実施するための最良の形態】

【0020】

以下に本発明の実施の形態を図面に基づいて詳細に説明する。図1は、本発明の実施形態に係るメモリカードが装着されるコンピュータシステムの一例を示す構成図である。

【0021】

図1において、コンピュータシステム1は、例えば、OADG(Open Architecture Developer's Group)仕様に準拠して、所定のオペレーティングシステム(OS)を搭載している。

【0022】

コンピュータシステム1におけるCPU2は、OSの制御下でユーティリティプログラムの他、各種プログラムを実行し、システムバスであるFSバス(Front Side Bus)3、高速I/O装置用バスとしてのPCI(Peripheral Component Interconnect)バス4、I/O装置用バスとしてのLPC(Low Pin Count)バス5という3段階のバスを介して、各構成要素と相互接続されており、CPU2内とその外部のキャッシュメモリにプログラムコードやデータを蓄えることにより処理の高速化を図っている。

【0023】

CPU2には、その内部に1次キャッシュとして例えば128KバイトのSRAMを集積させているが、その容量の不足を補うために、専用バスであるBSバス(Back Side Bus)6を介して、例えば512K〜2Mバイト程度の2次キャッシュ7が接続されている。

【0024】

FSバス3とPCIバス4は、メモリ/PCIチップと呼ばれるCPUブリッジ8を介して連絡されている。このCPUブリッジ8は、メインメモリ9へのアクセス動作を制御するためのメモリコントローラ機能や、FSバス3とPCIバス4との間のデータ転送速度の差を吸収するためのデータバッファ等を含んだ構成となっている。メインメモリ9は、CPU2の実行プログラムの読み込み領域として、あるいは実行プログラムの処理データを書き込む作業領域として利用されるメモリであり、複数個のDRAMチップで構成されている。その実行プログラムには、OSや周辺機器類をハードウェア操作するための各種ドライバや、アプリケーションプログラムや、LPCバス5に接続されるフラッシュROM17に格納されるBIOS(Basic Input/Output System)等のファームウェアが含まれる。

【0025】

また、CPUブリッジ8には、ビデオに関連する機能を実現するためのサブシステムであるビデオサブシステム10が接続されており、ビデオコントローラを含んでいる。

【0026】

PCIバス4には、I/Oブリッジ12の他、図示しないPCカードコントローラ、オーディオサブシステム、ドッキングステーションインターフェース、ミニPCIコネクタ等が接続されている。

【0027】

I/Oブリッジ12は、PCIバス4とLPCバス5のブリッジ機能を備え、さらに、DMAコントローラ機能、プログラマブル割り込みコントローラ(PIC)機能、プログラマブル・インターバル・タイマ(PIT)機能、ATA(IDE)インターフェース機能、USB(Universal Serial Bus)機能、SMバス(System Management Bus)インターフェース機能を備えると共に、リアルタイムクロックを内蔵している。DMAコントローラ機能は、フロッピー(登録商標)ディスクドライブ等の周辺機器とメインメモリ9との間のデータ転送をCPU2の介在なしに実行するための機能である。PIC機能は、周辺機器からの割り込み要求に応答して、所定のプログラムを実行させる機能である。PIT機能は、タイマ信号を所定周期で発生させる機能である。また、ATA(IDE)インターフェース機能によって実現されるインターフェースにはIDEハードディスクドライブ(HDD)14とCFカードスロット20が接続され、またATAPI(ATA Packet Interface)にはCD−ROMドライブ15が接続されている。CD−ROM15の代わりに、DVD(Digital Versatile Disc)ドライブを接続してもよい。なお、CFカードスロット20には、後述するメモリカード21が差し込まれ、メモリカード21に対してそれ以外のコンピュータ1の構成部分がホストとなる。

【0028】

ATA/ATAPIインターフェースに接続されたドライブ等は、コンピュータシステム1の起動時に接続が確認される。この接続の確認は、BIOSの動作の段階で行われ、各ドライブはそれぞれI/Oブリッジ12からのATA/ATAPIコマンドに対して応答を返し、その応答によりI/Oブリッジ12は接続を確認する。

【0029】

また、I/Oブリッジ12には、SMバスを介してEEPROM16が接続されている。このEEPROM16は、ユーザによって登録されたパスワードやスーパーバイザーパスワード、製品シリアル番号等の情報を保持するための不揮発性メモリであり、記憶内容の書換えが可能である。

【0030】

LPCバス5は、ISAバスを持たないシステムにレガシーデバイスを接続するためのインターフェース規格に基づくバスであり、コマンド、アドレス及びデータを同じ信号線を使って取り交わしている。このLPCバス5には、フラッシュROM17、エンベデッドコントローラ18等が接続されている。

【0031】

フラッシュROM17は、一括またはブロック単位でのデータの消去、新たな書き込みを行えるROMであり、上述したようにBIOSを格納している。

【0032】

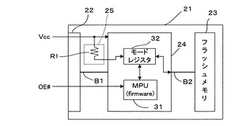

CFカードスロット20に接続されるメモリカード21は、例えば図2に示すようにCFカードの特別仕様であって外部入出力がATA規格に準拠する構成を有している。このメモリカード21は、図2に示すように、PCカードに準拠している外部端子22と、半導体デバイスからなるフラッシュメモリ23と、外部端子22とフラッシュメモリ23に接続されて外部との入出力を受け持つデバイスコントローラ24と、初期動作モード設定部25とを有している。デバイスコントローラ24と外部端子22は第1のバスB1を介して接続され、フラッシュメモリ23とデバイスコントローラ24は第2のバスB2を介して接続され、さらに、初期動作モード設定部25はデバイスコントローラ24に接続されている。

【0033】

デバイスコントローラ24は、例えば1チップのLSIで構成され、外部端子22に接続される制御部(MPU(Micro Processing Unit))24aとモードレジスタ部32を有し、MPU31はファームウェアとしても機能する。

【0034】

ここでモードレジスタ部32は、メモリカード21の動作モードを設定するためのレジスタ(モードレジスタ)を含む。本実施の形態において特徴的なことの一つは、このモードレジスタ部32が、初期動作モード設定部25からの初期モード設定信号を受けて、初期の動作モードを設定することである。例えば、メモリカード21に電源電圧Vccが外部端子22を通して投入された後、所定の時間(パワーオンリセット時間)内に、初期動作モード設定部25からHレベル信号が入力されると、この信号をForce IDE(強制IDE)信号と認識して、モードレジスタ部32は、メモリカード21の動作モードがTrue IDEモードとなるよう、モードレジスタを設定する。

【0035】

初期動作モード設定部25は、例えば抵抗器R1を含んで構成される。この抵抗器R1は、一端が電源に接続され且つ他端がモードレジスタ部32に接続されており、プルアップ抵抗として動作する。これにより、メモリカード21に電源が投入された後、モードレジスタ部32にHレベルのForce IDE信号が入力される。

【0036】

また、MPU31は、パワーオンリセット時間経過後に、アウトプットイネーブル信号OE#のレベルを判別し、その判別結果に基づいてモードレジスタ部32の動作モードを変更する。例えば、アウトプットイネーブル信号OE#がLレベルとなっている場合には、MPU31は、モードレジスタ部32の動作モードをTrue IDEモードに設定する。また、Hレベルとなっている場合には、MPU31は、モードレジスタ部32の動作モードをメモリモードに設定する。

【0037】

本実施の形態のメモリカード21は、上述の構成を有してなる。そして、このメモリカード21をCFカードスロット20に差し込み、電源電圧Vccが供給されると、メモリカード21は、次のように動作する。図3は、電源、Force IDE信号、アウトプットイネーブル信号OE#及び第43番ピン(以下、DMARQ/INPACK#と呼ぶ)の信号のタイミングチャートを表す説明図である。

【0038】

図3において、メモリカード21に電源が投入されるとともに、Force IDE信号はHレベルになってモードレジスタ部32に入力される。これにより、パワーオンリセット時間Tにモードレジスタ部32の動作モードはTrue IDEモードとなる。また、パワーオンリセット時間Tには、MPU31は、アウトプットイネーブル信号OE#のレベルを無視してモードレジスタ部32の動作モードを変更しない。

【0039】

つまり、パワーオンリセット時間T内に、メモリカード21が、そのDMARQ/INPACK#の信号レベルをLレベルとした場合、この信号の意味は、INPACK#ではなく、DMAリクエスト信号となる。一方で非対応ATAホストは、電源投入直後から、メモリカード21がTrue IDEモードにあるとして、メモリカード21へのアクセスを行っているので、I/Oブリッジ12のATAインターフェースを介してメインメモリ9へのDMA転送が可能になる。

【0040】

そのパワーオンリセット時間Tを経過した後には、アウトプットイネーブル信号OE#のレベルの高低によってファームウェアであるMPU31はモードレジスタ部32のモードを設定する。例えば、図3において、パワーオンリセット時間経過後のアウトプットイネーブル信号OE#はLレベルであるので、モードレジスタ部32の動作モードはTrue IDEモードのままとなる。

【0041】

一方、特別仕様のCFカードであるメモリカード21を、ATAホスト以外のホスト、例えばPCカードI/Oモードとして扱われるホストに接続する場合について説明する。図4に示すように、この場合もパワーオンリセット時間には、図3に示した例と同様に、モードレジスタ部32はTrue IDEモードで動作する。また、パワーオンリセット時間経過後には、アウトプットイネーブル信号OE#に応じてモードが設定される。つまり、パワーオンリセット時間経過後、アウトプットイネーブル信号OE#がHレベルの場合にはMPU31のモード設定によってメモリモードで動作し、アウトプットイネーブル信号OE#がLレベルの場合には、モードレジスタ部32はTrue IDEモードで動作を続ける。

【0042】

ところで、メモリカード21を、一般にATAホスト以外のホストに接続することを想定して、製造する場合には、図5に示すように、抵抗器R2を用い、その一端を接地電位GNDに接続し、他端をモードレジスタ部32に接続して初期動作モード設定部25を構成してもよい。

【0043】

このように構成すると、初期動作モード設定部25からモードレジスタ部32に入力する信号はLレベルとなってモードレジスタ部32の初期の動作モードはメモリモードとなる。従って、図5に示すメモリカード21は、通常仕様のCFカードと同様のものとなる。

【0044】

すなわち本実施の形態では、初期動作モード設定部25としての抵抗器の接続状態を変更するだけで、初期の動作モードを変更することができ、通常仕様/特別仕様の設定を容易に行うことができる。

【0045】

この通常仕様のCFカードであるメモリカード21を、図1に示すCFカードスロット20を介してI/Oブリッジ12に接続した場合の動作について説明する。この場合、図6に示すように、パワーオンリセット時間でのモードレジスタ部32の動作モードは、True IDEモード以外のモード、例えばメモリモードとなる。さらに、パワーオンリセット時間を経過した後には、ファームウェアであるMPU31は、アウトプットイネーブル信号OE#がLレベルの場合にモードレジスタ部32の動作モードをTrue IDEモードに変更する。

【0046】

この場合において、メモリカード21がDMA転送を要求するときには、当初のメモリモードにある間、DMARQ/INPACK#のピンは、Hレベルとなっている。そしてその後、モードレジスタ部32によってTrue IDEモードに切り替えられた後に、DMARQ/INPACK#のピンがLレベルとなって、DMA要求が行われることとなる。

【0047】

一方、図5に示すメモリカード21がATAホスト以外のホストに接続される場合について説明する。図7のタイミングチャートに示すように、この場合も、パワーオンリセット時間でのモードレジスタ部32の動作モードは、図6に示した場合と同様にメモリモードとなる。

【0048】

一方、パワーオンリセット時間を経過した後には、ファームウェアであるMPU31は、アウトプットイネーブル信号OE#がHレベルの場合には、モードレジスタ部32の動作モードをメモリモードに維持させる。

【0049】

ところで、図2に示したメモリカード21では、初期動作モード設定部25からHレベルの信号が入力されると、モードレジスタ部32が、当該信号をForce ID信号として認識し、True IDEモードとなるように設定することとしたが、これに限られるものではない。例えば、モードレジスタ部32は、Lレベルの信号が入力されたときに、当該信号をForce

ID信号として認識してもよい。この場合、Hレベルの信号が入力されるときは、メモリモードにて動作することとしてもよい。

【0050】

さらに、この初期動作モード設定部25の出力は1つである必要はなく、モードの数に合わせて複数の信号を入力可能となっていてもよい。この場合もモードレジスタ部32は、初期動作モード設定部25から入力される信号に対応して、予め定められた動作モードとなるようモードレジスタを設定する。

【0051】

また、図2に示した特別仕様のCFカードとなるメモリカード21と、図5に示した通常仕様のCFカードとなるメモリカード21の作り分けは、プルアップ抵抗R1を有するプリント配線基板とプルダウン抵抗R2を有するプリント配線基板の2種類用意して、どちらの種類のプリント配線基板を用いてメモリカード21を生成するかによって作り分けてもよい。また或いは、予めプルアップ抵抗とプルダウン抵抗の双方を搭載したプリント基板を用意して切り換えスイッチなどによりモードレジスタ部32にいずれかの抵抗を接続するようにしてもよい。

【0052】

これらの場合でも、特別仕様のメモリカード21と通常仕様のメモリカード21の違いは初期動作モード設定部15の内容だけであって、その他は全て同じ部品構成となっている。

【0053】

上記した実施形態では、ホスト機器としてコンピュータを例に挙げて説明したが、PDA、デジタルカメラ、携帯電話などの機器であってもよい。

【0054】

以上のように、本実施の形態では、メモリカードのコントローラ(LSI)に仕様を区別する入力信号Aの発生部を設け、その入力信号Aのレベルの高低に基づいて電源投入直後からTrue IDEモードで動作するのかメモリモードで動作するのかをハードウエアによって切り替える。入力信号Aは、CFカードのプリント基板上で、その信号レベルが定常的に確定するように、例えば電源電圧から直接的に(ゲート等を用いることなく)獲得できるようにしておく。

【0055】

これにより、メモリカードのコントローラに対する入力電源電圧Vccが安定し、パワーオンリセット時間が経過したときに、入力信号Aに基づいた所望の動作モードが設定されることになる。例えば起動時の動作モードがTrue IDEモードなるよう設定する特別仕様のCFカードの回路では、図8に示すように、電源が投入された直後からTrue IDEモードでCFカードが動作するようになり、ATAホストとの組合せでの問題を解決することができる。

【0056】

さらに、ここまでの説明では、デバイスコントローラ24と初期動作モード設定部25とを別個の回路として説明していたが、初期動作モード設定部25は、デバイスコントローラ24内に含まれてもよい。すなわち、電源投入後の初期の動作モードごとに複数種類のデバイスコントローラ24を用意し、メモリカード21の製造時に、所望の初期の動作モードに対応する種類のデバイスコントローラ24を選択的に用いて製造することとしてもよい。

【図面の簡単な説明】

【0057】

【図1】本発明の実施形態に係るメモリカードを装着したコンピュータシステムの構成図である。

【図2】本発明の実施形態に係るメモリカードの第1例のブロック図である。

【図3】図2に示したメモリカードをATAホストに接続した場合の動作を示すタイミングチャートである。

【図4】図2に示したメモリカードをATAホスト以外のホストに接続した場合の動作を示すタイミングチャートである。

【図5】本発明の実施形態に係るメモリカードの第2例のブロック図である。

【図6】図5に示したメモリカードをATAホストに接続した場合の動作を示すタイミングチャートである。

【図7】図5に示したメモリカードをATAホスト以外のホストに接続した場合の動作を示すタイミングチャートである。

【図8】本発明の実施形態に係るメモリカードの基本動作を示すタイミングチャートである。

【図9】従来技術に係るCFカードの動作を示すタイミングチャートである。

【符号の説明】

【0058】

1 コンピュータシステム、2 CPU、3 FSバス、4 PCIバス、5 LPCバス、8 CPUブリッジ、9 メインメモリ、12 I/Oブリッジ、17 フラッシュROM、20 CFカードスロット、21 メモリカード、22 外部端子、23 フラッシュメモリ、24 デバイスコントローラ、25 初期動作モード設定部、31 MPU、32 モードレジスタ部。

【技術分野】

【0001】

本発明は、メモリカードに関する。

【背景技術】

【0002】

コンピュータのメモリの拡張や、他の機器とのデータ交換・データ通信等のためにカード型媒体が用いられている。カード型媒体の規格としては、例えばPCカード、コンパクトフラッシュ(登録商標)カード(以下、「CFカード」)、スマートメディア等がある。CFカードは、サンディスク社が提唱しているメモリカードの規格である。

【0003】

CFカード、スマートメディア等の小型のメモリカードは、デジタルカメラ、パームトップパーソナルコンピュータ、PDA(Personal Digital Assistant)等の携帯機器に使用されている。

【0004】

また、CFカードスロットにそのまま装着できるカード型ハードディスクが開発されている。このハードディスクは、CF+TypeIIと呼ばれる規格に準拠している。

【0005】

ところで、このようなカード型媒体の規格の中には、複数の動作モードで動作を許容しているものがある。例えば、下記の特許文献1には、PCカードのピンの割り当てを変更してカスタムインターフェースとして一般化し、PCカードをZVポート(Zoomed Video port)対応カード等として使用することが記載されている。

【0006】

同様に、CFカードの規格においては、メモリモード(memory momde)、プライマリI/Oモード(primary I/O mode)、セカンダリI/Oモード(secondary I/O mode)、コンティギュアスI/Oモード(contiguous I/O mode)、True IDE モード(True Integrated Device Electronics mode)の5つの動作モードが定義されている。

【0007】

これらのモードのうち、メモリモードと3つのI/OモードはPCカード互換モードであり、PCカードコントローラから見ればPCカードとの区別はない。一方、True IDEモードは、一般的なハードディスクと同じインターフェースであり、PCカードと互換性はない。

【0008】

True IDEモードは、CF+V1.4と呼ばれる規格の策定時に追加された仕様で、CFカードの50ピンコネクタにIDEインターフェースの40本の信号ラインを割り当てたものである。このTrue IDEモードで動作するCFカードはIDEで接続した場合と同じ機能、性能が得られる。

【0009】

また、メモリモードは通信カードに対応する動作モードであり、さらに、I/OモードとTrue IDEモードはストレージカードに対応する動作モードである。ただし、I/OモードとTrue IDEモードではデータの転送速度に違いがある。すなわち、I/Oモードは、PCカードの16ビットI/Oカードとして扱われるので、16ビットI/Oカードで規定される転送速度、すなわちISA(Industrial Standard Architecture)バス相当のスピードが限界となる。これに対し、True IDEモードはPCカードの限界以上の転送速度でデータを転送することができる。

【0010】

CFカードのホストは、通常、上記の5つのモードのいずれか1つの動作モードを選択してCFカードにアクセスする。動作モードの選択は、ホストからCFカードに出力されるアウトプットイネーブル信号OE♯によって行われる。ホストがTrue IDEモードでの動作を選択する場合にはアウトプットイネーブル信号OE#を定常的に低レベル(Lレベル)にしてCFカードのコンフィギュレーション・オプション・レジスタ(Configuration Option Resister)をTrue IDEモードで動作させる。また、ホストが他のモードでの動作を選択する場合には、アウトプットイネーブル信号OE#を高レベル(Hレベル)にしてCFカードのコンフィギュレーション・オプション・レジスタに希望のモードを示す値を書き込むと、コンフィギュレーション・オプション・レジスタは書き換えられて希望のモードで動作するようになる。

【0011】

CFカードでは、電源電圧Vccの印加当初(電源投入後の初期)は、アウトプットイネーブル信号OE#のレベルが不安定となることにかんがみ、図9に示すタイミングチャートのように、最初にPCMCIA(Personal Computer Memory Card International Association)規格のメモリモードで動作するように設定されている。その後、アウトプットイネーブル信号OE#のレベルが安定してから、CFカードは、アウトプットイネーブル信号OE#のレベルに基づいてTrue IDEモードで動作すべきかどうかを判断する。そのため、True IDEモードでCFカードを動作させるシステムでも、コンピュータ等の機器からCFカードへの電源投入後の初期の段階で、CFカードは一時的にメモリモードで動作している。もし、CFカードがアウトプットイネーブル信号OE#のレベルを検知するタイミングが早すぎると、誤ってTrue IDEモードに切り替わってしまう。

【特許文献1】特開2001−319209号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

CFカードが暫くの時間、メモリモードで動作することについて、CFカード用のホストはモード切り換えまでの時間に配慮するように構成されているので問題はない。

【0013】

しかし、上記切り替え時間に対応していないATA(AT Attachment)(IDE)ホスト(以下、非対応ATAホストと呼ぶ)とCFカードとの組み合わせでは問題が起きてしまう。

【0014】

例えば、CFカードの43番ピンをLレベルとする信号は、True IDEモードで動作している場合には、DMA(Direct Memory Access)リクエスト信号を意味するが、メモリモードで動作している場合には異なる信号(INPACK#信号)を意味する。このため、モード切り替え前にメモリモードで動作している間、CFカードがINPACK#信号を出力すると、非対応ATAホストは、True IDE モードのDMAリクエスト信号と誤認してそのための処理を開始してしまう。

【0015】

なお、DMAリクエスト信号は、DMA転送のためにCFカードがホスト側へと出力する信号であり、INPACK#信号は、アドレスデコーダの出力信号である。

【0016】

このように非対応ATAホストのためには、電源投入直後からTrue IDE モードで動作する特別な仕様に変更したCFカードを用意しなければならない。この場合、CFカードを容易かつ安価に実現するために、通常仕様のCFカードと特別仕様のCFカードとで、なるべく多くの部品を共通にすることが好ましい。

【0017】

また、ファームウェアの違いのみで両方の仕様を実現できればよいが、上述したように、電源投入後にはファームウェアのモードを直ぐに変更してもファームウェアが実行されるまでの間はメモリモードになるので、例えばCFカードからのINPACK#信号を、非対応ATAホストがDMAリクエストであると誤認するなどの問題は解決されない。

【0018】

本発明の目的の一つは、非対応ATAホストに対応したモード切り替えを行うことができるメモリカードを提供することにある。

【課題を解決するための手段】

【0019】

上記の課題を解決するための本発明は、メモリカードであって、ホスト機器に接続される端子、メモリ部、前記端子と前記メモリ部に接続されるとともに動作モードが変更可能なモードレジスタと制御回路とを有するデバイスコントローラ、及び、前記モードレジスタの初期動作モードを設定する初期動作モード設定部を有することを特徴としている。

【発明を実施するための最良の形態】

【0020】

以下に本発明の実施の形態を図面に基づいて詳細に説明する。図1は、本発明の実施形態に係るメモリカードが装着されるコンピュータシステムの一例を示す構成図である。

【0021】

図1において、コンピュータシステム1は、例えば、OADG(Open Architecture Developer's Group)仕様に準拠して、所定のオペレーティングシステム(OS)を搭載している。

【0022】

コンピュータシステム1におけるCPU2は、OSの制御下でユーティリティプログラムの他、各種プログラムを実行し、システムバスであるFSバス(Front Side Bus)3、高速I/O装置用バスとしてのPCI(Peripheral Component Interconnect)バス4、I/O装置用バスとしてのLPC(Low Pin Count)バス5という3段階のバスを介して、各構成要素と相互接続されており、CPU2内とその外部のキャッシュメモリにプログラムコードやデータを蓄えることにより処理の高速化を図っている。

【0023】

CPU2には、その内部に1次キャッシュとして例えば128KバイトのSRAMを集積させているが、その容量の不足を補うために、専用バスであるBSバス(Back Side Bus)6を介して、例えば512K〜2Mバイト程度の2次キャッシュ7が接続されている。

【0024】

FSバス3とPCIバス4は、メモリ/PCIチップと呼ばれるCPUブリッジ8を介して連絡されている。このCPUブリッジ8は、メインメモリ9へのアクセス動作を制御するためのメモリコントローラ機能や、FSバス3とPCIバス4との間のデータ転送速度の差を吸収するためのデータバッファ等を含んだ構成となっている。メインメモリ9は、CPU2の実行プログラムの読み込み領域として、あるいは実行プログラムの処理データを書き込む作業領域として利用されるメモリであり、複数個のDRAMチップで構成されている。その実行プログラムには、OSや周辺機器類をハードウェア操作するための各種ドライバや、アプリケーションプログラムや、LPCバス5に接続されるフラッシュROM17に格納されるBIOS(Basic Input/Output System)等のファームウェアが含まれる。

【0025】

また、CPUブリッジ8には、ビデオに関連する機能を実現するためのサブシステムであるビデオサブシステム10が接続されており、ビデオコントローラを含んでいる。

【0026】

PCIバス4には、I/Oブリッジ12の他、図示しないPCカードコントローラ、オーディオサブシステム、ドッキングステーションインターフェース、ミニPCIコネクタ等が接続されている。

【0027】

I/Oブリッジ12は、PCIバス4とLPCバス5のブリッジ機能を備え、さらに、DMAコントローラ機能、プログラマブル割り込みコントローラ(PIC)機能、プログラマブル・インターバル・タイマ(PIT)機能、ATA(IDE)インターフェース機能、USB(Universal Serial Bus)機能、SMバス(System Management Bus)インターフェース機能を備えると共に、リアルタイムクロックを内蔵している。DMAコントローラ機能は、フロッピー(登録商標)ディスクドライブ等の周辺機器とメインメモリ9との間のデータ転送をCPU2の介在なしに実行するための機能である。PIC機能は、周辺機器からの割り込み要求に応答して、所定のプログラムを実行させる機能である。PIT機能は、タイマ信号を所定周期で発生させる機能である。また、ATA(IDE)インターフェース機能によって実現されるインターフェースにはIDEハードディスクドライブ(HDD)14とCFカードスロット20が接続され、またATAPI(ATA Packet Interface)にはCD−ROMドライブ15が接続されている。CD−ROM15の代わりに、DVD(Digital Versatile Disc)ドライブを接続してもよい。なお、CFカードスロット20には、後述するメモリカード21が差し込まれ、メモリカード21に対してそれ以外のコンピュータ1の構成部分がホストとなる。

【0028】

ATA/ATAPIインターフェースに接続されたドライブ等は、コンピュータシステム1の起動時に接続が確認される。この接続の確認は、BIOSの動作の段階で行われ、各ドライブはそれぞれI/Oブリッジ12からのATA/ATAPIコマンドに対して応答を返し、その応答によりI/Oブリッジ12は接続を確認する。

【0029】

また、I/Oブリッジ12には、SMバスを介してEEPROM16が接続されている。このEEPROM16は、ユーザによって登録されたパスワードやスーパーバイザーパスワード、製品シリアル番号等の情報を保持するための不揮発性メモリであり、記憶内容の書換えが可能である。

【0030】

LPCバス5は、ISAバスを持たないシステムにレガシーデバイスを接続するためのインターフェース規格に基づくバスであり、コマンド、アドレス及びデータを同じ信号線を使って取り交わしている。このLPCバス5には、フラッシュROM17、エンベデッドコントローラ18等が接続されている。

【0031】

フラッシュROM17は、一括またはブロック単位でのデータの消去、新たな書き込みを行えるROMであり、上述したようにBIOSを格納している。

【0032】

CFカードスロット20に接続されるメモリカード21は、例えば図2に示すようにCFカードの特別仕様であって外部入出力がATA規格に準拠する構成を有している。このメモリカード21は、図2に示すように、PCカードに準拠している外部端子22と、半導体デバイスからなるフラッシュメモリ23と、外部端子22とフラッシュメモリ23に接続されて外部との入出力を受け持つデバイスコントローラ24と、初期動作モード設定部25とを有している。デバイスコントローラ24と外部端子22は第1のバスB1を介して接続され、フラッシュメモリ23とデバイスコントローラ24は第2のバスB2を介して接続され、さらに、初期動作モード設定部25はデバイスコントローラ24に接続されている。

【0033】

デバイスコントローラ24は、例えば1チップのLSIで構成され、外部端子22に接続される制御部(MPU(Micro Processing Unit))24aとモードレジスタ部32を有し、MPU31はファームウェアとしても機能する。

【0034】

ここでモードレジスタ部32は、メモリカード21の動作モードを設定するためのレジスタ(モードレジスタ)を含む。本実施の形態において特徴的なことの一つは、このモードレジスタ部32が、初期動作モード設定部25からの初期モード設定信号を受けて、初期の動作モードを設定することである。例えば、メモリカード21に電源電圧Vccが外部端子22を通して投入された後、所定の時間(パワーオンリセット時間)内に、初期動作モード設定部25からHレベル信号が入力されると、この信号をForce IDE(強制IDE)信号と認識して、モードレジスタ部32は、メモリカード21の動作モードがTrue IDEモードとなるよう、モードレジスタを設定する。

【0035】

初期動作モード設定部25は、例えば抵抗器R1を含んで構成される。この抵抗器R1は、一端が電源に接続され且つ他端がモードレジスタ部32に接続されており、プルアップ抵抗として動作する。これにより、メモリカード21に電源が投入された後、モードレジスタ部32にHレベルのForce IDE信号が入力される。

【0036】

また、MPU31は、パワーオンリセット時間経過後に、アウトプットイネーブル信号OE#のレベルを判別し、その判別結果に基づいてモードレジスタ部32の動作モードを変更する。例えば、アウトプットイネーブル信号OE#がLレベルとなっている場合には、MPU31は、モードレジスタ部32の動作モードをTrue IDEモードに設定する。また、Hレベルとなっている場合には、MPU31は、モードレジスタ部32の動作モードをメモリモードに設定する。

【0037】

本実施の形態のメモリカード21は、上述の構成を有してなる。そして、このメモリカード21をCFカードスロット20に差し込み、電源電圧Vccが供給されると、メモリカード21は、次のように動作する。図3は、電源、Force IDE信号、アウトプットイネーブル信号OE#及び第43番ピン(以下、DMARQ/INPACK#と呼ぶ)の信号のタイミングチャートを表す説明図である。

【0038】

図3において、メモリカード21に電源が投入されるとともに、Force IDE信号はHレベルになってモードレジスタ部32に入力される。これにより、パワーオンリセット時間Tにモードレジスタ部32の動作モードはTrue IDEモードとなる。また、パワーオンリセット時間Tには、MPU31は、アウトプットイネーブル信号OE#のレベルを無視してモードレジスタ部32の動作モードを変更しない。

【0039】

つまり、パワーオンリセット時間T内に、メモリカード21が、そのDMARQ/INPACK#の信号レベルをLレベルとした場合、この信号の意味は、INPACK#ではなく、DMAリクエスト信号となる。一方で非対応ATAホストは、電源投入直後から、メモリカード21がTrue IDEモードにあるとして、メモリカード21へのアクセスを行っているので、I/Oブリッジ12のATAインターフェースを介してメインメモリ9へのDMA転送が可能になる。

【0040】

そのパワーオンリセット時間Tを経過した後には、アウトプットイネーブル信号OE#のレベルの高低によってファームウェアであるMPU31はモードレジスタ部32のモードを設定する。例えば、図3において、パワーオンリセット時間経過後のアウトプットイネーブル信号OE#はLレベルであるので、モードレジスタ部32の動作モードはTrue IDEモードのままとなる。

【0041】

一方、特別仕様のCFカードであるメモリカード21を、ATAホスト以外のホスト、例えばPCカードI/Oモードとして扱われるホストに接続する場合について説明する。図4に示すように、この場合もパワーオンリセット時間には、図3に示した例と同様に、モードレジスタ部32はTrue IDEモードで動作する。また、パワーオンリセット時間経過後には、アウトプットイネーブル信号OE#に応じてモードが設定される。つまり、パワーオンリセット時間経過後、アウトプットイネーブル信号OE#がHレベルの場合にはMPU31のモード設定によってメモリモードで動作し、アウトプットイネーブル信号OE#がLレベルの場合には、モードレジスタ部32はTrue IDEモードで動作を続ける。

【0042】

ところで、メモリカード21を、一般にATAホスト以外のホストに接続することを想定して、製造する場合には、図5に示すように、抵抗器R2を用い、その一端を接地電位GNDに接続し、他端をモードレジスタ部32に接続して初期動作モード設定部25を構成してもよい。

【0043】

このように構成すると、初期動作モード設定部25からモードレジスタ部32に入力する信号はLレベルとなってモードレジスタ部32の初期の動作モードはメモリモードとなる。従って、図5に示すメモリカード21は、通常仕様のCFカードと同様のものとなる。

【0044】

すなわち本実施の形態では、初期動作モード設定部25としての抵抗器の接続状態を変更するだけで、初期の動作モードを変更することができ、通常仕様/特別仕様の設定を容易に行うことができる。

【0045】

この通常仕様のCFカードであるメモリカード21を、図1に示すCFカードスロット20を介してI/Oブリッジ12に接続した場合の動作について説明する。この場合、図6に示すように、パワーオンリセット時間でのモードレジスタ部32の動作モードは、True IDEモード以外のモード、例えばメモリモードとなる。さらに、パワーオンリセット時間を経過した後には、ファームウェアであるMPU31は、アウトプットイネーブル信号OE#がLレベルの場合にモードレジスタ部32の動作モードをTrue IDEモードに変更する。

【0046】

この場合において、メモリカード21がDMA転送を要求するときには、当初のメモリモードにある間、DMARQ/INPACK#のピンは、Hレベルとなっている。そしてその後、モードレジスタ部32によってTrue IDEモードに切り替えられた後に、DMARQ/INPACK#のピンがLレベルとなって、DMA要求が行われることとなる。

【0047】

一方、図5に示すメモリカード21がATAホスト以外のホストに接続される場合について説明する。図7のタイミングチャートに示すように、この場合も、パワーオンリセット時間でのモードレジスタ部32の動作モードは、図6に示した場合と同様にメモリモードとなる。

【0048】

一方、パワーオンリセット時間を経過した後には、ファームウェアであるMPU31は、アウトプットイネーブル信号OE#がHレベルの場合には、モードレジスタ部32の動作モードをメモリモードに維持させる。

【0049】

ところで、図2に示したメモリカード21では、初期動作モード設定部25からHレベルの信号が入力されると、モードレジスタ部32が、当該信号をForce ID信号として認識し、True IDEモードとなるように設定することとしたが、これに限られるものではない。例えば、モードレジスタ部32は、Lレベルの信号が入力されたときに、当該信号をForce

ID信号として認識してもよい。この場合、Hレベルの信号が入力されるときは、メモリモードにて動作することとしてもよい。

【0050】

さらに、この初期動作モード設定部25の出力は1つである必要はなく、モードの数に合わせて複数の信号を入力可能となっていてもよい。この場合もモードレジスタ部32は、初期動作モード設定部25から入力される信号に対応して、予め定められた動作モードとなるようモードレジスタを設定する。

【0051】

また、図2に示した特別仕様のCFカードとなるメモリカード21と、図5に示した通常仕様のCFカードとなるメモリカード21の作り分けは、プルアップ抵抗R1を有するプリント配線基板とプルダウン抵抗R2を有するプリント配線基板の2種類用意して、どちらの種類のプリント配線基板を用いてメモリカード21を生成するかによって作り分けてもよい。また或いは、予めプルアップ抵抗とプルダウン抵抗の双方を搭載したプリント基板を用意して切り換えスイッチなどによりモードレジスタ部32にいずれかの抵抗を接続するようにしてもよい。

【0052】

これらの場合でも、特別仕様のメモリカード21と通常仕様のメモリカード21の違いは初期動作モード設定部15の内容だけであって、その他は全て同じ部品構成となっている。

【0053】

上記した実施形態では、ホスト機器としてコンピュータを例に挙げて説明したが、PDA、デジタルカメラ、携帯電話などの機器であってもよい。

【0054】

以上のように、本実施の形態では、メモリカードのコントローラ(LSI)に仕様を区別する入力信号Aの発生部を設け、その入力信号Aのレベルの高低に基づいて電源投入直後からTrue IDEモードで動作するのかメモリモードで動作するのかをハードウエアによって切り替える。入力信号Aは、CFカードのプリント基板上で、その信号レベルが定常的に確定するように、例えば電源電圧から直接的に(ゲート等を用いることなく)獲得できるようにしておく。

【0055】

これにより、メモリカードのコントローラに対する入力電源電圧Vccが安定し、パワーオンリセット時間が経過したときに、入力信号Aに基づいた所望の動作モードが設定されることになる。例えば起動時の動作モードがTrue IDEモードなるよう設定する特別仕様のCFカードの回路では、図8に示すように、電源が投入された直後からTrue IDEモードでCFカードが動作するようになり、ATAホストとの組合せでの問題を解決することができる。

【0056】

さらに、ここまでの説明では、デバイスコントローラ24と初期動作モード設定部25とを別個の回路として説明していたが、初期動作モード設定部25は、デバイスコントローラ24内に含まれてもよい。すなわち、電源投入後の初期の動作モードごとに複数種類のデバイスコントローラ24を用意し、メモリカード21の製造時に、所望の初期の動作モードに対応する種類のデバイスコントローラ24を選択的に用いて製造することとしてもよい。

【図面の簡単な説明】

【0057】

【図1】本発明の実施形態に係るメモリカードを装着したコンピュータシステムの構成図である。

【図2】本発明の実施形態に係るメモリカードの第1例のブロック図である。

【図3】図2に示したメモリカードをATAホストに接続した場合の動作を示すタイミングチャートである。

【図4】図2に示したメモリカードをATAホスト以外のホストに接続した場合の動作を示すタイミングチャートである。

【図5】本発明の実施形態に係るメモリカードの第2例のブロック図である。

【図6】図5に示したメモリカードをATAホストに接続した場合の動作を示すタイミングチャートである。

【図7】図5に示したメモリカードをATAホスト以外のホストに接続した場合の動作を示すタイミングチャートである。

【図8】本発明の実施形態に係るメモリカードの基本動作を示すタイミングチャートである。

【図9】従来技術に係るCFカードの動作を示すタイミングチャートである。

【符号の説明】

【0058】

1 コンピュータシステム、2 CPU、3 FSバス、4 PCIバス、5 LPCバス、8 CPUブリッジ、9 メインメモリ、12 I/Oブリッジ、17 フラッシュROM、20 CFカードスロット、21 メモリカード、22 外部端子、23 フラッシュメモリ、24 デバイスコントローラ、25 初期動作モード設定部、31 MPU、32 モードレジスタ部。

【特許請求の範囲】

【請求項1】

ホスト機器に接続される端子、

メモリ部、

前記端子と前記メモリ部に接続されるとともに、動作モードが変更可能なモードレジスタと制御回路とを有するデバイスコントローラ、

及び、前記モードレジスタの初期動作モードを設定する初期動作モード設定部、

を有することを特徴とするメモリカード。

【請求項2】

請求項1に記載のメモリカードにおいて、

前記初期動作モードは、True IDEモードであることを特徴とするメモリカード。

【請求項3】

請求項1に記載のメモリカードにおいて、

前記初期動作モード設定部は、前記モードレジスタに接続されるプルアップ抵抗、プルダウン抵抗のいずれか1つから構成されていることを特徴とするメモリカード。

【請求項4】

請求項1に記載のメモリカードにおいて、

前記初期動作モード設定部は、前記モードレジスタに選択的に接続されるプルアップ抵抗とプルダウン抵抗とを有することを特徴とするメモリカード。

【請求項5】

請求項1に記載のメモリカードにおいて、

前記制御回路は、前記モードレジスタが前記初期動作モードに設定された後に、前記ホスト機器からの入力信号によって前記モードレジスタの前記動作モードを設定する信号を出力することを特徴とするメモリカード。

【請求項1】

ホスト機器に接続される端子、

メモリ部、

前記端子と前記メモリ部に接続されるとともに、動作モードが変更可能なモードレジスタと制御回路とを有するデバイスコントローラ、

及び、前記モードレジスタの初期動作モードを設定する初期動作モード設定部、

を有することを特徴とするメモリカード。

【請求項2】

請求項1に記載のメモリカードにおいて、

前記初期動作モードは、True IDEモードであることを特徴とするメモリカード。

【請求項3】

請求項1に記載のメモリカードにおいて、

前記初期動作モード設定部は、前記モードレジスタに接続されるプルアップ抵抗、プルダウン抵抗のいずれか1つから構成されていることを特徴とするメモリカード。

【請求項4】

請求項1に記載のメモリカードにおいて、

前記初期動作モード設定部は、前記モードレジスタに選択的に接続されるプルアップ抵抗とプルダウン抵抗とを有することを特徴とするメモリカード。

【請求項5】

請求項1に記載のメモリカードにおいて、

前記制御回路は、前記モードレジスタが前記初期動作モードに設定された後に、前記ホスト機器からの入力信号によって前記モードレジスタの前記動作モードを設定する信号を出力することを特徴とするメモリカード。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2006−301882(P2006−301882A)

【公開日】平成18年11月2日(2006.11.2)

【国際特許分類】

【出願番号】特願2005−121574(P2005−121574)

【出願日】平成17年4月19日(2005.4.19)

【出願人】(503116280)ヒタチグローバルストレージテクノロジーズネザーランドビーブイ (1,121)

【Fターム(参考)】

【公開日】平成18年11月2日(2006.11.2)

【国際特許分類】

【出願日】平成17年4月19日(2005.4.19)

【出願人】(503116280)ヒタチグローバルストレージテクノロジーズネザーランドビーブイ (1,121)

【Fターム(参考)】

[ Back to top ]