メモリコントローラ、メモリ診断方法及びプロセッサシステム

【課題】主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整すること。

【解決手段】本発明にかかるメモリコントローラ12は、プロセッサ11からのアクセスリクエストRに応答するメモリ13へ、メモリ13の状態を診断するための診断リクエストDを発行し、診断リクエストDの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、診断リクエストDの発行周期を長くするメモリ診断回路120、を備える。

【解決手段】本発明にかかるメモリコントローラ12は、プロセッサ11からのアクセスリクエストRに応答するメモリ13へ、メモリ13の状態を診断するための診断リクエストDを発行し、診断リクエストDの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、診断リクエストDの発行周期を長くするメモリ診断回路120、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリコントローラ、メモリ診断方法及びプロセッサシステムに関し、特に、プロセッサからアクセスされるメモリの状態を診断するためのメモリコントローラ、メモリ診断方法及びプロセッサシステムに関する。

【背景技術】

【0002】

図7は、関連技術にかかるメモリコントローラを含む情報処理装置900の構成を示すブロック図である。情報処理装置900は、その構成の一部として、プロセッサ群91、メモリコントローラ92、主記憶装置93を備える。メモリコントローラ92は、プロセッサ群91内の通常リクエスト発行部911及び912から主記憶装置93への複数の主記憶アクセスリクエストを受け付け、複数の主記憶アクセスリクエストを調停した上で、主記憶装置93に対してアクセスを行う。

【0003】

メモリパトロール発行部921は、発行タイミング生成回路931と、パトロール発行回路932を有する。発行タイミング生成回路931はタイマ回路であり、予め定めた周期でメモリパトロールリクエストを発行するためのタイミング信号を生成する。但し、発行タイミング生成回路931は、先に発行したメモリパトロールリクエストのリプライ受信を監視し、リプライを受信するまでは次のメモリパトロールリクエスト発行を保留する。これは、主記憶アクセス経路及び主記憶装置93においてメモリパトロールリクエストを処理する回路を簡素化するためである。

【0004】

通常リクエスト発行部911及び912から発行された通常運用の主記憶アクセスリクエストは、それぞれリクエストキュー941及び942に格納され調停に参加する。この図7では、2つの通常リクエスト発行部と、1つのメモリパトロール発行部との三者で調停を行う構成を示す。

【0005】

尚、特許文献1には、CPUからメモリへのアクセスを制御するメモリコントローラに、メモリをアクセスして診断するメモリ診断手段を有するメモリコントローラに関する技術が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−048224号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上述したメモリコントローラ92においては、通常運用の主記憶アクセスが頻繁に発行され主記憶アクセス経路の負荷が高い時にも、予め定めた周期でメモリパトロールリクエストが発行されるため、通常運用の主記憶アクセスの調停通過を妨げてしまうという問題点があった。すなわち、メモリコントローラ92は、予め設定したメモリパトロールリクエストの発行周期でメモリパトロールを行っていたため、通常運用の主記憶アクセスによる主記憶アクセス経路の負荷が高い時にも一定間隔でメモリパトロールリクエストが割り込み、通常運用の主記憶アクセスがメモリパトロールにより待たされてしまうケースが発生し、通常運用の主記憶アクセス性能を低下させていた。

【0008】

ここで、上述した特許文献1にかかるメモリコントローラは、CPUからメモリへのアクセスと前記メモリ診断手段からメモリへのアクセスとの衝突を検出し、衝突率を算出する。そして、衝突率に応じて前記メモリ診断手段からメモリへのアクセスする周期を調整する。

【0009】

しかしながら、統計的に優位な衝突率を算出するには、それなりのサンプル数が必要となる。そのため、衝突率に応じて周期を調整する時点では、上記衝突がすでに減少し、アクセス性能が回復し、メモリ診断のためのアクセスの周期を調整する必要がなくなっている可能性がある。つまり、特許文献1では、通常運用の主記憶アクセスとメモリパトロールリクエストとの衝突が一定時間続いた場合にしか、上記周期を調整できず、リアルタイム性に欠ける。また、特許文献1では、実際に衝突が起こっている場合を検出しており、衝突を未然に防ぐことはできない。よって、特許文献1では、上述した問題点を解決することはできない。

【0010】

本発明は、このような問題点を解決するためになされたものであり、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整するためのメモリコントローラ、メモリ診断方法及びプロセッサシステムを提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の第1の態様にかかるメモリコントローラは、

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路、

を備える。

【0012】

本発明の第2の態様にかかるメモリコントローラは、

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備える。

【0013】

本発明の第3の態様にかかるメモリ診断方法は、

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くする。

【0014】

本発明の第4の態様にかかるメモリ診断方法は、

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くする。

【0015】

本発明の第5の態様にかかるプロセッサシステムは、

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記メモリの状態を診断するための診断リクエストを発行し、当該診断リクエストの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路と、

を備える。

【0016】

本発明の第6の態様にかかるプロセッサシステムは、

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備える。

【発明の効果】

【0017】

本発明により、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整するためのメモリコントローラ、メモリ診断方法及びプロセッサシステムを提供することができる。

【図面の簡単な説明】

【0018】

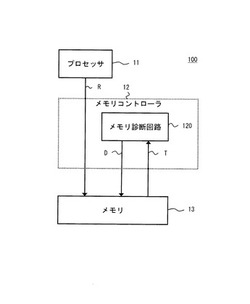

【図1】本発明の実施の形態1にかかるメモリコントローラを含むプロセッサシステムの構成を示すブロック図である。

【図2】本発明の実施の形態1にかかるメモリ診断処理の流れを示すフローチャートである。

【図3】本発明の実施の形態2にかかるメモリコントローラを含むプロセッサシステムの構成を示すブロック図である。

【図4】本発明の実施の形態2にかかるメモリ診断処理の流れを示すフローチャートである。

【図5】本発明の実施の形態3にかかるメモリコントローラを含む情報処理装置の構成を示すブロック図である。

【図6】本発明の実施の形態3にかかる主記憶アクセス経路負荷判定処理の流れを示すフローチャートである。

【図7】関連技術にかかるメモリコントローラの構成を示すブロック図である。

【発明を実施するための形態】

【0019】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。各図面において、同一要素には同一の符号が付されており、説明の明確化のため、必要に応じて重複説明は省略する。

【0020】

<発明の実施の形態1>

図1は、本発明の実施の形態1にかかるメモリコントローラ12を含むプロセッサシステム100の構成を示すブロック図である。プロセッサシステム100は、少なくともプロセッサ11がメモリ13にアクセスして動作する装置であり、例えば、コンピュータ等の情報処理装置である。プロセッサシステム100は、プロセッサ11と、メモリ13と、メモリコントローラ12と、を備える。プロセッサ11は、メモリ13に対してアクセスリクエストRを発行する。メモリ13は、アクセスリクエストRに対して応答する。メモリコントローラ12は、アクセスリクエストRや自己が発行する診断リクエストDによるメモリ13へのアクセスを制御する。

【0021】

メモリコントローラ12は、メモリ診断回路120を備える。メモリ診断回路120は、メモリ13の状態を診断する診断リクエストDをメモリ13へ発行する。そして、メモリ診断回路120は、発行した診断リクエストに対する応答Tを受信し、診断リクエストの発行時刻から応答Tの受信時刻までの応答時間を計測する。その後、メモリ診断回路120は、計測された応答時間が所定時間より長い場合、診断リクエストDの発行周期を長くする。

【0022】

図2は、本発明の実施の形態1にかかるメモリ診断処理の流れを示すフローチャートである。まず、メモリ診断回路120は、メモリ13へ診断リクエストDを発行する(S11)。次に、メモリ診断回路120は、診断リクエストDの応答時間を計測する(S12)。その後、メモリ診断回路120は、計測された応答時間が所定時間を超過しているか否かを判定する(S13)。ステップS13において応答時間が所定時間を超過していると判定した場合、メモリ診断回路120は、診断リクエストDの発行周期を長くする(S14)。

【0023】

このように、本発明の実施の形態1では、メモリ診断回路120により発行した診断リクエスト単位で応答時間を計測することで、少なくとも1回の診断リクエストの発行により主記憶アクセス経路の負荷が高まったことを検出できる。そして、主記憶アクセス経路の負荷を検出次第、診断リクエストの発行周期を長くする。これにより、主記憶アクセス経路の負荷が高いときに、メモリ診断アクセスの頻度を軽減することができる。よって、不要な負荷を減らし、メモリ診断アクセスに起因した性能低下を防ぐことができる。

【0024】

すなわち、特許文献1のように衝突率を算出するための時間や、そのサンプル数が溜まるまでの時間が不要となり、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整することができる。

【0025】

<発明の実施の形態2>

図3は、本発明の実施の形態2にかかるメモリコントローラ12aを含むプロセッサシステム101の構成を示すブロック図である。プロセッサシステム101は、少なくともプロセッサ11がメモリ13にアクセスして動作する装置であり、例えば、コンピュータ等の情報処理装置である。プロセッサシステム101は、プロセッサシステム100と同様に、プロセッサ11と、メモリ13とを備えるが、メモリコントローラ12aが異なる。メモリコントローラ12aは、アクセスリクエストRや自己が発行する診断リクエストDによるメモリ13へのアクセスを制御する。

【0026】

メモリコントローラ12aは、リクエストキュー121と、検出回路122と、メモリ診断回路123とを備える。リクエストキュー121は、プロセッサ11からメモリ13へのアクセスリクエストRを保持する。検出回路122は、リクエストキュー121に、所定数以上のアクセスリクエストRが保持されている場合に、ビジー状態であると検出する。メモリ診断回路123は、検出回路122によりビジー状態であると検出された場合、メモリ13の状態を診断するための診断リクエストDの発行周期を長くする。

【0027】

図4は、本発明の実施の形態2にかかるメモリ診断処理の流れを示すフローチャートである。まず、検出回路122は、リクエストキュー121を監視し、アクセスリクエストRが所定数以上保持されているか否かを判定する(S21)。アクセスリクエストRが所定数以上保持されていると判定した場合、検出回路122は、ビジー状態であると検出し(S21でYES)、その旨、メモリ診断回路123へ通知する。そして、メモリ診断回路123は、検出回路122からのビジー状態との通知を受信すると、診断リクエストDの発行周期を長くする(S22)。

【0028】

このように、本発明の実施の形態2では、検出回路122がリクエストキュー121の負荷状態を監視してビジー状態を検出することで、主記憶アクセス経路の負荷が高まったことを検出できる。そして、メモリ診断回路123は、主記憶アクセス経路の負荷を検出次第、診断リクエストの発行周期を長くする。これにより、少なくともメモリ診断アクセスの頻度を軽減することで、不要な負荷を減らし、メモリ診断アクセスに起因した性能低下を防ぐことができる。

【0029】

すなわち、特許文献1のように主記憶アクセスとメモリ診断アクセスとの間で相当数の衝突を必要とせず、衝突が発生する前であっても、主記憶アクセス経路の負荷を検出できる。つまり、診断リクエストによる影響があるか否かに関わらず、衝突を未然に防ぎ、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整することができる。

【0030】

<発明の実施の形態3>

図5は、本発明の実施の形態3にかかるメモリコントローラ22を含む情報処理装置200の構成を示すブロック図である。情報処理装置200は、上述したプロセッサシステム100及び101の主要な機能を共に採用した場合の一例である。情報処理装置200は、プロセッサ群21と、メモリコントローラ22と、主記憶装置23とを備える。情報処理装置200のその他の構成は、一般的なものであり、本発明の実施の形態3に影響しないため、図示及び説明を省略する。

【0031】

プロセッサ群21は、複数のプロセッサに相当する通常リクエスト発行部211及び212を含む。尚、通常リクエスト発行部211及び212は、例えば、CPU(Central Processing Unit)等の制御装置であるが、これに限定されない。また、通常リクエスト発行部211及び212の数は、少なくとも1以上であればよい。

【0032】

メモリコントローラ22は、メモリパトロール発行部221と、リクエスト調停部222と、リプライ振分け回路223とを備える。リクエスト調停部222は、リクエストキュー241及び242と、ビジー検出回路243及び244と、調停回路245とを備える。リクエストキュー241及び242のそれぞれは、通常リクエスト発行部211及び212から主記憶装置23への通常運用の主記憶アクセスリクエストを受け付け、所定数を保持する。

【0033】

ビジー検出回路243及び244は、それぞれリクエストキュー241及び242に格納された主記憶アクセスリクエストが一定の個数を超えた事を検出する。このとき、ビジー検出回路243及び244は、ビジー通知のフラグを"1"として主記憶アクセス経路負荷判定回路231へ通知する。例えば、ビジー検出回路243からのビジー通知のフラグが"1"のときは、リクエストキュー241に一定数以上の主記憶アクセスリクエストが格納され調停通過を待っていることを示す。また、ビジー検出回路243及び244は、それぞれリクエストキュー241及び242に、一定時間、主記憶アクセスリクエストが保持されていない場合に、無負荷状態であることを検出する。このとき、ビジー検出回路243及び244は、無負荷通知のフラグを"1"として主記憶アクセス経路負荷判定回路231へ通知する。例えば、ビジー検出回路243からの無負荷通知のフラグが"1"のときは、リクエストキュー241に一つも主記憶アクセスリクエストが格納されていない事を示す。

【0034】

調停回路245は、リクエストキュー241及び242からの2つの通常運用の主記憶アクセスリクエストのリクエストと、後述するパトロール発行回路233からの1つのメモリパトロールアクセスのリクエストとの3つを調停し、当該調停を経て主記憶アクセスリクエストを選択し、主記憶装置23へ出力する。尚、調停回路245による調停は、少なくとも通常運用の主記憶アクセスリクエストと、メモリパトロールのリクエストとの調停がなされるものであればよい。

【0035】

主記憶装置23は、調停回路245による調停を経て選択された主記憶アクセスリクエストについて、目的の処理を行い、リプライ振分け回路223へリプライを出力する。尚、主記憶装置23は、例えば、RAM(Random Access Memory)等の揮発性の記憶装置である。

【0036】

リプライ振分け回路223は、主記憶装置23からリプライを受け付け、当該リプライに対応する主記憶アクセスリクエストの発行元である通常リクエスト発行部211もしくは212又はメモリパトロール発行部221へ振り分けを行い、当該リプライを返却する。

【0037】

メモリパトロール発行部221は、主記憶アクセス経路負荷判定回路231と、発行タイミング生成回路232と、パトロール発行回路233とを備える。主記憶アクセス経路負荷判定回路231は、発行タイミング生成回路232からメモリパトロールリクエスト発行要求を受信し、また、リプライ振分け回路223からメモリパトロールリクエストに対するリプライを受信し、メモリパトロールリクエストの発行からメモリパトロールリクエストのリプライ受信までに掛かった時間を応答時間として計測する。そして、主記憶アクセス経路負荷判定回路231は、応答時間が所定時間より長い場合、発行タイミング生成回路232に対して、メモリパトロールリクエストの発行周期をより長くするように調整要求を出力する。これにより、少なくとも1回の診断リクエストの発行により、主記憶アクセス経路の負荷が高まったことを検出できる。

【0038】

また、主記憶アクセス経路負荷判定回路231には、ビジー検出回路243又は244からの上述したビジー通知又は無負荷通知が接続されている。そして、主記憶アクセス経路負荷判定回路231は、ビジー通知が"1"のときに主記憶アクセス経路の負荷が高いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期をより長くするように調整要求を出力する。これにより、診断リクエストの発行がなくとも、主記憶アクセスリクエスト自体の増加による主記憶アクセス経路の負荷を検出できる。

【0039】

また、主記憶アクセス経路負荷判定回路231は、上記応答時間が所定時間より短く、かつ、無負荷通知が"1"のときに主記憶アクセス経路の負荷が低いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期値に比べて短くするように調整要求を出力する。これにより、主記憶アクセスリクエスト自体による主記憶アクセス経路の負荷が低い時に、つまり、主記憶装置23の処理能力に余裕があるときにより多くのメモリパトロールリクエストを発行することができ、主記憶に対するメモリパトロールの網羅性が向上し、ソフトエラーに対する主記憶の信頼性を改善できる。

【0040】

特に、主記憶アクセス経路負荷判定回路231は、主記憶アクセス経路の負荷が低いと判断する条件として、上記応答時間が所定時間より短く、かつ、無負荷通知が"1"のときであって、さらに一定時間、ビジー通知が"1"以外のときを加えるとよい。これにより、主記憶アクセス経路の負荷が低い場合をより精度良く検出できる。

【0041】

また、主記憶アクセス経路負荷判定回路231は、上記応答時間が所定時間より短く、かつ、一定時間、ビジー通知及び無負荷通知が"1"以外のときに、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期値に戻すように調整要求を出力する。これにより、一時的に発行周期を初期値より長く又は短くした場合であっても、主記憶アクセス経路の負荷状態に応じてメモリパトロールリクエストを適切に発行させることができる。そのため、主記憶装置23の診断を妥当に行いつつ、性能を維持することができる。

【0042】

発行タイミング生成回路232は、メモリパトロールリクエストを周期的に発行するタイミング信号を生成するタイマ回路である。そして、発行タイミング生成回路232は、主記憶アクセス経路負荷判定回路231からの調整要求に応じて、メモリパトロールリクエストの発行周期を動的に延長又は短縮する。そして、発行タイミング生成回路232は、調整された発行周期に従ってパトロール発行回路233に対してメモリパトロールリクエストの発行指示を出力する。

【0043】

ここで、メモリパトロールリクエストは、情報処理装置200内で同時期に1つだけ存在するリクエストである。そのため、これを保証するために、たとえ次の発行周期が来てもメモリパトロール発行部221がメモリパトロールのリプライを受信するまでは発行を抑止する。尚、実際は、発行周期を1回スキップし、次回の発行タイミングまで待つ等の論理となっている。

【0044】

パトロール発行回路233は、発行タイミング生成回路232からの発行指示に応じて主記憶装置23の状態を診断するためのメモリパトロールリクエストを発行する。具体的には、パトロール発行回路233は、調停回路245へメモリパトロールリクエストを出力する。

【0045】

主記憶装置23は、パトロール発行回路233から発行されたメモリパトロールリクエストが調停回路245を経て入力された場合に、メモリ素子に対して読み出しおよびエラー訂正後再書き込みといったパトロール動作を行う。

【0046】

また、通常運用の主記憶アクセスリクエストは、通常リクエスト発行部211及び212からリクエスト調停部222に対して発行される。通常リクエスト発行部211又は212から発行された通常運用の主記憶アクセスリクエストは、リクエストキュー241又は242に格納され、調停回路245における調停に参加する。その後、調停回路245は、調停を経て選択したリクエストにより主記憶装置23にアクセスする。そのリプライは、リプライ振分け回路223を経て、発行元である通常リクエスト発行部211又は212に返却される。

【0047】

図6は、本発明の実施の形態3にかかる主記憶アクセス経路負荷判定処理の流れを示すフローチャートである。まず、主記憶アクセス経路負荷判定回路231は、ビジー検出回路243又は244からのビジー通知を監視し、いずれか1つのビジー通知のフラグが"1"であるか否かを判定する(S31)。

【0048】

ビジー検出回路243又は244からのビジー通知のフラグが、いずれも"1"以外である場合、主記憶アクセス経路負荷判定回路231は、メモリパトロールリクエストの発行からそのリプライの受信までの応答時間を計測し、計測した応答時間があらかじめ定めた時間を超過した否かを判定する(S32)。

【0049】

ステップS31又はS32のいずれかでYESと判定された場合、主記憶アクセス経路負荷判定回路231は、主記憶アクセス経路の負荷が高いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期をより延長するように調整要求を出力する(S34)。

【0050】

また、ステップS31又はS32のいずれもNOと判定された場合、主記憶アクセス経路負荷判定回路231は、ビジー検出回路243及び244からの無負荷通知のフラグのいずれもが"1"であるか否かを判定する(S33)。いずれの無負荷通知のフラグも"1"であると判定された場合、主記憶アクセス経路負荷判定回路231は、主記憶アクセス経路の負荷が低いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期値に比べて短縮するように調整要求を出力する(S35)。これは、通常リクエスト発行部211及び212から通常運用の主記憶アクセスリクエストが全く行われていない状態を示す。

【0051】

また、ステップS33でNOと判定された場合、主記憶アクセス経路負荷判定回路231は、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期化するように調整要求を出力する(S36)。これは、主記憶アクセス経路の負荷は高くないが、通常運用の主記憶アクセスリクエストが全く無い訳では無いので、メモリパトロールリクエストの発行周期を短くしたままであると通常運用の主記憶アクセスリクエストを必要以上に待たせてしまう事になるのを防ぐためである。

【0052】

尚、図6のステップS31及びS32の順序は逆であっても、並列に処理しても構わない。

【0053】

以上説明したように、本発明の実施の形態3においては、以下に記載するような効果を奏する。すなわち、第1の効果は、主記憶アクセス経路の負荷上昇に応じてメモリパトロールリクエスト発行周期を動的に延長しているので、主記憶アクセスリクエストの調停において通常運用の主記憶アクセスリクエストと競合して通常運用の主記憶アクセスリクエストが待たされてしまい、通常運用の主記憶アクセス性能が低下するのを軽減できることである。

【0054】

また、第2の効果は、通常運用の主記憶アクセスリクエストによる主記憶アクセス経路の負荷が低い時に、メモリパトロールリクエスト発行周期を動的に短縮しているので、主記憶に対するメモリパトロールの網羅性が向上し、ソフトエラーに対する主記憶の信頼性を改善できることである。

【0055】

<その他の発明の実施の形態>

本発明のその他の実施の形態は、コンピュータ等、情報処理装置運用中の主記憶におけるメモリ素子のソフトエラーによる間欠障害を検出および訂正するメモリパトロール制御方式であり、メモリパトロール動作による主記憶アクセスリクエストと通常運用の主記憶アクセスリクエストの競合により通常運用の主記憶アクセスが待たされてしまい、通常運用の主記憶アクセス性能が低下してしまうのを軽減したことを特徴としている。

【0056】

本発明のその他の実施の形態の特徴は、主記憶アクセスを行う複数の通常運用リクエスト発行部とメモリパトロールリクエスト発行部からの各主記憶アクセスを調停し、以後通常運用の主記憶アクセスとメモリパトロールによる主記憶アクセスで主記憶アクセス経路を共有する情報処理装置において、通常運用リクエストによる主記憶アクセス経路の負荷に応じてメモリパトロールリクエストの発行周期を動的に調整し、通常運用リクエストによる主記憶アクセス性能への影響を軽減したことにある。これにより、通常運用リクエストによる主記憶アクセス経路の負荷が高い時には、メモリパトロールリクエストの発行周期を長くする事によりメモリパトロール動作の頻度を少なくして、両者の競合による通常運用リクエストの主記憶アクセス性能低下を軽減する。一方、通常運用リクエストによる主記憶アクセス経路への負荷が低い時には、メモリパトロールリクエストの発行周期を短くする事によりメモリパトロールの頻度を高くして、主記憶に保持しているデータの信頼性を高める事ができる。

【0057】

尚、図5において、メモリパトロール発行部221に含まれる主記憶アクセス経路負荷判定回路231は、発行したメモリパトロールリクエストに対するリプライが返ってくるまでの時間を計測し、主記憶アクセス経路の負荷状況を判定する。また、主記憶アクセス経路負荷判定回路231は、リクエスト調停部222に含まれるビジー検出回路243及び244から調停参加待ちの通常リクエストが多数存在する事を示すビジー信号を受け取る。そして、この状態でメモリパトロールリクエストを発行すると、競合により通常リクエストの主記憶アクセス性能が低下する状況である事を知ることができる。以上の情報を用いて発行タイミング生成回路232は、メモリパトロールリクエストの発行周期を調整する事で、通常リクエストの主記憶アクセス性能低下を軽減できる。

【0058】

図5において、通常リクエスト発行部211及び212から発行された通常運用の主記憶アクセスは、それぞれリクエストキュー241及び242に格納され調停に参加する。以後の主記憶アクセスも順次、リクエストキュー241又は242に格納され、ある一定の個数が格納されるとビジー検出回路243又は244から主記憶アクセス経路負荷判定回路231へのビジー通知が"1"となる。主記憶アクセス経路負荷判定回路231は、ビジー通知が"1"となった事を記憶し、発行タイミング生成回路232にメモリパトロールリクエストの発行周期を長くする要求を行う。また、主記憶アクセス経路負荷判定回路231は、発行タイミング生成回路232からメモリパトロール発行要求信号を、リプライ振分け回路223からメモリパトロールリプライをそれぞれ受信し、メモリパトロールリクエストの発行からリプライの返却までに掛かった時間を計測し、予め定めた時間よりも長い場合にも発行タイミング生成回路232にメモリパトロールリクエストの発行周期を長くする要求を行う。

【0059】

一方、ビジー検出回路243及び244は、リクエストキュー241及び242に通常運用の主記憶アクセスリクエストが一つも存在しない事を検出すると、主記憶アクセス経路負荷判定回路231への無負荷通知が"1"となる。主記憶アクセス経路負荷判定回路231は、ビジー通知が"1"となった履歴が無く、かつ無負荷通知が"1"であった場合に発行タイミング生成回路232にメモリパトロールリクエストの発行周期を短くする要求を行う。

【0060】

以上に述べた事象が一つも発生しなかった場合には、メモリパトロールリクエストの発行周期は、予め設定された値に戻る。

【0061】

以上のように主記憶アクセス経路の負荷に応じ動的にメモリパトロールリクエストの発行周期を調整するので、通常運用の主記憶アクセスリクエストがメモリパトロールにより待たされてしまう頻度が少なくなり、通常運用の主記憶アクセス性能低下を軽減できる。

【0062】

さらに、本発明は上述した実施の形態のみに限定されるものではなく、既に述べた本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

【0063】

上記の実施形態の一部又は全部は、以下の付記のようにも記載され得るが、以下には限られない。

【0064】

(付記1)

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路、

を備えるメモリコントローラ。

【0065】

(付記2)

前記アクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路をさらに備え、

前記メモリ診断回路は、前記ビジー状態であると検出された場合、前記診断リクエストの発行周期を長くする

ことを特徴とする付記1に記載のメモリコントローラ。

【0066】

(付記3)

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるメモリコントローラ。

【0067】

(付記4)

前記メモリ診断回路は、

前記診断リクエストの応答時間を計測し、

前記検出回路により前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする付記3に記載のメモリコントローラ。

【0068】

(付記5)

前記検出回路は、一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記メモリ診断回路は、前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする付記2、3又は4のいずれか1項に記載のメモリコントローラ。

【0069】

(付記6)

前記メモリ診断回路は、前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする付記5に記載のメモリコントローラ。

【0070】

(付記7)

前記メモリ診断回路は、一定時間、前記検出回路により前記ビジー状態及び前記無負荷状態のいずれも検出されていない場合、前記発行周期を前記初期値に戻す

ことを特徴とする付記5又は6に記載のメモリコントローラ。

【0071】

(付記8)

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くする

メモリ診断方法。

【0072】

(付記9)

前記アクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記診断リクエストの発行周期を長くする

ことを特徴とする付記8に記載のメモリ診断方法。

【0073】

(付記10)

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くする

メモリ診断方法。

【0074】

(付記11)

前記診断リクエストの応答時間を計測し、

前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする付記10に記載のメモリ診断方法。

【0075】

(付記12)

一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする付記9、10又は11のいずれか1項に記載のメモリ診断方法。

【0076】

(付記13)

前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする付記12に記載のメモリ診断方法。

【0077】

(付記14)

一定時間、前記検出回路により前記ビジー状態及び前記無負荷状態のいずれも検出されていない場合、前記発行周期を前記初期値に戻す

ことを特徴とする付記12又は13に記載のメモリ診断方法。

【0078】

(付記15)

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記メモリの状態を診断するための診断リクエストを発行し、当該診断リクエストの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【0079】

(付記16)

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路とをさらに備え、

前記メモリ診断回路は、前記ビジー状態であると検出された場合、前記メモリへの診断リクエストの発行周期を長くする、

ことを特徴とする付記15に記載のプロセッサシステム。

【0080】

(付記17)

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【0081】

(付記18)

前記メモリ診断回路は、

前記診断リクエストの応答時間を計測し、

前記検出回路により前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする付記17に記載のプロセッサシステム。

【0082】

(付記19)

前記検出回路は、一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記メモリ診断回路は、前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする付記16、17又は18のいずれか1項に記載のプロセッサシステム。

【0083】

(付記20)

前記メモリ診断回路は、前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする付記19に記載のプロセッサシステム。

【0084】

(付記21)

前記メモリ診断回路は、一定時間、前記検出回路により前記ビジー状態及び前記無負荷状態のいずれも検出されていない場合、前記発行周期を前記初期値に戻す

ことを特徴とする付記19又は20に記載のプロセッサシステム。

【符号の説明】

【0085】

100 プロセッサシステム

101 プロセッサシステム

11 プロセッサ

12 メモリコントローラ

120 メモリ診断回路

12a メモリコントローラ

121 リクエストキュー

122 検出回路

123 メモリ診断回路

13 メモリ

R アクセスリクエスト

D 診断リクエスト

T 応答

200 情報処理装置

21 プロセッサ群

211 通常リクエスト発行部

212 通常リクエスト発行部

22 メモリコントローラ

221 メモリパトロール発行部

231 主記憶アクセス経路負荷判定回路

232 発行タイミング生成回路

233 パトロール発行回路

222 リクエスト調停部

241 リクエストキュー

242 リクエストキュー

243 ビジー検出回路

244 ビジー検出回路

245 調停回路

223 リプライ振分け回路

23 主記憶装置

900 情報処理装置

91 プロセッサ群

911 通常リクエスト発行部

912 通常リクエスト発行部

92 メモリコントローラ

921 メモリパトロール発行部

931 発行タイミング生成回路

932 パトロール発行回路

922 リクエスト調停部

941 リクエストキュー

942 リクエストキュー

943 調停回路

923 リプライ振分け回路

93 主記憶装置

【技術分野】

【0001】

本発明は、メモリコントローラ、メモリ診断方法及びプロセッサシステムに関し、特に、プロセッサからアクセスされるメモリの状態を診断するためのメモリコントローラ、メモリ診断方法及びプロセッサシステムに関する。

【背景技術】

【0002】

図7は、関連技術にかかるメモリコントローラを含む情報処理装置900の構成を示すブロック図である。情報処理装置900は、その構成の一部として、プロセッサ群91、メモリコントローラ92、主記憶装置93を備える。メモリコントローラ92は、プロセッサ群91内の通常リクエスト発行部911及び912から主記憶装置93への複数の主記憶アクセスリクエストを受け付け、複数の主記憶アクセスリクエストを調停した上で、主記憶装置93に対してアクセスを行う。

【0003】

メモリパトロール発行部921は、発行タイミング生成回路931と、パトロール発行回路932を有する。発行タイミング生成回路931はタイマ回路であり、予め定めた周期でメモリパトロールリクエストを発行するためのタイミング信号を生成する。但し、発行タイミング生成回路931は、先に発行したメモリパトロールリクエストのリプライ受信を監視し、リプライを受信するまでは次のメモリパトロールリクエスト発行を保留する。これは、主記憶アクセス経路及び主記憶装置93においてメモリパトロールリクエストを処理する回路を簡素化するためである。

【0004】

通常リクエスト発行部911及び912から発行された通常運用の主記憶アクセスリクエストは、それぞれリクエストキュー941及び942に格納され調停に参加する。この図7では、2つの通常リクエスト発行部と、1つのメモリパトロール発行部との三者で調停を行う構成を示す。

【0005】

尚、特許文献1には、CPUからメモリへのアクセスを制御するメモリコントローラに、メモリをアクセスして診断するメモリ診断手段を有するメモリコントローラに関する技術が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−048224号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上述したメモリコントローラ92においては、通常運用の主記憶アクセスが頻繁に発行され主記憶アクセス経路の負荷が高い時にも、予め定めた周期でメモリパトロールリクエストが発行されるため、通常運用の主記憶アクセスの調停通過を妨げてしまうという問題点があった。すなわち、メモリコントローラ92は、予め設定したメモリパトロールリクエストの発行周期でメモリパトロールを行っていたため、通常運用の主記憶アクセスによる主記憶アクセス経路の負荷が高い時にも一定間隔でメモリパトロールリクエストが割り込み、通常運用の主記憶アクセスがメモリパトロールにより待たされてしまうケースが発生し、通常運用の主記憶アクセス性能を低下させていた。

【0008】

ここで、上述した特許文献1にかかるメモリコントローラは、CPUからメモリへのアクセスと前記メモリ診断手段からメモリへのアクセスとの衝突を検出し、衝突率を算出する。そして、衝突率に応じて前記メモリ診断手段からメモリへのアクセスする周期を調整する。

【0009】

しかしながら、統計的に優位な衝突率を算出するには、それなりのサンプル数が必要となる。そのため、衝突率に応じて周期を調整する時点では、上記衝突がすでに減少し、アクセス性能が回復し、メモリ診断のためのアクセスの周期を調整する必要がなくなっている可能性がある。つまり、特許文献1では、通常運用の主記憶アクセスとメモリパトロールリクエストとの衝突が一定時間続いた場合にしか、上記周期を調整できず、リアルタイム性に欠ける。また、特許文献1では、実際に衝突が起こっている場合を検出しており、衝突を未然に防ぐことはできない。よって、特許文献1では、上述した問題点を解決することはできない。

【0010】

本発明は、このような問題点を解決するためになされたものであり、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整するためのメモリコントローラ、メモリ診断方法及びプロセッサシステムを提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の第1の態様にかかるメモリコントローラは、

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路、

を備える。

【0012】

本発明の第2の態様にかかるメモリコントローラは、

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備える。

【0013】

本発明の第3の態様にかかるメモリ診断方法は、

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くする。

【0014】

本発明の第4の態様にかかるメモリ診断方法は、

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くする。

【0015】

本発明の第5の態様にかかるプロセッサシステムは、

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記メモリの状態を診断するための診断リクエストを発行し、当該診断リクエストの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路と、

を備える。

【0016】

本発明の第6の態様にかかるプロセッサシステムは、

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備える。

【発明の効果】

【0017】

本発明により、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整するためのメモリコントローラ、メモリ診断方法及びプロセッサシステムを提供することができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施の形態1にかかるメモリコントローラを含むプロセッサシステムの構成を示すブロック図である。

【図2】本発明の実施の形態1にかかるメモリ診断処理の流れを示すフローチャートである。

【図3】本発明の実施の形態2にかかるメモリコントローラを含むプロセッサシステムの構成を示すブロック図である。

【図4】本発明の実施の形態2にかかるメモリ診断処理の流れを示すフローチャートである。

【図5】本発明の実施の形態3にかかるメモリコントローラを含む情報処理装置の構成を示すブロック図である。

【図6】本発明の実施の形態3にかかる主記憶アクセス経路負荷判定処理の流れを示すフローチャートである。

【図7】関連技術にかかるメモリコントローラの構成を示すブロック図である。

【発明を実施するための形態】

【0019】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。各図面において、同一要素には同一の符号が付されており、説明の明確化のため、必要に応じて重複説明は省略する。

【0020】

<発明の実施の形態1>

図1は、本発明の実施の形態1にかかるメモリコントローラ12を含むプロセッサシステム100の構成を示すブロック図である。プロセッサシステム100は、少なくともプロセッサ11がメモリ13にアクセスして動作する装置であり、例えば、コンピュータ等の情報処理装置である。プロセッサシステム100は、プロセッサ11と、メモリ13と、メモリコントローラ12と、を備える。プロセッサ11は、メモリ13に対してアクセスリクエストRを発行する。メモリ13は、アクセスリクエストRに対して応答する。メモリコントローラ12は、アクセスリクエストRや自己が発行する診断リクエストDによるメモリ13へのアクセスを制御する。

【0021】

メモリコントローラ12は、メモリ診断回路120を備える。メモリ診断回路120は、メモリ13の状態を診断する診断リクエストDをメモリ13へ発行する。そして、メモリ診断回路120は、発行した診断リクエストに対する応答Tを受信し、診断リクエストの発行時刻から応答Tの受信時刻までの応答時間を計測する。その後、メモリ診断回路120は、計測された応答時間が所定時間より長い場合、診断リクエストDの発行周期を長くする。

【0022】

図2は、本発明の実施の形態1にかかるメモリ診断処理の流れを示すフローチャートである。まず、メモリ診断回路120は、メモリ13へ診断リクエストDを発行する(S11)。次に、メモリ診断回路120は、診断リクエストDの応答時間を計測する(S12)。その後、メモリ診断回路120は、計測された応答時間が所定時間を超過しているか否かを判定する(S13)。ステップS13において応答時間が所定時間を超過していると判定した場合、メモリ診断回路120は、診断リクエストDの発行周期を長くする(S14)。

【0023】

このように、本発明の実施の形態1では、メモリ診断回路120により発行した診断リクエスト単位で応答時間を計測することで、少なくとも1回の診断リクエストの発行により主記憶アクセス経路の負荷が高まったことを検出できる。そして、主記憶アクセス経路の負荷を検出次第、診断リクエストの発行周期を長くする。これにより、主記憶アクセス経路の負荷が高いときに、メモリ診断アクセスの頻度を軽減することができる。よって、不要な負荷を減らし、メモリ診断アクセスに起因した性能低下を防ぐことができる。

【0024】

すなわち、特許文献1のように衝突率を算出するための時間や、そのサンプル数が溜まるまでの時間が不要となり、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整することができる。

【0025】

<発明の実施の形態2>

図3は、本発明の実施の形態2にかかるメモリコントローラ12aを含むプロセッサシステム101の構成を示すブロック図である。プロセッサシステム101は、少なくともプロセッサ11がメモリ13にアクセスして動作する装置であり、例えば、コンピュータ等の情報処理装置である。プロセッサシステム101は、プロセッサシステム100と同様に、プロセッサ11と、メモリ13とを備えるが、メモリコントローラ12aが異なる。メモリコントローラ12aは、アクセスリクエストRや自己が発行する診断リクエストDによるメモリ13へのアクセスを制御する。

【0026】

メモリコントローラ12aは、リクエストキュー121と、検出回路122と、メモリ診断回路123とを備える。リクエストキュー121は、プロセッサ11からメモリ13へのアクセスリクエストRを保持する。検出回路122は、リクエストキュー121に、所定数以上のアクセスリクエストRが保持されている場合に、ビジー状態であると検出する。メモリ診断回路123は、検出回路122によりビジー状態であると検出された場合、メモリ13の状態を診断するための診断リクエストDの発行周期を長くする。

【0027】

図4は、本発明の実施の形態2にかかるメモリ診断処理の流れを示すフローチャートである。まず、検出回路122は、リクエストキュー121を監視し、アクセスリクエストRが所定数以上保持されているか否かを判定する(S21)。アクセスリクエストRが所定数以上保持されていると判定した場合、検出回路122は、ビジー状態であると検出し(S21でYES)、その旨、メモリ診断回路123へ通知する。そして、メモリ診断回路123は、検出回路122からのビジー状態との通知を受信すると、診断リクエストDの発行周期を長くする(S22)。

【0028】

このように、本発明の実施の形態2では、検出回路122がリクエストキュー121の負荷状態を監視してビジー状態を検出することで、主記憶アクセス経路の負荷が高まったことを検出できる。そして、メモリ診断回路123は、主記憶アクセス経路の負荷を検出次第、診断リクエストの発行周期を長くする。これにより、少なくともメモリ診断アクセスの頻度を軽減することで、不要な負荷を減らし、メモリ診断アクセスに起因した性能低下を防ぐことができる。

【0029】

すなわち、特許文献1のように主記憶アクセスとメモリ診断アクセスとの間で相当数の衝突を必要とせず、衝突が発生する前であっても、主記憶アクセス経路の負荷を検出できる。つまり、診断リクエストによる影響があるか否かに関わらず、衝突を未然に防ぎ、主記憶アクセス経路の負荷をリアルタイムに検出して、メモリパトロールリクエストの発行周期を柔軟に調整することができる。

【0030】

<発明の実施の形態3>

図5は、本発明の実施の形態3にかかるメモリコントローラ22を含む情報処理装置200の構成を示すブロック図である。情報処理装置200は、上述したプロセッサシステム100及び101の主要な機能を共に採用した場合の一例である。情報処理装置200は、プロセッサ群21と、メモリコントローラ22と、主記憶装置23とを備える。情報処理装置200のその他の構成は、一般的なものであり、本発明の実施の形態3に影響しないため、図示及び説明を省略する。

【0031】

プロセッサ群21は、複数のプロセッサに相当する通常リクエスト発行部211及び212を含む。尚、通常リクエスト発行部211及び212は、例えば、CPU(Central Processing Unit)等の制御装置であるが、これに限定されない。また、通常リクエスト発行部211及び212の数は、少なくとも1以上であればよい。

【0032】

メモリコントローラ22は、メモリパトロール発行部221と、リクエスト調停部222と、リプライ振分け回路223とを備える。リクエスト調停部222は、リクエストキュー241及び242と、ビジー検出回路243及び244と、調停回路245とを備える。リクエストキュー241及び242のそれぞれは、通常リクエスト発行部211及び212から主記憶装置23への通常運用の主記憶アクセスリクエストを受け付け、所定数を保持する。

【0033】

ビジー検出回路243及び244は、それぞれリクエストキュー241及び242に格納された主記憶アクセスリクエストが一定の個数を超えた事を検出する。このとき、ビジー検出回路243及び244は、ビジー通知のフラグを"1"として主記憶アクセス経路負荷判定回路231へ通知する。例えば、ビジー検出回路243からのビジー通知のフラグが"1"のときは、リクエストキュー241に一定数以上の主記憶アクセスリクエストが格納され調停通過を待っていることを示す。また、ビジー検出回路243及び244は、それぞれリクエストキュー241及び242に、一定時間、主記憶アクセスリクエストが保持されていない場合に、無負荷状態であることを検出する。このとき、ビジー検出回路243及び244は、無負荷通知のフラグを"1"として主記憶アクセス経路負荷判定回路231へ通知する。例えば、ビジー検出回路243からの無負荷通知のフラグが"1"のときは、リクエストキュー241に一つも主記憶アクセスリクエストが格納されていない事を示す。

【0034】

調停回路245は、リクエストキュー241及び242からの2つの通常運用の主記憶アクセスリクエストのリクエストと、後述するパトロール発行回路233からの1つのメモリパトロールアクセスのリクエストとの3つを調停し、当該調停を経て主記憶アクセスリクエストを選択し、主記憶装置23へ出力する。尚、調停回路245による調停は、少なくとも通常運用の主記憶アクセスリクエストと、メモリパトロールのリクエストとの調停がなされるものであればよい。

【0035】

主記憶装置23は、調停回路245による調停を経て選択された主記憶アクセスリクエストについて、目的の処理を行い、リプライ振分け回路223へリプライを出力する。尚、主記憶装置23は、例えば、RAM(Random Access Memory)等の揮発性の記憶装置である。

【0036】

リプライ振分け回路223は、主記憶装置23からリプライを受け付け、当該リプライに対応する主記憶アクセスリクエストの発行元である通常リクエスト発行部211もしくは212又はメモリパトロール発行部221へ振り分けを行い、当該リプライを返却する。

【0037】

メモリパトロール発行部221は、主記憶アクセス経路負荷判定回路231と、発行タイミング生成回路232と、パトロール発行回路233とを備える。主記憶アクセス経路負荷判定回路231は、発行タイミング生成回路232からメモリパトロールリクエスト発行要求を受信し、また、リプライ振分け回路223からメモリパトロールリクエストに対するリプライを受信し、メモリパトロールリクエストの発行からメモリパトロールリクエストのリプライ受信までに掛かった時間を応答時間として計測する。そして、主記憶アクセス経路負荷判定回路231は、応答時間が所定時間より長い場合、発行タイミング生成回路232に対して、メモリパトロールリクエストの発行周期をより長くするように調整要求を出力する。これにより、少なくとも1回の診断リクエストの発行により、主記憶アクセス経路の負荷が高まったことを検出できる。

【0038】

また、主記憶アクセス経路負荷判定回路231には、ビジー検出回路243又は244からの上述したビジー通知又は無負荷通知が接続されている。そして、主記憶アクセス経路負荷判定回路231は、ビジー通知が"1"のときに主記憶アクセス経路の負荷が高いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期をより長くするように調整要求を出力する。これにより、診断リクエストの発行がなくとも、主記憶アクセスリクエスト自体の増加による主記憶アクセス経路の負荷を検出できる。

【0039】

また、主記憶アクセス経路負荷判定回路231は、上記応答時間が所定時間より短く、かつ、無負荷通知が"1"のときに主記憶アクセス経路の負荷が低いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期値に比べて短くするように調整要求を出力する。これにより、主記憶アクセスリクエスト自体による主記憶アクセス経路の負荷が低い時に、つまり、主記憶装置23の処理能力に余裕があるときにより多くのメモリパトロールリクエストを発行することができ、主記憶に対するメモリパトロールの網羅性が向上し、ソフトエラーに対する主記憶の信頼性を改善できる。

【0040】

特に、主記憶アクセス経路負荷判定回路231は、主記憶アクセス経路の負荷が低いと判断する条件として、上記応答時間が所定時間より短く、かつ、無負荷通知が"1"のときであって、さらに一定時間、ビジー通知が"1"以外のときを加えるとよい。これにより、主記憶アクセス経路の負荷が低い場合をより精度良く検出できる。

【0041】

また、主記憶アクセス経路負荷判定回路231は、上記応答時間が所定時間より短く、かつ、一定時間、ビジー通知及び無負荷通知が"1"以外のときに、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期値に戻すように調整要求を出力する。これにより、一時的に発行周期を初期値より長く又は短くした場合であっても、主記憶アクセス経路の負荷状態に応じてメモリパトロールリクエストを適切に発行させることができる。そのため、主記憶装置23の診断を妥当に行いつつ、性能を維持することができる。

【0042】

発行タイミング生成回路232は、メモリパトロールリクエストを周期的に発行するタイミング信号を生成するタイマ回路である。そして、発行タイミング生成回路232は、主記憶アクセス経路負荷判定回路231からの調整要求に応じて、メモリパトロールリクエストの発行周期を動的に延長又は短縮する。そして、発行タイミング生成回路232は、調整された発行周期に従ってパトロール発行回路233に対してメモリパトロールリクエストの発行指示を出力する。

【0043】

ここで、メモリパトロールリクエストは、情報処理装置200内で同時期に1つだけ存在するリクエストである。そのため、これを保証するために、たとえ次の発行周期が来てもメモリパトロール発行部221がメモリパトロールのリプライを受信するまでは発行を抑止する。尚、実際は、発行周期を1回スキップし、次回の発行タイミングまで待つ等の論理となっている。

【0044】

パトロール発行回路233は、発行タイミング生成回路232からの発行指示に応じて主記憶装置23の状態を診断するためのメモリパトロールリクエストを発行する。具体的には、パトロール発行回路233は、調停回路245へメモリパトロールリクエストを出力する。

【0045】

主記憶装置23は、パトロール発行回路233から発行されたメモリパトロールリクエストが調停回路245を経て入力された場合に、メモリ素子に対して読み出しおよびエラー訂正後再書き込みといったパトロール動作を行う。

【0046】

また、通常運用の主記憶アクセスリクエストは、通常リクエスト発行部211及び212からリクエスト調停部222に対して発行される。通常リクエスト発行部211又は212から発行された通常運用の主記憶アクセスリクエストは、リクエストキュー241又は242に格納され、調停回路245における調停に参加する。その後、調停回路245は、調停を経て選択したリクエストにより主記憶装置23にアクセスする。そのリプライは、リプライ振分け回路223を経て、発行元である通常リクエスト発行部211又は212に返却される。

【0047】

図6は、本発明の実施の形態3にかかる主記憶アクセス経路負荷判定処理の流れを示すフローチャートである。まず、主記憶アクセス経路負荷判定回路231は、ビジー検出回路243又は244からのビジー通知を監視し、いずれか1つのビジー通知のフラグが"1"であるか否かを判定する(S31)。

【0048】

ビジー検出回路243又は244からのビジー通知のフラグが、いずれも"1"以外である場合、主記憶アクセス経路負荷判定回路231は、メモリパトロールリクエストの発行からそのリプライの受信までの応答時間を計測し、計測した応答時間があらかじめ定めた時間を超過した否かを判定する(S32)。

【0049】

ステップS31又はS32のいずれかでYESと判定された場合、主記憶アクセス経路負荷判定回路231は、主記憶アクセス経路の負荷が高いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期をより延長するように調整要求を出力する(S34)。

【0050】

また、ステップS31又はS32のいずれもNOと判定された場合、主記憶アクセス経路負荷判定回路231は、ビジー検出回路243及び244からの無負荷通知のフラグのいずれもが"1"であるか否かを判定する(S33)。いずれの無負荷通知のフラグも"1"であると判定された場合、主記憶アクセス経路負荷判定回路231は、主記憶アクセス経路の負荷が低いと判断して、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期値に比べて短縮するように調整要求を出力する(S35)。これは、通常リクエスト発行部211及び212から通常運用の主記憶アクセスリクエストが全く行われていない状態を示す。

【0051】

また、ステップS33でNOと判定された場合、主記憶アクセス経路負荷判定回路231は、発行タイミング生成回路232に対してメモリパトロールリクエストの発行周期を初期化するように調整要求を出力する(S36)。これは、主記憶アクセス経路の負荷は高くないが、通常運用の主記憶アクセスリクエストが全く無い訳では無いので、メモリパトロールリクエストの発行周期を短くしたままであると通常運用の主記憶アクセスリクエストを必要以上に待たせてしまう事になるのを防ぐためである。

【0052】

尚、図6のステップS31及びS32の順序は逆であっても、並列に処理しても構わない。

【0053】

以上説明したように、本発明の実施の形態3においては、以下に記載するような効果を奏する。すなわち、第1の効果は、主記憶アクセス経路の負荷上昇に応じてメモリパトロールリクエスト発行周期を動的に延長しているので、主記憶アクセスリクエストの調停において通常運用の主記憶アクセスリクエストと競合して通常運用の主記憶アクセスリクエストが待たされてしまい、通常運用の主記憶アクセス性能が低下するのを軽減できることである。

【0054】

また、第2の効果は、通常運用の主記憶アクセスリクエストによる主記憶アクセス経路の負荷が低い時に、メモリパトロールリクエスト発行周期を動的に短縮しているので、主記憶に対するメモリパトロールの網羅性が向上し、ソフトエラーに対する主記憶の信頼性を改善できることである。

【0055】

<その他の発明の実施の形態>

本発明のその他の実施の形態は、コンピュータ等、情報処理装置運用中の主記憶におけるメモリ素子のソフトエラーによる間欠障害を検出および訂正するメモリパトロール制御方式であり、メモリパトロール動作による主記憶アクセスリクエストと通常運用の主記憶アクセスリクエストの競合により通常運用の主記憶アクセスが待たされてしまい、通常運用の主記憶アクセス性能が低下してしまうのを軽減したことを特徴としている。

【0056】

本発明のその他の実施の形態の特徴は、主記憶アクセスを行う複数の通常運用リクエスト発行部とメモリパトロールリクエスト発行部からの各主記憶アクセスを調停し、以後通常運用の主記憶アクセスとメモリパトロールによる主記憶アクセスで主記憶アクセス経路を共有する情報処理装置において、通常運用リクエストによる主記憶アクセス経路の負荷に応じてメモリパトロールリクエストの発行周期を動的に調整し、通常運用リクエストによる主記憶アクセス性能への影響を軽減したことにある。これにより、通常運用リクエストによる主記憶アクセス経路の負荷が高い時には、メモリパトロールリクエストの発行周期を長くする事によりメモリパトロール動作の頻度を少なくして、両者の競合による通常運用リクエストの主記憶アクセス性能低下を軽減する。一方、通常運用リクエストによる主記憶アクセス経路への負荷が低い時には、メモリパトロールリクエストの発行周期を短くする事によりメモリパトロールの頻度を高くして、主記憶に保持しているデータの信頼性を高める事ができる。

【0057】

尚、図5において、メモリパトロール発行部221に含まれる主記憶アクセス経路負荷判定回路231は、発行したメモリパトロールリクエストに対するリプライが返ってくるまでの時間を計測し、主記憶アクセス経路の負荷状況を判定する。また、主記憶アクセス経路負荷判定回路231は、リクエスト調停部222に含まれるビジー検出回路243及び244から調停参加待ちの通常リクエストが多数存在する事を示すビジー信号を受け取る。そして、この状態でメモリパトロールリクエストを発行すると、競合により通常リクエストの主記憶アクセス性能が低下する状況である事を知ることができる。以上の情報を用いて発行タイミング生成回路232は、メモリパトロールリクエストの発行周期を調整する事で、通常リクエストの主記憶アクセス性能低下を軽減できる。

【0058】

図5において、通常リクエスト発行部211及び212から発行された通常運用の主記憶アクセスは、それぞれリクエストキュー241及び242に格納され調停に参加する。以後の主記憶アクセスも順次、リクエストキュー241又は242に格納され、ある一定の個数が格納されるとビジー検出回路243又は244から主記憶アクセス経路負荷判定回路231へのビジー通知が"1"となる。主記憶アクセス経路負荷判定回路231は、ビジー通知が"1"となった事を記憶し、発行タイミング生成回路232にメモリパトロールリクエストの発行周期を長くする要求を行う。また、主記憶アクセス経路負荷判定回路231は、発行タイミング生成回路232からメモリパトロール発行要求信号を、リプライ振分け回路223からメモリパトロールリプライをそれぞれ受信し、メモリパトロールリクエストの発行からリプライの返却までに掛かった時間を計測し、予め定めた時間よりも長い場合にも発行タイミング生成回路232にメモリパトロールリクエストの発行周期を長くする要求を行う。

【0059】

一方、ビジー検出回路243及び244は、リクエストキュー241及び242に通常運用の主記憶アクセスリクエストが一つも存在しない事を検出すると、主記憶アクセス経路負荷判定回路231への無負荷通知が"1"となる。主記憶アクセス経路負荷判定回路231は、ビジー通知が"1"となった履歴が無く、かつ無負荷通知が"1"であった場合に発行タイミング生成回路232にメモリパトロールリクエストの発行周期を短くする要求を行う。

【0060】

以上に述べた事象が一つも発生しなかった場合には、メモリパトロールリクエストの発行周期は、予め設定された値に戻る。

【0061】

以上のように主記憶アクセス経路の負荷に応じ動的にメモリパトロールリクエストの発行周期を調整するので、通常運用の主記憶アクセスリクエストがメモリパトロールにより待たされてしまう頻度が少なくなり、通常運用の主記憶アクセス性能低下を軽減できる。

【0062】

さらに、本発明は上述した実施の形態のみに限定されるものではなく、既に述べた本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

【0063】

上記の実施形態の一部又は全部は、以下の付記のようにも記載され得るが、以下には限られない。

【0064】

(付記1)

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路、

を備えるメモリコントローラ。

【0065】

(付記2)

前記アクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路をさらに備え、

前記メモリ診断回路は、前記ビジー状態であると検出された場合、前記診断リクエストの発行周期を長くする

ことを特徴とする付記1に記載のメモリコントローラ。

【0066】

(付記3)

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるメモリコントローラ。

【0067】

(付記4)

前記メモリ診断回路は、

前記診断リクエストの応答時間を計測し、

前記検出回路により前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする付記3に記載のメモリコントローラ。

【0068】

(付記5)

前記検出回路は、一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記メモリ診断回路は、前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする付記2、3又は4のいずれか1項に記載のメモリコントローラ。

【0069】

(付記6)

前記メモリ診断回路は、前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする付記5に記載のメモリコントローラ。

【0070】

(付記7)

前記メモリ診断回路は、一定時間、前記検出回路により前記ビジー状態及び前記無負荷状態のいずれも検出されていない場合、前記発行周期を前記初期値に戻す

ことを特徴とする付記5又は6に記載のメモリコントローラ。

【0071】

(付記8)

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くする

メモリ診断方法。

【0072】

(付記9)

前記アクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記診断リクエストの発行周期を長くする

ことを特徴とする付記8に記載のメモリ診断方法。

【0073】

(付記10)

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くする

メモリ診断方法。

【0074】

(付記11)

前記診断リクエストの応答時間を計測し、

前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする付記10に記載のメモリ診断方法。

【0075】

(付記12)

一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする付記9、10又は11のいずれか1項に記載のメモリ診断方法。

【0076】

(付記13)

前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする付記12に記載のメモリ診断方法。

【0077】

(付記14)

一定時間、前記検出回路により前記ビジー状態及び前記無負荷状態のいずれも検出されていない場合、前記発行周期を前記初期値に戻す

ことを特徴とする付記12又は13に記載のメモリ診断方法。

【0078】

(付記15)

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記メモリの状態を診断するための診断リクエストを発行し、当該診断リクエストの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【0079】

(付記16)

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路とをさらに備え、

前記メモリ診断回路は、前記ビジー状態であると検出された場合、前記メモリへの診断リクエストの発行周期を長くする、

ことを特徴とする付記15に記載のプロセッサシステム。

【0080】

(付記17)

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【0081】

(付記18)

前記メモリ診断回路は、

前記診断リクエストの応答時間を計測し、

前記検出回路により前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする付記17に記載のプロセッサシステム。

【0082】

(付記19)

前記検出回路は、一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記メモリ診断回路は、前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする付記16、17又は18のいずれか1項に記載のプロセッサシステム。

【0083】

(付記20)

前記メモリ診断回路は、前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする付記19に記載のプロセッサシステム。

【0084】

(付記21)

前記メモリ診断回路は、一定時間、前記検出回路により前記ビジー状態及び前記無負荷状態のいずれも検出されていない場合、前記発行周期を前記初期値に戻す

ことを特徴とする付記19又は20に記載のプロセッサシステム。

【符号の説明】

【0085】

100 プロセッサシステム

101 プロセッサシステム

11 プロセッサ

12 メモリコントローラ

120 メモリ診断回路

12a メモリコントローラ

121 リクエストキュー

122 検出回路

123 メモリ診断回路

13 メモリ

R アクセスリクエスト

D 診断リクエスト

T 応答

200 情報処理装置

21 プロセッサ群

211 通常リクエスト発行部

212 通常リクエスト発行部

22 メモリコントローラ

221 メモリパトロール発行部

231 主記憶アクセス経路負荷判定回路

232 発行タイミング生成回路

233 パトロール発行回路

222 リクエスト調停部

241 リクエストキュー

242 リクエストキュー

243 ビジー検出回路

244 ビジー検出回路

245 調停回路

223 リプライ振分け回路

23 主記憶装置

900 情報処理装置

91 プロセッサ群

911 通常リクエスト発行部

912 通常リクエスト発行部

92 メモリコントローラ

921 メモリパトロール発行部

931 発行タイミング生成回路

932 パトロール発行回路

922 リクエスト調停部

941 リクエストキュー

942 リクエストキュー

943 調停回路

923 リプライ振分け回路

93 主記憶装置

【特許請求の範囲】

【請求項1】

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路、

を備えるメモリコントローラ。

【請求項2】

前記アクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路をさらに備え、

前記メモリ診断回路は、前記ビジー状態であると検出された場合、前記診断リクエストの発行周期を長くする

ことを特徴とする請求項1に記載のメモリコントローラ。

【請求項3】

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるメモリコントローラ。

【請求項4】

前記メモリ診断回路は、

前記診断リクエストの応答時間を計測し、

前記検出回路により前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする請求項3に記載のメモリコントローラ。

【請求項5】

前記検出回路は、一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記メモリ診断回路は、前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする請求項2、3又は4のいずれか1項に記載のメモリコントローラ。

【請求項6】

前記メモリ診断回路は、前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする請求項5に記載のメモリコントローラ。

【請求項7】

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くする

メモリ診断方法。

【請求項8】

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くする

メモリ診断方法。

【請求項9】

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記メモリの状態を診断するための診断リクエストを発行し、当該診断リクエストの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【請求項10】

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【請求項1】

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路、

を備えるメモリコントローラ。

【請求項2】

前記アクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路をさらに備え、

前記メモリ診断回路は、前記ビジー状態であると検出された場合、前記診断リクエストの発行周期を長くする

ことを特徴とする請求項1に記載のメモリコントローラ。

【請求項3】

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるメモリコントローラ。

【請求項4】

前記メモリ診断回路は、

前記診断リクエストの応答時間を計測し、

前記検出回路により前記ビジー状態であると検出されなかった場合であっても当該計測された応答時間が所定時間より長い場合、前記発行周期を長くする

ことを特徴とする請求項3に記載のメモリコントローラ。

【請求項5】

前記検出回路は、一定時間、前記アクセスリクエストが前記リクエストキューに保持されていない場合に、無負荷状態であると検出し、

前記メモリ診断回路は、前記無負荷状態であると検出された場合、前記発行周期を初期値に比べて短くする

ことを特徴とする請求項2、3又は4のいずれか1項に記載のメモリコントローラ。

【請求項6】

前記メモリ診断回路は、前記無負荷状態であると検出された場合であって、一定時間、前記検出回路により前記ビジー状態であると検出されていない場合に、前記発行周期を初期値に比べて短くする

ことを特徴とする請求項5に記載のメモリコントローラ。

【請求項7】

プロセッサからのアクセスリクエストに応答するメモリへ、当該メモリの状態を診断するための診断リクエストを発行し、

前記診断リクエストの応答時間を計測し、

当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くする

メモリ診断方法。

【請求項8】

プロセッサからメモリへのアクセスリクエストを保持するためのリクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出し、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くする

メモリ診断方法。

【請求項9】

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記メモリの状態を診断するための診断リクエストを発行し、当該診断リクエストの応答時間を計測し、当該計測された応答時間が所定時間より長い場合、前記診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【請求項10】

メモリと、

前記メモリへのアクセスリクエストを発行するプロセッサと、

前記アクセスリクエストを保持するためのリクエストキューと、

前記リクエストキューに、所定数以上の前記アクセスリクエストが保持されている場合に、ビジー状態であると検出する検出回路と、

前記ビジー状態であると検出された場合、前記メモリの状態を診断するための診断リクエストの発行周期を長くするメモリ診断回路と、

を備えるプロセッサシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−114311(P2013−114311A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257475(P2011−257475)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]