ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスの形成に関するものである。

半導体ウエハ処理中は、周知のパターン形成プロセスおよびエッチングプロセスを使用し、ウエハ内に半導体デバイスの特徴が定められる。これらのプロセスでは、フォトレジスト(PR)材料が、ウエハ上に堆積され、次いで、レチクルによるフィルタリングを経た光に暴露される。レチクルは、一般に、レチクルを通した光の伝搬を遮る代表的な幾何的特徴のパターンを形成されたガラス板である。

【先行技術文献】

【特許文献】

【0002】

【特許文献1】国際公開WO2005/024904号公報

【0003】

レチクルを通過した光は、フォトレジスト材料の表面に接触する。光は、現像剤によってフォトレジスト材料の一部が除去可能になるように、フォトレジスト材料の化学組成を変化させる。ポジ型フォトレジスト材料の場合は、露光された領域が除去され、ネガ型フォトレジスト材料の場合は、露光されなかった領域が除去される。その後、ウエハは、フォトレジスト材料による保護から外れた場所から下位の層を除去するために、エッチングされることにより、ウエハ内に所望の特徴を定める。

【0004】

このようなプロセスでの一問題は、幅の小さい微小なフォトレジスト特徴は、処理中に形状を変化させやすいことである。この変形は、被エッチング膜に転写され、意図した形状、寸法、または粗さから外れたエッチング特徴を生じさせる。エッチングに誘発されるこれらのフォトレジスト変形は、ラインエッジ粗さ、表面粗さ、およびラインうねりなどのグループに分けることができる。ラインエッジ粗さ(Line Edge Roughness,LER)は、パターンがフォトレジストから下位の膜へと転写されるゆえに、パターン形成されたラインのエッジがより不規則になることを意味する。

【発明の概要】

【0005】

本発明の内容を実現するために、かつ本発明の目的にしたがって、ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

【0006】

本発明の別の一態様では、エッジ粗さを低減させてエッチング層内に特徴を形成するための方法が提供される。フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、エッチング層の上に、パターン形成されたフォトレジスト層が形成される。フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成され、これは、複数のサイクルを実施することを含む。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることと、側壁層を残しつつ、フォトレジスト特徴の底部の上に形成された堆積層の部分を除去するために堆積層をエッチバックすることと、を含む。フォトレジスト特徴を通して、エッチング層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。ここで、フォトレジスト層上に層を堆積させること、エッチバックすること、特徴をエッチングすること、および剥ぎ取ることは、単一のプラズマチャンバ内で、in−situでなされる。

【0007】

本発明のこれらの特徴およびその他の特徴が、本発明の詳細な説明において、添付の図面と関連させて、以下で、より詳細に説明される。

【図面の簡単な説明】

【0008】

添付の図面では、限定ではなく例示を目的として本発明が図示されている。図中、類似の参照符号は、類似の要素を示すものとする。

【0009】

【図1】本発明の一実施形態で使用することができるプロセスの、ハイレベルなフローチャートである。

【0010】

【図2A】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図2B】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図2C】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図2D】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【0011】

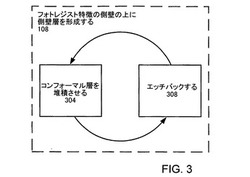

【図3】CDを低減させるためにフォトレジスト特徴の側壁の上に層を堆積させるステップの、より詳細なフローチャートである。

【0012】

【図4】本発明の実施にあたって使用することができるプラズマ処理チャンバの概略図である。

【0013】

【図5A】本発明の実施形態で使用されるコントローラを実現するのに適したコンピュータシステムの説明図である。

【図5B】本発明の実施形態で使用されるコントローラを実現するのに適したコンピュータシステムの説明図である。

【0014】

【図6A】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図6B】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【発明を実施するための形態】

【0015】

添付の図面に示されるようないくつかの好ましい実施形態に基づいて、本発明が詳細に説明される。以下の説明では、本発明の完全な理解を可能にするために、多くの詳細が特定されている。しかしながら、当業者ならば明らかなように、本発明は、これらの一部または全部の詳細を特定しなくても実施可能である。また、本発明が不必要に不明瞭になるのを避けるため、周知のプロセス工程および/構造の詳細な説明は省略される。

【0016】

ラインエッジ粗さは、不均一な堆積、ラインに対して急角度で入るイオンによるイオンスパッタリング、フォトレジストまたはマスクの可動性の欠如、フォトレジストと、マスクと、エッチング副産物(ポリマー)との間における応力不整合、およびフォトレジストまたはマスクの化学的変質によって引き起こされると考えられる。ラインエッジ粗さは、様々な形態で現れるが、同じ要因は、フォトレジストもしくはマスクのねじれまたはうねりを引き起こす可能性もある。うねりまたはねじれは、フォトレジストの粗化だけでなく、ラインの幅と同程度の長さスケールをともなう上から見たライン形状の変化も意味する。うねりは、具体的には、フォトレジストの粗化に起因する狭いライン構造の変形を意味する。ラインエッジ粗さは、フォトレジストのファセッティングによってフォトレジストの頂部に極狭構造が形成される密なコンタクトまたは密なセルのエッチングにおいて見ることができる。様々なリソグラフィ技術で様々な構成のレジストおよびマスクが使用されているにもかかわらず、うねりは、遠紫外線DUVフォトレジスト、193nmフォトレジスト、ひいては非晶質炭素など更に堅いマスクでも観測されてきた。

【0017】

うねりを引き起こすメカニズムの詳細は、よく理解されていないが、先に挙げられた要因が、原因として考えられる。しかしながら、フォトレジストラインの頂部に過剰にポリマーが堆積されるとうねりが誘発されうることがわかっている。これは、フォトレジストを引っ張ってその形状を崩す傾向がある堆積膜内の応力によって引き起こされると考えられる。この問題は、とりわけ193nmタイプのフォトレジストが持つエッチング処理中にやわらかくなる傾向によって、更に悪化する恐れがある。このメカニズムは、うねりの全ての事例を説明するものではない。場合によっては、フォトレジストが明らかに堆積ではなくエッチングされている場合でも、やはりフォトレジストがうねることがある。うねりは、エッチング中におけるフォトレジストの組成変化に関連する可能性がある。これは、193nmフォトレジストの場合により深刻である。

【0018】

理解を促すため、図1は、本発明の一実施形態で使用することができるプロセスの、ハイレベルなフローチャートである。パターン形成されたフォトレジストマスクが提供される(ステップ104)。図2Aは、スタック200を形成する、基板204の上の被エッチング層208と、特徴214をともなうパターン形成されたフォトレジストマスク212と、被エッチング層208の上のその下のARL210との概略断面図である。フォトレジストマスクは、可能な限り小さい特徴の最も広い幅316であるフォトレジスト特徴微小寸法(CD)を有する。現在のところ、248nmフォトレジストに従来のプロセスを使用した場合の、そのフォトレジストの代表的CDは、230〜250nmである。パターン形成されたフォトレジストマスクを提供するためには、先ず、被エッチング層の上に、フォトレジスト層を形成することができる。次いで、フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。

【0019】

フォトレジスト特徴の側壁の上に、側壁層が形成される(ステップ108)。図2Bは、特徴214の側壁の上に側壁層220を形成された、パターン形成されたフォトレジストマスク212の概略断面図である。側壁層は、実質的に垂直でかつコンフォーマルな側壁を形成することが好ましい。実質的に垂直な側壁の一例は、底部から頂部にかけて、特徴の底部との間に88〜90度の角度を形成する側壁である。コンフォーマルな側壁は、特徴の頂部から底部にかけて、実質的に同じ厚さの堆積層を有する。コンフォーマルでない側壁は、ファセッティング構造またはパン塊状構造を形成し、これは、側壁を実質的に垂直でなくする。テーパ側壁(ファセッティング構造に起因する)またはパン塊状側壁は、堆積層のCDを増大させ、質の悪いエッチングマスクを提供する。

【0020】

エッチング層のすぐ上に残留するあらゆる堆積層およびエッチング層の上のその他のあらゆる中間層をエッチングするために、ブレイクスルーエッチングを使用することができる(ステップ112)。

【0021】

次いで、形成された側壁層220を通して、被エッチング層208内に特徴がエッチングされる(ステップ116)。図2Cは、被エッチング層208内にエッチングされた特徴232を示している。

【0022】

次いで、フォトレジストおよび側壁層を剥ぎ取ることができる(ステップ120)。これは、単一のステップとして、または個々の堆積層除去ステップおよびフォトレジスト剥ぎ取りステップを含む2つの別々のステップとしてなすことができる。剥ぎ取りプロセスには、アッシングを使用することができる。図2Dは、堆積層およびフォトレジストマスクを除去された後のスタック200を示している。追加の形成ステップが実施可能である(ステップ124)。例えば、次いで、特徴内にコンタクト240が形成可能である。デュアルダマシン構造を提供するため、コンタクトの形成に先立って、トレンチがエッチング可能である。コンタクトの形成後は、更に追加のプロセスが実施可能である。

【0023】

図3は、フォトレジスト特徴の側壁の上に側壁層を形成する一実施形態の、より詳細なフローチャートである(ステップ108)。このステップは、少なくとも2回繰り返される循環ステップである。フォトレジスト層の上に、コンフォーマル層が堆積される(ステップ304)。コンフォーマル層は、次いで、フォトレジスト特徴の底部にあるあらゆる堆積物を除去して側壁層を形成するために、エッチバックされる(ステップ308)。

【0024】

実施例

1つの実施例では、基板204が、被エッチング層208と、ARC層210と、パターン形成されたフォトレジストマスク212とともに、エッチングチャンバ内に配される。

【0025】

図4は、側壁層形成、エッチング、および剥ぎ取りに使用することができる処理チャンバ400の概略図である。プラズマ処理チャンバ400は、閉じ込めリング402と、上部電極404と、下部電極408と、ガス源410と、排出ポンプ420とを含む。ガス源410は、堆積ガス源412と、エッチバックガス源416とを含む。ガス源410は、エッチングガス源418などの追加のガス源を含むことができる。プラズマ処理チャンバ400内において、基板204は、下部電極408の上に配置される。下部電極408は、基板204を保持するための、適切な基板チャックメカニズム(例えば、静電的クランプ、機械的クランプ等など)を搭載している。リアクタトップ428は、下部電極408の真向かいに設けられた上部電極404を搭載している。上部電極404と、下部電極408と、閉じ込めリング402とが、閉じ込めプラズマ体積を定める。ガスが、ガス源410によって閉じ込めプラズマ体積に供給され、排出ポンプ420によって閉じ込めリング402および排出口を通って閉じ込めプラズマ体積から排出される。上部電極404には、第1のRF源444が電気的に接続される。下部電極408には、第2のRF源448が電気的に接続される。チャンバ壁452が、閉じ込めリング402と、上部電極404と、下部電極408とを取り囲む。第1のRF源444および第2のRF源448は、ともに、27MHz電源と2MHz電源とを含むことができる。電極へのRF電源の接続としては、異なる組み合わせが可能である。本発明の好ましい一実施形態で使用することができる、カリフォルニア州フリーモント所在のラムリサーチ(LAM Reseach Corporation,登録商標)による二重周波数容量性(Dual Frequency Capacitive,DFC)システムの場合、下部電極に接続される第2のRF電源448は、27MHz電源および2MHz電源の両方で構成され、上部電極は、接地される。RF源444,448、排出ポンプ420、およびガス源410には、可制御式にコントローラ435が接続される。DFCシステムは、被エッチング層208がシリコン酸化物または有機ケイ酸塩ガラスなどの誘電層である場合に使用されると考えられる。

【0026】

図5Aおよび図5Bは、本発明の実施形態で使用されるコントローラ435を実現するのに適したコンピュータシステム1300を図示している。図5Aは、コンピュータシステムとして考えられる1つの物理的形態を示している。もちろん、コンピュータシステムは、集積回路、プリント回路基板、および小型携帯端末から、巨大スーパーコンピュータに到るまで、多くの物理的形態をとることができる。コンピュータシステム1300は、モニタ1302、ディスプレイ1304、筐体1306、ディスクドライブ1308、キーボード1310、およびマウス1312を含む。ディスク1314は、コンピュータシステム1300との間でデータをやりとりするために使用されるコンピュータ可読媒体である。

【0027】

図5Bは、コンピュータシステム1300のブロック図の一例である。システムバス1320には、種々様々なサブシステムが取り付けられる。プロセッサ1322(中央演算処理装置、すなわちCPUとも称される)は、メモリ1324を含む記憶装置に接続される。メモリ1324は、ランダムアクセスメモリ(RAM)および読み出し専用メモリ(ROM)を含む。当該分野で知られているように、ROMは、CPUに対してデータおよび命令を単方向的に伝送する働きをし、RAMは、一般に、データおよび命令を双方向的に伝送するために使用される。これらのメモリは、いずれのタイプも、後述される任意の適切なコンピュータ可読媒体を含むことができる。CPU1322には、固定ディスク1326も双方向的に接続され、これは、追加のデータ記憶容量を提供し、やはり、後述される任意のコンピュータ可読媒体を含むことができる。固定ディスク1326は、プログラムやデータなどを格納するために使用されてよく、一般に、一次記憶より低速な二次記憶媒体(ハードディスクなど)である。なお、固定ディスク1326内に保持される情報は、もし適切であれば、メモリ1324内の仮想メモリとして標準的な形で組み入れ可能であることがわかる。取り外し可能ディスク1314は、後述される任意のコンピュータ可読媒体の形態をとることができる。

【0028】

CPU1322は、ディスプレイ1304、キーボード1310、マウス1312、およびスピーカ1330などの様々な入出力装置にも接続される。概して、入出力装置は、ビデオディスプレイ、トラックボール、マウス、キーボード、マイクロフォン、タッチセンサ式ディスプレイ、トランスデューサカード読み取り装置、磁気テープもしくは紙テープ読み取り装置、タブレット、スタイラス、音声もしくは手書き文字認識装置、バイオメトリック読み取り装置、またはその他のコンピュータのうちの任意であることが可能である。CPU1322は、ネットワークインターフェース1340を使用して、別のコンピュータまたは通信ネットワークに随意に接続することができる。このようなネットワークインターフェースがあれば、CPUは、上述された方法のステップを実施する過程において、ネットワークから情報を受信する、またはネットワークに情報を出力することができると考えられる。更に、本発明の方法の実施形態は、CPU1322上のみで実行されてもよいし、あるいは処理の一部を共有するリモートCPUと連携してインターネットなどのネットワークを通じて実行されてもよい。

【0029】

また、本発明の実施形態は、更に、コンピュータによって実行される様々な動作を実施するためのコンピュータコードを記録されたコンピュータ可読媒体をともなった、コンピュータストレージ製品に関する。媒体およびコンピュータコードは、本発明の目的のために特別に設計および構成されたものであってもよいし、あるいはコンピュータソフトウェアの分野の当業者にとって周知でなおかつ利用可能なものであってもよい。コンピュータ可読媒体の例は、ハードディスク、フロッピィディスク、および磁気テープなどの磁気媒体、CD−ROM、およびホログラフィック装置などの光媒体、フロプティカルディスクなどの光磁気媒体、ならびに特定用途向け集積回路(ASIC)、プログラム可能論理装置(PLD)、ROM装置、およびRAM装置などプログラムコードの格納および実行のために特別に構成されたハードウェアデバイスを含むが、これらに限定されない。コンピュータコードの例は、コンパイラによって生成されるなどのマシンコード、およびインタープリタを使用してコンピュータによって実行される高水準コードを含むファイルを含む。コンピュータ可読媒体は、搬送波に組み込まれたコンピュータデータ信号によって伝送されなおかつプロセッサによって実行可能な一連の命令を表すコンピュータコードでもあることも可能である。

【0030】

エッチングチャンバ内において、フォトレジスト特徴の側壁の上に、側壁層が形成される(ステップ108)。コンフォーマル層の堆積(ステップ304)のためのレシピの一例として、堆積ガス源412は、150sccmのCH3Fのフローと、75sccmのN2のフローと、100sccmのArのフローとを提供する。圧力は、80ミリトールに設定される。基板は、20℃の温度に維持される。第2のRF源448は、27MHzの周波数では400ワットを、2MHzの周波数では0ワットを提供する。

【0031】

図6Aは、基板604と、その上のエッチング層608と、その上のARC層610と、その上のパターン形成されたフォトレジスト層612と、その上の堆積されたコンフォーマル層620とを示した概略断面図である。この実施例では、コンフォーマル層620は、フォトレジスト層612の側壁および頂部と、フォトレジスト特徴614の底部のARC610とを覆っている。その他の実施形態では、コンフォーマル層は、フォトレジスト特徴の底部のARC上に堆積されないかもしれない。好ましくは、堆積されたコンフォーマル層は、単分子層から20nmまでの厚さである。より好ましくは、堆積されたコンフォーマル層は、単分子層から7nmまでの厚さである。最も好ましくは、堆積されたコンフォーマル層は、単分子層から2nmまでの厚さである。

【0032】

好ましくは、コンフォーマル層の堆積は、原子層成長、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを含む。より好ましくは、コンフォーマル層の堆積は、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを含む。好ましくは、基板の温度は、−80℃から120℃の間に維持される。一般に、120℃は、フォトレジストのガラス転移温度である。基板の温度は、フォトレジストのそのガラス転移温度より低く維持することが好ましい。より好ましくは、基板の温度は、−10℃から50℃の間に維持される。最も好ましくは、基板の温度は、20℃に維持される。好ましくは、バイアス電位は、120ボルト未満である。より好ましくは、バイアス電位は、100ボルト未満である。最も好ましくは、バイアス電位は、20ボルトから80ボルトの間である。

【0033】

好ましくは、堆積層は、ポリマー、TEOS、SiO2、Si3N2、SiC、Si、Al2O3、AlN、Cu、HfO2、Mo、Ta、TaN、TaO2、Ti、TiN、TiO2、TiSiN、およびWのうちの少なくとも1つを含む。ポリマーは、フッ化炭化水素材料など炭化水素をベースにした材料である。

【0034】

エッチバック(ステップ308)中は、100sccmのCF4など、ハロゲン(すなわちフッ素、臭素、塩素)を含有するガスが提供される。この実施例では、CF4が、エッチバック中に提供される唯一のガスである。20ミリトールの圧力が、チャンバに提供される。第2のRF源448は、27MHzの周波数で600ワットを、2MHzの周波数で0ワットを提供する。

【0035】

図6Bは、堆積されたコンフォーマル層から側壁624を形成するためにコンフォーマル層がエッチバックされた後の、基板604と、その上のエッチング層608と、その上のARC層610と、その上のパターン形成されたフォトレジスト層612とを示した概略断面図である。この実施例では、フォトレジスト層612の頂部およびフォトレジスト特徴614の底部を覆っているコンフォーマル層の部分が除去され、フォトレジスト特徴の側壁上の層のみが残される。その他の実施形態では、フォトレジストの頂部上のコンフォーマル層の部分は残留し、フォトレジスト特徴の底部のARC上の層のみがエッチバックによって除去される。しかしながら、このような一実施形態では、フォトレジストの頂部の上のコンフォーマル層の一部が除去される。このような一実施形態では、フォトレジスト層の頂部の上に残留しているコンフォーマル層を、エッチングのハードマスクとして使用することができる。

【0036】

この実施例では、コンフォーマル層堆積のステップ(ステップ304)およびエッチバックのステップ(ステップ308)を含む側壁形成のサイクル(ステップ108)が、少なくとも2回実施される。より好ましくは、側壁の形成は、3〜50のサイクルにわたって実施される。最も好ましくは、側壁の形成は、3〜10サイクルにわたって実施される。好ましくは、完成した側壁層は、厚さ100nm未満のように、薄くなおかつエッチングに対して耐性である。より好ましくは、完成した側壁層は、単分子層から50nmまでの厚さである。最も好ましくは、完成した側壁層は、単分子層から2nmまでの厚さである。

【0037】

その他の実施形態では、エッチングサイクルは、追加堆積および/またはエッチバックのステップを更に含むことができる。

【0038】

フォトレジスト特徴の底部上に残留するあらゆる堆積層を除去するために、ブレイクスルーエッチングレシピの一例を使用することができる。このようなブレイクスルーは、エッチバックに使用されるレシピと同じようなレシピを使用することができる。

【0039】

被エッチング層の一例は、SiN、SiC、酸化物、または低k誘電体などの従来のエッチング層であることが可能である。被エッチング層のエッチングには、従来のエッチングレシピを使用することができる。

【0040】

フォトレジストおよび側壁層を剥ぎ取る(ステップ120)には、酸素アッシングを使用することができる。

【0041】

複数のサイクルにわたる側壁層の形成によって、より改良された側壁層プロファイルが提供される。上記の方法を通じて側壁層を提供すると、予想外にラインエッジ粗さが低減されることがわかった。また、側壁層は、より改良された選択性制御を提供する。頂部の層も底部の層もともなわない側壁層を形成することによって、ラインエッジ粗さを低減させられると考えられる。

【0042】

本発明の好ましい一実施形態では、堆積層の堆積、エッチバック、ブレイクスルーエッチ、および側壁層を通した層のエッチングを、図示されたような同一のエッチングチャンバ内で、in−situでなすことができる。

【0043】

以上では、複数の好ましい実施形態の観点から本発明が説明された。しかしながら、本発明の範囲には、変更形態、置換形態、および様々な代替の等価形態が含まれる。また、本発明の方法および装置を実現するものとして、多くの代替の方法がある。したがって、添付の特許請求の範囲は、本発明の真の趣旨および範囲に含まれるものとして、このようなあらゆる変更形態、置換形態、および様々な代替の等価形態を含むものと解釈される。

【技術分野】

【0001】

本発明は、半導体デバイスの形成に関するものである。

半導体ウエハ処理中は、周知のパターン形成プロセスおよびエッチングプロセスを使用し、ウエハ内に半導体デバイスの特徴が定められる。これらのプロセスでは、フォトレジスト(PR)材料が、ウエハ上に堆積され、次いで、レチクルによるフィルタリングを経た光に暴露される。レチクルは、一般に、レチクルを通した光の伝搬を遮る代表的な幾何的特徴のパターンを形成されたガラス板である。

【先行技術文献】

【特許文献】

【0002】

【特許文献1】国際公開WO2005/024904号公報

【0003】

レチクルを通過した光は、フォトレジスト材料の表面に接触する。光は、現像剤によってフォトレジスト材料の一部が除去可能になるように、フォトレジスト材料の化学組成を変化させる。ポジ型フォトレジスト材料の場合は、露光された領域が除去され、ネガ型フォトレジスト材料の場合は、露光されなかった領域が除去される。その後、ウエハは、フォトレジスト材料による保護から外れた場所から下位の層を除去するために、エッチングされることにより、ウエハ内に所望の特徴を定める。

【0004】

このようなプロセスでの一問題は、幅の小さい微小なフォトレジスト特徴は、処理中に形状を変化させやすいことである。この変形は、被エッチング膜に転写され、意図した形状、寸法、または粗さから外れたエッチング特徴を生じさせる。エッチングに誘発されるこれらのフォトレジスト変形は、ラインエッジ粗さ、表面粗さ、およびラインうねりなどのグループに分けることができる。ラインエッジ粗さ(Line Edge Roughness,LER)は、パターンがフォトレジストから下位の膜へと転写されるゆえに、パターン形成されたラインのエッジがより不規則になることを意味する。

【発明の概要】

【0005】

本発明の内容を実現するために、かつ本発明の目的にしたがって、ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

【0006】

本発明の別の一態様では、エッジ粗さを低減させてエッチング層内に特徴を形成するための方法が提供される。フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、エッチング層の上に、パターン形成されたフォトレジスト層が形成される。フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成され、これは、複数のサイクルを実施することを含む。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることと、側壁層を残しつつ、フォトレジスト特徴の底部の上に形成された堆積層の部分を除去するために堆積層をエッチバックすることと、を含む。フォトレジスト特徴を通して、エッチング層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。ここで、フォトレジスト層上に層を堆積させること、エッチバックすること、特徴をエッチングすること、および剥ぎ取ることは、単一のプラズマチャンバ内で、in−situでなされる。

【0007】

本発明のこれらの特徴およびその他の特徴が、本発明の詳細な説明において、添付の図面と関連させて、以下で、より詳細に説明される。

【図面の簡単な説明】

【0008】

添付の図面では、限定ではなく例示を目的として本発明が図示されている。図中、類似の参照符号は、類似の要素を示すものとする。

【0009】

【図1】本発明の一実施形態で使用することができるプロセスの、ハイレベルなフローチャートである。

【0010】

【図2A】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図2B】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図2C】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図2D】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【0011】

【図3】CDを低減させるためにフォトレジスト特徴の側壁の上に層を堆積させるステップの、より詳細なフローチャートである。

【0012】

【図4】本発明の実施にあたって使用することができるプラズマ処理チャンバの概略図である。

【0013】

【図5A】本発明の実施形態で使用されるコントローラを実現するのに適したコンピュータシステムの説明図である。

【図5B】本発明の実施形態で使用されるコントローラを実現するのに適したコンピュータシステムの説明図である。

【0014】

【図6A】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【図6B】本発明の一実施形態にしたがって処理されるスタックの概略断面図である。

【発明を実施するための形態】

【0015】

添付の図面に示されるようないくつかの好ましい実施形態に基づいて、本発明が詳細に説明される。以下の説明では、本発明の完全な理解を可能にするために、多くの詳細が特定されている。しかしながら、当業者ならば明らかなように、本発明は、これらの一部または全部の詳細を特定しなくても実施可能である。また、本発明が不必要に不明瞭になるのを避けるため、周知のプロセス工程および/構造の詳細な説明は省略される。

【0016】

ラインエッジ粗さは、不均一な堆積、ラインに対して急角度で入るイオンによるイオンスパッタリング、フォトレジストまたはマスクの可動性の欠如、フォトレジストと、マスクと、エッチング副産物(ポリマー)との間における応力不整合、およびフォトレジストまたはマスクの化学的変質によって引き起こされると考えられる。ラインエッジ粗さは、様々な形態で現れるが、同じ要因は、フォトレジストもしくはマスクのねじれまたはうねりを引き起こす可能性もある。うねりまたはねじれは、フォトレジストの粗化だけでなく、ラインの幅と同程度の長さスケールをともなう上から見たライン形状の変化も意味する。うねりは、具体的には、フォトレジストの粗化に起因する狭いライン構造の変形を意味する。ラインエッジ粗さは、フォトレジストのファセッティングによってフォトレジストの頂部に極狭構造が形成される密なコンタクトまたは密なセルのエッチングにおいて見ることができる。様々なリソグラフィ技術で様々な構成のレジストおよびマスクが使用されているにもかかわらず、うねりは、遠紫外線DUVフォトレジスト、193nmフォトレジスト、ひいては非晶質炭素など更に堅いマスクでも観測されてきた。

【0017】

うねりを引き起こすメカニズムの詳細は、よく理解されていないが、先に挙げられた要因が、原因として考えられる。しかしながら、フォトレジストラインの頂部に過剰にポリマーが堆積されるとうねりが誘発されうることがわかっている。これは、フォトレジストを引っ張ってその形状を崩す傾向がある堆積膜内の応力によって引き起こされると考えられる。この問題は、とりわけ193nmタイプのフォトレジストが持つエッチング処理中にやわらかくなる傾向によって、更に悪化する恐れがある。このメカニズムは、うねりの全ての事例を説明するものではない。場合によっては、フォトレジストが明らかに堆積ではなくエッチングされている場合でも、やはりフォトレジストがうねることがある。うねりは、エッチング中におけるフォトレジストの組成変化に関連する可能性がある。これは、193nmフォトレジストの場合により深刻である。

【0018】

理解を促すため、図1は、本発明の一実施形態で使用することができるプロセスの、ハイレベルなフローチャートである。パターン形成されたフォトレジストマスクが提供される(ステップ104)。図2Aは、スタック200を形成する、基板204の上の被エッチング層208と、特徴214をともなうパターン形成されたフォトレジストマスク212と、被エッチング層208の上のその下のARL210との概略断面図である。フォトレジストマスクは、可能な限り小さい特徴の最も広い幅316であるフォトレジスト特徴微小寸法(CD)を有する。現在のところ、248nmフォトレジストに従来のプロセスを使用した場合の、そのフォトレジストの代表的CDは、230〜250nmである。パターン形成されたフォトレジストマスクを提供するためには、先ず、被エッチング層の上に、フォトレジスト層を形成することができる。次いで、フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。

【0019】

フォトレジスト特徴の側壁の上に、側壁層が形成される(ステップ108)。図2Bは、特徴214の側壁の上に側壁層220を形成された、パターン形成されたフォトレジストマスク212の概略断面図である。側壁層は、実質的に垂直でかつコンフォーマルな側壁を形成することが好ましい。実質的に垂直な側壁の一例は、底部から頂部にかけて、特徴の底部との間に88〜90度の角度を形成する側壁である。コンフォーマルな側壁は、特徴の頂部から底部にかけて、実質的に同じ厚さの堆積層を有する。コンフォーマルでない側壁は、ファセッティング構造またはパン塊状構造を形成し、これは、側壁を実質的に垂直でなくする。テーパ側壁(ファセッティング構造に起因する)またはパン塊状側壁は、堆積層のCDを増大させ、質の悪いエッチングマスクを提供する。

【0020】

エッチング層のすぐ上に残留するあらゆる堆積層およびエッチング層の上のその他のあらゆる中間層をエッチングするために、ブレイクスルーエッチングを使用することができる(ステップ112)。

【0021】

次いで、形成された側壁層220を通して、被エッチング層208内に特徴がエッチングされる(ステップ116)。図2Cは、被エッチング層208内にエッチングされた特徴232を示している。

【0022】

次いで、フォトレジストおよび側壁層を剥ぎ取ることができる(ステップ120)。これは、単一のステップとして、または個々の堆積層除去ステップおよびフォトレジスト剥ぎ取りステップを含む2つの別々のステップとしてなすことができる。剥ぎ取りプロセスには、アッシングを使用することができる。図2Dは、堆積層およびフォトレジストマスクを除去された後のスタック200を示している。追加の形成ステップが実施可能である(ステップ124)。例えば、次いで、特徴内にコンタクト240が形成可能である。デュアルダマシン構造を提供するため、コンタクトの形成に先立って、トレンチがエッチング可能である。コンタクトの形成後は、更に追加のプロセスが実施可能である。

【0023】

図3は、フォトレジスト特徴の側壁の上に側壁層を形成する一実施形態の、より詳細なフローチャートである(ステップ108)。このステップは、少なくとも2回繰り返される循環ステップである。フォトレジスト層の上に、コンフォーマル層が堆積される(ステップ304)。コンフォーマル層は、次いで、フォトレジスト特徴の底部にあるあらゆる堆積物を除去して側壁層を形成するために、エッチバックされる(ステップ308)。

【0024】

実施例

1つの実施例では、基板204が、被エッチング層208と、ARC層210と、パターン形成されたフォトレジストマスク212とともに、エッチングチャンバ内に配される。

【0025】

図4は、側壁層形成、エッチング、および剥ぎ取りに使用することができる処理チャンバ400の概略図である。プラズマ処理チャンバ400は、閉じ込めリング402と、上部電極404と、下部電極408と、ガス源410と、排出ポンプ420とを含む。ガス源410は、堆積ガス源412と、エッチバックガス源416とを含む。ガス源410は、エッチングガス源418などの追加のガス源を含むことができる。プラズマ処理チャンバ400内において、基板204は、下部電極408の上に配置される。下部電極408は、基板204を保持するための、適切な基板チャックメカニズム(例えば、静電的クランプ、機械的クランプ等など)を搭載している。リアクタトップ428は、下部電極408の真向かいに設けられた上部電極404を搭載している。上部電極404と、下部電極408と、閉じ込めリング402とが、閉じ込めプラズマ体積を定める。ガスが、ガス源410によって閉じ込めプラズマ体積に供給され、排出ポンプ420によって閉じ込めリング402および排出口を通って閉じ込めプラズマ体積から排出される。上部電極404には、第1のRF源444が電気的に接続される。下部電極408には、第2のRF源448が電気的に接続される。チャンバ壁452が、閉じ込めリング402と、上部電極404と、下部電極408とを取り囲む。第1のRF源444および第2のRF源448は、ともに、27MHz電源と2MHz電源とを含むことができる。電極へのRF電源の接続としては、異なる組み合わせが可能である。本発明の好ましい一実施形態で使用することができる、カリフォルニア州フリーモント所在のラムリサーチ(LAM Reseach Corporation,登録商標)による二重周波数容量性(Dual Frequency Capacitive,DFC)システムの場合、下部電極に接続される第2のRF電源448は、27MHz電源および2MHz電源の両方で構成され、上部電極は、接地される。RF源444,448、排出ポンプ420、およびガス源410には、可制御式にコントローラ435が接続される。DFCシステムは、被エッチング層208がシリコン酸化物または有機ケイ酸塩ガラスなどの誘電層である場合に使用されると考えられる。

【0026】

図5Aおよび図5Bは、本発明の実施形態で使用されるコントローラ435を実現するのに適したコンピュータシステム1300を図示している。図5Aは、コンピュータシステムとして考えられる1つの物理的形態を示している。もちろん、コンピュータシステムは、集積回路、プリント回路基板、および小型携帯端末から、巨大スーパーコンピュータに到るまで、多くの物理的形態をとることができる。コンピュータシステム1300は、モニタ1302、ディスプレイ1304、筐体1306、ディスクドライブ1308、キーボード1310、およびマウス1312を含む。ディスク1314は、コンピュータシステム1300との間でデータをやりとりするために使用されるコンピュータ可読媒体である。

【0027】

図5Bは、コンピュータシステム1300のブロック図の一例である。システムバス1320には、種々様々なサブシステムが取り付けられる。プロセッサ1322(中央演算処理装置、すなわちCPUとも称される)は、メモリ1324を含む記憶装置に接続される。メモリ1324は、ランダムアクセスメモリ(RAM)および読み出し専用メモリ(ROM)を含む。当該分野で知られているように、ROMは、CPUに対してデータおよび命令を単方向的に伝送する働きをし、RAMは、一般に、データおよび命令を双方向的に伝送するために使用される。これらのメモリは、いずれのタイプも、後述される任意の適切なコンピュータ可読媒体を含むことができる。CPU1322には、固定ディスク1326も双方向的に接続され、これは、追加のデータ記憶容量を提供し、やはり、後述される任意のコンピュータ可読媒体を含むことができる。固定ディスク1326は、プログラムやデータなどを格納するために使用されてよく、一般に、一次記憶より低速な二次記憶媒体(ハードディスクなど)である。なお、固定ディスク1326内に保持される情報は、もし適切であれば、メモリ1324内の仮想メモリとして標準的な形で組み入れ可能であることがわかる。取り外し可能ディスク1314は、後述される任意のコンピュータ可読媒体の形態をとることができる。

【0028】

CPU1322は、ディスプレイ1304、キーボード1310、マウス1312、およびスピーカ1330などの様々な入出力装置にも接続される。概して、入出力装置は、ビデオディスプレイ、トラックボール、マウス、キーボード、マイクロフォン、タッチセンサ式ディスプレイ、トランスデューサカード読み取り装置、磁気テープもしくは紙テープ読み取り装置、タブレット、スタイラス、音声もしくは手書き文字認識装置、バイオメトリック読み取り装置、またはその他のコンピュータのうちの任意であることが可能である。CPU1322は、ネットワークインターフェース1340を使用して、別のコンピュータまたは通信ネットワークに随意に接続することができる。このようなネットワークインターフェースがあれば、CPUは、上述された方法のステップを実施する過程において、ネットワークから情報を受信する、またはネットワークに情報を出力することができると考えられる。更に、本発明の方法の実施形態は、CPU1322上のみで実行されてもよいし、あるいは処理の一部を共有するリモートCPUと連携してインターネットなどのネットワークを通じて実行されてもよい。

【0029】

また、本発明の実施形態は、更に、コンピュータによって実行される様々な動作を実施するためのコンピュータコードを記録されたコンピュータ可読媒体をともなった、コンピュータストレージ製品に関する。媒体およびコンピュータコードは、本発明の目的のために特別に設計および構成されたものであってもよいし、あるいはコンピュータソフトウェアの分野の当業者にとって周知でなおかつ利用可能なものであってもよい。コンピュータ可読媒体の例は、ハードディスク、フロッピィディスク、および磁気テープなどの磁気媒体、CD−ROM、およびホログラフィック装置などの光媒体、フロプティカルディスクなどの光磁気媒体、ならびに特定用途向け集積回路(ASIC)、プログラム可能論理装置(PLD)、ROM装置、およびRAM装置などプログラムコードの格納および実行のために特別に構成されたハードウェアデバイスを含むが、これらに限定されない。コンピュータコードの例は、コンパイラによって生成されるなどのマシンコード、およびインタープリタを使用してコンピュータによって実行される高水準コードを含むファイルを含む。コンピュータ可読媒体は、搬送波に組み込まれたコンピュータデータ信号によって伝送されなおかつプロセッサによって実行可能な一連の命令を表すコンピュータコードでもあることも可能である。

【0030】

エッチングチャンバ内において、フォトレジスト特徴の側壁の上に、側壁層が形成される(ステップ108)。コンフォーマル層の堆積(ステップ304)のためのレシピの一例として、堆積ガス源412は、150sccmのCH3Fのフローと、75sccmのN2のフローと、100sccmのArのフローとを提供する。圧力は、80ミリトールに設定される。基板は、20℃の温度に維持される。第2のRF源448は、27MHzの周波数では400ワットを、2MHzの周波数では0ワットを提供する。

【0031】

図6Aは、基板604と、その上のエッチング層608と、その上のARC層610と、その上のパターン形成されたフォトレジスト層612と、その上の堆積されたコンフォーマル層620とを示した概略断面図である。この実施例では、コンフォーマル層620は、フォトレジスト層612の側壁および頂部と、フォトレジスト特徴614の底部のARC610とを覆っている。その他の実施形態では、コンフォーマル層は、フォトレジスト特徴の底部のARC上に堆積されないかもしれない。好ましくは、堆積されたコンフォーマル層は、単分子層から20nmまでの厚さである。より好ましくは、堆積されたコンフォーマル層は、単分子層から7nmまでの厚さである。最も好ましくは、堆積されたコンフォーマル層は、単分子層から2nmまでの厚さである。

【0032】

好ましくは、コンフォーマル層の堆積は、原子層成長、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを含む。より好ましくは、コンフォーマル層の堆積は、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを含む。好ましくは、基板の温度は、−80℃から120℃の間に維持される。一般に、120℃は、フォトレジストのガラス転移温度である。基板の温度は、フォトレジストのそのガラス転移温度より低く維持することが好ましい。より好ましくは、基板の温度は、−10℃から50℃の間に維持される。最も好ましくは、基板の温度は、20℃に維持される。好ましくは、バイアス電位は、120ボルト未満である。より好ましくは、バイアス電位は、100ボルト未満である。最も好ましくは、バイアス電位は、20ボルトから80ボルトの間である。

【0033】

好ましくは、堆積層は、ポリマー、TEOS、SiO2、Si3N2、SiC、Si、Al2O3、AlN、Cu、HfO2、Mo、Ta、TaN、TaO2、Ti、TiN、TiO2、TiSiN、およびWのうちの少なくとも1つを含む。ポリマーは、フッ化炭化水素材料など炭化水素をベースにした材料である。

【0034】

エッチバック(ステップ308)中は、100sccmのCF4など、ハロゲン(すなわちフッ素、臭素、塩素)を含有するガスが提供される。この実施例では、CF4が、エッチバック中に提供される唯一のガスである。20ミリトールの圧力が、チャンバに提供される。第2のRF源448は、27MHzの周波数で600ワットを、2MHzの周波数で0ワットを提供する。

【0035】

図6Bは、堆積されたコンフォーマル層から側壁624を形成するためにコンフォーマル層がエッチバックされた後の、基板604と、その上のエッチング層608と、その上のARC層610と、その上のパターン形成されたフォトレジスト層612とを示した概略断面図である。この実施例では、フォトレジスト層612の頂部およびフォトレジスト特徴614の底部を覆っているコンフォーマル層の部分が除去され、フォトレジスト特徴の側壁上の層のみが残される。その他の実施形態では、フォトレジストの頂部上のコンフォーマル層の部分は残留し、フォトレジスト特徴の底部のARC上の層のみがエッチバックによって除去される。しかしながら、このような一実施形態では、フォトレジストの頂部の上のコンフォーマル層の一部が除去される。このような一実施形態では、フォトレジスト層の頂部の上に残留しているコンフォーマル層を、エッチングのハードマスクとして使用することができる。

【0036】

この実施例では、コンフォーマル層堆積のステップ(ステップ304)およびエッチバックのステップ(ステップ308)を含む側壁形成のサイクル(ステップ108)が、少なくとも2回実施される。より好ましくは、側壁の形成は、3〜50のサイクルにわたって実施される。最も好ましくは、側壁の形成は、3〜10サイクルにわたって実施される。好ましくは、完成した側壁層は、厚さ100nm未満のように、薄くなおかつエッチングに対して耐性である。より好ましくは、完成した側壁層は、単分子層から50nmまでの厚さである。最も好ましくは、完成した側壁層は、単分子層から2nmまでの厚さである。

【0037】

その他の実施形態では、エッチングサイクルは、追加堆積および/またはエッチバックのステップを更に含むことができる。

【0038】

フォトレジスト特徴の底部上に残留するあらゆる堆積層を除去するために、ブレイクスルーエッチングレシピの一例を使用することができる。このようなブレイクスルーは、エッチバックに使用されるレシピと同じようなレシピを使用することができる。

【0039】

被エッチング層の一例は、SiN、SiC、酸化物、または低k誘電体などの従来のエッチング層であることが可能である。被エッチング層のエッチングには、従来のエッチングレシピを使用することができる。

【0040】

フォトレジストおよび側壁層を剥ぎ取る(ステップ120)には、酸素アッシングを使用することができる。

【0041】

複数のサイクルにわたる側壁層の形成によって、より改良された側壁層プロファイルが提供される。上記の方法を通じて側壁層を提供すると、予想外にラインエッジ粗さが低減されることがわかった。また、側壁層は、より改良された選択性制御を提供する。頂部の層も底部の層もともなわない側壁層を形成することによって、ラインエッジ粗さを低減させられると考えられる。

【0042】

本発明の好ましい一実施形態では、堆積層の堆積、エッチバック、ブレイクスルーエッチ、および側壁層を通した層のエッチングを、図示されたような同一のエッチングチャンバ内で、in−situでなすことができる。

【0043】

以上では、複数の好ましい実施形態の観点から本発明が説明された。しかしながら、本発明の範囲には、変更形態、置換形態、および様々な代替の等価形態が含まれる。また、本発明の方法および装置を実現するものとして、多くの代替の方法がある。したがって、添付の特許請求の範囲は、本発明の真の趣旨および範囲に含まれるものとして、このようなあらゆる変更形態、置換形態、および様々な代替の等価形態を含むものと解釈される。

【特許請求の範囲】

【請求項1】

ラインエッジ粗さを低減させて層内に特徴を形成するための方法であって、

前記層の上に、フォトレジスト層を形成し、

フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、前記フォトレジスト層をパターン形成し、

各サイクルは、前記フォトレジスト層上に層を堆積させる工程を含み、前記堆積層は、単分子層から20nmまでの厚さとなる複数のサイクルを実施することにより、前記フォトレジスト特徴の前記側壁の上に、厚さ100nm未満の側壁層を形成し、

前記フォトレジスト特徴を通して前記層内に特徴をエッチングし、

前記フォトレジスト層および前記側壁層を剥ぎ取る

方法。

【請求項2】

請求項1に記載の方法であって、

前記側壁層を形成する各サイクルは、更に、側壁層を残しつつ、前記フォトレジスト特徴の底部の上に形成された前記堆積層の部分を除去するために前記堆積層をエッチバックする方法。

【請求項3】

請求項1または請求項2に記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、原子層成長、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを、120ボルト未満のバイアス電位で実施することにより行なわれる方法。

【請求項4】

請求項1ないし請求項3のいずれかに記載の方法であって、更に、

前記フォトレジスト層上に前記層を堆積させる間に、前記基板を摂氏−80〜120度の温度に加熱する方法。

【請求項5】

請求項1ないし請求項4のいずれかに記載の方法であって、

前記側壁の上への前記側壁層の堆積は、3〜10サイクルにわたって実施される方法。

【請求項6】

請求項1ないし請求項5のいずれかに記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、ポリマー、TEOS、SiO2、Si3N2、SiC、Si、Al2O3、AlN、Cu、HfO2、Mo、Ta、TaN、TaO2、Ti、TiN、TiO2、TiSiN、およびWのうちの少なくとも1つの層を堆積させることを含む方法。

【請求項7】

請求項1ないし請求項6のいずれかに記載の方法であって、更に、

残留するあらゆる堆積層をエッチングするために、ブレイクスルーエッチングを実施することを備える方法。

【請求項8】

請求項2ないし請求項7のいずれかに記載の方法であって、

前記フォトレジスト層上に前記層を堆積させること、前記エッチバックすること、前記ブレイクスルーすること、および前記特徴をエッチングすることは、単一のプラズマチャンバ内で、in−situで行なわれる方法。

【請求項9】

請求項2ないし請求項8のいずれかに記載の方法であって、

前記エッチバックすることは、更に、前記フォトレジスト層の頂部の上の前記堆積層の部分を除去する方法。

請求項1ないし請求項9のいずれかに記載の方法によって形成される半導体デバイス。

エッジ粗さを低減させてエッチング層内に特徴を形成するための方法であって、

フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、前記エッチング層の上に、パターン形成されたフォトレジスト層を形成し、

複数のサイクルを実施することにより、前記フォトレジスト特徴の前記側壁の上に、厚さ100nm未満の側壁層を形成し、

前記各サイクルは、

単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させる工程と、

側壁層を残しつつ、前記フォトレジスト特徴の底部の上に形成された前記堆積層の部分を除去するために前記堆積層をエッチバックする工程と

を含み、

前記フォトレジスト特徴を通して前記エッチング層内に特徴をエッチングし、

前記フォトレジスト層および前記側壁層を剥ぎ取り、

前記フォトレジスト層上への前記層の堆積と、前記エッチバック、前記特徴のエッチング、および前記剥ぎ取りは、単一のプラズマチャンバ内で、in−situでなされる方法。

【請求項10】

請求項11に記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、原子層成長、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを、120ボルト未満のバイアス電位で実施することにより行なわれる

方法。

【請求項11】

請求項11または請求項12のいずれかに記載の方法であって、更に、

前記フォトレジスト層上に前記層を堆積させる間に、前記基板を80〜120℃の温度に加熱する方法。

【請求項12】

請求項11ないし請求項13のいずれかに記載の方法であって、

前記側壁の上への前記側壁層の堆積は、3〜10サイクルにわたって実施される

方法。

【請求項13】

請求項11ないし請求項14のいずれかに記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、ポリマー、TEOS、SiO2、Si3N2、SiC、Si、Al2O3、AlN、Cu、HfO2、Mo、Ta、TaN、TaO2、Ti、TiN、TiO2、TiSiN、およびWのうちの少なくとも1つの層を堆積させることを含む

方法。

【請求項14】

請求項11ないし請求項15のいずれかに記載の方法によって形成される半導体デバイス。

【請求項1】

ラインエッジ粗さを低減させて層内に特徴を形成するための方法であって、

前記層の上に、フォトレジスト層を形成し、

フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、前記フォトレジスト層をパターン形成し、

各サイクルは、前記フォトレジスト層上に層を堆積させる工程を含み、前記堆積層は、単分子層から20nmまでの厚さとなる複数のサイクルを実施することにより、前記フォトレジスト特徴の前記側壁の上に、厚さ100nm未満の側壁層を形成し、

前記フォトレジスト特徴を通して前記層内に特徴をエッチングし、

前記フォトレジスト層および前記側壁層を剥ぎ取る

方法。

【請求項2】

請求項1に記載の方法であって、

前記側壁層を形成する各サイクルは、更に、側壁層を残しつつ、前記フォトレジスト特徴の底部の上に形成された前記堆積層の部分を除去するために前記堆積層をエッチバックする方法。

【請求項3】

請求項1または請求項2に記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、原子層成長、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを、120ボルト未満のバイアス電位で実施することにより行なわれる方法。

【請求項4】

請求項1ないし請求項3のいずれかに記載の方法であって、更に、

前記フォトレジスト層上に前記層を堆積させる間に、前記基板を摂氏−80〜120度の温度に加熱する方法。

【請求項5】

請求項1ないし請求項4のいずれかに記載の方法であって、

前記側壁の上への前記側壁層の堆積は、3〜10サイクルにわたって実施される方法。

【請求項6】

請求項1ないし請求項5のいずれかに記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、ポリマー、TEOS、SiO2、Si3N2、SiC、Si、Al2O3、AlN、Cu、HfO2、Mo、Ta、TaN、TaO2、Ti、TiN、TiO2、TiSiN、およびWのうちの少なくとも1つの層を堆積させることを含む方法。

【請求項7】

請求項1ないし請求項6のいずれかに記載の方法であって、更に、

残留するあらゆる堆積層をエッチングするために、ブレイクスルーエッチングを実施することを備える方法。

【請求項8】

請求項2ないし請求項7のいずれかに記載の方法であって、

前記フォトレジスト層上に前記層を堆積させること、前記エッチバックすること、前記ブレイクスルーすること、および前記特徴をエッチングすることは、単一のプラズマチャンバ内で、in−situで行なわれる方法。

【請求項9】

請求項2ないし請求項8のいずれかに記載の方法であって、

前記エッチバックすることは、更に、前記フォトレジスト層の頂部の上の前記堆積層の部分を除去する方法。

請求項1ないし請求項9のいずれかに記載の方法によって形成される半導体デバイス。

エッジ粗さを低減させてエッチング層内に特徴を形成するための方法であって、

フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、前記エッチング層の上に、パターン形成されたフォトレジスト層を形成し、

複数のサイクルを実施することにより、前記フォトレジスト特徴の前記側壁の上に、厚さ100nm未満の側壁層を形成し、

前記各サイクルは、

単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させる工程と、

側壁層を残しつつ、前記フォトレジスト特徴の底部の上に形成された前記堆積層の部分を除去するために前記堆積層をエッチバックする工程と

を含み、

前記フォトレジスト特徴を通して前記エッチング層内に特徴をエッチングし、

前記フォトレジスト層および前記側壁層を剥ぎ取り、

前記フォトレジスト層上への前記層の堆積と、前記エッチバック、前記特徴のエッチング、および前記剥ぎ取りは、単一のプラズマチャンバ内で、in−situでなされる方法。

【請求項10】

請求項11に記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、原子層成長、化学気相成長、スパッタリング蒸着、プラズマ蒸着、およびプラズマ化学気相成長のうちの少なくとも1つを、120ボルト未満のバイアス電位で実施することにより行なわれる

方法。

【請求項11】

請求項11または請求項12のいずれかに記載の方法であって、更に、

前記フォトレジスト層上に前記層を堆積させる間に、前記基板を80〜120℃の温度に加熱する方法。

【請求項12】

請求項11ないし請求項13のいずれかに記載の方法であって、

前記側壁の上への前記側壁層の堆積は、3〜10サイクルにわたって実施される

方法。

【請求項13】

請求項11ないし請求項14のいずれかに記載の方法であって、

前記フォトレジスト層上への前記層の堆積は、ポリマー、TEOS、SiO2、Si3N2、SiC、Si、Al2O3、AlN、Cu、HfO2、Mo、Ta、TaN、TaO2、Ti、TiN、TiO2、TiSiN、およびWのうちの少なくとも1つの層を堆積させることを含む

方法。

【請求項14】

請求項11ないし請求項15のいずれかに記載の方法によって形成される半導体デバイス。

【図1】

【図2A】

【図2B】

【図2C】

【図2D】

【図3】

【図4】

【図5A】

【図5B】

【図6A】

【図6B】

【図2A】

【図2B】

【図2C】

【図2D】

【図3】

【図4】

【図5A】

【図5B】

【図6A】

【図6B】

【公開番号】特開2013−110437(P2013−110437A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【外国語出願】

【出願番号】特願2013−23716(P2013−23716)

【出願日】平成25年2月8日(2013.2.8)

【分割の表示】特願2008−526963(P2008−526963)の分割

【原出願日】平成18年8月1日(2006.8.1)

【出願人】(592010081)ラム リサーチ コーポレーション (467)

【氏名又は名称原語表記】LAM RESEARCH CORPORATION

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2013−23716(P2013−23716)

【出願日】平成25年2月8日(2013.2.8)

【分割の表示】特願2008−526963(P2008−526963)の分割

【原出願日】平成18年8月1日(2006.8.1)

【出願人】(592010081)ラム リサーチ コーポレーション (467)

【氏名又は名称原語表記】LAM RESEARCH CORPORATION

【Fターム(参考)】

[ Back to top ]