低電力モード中にキャッシュされた情報を保存する技術

【課題】コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関するプロセッサ、システム、および、方法を提供する。

【解決手段】低電力モード中にキャッシュされた情報を保持するための技術である。プロセッサ100のローカル・キャッシュ107,113に格納された情報は、プロセッサが低電力モードに置かれる前に共有キャッシュ115に保存されるので、他のプロセッサは、低電力モードのプロセッサを、そのローカル・キャッシュへのアクセスを提供するように低電力モードから復帰させる代わりに、共有キャッシュからの情報にアクセスする。

【解決手段】低電力モード中にキャッシュされた情報を保持するための技術である。プロセッサ100のローカル・キャッシュ107,113に格納された情報は、プロセッサが低電力モードに置かれる前に共有キャッシュ115に保存されるので、他のプロセッサは、低電力モードのプロセッサを、そのローカル・キャッシュへのアクセスを提供するように低電力モードから復帰させる代わりに、共有キャッシュからの情報にアクセスする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施例は、一般に情報処理の分野に関し、より詳しくは、コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関する。

【背景技術】

【0002】

いくつかのマイクロプロセッサおよび/またはプロセッサ・コア(ここでは一般に「プロセッサ」と称する)は、レベル1(「L1」)キャッシュのような1次キャッシュ・メモリ、または他のメモリ構造を含み(または有し)、プロセッサは、それらから、比較的迅速に、プロセッサまたはコンピューティング・システム内の他のメモリ構造に関連する、頻繁にアクセスされるデータまたは命令のような情報を検索する。加えて、いくつかのプロセッサは、レベル2(「L2」)キャッシュ・メモリのような2次キャッシュ・メモリ、または他のメモリ構造を含み(または有し)、プロセッサは、それらから、1次キャッシュ・メモリから検索する場合ほど迅速ではないが、ダイナミック・ランダム・アクセス・メモリ(DRAM)、ハードドライブ・メモリのようなシステム・メモリから検索するよりは迅速に、あまり頻繁にアクセスされないデータまたは命令のような情報を検索する。

【0003】

いくつかのコンピュータ・システムはプロセッサを含み、各プロセッサは、それが対応するプロセッサによって主に使用される情報を格納するために、L1キャッシュのようなローカル・キャッシュ・メモリへのアクセスを含む(または有する)。さらに、いくつかのコンピュータ・システムは、L2キャッシュのような共有キャッシュ・メモリを含み、それは2以上のプロセッサによって使用される。共有キャッシュ・メモリを有するコンピュータ・システムでは、共有キャッシュ・メモリは、ローカル・キャッシュ・メモリの各々に格納された情報の全部またはいくらかの部分を格納するので、複数のローカル・キャッシュ・メモリは、共有キャッシュ・メモリ内に格納された頻繁に使用される情報のサブセットを格納する。ローカル・キャッシュ・メモリ内に格納された情報は、共有キャッシュ・メモリ内の対応する情報よりも頻繁に更新され、したがって、コンピュータ・システムは、1またはそれ以上のローカル・キャッシュ・メモリ内に格納された情報と同一の情報を共有キャッシュ・メモリ内で保持するために、キャッシュ・コヒーレンシ・スキームを実行する。

【0004】

特定のプロセッサが使用されていないとき、あるいは、プロセッサまたはコンピュータ・システムの温度がモニタされ、閾値温度を超過することを防止するアルゴリズムのような他のアルゴリズムに応答しているとき、いくつかのコンピュータ・システムは、システム内の1またはそれ以上のプロセッサへのクロック周波数および/または電圧を低減することによって、システム内のプロセッサを低電力モードに置くための電力管理技術を用いる。低電力モードに置かれたプロセッサは、例えばローカル・キャッシュへの電力を維持することによって、低電力モードにある間もそれらの対応するローカル・キャッシュ・メモリ内に格納された情報を保持するので、その情報は、プロセッサが低電力モードから復帰したときに利用可能になる。

【0005】

低電力モード中にキャッシュされた情報を保持するという先行技術の欠点の1つは、低電力モードにあるプロセッサのキャッシュにアクセスするプロセッサは、例えば「スヌープ」サイクルによって、低電力モードにあるプロセッサが低電力モードから復帰し、かつ、他のプロセッサによるアクセスに応答できるようになるまで待たなければならないことである。低電力モード・プロセッサのキャッシュにアクセスした時と、要求されたデータが検索されるか、または低電力モード・プロセッサのキャッシュに存在しないと決定された時との間の遅延は、対応するコンピュータ・システムの性能を著しく低下させる。このような問題は、プロセッサの数が増加するにつれて、低電力モードにあるプロセッサの数、およびこれらのプロセッサへのアクセス数も増加するので、より悪化する。さらに、コンピュータ・システムは、特に、要求された情報が低電力モードにあるプロセッサのローカル・キャッシュ内に存在しないと決定された場合に、不必要な電力を引き込む。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】国際公開第2006/028652号

【図面の簡単な説明】

【0007】

本発明の実施例は、制限目的ではなく例示目的のために示され、また、添付図面の図中にある類似の要素は同様の参照番号で示される。

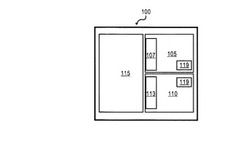

【図1】本発明の少なくとも一実施例が使用された、マルチコア・マイクロプロセッサのブロック図を示す。

【図2】本発明の少なくとも一実施例が使用された、共有バス・コンピュータ・システムのブロック図を示す。

【図3】本発明の少なくとも一実施例が使用された、ポイント・ツー・ポイント相互接続コンピュータ・システムのブロック図を示す。

【図4】本発明の少なくとも一実施例が使用された、リング・ベースド・マルチコア・マイクロプロセッサのブロック図を示す。

【図5】本発明の一実施例に従って、低電力モード中にキャッシュされた情報を保持するために用いられる動作のフローチャートである。

【発明を実施するための形態】

【0008】

ここでは、コンピュータ・システム内の低電力モード中にキャッシュされた情報を保持するための少なくとも1つの技術が示される。以下の記述では、本発明の実施例について完全な理解を提供するために、説明目的のための多くの特定の詳細事項が述べられる。しかしながら、当業者にとって、これらの特定の詳細事項がなくても本発明の実施例を実行することができることは明白であろう。

【0009】

一般に、ここに記述された実施例は、複数のマイクロプロセッサ、複数のプロセッサ・コア、複数のプロセッサ・コアを有する単一のマイクロプロセッサ、または、各々が複数のプロセッサ・コアを有する複数のプロセッサ、を含む任意の数のマルチプロセッサ・システムに適用することができる。

【0010】

簡略化するために、マイクロプロセッサおよびマイクロプロセッサ・コアは、ここでは「プロセッサ」と総称する。さらに、1次キャッシュ(すなわち、それらは、プロセッサが最も頻繁に用いる情報を格納するために使用される)は、ここでは「ローカル・キャッシュ」と総称する。一方、2次キャッシュ(すなわち、それらは、L2キャッシュ、L3キャッシュ等のように、ローカル・キャッシュよりも頻繁に用いない情報を格納するために使用される)は、2またはそれ以上のプロセッサの1次キャッシュ内に格納された情報の少なくともいくらかを格納するために使用され、ここでは「共有キャッシュ」と総称される。最後に、プロセッサが動作する電圧および/または周波数状態は、1またはそれ以上のプロセッサのクロックが、アイドル、停止、ホールト、または最大動作周波数以下に低減される状態、および/または、1またはそれ以上のプロセッサの電圧が、最大動作電圧以下に低減される状態を含み、ここでは「電力モード」と総称される。

【0011】

いくつかの実施例では、プロセッサは、低電力モードに置かれる前に、そのローカル・キャッシュ内に格納された情報を共有キャッシュ内の対応する位置に保存し、その結果、さもなければ低電力モードのプロセッサのローカル・キャッシュからの情報に対してアクセスを試みるであろう他のプロセッサは、その代りに共有キャッシュから必要な情報を検索し、そして、低電力モードにあるプロセッサは、それが他に必要とされるまで低電力モードのままである。都合の良いことに、少なくとも一実施例では、コンピュータ・システム内の性能を改善することができる。なぜならば、他のプロセッサによるローカル・キャッシュへのアクセスを提供するために、低電力状態にあるプロセッサが低電力状態から復帰するのを待つシステムの代わりに、情報は、低電力状態に入る前に低電力モード・プロセッサが情報を保存した共有キャッシュから検索されるからである。いくつかの実施例では、共有キャッシュへのアクセスは、低電力モードのプロセッサのローカル・キャッシュへのアクセスよりも迅速に提供される。さらに、低電力モードのプロセッサは、そのローカル・キャッシュへのアクセスを提供するために低電力モードから復帰する必要がないので、少なくとも一実施例では、その実施例を使用するシステム内の電力の保存に役立つ。

【0012】

一実施例では、低電力モードに置かれるプロセッサは、最初に、キャッシュ・フラッシュ(一括消去)動作、キャッシュ無効動作、ライトバック動作、または、プロセッサのローカル・キャッシュ内に格納された情報を共有キャッシュに保存させるような他の動作を実行する。一実施例では、低電力モードは、プロセッサを低電力モードに置くために、プロセッサへの1またはそれ以上のクロックをオフにすることを含む。他の実施例では、低電力モードは、プロセッサ、ローカル・キャッシュ、またはその両方に電力を与えるために使用される1またはそれ以上の動作電圧の低減または取り除くことを含む。さらに他の実施例では、低電力モードは、プロセッサへの周波数および電圧の両方を、低減または完全に不能にしてもよい。

【0013】

図1は、本発明の少なくとも一実施例を用いたマルチコア・マイクロプロセッサを示す。特に、図1は、少なくとも2つのプロセッサ・コア105,110を有するマイクロプロセッサ100を示し、プロセッサ・コア105はローカル・キャッシュ107と、プロセッサ・コア110はローカル・キャッシュ113と、それぞれ関連している。さらに、図1には、ローカル・キャッシュ107,113の各々に格納された情報の少なくともいくつかのバージョンを格納する共有キャッシュ・メモリ115が示される。いくつかの実施例では、マイクロプロセッサ100は、さらに、図1に示されない他の論理、例えば、集積メモリ・コントローラ、集積グラフィック・コントローラを含むほか、I/O制御のようなコンピュータ・システム内の他の機能を実行するための他の論理も含む。一実施例では、マルチプロセッサ・システム内の各マイクロプロセッサ、またはマルチコアプロセッサ内の各プロセッサ・コアは、いずれの所定の時間においてもプロセッサ/コアの電力状態に依存してローカル・キャッシュまたは共有キャッシュのいずれかへのアクセスを指示するための論理119を含む(または、それに関連している)。論理は、コンピュータ・システムの動作中のいずれの時間においてもコアまたはプロセッサの電力状態を格納するために、不揮発性プログラマブル・メモリのようなメモリを含む(または、それに関連している)。そのような実施例では、プロセッサまたはコアへのアクセスは、ターゲット・プロセッサまたはコアの電力状態を考慮せずに行なわれるので、スヌープのような同一タイプのアクセスが各プロセッサまたはコアへ送られ、そして、ターゲット・プロセッサまたはコアは、プロセッサまたはコアの電力状態に依存して、スヌープをそのローカル・キャッシュへ提供するか、あるいは、スヌープを共有キャッシュへのアクセス(スヌープまたは他の動作)へ転送する。

【0014】

一実施例では、図1に示されたプロセッサ・コアの1つは、低電力モードに入る前に、そのローカル・キャッシュに格納された情報の最新バージョンを共有キャッシュに格納する。コアの1つが低電力モードにあるとき(「低電力モード・コア」)、低電力モード・コアは、低電力モードに入る前に、そのローカル・キャッシュから共有キャッシュへ最新情報を保存しているので、他のコアは、共有キャッシュへアクセスすることにより、低電力モード・コアのローカル・キャッシュ内に格納された情報の最新バージョンを獲得することができる。一実施例では、低電力モード・コアは、キャッシュ・フラッシュ動作を実行し、そこでは、ローカル・キャッシュされた情報の一部または全部が無効にされるか、あるいは、低電力モード・コアが低電力モードに入る前に、低電力モード・コアのローカル・キャッシュ内に格納された情報の一部または全部が共有キャッシュに保存される。他の実施例では、コアの命令セット・アーキテクチャに依存して、他の動作が、低電力モード・コアのローカル・キャッシュの情報の一部または全部を共有キャッシュへ保存するために実行される。

【0015】

一実施例では、プロセッサは、いつでも、1またはそれ以上の低電力モードを含む、多くの異なる電力状態の1つにある。例えば、プロセッサは、最大許容量の電力が消費されるような完全に電力供給されたコンポーネント状態(「C0」)、C0状態よりも低い許容電力消費量によって定義される低減電力コンポーネント状態(「C1」)、あるいは、他の低電力状態(例えばC3、C6など)にあり、それぞれが、連続的により低い許容電力消費によって定義される。さらに、1またはそれ以上のプロセッサのクロックあるいは電力供給は、各状態に関連する許容電力消費を遂行するために調整される。

【0016】

例えば、一実施例では、完全に電力供給されたC0状態は、プロセッサの性能を最大限にするために、周波数の範囲内で1またはそれ以上のプロセッサのクロックを操作することによって、および、電圧の範囲内でプロセッサへの1またはそれ以上の電力供給を操作することによって達成される。そのような電力状態は、例えば、プロセッサ上で実行されるプログラムによって、大きな実行要求がプロセッサに課されるときに有用である。低減電力状態C1は、電圧の範囲内でプロセッサへの1またはそれ以上の電力供給を維持しつつ、1またはそれ以上のプロセッサのクロックを停止または低減することによって、プロセッサをアイドル、ホールト、または他の低実行状態状に置くことにより遂行される。そのような低減電力状態では、プロセッサは、C0状態よりも少ない電力しか引き込まないが、例えばスヌープ動作と比較して、他のプロセッサからローカル・キャッシュへのアクセスは、なおも提供することができる。

【0017】

一実施例では、図1に示されたコアの1つのようなプロセッサは、プロセッサへの1またはそれ以上のクロックを停止または低減すること、および、プロセッサに供給される1またはそれ以上の電源の電圧を除去または低減することによって、C0またはC1よりも低電力状態に置かれるので、その結果、プロセッサのローカル・キャッシュ内に格納された情報は保持されないであろう。例えば、図1において、コアの1つが低電力コア・コンポーネント状態(「CC3」状態)に置かれ、そこでは、コアへの全てのクロックがホールトされ、さらに、全ての電源電圧が除去されるか、あるいは非活動レベルまで低減される。一実施例によれば、CC3状態では、コアは最小量の電力を引き込むか、恐らく電力を引き込まない。したがって、図1に示されたプロセッサまたはコアがCC3状態に置かれる前に、コアのローカル・キャッシュ内に格納された修正された情報の少なくとも一部が、共有キャッシュ内の対応する位置に格納される。一実施例では、コアがCC3状態に入る前に、修正された情報のみ(すなわち、共有キャッシュ内に格納された同一情報のバージョンよりも最新の、ローカル・キャッシュ内の情報のバージョン)が共有キャッシュ内に格納される。他の実施例では、ローカル・キャッシュの全コンテンツは、共有キャッシュ内で利用可能なバージョンから修正されたかどうかにかかわらず、コアがCC3状態に入る前に共有キャッシュに格納される。

【0018】

都合の良いことに、共有キャッシュは、CC3状態に置かれるコアのローカル・キャッシュ内に格納された少なくとも修正された情報を含んでいるので、一実施例では、図1に示された他のいずれのプロセッサまたはコアも、別な状態ではアクセスされるコアが低減されたコア・コンポーネント状態(つまり「CC1」)にあるときのようにCC3にあるコアのキャッシュへアクセスすることを試みるであろうが、それに代えて、CC3コアを低電力モードに残した状態で、共有キャッシュに直接に要求された情報にアクセスし、それによって電力を節約することができる。さらに、一実施例では、CC3のコアは、他のコアまたはプロセッサからそのローカル・キャッシュへのアクセスにサービスするために低電力状態から復帰していないので、例えば、スヌープ動作と比べて、そのアクセスしているプロセッサまたはコアは、そのアクセスされたコアが要求にサービスするためにその低電力状態から復帰するのを待たなければならない場合ほど、その要求する情報のために長く待つ必要がない。様々な実施例における上記の技術は、任意の数のプロセッサまたはプロセッサ・コアを有するシステムに適用することができる。

【0019】

図2は、例えば、本発明の一実施例が使用されたフロントサイド・バス(FSB)コンピュータ・システムを示す。いずれのプロセッサ201,205,210,215も、ローカル・レベル1(L1)キャッシュ・メモリ220,225,230,235,240,245,250,255のいずれかからの情報にアクセスすることができるが、これらは、プロセッサ・コア223,227,233,237,243,247,253,257の1つの中にあるか、あるいはそれらと関連している。さらに、プロセッサ201,205,210,215のいずれかは、共有レベル2(L2)キャッシュ203,207,213,217のいずれか1つからの情報、あるいは、チップセット265を介してシステム・メモリ260からの情報にアクセスすることができる。図2のプロセッサの1またはそれ以上は、いずれの時間においてもプロセッサ/コアの電力状態に依存して、ローカル・キャッシュまたは共有キャッシュのいずれかへのアクセスを指示するための論理219を含む(または、それに関連している)。論理は、コンピュータ・システムの動作中、コアまたはプロセッサの電力状態をいつでも格納するための不揮発性プログラマブル・メモリのようなメモリを含む(または、それに関係している)。

【0020】

図2に示された例において、プロセッサ201内では、両方のコアは、アクティブ・コア・コンポーネント状態(「CC0」状態)であるのに対して、プロセッサ205内では、両方のコアは、低減電力状態(「CC1」状態)であり、その結果、各コアはスヌープをサービスすることができ、あるいはアクティブ・コア223,227から同様の動作を提供することができる。プロセッサ210,215のそれぞれは、プロセッサ201,205のコアよりも低電力モード(「CC3」状態)にあるコアを有し、その結果、ローカル・キャッシュ240,245,250,255は、もはや利用することができない。一実施例では、アクティブ・コア223または227がプロセッサ210,215のコアのローカル・キャッシュ内に格納された情報にアクセスする場合、それらは、それぞれプロセッサ210,215の共有キャッシュから、情報を獲得しなければならない。なぜなら、一実施例において、プロセッサのコア223,227は、CC3状態に入る前に、それらのローカル・キャッシュ内に格納された情報の少なくとも修正されたバージョンをそれらの個々の共有キャッシュ213,217へ格納したからである。プロセッサ201のコアから要求された情報が、共有キャッシュ213,217内で利用できず、またローカル・キャッシュ230,235でも利用できない場合、次に、プロセッサ201のコアは、チップセット265を介して、あるいは図2に示されないハード・ドライブまたは他のメモリ・ソースを介して、システム・メモリ260からの情報にアクセスせざるを得ないであろう。

【0021】

いくつかの実施例では、図2の各プロセッサのコアは、図2に示されたように同一の電力モードではなく、互いに異なる電力モードにある。一実施例では、論理は、各プロセッサまたは各コアに含まれ、アクセスされているコアが、CC3状態にあるのか、または他の状態にあるのかを、スヌープまたは同様の動作で表示し、その結果、要求しているコアは、アクセスされているコアの適切なメモリ構造(ローカル・キャッシュまたは共有キャッシュ)をアドレスするために適切なトランザクションを送出する。いくつかの実施例では、コアの電力状態の表示は、コンピュータ・システムのBIOSによってアクセス可能なテーブルのようなソフトウェア・プログラムに記録され、追跡される。例えば、一実施例では、コアまたはプロセッサが電力状態を変更する場合は常に、その変更が論理またはメモリに格納されたテーブルに記録され、それをシステムのBIOSが読み取り、他のプロセッサまたはコアのローカル・キャッシュへのアクセスを試みるあらゆるコアまたはプロセッサに通知することができる。他のプロセッサまたはコアの電力モードについて、アクセスしているプロセッサまたはコアに通知することによって、それは、アクセスされる対応するローカル・キャッシュがCC3のような低減電力状態であるとき、共有キャッシュのような適切なメモリ構造にアクセスすることができる。他の実施例では、各プロセッサまたは各コアの電力モード情報は、BIOSのほかにハードウェア論理または他のソフトウェアを含む他の手段によって、修正され記録されてもよい。

【0022】

いくつかの実施例では、アクセスされているプロセッサまたはコアは、アクセスされたプロセッサ/コアの応答を制御するための論理を含む。例えば、一実施例において、ここで記述した技術を使用するためのコンピュータ・システム内の各プロセッサ(またはコア)は、あらゆる指定の時間でプロセッサの電力状態を格納するための、不揮発性プログラマブル・メモリのようなストレージを含み、そして、関連する論理は、他のプロセッサ/コアからのスヌープ要求または他の同様の動作にどのように応答すべきかを決定する。一実施例では、ストレージおよび論理は、例えば、CC3状態のプロセッサまたはコアへのアクセスを、プロセッサまたはコアのローカル・キャッシュから、共有キャッシュまたは他のL2キャッシュへ転送するために使用される。ところが、アクセスされているプロセッサまたはコアが、CC0またはCC1状態(すなわち、CC3よりも高い電力状態)のような他の状態である場合は、アクセスされたプロセッサまたはコア内の論理は、そのローカル・キャッシュをスヌープあるいはアクセスすることを許可するであろう。そのような実施例では、アクセスしているプロセッサ・コアは、プロセッサの電力状態を認識している必要はないが、他のプロセッサのローカル・キャッシュへスヌープのようなアクセスを単に送出し、そして、アクセスされたプロセッサ(またはコア)は、その時の電力状態に基づいて、どこへアクセスすべきかを指示する。

【0023】

図2に示されたFSBコンピュータ・システムに加えて、ポイント・ツー・ポイント(P2P)相互接続システムおよびリング相互接続システムを含む他のシステム構成が、本発明の様々な実施例と共に使用される。図3のP2Pシステムは、例えばいくつかのプロセッサを含んでもよいが、ここではプロセッサ370,380の2つのみが例示される。プロセッサ370,380は、メモリ32,34に接続するためのローカル・メモリ・コントローラ・ハブ(MCH)372,382をそれぞれ含む。プロセッサ370,380は、ポイント・ツー・ポイント(PtP)インターフェイス回路378,388を使用して、PtPインターフェイス350を介してデータを交換する。プロセッサ370,380は、ポイント・ツー・ポイント・インターフェイス回路376,394,386,398をそれぞれ使用して、個別のPtPインターフェイス352,354を介してチップセット390とデータを交換する。チップセット390は、さらに、高性能グラフィック・インターフェイス339を介して高性能グラフィック回路338とデータを交換する。本発明の実施例は、任意の数の処理コアを有するあらゆるプロセッサ内、または図3の各PtPバス・エージェント内に配置される。一実施例では、あらゆるプロセッサ・コアは、ローカル・キャッシュ・メモリ(図示せず)に含まれるか、あるいはそれと関連する。さらに、共有キャッシュ(図示せず)は、両方のプロセッサの外部のプロセッサの一方に含まれ、それもまたp2p相互接続を介してプロセッサに接続されるので、一方または両方のプロセッサのローカル・キャッシュ情報は、プロセッサが低電力モードに置かれた場合には、共有キャッシュに格納される。図3のプロセッサまたはコアの1つまたはそれ以上は、あらゆる所定の時間でプロセッサ/コアの電力状態に依存して、ローカル・キャッシュまたは共有キャッシュのいずれかへのアクセスを指示するための論理319含む(または、それらと関連している)。論理は、コンピュータ・システムの動作中にコアまたはプロセッサの電力状態をいつでも格納するための、不揮発性プログラマブル・メモリのようなメモリを含む(または、それらと関連している)。

【0024】

図4は、少なくとも一実施例を使用する、リング構成で組織されたコンピュータ・システムまたはプロセッサを示す。図1のリング・システムは、同心円のリング相互接続に沿って組織された、8つのプロセッサまたはプロセッサ・コア401,405,410,415,420,425,430,435を含み、各プロセッサまたはコアは、対応するローカル・キャッシュを有し、そのローカル・キャッシュは、リング相互接続に沿って他のコアによってアクセスされる。図4のシステムまたはプロセッサは、さらに、最終レベルの共有キャッシュ(LLC)440を含み、それが、ローカル・キャッシュ403,407,413,417,423,427,433,437に格納された情報の全てまたはいくつかのバージョンを格納する。一実施例では、図4のプロセッサまたはコアの1つが電力モードにある場合、もはやプロセッサまたはコアのローカル・キャッシュから情報にアクセスすることができず、したがって、低電力モード・プロセッサ/コアのローカル・キャッシュに格納された情報へのアクセスを試みる他のあらゆるプロセッサまたはコアは、その代りに、LLCからこの情報にアクセスすることを試みなければならない。一実施例では、情報がLLC内で利用できない場合、アクセスするプロセッサまたはコアは、メモリ・コントローラ445を介してシステム・メモリ・ソース(図示せず)からデータにアクセスする必要がある。図4のプロセッサの1つまたはそれ以上は、あらゆる所定の時間でプロセッサ/コアの電力状態に依存して、ローカル・キャッシュあるいは共有キャッシュのいずれかへのアクセスを指示するための論理419を含む(または、これらと関連している)。論理は、コンピュータ・システムの動作中に、コアまたはプロセッサの電力状態をいつでも格納するための、不揮発性プログラマブル・メモリのようなメモリを含む(または、これらと関連している)。

【0025】

図5は、本実施例が使用されるプロセッサまたはシステムの構成にかかわらず、本発明の少なくとも一実施例と共に使用される動作のフローチャートを示す。動作501で、例えば、スヌープ動作または他のキャッシュ・アクセス動作等によって、プロセッサへのアクセスが行なわれる。動作505で、アクセスされたプロセッサがCC3状態のような低電力モードである場合、動作510で、プロセッサの共有キャッシュがアクセスされる。アクセスは、使用されるプロトコルに依存して、共有キャッシュへのスヌープかもしれないし、あるいは、そのスヌープは、共有キャッシュにアクセスするための他の動作に変換されるかもしれない。動作515で、要求された情報が共有キャッシュ内にない場合、動作520で、システム・メモリへのアクセスが行なわれ、さらに、動作530で、情報がシステム・メモリから戻され、そうでない場合は、動作525で、情報が共有キャッシュから戻される。

【0026】

動作505で、プロセッサがCC3のような低電力モードでなかった場合、動作535で、プロセッサのローカル・キャッシュがアクセスされる。動作540で、情報がローカル・キャッシュ内で利用可能な場合、次に、動作545で、情報がローカル・キャッシュから戻される。そうでない場合は、上述のように、共有キャッシュまたはシステム・メモリのいずれかから情報にアクセスするために、そのプロセスは動作510に返る。一実施例では、アクセスするプロセッサは、それらが置かれている電力状態にかかわらずシステム内の他のプロセッサへスヌープを送り、アクセスされたプロセッサは、アクセスされたプロセッサの電力状態に基づいて、ローカル・キャッシュまたは共有キャッシュへアクセスを送るべきかどうかを決定する。例えば、アクセスされたときにアクセスされたプロセッサがCC3状態である場合は、他のプロセッサからのスヌープ動作は、スヌープまたは他の動作のいずれかとしてアクセスされたプロセッサの共有キャッシュに転送されるであろう。そうでない場合は、アクセスされたプロセッサが、ローカル・キャッシュがスヌープされることを可能にする電力状態である場合は、スヌープ動作は、アクセスされたプロセッサのローカル・キャッシュへアクセスする結果になる。他の実施例では、テーブルは、例えばBIOSを通して保持され、アクセスするプロセッサは、テーブル内に示された電力状態に基づいて、そのプロセッサのローカル・キャッシュがアクセスされるべきであるか、あるいは、その共有キャッシュがアクセスされるべきであるかを決定するために、他のプロセッサへのアクセスに先立って参照する。他の実施例では、アクセスが、アクセスされたプロセッサの電力状態に基づいて指示されるべき場合を管理するための他の技術が使用される。

【0027】

ここに記述された実施例は、多くの技術を用いて、多くの方法で実行することができる。例えば、少なくとも一実施例は、CMOS論理で実行されるが、他の実施例は、ソフトウェアで実行される。さらに、他の実施例は、ハードウェア論理およびソフトウェアの組合せによって実行される。

【0028】

一実施例では、ルーチンを促進するために使用されるソフトウェアは、機械読取り可能な媒体上に埋め込むことができる。機械読取り可能な媒体は、機械(例えば、コンピュータ、ネットワーク装置、携帯情報端末、製造ツール、1またはそれ以上のプロセッサのセットを具備する任意の装置等)によってアクセス可能な形式で情報を提供(すなわち、格納および/または転送)する、あらゆるメカニズムを含む。例えば、機械読取り可能な媒体は、記録可能/記録不可能な媒体(例えば、ファームウェアを含むリード・オンリ・メモリ(ROM)、ランダム・アクセス・メモリ(RAM)、磁気ディスク記憶媒体、光記憶媒体、フラッシュ・メモリ装置など)を含むほか、電気的、光学的、音響的、または他の形式の伝播信号(例えば、搬送波、赤外線信号、デジタル信号など)も同様に含む。

【0029】

少なくとも一実施例の1またはそれ以上の側面が、プロセッサ内の様々な論理を表わす機械可読媒体上に格納された代表的なデータによって実行され、それが機械によって読み取られたとき、機械にここに記述された技術を実行させるための論理を作り上げる。このような表現は、「IPコア」として知られ、有形の、機械読取り可能な媒体(「テープ」)に格納され、そして、実際に論理またはプロセッサを作成する組立機械内でロードするために様々な顧客または生産設備に提供される。

【0030】

以上、マイクロアーキテクチャのメモリ領域アクセスを指示するための方法および機器が記述された。上記の記述は、例示であり、これらに限定する意図ではないと理解すべきである。上記の記述を読みかつ理解することによって、当業者には他の多くの実施例が明らかになるであろう。したがって、本発明の範囲は、添付の請求項に付与されるべき全均等範囲に加えて、かかる請求項に関して決定されるべきである。

【符号の説明】

【0031】

100 マイクロプロセッサ

105,110 プロセッサ・コア

107,113 ローカル・キャッシュ

119 論理

201,205,210,215 プロセッサ

203,207,213,217 共有レベル2(L2)キャッシュ

219 論理

220,225,230,235,240,245,250,255 ローカル・レベル1(L1)キャッシュ・メモリ

223,227,233,237,243,247,253,257 プロセッサ・コア

260 システム・メモリ

265 チップセット

32,34 メモリ

319 論理

338 高性能グラフィック回路

339 高性能グラフィック・インターフェイス

350,352,354 PtPインターフェイス

370,380 プロセッサ

372,382 ローカル・メモリ・コントローラ・ハブ(MCH)

376,378,386,388,394,398 ポイント・ツー・ポイント(PtP)インターフェイス回路

390 チップセット

401,405,410,415,420,425,430,435 プロセッサまたはプロセッサ・コア

403,407,413,417,423,427,433,437 ローカル・キャッシュ

419 論理

440 共有キャッシュ(LLC)

【技術分野】

【0001】

本発明の実施例は、一般に情報処理の分野に関し、より詳しくは、コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関する。

【背景技術】

【0002】

いくつかのマイクロプロセッサおよび/またはプロセッサ・コア(ここでは一般に「プロセッサ」と称する)は、レベル1(「L1」)キャッシュのような1次キャッシュ・メモリ、または他のメモリ構造を含み(または有し)、プロセッサは、それらから、比較的迅速に、プロセッサまたはコンピューティング・システム内の他のメモリ構造に関連する、頻繁にアクセスされるデータまたは命令のような情報を検索する。加えて、いくつかのプロセッサは、レベル2(「L2」)キャッシュ・メモリのような2次キャッシュ・メモリ、または他のメモリ構造を含み(または有し)、プロセッサは、それらから、1次キャッシュ・メモリから検索する場合ほど迅速ではないが、ダイナミック・ランダム・アクセス・メモリ(DRAM)、ハードドライブ・メモリのようなシステム・メモリから検索するよりは迅速に、あまり頻繁にアクセスされないデータまたは命令のような情報を検索する。

【0003】

いくつかのコンピュータ・システムはプロセッサを含み、各プロセッサは、それが対応するプロセッサによって主に使用される情報を格納するために、L1キャッシュのようなローカル・キャッシュ・メモリへのアクセスを含む(または有する)。さらに、いくつかのコンピュータ・システムは、L2キャッシュのような共有キャッシュ・メモリを含み、それは2以上のプロセッサによって使用される。共有キャッシュ・メモリを有するコンピュータ・システムでは、共有キャッシュ・メモリは、ローカル・キャッシュ・メモリの各々に格納された情報の全部またはいくらかの部分を格納するので、複数のローカル・キャッシュ・メモリは、共有キャッシュ・メモリ内に格納された頻繁に使用される情報のサブセットを格納する。ローカル・キャッシュ・メモリ内に格納された情報は、共有キャッシュ・メモリ内の対応する情報よりも頻繁に更新され、したがって、コンピュータ・システムは、1またはそれ以上のローカル・キャッシュ・メモリ内に格納された情報と同一の情報を共有キャッシュ・メモリ内で保持するために、キャッシュ・コヒーレンシ・スキームを実行する。

【0004】

特定のプロセッサが使用されていないとき、あるいは、プロセッサまたはコンピュータ・システムの温度がモニタされ、閾値温度を超過することを防止するアルゴリズムのような他のアルゴリズムに応答しているとき、いくつかのコンピュータ・システムは、システム内の1またはそれ以上のプロセッサへのクロック周波数および/または電圧を低減することによって、システム内のプロセッサを低電力モードに置くための電力管理技術を用いる。低電力モードに置かれたプロセッサは、例えばローカル・キャッシュへの電力を維持することによって、低電力モードにある間もそれらの対応するローカル・キャッシュ・メモリ内に格納された情報を保持するので、その情報は、プロセッサが低電力モードから復帰したときに利用可能になる。

【0005】

低電力モード中にキャッシュされた情報を保持するという先行技術の欠点の1つは、低電力モードにあるプロセッサのキャッシュにアクセスするプロセッサは、例えば「スヌープ」サイクルによって、低電力モードにあるプロセッサが低電力モードから復帰し、かつ、他のプロセッサによるアクセスに応答できるようになるまで待たなければならないことである。低電力モード・プロセッサのキャッシュにアクセスした時と、要求されたデータが検索されるか、または低電力モード・プロセッサのキャッシュに存在しないと決定された時との間の遅延は、対応するコンピュータ・システムの性能を著しく低下させる。このような問題は、プロセッサの数が増加するにつれて、低電力モードにあるプロセッサの数、およびこれらのプロセッサへのアクセス数も増加するので、より悪化する。さらに、コンピュータ・システムは、特に、要求された情報が低電力モードにあるプロセッサのローカル・キャッシュ内に存在しないと決定された場合に、不必要な電力を引き込む。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】国際公開第2006/028652号

【図面の簡単な説明】

【0007】

本発明の実施例は、制限目的ではなく例示目的のために示され、また、添付図面の図中にある類似の要素は同様の参照番号で示される。

【図1】本発明の少なくとも一実施例が使用された、マルチコア・マイクロプロセッサのブロック図を示す。

【図2】本発明の少なくとも一実施例が使用された、共有バス・コンピュータ・システムのブロック図を示す。

【図3】本発明の少なくとも一実施例が使用された、ポイント・ツー・ポイント相互接続コンピュータ・システムのブロック図を示す。

【図4】本発明の少なくとも一実施例が使用された、リング・ベースド・マルチコア・マイクロプロセッサのブロック図を示す。

【図5】本発明の一実施例に従って、低電力モード中にキャッシュされた情報を保持するために用いられる動作のフローチャートである。

【発明を実施するための形態】

【0008】

ここでは、コンピュータ・システム内の低電力モード中にキャッシュされた情報を保持するための少なくとも1つの技術が示される。以下の記述では、本発明の実施例について完全な理解を提供するために、説明目的のための多くの特定の詳細事項が述べられる。しかしながら、当業者にとって、これらの特定の詳細事項がなくても本発明の実施例を実行することができることは明白であろう。

【0009】

一般に、ここに記述された実施例は、複数のマイクロプロセッサ、複数のプロセッサ・コア、複数のプロセッサ・コアを有する単一のマイクロプロセッサ、または、各々が複数のプロセッサ・コアを有する複数のプロセッサ、を含む任意の数のマルチプロセッサ・システムに適用することができる。

【0010】

簡略化するために、マイクロプロセッサおよびマイクロプロセッサ・コアは、ここでは「プロセッサ」と総称する。さらに、1次キャッシュ(すなわち、それらは、プロセッサが最も頻繁に用いる情報を格納するために使用される)は、ここでは「ローカル・キャッシュ」と総称する。一方、2次キャッシュ(すなわち、それらは、L2キャッシュ、L3キャッシュ等のように、ローカル・キャッシュよりも頻繁に用いない情報を格納するために使用される)は、2またはそれ以上のプロセッサの1次キャッシュ内に格納された情報の少なくともいくらかを格納するために使用され、ここでは「共有キャッシュ」と総称される。最後に、プロセッサが動作する電圧および/または周波数状態は、1またはそれ以上のプロセッサのクロックが、アイドル、停止、ホールト、または最大動作周波数以下に低減される状態、および/または、1またはそれ以上のプロセッサの電圧が、最大動作電圧以下に低減される状態を含み、ここでは「電力モード」と総称される。

【0011】

いくつかの実施例では、プロセッサは、低電力モードに置かれる前に、そのローカル・キャッシュ内に格納された情報を共有キャッシュ内の対応する位置に保存し、その結果、さもなければ低電力モードのプロセッサのローカル・キャッシュからの情報に対してアクセスを試みるであろう他のプロセッサは、その代りに共有キャッシュから必要な情報を検索し、そして、低電力モードにあるプロセッサは、それが他に必要とされるまで低電力モードのままである。都合の良いことに、少なくとも一実施例では、コンピュータ・システム内の性能を改善することができる。なぜならば、他のプロセッサによるローカル・キャッシュへのアクセスを提供するために、低電力状態にあるプロセッサが低電力状態から復帰するのを待つシステムの代わりに、情報は、低電力状態に入る前に低電力モード・プロセッサが情報を保存した共有キャッシュから検索されるからである。いくつかの実施例では、共有キャッシュへのアクセスは、低電力モードのプロセッサのローカル・キャッシュへのアクセスよりも迅速に提供される。さらに、低電力モードのプロセッサは、そのローカル・キャッシュへのアクセスを提供するために低電力モードから復帰する必要がないので、少なくとも一実施例では、その実施例を使用するシステム内の電力の保存に役立つ。

【0012】

一実施例では、低電力モードに置かれるプロセッサは、最初に、キャッシュ・フラッシュ(一括消去)動作、キャッシュ無効動作、ライトバック動作、または、プロセッサのローカル・キャッシュ内に格納された情報を共有キャッシュに保存させるような他の動作を実行する。一実施例では、低電力モードは、プロセッサを低電力モードに置くために、プロセッサへの1またはそれ以上のクロックをオフにすることを含む。他の実施例では、低電力モードは、プロセッサ、ローカル・キャッシュ、またはその両方に電力を与えるために使用される1またはそれ以上の動作電圧の低減または取り除くことを含む。さらに他の実施例では、低電力モードは、プロセッサへの周波数および電圧の両方を、低減または完全に不能にしてもよい。

【0013】

図1は、本発明の少なくとも一実施例を用いたマルチコア・マイクロプロセッサを示す。特に、図1は、少なくとも2つのプロセッサ・コア105,110を有するマイクロプロセッサ100を示し、プロセッサ・コア105はローカル・キャッシュ107と、プロセッサ・コア110はローカル・キャッシュ113と、それぞれ関連している。さらに、図1には、ローカル・キャッシュ107,113の各々に格納された情報の少なくともいくつかのバージョンを格納する共有キャッシュ・メモリ115が示される。いくつかの実施例では、マイクロプロセッサ100は、さらに、図1に示されない他の論理、例えば、集積メモリ・コントローラ、集積グラフィック・コントローラを含むほか、I/O制御のようなコンピュータ・システム内の他の機能を実行するための他の論理も含む。一実施例では、マルチプロセッサ・システム内の各マイクロプロセッサ、またはマルチコアプロセッサ内の各プロセッサ・コアは、いずれの所定の時間においてもプロセッサ/コアの電力状態に依存してローカル・キャッシュまたは共有キャッシュのいずれかへのアクセスを指示するための論理119を含む(または、それに関連している)。論理は、コンピュータ・システムの動作中のいずれの時間においてもコアまたはプロセッサの電力状態を格納するために、不揮発性プログラマブル・メモリのようなメモリを含む(または、それに関連している)。そのような実施例では、プロセッサまたはコアへのアクセスは、ターゲット・プロセッサまたはコアの電力状態を考慮せずに行なわれるので、スヌープのような同一タイプのアクセスが各プロセッサまたはコアへ送られ、そして、ターゲット・プロセッサまたはコアは、プロセッサまたはコアの電力状態に依存して、スヌープをそのローカル・キャッシュへ提供するか、あるいは、スヌープを共有キャッシュへのアクセス(スヌープまたは他の動作)へ転送する。

【0014】

一実施例では、図1に示されたプロセッサ・コアの1つは、低電力モードに入る前に、そのローカル・キャッシュに格納された情報の最新バージョンを共有キャッシュに格納する。コアの1つが低電力モードにあるとき(「低電力モード・コア」)、低電力モード・コアは、低電力モードに入る前に、そのローカル・キャッシュから共有キャッシュへ最新情報を保存しているので、他のコアは、共有キャッシュへアクセスすることにより、低電力モード・コアのローカル・キャッシュ内に格納された情報の最新バージョンを獲得することができる。一実施例では、低電力モード・コアは、キャッシュ・フラッシュ動作を実行し、そこでは、ローカル・キャッシュされた情報の一部または全部が無効にされるか、あるいは、低電力モード・コアが低電力モードに入る前に、低電力モード・コアのローカル・キャッシュ内に格納された情報の一部または全部が共有キャッシュに保存される。他の実施例では、コアの命令セット・アーキテクチャに依存して、他の動作が、低電力モード・コアのローカル・キャッシュの情報の一部または全部を共有キャッシュへ保存するために実行される。

【0015】

一実施例では、プロセッサは、いつでも、1またはそれ以上の低電力モードを含む、多くの異なる電力状態の1つにある。例えば、プロセッサは、最大許容量の電力が消費されるような完全に電力供給されたコンポーネント状態(「C0」)、C0状態よりも低い許容電力消費量によって定義される低減電力コンポーネント状態(「C1」)、あるいは、他の低電力状態(例えばC3、C6など)にあり、それぞれが、連続的により低い許容電力消費によって定義される。さらに、1またはそれ以上のプロセッサのクロックあるいは電力供給は、各状態に関連する許容電力消費を遂行するために調整される。

【0016】

例えば、一実施例では、完全に電力供給されたC0状態は、プロセッサの性能を最大限にするために、周波数の範囲内で1またはそれ以上のプロセッサのクロックを操作することによって、および、電圧の範囲内でプロセッサへの1またはそれ以上の電力供給を操作することによって達成される。そのような電力状態は、例えば、プロセッサ上で実行されるプログラムによって、大きな実行要求がプロセッサに課されるときに有用である。低減電力状態C1は、電圧の範囲内でプロセッサへの1またはそれ以上の電力供給を維持しつつ、1またはそれ以上のプロセッサのクロックを停止または低減することによって、プロセッサをアイドル、ホールト、または他の低実行状態状に置くことにより遂行される。そのような低減電力状態では、プロセッサは、C0状態よりも少ない電力しか引き込まないが、例えばスヌープ動作と比較して、他のプロセッサからローカル・キャッシュへのアクセスは、なおも提供することができる。

【0017】

一実施例では、図1に示されたコアの1つのようなプロセッサは、プロセッサへの1またはそれ以上のクロックを停止または低減すること、および、プロセッサに供給される1またはそれ以上の電源の電圧を除去または低減することによって、C0またはC1よりも低電力状態に置かれるので、その結果、プロセッサのローカル・キャッシュ内に格納された情報は保持されないであろう。例えば、図1において、コアの1つが低電力コア・コンポーネント状態(「CC3」状態)に置かれ、そこでは、コアへの全てのクロックがホールトされ、さらに、全ての電源電圧が除去されるか、あるいは非活動レベルまで低減される。一実施例によれば、CC3状態では、コアは最小量の電力を引き込むか、恐らく電力を引き込まない。したがって、図1に示されたプロセッサまたはコアがCC3状態に置かれる前に、コアのローカル・キャッシュ内に格納された修正された情報の少なくとも一部が、共有キャッシュ内の対応する位置に格納される。一実施例では、コアがCC3状態に入る前に、修正された情報のみ(すなわち、共有キャッシュ内に格納された同一情報のバージョンよりも最新の、ローカル・キャッシュ内の情報のバージョン)が共有キャッシュ内に格納される。他の実施例では、ローカル・キャッシュの全コンテンツは、共有キャッシュ内で利用可能なバージョンから修正されたかどうかにかかわらず、コアがCC3状態に入る前に共有キャッシュに格納される。

【0018】

都合の良いことに、共有キャッシュは、CC3状態に置かれるコアのローカル・キャッシュ内に格納された少なくとも修正された情報を含んでいるので、一実施例では、図1に示された他のいずれのプロセッサまたはコアも、別な状態ではアクセスされるコアが低減されたコア・コンポーネント状態(つまり「CC1」)にあるときのようにCC3にあるコアのキャッシュへアクセスすることを試みるであろうが、それに代えて、CC3コアを低電力モードに残した状態で、共有キャッシュに直接に要求された情報にアクセスし、それによって電力を節約することができる。さらに、一実施例では、CC3のコアは、他のコアまたはプロセッサからそのローカル・キャッシュへのアクセスにサービスするために低電力状態から復帰していないので、例えば、スヌープ動作と比べて、そのアクセスしているプロセッサまたはコアは、そのアクセスされたコアが要求にサービスするためにその低電力状態から復帰するのを待たなければならない場合ほど、その要求する情報のために長く待つ必要がない。様々な実施例における上記の技術は、任意の数のプロセッサまたはプロセッサ・コアを有するシステムに適用することができる。

【0019】

図2は、例えば、本発明の一実施例が使用されたフロントサイド・バス(FSB)コンピュータ・システムを示す。いずれのプロセッサ201,205,210,215も、ローカル・レベル1(L1)キャッシュ・メモリ220,225,230,235,240,245,250,255のいずれかからの情報にアクセスすることができるが、これらは、プロセッサ・コア223,227,233,237,243,247,253,257の1つの中にあるか、あるいはそれらと関連している。さらに、プロセッサ201,205,210,215のいずれかは、共有レベル2(L2)キャッシュ203,207,213,217のいずれか1つからの情報、あるいは、チップセット265を介してシステム・メモリ260からの情報にアクセスすることができる。図2のプロセッサの1またはそれ以上は、いずれの時間においてもプロセッサ/コアの電力状態に依存して、ローカル・キャッシュまたは共有キャッシュのいずれかへのアクセスを指示するための論理219を含む(または、それに関連している)。論理は、コンピュータ・システムの動作中、コアまたはプロセッサの電力状態をいつでも格納するための不揮発性プログラマブル・メモリのようなメモリを含む(または、それに関係している)。

【0020】

図2に示された例において、プロセッサ201内では、両方のコアは、アクティブ・コア・コンポーネント状態(「CC0」状態)であるのに対して、プロセッサ205内では、両方のコアは、低減電力状態(「CC1」状態)であり、その結果、各コアはスヌープをサービスすることができ、あるいはアクティブ・コア223,227から同様の動作を提供することができる。プロセッサ210,215のそれぞれは、プロセッサ201,205のコアよりも低電力モード(「CC3」状態)にあるコアを有し、その結果、ローカル・キャッシュ240,245,250,255は、もはや利用することができない。一実施例では、アクティブ・コア223または227がプロセッサ210,215のコアのローカル・キャッシュ内に格納された情報にアクセスする場合、それらは、それぞれプロセッサ210,215の共有キャッシュから、情報を獲得しなければならない。なぜなら、一実施例において、プロセッサのコア223,227は、CC3状態に入る前に、それらのローカル・キャッシュ内に格納された情報の少なくとも修正されたバージョンをそれらの個々の共有キャッシュ213,217へ格納したからである。プロセッサ201のコアから要求された情報が、共有キャッシュ213,217内で利用できず、またローカル・キャッシュ230,235でも利用できない場合、次に、プロセッサ201のコアは、チップセット265を介して、あるいは図2に示されないハード・ドライブまたは他のメモリ・ソースを介して、システム・メモリ260からの情報にアクセスせざるを得ないであろう。

【0021】

いくつかの実施例では、図2の各プロセッサのコアは、図2に示されたように同一の電力モードではなく、互いに異なる電力モードにある。一実施例では、論理は、各プロセッサまたは各コアに含まれ、アクセスされているコアが、CC3状態にあるのか、または他の状態にあるのかを、スヌープまたは同様の動作で表示し、その結果、要求しているコアは、アクセスされているコアの適切なメモリ構造(ローカル・キャッシュまたは共有キャッシュ)をアドレスするために適切なトランザクションを送出する。いくつかの実施例では、コアの電力状態の表示は、コンピュータ・システムのBIOSによってアクセス可能なテーブルのようなソフトウェア・プログラムに記録され、追跡される。例えば、一実施例では、コアまたはプロセッサが電力状態を変更する場合は常に、その変更が論理またはメモリに格納されたテーブルに記録され、それをシステムのBIOSが読み取り、他のプロセッサまたはコアのローカル・キャッシュへのアクセスを試みるあらゆるコアまたはプロセッサに通知することができる。他のプロセッサまたはコアの電力モードについて、アクセスしているプロセッサまたはコアに通知することによって、それは、アクセスされる対応するローカル・キャッシュがCC3のような低減電力状態であるとき、共有キャッシュのような適切なメモリ構造にアクセスすることができる。他の実施例では、各プロセッサまたは各コアの電力モード情報は、BIOSのほかにハードウェア論理または他のソフトウェアを含む他の手段によって、修正され記録されてもよい。

【0022】

いくつかの実施例では、アクセスされているプロセッサまたはコアは、アクセスされたプロセッサ/コアの応答を制御するための論理を含む。例えば、一実施例において、ここで記述した技術を使用するためのコンピュータ・システム内の各プロセッサ(またはコア)は、あらゆる指定の時間でプロセッサの電力状態を格納するための、不揮発性プログラマブル・メモリのようなストレージを含み、そして、関連する論理は、他のプロセッサ/コアからのスヌープ要求または他の同様の動作にどのように応答すべきかを決定する。一実施例では、ストレージおよび論理は、例えば、CC3状態のプロセッサまたはコアへのアクセスを、プロセッサまたはコアのローカル・キャッシュから、共有キャッシュまたは他のL2キャッシュへ転送するために使用される。ところが、アクセスされているプロセッサまたはコアが、CC0またはCC1状態(すなわち、CC3よりも高い電力状態)のような他の状態である場合は、アクセスされたプロセッサまたはコア内の論理は、そのローカル・キャッシュをスヌープあるいはアクセスすることを許可するであろう。そのような実施例では、アクセスしているプロセッサ・コアは、プロセッサの電力状態を認識している必要はないが、他のプロセッサのローカル・キャッシュへスヌープのようなアクセスを単に送出し、そして、アクセスされたプロセッサ(またはコア)は、その時の電力状態に基づいて、どこへアクセスすべきかを指示する。

【0023】

図2に示されたFSBコンピュータ・システムに加えて、ポイント・ツー・ポイント(P2P)相互接続システムおよびリング相互接続システムを含む他のシステム構成が、本発明の様々な実施例と共に使用される。図3のP2Pシステムは、例えばいくつかのプロセッサを含んでもよいが、ここではプロセッサ370,380の2つのみが例示される。プロセッサ370,380は、メモリ32,34に接続するためのローカル・メモリ・コントローラ・ハブ(MCH)372,382をそれぞれ含む。プロセッサ370,380は、ポイント・ツー・ポイント(PtP)インターフェイス回路378,388を使用して、PtPインターフェイス350を介してデータを交換する。プロセッサ370,380は、ポイント・ツー・ポイント・インターフェイス回路376,394,386,398をそれぞれ使用して、個別のPtPインターフェイス352,354を介してチップセット390とデータを交換する。チップセット390は、さらに、高性能グラフィック・インターフェイス339を介して高性能グラフィック回路338とデータを交換する。本発明の実施例は、任意の数の処理コアを有するあらゆるプロセッサ内、または図3の各PtPバス・エージェント内に配置される。一実施例では、あらゆるプロセッサ・コアは、ローカル・キャッシュ・メモリ(図示せず)に含まれるか、あるいはそれと関連する。さらに、共有キャッシュ(図示せず)は、両方のプロセッサの外部のプロセッサの一方に含まれ、それもまたp2p相互接続を介してプロセッサに接続されるので、一方または両方のプロセッサのローカル・キャッシュ情報は、プロセッサが低電力モードに置かれた場合には、共有キャッシュに格納される。図3のプロセッサまたはコアの1つまたはそれ以上は、あらゆる所定の時間でプロセッサ/コアの電力状態に依存して、ローカル・キャッシュまたは共有キャッシュのいずれかへのアクセスを指示するための論理319含む(または、それらと関連している)。論理は、コンピュータ・システムの動作中にコアまたはプロセッサの電力状態をいつでも格納するための、不揮発性プログラマブル・メモリのようなメモリを含む(または、それらと関連している)。

【0024】

図4は、少なくとも一実施例を使用する、リング構成で組織されたコンピュータ・システムまたはプロセッサを示す。図1のリング・システムは、同心円のリング相互接続に沿って組織された、8つのプロセッサまたはプロセッサ・コア401,405,410,415,420,425,430,435を含み、各プロセッサまたはコアは、対応するローカル・キャッシュを有し、そのローカル・キャッシュは、リング相互接続に沿って他のコアによってアクセスされる。図4のシステムまたはプロセッサは、さらに、最終レベルの共有キャッシュ(LLC)440を含み、それが、ローカル・キャッシュ403,407,413,417,423,427,433,437に格納された情報の全てまたはいくつかのバージョンを格納する。一実施例では、図4のプロセッサまたはコアの1つが電力モードにある場合、もはやプロセッサまたはコアのローカル・キャッシュから情報にアクセスすることができず、したがって、低電力モード・プロセッサ/コアのローカル・キャッシュに格納された情報へのアクセスを試みる他のあらゆるプロセッサまたはコアは、その代りに、LLCからこの情報にアクセスすることを試みなければならない。一実施例では、情報がLLC内で利用できない場合、アクセスするプロセッサまたはコアは、メモリ・コントローラ445を介してシステム・メモリ・ソース(図示せず)からデータにアクセスする必要がある。図4のプロセッサの1つまたはそれ以上は、あらゆる所定の時間でプロセッサ/コアの電力状態に依存して、ローカル・キャッシュあるいは共有キャッシュのいずれかへのアクセスを指示するための論理419を含む(または、これらと関連している)。論理は、コンピュータ・システムの動作中に、コアまたはプロセッサの電力状態をいつでも格納するための、不揮発性プログラマブル・メモリのようなメモリを含む(または、これらと関連している)。

【0025】

図5は、本実施例が使用されるプロセッサまたはシステムの構成にかかわらず、本発明の少なくとも一実施例と共に使用される動作のフローチャートを示す。動作501で、例えば、スヌープ動作または他のキャッシュ・アクセス動作等によって、プロセッサへのアクセスが行なわれる。動作505で、アクセスされたプロセッサがCC3状態のような低電力モードである場合、動作510で、プロセッサの共有キャッシュがアクセスされる。アクセスは、使用されるプロトコルに依存して、共有キャッシュへのスヌープかもしれないし、あるいは、そのスヌープは、共有キャッシュにアクセスするための他の動作に変換されるかもしれない。動作515で、要求された情報が共有キャッシュ内にない場合、動作520で、システム・メモリへのアクセスが行なわれ、さらに、動作530で、情報がシステム・メモリから戻され、そうでない場合は、動作525で、情報が共有キャッシュから戻される。

【0026】

動作505で、プロセッサがCC3のような低電力モードでなかった場合、動作535で、プロセッサのローカル・キャッシュがアクセスされる。動作540で、情報がローカル・キャッシュ内で利用可能な場合、次に、動作545で、情報がローカル・キャッシュから戻される。そうでない場合は、上述のように、共有キャッシュまたはシステム・メモリのいずれかから情報にアクセスするために、そのプロセスは動作510に返る。一実施例では、アクセスするプロセッサは、それらが置かれている電力状態にかかわらずシステム内の他のプロセッサへスヌープを送り、アクセスされたプロセッサは、アクセスされたプロセッサの電力状態に基づいて、ローカル・キャッシュまたは共有キャッシュへアクセスを送るべきかどうかを決定する。例えば、アクセスされたときにアクセスされたプロセッサがCC3状態である場合は、他のプロセッサからのスヌープ動作は、スヌープまたは他の動作のいずれかとしてアクセスされたプロセッサの共有キャッシュに転送されるであろう。そうでない場合は、アクセスされたプロセッサが、ローカル・キャッシュがスヌープされることを可能にする電力状態である場合は、スヌープ動作は、アクセスされたプロセッサのローカル・キャッシュへアクセスする結果になる。他の実施例では、テーブルは、例えばBIOSを通して保持され、アクセスするプロセッサは、テーブル内に示された電力状態に基づいて、そのプロセッサのローカル・キャッシュがアクセスされるべきであるか、あるいは、その共有キャッシュがアクセスされるべきであるかを決定するために、他のプロセッサへのアクセスに先立って参照する。他の実施例では、アクセスが、アクセスされたプロセッサの電力状態に基づいて指示されるべき場合を管理するための他の技術が使用される。

【0027】

ここに記述された実施例は、多くの技術を用いて、多くの方法で実行することができる。例えば、少なくとも一実施例は、CMOS論理で実行されるが、他の実施例は、ソフトウェアで実行される。さらに、他の実施例は、ハードウェア論理およびソフトウェアの組合せによって実行される。

【0028】

一実施例では、ルーチンを促進するために使用されるソフトウェアは、機械読取り可能な媒体上に埋め込むことができる。機械読取り可能な媒体は、機械(例えば、コンピュータ、ネットワーク装置、携帯情報端末、製造ツール、1またはそれ以上のプロセッサのセットを具備する任意の装置等)によってアクセス可能な形式で情報を提供(すなわち、格納および/または転送)する、あらゆるメカニズムを含む。例えば、機械読取り可能な媒体は、記録可能/記録不可能な媒体(例えば、ファームウェアを含むリード・オンリ・メモリ(ROM)、ランダム・アクセス・メモリ(RAM)、磁気ディスク記憶媒体、光記憶媒体、フラッシュ・メモリ装置など)を含むほか、電気的、光学的、音響的、または他の形式の伝播信号(例えば、搬送波、赤外線信号、デジタル信号など)も同様に含む。

【0029】

少なくとも一実施例の1またはそれ以上の側面が、プロセッサ内の様々な論理を表わす機械可読媒体上に格納された代表的なデータによって実行され、それが機械によって読み取られたとき、機械にここに記述された技術を実行させるための論理を作り上げる。このような表現は、「IPコア」として知られ、有形の、機械読取り可能な媒体(「テープ」)に格納され、そして、実際に論理またはプロセッサを作成する組立機械内でロードするために様々な顧客または生産設備に提供される。

【0030】

以上、マイクロアーキテクチャのメモリ領域アクセスを指示するための方法および機器が記述された。上記の記述は、例示であり、これらに限定する意図ではないと理解すべきである。上記の記述を読みかつ理解することによって、当業者には他の多くの実施例が明らかになるであろう。したがって、本発明の範囲は、添付の請求項に付与されるべき全均等範囲に加えて、かかる請求項に関して決定されるべきである。

【符号の説明】

【0031】

100 マイクロプロセッサ

105,110 プロセッサ・コア

107,113 ローカル・キャッシュ

119 論理

201,205,210,215 プロセッサ

203,207,213,217 共有レベル2(L2)キャッシュ

219 論理

220,225,230,235,240,245,250,255 ローカル・レベル1(L1)キャッシュ・メモリ

223,227,233,237,243,247,253,257 プロセッサ・コア

260 システム・メモリ

265 チップセット

32,34 メモリ

319 論理

338 高性能グラフィック回路

339 高性能グラフィック・インターフェイス

350,352,354 PtPインターフェイス

370,380 プロセッサ

372,382 ローカル・メモリ・コントローラ・ハブ(MCH)

376,378,386,388,394,398 ポイント・ツー・ポイント(PtP)インターフェイス回路

390 チップセット

401,405,410,415,420,425,430,435 プロセッサまたはプロセッサ・コア

403,407,413,417,423,427,433,437 ローカル・キャッシュ

419 論理

440 共有キャッシュ(LLC)

【特許請求の範囲】

【請求項1】

低電力モードに置かれる第1プロセッサ・コアであって、前記第1プロセッサ・コアが前記低電力モードに入る前に、前記第1プロセッサ・コアのローカル・キャッシュ内に格納された少なくとも修正された情報は、共有キャッシュに格納される、第1プロセッサ・コアと、

前記第1プロセッサ・コアの前記ローカル・キャッシュからの情報にアクセスするためにスヌープを開始する第2プロセッサ・コアと、

前記第1プロセッサ・コアのいずれか所定の時間の電力状態に依存して、前記情報に対するスヌープを前記第1プロセッサ・コアの前記ローカル・キャッシュまたは前記共有キャッシュのいずれかへ指示する前記第1プロセッサ・コアの論理であって、前記第2プロセッサ・コアは、前記第1プロセッサ・コアが前記低電力モードであることに応答して、前記第1プロセッサ・コアのローカル・キャッシュに代えて、前記共有キャッシュにアクセスする、論理と、

から構成されることを特徴とするプロセッサ。

【請求項2】

前記論理は、前記第1プロセッサ・コアの電力状態に依存して、前記アクセスを前記第1プロセッサ・コアの前記共有キャッシュまたは前記ローカル・キャッシュに指示することを特徴とする請求項1記載のプロセッサ。

【請求項3】

前記論理は、前記第1プロセッサ・コアが前記低電力モードであるかどうかを判定し、かつ、前記第1プロセッサが前記低電力モードであるかどうかに基づいて、前記第1プロセッサ・コアのローカル・キャッシュからの情報にアクセスすることを試みることを特徴とする請求項2記載のプロセッサ。

【請求項4】

前記共有キャッシュは、少なくとも2つのプロセッサ・コアに対応する少なくとも2つのローカル・キャッシュ内に格納された少なくともいくつかの情報を格納することを特徴とする請求項1記載のプロセッサ。

【請求項5】

前記ローカル・キャッシュは、レベル1(L1)キャッシュを含み、前記共有キャッシュは、レベル2(L2)キャッシュを含むことを特徴とする請求項4記載のプロセッサ。

【請求項6】

前記低電力モードは、前記第1プロセッサ・コアの少なくとも1個のクロックを低減し、前記第1プロセッサ・コアへの電力を不能にすることを含むことを特徴とする請求項1記載のプロセッサ。

【請求項7】

前記低電力モードは、前記第1プロセッサ・コアをアイドル状態に置き、かつ、前記第1プロセッサ・コアの動作電圧を零に低減することを含むことを特徴とする請求項1記載のプロセッサ。

【請求項8】

前記低電力状態に入った結果、前記ローカル・キャッシュはフラッシュされることを特徴とする請求項1記載のプロセッサ。

【請求項9】

少なくとも2つのプロセッサ・コアを有する第1プロセッサであって、前記プロセッサ・コアの少なくとも1つが低電力モードに入ると、前記少なくとも1つのプロセッサ・コアのローカル・キャッシュ内に格納された情報はもはやアクセス可能ではなくなり、前記少なくとも1つのプロセッサ・コアは、前記少なくとも1つのプロセッサ・コアのローカル・キャッシュ内に格納された情報に対するスヌープを、前記少なくとも1つのプロセッサ・コアがアクティブである場合前記少なくとも1つのプロセッサ・コアのローカル・キャッシュに、かつ、前記少なくとも1つのプロセッサ・コアが前記低電力モードである場合共有キャッシュに、指示する、第1プロセッサと、

前記第1プロセッサの前記少なくとも1つのプロセッサ・コアが低電力モードである場合は、前記第1プロセッサの前記共有キャッシュからの情報にアクセスする少なくとも1つのプロセッサ・コアを有する第2プロセッサであって、前記共有キャッシュは、前記少なくとも2つのプロセッサ・コアのローカル・キャッシュのそれぞれに格納された情報のバージョンを格納する、第2プロセッサと、

前記共有キャッシュ内に格納された情報のバージョンを格納するためのシステム・メモリと、

メモリ・コントローラであって、そこを通って前記第2プロセッサの少なくとも1つのプロセッサ・コアは前記システム・メモリにアクセスする、メモリ・コントローラと、

から構成されることを特徴とするシステム。

【請求項10】

前記第1プロセッサの少なくとも1つのプロセッサ・コアの電力状態を格納するための不揮発性メモリをさらに含むことを特徴とする請求項9記載のシステム。

【請求項11】

前記第2プロセッサの少なくとも1つのプロセッサ・コアは、前記第1プロセッサの少なくとも1つのプロセッサ・コアがどのような電力状態にあるかにかかわらず、前記第1プロセッサの少なくとも1つのプロセッサ・コアからの情報へのアクセスを試みることを特徴とする請求項10記載のシステム。

【請求項12】

前記第1プロセッサの少なくとも1つのプロセッサ・コアが低電力モードに入っていない場合、前記第2プロセッサの少なくとも1つのプロセッサ・コアは、前記第1プロセッサの少なくとも1つのプロセッサ・コアのローカル・キャッシュをスヌープすることを特徴とする請求項11記載のシステム。

【請求項13】

前記第1および第2プロセッサは、フロントサイド・バスを介して結合されることを特徴とする請求項9記載のシステム。

【請求項14】

前記第1および第2プロセッサは、ポイント・ツー・ポイント相互接続を介して結合されることを特徴とする請求項9記載のシステム。

【請求項15】

前記第1および第2プロセッサは、リング相互接続を介して結合されることを特徴とする請求項9記載のシステム。

【請求項16】

前記低電力モードは、クロックを停止し、かつ、前記第1プロセッサの少なくとも1つのプロセッサ・コアへの電力を除去することを含むことを特徴とする請求項9記載のシステム。

【請求項17】

前記第1プロセッサの少なくとも1つのプロセッサ・コアが前記低電力モードから復帰し、かつ、そのローカル・キャッシュにアクセスするのを待つ時間よりも、前記共有キャッシュからの情報にアクセスするために要求される時間の方が短いことを特徴とする請求項9記載のシステム。

【請求項18】

第1プロセッサ・コアを、前記第1プロセッサ・コアによって、低電力モードに置く段階であって、前記低電力モードは、前記第1プロセッサ・コアのレベル1(L1)キャッシュからレベル2(L2)キャッシュへ少なくとも修正された情報を格納する段階を含む、段階と、

前記第1プロセッサ・コアが前記低電力モードに入ることに応答して、前記L1キャッシュの代わりに、前記第2プロセッサ・コアによって、前記L2キャッシュにアクセスする段階と、

前記第2プロセッサ・コアによって要求された情報が前記L2キャッシュに格納されていない場合に、システム・メモリへのアクセスを生成する段階であって、前記第1プロセッサ・コアの論理は、前記第1プロセッサ・コアがアクティブである場合前記L1キャッシュへ、かつ、前記第1プロセッサ・コアが前記低電力モードである場合前記L2キャッシュへ、前記アクセスをルートする、段階と、

から構成されることを特徴とする方法。

【請求項19】

前記第1プロセッサ・コアは、前記第1プロセッサ・コアの前記低電力モードに基づいて、前記アクセスを前記L1またはL2キャッシュへルートすることを特徴とする請求項18記載の方法。

【請求項20】

前記低電力モードは、前記第1プロセッサ・コアに関連する不揮発性プログラマブル・メモリ内に示されることを特徴とする請求項19記載の方法。

【請求項21】

前記論理は、前記第1プロセッサ・コアが前記低電力モードにあるかどうかに基づいて、前記第2プロセッサからの前記アクセスをどこへルートするのかを決定することを特徴とする請求項18記載の方法。

【請求項22】

前記低電力モードは、前記第1プロセッサ・コアを停止状態に置き、かつ、前記動作電圧を低減することを含むことを特徴とする請求項18記載の方法。

【請求項1】

低電力モードに置かれる第1プロセッサ・コアであって、前記第1プロセッサ・コアが前記低電力モードに入る前に、前記第1プロセッサ・コアのローカル・キャッシュ内に格納された少なくとも修正された情報は、共有キャッシュに格納される、第1プロセッサ・コアと、

前記第1プロセッサ・コアの前記ローカル・キャッシュからの情報にアクセスするためにスヌープを開始する第2プロセッサ・コアと、

前記第1プロセッサ・コアのいずれか所定の時間の電力状態に依存して、前記情報に対するスヌープを前記第1プロセッサ・コアの前記ローカル・キャッシュまたは前記共有キャッシュのいずれかへ指示する前記第1プロセッサ・コアの論理であって、前記第2プロセッサ・コアは、前記第1プロセッサ・コアが前記低電力モードであることに応答して、前記第1プロセッサ・コアのローカル・キャッシュに代えて、前記共有キャッシュにアクセスする、論理と、

から構成されることを特徴とするプロセッサ。

【請求項2】

前記論理は、前記第1プロセッサ・コアの電力状態に依存して、前記アクセスを前記第1プロセッサ・コアの前記共有キャッシュまたは前記ローカル・キャッシュに指示することを特徴とする請求項1記載のプロセッサ。

【請求項3】

前記論理は、前記第1プロセッサ・コアが前記低電力モードであるかどうかを判定し、かつ、前記第1プロセッサが前記低電力モードであるかどうかに基づいて、前記第1プロセッサ・コアのローカル・キャッシュからの情報にアクセスすることを試みることを特徴とする請求項2記載のプロセッサ。

【請求項4】

前記共有キャッシュは、少なくとも2つのプロセッサ・コアに対応する少なくとも2つのローカル・キャッシュ内に格納された少なくともいくつかの情報を格納することを特徴とする請求項1記載のプロセッサ。

【請求項5】

前記ローカル・キャッシュは、レベル1(L1)キャッシュを含み、前記共有キャッシュは、レベル2(L2)キャッシュを含むことを特徴とする請求項4記載のプロセッサ。

【請求項6】

前記低電力モードは、前記第1プロセッサ・コアの少なくとも1個のクロックを低減し、前記第1プロセッサ・コアへの電力を不能にすることを含むことを特徴とする請求項1記載のプロセッサ。

【請求項7】

前記低電力モードは、前記第1プロセッサ・コアをアイドル状態に置き、かつ、前記第1プロセッサ・コアの動作電圧を零に低減することを含むことを特徴とする請求項1記載のプロセッサ。

【請求項8】

前記低電力状態に入った結果、前記ローカル・キャッシュはフラッシュされることを特徴とする請求項1記載のプロセッサ。

【請求項9】

少なくとも2つのプロセッサ・コアを有する第1プロセッサであって、前記プロセッサ・コアの少なくとも1つが低電力モードに入ると、前記少なくとも1つのプロセッサ・コアのローカル・キャッシュ内に格納された情報はもはやアクセス可能ではなくなり、前記少なくとも1つのプロセッサ・コアは、前記少なくとも1つのプロセッサ・コアのローカル・キャッシュ内に格納された情報に対するスヌープを、前記少なくとも1つのプロセッサ・コアがアクティブである場合前記少なくとも1つのプロセッサ・コアのローカル・キャッシュに、かつ、前記少なくとも1つのプロセッサ・コアが前記低電力モードである場合共有キャッシュに、指示する、第1プロセッサと、

前記第1プロセッサの前記少なくとも1つのプロセッサ・コアが低電力モードである場合は、前記第1プロセッサの前記共有キャッシュからの情報にアクセスする少なくとも1つのプロセッサ・コアを有する第2プロセッサであって、前記共有キャッシュは、前記少なくとも2つのプロセッサ・コアのローカル・キャッシュのそれぞれに格納された情報のバージョンを格納する、第2プロセッサと、

前記共有キャッシュ内に格納された情報のバージョンを格納するためのシステム・メモリと、

メモリ・コントローラであって、そこを通って前記第2プロセッサの少なくとも1つのプロセッサ・コアは前記システム・メモリにアクセスする、メモリ・コントローラと、

から構成されることを特徴とするシステム。

【請求項10】

前記第1プロセッサの少なくとも1つのプロセッサ・コアの電力状態を格納するための不揮発性メモリをさらに含むことを特徴とする請求項9記載のシステム。

【請求項11】

前記第2プロセッサの少なくとも1つのプロセッサ・コアは、前記第1プロセッサの少なくとも1つのプロセッサ・コアがどのような電力状態にあるかにかかわらず、前記第1プロセッサの少なくとも1つのプロセッサ・コアからの情報へのアクセスを試みることを特徴とする請求項10記載のシステム。

【請求項12】

前記第1プロセッサの少なくとも1つのプロセッサ・コアが低電力モードに入っていない場合、前記第2プロセッサの少なくとも1つのプロセッサ・コアは、前記第1プロセッサの少なくとも1つのプロセッサ・コアのローカル・キャッシュをスヌープすることを特徴とする請求項11記載のシステム。

【請求項13】

前記第1および第2プロセッサは、フロントサイド・バスを介して結合されることを特徴とする請求項9記載のシステム。

【請求項14】

前記第1および第2プロセッサは、ポイント・ツー・ポイント相互接続を介して結合されることを特徴とする請求項9記載のシステム。

【請求項15】

前記第1および第2プロセッサは、リング相互接続を介して結合されることを特徴とする請求項9記載のシステム。

【請求項16】

前記低電力モードは、クロックを停止し、かつ、前記第1プロセッサの少なくとも1つのプロセッサ・コアへの電力を除去することを含むことを特徴とする請求項9記載のシステム。

【請求項17】

前記第1プロセッサの少なくとも1つのプロセッサ・コアが前記低電力モードから復帰し、かつ、そのローカル・キャッシュにアクセスするのを待つ時間よりも、前記共有キャッシュからの情報にアクセスするために要求される時間の方が短いことを特徴とする請求項9記載のシステム。

【請求項18】

第1プロセッサ・コアを、前記第1プロセッサ・コアによって、低電力モードに置く段階であって、前記低電力モードは、前記第1プロセッサ・コアのレベル1(L1)キャッシュからレベル2(L2)キャッシュへ少なくとも修正された情報を格納する段階を含む、段階と、

前記第1プロセッサ・コアが前記低電力モードに入ることに応答して、前記L1キャッシュの代わりに、前記第2プロセッサ・コアによって、前記L2キャッシュにアクセスする段階と、

前記第2プロセッサ・コアによって要求された情報が前記L2キャッシュに格納されていない場合に、システム・メモリへのアクセスを生成する段階であって、前記第1プロセッサ・コアの論理は、前記第1プロセッサ・コアがアクティブである場合前記L1キャッシュへ、かつ、前記第1プロセッサ・コアが前記低電力モードである場合前記L2キャッシュへ、前記アクセスをルートする、段階と、

から構成されることを特徴とする方法。

【請求項19】

前記第1プロセッサ・コアは、前記第1プロセッサ・コアの前記低電力モードに基づいて、前記アクセスを前記L1またはL2キャッシュへルートすることを特徴とする請求項18記載の方法。

【請求項20】

前記低電力モードは、前記第1プロセッサ・コアに関連する不揮発性プログラマブル・メモリ内に示されることを特徴とする請求項19記載の方法。

【請求項21】

前記論理は、前記第1プロセッサ・コアが前記低電力モードにあるかどうかに基づいて、前記第2プロセッサからの前記アクセスをどこへルートするのかを決定することを特徴とする請求項18記載の方法。

【請求項22】

前記低電力モードは、前記第1プロセッサ・コアを停止状態に置き、かつ、前記動作電圧を低減することを含むことを特徴とする請求項18記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−69320(P2013−69320A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2012−249462(P2012−249462)

【出願日】平成24年11月13日(2012.11.13)

【分割の表示】特願2010−518285(P2010−518285)の分割

【原出願日】平成20年7月14日(2008.7.14)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成24年11月13日(2012.11.13)

【分割の表示】特願2010−518285(P2010−518285)の分割

【原出願日】平成20年7月14日(2008.7.14)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

[ Back to top ]