光学情報読取装置

【課題】第1、第2のプロセッサを備え、第1のプロセッサと第2のプロセッサで画像処理とデコード処理を並列処理する光学情報読取装置を前提として、その処理効率を高める。

【解決手段】共有メモリ104には複数の設定バンク116が記憶されており、この設定バンク116は第1、第2のCPU101,102によって夫々参照される。各設定バンク116には、撮像パラメータ、デコードパラメータが含まれる。第1CPU101の画像処理は撮像間隔P毎に実行される。撮像間隔PはP=Ta−Tbによって求められる。ここに、Taはデコードタイムアウト時間であり、Tbは撮像時間である。第1CPU101の画像処理及び第2CPU102のデコード処理は設定バンクに含まれるパラメータに従って実行される。

【解決手段】共有メモリ104には複数の設定バンク116が記憶されており、この設定バンク116は第1、第2のCPU101,102によって夫々参照される。各設定バンク116には、撮像パラメータ、デコードパラメータが含まれる。第1CPU101の画像処理は撮像間隔P毎に実行される。撮像間隔PはP=Ta−Tbによって求められる。ここに、Taはデコードタイムアウト時間であり、Tbは撮像時間である。第1CPU101の画像処理及び第2CPU102のデコード処理は設定バンクに含まれるパラメータに従って実行される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、バーコードやQRコードのような光学情報を読み取ってデコードする光学情報読取装置に関する。

【背景技術】

【0002】

トレーサビリティ(traceability)が普及した今日、工場や物流拠点などに光学情報読取装置を設置して、製品や産品に付与されたバーコードなどの光学情報又は光学符号の解読が行われている。この種の光学情報読取装置は「バーコードリーダ」又は「コードリーダ」と呼ばれている。

【0003】

バーコードリーダはレーザ光、可視光、赤外光を光学情報に照射し、その反射光を光学読取素子(撮像素子)で取り込む。そして、この取り込んだ撮像画像を画像処理して光学情報を抽出した読取画像を作成し、そして、この読取画像のデコードを実行する(特許文献1)。

【0004】

ところで、光学情報読取装置に2つのCPU(プロセッサ)を用意し、この2つのプロセッサで画像処理とデコード処理とを並列処理することが考えられている。この場合、第1のプロセッサで撮像及び画像処理を完了した後、第2のプロセッサに対してデコード処理の要求を行い、このデコード処理要求を受け取った第2のプロセッサはデコード処理を開始する手順で並列処理が実行されることになる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−33465号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

第2プロセッサがデコード処理している最中に、第1プロセッサは次の画像処理を実行することになる。しかし、第2プロセッサのデコード処理が所定時間内に成功しなかった場合には、このデコード処理がキャンセルされ、第1プロセッサは第2プロセッサに対して再度のデコード要求を行うことになるが、このデコード要求を受けたとしても第1プロセッサが画像処理中であれば、第2プロセッサはデコードを開始することができないという問題が発生して第2プロセッサは待機状態に置かれる。

【0007】

一般的に、第1プロセッサには複数のタスクが割り当てられ、重要なタスクから優先順位が付けられて、優先順位の高いタスクを処理している間は、優先順位の低いタスクは実行されずに待機状態にある。バーコードリーダにとって、撮像処理は比較的優先順位の高いタスクとして設定されることから、他のタスク(例えば画像の保存や画像の送信など)は撮像処理が行われていない間に第1プロセッサによって実行される。

【0008】

これに対して第2プロセッサは、第1プロセッサが撮像した画像を受け取ってデコード処理を実行することから、この第2プロセッサにデコード待機状態が発生するのは回避したい。例えば、第1プロセッサが連続的に撮像処理を実行すれば、第2プロセッサのデコード開始時には必ず第1プロセッサの撮像処理を完了させるように制御することは可能である。しかし、第2プロセッサにデコード待機状態が発生するのを防止する目的で第1プロセッサが連続的に撮像処理を実行すると、第1プロセッサに割り当てられている撮像処理以外のタスクの実行が遅れてしまうという他の問題が浮上してしまう。

【0009】

本発明の目的は、第1、第2のプロセッサを備え、第1のプロセッサと第2のプロセッサで画像処理とデコード処理を並列処理する光学情報読取装置を前提として、その処理効率を高めることのできる光学情報読取装置を提供することにある。

本発明の更なる目的は、第1のプロセッサのリソースを最大限に有効活用しながら、第2のプロセッサのデコード待機状態の発生を抑えることのできる光学情報読取装置を提供することにある。

【課題を解決するための手段】

【0010】

上記の技術的課題は、本発明によれば、

光学情報を撮像する光学読取素子と、

撮像パラメータとデコードパラメータとを含む設定バンクを記憶した共有メモリと、

該共有メモリの前記設定バンクの撮像パラメータに従って画像処理して読取画像を生成すると共に生成した読取画像を前記共有メモリに転送する撮像処理を少なくとも含む複数の処理を実行する第1プロセッサと、

該共有メモリに記憶されている前記読取画像を呼び出して、該読取画像を前記共有メモリの前記設定バンクのデコードパラメータに従ってデコード処理する第2プロセッサとを有し、

前記第1プロセッサは、前回の撮像処理が終了した後、撮像処理以外のタスクを実行しながら所定の撮像間隔を待機してから次回の撮像処理を実行し、

前記所定の撮像間隔が、前記第2プロセッサでデコード処理のデコードタイムアウト時間から撮像時間を引いた値と略等しい値に設定されることを特徴とする光学情報読取装置を提供することにより達成される。

【0011】

所定の撮像間隔として、(1)前記第2プロセッサのデコード処理のデコードタイムアウト時間から撮像時間を引いた値であってもよいし、(2)ユーザによって設定された値であってもよい。

【0012】

上記(1)の撮像間隔であれば、デコードが上手く行かずタイムアウトによりキャンセルされた時点では、第1プロセッサによる画像処理が必ず終了していることから、第2プロセッサは、直ちに第1プロセッサが作成した読取画像のデコード処理を開始することができる。

【0013】

上記(2)の撮像間隔は、一般的にユーザが撮像間隔を「ゼロ」に設定すると予想できることから、第1プロセッサによる画像処理が次々と実行されるため、第2プロセッサでデコードが上手く行かずタイムアウトによりキャンセルされた時点では、次にデコードする読取画像が既に存在していることから第2プロセッサは直ちにデコードを開始することができる。

【0014】

本発明の他の目的、作用効果は、以下の本発明の実施例の詳しい説明から明らかになろう。

【図面の簡単な説明】

【0015】

【図1】バーコードリーダ・システムの全体構成図である。

【図2】光学情報読取装置であるバーコードリーダの斜視図である。

【図3】バーコードリーダの内部に配置される各種基板の配置を斜め前方から見た図である。

【図4】図3に関連した図であって、バーコードリーダの内部に配置される各種基板の配置を斜め後方から見た図である。

【図5】バーコードリーダに内蔵される各種基板の結線関係を説明するための図である。

【図6】バーコードリーダに内蔵されるシャーシと、このシャーシに組み付けられたメイン基板、電源基板、サブ基板の配置を説明するための図である。

【図7】シャーシに組み付けられる各種の要素を説明するための図である。

【図8】カメラモジュールを斜め後方から見た図である。

【図9】カメラモジュールを斜め前方から見た図である。

【図10】カメラモジュールの内部構造を説明するための概念図である。

【図11】カメラモジュールと各種基板の関係を示す図であり、この状態でバーコードリーダのメインケースに収容される。

【図12】図11と同様に、カメラモジュールと各種基板の関係を示す図であり、好ましい例として、電源基板、メイン基板の上に放熱部材である熱伝導ゴムを載置した例を示す図である。

【図13】図12に関連して、熱伝導ゴムが電源基板、メイン基板とメインケースとに当接した状態を説明するための図である。

【図14】メインケースから前方に延びる一対のロッド状の延長部分の前端面にLED基板(内部照明基板)を取り付け、また、延長部分に電源基板、メイン基板の前端を固定することを説明するための図である。

【図15】バーコードリーダのメインケース及びその開放した後端がリヤケースによって閉じられることを説明するための図であり、このリヤケースにコネクタ基板を固定した状態を示す分解斜視図である。

【図16】図15に図示の内蔵物を収容したメインケースの正面図である。

【図17】図16からカメラモジュールを取り除いた状態のメインケースの正面図である。

【図18】バーコードリーダの機能構成図である。

【図19】バーコードリーダの画像バッファと共有メモリとの関係を説明するための図である。

【図20】共有メモリに複数の設定バンクが格納されていることを説明するための図である。

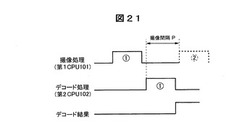

【図21】バーコードリーダの第1CPUで実行される撮像処理が撮像間隔毎に実行されることを説明するためのタイムチャートである。

【図22】設定バンクの条件に基づいて撮像処理及びデコード処理する場合に、複数の設定バンクを夫々一回だけ使用して処理する例を説明するための図である。

【図23】設定バンクの条件に基づいて撮像処理及びデコード処理する場合に、複数の設定バンクから一つの設定バンクを複数回使用して処理する例を説明するための図である。

【図24】複数の設定バンクを夫々一回だけ使用して処理した具体例を示すタイムチャートである。

【図25】複数の設定バンクから一つの設定バンクを2回使用して処理した具体例を示すタイムチャートである。

【図26】複数の設定バンクを夫々一回だけ使用して処理した他の具体例を示すタイムチャートである。

【図27】撮像間隔が「ゼロ」(バースト撮像)の連続的に撮像する連続撮像モードでのタイムチャートである。

【発明を実施するための形態】

【実施例】

【0016】

以下に、添付の図面に基づいて本発明の好ましい実施例を説明する。

【0017】

バーコードリーダ・システム(図1):

図1はバーコードリーダ・システムの概要を説明するための図である。図1を参照して、バーコードリーダ・システム1は、二次元情報読取装置であるバーコードリーダ2と、必要に応じてバーコードリーダ2に接続されるパーソナルコンピュータ3とを有し、バーコードリーダ2で撮像した画像をパーソナルコンピュータ3で確認しながら、このパーソナルコンピュータ3を使って各種の設定が行われる。バーコードリーダ・システム1には、更に、必要に応じてリング型の外部照明ユニット4がバーコードリーダ2に接続され、バーコードリーダ2の内部照明ユニット5と一緒になって又は内部照明ユニット5の動作を止めて外部照明ユニット4だけでワークを照明する。

【0018】

リング型の外部照明ユニット4は、このバーコードリーダ・システム1のための専用品であり、異なる種類の複数の外部照明ユニット4を用意するのが好ましい。勿論、外部照明ユニット4として専用品以外の照明ユニットを組み込むことも可能である。

【0019】

バーコードリーダ・システム1は、バーコード、QRコードなどの光学情報又は光学符号が印字又は刻印された商品あるいは物品を製造する工場では物品の搬送経路に設置され、バーコードリーダ2で商品又は物品に印字された光学情報に記録されている情報を読み取り、この情報をパーソナルコンピュータ3に転送して情報の解析が行われる。「光学情報読取装置」は一般的に“バーコードリーダ”又は“コードリーダ”を呼ばれており、ここでは“バーコードリーダ”という業界用語を使用する。

【0020】

また、図示の例では、図1に開示のように、パーソナルコンピュータ3に設定プログラムをインストールすることにより、このパーソナルコンピュータ3を使ってバーコードリーダ・システム1の各種の設定が行われる。勿論、バーコードリーダ2に例えばタッチパネル付き表示手段を設けて、この表示手段を使ってバーコードリーダ2、内部照明ユニット5(図3)及び/又は外部照明4(図20、図21)の設定作業ができるようにしてもよい。

【0021】

バーコードリーダ2(図2〜図19):

図2はバーコードリーダ2の外観を示す斜視図である。バーコードリーダ2は、断面多角形の形状のメインケース6と、メインケース6の前端に固定される円筒状のフロントケース7とを有し、この円筒状のフロントケース7に前述した内部照明ユニット5が内蔵されている。メインケース6は、図2などから分かるように略正方形の断面形状を備えているのが好ましい。

【0022】

バーコードリーダ2には互いに独立した複数の基板が内蔵されている。図3〜図5を参照して、バーコードリーダ2が備える複数の基板は次の通りである。

(1)メイン基板10:

メイン基板10には、CPU、メモリMが搭載され、画像をメモリMに転送してDSP(digital Signal Processor)で画像処理する。そして、メイン基板10のCPUで内部照明ユニット5を具備したバーコードリーダ2を制御し、また、外部照明ユニット4との通信を実行する。

(2)電源基板11:

バーコードリーダ2の電源を生成する。絶縁入出力回路が実装されている。

【0023】

(3)サブ基板12:

大容量メモリが搭載されており、この大容量メモリに取得画像や各種の設定が保存される。制限した大きさ及び形状のメイン基板10では、このメイン基板10に実装することのできなかった要素が実装される。

(4)CMOS基板13(受光基板):

CMOSイメージセンサ(光学読取素子)が実装され、画像を取得してメイン基板10に転送する。ポインタ用のLED40(図10)が搭載される。

【0024】

(5)LED基板14:

内部照明ユニット5を構成する円形開口14aを備えた円板状の基板であり、このLED基板14に複数の照明用LED80が実装され(後に説明する図32)、この複数の照明用LED80の点灯制御を実行する。複数の照明用LED80は、後に説明するバーコードリーダ2のレンズ組立体36の光軸を中心とする複数の径の異なる同心円上に配列される。内部照明ユニット5(LED基板14)に実装された複数の照明用LED80は後に説明するようにエリア分けして点灯制御される。また、このLED基板14には、各エリアに属する複数の照明用LEDに定電流を供給する定電流回路が設けられる。

(6)コネクタ基板15:

外部電源、IO、RS232C、Ethernet(登録商標)、外部照明ユニット4との入出力のインターフェースを構成する基板である。なお、外部照明ユニット4には、電源基板11から電源が供給される。

【0025】

図3、図4を参照して、メイン基板10と電源基板11とは互いに対向して配置され、このメイン基板10と電源基板11の各々の側縁で挟まれた領域に、これらメイン基板10と電源基板11と直交するようにしてサブ基板12が配設されている。サブ基板12とメイン基板10の配置位置を互いに置換してもよい。メイン基板10、電源基板11、サブ基板12は、バーコードリーダ2は矩形断面のメインケース6の4つの側面のうち3つの側面に隣接し且つこの3つの側面の各々に沿って配設される。そして、このメイン基板10、電源基板11、サブ基板12で囲まれた空間にCMOS基板13が位置し、このCMOS基板13は各基板10〜12と直交する一つの鉛直面に配設される。また、このCMOS基板13と平行に且つCMOS基板13を挟んで互いに対峙してLED基板14とコネクタ基板15が位置決めされる。

【0026】

図5は、上述した各基板10〜15の接続関係を説明するための図である。メイン基板10は、電源基板11と第1のFFC20(Flexible Flat Cable)で接続され、サブ基板12と第2のFFC21で接続され、CMOS基板13とFPC(Flexible Printed Circuit)22で接続され、内部照明ユニット4LED基板14と第3のFFC23で接続され、コネクタ基板15と第1のハーネス24で接続されている。電源基板11は、また、内部照明ユニット5のLED基板14と第2のハーネス25で接続され、LED基板14に実装された照明用LEDを発光させるための電源が電源基板11からLED基板14に供給される。電源基板11とコネクタ基板15は、2本のハーネス26、27とFFC28で接続されている。

【0027】

図5を再び参照して、メイン基板10と電源基板11とが略同じ大きさ及び形状を有している点に注目すべきである。換言すれば、メイン基板10は、電源基板11と略同じ大きさ及び形状となるように設計され、この制約のためにメイン基板10に搭載できなかった電子部品がサブ基板12に搭載される。

【0028】

図6、図7を参照して、メイン基板10、電源基板11、サブ基板12、CMOS基板13は、樹脂成型品であるシャーシ30に組み付けられる。シャーシ30は、図7から最も良く分かるように、メインケース6の断面形状とほぼ相似形の略正方形の断面形状を有するボックス形状を有し、このボックス形状の一つの側面30aを閉塞し、他の5つの面を開放した形態を有している。メイン基板10、電源基板11、サブ基板12は、開放した3つの側面10b〜10dに夫々配設される。樹脂成型品のシャーシ30は前後に開放しており、その一端開口30fからカメラモジュール32が挿入され(図7)、シャーシ30の中に挿入されたカメラモジュール32は、その周囲にメイン基板10、電源基板11、サブ基板12が位置し、これらメイン基板10、電源基板11、サブ基板12によってカメラモジュール32が包囲された状態になる。

【0029】

図8、図9を参照して、カメラモジュール32は、アルミニウムなどのダイキャスト品からなるカメラホルダ35を有し、このカメラホルダ35は、矩形断面のホルダ本体35aと、ホルダ本体35aの互いに対向する側面から前方に且つ互いに平行に延びる一対のアーム35bと、一対のアーム35bの前端から互いに離れる方向に延びる一対の取付部35cとを有している。ホルダ本体35aには、後方に向けて開放した後端面にCMOS基板13が複数のネジ37によって固定される(図8)。

【0030】

メイン基板10と電源基板11の位置決めのために、シャーシ30には6つの爪38が一体成形されており(図7)、この6つの爪38を使ってメイン基板10と、これに対向する電源基板11が、シャーシ30の開放した互いに対向する2つの側面30b、30dの夫々に位置決めされる。メイン基板10には爪38を受け入れる切り欠き10aが形成されている(図7)。電源基板11にも同様に切り欠き11aが形成されている(図3)。図7を参照して、矩形のサブ基板12は、対角線上の角隅部に一対の透孔12a、12bを有し、この一対の透孔12a、12bに対応してシャーシ30にも一対の透孔30g(一方の透孔は作図上の理由から図面には現れていない)が形成され、これら透孔12a、12b、30gを整合させることによりサブ基板12はシャーシ30にネジ止めされる。

【0031】

ポインタ用LEDの配置(図10):

カメラモジュール32は円筒状のレンズ組立体36を有し、このレンズ組立体36はカメラホルダ35の一対のアーム35b、35bの間に配設されている。図10を参照して、ホルダ本体35aの後端開口には、CMOS基板13がネジ37(図8)を使って固定される。CMOS基板13には、一対のポインタ用LED40、40が搭載されている。このポインタ用LED40に関連して、ホルダ本体35aには、各ポインタ用LED40の直ぐ前方に拡散シート41が配設されている。2つのポインタ用LED40の光は、夫々、拡散シート41を通じて且つレンズ組立体36を通じて前方に照射され、バーコードリーダ2の視野範囲の中の互いに離間した2点を指し示す。図10の参照符合43は光学読取素子であるCMOSイメージセンサを示し、光学読取素子43はCMOS基板13に実装されている。

【0032】

ポインタ用LED40をカメラモジュール32に内蔵させたことにより、光学読取素子43とポインタ用LED40との相対位置を一定に保つのが容易になると共にバーコードリーダ2を小型化するのが容易になる。特に、ポインタ用LED40がバーコードリーダ2のレンズ組立体36を光学読取素子43と共用することによって、ポインタ用LED40のための専用のレンズが不要となるためバーコードリーダ2の小型化が容易である。

【0033】

カメラモジュール32は、光学読取素子(撮像素子)43とレンズ組立体36との間の距離が従来との対比で非常に大きく、高い分解能でバーコードやQRコードなどの光学情報を超微小な領域まで読み取ることができるという特徴を有している。このように従来との対比で長さ寸法が大きいカメラモジュール32をバーコードリーダ2の中に収容するとき、上述した基板配置に注目すべきである。すなわち、カメラモジュール32をメイン基板10、電源基板11、サブ基板12で囲むという技術的思想を導入することで、バーコードリーダ2を小型化しつつ長尺のカメラモジュール32をアウターケースの中に収容することができる。

【0034】

ちにみに、カメラモジュール32のスペックは次のとおりである。

(1)光学倍率:0.6〜1.0倍(実施例では、0.823倍);

(2)視野範囲:7.5mm×4.8mm〜4.5mm×2.9mm(実施例では、5.5mm×3.5mm);

(3)光学読取素子から先端のレンズまでの距離:35mm以上(実施例では40mm)。

【0035】

図11は、シャーシ30に基板10、11、12及びカメラモジュール32を組み付けた組立体の斜視図である。図12は、メイン基板10、電源基板11の上に、夫々、クッション性を備え且つ優れた熱伝導性を備えた放熱部材として熱伝導ゴム45を設置した状態を示す。バーコードリーダ2の放熱性に関して必要があれば、図12に例示した態様で熱伝導ゴム45を添設した状態で矩形断面のメインケース6(図2)に収容される(図13)。

【0036】

伝熱性に優れた金属材料からなる多角形断面のメインケース6の異なる側面に隣接し且つこれに沿ってメイン基板10と電源基板11を配置したことにより、これらメイン基板10及び電源基板11の熱を外部に放出し易くなると共に、このメイン基板10と電源基板11で囲まれた空間にカメラモジュール32を収容することができるため、バーコードリーダ2の一層の小型化が可能である。特に、メイン基板10、電源基板11とメインケース6との間に熱伝導ゴム45のような放熱部材を介在させることで放熱効率を高めることができ、この観点からもバーコードリーダ2の一層の小型化が可能になる。

【0037】

図13及び図15の参照符合46はリヤケースを示し、メインケース6の後端開口に脱着可能に装着されてメインケース6を閉塞する。リヤケース46にはコネクタ基板15が取付けられており、このコネクタ基板15はリヤケース46にネジ47を使って固定される(図15)。バーコードリーダ2のアウターケースを構成するメインケース6、フロントケース7、リヤケース46は、例えばメインケース6を熱伝導に優れた金属材料、例えばアルミニウムなどの伝熱性材料から作られるのがよい。

【0038】

図6を参照して、メイン基板10及び電源基板11には、その前端幅狭部に夫々透孔50、51を有する。バーコードリーダ2のメインケース6は、円筒状のフロントケース7の内部まで前方に且つ互いに平行に延びるロッド状の一対の延長部分6aを有する(図15)。

【0039】

メインケース6の前端部を抽出した図14を参照して、メインケース6の一対の延長部分6aには、メイン基板10及び電源基板11の前端幅狭部の透孔50、51に関連した透孔52、53が形成され、この透孔52、53に挿入したネジ54を使ってメイン基板10及び電源基板11がメインケース6(延長部分6a)に固定される。これにより、シャーシ30の3つの爪38で位置決めされたメイン基板10、電源基板11は、その各々が、メインケース6の前方に延びる延長部分6aに1本のネジ54によって固定される。換言すれば、この合計2本のネジ54によってシャーシ30がメインケース6に固定された状態となる。ネジ54を締結する作業及びネジ54を取り外す作業を容易にするために、メイン基板10の透孔50及び電源基板11の透孔51に、ネジ54が螺着するナット55を実装するのが好ましい。メインケース6の一対のロッド状の延長部分6aには、また、その前端面にLED基板14がネジ60を使って固定される。このリング状のLED基板14がレンズ組立体36の周囲に配置され、LED基板14に搭載された複数の照明用LED80によって、レンズ組立体36の外周側に位置するリング状の面光源が形成される。

【0040】

図17は、メインケース6を正面から見た図である。メインケース6は、その前端面に左右一対の取付座62を有し、この一対の取付座62を使ってカメラモジュール32がメインケース6に固定される。図16は、メインケース6の中にカメラモジュール32を内蔵させた状態の正面図である、図17は、カメラモジュール32を取り除いた状態で描いたメインケース6の正面図である。

【0041】

金属成型品であるメインケース6にカメラモジュール32を固定することで、カメラモジュール32をシャーシ30に固定するのに比べてカメラモジュール32の位置決め精度を高めて視野範囲の位置決め精度を高めることができる。

【0042】

バーコードリーダ2が内蔵する主要な基板、つまり電源基板10、メイン基板12などと、レンズ組立体36を含むカメラモジュール32とをシャーシに組み付けた組立体をアウターケース(メインケース6)に内蔵させる構成を採用したことにより、複数種類のカメラモジュール32を用意することで同じアウターケースを使って複数種類のバーコードリーダ2をユーザに提供することができる。また、異なる種類のカメラモジュール32に対して、同一の電源基板10やメイン基板12などを採用し且つ同じアウターケースを使ってバーコードリーダ2を製造することができる。

【0043】

前述したカメラモジュール32の左右一対の取付部35cがメインケース6の左右一対の取付座62に着座され、4本のネジ63を使って各取付部35cが、対応する取付座62に固定される(図16)。

【0044】

バーコードリーダ2の機能構成(図18):

図18を参照して、バーコードリーダ2の機能構成を説明する。バーコードリーダ2は、第1、第2のCPU101、102と、共有バス103と、共有メモリ104と、前述した光学読取素子(CMOS)43と、撮像制御回路105と有する。また、バーコードリーダ2は、ネットワークコントローラ106と、シリアル通信コントローラ107と、フラッシュメモリ108と、入出力コントローラ110と、DMAC111とを有している。

【0045】

第1、第2のCPU101、102は、共有バス103を介して、共有メモリ104にアクセスするプロセッサであり、所定の演算処理回路からなる。共有バス103は、第1、第2のCPU101、102に共通のデータバスである。共有メモリ104は、撮像パラメータやデコードパラメータ、読取画像、デコード結果を保持するための揮発性の半導体記憶素子からなり、典型的にはRAM(ランダムアクセスメモリ)である。

【0046】

光学読取素子43は、ワークからの反射光を受光して読取画像を生成する例えばCMOSイメージセンサで構成される。撮像制御回路105は、光学読取素子43からの画像信号を増幅する増幅器、増幅後の画像信号をデジタル信号に変換するA/D変換器などからなり、共有メモリ104内の撮像パラメータ、例えば、露光時間、ゲイン、フィルタ処理の有無に基づいて光学読取素子43を制御する。

【0047】

DMAC(Direct Memory Access Controller:DMAコントローラ)111は、光学読取素子43により生成された読取画像を撮像制御回路105から共有バス103を介して共有メモリ104へ転送する。

【0048】

ネットワークコントローラ106は、LAN112(図1)を介してパーソナルコンピュータ3などの外部機器と通信する通信回路であり、例えば、EMAC(Ethernet Media Access Controller)からなる。シリアル通信コントローラ107は、シリアル通信インターフェースを介して外部機器と通信する通信回路であり、例えば、UART(Universal Asynchronous Receiver Transmitter)からなる。

【0049】

フラッシュメモリ108は、画像ファイルを保持するための不揮発性の半導体記憶素子からなり、例えば、SD(Secure Digital、登録商標)カードなどの着脱可能なメモリカードが用いられる。入出力コントローラ110は、フラッシュメモリ108に対する画像ファイルの書き込み及び読み出しを制御する。

【0050】

第1CPU101は、ネットワークコントローラ106又はシリアル通信コントローラ107がコマンドを受信した場合に、当該コマンドが読み取りを開始させるための読取開始コマンドであれば、撮像制御回路105に対して読取開始を指示する。第1CPU101は、また、光学読取素子43から受け取った読取画像を共有メモリ104に転送する。

【0051】

第2CPU102は、第1CPU101からのデコード処理要求に基づいて、共有メモリ104内から読取画像を読み出してデコード処理するデコード手段を構成する。第2CPU102でデコード処理が終了したら、そのデコード結果を共有メモリ104内に書き込む。

【0052】

第1CPU101では、プログラムに従って実行される、撮像制御、デコード結果の送信制御、読取画像の送信制御、画像ファイルの送信制御などの処理に、その重要度の順に優先順位が割り付けられ、実行待ちの状態のタスクが複数存在するときには、実行待ち状態のタスクのうち優先順位の高いタスクにこの第1CPU101のソースが割り当てられる。

【0053】

図19は、図18のバーコードリーダ2の動作の一例を模式的に示した説明図であり、画像バッファ115及び共有メモリ104に格納されている設定バンク116が示されている。DMAC111により共有メモリ104内に転送された読取画像は、画像バッファ115として保持される。この画像バッファ115は、読取画像を保持するための画像記憶領域117と、読取画像の参照タスク数を保持するためのタスク数記憶領域118と、共有メモリ104に記憶されている設定バンク116を指定するバンク番号を保持するためのバンク番号記憶領域119とからなる。

【0054】

画像記憶領域117には読取画像が格納される。設定バンク116には、撮像パラメータやデコードパラメータなどの各種設定が保持される。これらの撮像パラメータ、デコードパラメータはパーソナルコンピュータ3を使って設定される。設定バンク116は、上述したように、撮像パラメータとデコードパラメータとを含む。

【0055】

共有メモリ104には複数の設定バンク116が記憶されており(図20)、この設定バンク116は第1、第2のCPU101、102によって夫々参照される。バーコードリーダ2は、一つのバンク116に基づいて読み取りを実行して読み取りに失敗したときには、次のバンク116に基づいて読み取りが試行され、この第2のバンク116でも読み取りに失敗したときには、次のバンク116に基づいて読み取りを試行するというように、読み取りが成功するまで次々とバンク116の切り替えが行われる。

【0056】

撮像系の設定パラメータの代表例を挙げれば次の通りである。

(1)照明のON/OFF;

(2)照明の照射強度;

(3)照明の点灯パターン;

(4)露光時間;

(5)ゲイン;

(6)オフセット;

(7)ダイナミックレンジ;

(8)取り込み範囲。

【0057】

読取系の設定パラメータ(デコード設定)の代表例を挙げれば次の通りである。

(1)シンボル(光学情報)の種類;

(2)フィルタ種類;

(3)フィルタ回数;

(4)チルト角;

(5)PPC;

(6)デコードタイムアウト;

(7)取り込み範囲。

【0058】

バーコードリーダ2の撮像シーケンス:

第1CPU101は撮像処理を行うと共に光学読取素子(CMOS)43から転送された読取画像を共有メモリ104に格納する。他方、第2CPU102は共有メモリ104に格納された読取画像に対してデコード処理を行う。この第2CPU102がデコード処理を行っている最中に、これに並行して第1CPU101は次の画像処理を実行する。

【0059】

第1CPU101は、第2CPU102にデコード処理要求を行った後一定時間が経過した時点で次の撮像処理を実行する。上記のデコード処理要求は、第1CPU101が撮像処理を完了したときに行われる。このデコード処理要求から次の撮像処理を実行するまでの時間を撮像間隔P(図21)と呼ぶと、第1CPU101は、1つの撮像処理が完了すると、上記撮像間隔Pとして設定されている時間が経過するのを待って次の撮像処理が実行される。

【0060】

撮像間隔Pは最も好ましくは次のように規定される。

(1)デコードタイムアウト時間Taから撮像時間Tbを引いた値を撮像間隔Pとする(下記の式1)。この撮像間隔Pは、バーコードリーダ2の内部で演算によって求められる。

(式1)P={Ta−Tb}

【0061】

ここに、デコードタイムアウト時間Taは、ユーザによって予め設定された最適値であり、第2CPU102が成功裏にデコード処理に要する合理的な時間である。撮像時間Tbは、露光時間とデータ転送速度で一義的に決まる値であり、データ転送速度は、画像の取り込み範囲の指定によって決まる。

【0062】

上記式1に従って撮像間隔Pを設定したときには、デコードが成功するか否かの見極めがつくまで撮像処理をぎりぎりのタイミングまで待機させることができる。逆に、デコードに失敗した場合にはP<{Ta−Tb}であれば、第2CPU102はデコード待機状態にはならない。しかし、撮像間隔Pが短すぎた場合には、デコードが成功した場合に無駄な撮像処理を行うことになる。このことから、上記式1に基づく撮像間隔Pが最も合理的であるが、P<{Ta−Tb}であればP≒{Ta−Tb}であってもよい。

【0063】

上述の撮像間隔Pは各設定バンク116のパラメータに従って演算され、そして、対応する設定バンク116に記憶される。

【0064】

(2)ユーザが撮像間隔Pを設定する。なお、P>{Ta−Tb}となる撮像間隔Pを設定した場合には、デコードが失敗した場合に、次のデコードを開始するまでに第1CPU101の撮像処理が完了せず、これにより第2CPU102はデコード待機状態に入ってしまうため、典型的には、ユーザは上記式1で求まる撮像間隔Pが設定される第1モードを選択するか、撮像間隔Pが「ゼロ」に設定される連続撮像モードのいずれかを選択することになる。

【0065】

撮像処理及びデコード処理は、図22に示すように各設定バンクを一回だけ使用する第1の方法を採用してもよいし、図23に示すように共通の設定バンクを複数回使用する第2の方法を採用してもよい。すなわち、デコードが成功するまで予め設定した所定回数デコードを実行する場合に、第1の方法(図22)では、次々と異なる設定バンクを使って撮像処理及びデコード処理が実行される。他方、第2の方法(図23)では、所定回数(図23の例では2回)、同じ設定バンクの下で撮像処理及びデコード処理が実行され、その次に、第2設定バンクの下で所定回数撮像処理及びデコード処理が実行され、以後、第3設定バンク、第4設定バンクの下で所定回数撮像処理及びデコード処理が実行される。勿論、設定バンクの数又はデコードの回数は予め設定される。

【0066】

第1具体例(図24):

図24を参照して第1具体例を説明する。この第1具体例は、設定バンク116に登録されている撮像間隔Pを使って撮像処理が実行された例である。設定バンクの撮像間隔Pを使用するかユーザが設定した撮像間隔Pを使用するかはユーザの選択に委ねられる。

【0067】

第1CPU101は、第1設定バンク、第2設定バンク・・・の順で撮像処理が実行され、また、第2CPU102では、第1設定バンク、第2設定バンク・・・の順でデコードが実行される。この図24の例では、第1回目のデコード処理はタイムアウトでキャンセルされ、次の第2回目のデコード処理でデコードが成功している。第2回目のデコード処理は、その前に第1CPU101で第2回目の画像処理が完了しているため、第1回目のデコード処理がキャンセルされた直後から次のデコード処理を開始することができる。

【0068】

この図24の例では、各撮像毎に異なる設定バンクが用いられており、各設定バンクには異なるデコードタイムアウト時間が設定される。デコードタイムアウト時間が異なることから、上記式1で求まる撮像間隔Pも各撮像毎に異なる値となる。これにより、第2CPU102にデコード待機状態が発生しないように各設定バンクに対応した撮像間隔Pを自動的に設定することができる。

【0069】

第2具体例(図25):

図25を参照して第2具体例を説明する。この第2具体例は、第1具体例と同様に、設定バンク116に登録されている撮像間隔Pを使って撮像処理が実行された例である。この第2具体例は、共通の設定バンクで複数回デコード処理を実行した例を示す。図25から分かるように、この具体例2は、第2回目のデコード処理が成功した例である。

【0070】

第3具体例(図26):

図26を参照して第3具体例を説明する。この第3具体例は、設定バンク116に登録されている撮像間隔Pを使って撮像処理が実行された例である。

【0071】

第1CPU101は、第1設定バンク、第2設定バンク、・・の順で撮像処理が実行され、また、第2CPU102では、第1設定バンク、第2設定バンク、・・の順でデコード処理が実行される。この図26の例では、第1回目のデコード処理はタイムアウトでキャンセルされ、次の第2回目のデコード処理が不成功で終わっており、第3回目のデコード処理でデコードが成功している。第2回目、第3回目のデコード処理は、その前に第1CPU101で第2回目、第3回目の画像処理が完了しているため、殆どロスタイム無しにデコード処理を開始できる。換言すると、第1CPU101での画像処理を途中で終了させることなく最後まで画像処理を実行させることができる。したがって、第1CPU101での画像処理を無駄にすることなくデコード処理ができる。

【0072】

第4具体例(図27):

図27を参照して第4具体例を説明する。この第4具体例は、撮像間隔Pが「ゼロ」に設定される連続撮像モードをユーザが選択した例を示す。この連続撮像モードでの例示は、第1回目のデコードがタイムアウトでキャンセルされ、次の第2回目のデコード処理でデコードが成功した例である。撮像間隔Pがゼロであることから、第1CPU101は次々と撮像処理を実行することになる。この連続的に撮像するモードでは、例えば高速で移動してくるワークに対して撮像タイミングが一定であるため、ワークの光学情報の読み取りが安定することから、この安定した読み取りによってデコード成功確率を高めることができるというメリットがある。しかしながら、図27の連続撮像モードでは、第1CPU101は、撮像処理よりも優先順位の低いタスクの実行に遅れがでる。

【0073】

この第4の具体例に対して、撮像間隔Pを設けた場合には、この撮像間隔Pの期間に第1CPU101は、撮像処理よりも優先順位の低いタスクにリソースを割り当てることができる。したがって、撮像間隔Pを設けることで、この期間に優先順位の低いタスクを実行することができる。しかも、撮像間隔Pは、デコードタイムアウト時間(Ta)と撮像処理に要する時間(Tb)に基づいて決定することにより、撮像間隔Pを大きく取りすぎて、第2CPU102にデコード待機状態を発生してしまうのを回避することができる。このように、第1CPU101のリソースを最大限に有効活用しながら、第2CPU102のデコード待機状態の発生を防止することができる。その一方で図27を参照した連続撮像モードを選択できることから、ワークが比較的高速に移動している場合にも対応することができる。

【0074】

なお、実施例の説明では、第1、第2の2つのCPU101、102を備えた構成を前提として説明したが、これを一つのCPUで第1、第2の2つのCPU101、102の処理を実行するようにしてもよい。すなわち、一つのCPUで撮像処理、デコード処理、画像データの送信、画像の保存などの複数のタスクを実行する場合に、デコード待機状態を防ぐために撮像間隔Pを設定するようにしてもよい。一般的に撮像処理は優先順位の高いタスクと考えられており、デコード処理は他のタスクが実行されない比較的低位の優先順位に割り当てられるのが通常である。各撮像結果に対するデコードタイムアウト時間は予めユーザにより設定される。したがって、デコードタイムアウトになるときには次回の撮像処理が完了するように、デコード処理よりも上位の優先順位に割り当てられた撮像処理タスクにCPUの処理を移行させることで、デコードタイムアウトになったタイミングでは撮像処理が完了しているように制御することができる。

【0075】

すなわち、一つのCPUであっても、上述した第1、第2のCPU101、102を用いた実施例と同様に、撮像間隔Pを設けて撮像処理を実行することにより、撮像処理が開始する直前までデコード成功の可否を見極めることができるので、無駄な撮像処理を実行する可能性を極めて小さく抑えることができる。特に、単一のCPUを用いて撮像処理及びデコード処理を行う場合は、デコード処理中にデコード処理よりも優先順位の高い、例えば画像保存タスクなどの別の処理に入った場合には、デコード処理が中断してしまうため、画像処理を連続して行わずに撮像間隔Pを設ける本発明は、できる限りデコード処理にCPUのリソースを割り当てることができるという点で非常に有効である。

【産業上の利用可能性】

【0076】

本発明は光学情報のデコード処理に適用される。

【符号の説明】

【0077】

1 バーコードリーダ・システム

2 バーコードリーダ

3 パーソナルコンピュータ

101 第1CPU

102 第2CPU

103 共有バス

104 共有メモリ

116 設定バンク

【技術分野】

【0001】

本発明は、バーコードやQRコードのような光学情報を読み取ってデコードする光学情報読取装置に関する。

【背景技術】

【0002】

トレーサビリティ(traceability)が普及した今日、工場や物流拠点などに光学情報読取装置を設置して、製品や産品に付与されたバーコードなどの光学情報又は光学符号の解読が行われている。この種の光学情報読取装置は「バーコードリーダ」又は「コードリーダ」と呼ばれている。

【0003】

バーコードリーダはレーザ光、可視光、赤外光を光学情報に照射し、その反射光を光学読取素子(撮像素子)で取り込む。そして、この取り込んだ撮像画像を画像処理して光学情報を抽出した読取画像を作成し、そして、この読取画像のデコードを実行する(特許文献1)。

【0004】

ところで、光学情報読取装置に2つのCPU(プロセッサ)を用意し、この2つのプロセッサで画像処理とデコード処理とを並列処理することが考えられている。この場合、第1のプロセッサで撮像及び画像処理を完了した後、第2のプロセッサに対してデコード処理の要求を行い、このデコード処理要求を受け取った第2のプロセッサはデコード処理を開始する手順で並列処理が実行されることになる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−33465号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

第2プロセッサがデコード処理している最中に、第1プロセッサは次の画像処理を実行することになる。しかし、第2プロセッサのデコード処理が所定時間内に成功しなかった場合には、このデコード処理がキャンセルされ、第1プロセッサは第2プロセッサに対して再度のデコード要求を行うことになるが、このデコード要求を受けたとしても第1プロセッサが画像処理中であれば、第2プロセッサはデコードを開始することができないという問題が発生して第2プロセッサは待機状態に置かれる。

【0007】

一般的に、第1プロセッサには複数のタスクが割り当てられ、重要なタスクから優先順位が付けられて、優先順位の高いタスクを処理している間は、優先順位の低いタスクは実行されずに待機状態にある。バーコードリーダにとって、撮像処理は比較的優先順位の高いタスクとして設定されることから、他のタスク(例えば画像の保存や画像の送信など)は撮像処理が行われていない間に第1プロセッサによって実行される。

【0008】

これに対して第2プロセッサは、第1プロセッサが撮像した画像を受け取ってデコード処理を実行することから、この第2プロセッサにデコード待機状態が発生するのは回避したい。例えば、第1プロセッサが連続的に撮像処理を実行すれば、第2プロセッサのデコード開始時には必ず第1プロセッサの撮像処理を完了させるように制御することは可能である。しかし、第2プロセッサにデコード待機状態が発生するのを防止する目的で第1プロセッサが連続的に撮像処理を実行すると、第1プロセッサに割り当てられている撮像処理以外のタスクの実行が遅れてしまうという他の問題が浮上してしまう。

【0009】

本発明の目的は、第1、第2のプロセッサを備え、第1のプロセッサと第2のプロセッサで画像処理とデコード処理を並列処理する光学情報読取装置を前提として、その処理効率を高めることのできる光学情報読取装置を提供することにある。

本発明の更なる目的は、第1のプロセッサのリソースを最大限に有効活用しながら、第2のプロセッサのデコード待機状態の発生を抑えることのできる光学情報読取装置を提供することにある。

【課題を解決するための手段】

【0010】

上記の技術的課題は、本発明によれば、

光学情報を撮像する光学読取素子と、

撮像パラメータとデコードパラメータとを含む設定バンクを記憶した共有メモリと、

該共有メモリの前記設定バンクの撮像パラメータに従って画像処理して読取画像を生成すると共に生成した読取画像を前記共有メモリに転送する撮像処理を少なくとも含む複数の処理を実行する第1プロセッサと、

該共有メモリに記憶されている前記読取画像を呼び出して、該読取画像を前記共有メモリの前記設定バンクのデコードパラメータに従ってデコード処理する第2プロセッサとを有し、

前記第1プロセッサは、前回の撮像処理が終了した後、撮像処理以外のタスクを実行しながら所定の撮像間隔を待機してから次回の撮像処理を実行し、

前記所定の撮像間隔が、前記第2プロセッサでデコード処理のデコードタイムアウト時間から撮像時間を引いた値と略等しい値に設定されることを特徴とする光学情報読取装置を提供することにより達成される。

【0011】

所定の撮像間隔として、(1)前記第2プロセッサのデコード処理のデコードタイムアウト時間から撮像時間を引いた値であってもよいし、(2)ユーザによって設定された値であってもよい。

【0012】

上記(1)の撮像間隔であれば、デコードが上手く行かずタイムアウトによりキャンセルされた時点では、第1プロセッサによる画像処理が必ず終了していることから、第2プロセッサは、直ちに第1プロセッサが作成した読取画像のデコード処理を開始することができる。

【0013】

上記(2)の撮像間隔は、一般的にユーザが撮像間隔を「ゼロ」に設定すると予想できることから、第1プロセッサによる画像処理が次々と実行されるため、第2プロセッサでデコードが上手く行かずタイムアウトによりキャンセルされた時点では、次にデコードする読取画像が既に存在していることから第2プロセッサは直ちにデコードを開始することができる。

【0014】

本発明の他の目的、作用効果は、以下の本発明の実施例の詳しい説明から明らかになろう。

【図面の簡単な説明】

【0015】

【図1】バーコードリーダ・システムの全体構成図である。

【図2】光学情報読取装置であるバーコードリーダの斜視図である。

【図3】バーコードリーダの内部に配置される各種基板の配置を斜め前方から見た図である。

【図4】図3に関連した図であって、バーコードリーダの内部に配置される各種基板の配置を斜め後方から見た図である。

【図5】バーコードリーダに内蔵される各種基板の結線関係を説明するための図である。

【図6】バーコードリーダに内蔵されるシャーシと、このシャーシに組み付けられたメイン基板、電源基板、サブ基板の配置を説明するための図である。

【図7】シャーシに組み付けられる各種の要素を説明するための図である。

【図8】カメラモジュールを斜め後方から見た図である。

【図9】カメラモジュールを斜め前方から見た図である。

【図10】カメラモジュールの内部構造を説明するための概念図である。

【図11】カメラモジュールと各種基板の関係を示す図であり、この状態でバーコードリーダのメインケースに収容される。

【図12】図11と同様に、カメラモジュールと各種基板の関係を示す図であり、好ましい例として、電源基板、メイン基板の上に放熱部材である熱伝導ゴムを載置した例を示す図である。

【図13】図12に関連して、熱伝導ゴムが電源基板、メイン基板とメインケースとに当接した状態を説明するための図である。

【図14】メインケースから前方に延びる一対のロッド状の延長部分の前端面にLED基板(内部照明基板)を取り付け、また、延長部分に電源基板、メイン基板の前端を固定することを説明するための図である。

【図15】バーコードリーダのメインケース及びその開放した後端がリヤケースによって閉じられることを説明するための図であり、このリヤケースにコネクタ基板を固定した状態を示す分解斜視図である。

【図16】図15に図示の内蔵物を収容したメインケースの正面図である。

【図17】図16からカメラモジュールを取り除いた状態のメインケースの正面図である。

【図18】バーコードリーダの機能構成図である。

【図19】バーコードリーダの画像バッファと共有メモリとの関係を説明するための図である。

【図20】共有メモリに複数の設定バンクが格納されていることを説明するための図である。

【図21】バーコードリーダの第1CPUで実行される撮像処理が撮像間隔毎に実行されることを説明するためのタイムチャートである。

【図22】設定バンクの条件に基づいて撮像処理及びデコード処理する場合に、複数の設定バンクを夫々一回だけ使用して処理する例を説明するための図である。

【図23】設定バンクの条件に基づいて撮像処理及びデコード処理する場合に、複数の設定バンクから一つの設定バンクを複数回使用して処理する例を説明するための図である。

【図24】複数の設定バンクを夫々一回だけ使用して処理した具体例を示すタイムチャートである。

【図25】複数の設定バンクから一つの設定バンクを2回使用して処理した具体例を示すタイムチャートである。

【図26】複数の設定バンクを夫々一回だけ使用して処理した他の具体例を示すタイムチャートである。

【図27】撮像間隔が「ゼロ」(バースト撮像)の連続的に撮像する連続撮像モードでのタイムチャートである。

【発明を実施するための形態】

【実施例】

【0016】

以下に、添付の図面に基づいて本発明の好ましい実施例を説明する。

【0017】

バーコードリーダ・システム(図1):

図1はバーコードリーダ・システムの概要を説明するための図である。図1を参照して、バーコードリーダ・システム1は、二次元情報読取装置であるバーコードリーダ2と、必要に応じてバーコードリーダ2に接続されるパーソナルコンピュータ3とを有し、バーコードリーダ2で撮像した画像をパーソナルコンピュータ3で確認しながら、このパーソナルコンピュータ3を使って各種の設定が行われる。バーコードリーダ・システム1には、更に、必要に応じてリング型の外部照明ユニット4がバーコードリーダ2に接続され、バーコードリーダ2の内部照明ユニット5と一緒になって又は内部照明ユニット5の動作を止めて外部照明ユニット4だけでワークを照明する。

【0018】

リング型の外部照明ユニット4は、このバーコードリーダ・システム1のための専用品であり、異なる種類の複数の外部照明ユニット4を用意するのが好ましい。勿論、外部照明ユニット4として専用品以外の照明ユニットを組み込むことも可能である。

【0019】

バーコードリーダ・システム1は、バーコード、QRコードなどの光学情報又は光学符号が印字又は刻印された商品あるいは物品を製造する工場では物品の搬送経路に設置され、バーコードリーダ2で商品又は物品に印字された光学情報に記録されている情報を読み取り、この情報をパーソナルコンピュータ3に転送して情報の解析が行われる。「光学情報読取装置」は一般的に“バーコードリーダ”又は“コードリーダ”を呼ばれており、ここでは“バーコードリーダ”という業界用語を使用する。

【0020】

また、図示の例では、図1に開示のように、パーソナルコンピュータ3に設定プログラムをインストールすることにより、このパーソナルコンピュータ3を使ってバーコードリーダ・システム1の各種の設定が行われる。勿論、バーコードリーダ2に例えばタッチパネル付き表示手段を設けて、この表示手段を使ってバーコードリーダ2、内部照明ユニット5(図3)及び/又は外部照明4(図20、図21)の設定作業ができるようにしてもよい。

【0021】

バーコードリーダ2(図2〜図19):

図2はバーコードリーダ2の外観を示す斜視図である。バーコードリーダ2は、断面多角形の形状のメインケース6と、メインケース6の前端に固定される円筒状のフロントケース7とを有し、この円筒状のフロントケース7に前述した内部照明ユニット5が内蔵されている。メインケース6は、図2などから分かるように略正方形の断面形状を備えているのが好ましい。

【0022】

バーコードリーダ2には互いに独立した複数の基板が内蔵されている。図3〜図5を参照して、バーコードリーダ2が備える複数の基板は次の通りである。

(1)メイン基板10:

メイン基板10には、CPU、メモリMが搭載され、画像をメモリMに転送してDSP(digital Signal Processor)で画像処理する。そして、メイン基板10のCPUで内部照明ユニット5を具備したバーコードリーダ2を制御し、また、外部照明ユニット4との通信を実行する。

(2)電源基板11:

バーコードリーダ2の電源を生成する。絶縁入出力回路が実装されている。

【0023】

(3)サブ基板12:

大容量メモリが搭載されており、この大容量メモリに取得画像や各種の設定が保存される。制限した大きさ及び形状のメイン基板10では、このメイン基板10に実装することのできなかった要素が実装される。

(4)CMOS基板13(受光基板):

CMOSイメージセンサ(光学読取素子)が実装され、画像を取得してメイン基板10に転送する。ポインタ用のLED40(図10)が搭載される。

【0024】

(5)LED基板14:

内部照明ユニット5を構成する円形開口14aを備えた円板状の基板であり、このLED基板14に複数の照明用LED80が実装され(後に説明する図32)、この複数の照明用LED80の点灯制御を実行する。複数の照明用LED80は、後に説明するバーコードリーダ2のレンズ組立体36の光軸を中心とする複数の径の異なる同心円上に配列される。内部照明ユニット5(LED基板14)に実装された複数の照明用LED80は後に説明するようにエリア分けして点灯制御される。また、このLED基板14には、各エリアに属する複数の照明用LEDに定電流を供給する定電流回路が設けられる。

(6)コネクタ基板15:

外部電源、IO、RS232C、Ethernet(登録商標)、外部照明ユニット4との入出力のインターフェースを構成する基板である。なお、外部照明ユニット4には、電源基板11から電源が供給される。

【0025】

図3、図4を参照して、メイン基板10と電源基板11とは互いに対向して配置され、このメイン基板10と電源基板11の各々の側縁で挟まれた領域に、これらメイン基板10と電源基板11と直交するようにしてサブ基板12が配設されている。サブ基板12とメイン基板10の配置位置を互いに置換してもよい。メイン基板10、電源基板11、サブ基板12は、バーコードリーダ2は矩形断面のメインケース6の4つの側面のうち3つの側面に隣接し且つこの3つの側面の各々に沿って配設される。そして、このメイン基板10、電源基板11、サブ基板12で囲まれた空間にCMOS基板13が位置し、このCMOS基板13は各基板10〜12と直交する一つの鉛直面に配設される。また、このCMOS基板13と平行に且つCMOS基板13を挟んで互いに対峙してLED基板14とコネクタ基板15が位置決めされる。

【0026】

図5は、上述した各基板10〜15の接続関係を説明するための図である。メイン基板10は、電源基板11と第1のFFC20(Flexible Flat Cable)で接続され、サブ基板12と第2のFFC21で接続され、CMOS基板13とFPC(Flexible Printed Circuit)22で接続され、内部照明ユニット4LED基板14と第3のFFC23で接続され、コネクタ基板15と第1のハーネス24で接続されている。電源基板11は、また、内部照明ユニット5のLED基板14と第2のハーネス25で接続され、LED基板14に実装された照明用LEDを発光させるための電源が電源基板11からLED基板14に供給される。電源基板11とコネクタ基板15は、2本のハーネス26、27とFFC28で接続されている。

【0027】

図5を再び参照して、メイン基板10と電源基板11とが略同じ大きさ及び形状を有している点に注目すべきである。換言すれば、メイン基板10は、電源基板11と略同じ大きさ及び形状となるように設計され、この制約のためにメイン基板10に搭載できなかった電子部品がサブ基板12に搭載される。

【0028】

図6、図7を参照して、メイン基板10、電源基板11、サブ基板12、CMOS基板13は、樹脂成型品であるシャーシ30に組み付けられる。シャーシ30は、図7から最も良く分かるように、メインケース6の断面形状とほぼ相似形の略正方形の断面形状を有するボックス形状を有し、このボックス形状の一つの側面30aを閉塞し、他の5つの面を開放した形態を有している。メイン基板10、電源基板11、サブ基板12は、開放した3つの側面10b〜10dに夫々配設される。樹脂成型品のシャーシ30は前後に開放しており、その一端開口30fからカメラモジュール32が挿入され(図7)、シャーシ30の中に挿入されたカメラモジュール32は、その周囲にメイン基板10、電源基板11、サブ基板12が位置し、これらメイン基板10、電源基板11、サブ基板12によってカメラモジュール32が包囲された状態になる。

【0029】

図8、図9を参照して、カメラモジュール32は、アルミニウムなどのダイキャスト品からなるカメラホルダ35を有し、このカメラホルダ35は、矩形断面のホルダ本体35aと、ホルダ本体35aの互いに対向する側面から前方に且つ互いに平行に延びる一対のアーム35bと、一対のアーム35bの前端から互いに離れる方向に延びる一対の取付部35cとを有している。ホルダ本体35aには、後方に向けて開放した後端面にCMOS基板13が複数のネジ37によって固定される(図8)。

【0030】

メイン基板10と電源基板11の位置決めのために、シャーシ30には6つの爪38が一体成形されており(図7)、この6つの爪38を使ってメイン基板10と、これに対向する電源基板11が、シャーシ30の開放した互いに対向する2つの側面30b、30dの夫々に位置決めされる。メイン基板10には爪38を受け入れる切り欠き10aが形成されている(図7)。電源基板11にも同様に切り欠き11aが形成されている(図3)。図7を参照して、矩形のサブ基板12は、対角線上の角隅部に一対の透孔12a、12bを有し、この一対の透孔12a、12bに対応してシャーシ30にも一対の透孔30g(一方の透孔は作図上の理由から図面には現れていない)が形成され、これら透孔12a、12b、30gを整合させることによりサブ基板12はシャーシ30にネジ止めされる。

【0031】

ポインタ用LEDの配置(図10):

カメラモジュール32は円筒状のレンズ組立体36を有し、このレンズ組立体36はカメラホルダ35の一対のアーム35b、35bの間に配設されている。図10を参照して、ホルダ本体35aの後端開口には、CMOS基板13がネジ37(図8)を使って固定される。CMOS基板13には、一対のポインタ用LED40、40が搭載されている。このポインタ用LED40に関連して、ホルダ本体35aには、各ポインタ用LED40の直ぐ前方に拡散シート41が配設されている。2つのポインタ用LED40の光は、夫々、拡散シート41を通じて且つレンズ組立体36を通じて前方に照射され、バーコードリーダ2の視野範囲の中の互いに離間した2点を指し示す。図10の参照符合43は光学読取素子であるCMOSイメージセンサを示し、光学読取素子43はCMOS基板13に実装されている。

【0032】

ポインタ用LED40をカメラモジュール32に内蔵させたことにより、光学読取素子43とポインタ用LED40との相対位置を一定に保つのが容易になると共にバーコードリーダ2を小型化するのが容易になる。特に、ポインタ用LED40がバーコードリーダ2のレンズ組立体36を光学読取素子43と共用することによって、ポインタ用LED40のための専用のレンズが不要となるためバーコードリーダ2の小型化が容易である。

【0033】

カメラモジュール32は、光学読取素子(撮像素子)43とレンズ組立体36との間の距離が従来との対比で非常に大きく、高い分解能でバーコードやQRコードなどの光学情報を超微小な領域まで読み取ることができるという特徴を有している。このように従来との対比で長さ寸法が大きいカメラモジュール32をバーコードリーダ2の中に収容するとき、上述した基板配置に注目すべきである。すなわち、カメラモジュール32をメイン基板10、電源基板11、サブ基板12で囲むという技術的思想を導入することで、バーコードリーダ2を小型化しつつ長尺のカメラモジュール32をアウターケースの中に収容することができる。

【0034】

ちにみに、カメラモジュール32のスペックは次のとおりである。

(1)光学倍率:0.6〜1.0倍(実施例では、0.823倍);

(2)視野範囲:7.5mm×4.8mm〜4.5mm×2.9mm(実施例では、5.5mm×3.5mm);

(3)光学読取素子から先端のレンズまでの距離:35mm以上(実施例では40mm)。

【0035】

図11は、シャーシ30に基板10、11、12及びカメラモジュール32を組み付けた組立体の斜視図である。図12は、メイン基板10、電源基板11の上に、夫々、クッション性を備え且つ優れた熱伝導性を備えた放熱部材として熱伝導ゴム45を設置した状態を示す。バーコードリーダ2の放熱性に関して必要があれば、図12に例示した態様で熱伝導ゴム45を添設した状態で矩形断面のメインケース6(図2)に収容される(図13)。

【0036】

伝熱性に優れた金属材料からなる多角形断面のメインケース6の異なる側面に隣接し且つこれに沿ってメイン基板10と電源基板11を配置したことにより、これらメイン基板10及び電源基板11の熱を外部に放出し易くなると共に、このメイン基板10と電源基板11で囲まれた空間にカメラモジュール32を収容することができるため、バーコードリーダ2の一層の小型化が可能である。特に、メイン基板10、電源基板11とメインケース6との間に熱伝導ゴム45のような放熱部材を介在させることで放熱効率を高めることができ、この観点からもバーコードリーダ2の一層の小型化が可能になる。

【0037】

図13及び図15の参照符合46はリヤケースを示し、メインケース6の後端開口に脱着可能に装着されてメインケース6を閉塞する。リヤケース46にはコネクタ基板15が取付けられており、このコネクタ基板15はリヤケース46にネジ47を使って固定される(図15)。バーコードリーダ2のアウターケースを構成するメインケース6、フロントケース7、リヤケース46は、例えばメインケース6を熱伝導に優れた金属材料、例えばアルミニウムなどの伝熱性材料から作られるのがよい。

【0038】

図6を参照して、メイン基板10及び電源基板11には、その前端幅狭部に夫々透孔50、51を有する。バーコードリーダ2のメインケース6は、円筒状のフロントケース7の内部まで前方に且つ互いに平行に延びるロッド状の一対の延長部分6aを有する(図15)。

【0039】

メインケース6の前端部を抽出した図14を参照して、メインケース6の一対の延長部分6aには、メイン基板10及び電源基板11の前端幅狭部の透孔50、51に関連した透孔52、53が形成され、この透孔52、53に挿入したネジ54を使ってメイン基板10及び電源基板11がメインケース6(延長部分6a)に固定される。これにより、シャーシ30の3つの爪38で位置決めされたメイン基板10、電源基板11は、その各々が、メインケース6の前方に延びる延長部分6aに1本のネジ54によって固定される。換言すれば、この合計2本のネジ54によってシャーシ30がメインケース6に固定された状態となる。ネジ54を締結する作業及びネジ54を取り外す作業を容易にするために、メイン基板10の透孔50及び電源基板11の透孔51に、ネジ54が螺着するナット55を実装するのが好ましい。メインケース6の一対のロッド状の延長部分6aには、また、その前端面にLED基板14がネジ60を使って固定される。このリング状のLED基板14がレンズ組立体36の周囲に配置され、LED基板14に搭載された複数の照明用LED80によって、レンズ組立体36の外周側に位置するリング状の面光源が形成される。

【0040】

図17は、メインケース6を正面から見た図である。メインケース6は、その前端面に左右一対の取付座62を有し、この一対の取付座62を使ってカメラモジュール32がメインケース6に固定される。図16は、メインケース6の中にカメラモジュール32を内蔵させた状態の正面図である、図17は、カメラモジュール32を取り除いた状態で描いたメインケース6の正面図である。

【0041】

金属成型品であるメインケース6にカメラモジュール32を固定することで、カメラモジュール32をシャーシ30に固定するのに比べてカメラモジュール32の位置決め精度を高めて視野範囲の位置決め精度を高めることができる。

【0042】

バーコードリーダ2が内蔵する主要な基板、つまり電源基板10、メイン基板12などと、レンズ組立体36を含むカメラモジュール32とをシャーシに組み付けた組立体をアウターケース(メインケース6)に内蔵させる構成を採用したことにより、複数種類のカメラモジュール32を用意することで同じアウターケースを使って複数種類のバーコードリーダ2をユーザに提供することができる。また、異なる種類のカメラモジュール32に対して、同一の電源基板10やメイン基板12などを採用し且つ同じアウターケースを使ってバーコードリーダ2を製造することができる。

【0043】

前述したカメラモジュール32の左右一対の取付部35cがメインケース6の左右一対の取付座62に着座され、4本のネジ63を使って各取付部35cが、対応する取付座62に固定される(図16)。

【0044】

バーコードリーダ2の機能構成(図18):

図18を参照して、バーコードリーダ2の機能構成を説明する。バーコードリーダ2は、第1、第2のCPU101、102と、共有バス103と、共有メモリ104と、前述した光学読取素子(CMOS)43と、撮像制御回路105と有する。また、バーコードリーダ2は、ネットワークコントローラ106と、シリアル通信コントローラ107と、フラッシュメモリ108と、入出力コントローラ110と、DMAC111とを有している。

【0045】

第1、第2のCPU101、102は、共有バス103を介して、共有メモリ104にアクセスするプロセッサであり、所定の演算処理回路からなる。共有バス103は、第1、第2のCPU101、102に共通のデータバスである。共有メモリ104は、撮像パラメータやデコードパラメータ、読取画像、デコード結果を保持するための揮発性の半導体記憶素子からなり、典型的にはRAM(ランダムアクセスメモリ)である。

【0046】

光学読取素子43は、ワークからの反射光を受光して読取画像を生成する例えばCMOSイメージセンサで構成される。撮像制御回路105は、光学読取素子43からの画像信号を増幅する増幅器、増幅後の画像信号をデジタル信号に変換するA/D変換器などからなり、共有メモリ104内の撮像パラメータ、例えば、露光時間、ゲイン、フィルタ処理の有無に基づいて光学読取素子43を制御する。

【0047】

DMAC(Direct Memory Access Controller:DMAコントローラ)111は、光学読取素子43により生成された読取画像を撮像制御回路105から共有バス103を介して共有メモリ104へ転送する。

【0048】

ネットワークコントローラ106は、LAN112(図1)を介してパーソナルコンピュータ3などの外部機器と通信する通信回路であり、例えば、EMAC(Ethernet Media Access Controller)からなる。シリアル通信コントローラ107は、シリアル通信インターフェースを介して外部機器と通信する通信回路であり、例えば、UART(Universal Asynchronous Receiver Transmitter)からなる。

【0049】

フラッシュメモリ108は、画像ファイルを保持するための不揮発性の半導体記憶素子からなり、例えば、SD(Secure Digital、登録商標)カードなどの着脱可能なメモリカードが用いられる。入出力コントローラ110は、フラッシュメモリ108に対する画像ファイルの書き込み及び読み出しを制御する。

【0050】

第1CPU101は、ネットワークコントローラ106又はシリアル通信コントローラ107がコマンドを受信した場合に、当該コマンドが読み取りを開始させるための読取開始コマンドであれば、撮像制御回路105に対して読取開始を指示する。第1CPU101は、また、光学読取素子43から受け取った読取画像を共有メモリ104に転送する。

【0051】

第2CPU102は、第1CPU101からのデコード処理要求に基づいて、共有メモリ104内から読取画像を読み出してデコード処理するデコード手段を構成する。第2CPU102でデコード処理が終了したら、そのデコード結果を共有メモリ104内に書き込む。

【0052】

第1CPU101では、プログラムに従って実行される、撮像制御、デコード結果の送信制御、読取画像の送信制御、画像ファイルの送信制御などの処理に、その重要度の順に優先順位が割り付けられ、実行待ちの状態のタスクが複数存在するときには、実行待ち状態のタスクのうち優先順位の高いタスクにこの第1CPU101のソースが割り当てられる。

【0053】

図19は、図18のバーコードリーダ2の動作の一例を模式的に示した説明図であり、画像バッファ115及び共有メモリ104に格納されている設定バンク116が示されている。DMAC111により共有メモリ104内に転送された読取画像は、画像バッファ115として保持される。この画像バッファ115は、読取画像を保持するための画像記憶領域117と、読取画像の参照タスク数を保持するためのタスク数記憶領域118と、共有メモリ104に記憶されている設定バンク116を指定するバンク番号を保持するためのバンク番号記憶領域119とからなる。

【0054】

画像記憶領域117には読取画像が格納される。設定バンク116には、撮像パラメータやデコードパラメータなどの各種設定が保持される。これらの撮像パラメータ、デコードパラメータはパーソナルコンピュータ3を使って設定される。設定バンク116は、上述したように、撮像パラメータとデコードパラメータとを含む。

【0055】

共有メモリ104には複数の設定バンク116が記憶されており(図20)、この設定バンク116は第1、第2のCPU101、102によって夫々参照される。バーコードリーダ2は、一つのバンク116に基づいて読み取りを実行して読み取りに失敗したときには、次のバンク116に基づいて読み取りが試行され、この第2のバンク116でも読み取りに失敗したときには、次のバンク116に基づいて読み取りを試行するというように、読み取りが成功するまで次々とバンク116の切り替えが行われる。

【0056】

撮像系の設定パラメータの代表例を挙げれば次の通りである。

(1)照明のON/OFF;

(2)照明の照射強度;

(3)照明の点灯パターン;

(4)露光時間;

(5)ゲイン;

(6)オフセット;

(7)ダイナミックレンジ;

(8)取り込み範囲。

【0057】

読取系の設定パラメータ(デコード設定)の代表例を挙げれば次の通りである。

(1)シンボル(光学情報)の種類;

(2)フィルタ種類;

(3)フィルタ回数;

(4)チルト角;

(5)PPC;

(6)デコードタイムアウト;

(7)取り込み範囲。

【0058】

バーコードリーダ2の撮像シーケンス:

第1CPU101は撮像処理を行うと共に光学読取素子(CMOS)43から転送された読取画像を共有メモリ104に格納する。他方、第2CPU102は共有メモリ104に格納された読取画像に対してデコード処理を行う。この第2CPU102がデコード処理を行っている最中に、これに並行して第1CPU101は次の画像処理を実行する。

【0059】

第1CPU101は、第2CPU102にデコード処理要求を行った後一定時間が経過した時点で次の撮像処理を実行する。上記のデコード処理要求は、第1CPU101が撮像処理を完了したときに行われる。このデコード処理要求から次の撮像処理を実行するまでの時間を撮像間隔P(図21)と呼ぶと、第1CPU101は、1つの撮像処理が完了すると、上記撮像間隔Pとして設定されている時間が経過するのを待って次の撮像処理が実行される。

【0060】

撮像間隔Pは最も好ましくは次のように規定される。

(1)デコードタイムアウト時間Taから撮像時間Tbを引いた値を撮像間隔Pとする(下記の式1)。この撮像間隔Pは、バーコードリーダ2の内部で演算によって求められる。

(式1)P={Ta−Tb}

【0061】

ここに、デコードタイムアウト時間Taは、ユーザによって予め設定された最適値であり、第2CPU102が成功裏にデコード処理に要する合理的な時間である。撮像時間Tbは、露光時間とデータ転送速度で一義的に決まる値であり、データ転送速度は、画像の取り込み範囲の指定によって決まる。

【0062】

上記式1に従って撮像間隔Pを設定したときには、デコードが成功するか否かの見極めがつくまで撮像処理をぎりぎりのタイミングまで待機させることができる。逆に、デコードに失敗した場合にはP<{Ta−Tb}であれば、第2CPU102はデコード待機状態にはならない。しかし、撮像間隔Pが短すぎた場合には、デコードが成功した場合に無駄な撮像処理を行うことになる。このことから、上記式1に基づく撮像間隔Pが最も合理的であるが、P<{Ta−Tb}であればP≒{Ta−Tb}であってもよい。

【0063】

上述の撮像間隔Pは各設定バンク116のパラメータに従って演算され、そして、対応する設定バンク116に記憶される。

【0064】

(2)ユーザが撮像間隔Pを設定する。なお、P>{Ta−Tb}となる撮像間隔Pを設定した場合には、デコードが失敗した場合に、次のデコードを開始するまでに第1CPU101の撮像処理が完了せず、これにより第2CPU102はデコード待機状態に入ってしまうため、典型的には、ユーザは上記式1で求まる撮像間隔Pが設定される第1モードを選択するか、撮像間隔Pが「ゼロ」に設定される連続撮像モードのいずれかを選択することになる。

【0065】

撮像処理及びデコード処理は、図22に示すように各設定バンクを一回だけ使用する第1の方法を採用してもよいし、図23に示すように共通の設定バンクを複数回使用する第2の方法を採用してもよい。すなわち、デコードが成功するまで予め設定した所定回数デコードを実行する場合に、第1の方法(図22)では、次々と異なる設定バンクを使って撮像処理及びデコード処理が実行される。他方、第2の方法(図23)では、所定回数(図23の例では2回)、同じ設定バンクの下で撮像処理及びデコード処理が実行され、その次に、第2設定バンクの下で所定回数撮像処理及びデコード処理が実行され、以後、第3設定バンク、第4設定バンクの下で所定回数撮像処理及びデコード処理が実行される。勿論、設定バンクの数又はデコードの回数は予め設定される。

【0066】

第1具体例(図24):

図24を参照して第1具体例を説明する。この第1具体例は、設定バンク116に登録されている撮像間隔Pを使って撮像処理が実行された例である。設定バンクの撮像間隔Pを使用するかユーザが設定した撮像間隔Pを使用するかはユーザの選択に委ねられる。

【0067】

第1CPU101は、第1設定バンク、第2設定バンク・・・の順で撮像処理が実行され、また、第2CPU102では、第1設定バンク、第2設定バンク・・・の順でデコードが実行される。この図24の例では、第1回目のデコード処理はタイムアウトでキャンセルされ、次の第2回目のデコード処理でデコードが成功している。第2回目のデコード処理は、その前に第1CPU101で第2回目の画像処理が完了しているため、第1回目のデコード処理がキャンセルされた直後から次のデコード処理を開始することができる。

【0068】

この図24の例では、各撮像毎に異なる設定バンクが用いられており、各設定バンクには異なるデコードタイムアウト時間が設定される。デコードタイムアウト時間が異なることから、上記式1で求まる撮像間隔Pも各撮像毎に異なる値となる。これにより、第2CPU102にデコード待機状態が発生しないように各設定バンクに対応した撮像間隔Pを自動的に設定することができる。

【0069】

第2具体例(図25):

図25を参照して第2具体例を説明する。この第2具体例は、第1具体例と同様に、設定バンク116に登録されている撮像間隔Pを使って撮像処理が実行された例である。この第2具体例は、共通の設定バンクで複数回デコード処理を実行した例を示す。図25から分かるように、この具体例2は、第2回目のデコード処理が成功した例である。

【0070】

第3具体例(図26):

図26を参照して第3具体例を説明する。この第3具体例は、設定バンク116に登録されている撮像間隔Pを使って撮像処理が実行された例である。

【0071】

第1CPU101は、第1設定バンク、第2設定バンク、・・の順で撮像処理が実行され、また、第2CPU102では、第1設定バンク、第2設定バンク、・・の順でデコード処理が実行される。この図26の例では、第1回目のデコード処理はタイムアウトでキャンセルされ、次の第2回目のデコード処理が不成功で終わっており、第3回目のデコード処理でデコードが成功している。第2回目、第3回目のデコード処理は、その前に第1CPU101で第2回目、第3回目の画像処理が完了しているため、殆どロスタイム無しにデコード処理を開始できる。換言すると、第1CPU101での画像処理を途中で終了させることなく最後まで画像処理を実行させることができる。したがって、第1CPU101での画像処理を無駄にすることなくデコード処理ができる。

【0072】

第4具体例(図27):

図27を参照して第4具体例を説明する。この第4具体例は、撮像間隔Pが「ゼロ」に設定される連続撮像モードをユーザが選択した例を示す。この連続撮像モードでの例示は、第1回目のデコードがタイムアウトでキャンセルされ、次の第2回目のデコード処理でデコードが成功した例である。撮像間隔Pがゼロであることから、第1CPU101は次々と撮像処理を実行することになる。この連続的に撮像するモードでは、例えば高速で移動してくるワークに対して撮像タイミングが一定であるため、ワークの光学情報の読み取りが安定することから、この安定した読み取りによってデコード成功確率を高めることができるというメリットがある。しかしながら、図27の連続撮像モードでは、第1CPU101は、撮像処理よりも優先順位の低いタスクの実行に遅れがでる。

【0073】

この第4の具体例に対して、撮像間隔Pを設けた場合には、この撮像間隔Pの期間に第1CPU101は、撮像処理よりも優先順位の低いタスクにリソースを割り当てることができる。したがって、撮像間隔Pを設けることで、この期間に優先順位の低いタスクを実行することができる。しかも、撮像間隔Pは、デコードタイムアウト時間(Ta)と撮像処理に要する時間(Tb)に基づいて決定することにより、撮像間隔Pを大きく取りすぎて、第2CPU102にデコード待機状態を発生してしまうのを回避することができる。このように、第1CPU101のリソースを最大限に有効活用しながら、第2CPU102のデコード待機状態の発生を防止することができる。その一方で図27を参照した連続撮像モードを選択できることから、ワークが比較的高速に移動している場合にも対応することができる。

【0074】

なお、実施例の説明では、第1、第2の2つのCPU101、102を備えた構成を前提として説明したが、これを一つのCPUで第1、第2の2つのCPU101、102の処理を実行するようにしてもよい。すなわち、一つのCPUで撮像処理、デコード処理、画像データの送信、画像の保存などの複数のタスクを実行する場合に、デコード待機状態を防ぐために撮像間隔Pを設定するようにしてもよい。一般的に撮像処理は優先順位の高いタスクと考えられており、デコード処理は他のタスクが実行されない比較的低位の優先順位に割り当てられるのが通常である。各撮像結果に対するデコードタイムアウト時間は予めユーザにより設定される。したがって、デコードタイムアウトになるときには次回の撮像処理が完了するように、デコード処理よりも上位の優先順位に割り当てられた撮像処理タスクにCPUの処理を移行させることで、デコードタイムアウトになったタイミングでは撮像処理が完了しているように制御することができる。

【0075】

すなわち、一つのCPUであっても、上述した第1、第2のCPU101、102を用いた実施例と同様に、撮像間隔Pを設けて撮像処理を実行することにより、撮像処理が開始する直前までデコード成功の可否を見極めることができるので、無駄な撮像処理を実行する可能性を極めて小さく抑えることができる。特に、単一のCPUを用いて撮像処理及びデコード処理を行う場合は、デコード処理中にデコード処理よりも優先順位の高い、例えば画像保存タスクなどの別の処理に入った場合には、デコード処理が中断してしまうため、画像処理を連続して行わずに撮像間隔Pを設ける本発明は、できる限りデコード処理にCPUのリソースを割り当てることができるという点で非常に有効である。

【産業上の利用可能性】

【0076】

本発明は光学情報のデコード処理に適用される。

【符号の説明】

【0077】

1 バーコードリーダ・システム

2 バーコードリーダ

3 パーソナルコンピュータ

101 第1CPU

102 第2CPU

103 共有バス

104 共有メモリ

116 設定バンク

【特許請求の範囲】

【請求項1】

光学情報を撮像する光学読取素子と、

撮像パラメータとデコードパラメータとを含む設定バンクを記憶した共有メモリと、

該共有メモリの前記設定バンクの撮像パラメータに従って画像処理して読取画像を生成すると共に生成した読取画像を前記共有メモリに転送する撮像処理を少なくとも含む複数の処理を実行する第1プロセッサと、

該共有メモリに記憶されている前記読取画像を呼び出して、該読取画像を前記共有メモリの前記設定バンクのデコードパラメータに従ってデコード処理する第2プロセッサとを有し、

前記第1プロセッサは、前回の撮像処理が終了した後、撮像処理以外のタスクを実行しながら所定の撮像間隔を待機してから次回の撮像処理を実行し、

前記所定の撮像間隔が、前記第2プロセッサでデコード処理のデコードタイムアウト時間から撮像時間を引いた値と略等しい値に設定されることを特徴とする光学情報読取装置。

【請求項2】

前記所定の撮像間隔が、前記第2プロセッサのデコード処理のデコードタイムアウト時間から撮像時間を引いた値である、請求項1に記載の光学情報読取装置。

【請求項3】

前記所定の撮像間隔を設定せずに、連続的に撮像処理を事項する連続撮像モードを更に有し、該連続撮像モードをユーザが選択可能である、請求項1に記載の光学情報読取装置。

【請求項4】

前記所定の撮像間隔が前記設定バンクに含まれ、該設定バンクに含まれている前記撮像間隔に従って前記第1プロセッサの画像処理が実行される、請求項2に記載の光学情報読取装置。

【請求項5】

前記共有メモリに複数の設定バンクが記憶されている、請求項4に記載の光学情報読取装置。

【請求項6】

前記複数の設定バンクの一つの設定バンクを一回だけ使用して前記画像処理及び前記デコード処理が実行される、請求項5に記載の光学情報読取装置。

【請求項7】

前記複数の設定バンクの一つの設定バンクを複数回使用して前記画像処理及び前記デコード処理が実行される、請求項5に記載の光学情報読取装置。

【請求項1】

光学情報を撮像する光学読取素子と、

撮像パラメータとデコードパラメータとを含む設定バンクを記憶した共有メモリと、

該共有メモリの前記設定バンクの撮像パラメータに従って画像処理して読取画像を生成すると共に生成した読取画像を前記共有メモリに転送する撮像処理を少なくとも含む複数の処理を実行する第1プロセッサと、

該共有メモリに記憶されている前記読取画像を呼び出して、該読取画像を前記共有メモリの前記設定バンクのデコードパラメータに従ってデコード処理する第2プロセッサとを有し、

前記第1プロセッサは、前回の撮像処理が終了した後、撮像処理以外のタスクを実行しながら所定の撮像間隔を待機してから次回の撮像処理を実行し、

前記所定の撮像間隔が、前記第2プロセッサでデコード処理のデコードタイムアウト時間から撮像時間を引いた値と略等しい値に設定されることを特徴とする光学情報読取装置。

【請求項2】

前記所定の撮像間隔が、前記第2プロセッサのデコード処理のデコードタイムアウト時間から撮像時間を引いた値である、請求項1に記載の光学情報読取装置。

【請求項3】

前記所定の撮像間隔を設定せずに、連続的に撮像処理を事項する連続撮像モードを更に有し、該連続撮像モードをユーザが選択可能である、請求項1に記載の光学情報読取装置。

【請求項4】

前記所定の撮像間隔が前記設定バンクに含まれ、該設定バンクに含まれている前記撮像間隔に従って前記第1プロセッサの画像処理が実行される、請求項2に記載の光学情報読取装置。

【請求項5】

前記共有メモリに複数の設定バンクが記憶されている、請求項4に記載の光学情報読取装置。

【請求項6】

前記複数の設定バンクの一つの設定バンクを一回だけ使用して前記画像処理及び前記デコード処理が実行される、請求項5に記載の光学情報読取装置。

【請求項7】

前記複数の設定バンクの一つの設定バンクを複数回使用して前記画像処理及び前記デコード処理が実行される、請求項5に記載の光学情報読取装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【公開番号】特開2012−64178(P2012−64178A)

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願番号】特願2010−210253(P2010−210253)

【出願日】平成22年9月17日(2010.9.17)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.QRコード

【出願人】(000129253)株式会社キーエンス (681)

【Fターム(参考)】

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願日】平成22年9月17日(2010.9.17)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.QRコード

【出願人】(000129253)株式会社キーエンス (681)

【Fターム(参考)】

[ Back to top ]