分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、分子メモリ装置の製造方法に関する。

【背景技術】

【0002】

従来より、大容量な不揮発性記憶装置として、NAND型フラッシュメモリが知られている。これまでNAND型フラッシュメモリは、微細化により大容量化及び低コスト化を実現してきた。しかしながら、NAND型フラッシュメモリの微細化は限界に近づいている。そこで、近年、NAND型フラッシュメモリ以外の記憶装置の開発が進められている。

【0003】

その一つとして、メモリ素子として分子を用いた分子メモリ装置が提案されている。分子メモリ装置においては、下層電極と上層電極との間に分子が配置されており、分子の状態を制御することによって、下層電極と上層電極との間の電気抵抗値を異ならせて、データを記憶する。このような分子メモリ装置の記憶密度を増加させるためには、クロスポイント構造を作製してメモリ素子を3次元的に積層させることが効果的である。しかしながら、メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置を製造することは困難である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許出願公開第2007/0045615号明細書

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供することである。

【課題を解決するための手段】

【0006】

実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって、前記第2配線間に、前記犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記配線層に接するように形成する工程と、前記犠牲膜を除去することにより、ギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、を備える。

【図面の簡単な説明】

【0007】

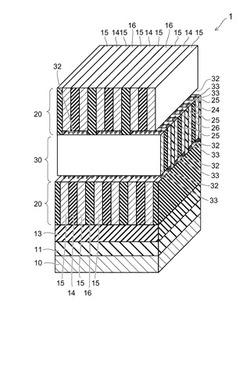

【図1】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図2】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図3】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図4】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図5】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図6】実施形態に係る分子メモリ装置の製造方法を例示する工程断面図である。

【図7】実施形態に係る分子メモリ装置の製造方法を例示する工程断面図である。

【図8】実施形態に係る分子メモリ装置の製造方法を例示する工程断面図である。

【図9】実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図10】(a)はエアギャップとビアホールとの関係を例示する模式的平面図であり、(b)はその模式的断面図である。

【図11】実施形態に係る分子メモリ装置を例示する斜視図である。

【図12】実施形態に係る分子メモリ装置を例示する断面図である。

【図13】(a)及び(b)は、実施形態に係る分子メモリ装置を例示する断面図である。

【図14】実施形態に係る分子メモリ装置の導電部分を例示する斜視図である。

【発明を実施するための形態】

【0008】

以下、図面を参照しつつ、本発明の実施形態について説明する。

図1(a)及び(b)、図2(a)及び(b)、図3(a)及び(b)、図4(a)及び(b)、図5(a)及び(b)は、本実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図であり、

図6〜図8は、本実施形態に係る分子メモリ装置の製造方法を例示する工程断面図であり、

図9は、本実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図であり、

図10(a)はエアギャップとビアホールとの関係を例示する模式的平面図であり、(b)はその模式的断面図であり、

図11は、本実施形態に係る分子メモリ装置を例示する斜視図であり、

図12並びに図13(a)及び(b)は、本実施形態に係る分子メモリ装置を例示する断面図であり、

図14は、本実施形態に係る分子メモリ装置の導電部分を例示する斜視図である。

【0009】

なお、図1〜図6、図9、図11、図13は、メモリセルが形成されるクロスポイント構造部を示し、

図7、図8、図12は、ビアコンタクトの周辺を示し、

図10及び図14は、クロスポイント構造部及びビアコンタクトの双方を示す。

本実施形態は、分子メモリ装置の製造方法の実施形態である。

【0010】

先ず、図1(a)に示すように、シリコン基板10を用意する。次に、シリコン基板10の上面にnチャネル形MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:金属酸化物半導体電界効果トランジスタ)(NMOS)及びpチャネル形MOSFET(PMOS)を形成する。次に、シリコン基板10上に多層配線層11を形成する。これにより、シリコン基板10及び多層配線層11に、NMOS及びPMOSを組み合わせた駆動回路(図示せず)が形成される。多層配線層11上には、駆動回路に接続された電極パッド12(図7参照)を形成する。なお、後述する図1(b)〜図5(b)においては、シリコン基板10及び多層配線層11を省略している。

【0011】

次に、多層配線層11上に、層間絶縁膜として、例えばLPCVD(Low Pressure Chemical Vapor Deposition:低圧化学気相成長)法により、シリコン酸化膜13を形成する。次に、例えばLPCVD法又はPCVD(Plasma CVD:プラズマCVD)法により、シリコン窒化膜を形成する。次に、リソグラフィー法を用いて、シリコン窒化膜上に、フォトレジストのLS(ラインアンドスペース)パターン(図示せず)を形成する。このとき、LSパターンの配列周期をaとする。次に、このフォトレジストをマスクとしてRIE(Reactive Ion Etching:反応性イオンエッチング)等の異方性エッチングを施し、シリコン窒化膜をLSパターンに加工する。これにより、シリコン酸化膜13上に、一方向に延び、周期的に配列された複数本のライン状のシリコン窒化部材14が形成される。

【0012】

次に、シリコン窒化部材14をスリミングし、幅を細くする。例えば、各シリコン窒化部材14の幅を(1/4)aとし、隣り合うシリコン窒化部材14間の距離、すなわち、スペース領域の幅を(3/4)aとする。これにより、後の工程において、配線の幅とスペースの幅が等しくなる。

【0013】

次に、図1(b)に示すように、例えばCVD法により、金属膜を全面に均一な膜厚で成膜する。このとき、金属膜の膜厚は(1/4)aとする。金属膜の材料には、例えば、CVD法によって容易に成膜できるタングステンを用いる。また、金属膜の材料によっては、金属膜を成膜する前に、シード層を形成してもよい。このシード層は、金属の拡散を抑制するバリアメタル層としても機能する。例えば、金属膜の材料をタングステンとする場合は、シード層の材料はチタン窒化物とすることができる。

【0014】

次に、RIEを行い、金属膜をエッチバックする。これにより、金属膜のうち、シリコン酸化膜13の上面上に形成された部分及びシリコン窒化部材14の上面上に形成された部分が除去され、シリコン窒化部材14の側面上に形成された部分が残留する。この結果、シリコン窒化部材14の側面上に、金属からなり、幅が約(1/4)aのスペーサ形状のメタル配線15が形成される。このとき、メタル配線15間のスペース領域の幅も約(1/4)aとなる。なお、上述のシード層を形成した場合は、金属膜を加工する際に、スペース領域からシード層も除去する。

【0015】

次に、図2(a)に示すように、異方性CVD法、例えば、HDP(High Density Plasma:高密度プラズマ)−CVD法によりシリコン酸化物を堆積させて、シリコン窒化部材14及びメタル配線15を覆うように、全面にシリコン酸化膜を成膜する。次に、シリコン窒化部材14及びメタル配線15をストッパとした平坦化処理、例えばCMP(Chemical Mechanical Polishing:化学的機械研磨)を施すことにより、シリコン酸化膜におけるシリコン窒化部材14及びメタル配線15の上面上に形成された部分を除去する。これにより、隣り合うシリコン窒化部材14間であって、メタル配線15間の空間に、シリコン酸化部材16が埋め込まれる。このようにして、シリコン窒化部材14、メタル配線15及びシリコン酸化部材16からなる配線層20が形成される。なお、上述の如く、メタル配線15間のスペース領域の幅は約(1/4)aであるから、メタル配線15間に埋め込まれたシリコン酸化部材16の幅も、約(1/4)aとなる。

【0016】

次に、図2(b)に示すように、配線層20上に、例えば、ランタンアルミニウムシリケート(LaAlSiO)からなる犠牲膜21を形成する。犠牲膜21は、後の工程において除去されることにより、メモリ材料となる分子が配置されるためのエアギャップとなる。犠牲膜21の膜厚は、後述する分子材料33(図11参照)の長さとほぼ等しくする。また、犠牲膜21の材料は、他の材料との間で十分な選択比をもつウェットエッチングによって除去できる材料とする。本実施形態においては、シリコン酸化物に対するウェットエッチングの選択比が極めて大きいLaAlSiOを用いる。

【0017】

次に、図3(a)に示すように、犠牲膜21上にシリコン窒化膜を形成する。次に、シリコン窒化部材14と同様な方法により、シリコン窒化膜をLSパターンに加工すると共に、スリミングすることにより、複数本のライン状のシリコン窒化部材24を形成する。このとき、シリコン窒化部材24が延びる方向は、シリコン窒化部材14が延びる方向に対して交差、例えば直交した方向とする。シリコン窒化部材24の幅は(1/4)aとし、シリコン窒化部材24間の距離は(3/4)aとする。なお、シリコン窒化部材24の加工は、犠牲膜21との間の選択比が高い方法によって行うことが望ましい。犠牲膜21が削られると、後の工程においてエアギャップを形成することが困難になるからである。

【0018】

次に、図3(b)に示すように、メタル配線15と同様に、金属膜を成膜し、エッチバックすることにより、シリコン窒化部材24の側面上にメタル配線25を形成する。但し、メタル配線25の材料は、メタル配線15の材料とは異ならせる。例えば、メタル配線25はモリブデンにより形成する。また、金属膜をエッチバックしてメタル配線25を形成する際には、犠牲膜21もエッチングする。これにより、シリコン窒化部材24及びメタル配線25をマスクとして、犠牲膜21における隣り合うシリコン窒化部材24間であってメタル配線25間の直下域に相当する部分が、エッチングされて除去される。この結果、隣り合うシリコン窒化部材24間に一対のメタル配線25が配置され、この一対のメタル配線25間には、上方に開口した空間が形成され、この空間の底面においては、犠牲膜21が除去されて、配線層20が露出する。

【0019】

次に、上述のシリコン酸化部材16と同様に、全面にシリコン酸化膜を堆積させ、CMP等の平坦化処理を施すことにより、メタル配線25間にシリコン酸化部材26を埋め込む。このとき、シリコン酸化部材26の直下域においては、犠牲膜21が除去されているため、シリコン酸化部材26の下端は配線層20を構成する各部材、すなわち、シリコン窒化部材14、メタル配線15及びシリコン酸化部材16に接触する。すなわち、隣り合うシリコン窒化部材24間であって、メタル配線25間に、犠牲膜21及びシリコン窒化部材24とは異なる絶縁材料によって形成された複数本のシリコン酸化部材26が、配線層20に接するように形成される。シリコン窒化部材24、メタル配線25及びシリコン酸化部材26により、配線層30が形成される。

【0020】

次に、図4(a)に示すように、配線層30上に犠牲膜31を形成する。犠牲膜31は、犠牲膜21と同様に、ランタンアルミニウムシリケート(LaAlSiO)により形成する。

【0021】

次に、図4(b)〜図5(b)に示すように、犠牲膜31上に、再び配線層20を形成する。

すなわち、図4(b)に示すように、犠牲膜31上に、複数本のシリコン窒化部材14を形成する。このとき、これらのシリコン窒化部材14が延びる方向は、下層の配線層20におけるシリコン窒化部材14が延びる方向と同じとなる。

【0022】

次に、図5(a)に示すように、全面にタングステン膜を堆積させ、エッチバックすることにより、シリコン窒化部材14の側面上にメタル配線15を形成する。このとき、シリコン窒化部材14及びメタル配線15をマスクとしてエッチングを行い、犠牲膜31を選択的に除去する。これにより、犠牲膜31における隣り合うシリコン窒化部材14間であってメタル配線15間の直下域に相当する部分が除去される。

【0023】

次に、図5(b)に示すように、全面にシリコン酸化膜を堆積させ、平坦化処理を施すことにより、メタル配線15間にシリコン酸化部材16を形成する。シリコン酸化部材16の直下域においては、犠牲膜31が除去されているため、シリコン酸化部材16は配線層30に接触する。このようにして、犠牲膜31上に配線層20が形成される。以下、同様にして、配線層30及び配線層20を交互に積層する。

【0024】

図6に示すように、この段階においては、配線層20に属する下層のメタル配線15上に、配線層30に属する上層のメタル配線25が配置されており、メタル配線25間には、交互に、シリコン窒化部材24及びシリコン酸化部材26が配置されている。メタル配線25が延びる方向は、メタル配線15が延びる方向に対して直交している。そして、シリコン窒化部材24及びメタル配線25と、配線層20との間には、犠牲膜21が介在している。一方、シリコン酸化部材26は配線層20に接しているため、これらの間には犠牲膜21は介在していない。このようにして、配線層20及び30からなる積層体においては、それぞれ複数本のメタル配線15及びメタル配線25によって、犠牲膜21及び31を内包したクロスポイント構造が構成される。

【0025】

なお、図1〜図5においては、各部材の形状を直方体で示したが、図6においては、実際の形状に近い形状を示している。例えば、犠牲膜21の側面は傾斜しており、メタル配線25の上部は上端に向けて細くなっている。これにより、シリコン酸化部材26の下端部は細く、上端部は太くなっている。

【0026】

また、図7に示すように、上方から見て、電極パッド12は、上述のクロスポイント構造部の外部に配置されている。そして、メタル配線15及び25を、電極パッド12の直上域まで引き出す。メタル配線15及び25は、電極パッド12の直上域近傍において、相互に少しずつ位置をずらして形成する。更に、各メタル配線15は、シリコン窒化部材14及びシリコン酸化部材16によって挟まれるようにし、各メタル配線25は、シリコン窒化部材24及びシリコン酸化部材26によって挟まれるようにする。

【0027】

次に、図8に示すように、RIE等の異方性エッチングを施すことにより、配線層20及び30における電極パッド12の直上域を含む部分に、電極パッド12に到達するように、1本以上のビアホール41を形成する。このRIEは、金属及びシリコン窒化物のエッチング速度に対してシリコン酸化物のエッチング速度が高くなるような条件で行う。

【0028】

例えば、エッチングガスとして、CF4ガス、CHF3ガス、又はC2F6ガス等のフッ素系のガスを用いる。CF4ガスを例にとると、プラズマ中において、CF4ガスが下記化学式(1)の反応により分解され、発生したフッ素原子及び二フッ化炭素が下記化学式(2)及び(3)に示すようにシリコン酸化物と反応し、発生したSiF4ガス、COガス等が系外に排出される。これらのガスは、例えばポンプにより、反応チャンバーから排出される。

CF4 → 2F+CF2 (1)

SiO2+4F → SiF4+2O (2)

SiO2+2CF2 → SiF4+2CO (3)

【0029】

このとき、ビアホール41は、シリコン酸化膜中においては、下方に向かうほど連続的に細くなる。一方、シリコン窒化膜及びメタル配線はほとんどエッチングされないため、ビアホール41は、シリコン窒化膜及びメタル配線に到達すると、これらを迂回するように、非連続的に細くなる。すなわち、ビアホール41は、メタル配線に到達するたびに非連続的に細くなりながら、電極パッド12に到達する。ビアホール41は配線層20及び30を貫いて形成されるため、ビアホール41の内面には、メタル配線及び犠牲膜が露出する。

【0030】

次に、図8及び図9に示すように、ビアホール41を介して薬液を流し込むことにより、犠牲膜21及び31をサイドエッチングして除去する。例えば、犠牲膜21及び31がランタンアルミニウムシリケート(LaAlSiO)によって形成されている場合には、酸性の薬液、例えば、フッ酸を含む薬液により、犠牲膜21及び31を溶解させる。これにより、犠牲膜21及び31が除去された後の空間が、エアギャップ32となる。すなわち、配線層20におけるシリコン窒化部材14及びメタル配線15の直下域、並びに、配線層30におけるシリコン窒化部材24及びメタル配線25の直下域に、エアギャップ32が形成される。このとき、配線層20及び30の積層体は、シリコン酸化部材16及び26によって支持される。これにより、メタル配線15とメタル配線25からなり、内部にエアギャップ32が形成されたクロスポイント構造が作製される。

【0031】

次に、メモリ素子となる分子材料33(図11参照)又はその部分を含む溶剤34(図10参照)を用意する。分子材料33には、上述のクロスポイント構造を構成する2種類の配線、すなわち、メタル配線15及び25のうち、一方の配線に結合し、他方の配線には結合しないようなリンカーが一端に結合した直鎖状の分子を用いる。例えば、分子材料33として、チオールリンカーを用いた自己組織化が可能な分子を用いる。溶剤34には、このような分子材料33、又は、上述のリンカーを起点として直鎖状に成長可能な分子材料33の部分を含有させる。

【0032】

そして、図10(a)及び(b)に示すように、この溶剤34中に、シリコン基板10、配線層20及び30等からなる中間構造体を浸漬する。これにより、溶剤34がビアホール41を介してエアギャップ32内に進入し、配線層20及び30を構成する各部材に接触する。このとき、分子材料33のリンカーは、一方のメタル配線のみに結合し、他方のメタル配線には結合しない。例えば、上述の如く、メタル配線15をタングステンにより形成し、メタル配線25をモリブデンにより形成し、分子材料33をチオールリンカーを含む分子とした場合には、チオールリンカーはメタル配線25に結合し、メタル配線15には結合しない。このため、分子材料33はメタル配線25の露出面上に形成される。その後、エアギャップ32内に注入された溶剤34を、ビアホール41を介して排出する。

【0033】

これにより、図11に示すように、エアギャップ32におけるメタル配線25の上下面上に、分子材料33が形成される。これにより、エアギャップ32のうち、メタル配線25と配線層20を構成する各部材との間に分子材料33が配置される。一方、分子材料33は、シリコン窒化部材14及び24、シリコン酸化部材16及び26、並びにメタル配線15には結合しないため、シリコン窒化部材24及びシリコン酸化部材26と、配線層20の各部材との間には分子材料33が配置されない。このため、分子材料33がメタル配線25の上下面上に形成された後も、エアギャップ32内には溶剤34の流通経路が確保される。これにより、エアギャップ32の手前側から分子材料33が形成されても、エアギャップ32が目詰まりすることなく、エアギャップ32の最深部まで溶剤34を進入させることができる。なお、メタル配線25の上面上に形成されたエアギャップ32においては、分子材料33がこのエアギャップ32を横切る領域に形成されるが、この領域の幅は狭いため、溶剤34が通過可能である。

【0034】

次に、図12に示すように、ビアホール41の内面上に、例えばチタン層及びチタン窒化層の2層からなるバリアメタル層42を形成する。次に、ビアホール41内にタングステンを埋め込んで、ビアコンタクト43を形成する。ビアコンタクト43は、電極パッド12及び上下方向に一列に配列されたメタル配線15又は25に接続される。このとき、バリアメタル層42及びビアコンタクト43を形成する金属材料がエアギャップ32内に侵入する可能性もあるが、クロスポイント構造部に到達することはなく、問題は生じない。このようにして、本実施形態に係る分子メモリ装置1が製造される。

【0035】

図11〜図14に示すように、分子メモリ装置1においては、シリコン基板10上に多層配線層11が形成されている。シリコン基板10及び多層配線層11には、PMOS及びNMOSを含む駆動回路(図示せず)が形成されている。多層配線層11上には、層間絶縁膜としてシリコン酸化膜13が形成されている。

【0036】

シリコン酸化膜13上には、配線層20と配線層30とが交互に積層されている。配線層20においては、例えばタングステンからなる複数本のメタル配線15が、相互に平行に且つ略周期的に配列されており、メタル配線15間には、交互に、シリコン窒化部材14及びシリコン酸化部材16が設けられている。同様に、配線層30においては、例えばモリブデンからなる複数本のメタル配線25が、相互に平行に且つ略周期的に配列されており、メタル配線25間には、交互に、シリコン窒化部材24及びシリコン酸化部材26が設けられている。メタル配線25が延びる方向は、メタル配線15が延びる方向に対して交差、例えば直交している。このように、分子メモリ装置1においては、それぞれ複数本のメタル配線15及び25からなるクロスポイント構造が形成されている。

【0037】

配線層20においては、シリコン酸化部材16のみが下層の配線層30に接しており、シリコン窒化部材14及びメタル配線15と下層の配線層30との間にはエアギャップ32が形成されている。同様に、配線層30においては、シリコン酸化部材26のみが下層の配線層20に接しており、シリコン窒化部材24及びメタル配線25と下層の配線層20との間にはエアギャップ32が形成されている。そして、エアギャップ32におけるメタル配線25の上下面上には、分子材料33が形成されている。分子材料33のうち、メタル配線25とメタル配線15との間に介在した分子材料33が、メモリ素子となる。これにより、分子メモリ装置1においては、メタル配線15とメタル配線25との最近接点毎に、メモリセルが形成されている。

【0038】

一方、多層配線層11の上面上におけるクロスポイント構造部から外れた領域には、駆動回路に接続された電極パッド12が形成されている。電極パッド12上には、ビアコンタクト43が設けられており、電極パッド12に接続されている。ビアコンタクト43の表面は、バリアメタル層42によって被覆されている。メタル配線15及び25は、クロスポイント構造部から電極パッド12の直上域まで引き出されており、ビアコンタクト43に接続されている。ビアコンタクト43は、メタル配線15又は25に引っ掛かるように形成されることにより、メタル配線15又は25に接続されている。また、エアギャップ32はビアコンタクト43まで到達している。

【0039】

本実施形態に係る分子メモリ装置1においては、メタル配線15及び25をワード線及びビット線として使用し、各ワード線と各ビット線との間に配置された分子材料33を、メモリ素子兼整流素子として使用する。例えば、メタル配線25の正電位を印加し、メタル配線15に負電位を印加すると、メタル配線25の上下面に結合した分子材料33がメタル配線15に到達し、このメタル配線25とメタル配線15との間が低抵抗状態となる。また、メタル配線25に負電位を印加し、メタル配線15に正電位を印加すると、分子材料33がメタル配線15から離れ、このメタル配線25とメタル配線15との間が高抵抗状態となる。これにより、各メタル配線25と各メタル配線15との最近接点毎に、1ビットの情報を記憶することができる。また、メタル配線25とメタル配線15との間に読出電流を流すことにより抵抗値を検出し、記憶された情報を読み出すことができる。このとき、読出電流は、メタル配線25からメタル配線15に向かう方向には流れるが、その逆方向には流れない。

【0040】

次に、本実施形態の作用効果について説明する。

本実施形態においては、図1〜図7に示す工程において、犠牲膜21及び犠牲膜31を介して配線層20及び配線層30を交互に積層させた後、図8及び図9に示す工程において、犠牲膜21及び32を除去することにより、内部にエアギャップ32が形成されたクロスポイント構造を作製する。その後、図10及び図11に示すように、エアギャップ32内に溶剤34を侵入させることにより、メタル配線25の上下面上に分子材料33を形成する。このように、本実施形態によれば、クロスポイント構造の作製後に、1回の工程で分子材料33を形成することができる。これにより、分子材料33の形成工程数を低減できると共に、分子材料33の形成後に熱処理の影響を受けることが少なくなり、分子材料33に印加されるダメージを軽減できる。また、分子メモリ装置1全体において、分子材料33を均一に形成することができる。更に、クロスポイント構造を作製した後に分子材料33を形成しているため、分子材料33の間にメタル配線を形成する金属材料が侵入することがない。これらの理由により、本実施形態に係る分子メモリ装置1においては、メモリ素子としての分子材料33の状態が良好且つ均一である。

【0041】

これに対して、第1の配線層、分子材料層、第2の配線層及び分子材料層を繰り返し形成して、分子メモリ装置を製造することも考えられる。しかしながら、この場合は、配線層を形成する度に分子材料層を形成する必要があるため、工程数が多くなる。また、分子材料層を形成した後、配線層を形成しているため、形成された分子材料が熱処理の影響を受け、損傷する可能性がある。更に、製造プロセスの初期に形成された下層の分子材料層と、製造プロセスの終期に形成された上層の分子材料層との間で、特性が異なってしまう可能性もある。更にまた、分子材料層の分子材料間に配線材料が入り込み、上下に配列された配線同士が短絡してしまう可能性がある。このため、メモリ素子の状態を良好に保ったまま、分子メモリ装置を製造することが困難である。

【0042】

また、本実施形態においては、図9に示す工程において、ビアホール41を形成した後、ビアホール41を介して薬液を流し込むことにより犠牲膜21及び31を除去してエアギャップ32を形成し、図10に示す工程において、ビアホール41を介して溶剤34を流し込むことによりエアギャップ32内に分子材料33を形成し、その後、図12に示す工程において、ビアホール41内にビアコンタクト43を形成している。このように、ビアホール41を利用して薬液及び溶剤を注入することにより、エアギャップ32及び分子材料33を形成するための工程数を削減することができる。

【0043】

更に、本実施形態においては、犠牲膜21及び31をランタンアルミニウムシリケート(LaAlSiO)により形成し、犠牲膜21及び31を除去するための薬液として、フッ酸等を含む酸性の薬液を使用している。ランタンアルミニウムシリケートは酸性の薬液に対する溶解速度が高く、一方、シリコン酸化物及びシリコン窒化物、並びに、タングステン及びモリブデンは酸性の薬液に対する溶解速度が低いため、酸性の薬液を用いてウェットエッチングを行うことにより、犠牲膜21及び31を高い選択性で除去することができる。この結果、ミリメートルオーダーの長距離にわたって、エアギャップ32を形成することができる。

【0044】

更にまた、本実施形態においては、各段のメタル配線15を電極パッド12上における相互にずれた位置に引き出し、各段のメタル配線25を他の電極パッド12上における相互にずれた位置に引き出し、各メタル配線の両側にシリコン窒化部材及びシリコン酸化部材を配置した上で、シリコン酸化物のエッチング速度がシリコン窒化物及び金属材料のエッチング速度よりも著しく高くなるような条件で異方性エッチングを施して、ビアホール41を形成している。これにより、ビアホール41を、各段のメタル配線の片側に引っ掛けるように形成して、電極パッド12に到達させることができる。この結果、少数のビアホール41を介して各段のエアギャップ32を形成し、各エアギャップ32内に分子材料33を形成することができる。また、上下方向に配列された各段のメタル配線を1本のビアコンタクト43を介して電極パッド12に共通接続することができる。これにより、ビアコンタクト43の本数を低減することができ、分子メモリ装置1の小型化を図ることができる。

【0045】

なお、本実施形態においては、メタル配線15をタングステンにより形成し、メタル配線25をモリブデンにより形成する例を示したが、これには限定されない。メタル配線の材料は、分子材料が一方に結合し他方に結合しないような組合せであればよい。例えば、メタル配線の材料は、チタン窒化物とモリブデンの組合せであってもよい。すなわち、メタル配線15をチタン窒化物によって形成してもよい。

【0046】

また、本実施形態においては、犠牲膜21及び31をランタンアルミニウムシリケートにより形成する例を示したが、これには限定されない。犠牲膜の材料は、他の部材との間でエッチング選択比がとれるものであればよい。例えば、犠牲膜は有機材料によって形成してもよい。

【0047】

更に、本実施形態においては、各配線層を構成する絶縁部材として、シリコン窒化部材及びシリコン酸化部材を用いる例を示したが、これには限定されない。これらの絶縁部材は、絶縁性が高く、図8に示すエッチング工程において、一方の絶縁部材をエッチングする際に他方の絶縁部材がエッチングされにくい組合せであればよく、更に、図2(a)に示す工程において、一方の絶縁部材に対してCMP等の平坦化処理を施す際に、他方の絶縁部材がストッパとなるような組合せであることが好ましい。

【0048】

更にまた、本実施形態においては、メタル配線の幅とメタル配線間のスペース領域の幅がほぼ等しくなる例を示したが、これには限定されない。更にまた、図11等においては、2段の配線層20と1段の配線層30のみを図示しているが、配線層20及び30は交互に積層されていればよく、その段数は任意である。

【0049】

更にまた、本実施形態においては、ビアホール41を介して犠牲膜21及び31を除去してエアギャップ32を形成し、エアギャップ32内に分子材料33を形成する例を示したが、これには限定されない。例えば、配線層20及び30に、ビアホール以外のホール又はトレンチ等の貫通部を形成し、この貫通部を介して、犠牲膜の除去及び分子材料の形成を行ってもよい。なお、「貫通部」の概念には、2本以上のホール及びトレンチ等も含まれる。ホール又はトレンチが複数本形成されている場合には、各ホール又はトレンチの内面に全ての犠牲膜が露出している必要はなく、各犠牲膜がいずれかのホール又はトレンチの内面に露出していればよい。

【0050】

以上説明した実施形態によれば、メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を実現することができる。

【0051】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。

【0052】

本発明は、以下の態様を含む。

(付記1)

タングステンからなり第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上にランタンアルミニウムシリケートからなる第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して直交した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、ランタンアルミニウムシリケートからなる第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に、前記第1犠牲膜及び前記第2犠牲膜並びに前記第2配線が露出した1本以上のビアホールを形成する工程と、

前記ビアホールを介して、前記第1犠牲膜及び前記第2犠牲膜をフッ酸を含む薬液によって溶解させることにより、ギャップを形成する工程と、

前記ギャップ内に、チオールリンカーを含む分子を含む溶剤を進入させることにより、前記ギャップ内に分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延びる複数本の第1のシリコン窒化部材を形成する工程と、

前記第1のシリコン窒化部材の側面上に、モリブデンからなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1のシリコン窒化部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1のシリコン窒化部材間であって前記第2配線間に、複数本の第1のシリコン酸化部材を前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第2のシリコン窒化部材を形成する工程と、

前記第2のシリコン窒化部材の側面上に、タングステンからなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第2のシリコン窒化部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第2のシリコン窒化部材間であって前記第3配線間に、複数本の第2のシリコン酸化部材を前記第2配線層に接するように形成する工程と、

を有し、

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記ビアホールを形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層を貫通するように前記ビアホールを形成する分子メモリ装置の製造方法。

【0053】

(付記2)

第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上に第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して交差した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に前記第1犠牲膜及び前記第2犠牲膜が露出した貫通部を形成する工程と、

前記貫通部を介して、前記第1犠牲膜及び前記第2犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第3配線、並びに、前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延び、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延び、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第3絶縁部材を形成する工程と、

前記第3絶縁部材の側面上に、前記第2配線とは異なる導電材料からなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第3絶縁部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第3絶縁部材間であって前記第3配線間に、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第4絶縁部材を、前記第2配線層に接するように形成する工程と、

を有した分子メモリ装置の製造方法。

【0054】

(付記3)

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記貫通部を形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層が内面に露出するように前記貫通部を形成する付記2記載の分子メモリ装置の製造方法。

【0055】

(付記4)

第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、

前記配線層上に犠牲膜を形成する工程と、

前記犠牲膜上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記配線層に接するように形成する工程と、

前記犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備えた分子メモリ装置の製造方法。

【0056】

(付記5)

前記分子材料を形成する工程は、前記ギャップ内に前記分子材料又はその部分を含む溶剤を進入させる工程を有する付記4記載の分子メモリ装置の製造方法。

【0057】

(付記6)

前記分子材料は、前記第1絶縁部材及び前記第2絶縁部材には結合しない付記4または5に記載の分子メモリ装置の製造方法。

【0058】

(付記7)

前記第1絶縁部材、前記第2配線及び前記第2絶縁部材からなる他の配線層、並びに、前記配線層に、その内面に前記犠牲膜が露出するように、貫通部を形成する工程と、

をさらに備え、

前記犠牲膜の除去及び前記分子材料の形成は、前記貫通部を介して行う付記4〜6のいずれか1つに記載の分子メモリ装置の製造方法。

【0059】

(付記8)

前記貫通部は、その内面に前記第2配線が露出する1本以上のビアホールである付記7記載の分子メモリ装置の製造方法。

【0060】

(付記9)

前記第1絶縁部材、前記第2配線及び前記第2絶縁部材からなる他の配線層上に、他の犠牲膜を形成する工程と、

前記他の犠牲膜上に、前記第1方向に延び、前記他の犠牲膜とは異なる絶縁材料からなる複数本の第3絶縁部材を形成する工程と、

前記第3絶縁部材の側面上に、前記第2配線とは異なる導電材料からなる第3配線を形成すると共に、前記他の犠牲膜における隣り合う前記第3絶縁部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第3絶縁部材間であって前記第3配線間に、前記他の犠牲膜とは異なる絶縁材料からなる複数本の第4絶縁部材を、前記他の配線層に接するように形成する工程と、

をさらに備え、

前記ギャップを形成する工程において、前記他の犠牲膜も除去することにより、他のギャップも形成し、

前記分子材料を形成する工程において、前記他のギャップ内にも前記分子材料を形成する付記4〜8のいずれか1つに記載の分子メモリ装置の製造方法。

【0061】

(付記10)

前記犠牲膜を形成する工程、前記他の配線層を形成する工程、前記他の犠牲膜を形成する工程、並びに、前記第3絶縁部材、前記第3配線及び前記第4絶縁部材からなる更に他の配線層を形成する工程を、複数回繰り返し、

前記犠牲膜を除去する工程において、全ての前記犠牲膜及び全ての前記他の犠牲膜を、一括して除去する付記9記載の分子メモリ装置の製造方法。

【0062】

(付記11)

前記第1絶縁部材をシリコン窒化物により形成し、前記第2配線部材をシリコン酸化物により形成する付記2〜10のいずれか1つに記載の分子メモリ装置の製造方法。

【0063】

(付記12)

前記犠牲膜をランタンアルミニウムシリケートにより形成し、

前記犠牲膜を除去する工程は、前記犠牲膜を酸性の薬液によって溶解させる工程を有する付記2〜11のいずれか1つに記載の分子メモリ装置の製造方法。

【0064】

(付記13)

前記薬液はフッ酸を含む付記12記載の分子メモリ装置の製造方法。

【0065】

(付記14)

前記第1配線をタングステン又はチタン窒化物により形成し、前記第2配線をモリブデンにより形成し、前記分子材料をチオールリンカーを含む分子とする付記2〜13のいずれか1つに記載の分子メモリ装置の製造方法。

【符号の説明】

【0066】

1:分子メモリ装置、10:シリコン基板、11:多層配線層、12:電極パッド、13:シリコン酸化膜、14:シリコン窒化部材、15:メタル配線、16:シリコン酸化部材、20:配線層、21:犠牲膜、24:シリコン窒化部材、25:メタル配線、26:シリコン酸化部材、30:配線層、31:犠牲膜、32:エアギャップ、33:分子材料、34:溶剤、41:ビアホール、42:バリアメタル層、43:ビアコンタクト

【技術分野】

【0001】

本発明の実施形態は、分子メモリ装置の製造方法に関する。

【背景技術】

【0002】

従来より、大容量な不揮発性記憶装置として、NAND型フラッシュメモリが知られている。これまでNAND型フラッシュメモリは、微細化により大容量化及び低コスト化を実現してきた。しかしながら、NAND型フラッシュメモリの微細化は限界に近づいている。そこで、近年、NAND型フラッシュメモリ以外の記憶装置の開発が進められている。

【0003】

その一つとして、メモリ素子として分子を用いた分子メモリ装置が提案されている。分子メモリ装置においては、下層電極と上層電極との間に分子が配置されており、分子の状態を制御することによって、下層電極と上層電極との間の電気抵抗値を異ならせて、データを記憶する。このような分子メモリ装置の記憶密度を増加させるためには、クロスポイント構造を作製してメモリ素子を3次元的に積層させることが効果的である。しかしながら、メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置を製造することは困難である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許出願公開第2007/0045615号明細書

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供することである。

【課題を解決するための手段】

【0006】

実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって、前記第2配線間に、前記犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記配線層に接するように形成する工程と、前記犠牲膜を除去することにより、ギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、を備える。

【図面の簡単な説明】

【0007】

【図1】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図2】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図3】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図4】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図5】(a)及び(b)は、実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図6】実施形態に係る分子メモリ装置の製造方法を例示する工程断面図である。

【図7】実施形態に係る分子メモリ装置の製造方法を例示する工程断面図である。

【図8】実施形態に係る分子メモリ装置の製造方法を例示する工程断面図である。

【図9】実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図である。

【図10】(a)はエアギャップとビアホールとの関係を例示する模式的平面図であり、(b)はその模式的断面図である。

【図11】実施形態に係る分子メモリ装置を例示する斜視図である。

【図12】実施形態に係る分子メモリ装置を例示する断面図である。

【図13】(a)及び(b)は、実施形態に係る分子メモリ装置を例示する断面図である。

【図14】実施形態に係る分子メモリ装置の導電部分を例示する斜視図である。

【発明を実施するための形態】

【0008】

以下、図面を参照しつつ、本発明の実施形態について説明する。

図1(a)及び(b)、図2(a)及び(b)、図3(a)及び(b)、図4(a)及び(b)、図5(a)及び(b)は、本実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図であり、

図6〜図8は、本実施形態に係る分子メモリ装置の製造方法を例示する工程断面図であり、

図9は、本実施形態に係る分子メモリ装置の製造方法を例示する工程斜視図であり、

図10(a)はエアギャップとビアホールとの関係を例示する模式的平面図であり、(b)はその模式的断面図であり、

図11は、本実施形態に係る分子メモリ装置を例示する斜視図であり、

図12並びに図13(a)及び(b)は、本実施形態に係る分子メモリ装置を例示する断面図であり、

図14は、本実施形態に係る分子メモリ装置の導電部分を例示する斜視図である。

【0009】

なお、図1〜図6、図9、図11、図13は、メモリセルが形成されるクロスポイント構造部を示し、

図7、図8、図12は、ビアコンタクトの周辺を示し、

図10及び図14は、クロスポイント構造部及びビアコンタクトの双方を示す。

本実施形態は、分子メモリ装置の製造方法の実施形態である。

【0010】

先ず、図1(a)に示すように、シリコン基板10を用意する。次に、シリコン基板10の上面にnチャネル形MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:金属酸化物半導体電界効果トランジスタ)(NMOS)及びpチャネル形MOSFET(PMOS)を形成する。次に、シリコン基板10上に多層配線層11を形成する。これにより、シリコン基板10及び多層配線層11に、NMOS及びPMOSを組み合わせた駆動回路(図示せず)が形成される。多層配線層11上には、駆動回路に接続された電極パッド12(図7参照)を形成する。なお、後述する図1(b)〜図5(b)においては、シリコン基板10及び多層配線層11を省略している。

【0011】

次に、多層配線層11上に、層間絶縁膜として、例えばLPCVD(Low Pressure Chemical Vapor Deposition:低圧化学気相成長)法により、シリコン酸化膜13を形成する。次に、例えばLPCVD法又はPCVD(Plasma CVD:プラズマCVD)法により、シリコン窒化膜を形成する。次に、リソグラフィー法を用いて、シリコン窒化膜上に、フォトレジストのLS(ラインアンドスペース)パターン(図示せず)を形成する。このとき、LSパターンの配列周期をaとする。次に、このフォトレジストをマスクとしてRIE(Reactive Ion Etching:反応性イオンエッチング)等の異方性エッチングを施し、シリコン窒化膜をLSパターンに加工する。これにより、シリコン酸化膜13上に、一方向に延び、周期的に配列された複数本のライン状のシリコン窒化部材14が形成される。

【0012】

次に、シリコン窒化部材14をスリミングし、幅を細くする。例えば、各シリコン窒化部材14の幅を(1/4)aとし、隣り合うシリコン窒化部材14間の距離、すなわち、スペース領域の幅を(3/4)aとする。これにより、後の工程において、配線の幅とスペースの幅が等しくなる。

【0013】

次に、図1(b)に示すように、例えばCVD法により、金属膜を全面に均一な膜厚で成膜する。このとき、金属膜の膜厚は(1/4)aとする。金属膜の材料には、例えば、CVD法によって容易に成膜できるタングステンを用いる。また、金属膜の材料によっては、金属膜を成膜する前に、シード層を形成してもよい。このシード層は、金属の拡散を抑制するバリアメタル層としても機能する。例えば、金属膜の材料をタングステンとする場合は、シード層の材料はチタン窒化物とすることができる。

【0014】

次に、RIEを行い、金属膜をエッチバックする。これにより、金属膜のうち、シリコン酸化膜13の上面上に形成された部分及びシリコン窒化部材14の上面上に形成された部分が除去され、シリコン窒化部材14の側面上に形成された部分が残留する。この結果、シリコン窒化部材14の側面上に、金属からなり、幅が約(1/4)aのスペーサ形状のメタル配線15が形成される。このとき、メタル配線15間のスペース領域の幅も約(1/4)aとなる。なお、上述のシード層を形成した場合は、金属膜を加工する際に、スペース領域からシード層も除去する。

【0015】

次に、図2(a)に示すように、異方性CVD法、例えば、HDP(High Density Plasma:高密度プラズマ)−CVD法によりシリコン酸化物を堆積させて、シリコン窒化部材14及びメタル配線15を覆うように、全面にシリコン酸化膜を成膜する。次に、シリコン窒化部材14及びメタル配線15をストッパとした平坦化処理、例えばCMP(Chemical Mechanical Polishing:化学的機械研磨)を施すことにより、シリコン酸化膜におけるシリコン窒化部材14及びメタル配線15の上面上に形成された部分を除去する。これにより、隣り合うシリコン窒化部材14間であって、メタル配線15間の空間に、シリコン酸化部材16が埋め込まれる。このようにして、シリコン窒化部材14、メタル配線15及びシリコン酸化部材16からなる配線層20が形成される。なお、上述の如く、メタル配線15間のスペース領域の幅は約(1/4)aであるから、メタル配線15間に埋め込まれたシリコン酸化部材16の幅も、約(1/4)aとなる。

【0016】

次に、図2(b)に示すように、配線層20上に、例えば、ランタンアルミニウムシリケート(LaAlSiO)からなる犠牲膜21を形成する。犠牲膜21は、後の工程において除去されることにより、メモリ材料となる分子が配置されるためのエアギャップとなる。犠牲膜21の膜厚は、後述する分子材料33(図11参照)の長さとほぼ等しくする。また、犠牲膜21の材料は、他の材料との間で十分な選択比をもつウェットエッチングによって除去できる材料とする。本実施形態においては、シリコン酸化物に対するウェットエッチングの選択比が極めて大きいLaAlSiOを用いる。

【0017】

次に、図3(a)に示すように、犠牲膜21上にシリコン窒化膜を形成する。次に、シリコン窒化部材14と同様な方法により、シリコン窒化膜をLSパターンに加工すると共に、スリミングすることにより、複数本のライン状のシリコン窒化部材24を形成する。このとき、シリコン窒化部材24が延びる方向は、シリコン窒化部材14が延びる方向に対して交差、例えば直交した方向とする。シリコン窒化部材24の幅は(1/4)aとし、シリコン窒化部材24間の距離は(3/4)aとする。なお、シリコン窒化部材24の加工は、犠牲膜21との間の選択比が高い方法によって行うことが望ましい。犠牲膜21が削られると、後の工程においてエアギャップを形成することが困難になるからである。

【0018】

次に、図3(b)に示すように、メタル配線15と同様に、金属膜を成膜し、エッチバックすることにより、シリコン窒化部材24の側面上にメタル配線25を形成する。但し、メタル配線25の材料は、メタル配線15の材料とは異ならせる。例えば、メタル配線25はモリブデンにより形成する。また、金属膜をエッチバックしてメタル配線25を形成する際には、犠牲膜21もエッチングする。これにより、シリコン窒化部材24及びメタル配線25をマスクとして、犠牲膜21における隣り合うシリコン窒化部材24間であってメタル配線25間の直下域に相当する部分が、エッチングされて除去される。この結果、隣り合うシリコン窒化部材24間に一対のメタル配線25が配置され、この一対のメタル配線25間には、上方に開口した空間が形成され、この空間の底面においては、犠牲膜21が除去されて、配線層20が露出する。

【0019】

次に、上述のシリコン酸化部材16と同様に、全面にシリコン酸化膜を堆積させ、CMP等の平坦化処理を施すことにより、メタル配線25間にシリコン酸化部材26を埋め込む。このとき、シリコン酸化部材26の直下域においては、犠牲膜21が除去されているため、シリコン酸化部材26の下端は配線層20を構成する各部材、すなわち、シリコン窒化部材14、メタル配線15及びシリコン酸化部材16に接触する。すなわち、隣り合うシリコン窒化部材24間であって、メタル配線25間に、犠牲膜21及びシリコン窒化部材24とは異なる絶縁材料によって形成された複数本のシリコン酸化部材26が、配線層20に接するように形成される。シリコン窒化部材24、メタル配線25及びシリコン酸化部材26により、配線層30が形成される。

【0020】

次に、図4(a)に示すように、配線層30上に犠牲膜31を形成する。犠牲膜31は、犠牲膜21と同様に、ランタンアルミニウムシリケート(LaAlSiO)により形成する。

【0021】

次に、図4(b)〜図5(b)に示すように、犠牲膜31上に、再び配線層20を形成する。

すなわち、図4(b)に示すように、犠牲膜31上に、複数本のシリコン窒化部材14を形成する。このとき、これらのシリコン窒化部材14が延びる方向は、下層の配線層20におけるシリコン窒化部材14が延びる方向と同じとなる。

【0022】

次に、図5(a)に示すように、全面にタングステン膜を堆積させ、エッチバックすることにより、シリコン窒化部材14の側面上にメタル配線15を形成する。このとき、シリコン窒化部材14及びメタル配線15をマスクとしてエッチングを行い、犠牲膜31を選択的に除去する。これにより、犠牲膜31における隣り合うシリコン窒化部材14間であってメタル配線15間の直下域に相当する部分が除去される。

【0023】

次に、図5(b)に示すように、全面にシリコン酸化膜を堆積させ、平坦化処理を施すことにより、メタル配線15間にシリコン酸化部材16を形成する。シリコン酸化部材16の直下域においては、犠牲膜31が除去されているため、シリコン酸化部材16は配線層30に接触する。このようにして、犠牲膜31上に配線層20が形成される。以下、同様にして、配線層30及び配線層20を交互に積層する。

【0024】

図6に示すように、この段階においては、配線層20に属する下層のメタル配線15上に、配線層30に属する上層のメタル配線25が配置されており、メタル配線25間には、交互に、シリコン窒化部材24及びシリコン酸化部材26が配置されている。メタル配線25が延びる方向は、メタル配線15が延びる方向に対して直交している。そして、シリコン窒化部材24及びメタル配線25と、配線層20との間には、犠牲膜21が介在している。一方、シリコン酸化部材26は配線層20に接しているため、これらの間には犠牲膜21は介在していない。このようにして、配線層20及び30からなる積層体においては、それぞれ複数本のメタル配線15及びメタル配線25によって、犠牲膜21及び31を内包したクロスポイント構造が構成される。

【0025】

なお、図1〜図5においては、各部材の形状を直方体で示したが、図6においては、実際の形状に近い形状を示している。例えば、犠牲膜21の側面は傾斜しており、メタル配線25の上部は上端に向けて細くなっている。これにより、シリコン酸化部材26の下端部は細く、上端部は太くなっている。

【0026】

また、図7に示すように、上方から見て、電極パッド12は、上述のクロスポイント構造部の外部に配置されている。そして、メタル配線15及び25を、電極パッド12の直上域まで引き出す。メタル配線15及び25は、電極パッド12の直上域近傍において、相互に少しずつ位置をずらして形成する。更に、各メタル配線15は、シリコン窒化部材14及びシリコン酸化部材16によって挟まれるようにし、各メタル配線25は、シリコン窒化部材24及びシリコン酸化部材26によって挟まれるようにする。

【0027】

次に、図8に示すように、RIE等の異方性エッチングを施すことにより、配線層20及び30における電極パッド12の直上域を含む部分に、電極パッド12に到達するように、1本以上のビアホール41を形成する。このRIEは、金属及びシリコン窒化物のエッチング速度に対してシリコン酸化物のエッチング速度が高くなるような条件で行う。

【0028】

例えば、エッチングガスとして、CF4ガス、CHF3ガス、又はC2F6ガス等のフッ素系のガスを用いる。CF4ガスを例にとると、プラズマ中において、CF4ガスが下記化学式(1)の反応により分解され、発生したフッ素原子及び二フッ化炭素が下記化学式(2)及び(3)に示すようにシリコン酸化物と反応し、発生したSiF4ガス、COガス等が系外に排出される。これらのガスは、例えばポンプにより、反応チャンバーから排出される。

CF4 → 2F+CF2 (1)

SiO2+4F → SiF4+2O (2)

SiO2+2CF2 → SiF4+2CO (3)

【0029】

このとき、ビアホール41は、シリコン酸化膜中においては、下方に向かうほど連続的に細くなる。一方、シリコン窒化膜及びメタル配線はほとんどエッチングされないため、ビアホール41は、シリコン窒化膜及びメタル配線に到達すると、これらを迂回するように、非連続的に細くなる。すなわち、ビアホール41は、メタル配線に到達するたびに非連続的に細くなりながら、電極パッド12に到達する。ビアホール41は配線層20及び30を貫いて形成されるため、ビアホール41の内面には、メタル配線及び犠牲膜が露出する。

【0030】

次に、図8及び図9に示すように、ビアホール41を介して薬液を流し込むことにより、犠牲膜21及び31をサイドエッチングして除去する。例えば、犠牲膜21及び31がランタンアルミニウムシリケート(LaAlSiO)によって形成されている場合には、酸性の薬液、例えば、フッ酸を含む薬液により、犠牲膜21及び31を溶解させる。これにより、犠牲膜21及び31が除去された後の空間が、エアギャップ32となる。すなわち、配線層20におけるシリコン窒化部材14及びメタル配線15の直下域、並びに、配線層30におけるシリコン窒化部材24及びメタル配線25の直下域に、エアギャップ32が形成される。このとき、配線層20及び30の積層体は、シリコン酸化部材16及び26によって支持される。これにより、メタル配線15とメタル配線25からなり、内部にエアギャップ32が形成されたクロスポイント構造が作製される。

【0031】

次に、メモリ素子となる分子材料33(図11参照)又はその部分を含む溶剤34(図10参照)を用意する。分子材料33には、上述のクロスポイント構造を構成する2種類の配線、すなわち、メタル配線15及び25のうち、一方の配線に結合し、他方の配線には結合しないようなリンカーが一端に結合した直鎖状の分子を用いる。例えば、分子材料33として、チオールリンカーを用いた自己組織化が可能な分子を用いる。溶剤34には、このような分子材料33、又は、上述のリンカーを起点として直鎖状に成長可能な分子材料33の部分を含有させる。

【0032】

そして、図10(a)及び(b)に示すように、この溶剤34中に、シリコン基板10、配線層20及び30等からなる中間構造体を浸漬する。これにより、溶剤34がビアホール41を介してエアギャップ32内に進入し、配線層20及び30を構成する各部材に接触する。このとき、分子材料33のリンカーは、一方のメタル配線のみに結合し、他方のメタル配線には結合しない。例えば、上述の如く、メタル配線15をタングステンにより形成し、メタル配線25をモリブデンにより形成し、分子材料33をチオールリンカーを含む分子とした場合には、チオールリンカーはメタル配線25に結合し、メタル配線15には結合しない。このため、分子材料33はメタル配線25の露出面上に形成される。その後、エアギャップ32内に注入された溶剤34を、ビアホール41を介して排出する。

【0033】

これにより、図11に示すように、エアギャップ32におけるメタル配線25の上下面上に、分子材料33が形成される。これにより、エアギャップ32のうち、メタル配線25と配線層20を構成する各部材との間に分子材料33が配置される。一方、分子材料33は、シリコン窒化部材14及び24、シリコン酸化部材16及び26、並びにメタル配線15には結合しないため、シリコン窒化部材24及びシリコン酸化部材26と、配線層20の各部材との間には分子材料33が配置されない。このため、分子材料33がメタル配線25の上下面上に形成された後も、エアギャップ32内には溶剤34の流通経路が確保される。これにより、エアギャップ32の手前側から分子材料33が形成されても、エアギャップ32が目詰まりすることなく、エアギャップ32の最深部まで溶剤34を進入させることができる。なお、メタル配線25の上面上に形成されたエアギャップ32においては、分子材料33がこのエアギャップ32を横切る領域に形成されるが、この領域の幅は狭いため、溶剤34が通過可能である。

【0034】

次に、図12に示すように、ビアホール41の内面上に、例えばチタン層及びチタン窒化層の2層からなるバリアメタル層42を形成する。次に、ビアホール41内にタングステンを埋め込んで、ビアコンタクト43を形成する。ビアコンタクト43は、電極パッド12及び上下方向に一列に配列されたメタル配線15又は25に接続される。このとき、バリアメタル層42及びビアコンタクト43を形成する金属材料がエアギャップ32内に侵入する可能性もあるが、クロスポイント構造部に到達することはなく、問題は生じない。このようにして、本実施形態に係る分子メモリ装置1が製造される。

【0035】

図11〜図14に示すように、分子メモリ装置1においては、シリコン基板10上に多層配線層11が形成されている。シリコン基板10及び多層配線層11には、PMOS及びNMOSを含む駆動回路(図示せず)が形成されている。多層配線層11上には、層間絶縁膜としてシリコン酸化膜13が形成されている。

【0036】

シリコン酸化膜13上には、配線層20と配線層30とが交互に積層されている。配線層20においては、例えばタングステンからなる複数本のメタル配線15が、相互に平行に且つ略周期的に配列されており、メタル配線15間には、交互に、シリコン窒化部材14及びシリコン酸化部材16が設けられている。同様に、配線層30においては、例えばモリブデンからなる複数本のメタル配線25が、相互に平行に且つ略周期的に配列されており、メタル配線25間には、交互に、シリコン窒化部材24及びシリコン酸化部材26が設けられている。メタル配線25が延びる方向は、メタル配線15が延びる方向に対して交差、例えば直交している。このように、分子メモリ装置1においては、それぞれ複数本のメタル配線15及び25からなるクロスポイント構造が形成されている。

【0037】

配線層20においては、シリコン酸化部材16のみが下層の配線層30に接しており、シリコン窒化部材14及びメタル配線15と下層の配線層30との間にはエアギャップ32が形成されている。同様に、配線層30においては、シリコン酸化部材26のみが下層の配線層20に接しており、シリコン窒化部材24及びメタル配線25と下層の配線層20との間にはエアギャップ32が形成されている。そして、エアギャップ32におけるメタル配線25の上下面上には、分子材料33が形成されている。分子材料33のうち、メタル配線25とメタル配線15との間に介在した分子材料33が、メモリ素子となる。これにより、分子メモリ装置1においては、メタル配線15とメタル配線25との最近接点毎に、メモリセルが形成されている。

【0038】

一方、多層配線層11の上面上におけるクロスポイント構造部から外れた領域には、駆動回路に接続された電極パッド12が形成されている。電極パッド12上には、ビアコンタクト43が設けられており、電極パッド12に接続されている。ビアコンタクト43の表面は、バリアメタル層42によって被覆されている。メタル配線15及び25は、クロスポイント構造部から電極パッド12の直上域まで引き出されており、ビアコンタクト43に接続されている。ビアコンタクト43は、メタル配線15又は25に引っ掛かるように形成されることにより、メタル配線15又は25に接続されている。また、エアギャップ32はビアコンタクト43まで到達している。

【0039】

本実施形態に係る分子メモリ装置1においては、メタル配線15及び25をワード線及びビット線として使用し、各ワード線と各ビット線との間に配置された分子材料33を、メモリ素子兼整流素子として使用する。例えば、メタル配線25の正電位を印加し、メタル配線15に負電位を印加すると、メタル配線25の上下面に結合した分子材料33がメタル配線15に到達し、このメタル配線25とメタル配線15との間が低抵抗状態となる。また、メタル配線25に負電位を印加し、メタル配線15に正電位を印加すると、分子材料33がメタル配線15から離れ、このメタル配線25とメタル配線15との間が高抵抗状態となる。これにより、各メタル配線25と各メタル配線15との最近接点毎に、1ビットの情報を記憶することができる。また、メタル配線25とメタル配線15との間に読出電流を流すことにより抵抗値を検出し、記憶された情報を読み出すことができる。このとき、読出電流は、メタル配線25からメタル配線15に向かう方向には流れるが、その逆方向には流れない。

【0040】

次に、本実施形態の作用効果について説明する。

本実施形態においては、図1〜図7に示す工程において、犠牲膜21及び犠牲膜31を介して配線層20及び配線層30を交互に積層させた後、図8及び図9に示す工程において、犠牲膜21及び32を除去することにより、内部にエアギャップ32が形成されたクロスポイント構造を作製する。その後、図10及び図11に示すように、エアギャップ32内に溶剤34を侵入させることにより、メタル配線25の上下面上に分子材料33を形成する。このように、本実施形態によれば、クロスポイント構造の作製後に、1回の工程で分子材料33を形成することができる。これにより、分子材料33の形成工程数を低減できると共に、分子材料33の形成後に熱処理の影響を受けることが少なくなり、分子材料33に印加されるダメージを軽減できる。また、分子メモリ装置1全体において、分子材料33を均一に形成することができる。更に、クロスポイント構造を作製した後に分子材料33を形成しているため、分子材料33の間にメタル配線を形成する金属材料が侵入することがない。これらの理由により、本実施形態に係る分子メモリ装置1においては、メモリ素子としての分子材料33の状態が良好且つ均一である。

【0041】

これに対して、第1の配線層、分子材料層、第2の配線層及び分子材料層を繰り返し形成して、分子メモリ装置を製造することも考えられる。しかしながら、この場合は、配線層を形成する度に分子材料層を形成する必要があるため、工程数が多くなる。また、分子材料層を形成した後、配線層を形成しているため、形成された分子材料が熱処理の影響を受け、損傷する可能性がある。更に、製造プロセスの初期に形成された下層の分子材料層と、製造プロセスの終期に形成された上層の分子材料層との間で、特性が異なってしまう可能性もある。更にまた、分子材料層の分子材料間に配線材料が入り込み、上下に配列された配線同士が短絡してしまう可能性がある。このため、メモリ素子の状態を良好に保ったまま、分子メモリ装置を製造することが困難である。

【0042】

また、本実施形態においては、図9に示す工程において、ビアホール41を形成した後、ビアホール41を介して薬液を流し込むことにより犠牲膜21及び31を除去してエアギャップ32を形成し、図10に示す工程において、ビアホール41を介して溶剤34を流し込むことによりエアギャップ32内に分子材料33を形成し、その後、図12に示す工程において、ビアホール41内にビアコンタクト43を形成している。このように、ビアホール41を利用して薬液及び溶剤を注入することにより、エアギャップ32及び分子材料33を形成するための工程数を削減することができる。

【0043】

更に、本実施形態においては、犠牲膜21及び31をランタンアルミニウムシリケート(LaAlSiO)により形成し、犠牲膜21及び31を除去するための薬液として、フッ酸等を含む酸性の薬液を使用している。ランタンアルミニウムシリケートは酸性の薬液に対する溶解速度が高く、一方、シリコン酸化物及びシリコン窒化物、並びに、タングステン及びモリブデンは酸性の薬液に対する溶解速度が低いため、酸性の薬液を用いてウェットエッチングを行うことにより、犠牲膜21及び31を高い選択性で除去することができる。この結果、ミリメートルオーダーの長距離にわたって、エアギャップ32を形成することができる。

【0044】

更にまた、本実施形態においては、各段のメタル配線15を電極パッド12上における相互にずれた位置に引き出し、各段のメタル配線25を他の電極パッド12上における相互にずれた位置に引き出し、各メタル配線の両側にシリコン窒化部材及びシリコン酸化部材を配置した上で、シリコン酸化物のエッチング速度がシリコン窒化物及び金属材料のエッチング速度よりも著しく高くなるような条件で異方性エッチングを施して、ビアホール41を形成している。これにより、ビアホール41を、各段のメタル配線の片側に引っ掛けるように形成して、電極パッド12に到達させることができる。この結果、少数のビアホール41を介して各段のエアギャップ32を形成し、各エアギャップ32内に分子材料33を形成することができる。また、上下方向に配列された各段のメタル配線を1本のビアコンタクト43を介して電極パッド12に共通接続することができる。これにより、ビアコンタクト43の本数を低減することができ、分子メモリ装置1の小型化を図ることができる。

【0045】

なお、本実施形態においては、メタル配線15をタングステンにより形成し、メタル配線25をモリブデンにより形成する例を示したが、これには限定されない。メタル配線の材料は、分子材料が一方に結合し他方に結合しないような組合せであればよい。例えば、メタル配線の材料は、チタン窒化物とモリブデンの組合せであってもよい。すなわち、メタル配線15をチタン窒化物によって形成してもよい。

【0046】

また、本実施形態においては、犠牲膜21及び31をランタンアルミニウムシリケートにより形成する例を示したが、これには限定されない。犠牲膜の材料は、他の部材との間でエッチング選択比がとれるものであればよい。例えば、犠牲膜は有機材料によって形成してもよい。

【0047】

更に、本実施形態においては、各配線層を構成する絶縁部材として、シリコン窒化部材及びシリコン酸化部材を用いる例を示したが、これには限定されない。これらの絶縁部材は、絶縁性が高く、図8に示すエッチング工程において、一方の絶縁部材をエッチングする際に他方の絶縁部材がエッチングされにくい組合せであればよく、更に、図2(a)に示す工程において、一方の絶縁部材に対してCMP等の平坦化処理を施す際に、他方の絶縁部材がストッパとなるような組合せであることが好ましい。

【0048】

更にまた、本実施形態においては、メタル配線の幅とメタル配線間のスペース領域の幅がほぼ等しくなる例を示したが、これには限定されない。更にまた、図11等においては、2段の配線層20と1段の配線層30のみを図示しているが、配線層20及び30は交互に積層されていればよく、その段数は任意である。

【0049】

更にまた、本実施形態においては、ビアホール41を介して犠牲膜21及び31を除去してエアギャップ32を形成し、エアギャップ32内に分子材料33を形成する例を示したが、これには限定されない。例えば、配線層20及び30に、ビアホール以外のホール又はトレンチ等の貫通部を形成し、この貫通部を介して、犠牲膜の除去及び分子材料の形成を行ってもよい。なお、「貫通部」の概念には、2本以上のホール及びトレンチ等も含まれる。ホール又はトレンチが複数本形成されている場合には、各ホール又はトレンチの内面に全ての犠牲膜が露出している必要はなく、各犠牲膜がいずれかのホール又はトレンチの内面に露出していればよい。

【0050】

以上説明した実施形態によれば、メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を実現することができる。

【0051】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。

【0052】

本発明は、以下の態様を含む。

(付記1)

タングステンからなり第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上にランタンアルミニウムシリケートからなる第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して直交した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、ランタンアルミニウムシリケートからなる第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に、前記第1犠牲膜及び前記第2犠牲膜並びに前記第2配線が露出した1本以上のビアホールを形成する工程と、

前記ビアホールを介して、前記第1犠牲膜及び前記第2犠牲膜をフッ酸を含む薬液によって溶解させることにより、ギャップを形成する工程と、

前記ギャップ内に、チオールリンカーを含む分子を含む溶剤を進入させることにより、前記ギャップ内に分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延びる複数本の第1のシリコン窒化部材を形成する工程と、

前記第1のシリコン窒化部材の側面上に、モリブデンからなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1のシリコン窒化部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1のシリコン窒化部材間であって前記第2配線間に、複数本の第1のシリコン酸化部材を前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第2のシリコン窒化部材を形成する工程と、

前記第2のシリコン窒化部材の側面上に、タングステンからなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第2のシリコン窒化部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第2のシリコン窒化部材間であって前記第3配線間に、複数本の第2のシリコン酸化部材を前記第2配線層に接するように形成する工程と、

を有し、

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記ビアホールを形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層を貫通するように前記ビアホールを形成する分子メモリ装置の製造方法。

【0053】

(付記2)

第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上に第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して交差した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に前記第1犠牲膜及び前記第2犠牲膜が露出した貫通部を形成する工程と、

前記貫通部を介して、前記第1犠牲膜及び前記第2犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第3配線、並びに、前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延び、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延び、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第3絶縁部材を形成する工程と、

前記第3絶縁部材の側面上に、前記第2配線とは異なる導電材料からなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第3絶縁部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第3絶縁部材間であって前記第3配線間に、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第4絶縁部材を、前記第2配線層に接するように形成する工程と、

を有した分子メモリ装置の製造方法。

【0054】

(付記3)

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記貫通部を形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層が内面に露出するように前記貫通部を形成する付記2記載の分子メモリ装置の製造方法。

【0055】

(付記4)

第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、

前記配線層上に犠牲膜を形成する工程と、

前記犠牲膜上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記配線層に接するように形成する工程と、

前記犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備えた分子メモリ装置の製造方法。

【0056】

(付記5)

前記分子材料を形成する工程は、前記ギャップ内に前記分子材料又はその部分を含む溶剤を進入させる工程を有する付記4記載の分子メモリ装置の製造方法。

【0057】

(付記6)

前記分子材料は、前記第1絶縁部材及び前記第2絶縁部材には結合しない付記4または5に記載の分子メモリ装置の製造方法。

【0058】

(付記7)

前記第1絶縁部材、前記第2配線及び前記第2絶縁部材からなる他の配線層、並びに、前記配線層に、その内面に前記犠牲膜が露出するように、貫通部を形成する工程と、

をさらに備え、

前記犠牲膜の除去及び前記分子材料の形成は、前記貫通部を介して行う付記4〜6のいずれか1つに記載の分子メモリ装置の製造方法。

【0059】

(付記8)

前記貫通部は、その内面に前記第2配線が露出する1本以上のビアホールである付記7記載の分子メモリ装置の製造方法。

【0060】

(付記9)

前記第1絶縁部材、前記第2配線及び前記第2絶縁部材からなる他の配線層上に、他の犠牲膜を形成する工程と、

前記他の犠牲膜上に、前記第1方向に延び、前記他の犠牲膜とは異なる絶縁材料からなる複数本の第3絶縁部材を形成する工程と、

前記第3絶縁部材の側面上に、前記第2配線とは異なる導電材料からなる第3配線を形成すると共に、前記他の犠牲膜における隣り合う前記第3絶縁部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第3絶縁部材間であって前記第3配線間に、前記他の犠牲膜とは異なる絶縁材料からなる複数本の第4絶縁部材を、前記他の配線層に接するように形成する工程と、

をさらに備え、

前記ギャップを形成する工程において、前記他の犠牲膜も除去することにより、他のギャップも形成し、

前記分子材料を形成する工程において、前記他のギャップ内にも前記分子材料を形成する付記4〜8のいずれか1つに記載の分子メモリ装置の製造方法。

【0061】

(付記10)

前記犠牲膜を形成する工程、前記他の配線層を形成する工程、前記他の犠牲膜を形成する工程、並びに、前記第3絶縁部材、前記第3配線及び前記第4絶縁部材からなる更に他の配線層を形成する工程を、複数回繰り返し、

前記犠牲膜を除去する工程において、全ての前記犠牲膜及び全ての前記他の犠牲膜を、一括して除去する付記9記載の分子メモリ装置の製造方法。

【0062】

(付記11)

前記第1絶縁部材をシリコン窒化物により形成し、前記第2配線部材をシリコン酸化物により形成する付記2〜10のいずれか1つに記載の分子メモリ装置の製造方法。

【0063】

(付記12)

前記犠牲膜をランタンアルミニウムシリケートにより形成し、

前記犠牲膜を除去する工程は、前記犠牲膜を酸性の薬液によって溶解させる工程を有する付記2〜11のいずれか1つに記載の分子メモリ装置の製造方法。

【0064】

(付記13)

前記薬液はフッ酸を含む付記12記載の分子メモリ装置の製造方法。

【0065】

(付記14)

前記第1配線をタングステン又はチタン窒化物により形成し、前記第2配線をモリブデンにより形成し、前記分子材料をチオールリンカーを含む分子とする付記2〜13のいずれか1つに記載の分子メモリ装置の製造方法。

【符号の説明】

【0066】

1:分子メモリ装置、10:シリコン基板、11:多層配線層、12:電極パッド、13:シリコン酸化膜、14:シリコン窒化部材、15:メタル配線、16:シリコン酸化部材、20:配線層、21:犠牲膜、24:シリコン窒化部材、25:メタル配線、26:シリコン酸化部材、30:配線層、31:犠牲膜、32:エアギャップ、33:分子材料、34:溶剤、41:ビアホール、42:バリアメタル層、43:ビアコンタクト

【特許請求の範囲】

【請求項1】

タングステンからなり第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上にランタンアルミニウムシリケートからなる第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して直交した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、ランタンアルミニウムシリケートからなる第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に、前記第1犠牲膜及び前記第2犠牲膜並びに前記第2配線が露出した1本以上のビアホールを形成する工程と、

前記ビアホールを介して、前記第1犠牲膜及び前記第2犠牲膜をフッ酸を含む薬液によって溶解させることにより、ギャップを形成する工程と、

前記ギャップ内に、チオールリンカーを含む分子を含む溶剤を進入させることにより、前記ギャップ内に分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延びる複数本の第1のシリコン窒化部材を形成する工程と、

前記第1のシリコン窒化部材の側面上に、モリブデンからなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1のシリコン窒化部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1のシリコン窒化部材間であって前記第2配線間に、複数本の第1のシリコン酸化部材を前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第2のシリコン窒化部材を形成する工程と、

前記第2のシリコン窒化部材の側面上に、タングステンからなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第2のシリコン窒化部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第2のシリコン窒化部材間であって前記第3配線間に、複数本の第2のシリコン酸化部材を前記第2配線層に接するように形成する工程と、

を有し、

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記ビアホールを形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層を貫通するように前記ビアホールを形成する分子メモリ装置の製造方法。

【請求項2】

第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上に第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して交差した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に前記第1犠牲膜及び前記第2犠牲膜が露出した貫通部を形成する工程と、

前記貫通部を介して、前記第1犠牲膜及び前記第2犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第3配線、並びに、前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延び、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延び、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第3絶縁部材を形成する工程と、

前記第3絶縁部材の側面上に、前記第2配線とは異なる導電材料からなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第3絶縁部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第3絶縁部材間であって前記第3配線間に、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第4絶縁部材を、前記第2配線層に接するように形成する工程と、

を有した分子メモリ装置の製造方法。

【請求項3】

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記貫通部を形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層が内面に露出するように前記貫通部を形成する請求項2記載の分子メモリ装置の製造方法。

【請求項4】

第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、

前記配線層上に犠牲膜を形成する工程と、

前記犠牲膜上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記配線層に接するように形成する工程と、

前記犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備えた分子メモリ装置の製造方法。

【請求項5】

前記第1絶縁部材、前記第2配線及び前記第2絶縁部材からなる他の配線層、並びに、前記配線層に、その内面に前記犠牲膜が露出するように、貫通部を形成する工程と、

をさらに備え、

前記犠牲膜の除去及び前記分子材料の形成は、前記貫通部を介して行う請求項4記載の分子メモリ装置の製造方法。

【請求項1】

タングステンからなり第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上にランタンアルミニウムシリケートからなる第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して直交した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、ランタンアルミニウムシリケートからなる第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に、前記第1犠牲膜及び前記第2犠牲膜並びに前記第2配線が露出した1本以上のビアホールを形成する工程と、

前記ビアホールを介して、前記第1犠牲膜及び前記第2犠牲膜をフッ酸を含む薬液によって溶解させることにより、ギャップを形成する工程と、

前記ギャップ内に、チオールリンカーを含む分子を含む溶剤を進入させることにより、前記ギャップ内に分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延びる複数本の第1のシリコン窒化部材を形成する工程と、

前記第1のシリコン窒化部材の側面上に、モリブデンからなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1のシリコン窒化部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1のシリコン窒化部材間であって前記第2配線間に、複数本の第1のシリコン酸化部材を前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第2のシリコン窒化部材を形成する工程と、

前記第2のシリコン窒化部材の側面上に、タングステンからなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第2のシリコン窒化部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第2のシリコン窒化部材間であって前記第3配線間に、複数本の第2のシリコン酸化部材を前記第2配線層に接するように形成する工程と、

を有し、

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記ビアホールを形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層を貫通するように前記ビアホールを形成する分子メモリ装置の製造方法。

【請求項2】

第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、

前記第1配線層上に第1犠牲膜を形成する工程と、

前記第1犠牲膜上に、前記第1方向に対して交差した第2方向に延びる複数本の第2配線を含む第2配線層を形成する工程と、

前記第2配線層上に、第2犠牲膜を形成する工程と、

前記第2犠牲膜上に、前記第1方向に延びる複数本の第3配線を含む第3配線層を形成する工程と、

前記第2配線層及び前記第3配線層を貫通し、その内面に前記第1犠牲膜及び前記第2犠牲膜が露出した貫通部を形成する工程と、

前記貫通部を介して、前記第1犠牲膜及び前記第2犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第3配線、並びに、前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備え、

前記第2配線層を形成する工程は、

前記第1犠牲膜上に、前記第2方向に延び、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記第1犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記第1犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記第1配線層に接するように形成する工程と、

を有し、

前記第3配線層を形成する工程は、

前記第2犠牲膜上に、前記第1方向に延び、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第3絶縁部材を形成する工程と、

前記第3絶縁部材の側面上に、前記第2配線とは異なる導電材料からなる第3配線を形成すると共に、前記第2犠牲膜における隣り合う前記第3絶縁部材間であって前記第3配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第3絶縁部材間であって前記第3配線間に、前記第2犠牲膜とは異なる絶縁材料からなる複数本の第4絶縁部材を、前記第2配線層に接するように形成する工程と、

を有した分子メモリ装置の製造方法。

【請求項3】

前記第1犠牲膜を形成する工程、前記第2配線層を形成する工程、前記第2犠牲膜を形成する工程、及び前記第3配線層を形成する工程を、複数回繰り返し、

前記貫通部を形成する工程においては、全ての前記第2配線層及び全ての前記第3配線層が内面に露出するように前記貫通部を形成する請求項2記載の分子メモリ装置の製造方法。

【請求項4】

第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、

前記配線層上に犠牲膜を形成する工程と、

前記犠牲膜上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料からなる複数本の第1絶縁部材を形成する工程と、

前記第1絶縁部材の側面上に、前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、

隣り合う前記第1絶縁部材間であって前記第2配線間に、前記犠牲膜とは異なる絶縁材料からなる複数本の第2絶縁部材を、前記配線層に接するように形成する工程と、

前記犠牲膜を除去することにより、ギャップを形成する工程と、

前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し、他方には結合しない分子材料を形成する工程と、

を備えた分子メモリ装置の製造方法。

【請求項5】

前記第1絶縁部材、前記第2配線及び前記第2絶縁部材からなる他の配線層、並びに、前記配線層に、その内面に前記犠牲膜が露出するように、貫通部を形成する工程と、

をさらに備え、

前記犠牲膜の除去及び前記分子材料の形成は、前記貫通部を介して行う請求項4記載の分子メモリ装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−115295(P2013−115295A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−261445(P2011−261445)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]