半導体レーザ素子およびその製造方法

【課題】素子特性が低下するのを抑制することが可能な半導体レーザ素子を提供する。

【解決手段】この半導体レーザ素子は、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、素子部50の側端面と平行に延びるように設けられた一対の溝部20が設けられている。また、素子部50の両側端面には、溝部20と平行に延びるように、段差部30aが設けられており、GaAs基板1の裏面であって、段差部30aの底面の真下に位置する領域に、段差部30aと平行に延びるスクライブライン40が設けられている。

【解決手段】この半導体レーザ素子は、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、素子部50の側端面と平行に延びるように設けられた一対の溝部20が設けられている。また、素子部50の両側端面には、溝部20と平行に延びるように、段差部30aが設けられており、GaAs基板1の裏面であって、段差部30aの底面の真下に位置する領域に、段差部30aと平行に延びるスクライブライン40が設けられている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体レーザ素子およびその製造方法に関し、特に、高出力でレーザ光を出射可能な半導体レーザ素子およびその製造方法に関する。

【背景技術】

【0002】

従来、電流注入幅(ストライプ幅)を10μm以上に形成することによって、高出力でレーザ光を出射することが可能なブロードエリア型の半導体レーザ素子が知られている(たとえば、特許文献1参照)。

【0003】

上記特許文献1には、ストライプ幅が10μm以上のストライプリッジを有するとともに、活性層およびp型クラッド層における発光領域の両側の領域を二次元フォトニック結晶化したブロードエリア型の半導体レーザ素子が記載されている。このような従来のブロードエリア型半導体レーザ素子では、一般的に、活性層(発光層)が形成されている素子表面(上面)の素子長さ方向に素子分離溝を形成し、素子分離溝の底面に素子分離溝と平行にスクライブラインを設けた後、素子に応力を加えることによって、素子分離が行われる。

【特許文献1】特開2004−172506号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上記した従来のブロードエリア型半導体レーザ素子では、素子分離溝を形成し、素子分離溝の底面に素子分離溝と平行にスクライブラインを設けた後、素子に応力を加えることによって素子分離を行う際に、素子分離後のエッジ部に欠けが発生するという不都合があった。このため、エッジ部が欠けることによって活性層(発光層)内に結晶欠陥が引き起こされ、半導体レーザ素子の高出力動作時に、活性層(発光層)内の結晶欠陥が伸張および増殖するという不都合があった。その結果、素子特性が低下するという問題点があった。

【0005】

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、素子特性が低下するのを抑制することが可能な半導体レーザ素子およびその製造方法を提供することである。

【課題を解決するための手段】

【0006】

上記目的を達成するために、この発明の第1の局面における半導体レーザ素子は、基板と、基板の表面上に形成された発光層と発光層の電流注入領域を制限する電流ブロック層とを含む素子部と、電流注入領域を挟んで対向するとともに、素子部の上面から発光層より深い位置に達し、かつ、素子部の側端面と平行に延びるように設けられた一対の溝部とを備えている。

【0007】

この第1の局面による半導体レーザ素子では、上記のように、電流注入領域を挟んで対向するとともに、素子部の上面から発光層より深い位置に達し、かつ、素子部の側端面と平行に延びるように一対の溝部を設けることによって、素子部(発光層)の電流注入領域側と側端面側とを、溝部により隔てることができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを抑制することができる。すなわち、発光層内の結晶欠陥は、発光層の側端面近傍の領域に存在することになるため、素子部(発光層)の電流注入領域側と側端面側とを隔てる溝部によって、結晶欠陥が電流注入領域に伸張するのを妨げることができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを抑制することができる。その結果、素子特性が低下するのを抑制することができる。

【0008】

上記第1の局面による半導体レーザ素子において、好ましくは、溝部は、素子部の側端面と平行に延びるように、素子部の全長にわたって設けられている。このように構成すれば、素子部(発光層)の電流注入領域側と側端面側とを、溝部により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを有効に抑制することができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0009】

上記第1の局面による半導体レーザ素子において、溝部を、素子部の上面から基板に達する深さに設けることができる。

【0010】

上記第1の局面による半導体レーザ素子において、好ましくは、素子部上には、発光層に電流を注入するための電極が形成されており、溝部は、平面的に見て、電極を挟んで対向するように設けられている。このように構成すれば、溝部は、電極が形成されない領域に設けられるので、溝部を設ける際に、素子部の上面を覆う電極を除去する工程を省略することができる。これにより、発光層に電流を注入するための電極が素子部上に形成されている場合でも、製造工程が増加するのを抑制しながら、溝部を設けることができる。

【0011】

上記第1の局面による半導体レーザ素子において、好ましくは、素子部の両側端面には、溝部と平行に延びるように、段差部が設けられており、基板の裏面であって、段差部の底面の真下に位置する領域には、段差部と平行に延びるように、スクライブラインが設けられている。このように構成すれば、素子分離を行う部分の厚みを小さくすることができるので、容易に、基板の裏面に設けたスクライブラインを起点として素子分離を行うことができる。これにより、素子分離の際に、溝部に割れおよび欠けなどが発生するのを抑制することができるので、溝部を容易に設けることができるとともに、溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを抑制することができる。

【0012】

この場合において、好ましくは、段差部の底面は、溝部の底面よりも深い位置に設けられている。このように構成すれば、溝部の底面下部の厚みよりも、素子分離を行う部分の厚みを小さくすることができるので、より容易に、基板の裏面に設けたスクライブラインを起点として素子分離を行うことができる。これにより、素子分離の際に、溝部に割れおよび欠けなどが発生するのを有効に抑制することができるので、溝部をより容易に設けることができるとともに、溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを有効に抑制することができる。

【0013】

この発明の第2の局面における半導体レーザ素子の製造方法は、基板の表面上に、発光層と発光層の電流注入領域を制限する電流ブロック層とを含む素子部を形成する工程と、電流注入領域を挟んで対向するとともに、素子部の上面から基板に達する深さを有し、かつ、所定の方向に延びるように、一対の第1溝部を形成する工程と、素子部に、第1溝部の延びる方向と直交する共振器面を形成する工程と、第1溝部に沿って、一対の第1溝部の外側で素子分離を行う工程とを備えている。

【0014】

この第2の局面による半導体レーザ素子の製造方法では、上記のように、電流注入領域を挟んで対向するとともに、素子部の上面から基板に達する深さを有し、かつ、所定の方向に延びるように、一対の第1溝部を形成する工程を備えることによって、素子部(発光層)の電流注入領域側と素子分離を行う領域側とを、第1溝部により隔てることができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを抑制することができる。すなわち、発光層内の結晶欠陥は、発光層の素子分離を行う領域の近傍の領域に存在することになるため、素子部(発光層)の電流注入領域側と素子分離を行う領域側とを隔てる第1溝部によって、結晶欠陥が電流注入領域に伸張するのを妨げることができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを抑制することができる。その結果、素子特性が低下するのを抑制することができる。

【0015】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、第1溝部を形成する工程は、素子部に共振器面を形成した際に、素子部の全長にわたって、素子部の共振器面と直交する方向に延びるように、第1溝部を形成する工程を含む。このように構成すれば、素子部(発光層)の電流注入領域側と素子分離する領域側とを、第1溝部により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを有効に抑制することができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0016】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、第1溝部を形成する工程の前に、素子部上に、発光層に電流を注入するための電極を形成する工程を備え、第1溝部を形成する工程は、平面的に見て、電極を挟んで対向するように、一対の第1溝部を形成する工程を含む。このように構成すれば、電極が形成されない領域に第1溝部を設けることになるので、第1溝部を形成する際に、素子部の上面を覆う電極を除去する工程を省略することができる。これにより、発光層に電流を注入するための電極を素子部上に形成した場合でも、製造工程が増加するのを抑制しながら、第1溝部を形成することができる。

【0017】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、第1溝部を形成する工程は、第1溝部をエッチングにより形成する工程を含む。このように構成すれば、第1溝部を、電流注入領域を挟んで対向するとともに、素子部の上面から基板に達する深さを有し、かつ、所定の方向に延びるように形成する場合でも、エッチングにより、容易に第1溝部を形成することができる。

【0018】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、素子分離を行う工程は、一対の第1溝部の外側に、第1溝部と平行に延びるように、第2溝部を形成する工程と、基板の裏面であって、第2溝部の底面の真下に位置する領域に、第2溝部と平行に延びるように、スクライブラインを設ける工程と、スクライブラインを起点として基板を分割する工程とを含む。このように構成すれば、素子分離を行う部分の厚みを小さくすることができるので、スクライブラインを起点として基板を分割する工程により、容易に、素子分離を行うことができる。これにより、基板を分割する工程の際に、第1溝部に割れおよび欠けなどが発生するのを抑制することができるので、第1溝部を容易に形成することができるとともに、第1溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを抑制することができる。

【0019】

この場合において、好ましくは、第2溝部を形成する工程は、第2溝部を、第1溝部より深く形成する工程を有している。このように構成すれば、第1溝部の底面下部の厚みよりも、素子分離する部分の厚みを小さくすることができるので、スクライブラインを起点として基板を分割する工程により、より容易に、素子分離を行うことができる。これにより、基板を分割する工程の際に、第1溝部に割れおよび欠けなどが発生するのを有効に抑制することができるので、第1溝部をより容易に形成することができるとともに、第1溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを有効に抑制することができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施形態を図面に基づいて説明する。なお、本発明の一実施形態による半導体レーザ素子は、高出力でレーザ光を出射可能であるとともに、発光パターンが単峰性でないブロードエリア型の半導体レーザ素子である。

【0021】

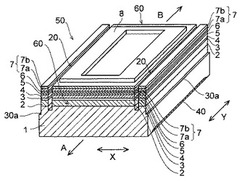

図1は、本発明の一実施形態による半導体レーザ素子の全体斜視図であり、図2は、図1に示した一実施形態による半導体レーザ素子の平面図である。図3〜図6は、図1に示した一実施形態による半導体レーザ素子の構造を説明するための図である。まず、図1〜図6を参照して、本発明の一実施形態による半導体レーザ素子の構造について説明する。

【0022】

一実施形態による半導体レーザ素子の素子部50は、図1および図2に示すように、共振器面60に直交する方向(矢印Y方向)に、約1000μmの長さ(L1)を有しているとともに、共振器面60に沿った方向(矢印X方向)に、約800μmの幅(W1)を有している。なお、素子部50には、劈開面からなる一対の共振器面60が形成されている。

【0023】

また、本実施形態による半導体レーザ素子は、図1および図3に示すように、約100μmの厚みを有するGaAs基板1上に、約3.3μmの厚みを有するn型Al0.48Ga0.52Asからなるn型クラッド層2が形成されている。n型クラッド層2上には、発光層3が形成されている。この発光層3は、図4に示すように、約9nmの厚みを有するGaAsからなる2つの量子井戸層3aと、約8nmの厚みを有するAl0.39Ga0.61Asからなる1つの障壁層3bとが交互に積層されたMQW(多重量子井戸)構造を有する活性層3cを含んでいる。また、活性層3cを挟むように、約30nmの厚みを有するAl0.39Ga0.61Asからなる光ガイド層3dおよび3eが設けられている。そして、活性層3c、光ガイド層3dおよび3eとによって、発光層3が構成されている。なお、GaAs基板1は、本発明の「基板」の一例である。

【0024】

また、発光層3の光ガイド層3e上には、図3に示すように、約1.2μmの厚みを有するp型Al0.49Ga0.51Asからなるp型クラッド層4が形成されている。p型クラッド層4上には、約0.5μmの厚みを有するp型GaAsからなるp型コンタクト層5が形成されている。p型コンタクト層5上には、約0.5μmの厚みを有するp型GaAsからなるp型キャップ層6が形成されている。p型キャップ層6上の所定の領域には、電流ブロック層7が形成されている。この電流ブロック層7は、図2、図3、および、図5に示すように、平面的に見て、電流注入領域70に対応する領域に開口部7cを有している。また、電流ブロック層7の開口部7cに対応する領域に形成された電流注入領域70は、図2に示すように、約360μmの幅W2を有するとともに、共振器面60に対して直交する方向(矢印Y方向)に延びる細長状(ストライプ状)に形成されている。

【0025】

また、素子部50の共振器面60の近傍には、電流ブロック層7によって、各共振器面60から約25μmの長さL2を有する電流非注入領域7dがそれぞれ形成されている。このように、共振器面60近傍に電流非注入領域7dを形成することにより、高出力動作時において、共振器面60近傍の温度上昇が抑制され、COD(Catastrophic Optical Damage)による半導体レーザ素子の破壊が抑制される。

【0026】

また、図1および図3に示すように、電流ブロック層7は、p型キャップ層6側から、約0.6μmの厚みを有するn型Al0.7Ga0.3Asからなるn型AlGaAs層7aと、約0.3μmの厚みを有するn型GaAs層7bとが積層された2層構造を有している。

【0027】

そして、図3に示すように、p型キャップ層6上および電流ブロック層7上には、p型キャップ層6および電流ブロック層7側から、Cr層と、Au層と、Pt層と、Au層とが順次積層された約2.3μmの厚みを有するp側電極8が形成されている。なお、P側電極8は、本発明の「電極」の一例である。また、GaAs基板1の裏面上には、GaAs基板1側から、Au層と、Ge層と、Au層と、Ni層と、Au層と、Pt層と、Au層とが順次積層された約1.2μmの厚みを有するn側電極9が形成されている。

【0028】

ここで、本実施形態では、図1〜図3に示すように、半導体レーザ素子には、電流注入領域70を挟んで対向する一対の溝部20がエッチングにより形成されている。この溝部20は、約10μmの幅W3(図3参照)を有するとともに、共振器面60に直交する方向である矢印Y方向に延びるように、素子部50の全長にわたって形成されている。また、溝部20は、図1および図3に示すように、素子部50の上面から発光層3より深い位置であるGaAs基板1に達する深さまで形成されている。なお、一対の溝部20は、エッチングにより形成されているため、発光層3に結晶欠陥が引き起こされることなく、溝部20が形成される。また、図2に示すように、一対の溝部20は、平面的に見て、p側電極8を挟んで対向するように設けられている。

【0029】

また、本実施形態では、図1〜図3に示すように、素子部50の共振器面60と直交する方向(矢印Y方向)に延びる両側端面には、側端面に沿って延びるように、素子部50の全長にわたって、段差部30aが設けられている。この段差部30aは、後述する溝部30(図17参照)で素子を分離する際に形成されたものである。また、段差部30aの底面は、約5μmの幅(W4)を有している。また、段差部30aの底面は、GaAs基板1に形成されているとともに、一対の溝部20よりも深い位置に形成されている。

【0030】

また、本実施形態では、図1、図3、および、図6に示すように、GaAs基板1の裏面であるとともに、両側端面に設けられた段差部30aの底面の真下に位置する領域には、素子分離の際に基点となったスクライブライン40が段差部30aと平行に延びるように設けられている。具体的には、スクライブライン40は、GaAs基板1の裏面のエッジ部に設けられている。このスクライブライン40は、図6に示すように、各共振器面60からそれぞれ50μm以上の長さL3だけ離れた位置に設けられている。すなわち、スクライブライン40は、素子部50の長さ方向(矢印Y方向)の中心から対称に、素子部50の長さ(L1:約1000μm)よりも小さい長さである約900μmの長さ(L4)に設けられている。

【0031】

また、図2に示すように、レーザ光を出射する側(A側)の共振器面60には、約142nmの合計厚みを有する前面反射率4%の前面誘電体層10が形成されている。この前面誘電体層10は、共振器面60側から、約2nmの厚みを有するSi層と、約140nmの厚みを有するAl2O3層とによって構成されている。また、レーザ光を出射する側と反対側(B側)の共振器面60には、約590nmの合計厚みを有する後面反射率95%の後面誘電体層11が形成されている。この後面誘電体層11は、共振器面60側から、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層とによって構成されている。

【0032】

本実施形態では、上記のように、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、素子部50の側端面と平行に延びるように、素子部50の全長にわたり一対の溝部20を設けることによって、素子部50の電流注入領域70側と側端面側とを、溝部20により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層3(活性層3c)内に結晶欠陥が引き起こされた場合でも、発光層3内の結晶欠陥が電流注入領域70に伸張するのを有効に抑制することができる。すなわち、発光層3内の結晶欠陥は、発光層3の側端面近傍の領域に存在することになるため、素子部50の電流注入領域70側と側端面側とを隔てる溝部20によって、結晶欠陥が電流注入領域70に伸張するのを妨げることができる。これにより、電流注入領域70に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0033】

また、本実施形態では、溝部20を、平面的に見て、P側電極8を挟んで対向するように設けることによって、溝部20を設ける際に、素子部50の上面を覆うP側電極8を除去する工程を省略することができるので、発光層3に電流を注入するためのP側電極8が素子部50上に形成されている場合でも、製造工程が増加するのを抑制しながら、溝部20を設けることができる。

【0034】

図7〜図20は、図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための図である。次に、図1〜図5、および、図7〜図20を参照して、本発明の一実施形態による半導体レーザ素子の製造方法について説明する。

【0035】

まず、図7に示すように、MOCVD法(Metal Organic Chemical Vapor Deposition:有機金属気相成長法)などを用いて、約350μmの厚みを有するとともに、{100}結晶面から約4°傾斜したGaAs基板1の上面上に、約3.3μmの厚みを有するn型Al0.48Ga0.52Asからなるn型クラッド層2、発光層3、約1.2μmの厚みを有するp型Al0.49Ga0.51Asからなるp型クラッド層4、約0.5μmの厚みを有するp型GaAsからなるp型コンタクト層5、および、約0.5μmの厚みを有するp型GaAsからなるp型キャップ層6を順次成長させる。

【0036】

なお、発光層3は、図4に示したように、約30nmの厚みを有するAl0.39Ga0.61Asからなる光ガイド層3d上に、MQW構造を有する活性層3c、および、約30nmの厚みを有するAl0.39Ga0.61Asからなる光ガイド層3eを順次成長させることにより形成する。また、活性層3cは、約9nmの厚みを有するGaAsからなる2つの量子井戸層3aと、約8nmの厚みを有するAl0.39Ga0.61Asからなる1つの障壁層3bとを交互に積層することにより形成する。

【0037】

次に、図8に示すように、p型キャップ層6上に、p型キャップ層6側から、約0.6μmの厚みを有するn型Al0.18Ga0.82Asからなるn型AlGaAs層7aと、約0.3μmの厚みを有するn型GaAs層7bとを順次成長させることによって、n型AlGaAs層7aとn型GaAs層7bとの2層からなる電流ブロック層7を形成する。

【0038】

そして、図9に示すように、フォトリソグラフィ技術を用いて、電流ブロック層7上の所定の領域にレジスト膜12を形成する。その後、図10に示すように、形成したレジスト膜12をマスクとして、電流ブロック層7をエッチングする。これにより、図2および図5に示したような、幅W2(約360μm)を有する、電流注入領域70に対応する開口部7cが電流ブロック層7に形成される。その後、形成したレジスト膜12を除去することにより、図11に示す形状を得る。

【0039】

次に、図12に示すように、真空蒸着法などを用いて、p型キャップ層6上および電流ブロック層7上に、p型キャップ層6および電流ブロック層7側から、Cr層と、Au層と、Pt層と、Au層とが順次積層された約2.3μmの合計厚みを有するp側電極8を形成する。

【0040】

続いて、図13に示すように、フォトリソグラフィ技術を用いて、電流ブロック層7上およびp側電極8上の所定の領域にレジスト膜13を形成する。次に、図14に示すように、形成したレジスト膜13をマスクとして、GaAs基板1に達する深さまで、素子部50の全長にわたってエッチングを行う。これにより、図1〜図3に示したような、電流注入領域70およびP側電極8を挟んで対向するとともに、矢印Y方向に延びる一対の溝部20が形成される。なお、溝部20は、本発明の「第1溝部」の一例である。その後、形成したレジスト膜13を除去することにより、図15に示す形状を得る。

【0041】

次に、図16に示すように、フォトリソグラフィ技術を用いて、再度、電流ブロック層7上およびp側電極8上の所定の領域にレジスト膜14を形成する。そして、図17に示すように、形成したレジスト膜14をマスクとして、GaAs基板1に達する深さまで、素子部50の全長にわたってエッチングを行う。この際、先に形成した溝部20の深さよりも深くなるように、エッチングを行う。これにより、溝部20と平行に延びる溝部30が形成される。その後、形成したレジスト膜14を除去する。なお、溝部30は、本発明の「第2溝部」の一例である。

【0042】

次に、GaAs基板1の裏面を研磨等の方法を用いて、GaAs基板1の厚みが約100μmの厚みになるまで薄くする。これは、後の素子分離工程において、GaAs基板1を割りやすくするためである。次に、図18に示すように、真空蒸着法などを用いて、GaAs基板1の裏面上に、GaAs基板1側から、Au層と、Ge層と、Au層と、Ni層と、Au層と、Pt層と、Au層とが順次積層された約1.2μmの合計厚みを有するn側電極9を形成する。そして、GaAs基板1をX方向に劈開し、一対の共振器面60を形成するとともに、形成した共振器面60に誘電体層を形成する。具体的には、図2に示したように、素子部50のレーザ光を出射する側(A側)の共振器面60に、共振器面60側から、約2nmの厚みを有するSi層と、約140nmの厚みを有するAl2O3層とが積層された約142nmの厚みを有するとともに、前面反射率4%の前面誘電体層10を形成する。また、レーザ光を出射する側と反対側(B側)の共振器面60に、共振器面60側から、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層とが積層された約590nmの厚みを有するとともに、後面反射率95%の後面誘電体層11を形成する。

【0043】

次に、図19および図20に示すように、GaAs基板1の裏面であって、溝部30の底面の真下に位置する領域に、溝部30と平行に延びるスクライブライン40を設ける。この際、図20に示すように、各共振器面60からそれぞれ50μm以上の長さL3だけ離れるようにスクライブライン40を形成する。具体的には、素子部50の長さ方向(矢印Y方向)の中心から対称に、素子部50の長さ(L1:約1000μm)よりも小さい長さである約900μmの長さ(L4)にスクライブライン40を形成する。これにより、素子分離の際に、GaAs基板1のコーナ部に欠けが発生するのが抑制される。

【0044】

最後に、素子に応力を加えることによって、GaAs基板1を分割し、素子分離を行う。このようにして、図1に示した本発明の一実施形態による半導体レーザ素子が形成される。

【0045】

本実施形態では、上記のように、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、矢印Y方向に延びるように、素子部50の全長にわたり一対の溝部20を形成することによって、素子部50の電流注入領域70側と素子分離を行う領域側とを、溝部20により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層3内に結晶欠陥が引き起こされた場合でも、発光層3内の結晶欠陥が電流注入領域70に伸張するのを有効に抑制することができる。すなわち、発光層3内の結晶欠陥は、発光層3の素子分離を行う領域の近傍の領域に存在することになるため、素子部50の電流注入領域70側と素子分離を行う領域側とを隔てる溝部20によって、結晶欠陥が電流注入領域70に伸張するのを妨げることができる。これにより、電流注入領域70に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0046】

また、本実施形態では、平面的に見て、P側電極8を挟んで対向するように、一対の溝部20を形成することによって、溝部20を形成する際に、素子部50の上面を覆うP側電極8を除去する工程を省略することができるので、発光層3に電流を注入するためのP側電極8を素子部50上に形成した場合でも、製造工程が増加するのを抑制しながら、溝部20を形成することができる。

【0047】

また、本実施形態では、溝部20をエッチングにより形成することによって、溝部20を、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、矢印Y方向に延びるように形成する場合でも、エッチングにより、容易に溝部20を形成することができる。

【0048】

また、本実施形態では、素子分離を行う際に、一対の溝部20の外側に、溝部20と平行に延びるように、溝部30を形成し、GaAs基板1の裏面であって、溝部30の底面の真下に位置する領域に、溝部30と平行に延びるように、スクライブライン40を設け、かつ、スクライブライン40を起点としてGaAs基板1を分割することによって、素子分離を行う部分の厚みを小さくすることができるので、素子分離工程の際に、容易に、スクライブライン40を起点としてGaAs基板1を分割することができる。これにより、GaAs基板1を分割する際に、溝部20に割れおよび欠けなどが発生するのを抑制することができるので、溝部20を容易に形成することができるとともに、溝部20に割れおよび欠けなどが発生することに起因して、発光層3に結晶欠陥が引き起こされるのを抑制することができる。

【0049】

また、本実施形態では、溝部30を、溝部20より深く形成することによって、溝部20の底面下部の厚みよりも、素子分離する部分の厚みを小さくすることができるので、素子分離工程の際に、より容易に、スクライブライン40を起点としてGaAs基板1を分割することができる。これにより、GaAs基板1を分割する際に、溝部20に割れおよび欠けなどが発生するのを有効に抑制することができるので、溝部20をより容易に形成することができるとともに、溝部20に割れおよび欠けなどが発生することに起因して、発光層3に結晶欠陥が引き起こされるのを有効に抑制することができる。

【0050】

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

【0051】

たとえば、上記実施形態では、一対の溝部を、素子部の全長にわたって形成した例を示したが、本発明はこれに限らず、一対の溝部は、素子部のほぼ全長にわたって形成されていればよく、一部に溝部が形成されていない部分があってもよい。

【0052】

また、上記実施形態では、一対の溝部を、素子部の上面からGaAs基板に達する深さまで形成した例を示したが、本発明はこれに限らず、一対の溝部は、発光層よりも深い位置に達していれば、GaAs基板に達していなくてもよい。

【0053】

また、上記実施形態では、素子部の両側端面に段差部を設けるとともに、段差部の底面の位置を、一対の溝部の底面よりも深い位置に設けた例を示したが、本発明はこれに限らず、段差部の底面は、一対の溝部の底面と同一または一対の溝部の底面よりも浅い位置に設けるようにしてもよい。なお、段差部の底面を、一対の溝部の底面と同じ深さ位置に設けた場合には、溝部を形成する工程と同一工程で、段差部となる前の溝部を形成することができるので、製造工程が増加するのを抑制しながら、段差部を設けることができる。

【0054】

また、上記実施形態では、素子部の両側端面に段差部を設けた例を示したが、本発明はこれに限らず、一対の溝部の外側の領域で素子分離が行われれば、素子部の両側端面に段差部を設けない構成にしてもよい。

【0055】

また、上記実施形態では、スクライブラインを、各共振器面からそれぞれ50μm以上離れた位置に設けた例を示したが、本発明はこれに限らず、スクライブラインを、各共振器面に達するように、素子部の全長にわたって設けるようにしてもよい。すなわち、スクライブラインの長さを、素子部の長さと同じ長さに構成してもよい。

【図面の簡単な説明】

【0056】

【図1】本発明の一実施形態による半導体レーザ素子の全体斜視図である。

【図2】図1に示した本発明の一実施形態による半導体レーザ素子の平面図である。

【図3】図2の100−100線に沿った断面図である。

【図4】本発明の一実施形態による半導体レーザ素子の発光層の構造を示した断面図である。

【図5】本発明の一実施形態による半導体レーザ素子のp側電極を省略した斜視図である。

【図6】図1に示した本発明の一実施形態による半導体レーザ素子を裏面側から見た平面図である。

【図7】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図8】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図9】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図10】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図11】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面である。

【図12】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図13】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図14】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図15】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図16】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図17】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図18】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図19】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図20】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための平面図である。

【符号の説明】

【0057】

1 GaAs基板(基板)

2 n型クラッド層

3 発光層

3a 量子井戸層

3b 障壁層

3c 活性層

3d、3e 光ガイド層

4 p型クラッド層

5 p型コンタクト層

6 p型キャップ層

7 電流ブロック層

8 p側電極(電極)

9 n側電極

10 前面誘電体層

11 後面誘電体層

20 溝部(第1溝部)

30a 段差部

30 溝部(第2溝部)

40 スクライブライン

50 素子部

60 共振器面

70 電流注入領域

【技術分野】

【0001】

本発明は、半導体レーザ素子およびその製造方法に関し、特に、高出力でレーザ光を出射可能な半導体レーザ素子およびその製造方法に関する。

【背景技術】

【0002】

従来、電流注入幅(ストライプ幅)を10μm以上に形成することによって、高出力でレーザ光を出射することが可能なブロードエリア型の半導体レーザ素子が知られている(たとえば、特許文献1参照)。

【0003】

上記特許文献1には、ストライプ幅が10μm以上のストライプリッジを有するとともに、活性層およびp型クラッド層における発光領域の両側の領域を二次元フォトニック結晶化したブロードエリア型の半導体レーザ素子が記載されている。このような従来のブロードエリア型半導体レーザ素子では、一般的に、活性層(発光層)が形成されている素子表面(上面)の素子長さ方向に素子分離溝を形成し、素子分離溝の底面に素子分離溝と平行にスクライブラインを設けた後、素子に応力を加えることによって、素子分離が行われる。

【特許文献1】特開2004−172506号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上記した従来のブロードエリア型半導体レーザ素子では、素子分離溝を形成し、素子分離溝の底面に素子分離溝と平行にスクライブラインを設けた後、素子に応力を加えることによって素子分離を行う際に、素子分離後のエッジ部に欠けが発生するという不都合があった。このため、エッジ部が欠けることによって活性層(発光層)内に結晶欠陥が引き起こされ、半導体レーザ素子の高出力動作時に、活性層(発光層)内の結晶欠陥が伸張および増殖するという不都合があった。その結果、素子特性が低下するという問題点があった。

【0005】

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、素子特性が低下するのを抑制することが可能な半導体レーザ素子およびその製造方法を提供することである。

【課題を解決するための手段】

【0006】

上記目的を達成するために、この発明の第1の局面における半導体レーザ素子は、基板と、基板の表面上に形成された発光層と発光層の電流注入領域を制限する電流ブロック層とを含む素子部と、電流注入領域を挟んで対向するとともに、素子部の上面から発光層より深い位置に達し、かつ、素子部の側端面と平行に延びるように設けられた一対の溝部とを備えている。

【0007】

この第1の局面による半導体レーザ素子では、上記のように、電流注入領域を挟んで対向するとともに、素子部の上面から発光層より深い位置に達し、かつ、素子部の側端面と平行に延びるように一対の溝部を設けることによって、素子部(発光層)の電流注入領域側と側端面側とを、溝部により隔てることができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを抑制することができる。すなわち、発光層内の結晶欠陥は、発光層の側端面近傍の領域に存在することになるため、素子部(発光層)の電流注入領域側と側端面側とを隔てる溝部によって、結晶欠陥が電流注入領域に伸張するのを妨げることができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを抑制することができる。その結果、素子特性が低下するのを抑制することができる。

【0008】

上記第1の局面による半導体レーザ素子において、好ましくは、溝部は、素子部の側端面と平行に延びるように、素子部の全長にわたって設けられている。このように構成すれば、素子部(発光層)の電流注入領域側と側端面側とを、溝部により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを有効に抑制することができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0009】

上記第1の局面による半導体レーザ素子において、溝部を、素子部の上面から基板に達する深さに設けることができる。

【0010】

上記第1の局面による半導体レーザ素子において、好ましくは、素子部上には、発光層に電流を注入するための電極が形成されており、溝部は、平面的に見て、電極を挟んで対向するように設けられている。このように構成すれば、溝部は、電極が形成されない領域に設けられるので、溝部を設ける際に、素子部の上面を覆う電極を除去する工程を省略することができる。これにより、発光層に電流を注入するための電極が素子部上に形成されている場合でも、製造工程が増加するのを抑制しながら、溝部を設けることができる。

【0011】

上記第1の局面による半導体レーザ素子において、好ましくは、素子部の両側端面には、溝部と平行に延びるように、段差部が設けられており、基板の裏面であって、段差部の底面の真下に位置する領域には、段差部と平行に延びるように、スクライブラインが設けられている。このように構成すれば、素子分離を行う部分の厚みを小さくすることができるので、容易に、基板の裏面に設けたスクライブラインを起点として素子分離を行うことができる。これにより、素子分離の際に、溝部に割れおよび欠けなどが発生するのを抑制することができるので、溝部を容易に設けることができるとともに、溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを抑制することができる。

【0012】

この場合において、好ましくは、段差部の底面は、溝部の底面よりも深い位置に設けられている。このように構成すれば、溝部の底面下部の厚みよりも、素子分離を行う部分の厚みを小さくすることができるので、より容易に、基板の裏面に設けたスクライブラインを起点として素子分離を行うことができる。これにより、素子分離の際に、溝部に割れおよび欠けなどが発生するのを有効に抑制することができるので、溝部をより容易に設けることができるとともに、溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを有効に抑制することができる。

【0013】

この発明の第2の局面における半導体レーザ素子の製造方法は、基板の表面上に、発光層と発光層の電流注入領域を制限する電流ブロック層とを含む素子部を形成する工程と、電流注入領域を挟んで対向するとともに、素子部の上面から基板に達する深さを有し、かつ、所定の方向に延びるように、一対の第1溝部を形成する工程と、素子部に、第1溝部の延びる方向と直交する共振器面を形成する工程と、第1溝部に沿って、一対の第1溝部の外側で素子分離を行う工程とを備えている。

【0014】

この第2の局面による半導体レーザ素子の製造方法では、上記のように、電流注入領域を挟んで対向するとともに、素子部の上面から基板に達する深さを有し、かつ、所定の方向に延びるように、一対の第1溝部を形成する工程を備えることによって、素子部(発光層)の電流注入領域側と素子分離を行う領域側とを、第1溝部により隔てることができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを抑制することができる。すなわち、発光層内の結晶欠陥は、発光層の素子分離を行う領域の近傍の領域に存在することになるため、素子部(発光層)の電流注入領域側と素子分離を行う領域側とを隔てる第1溝部によって、結晶欠陥が電流注入領域に伸張するのを妨げることができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを抑制することができる。その結果、素子特性が低下するのを抑制することができる。

【0015】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、第1溝部を形成する工程は、素子部に共振器面を形成した際に、素子部の全長にわたって、素子部の共振器面と直交する方向に延びるように、第1溝部を形成する工程を含む。このように構成すれば、素子部(発光層)の電流注入領域側と素子分離する領域側とを、第1溝部により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層内に結晶欠陥が引き起こされた場合でも、発光層内の結晶欠陥が電流注入領域に伸張するのを有効に抑制することができる。これにより、電流注入領域に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0016】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、第1溝部を形成する工程の前に、素子部上に、発光層に電流を注入するための電極を形成する工程を備え、第1溝部を形成する工程は、平面的に見て、電極を挟んで対向するように、一対の第1溝部を形成する工程を含む。このように構成すれば、電極が形成されない領域に第1溝部を設けることになるので、第1溝部を形成する際に、素子部の上面を覆う電極を除去する工程を省略することができる。これにより、発光層に電流を注入するための電極を素子部上に形成した場合でも、製造工程が増加するのを抑制しながら、第1溝部を形成することができる。

【0017】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、第1溝部を形成する工程は、第1溝部をエッチングにより形成する工程を含む。このように構成すれば、第1溝部を、電流注入領域を挟んで対向するとともに、素子部の上面から基板に達する深さを有し、かつ、所定の方向に延びるように形成する場合でも、エッチングにより、容易に第1溝部を形成することができる。

【0018】

上記第2の局面による半導体レーザ素子の製造方法において、好ましくは、素子分離を行う工程は、一対の第1溝部の外側に、第1溝部と平行に延びるように、第2溝部を形成する工程と、基板の裏面であって、第2溝部の底面の真下に位置する領域に、第2溝部と平行に延びるように、スクライブラインを設ける工程と、スクライブラインを起点として基板を分割する工程とを含む。このように構成すれば、素子分離を行う部分の厚みを小さくすることができるので、スクライブラインを起点として基板を分割する工程により、容易に、素子分離を行うことができる。これにより、基板を分割する工程の際に、第1溝部に割れおよび欠けなどが発生するのを抑制することができるので、第1溝部を容易に形成することができるとともに、第1溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを抑制することができる。

【0019】

この場合において、好ましくは、第2溝部を形成する工程は、第2溝部を、第1溝部より深く形成する工程を有している。このように構成すれば、第1溝部の底面下部の厚みよりも、素子分離する部分の厚みを小さくすることができるので、スクライブラインを起点として基板を分割する工程により、より容易に、素子分離を行うことができる。これにより、基板を分割する工程の際に、第1溝部に割れおよび欠けなどが発生するのを有効に抑制することができるので、第1溝部をより容易に形成することができるとともに、第1溝部に割れおよび欠けなどが発生することに起因して、発光層に結晶欠陥が引き起こされるのを有効に抑制することができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施形態を図面に基づいて説明する。なお、本発明の一実施形態による半導体レーザ素子は、高出力でレーザ光を出射可能であるとともに、発光パターンが単峰性でないブロードエリア型の半導体レーザ素子である。

【0021】

図1は、本発明の一実施形態による半導体レーザ素子の全体斜視図であり、図2は、図1に示した一実施形態による半導体レーザ素子の平面図である。図3〜図6は、図1に示した一実施形態による半導体レーザ素子の構造を説明するための図である。まず、図1〜図6を参照して、本発明の一実施形態による半導体レーザ素子の構造について説明する。

【0022】

一実施形態による半導体レーザ素子の素子部50は、図1および図2に示すように、共振器面60に直交する方向(矢印Y方向)に、約1000μmの長さ(L1)を有しているとともに、共振器面60に沿った方向(矢印X方向)に、約800μmの幅(W1)を有している。なお、素子部50には、劈開面からなる一対の共振器面60が形成されている。

【0023】

また、本実施形態による半導体レーザ素子は、図1および図3に示すように、約100μmの厚みを有するGaAs基板1上に、約3.3μmの厚みを有するn型Al0.48Ga0.52Asからなるn型クラッド層2が形成されている。n型クラッド層2上には、発光層3が形成されている。この発光層3は、図4に示すように、約9nmの厚みを有するGaAsからなる2つの量子井戸層3aと、約8nmの厚みを有するAl0.39Ga0.61Asからなる1つの障壁層3bとが交互に積層されたMQW(多重量子井戸)構造を有する活性層3cを含んでいる。また、活性層3cを挟むように、約30nmの厚みを有するAl0.39Ga0.61Asからなる光ガイド層3dおよび3eが設けられている。そして、活性層3c、光ガイド層3dおよび3eとによって、発光層3が構成されている。なお、GaAs基板1は、本発明の「基板」の一例である。

【0024】

また、発光層3の光ガイド層3e上には、図3に示すように、約1.2μmの厚みを有するp型Al0.49Ga0.51Asからなるp型クラッド層4が形成されている。p型クラッド層4上には、約0.5μmの厚みを有するp型GaAsからなるp型コンタクト層5が形成されている。p型コンタクト層5上には、約0.5μmの厚みを有するp型GaAsからなるp型キャップ層6が形成されている。p型キャップ層6上の所定の領域には、電流ブロック層7が形成されている。この電流ブロック層7は、図2、図3、および、図5に示すように、平面的に見て、電流注入領域70に対応する領域に開口部7cを有している。また、電流ブロック層7の開口部7cに対応する領域に形成された電流注入領域70は、図2に示すように、約360μmの幅W2を有するとともに、共振器面60に対して直交する方向(矢印Y方向)に延びる細長状(ストライプ状)に形成されている。

【0025】

また、素子部50の共振器面60の近傍には、電流ブロック層7によって、各共振器面60から約25μmの長さL2を有する電流非注入領域7dがそれぞれ形成されている。このように、共振器面60近傍に電流非注入領域7dを形成することにより、高出力動作時において、共振器面60近傍の温度上昇が抑制され、COD(Catastrophic Optical Damage)による半導体レーザ素子の破壊が抑制される。

【0026】

また、図1および図3に示すように、電流ブロック層7は、p型キャップ層6側から、約0.6μmの厚みを有するn型Al0.7Ga0.3Asからなるn型AlGaAs層7aと、約0.3μmの厚みを有するn型GaAs層7bとが積層された2層構造を有している。

【0027】

そして、図3に示すように、p型キャップ層6上および電流ブロック層7上には、p型キャップ層6および電流ブロック層7側から、Cr層と、Au層と、Pt層と、Au層とが順次積層された約2.3μmの厚みを有するp側電極8が形成されている。なお、P側電極8は、本発明の「電極」の一例である。また、GaAs基板1の裏面上には、GaAs基板1側から、Au層と、Ge層と、Au層と、Ni層と、Au層と、Pt層と、Au層とが順次積層された約1.2μmの厚みを有するn側電極9が形成されている。

【0028】

ここで、本実施形態では、図1〜図3に示すように、半導体レーザ素子には、電流注入領域70を挟んで対向する一対の溝部20がエッチングにより形成されている。この溝部20は、約10μmの幅W3(図3参照)を有するとともに、共振器面60に直交する方向である矢印Y方向に延びるように、素子部50の全長にわたって形成されている。また、溝部20は、図1および図3に示すように、素子部50の上面から発光層3より深い位置であるGaAs基板1に達する深さまで形成されている。なお、一対の溝部20は、エッチングにより形成されているため、発光層3に結晶欠陥が引き起こされることなく、溝部20が形成される。また、図2に示すように、一対の溝部20は、平面的に見て、p側電極8を挟んで対向するように設けられている。

【0029】

また、本実施形態では、図1〜図3に示すように、素子部50の共振器面60と直交する方向(矢印Y方向)に延びる両側端面には、側端面に沿って延びるように、素子部50の全長にわたって、段差部30aが設けられている。この段差部30aは、後述する溝部30(図17参照)で素子を分離する際に形成されたものである。また、段差部30aの底面は、約5μmの幅(W4)を有している。また、段差部30aの底面は、GaAs基板1に形成されているとともに、一対の溝部20よりも深い位置に形成されている。

【0030】

また、本実施形態では、図1、図3、および、図6に示すように、GaAs基板1の裏面であるとともに、両側端面に設けられた段差部30aの底面の真下に位置する領域には、素子分離の際に基点となったスクライブライン40が段差部30aと平行に延びるように設けられている。具体的には、スクライブライン40は、GaAs基板1の裏面のエッジ部に設けられている。このスクライブライン40は、図6に示すように、各共振器面60からそれぞれ50μm以上の長さL3だけ離れた位置に設けられている。すなわち、スクライブライン40は、素子部50の長さ方向(矢印Y方向)の中心から対称に、素子部50の長さ(L1:約1000μm)よりも小さい長さである約900μmの長さ(L4)に設けられている。

【0031】

また、図2に示すように、レーザ光を出射する側(A側)の共振器面60には、約142nmの合計厚みを有する前面反射率4%の前面誘電体層10が形成されている。この前面誘電体層10は、共振器面60側から、約2nmの厚みを有するSi層と、約140nmの厚みを有するAl2O3層とによって構成されている。また、レーザ光を出射する側と反対側(B側)の共振器面60には、約590nmの合計厚みを有する後面反射率95%の後面誘電体層11が形成されている。この後面誘電体層11は、共振器面60側から、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層とによって構成されている。

【0032】

本実施形態では、上記のように、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、素子部50の側端面と平行に延びるように、素子部50の全長にわたり一対の溝部20を設けることによって、素子部50の電流注入領域70側と側端面側とを、溝部20により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層3(活性層3c)内に結晶欠陥が引き起こされた場合でも、発光層3内の結晶欠陥が電流注入領域70に伸張するのを有効に抑制することができる。すなわち、発光層3内の結晶欠陥は、発光層3の側端面近傍の領域に存在することになるため、素子部50の電流注入領域70側と側端面側とを隔てる溝部20によって、結晶欠陥が電流注入領域70に伸張するのを妨げることができる。これにより、電流注入領域70に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0033】

また、本実施形態では、溝部20を、平面的に見て、P側電極8を挟んで対向するように設けることによって、溝部20を設ける際に、素子部50の上面を覆うP側電極8を除去する工程を省略することができるので、発光層3に電流を注入するためのP側電極8が素子部50上に形成されている場合でも、製造工程が増加するのを抑制しながら、溝部20を設けることができる。

【0034】

図7〜図20は、図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための図である。次に、図1〜図5、および、図7〜図20を参照して、本発明の一実施形態による半導体レーザ素子の製造方法について説明する。

【0035】

まず、図7に示すように、MOCVD法(Metal Organic Chemical Vapor Deposition:有機金属気相成長法)などを用いて、約350μmの厚みを有するとともに、{100}結晶面から約4°傾斜したGaAs基板1の上面上に、約3.3μmの厚みを有するn型Al0.48Ga0.52Asからなるn型クラッド層2、発光層3、約1.2μmの厚みを有するp型Al0.49Ga0.51Asからなるp型クラッド層4、約0.5μmの厚みを有するp型GaAsからなるp型コンタクト層5、および、約0.5μmの厚みを有するp型GaAsからなるp型キャップ層6を順次成長させる。

【0036】

なお、発光層3は、図4に示したように、約30nmの厚みを有するAl0.39Ga0.61Asからなる光ガイド層3d上に、MQW構造を有する活性層3c、および、約30nmの厚みを有するAl0.39Ga0.61Asからなる光ガイド層3eを順次成長させることにより形成する。また、活性層3cは、約9nmの厚みを有するGaAsからなる2つの量子井戸層3aと、約8nmの厚みを有するAl0.39Ga0.61Asからなる1つの障壁層3bとを交互に積層することにより形成する。

【0037】

次に、図8に示すように、p型キャップ層6上に、p型キャップ層6側から、約0.6μmの厚みを有するn型Al0.18Ga0.82Asからなるn型AlGaAs層7aと、約0.3μmの厚みを有するn型GaAs層7bとを順次成長させることによって、n型AlGaAs層7aとn型GaAs層7bとの2層からなる電流ブロック層7を形成する。

【0038】

そして、図9に示すように、フォトリソグラフィ技術を用いて、電流ブロック層7上の所定の領域にレジスト膜12を形成する。その後、図10に示すように、形成したレジスト膜12をマスクとして、電流ブロック層7をエッチングする。これにより、図2および図5に示したような、幅W2(約360μm)を有する、電流注入領域70に対応する開口部7cが電流ブロック層7に形成される。その後、形成したレジスト膜12を除去することにより、図11に示す形状を得る。

【0039】

次に、図12に示すように、真空蒸着法などを用いて、p型キャップ層6上および電流ブロック層7上に、p型キャップ層6および電流ブロック層7側から、Cr層と、Au層と、Pt層と、Au層とが順次積層された約2.3μmの合計厚みを有するp側電極8を形成する。

【0040】

続いて、図13に示すように、フォトリソグラフィ技術を用いて、電流ブロック層7上およびp側電極8上の所定の領域にレジスト膜13を形成する。次に、図14に示すように、形成したレジスト膜13をマスクとして、GaAs基板1に達する深さまで、素子部50の全長にわたってエッチングを行う。これにより、図1〜図3に示したような、電流注入領域70およびP側電極8を挟んで対向するとともに、矢印Y方向に延びる一対の溝部20が形成される。なお、溝部20は、本発明の「第1溝部」の一例である。その後、形成したレジスト膜13を除去することにより、図15に示す形状を得る。

【0041】

次に、図16に示すように、フォトリソグラフィ技術を用いて、再度、電流ブロック層7上およびp側電極8上の所定の領域にレジスト膜14を形成する。そして、図17に示すように、形成したレジスト膜14をマスクとして、GaAs基板1に達する深さまで、素子部50の全長にわたってエッチングを行う。この際、先に形成した溝部20の深さよりも深くなるように、エッチングを行う。これにより、溝部20と平行に延びる溝部30が形成される。その後、形成したレジスト膜14を除去する。なお、溝部30は、本発明の「第2溝部」の一例である。

【0042】

次に、GaAs基板1の裏面を研磨等の方法を用いて、GaAs基板1の厚みが約100μmの厚みになるまで薄くする。これは、後の素子分離工程において、GaAs基板1を割りやすくするためである。次に、図18に示すように、真空蒸着法などを用いて、GaAs基板1の裏面上に、GaAs基板1側から、Au層と、Ge層と、Au層と、Ni層と、Au層と、Pt層と、Au層とが順次積層された約1.2μmの合計厚みを有するn側電極9を形成する。そして、GaAs基板1をX方向に劈開し、一対の共振器面60を形成するとともに、形成した共振器面60に誘電体層を形成する。具体的には、図2に示したように、素子部50のレーザ光を出射する側(A側)の共振器面60に、共振器面60側から、約2nmの厚みを有するSi層と、約140nmの厚みを有するAl2O3層とが積層された約142nmの厚みを有するとともに、前面反射率4%の前面誘電体層10を形成する。また、レーザ光を出射する側と反対側(B側)の共振器面60に、共振器面60側から、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層と、約55nmの厚みを有するSi層と、約120nmの厚みを有するAl2O3層とが積層された約590nmの厚みを有するとともに、後面反射率95%の後面誘電体層11を形成する。

【0043】

次に、図19および図20に示すように、GaAs基板1の裏面であって、溝部30の底面の真下に位置する領域に、溝部30と平行に延びるスクライブライン40を設ける。この際、図20に示すように、各共振器面60からそれぞれ50μm以上の長さL3だけ離れるようにスクライブライン40を形成する。具体的には、素子部50の長さ方向(矢印Y方向)の中心から対称に、素子部50の長さ(L1:約1000μm)よりも小さい長さである約900μmの長さ(L4)にスクライブライン40を形成する。これにより、素子分離の際に、GaAs基板1のコーナ部に欠けが発生するのが抑制される。

【0044】

最後に、素子に応力を加えることによって、GaAs基板1を分割し、素子分離を行う。このようにして、図1に示した本発明の一実施形態による半導体レーザ素子が形成される。

【0045】

本実施形態では、上記のように、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、矢印Y方向に延びるように、素子部50の全長にわたり一対の溝部20を形成することによって、素子部50の電流注入領域70側と素子分離を行う領域側とを、溝部20により完全に分離することができるので、素子分離の際に側端面のエッジ部に欠けが生じ、その欠けによって発光層3内に結晶欠陥が引き起こされた場合でも、発光層3内の結晶欠陥が電流注入領域70に伸張するのを有効に抑制することができる。すなわち、発光層3内の結晶欠陥は、発光層3の素子分離を行う領域の近傍の領域に存在することになるため、素子部50の電流注入領域70側と素子分離を行う領域側とを隔てる溝部20によって、結晶欠陥が電流注入領域70に伸張するのを妨げることができる。これにより、電流注入領域70に対応した発光領域において、結晶欠陥が増殖するのを有効に抑制することができるので、半導体レーザ素子を高出力で動作させた場合でも、素子の劣化速度が速くなるのを有効に抑制することができる。その結果、素子特性が低下するのを有効に抑制することができる。

【0046】

また、本実施形態では、平面的に見て、P側電極8を挟んで対向するように、一対の溝部20を形成することによって、溝部20を形成する際に、素子部50の上面を覆うP側電極8を除去する工程を省略することができるので、発光層3に電流を注入するためのP側電極8を素子部50上に形成した場合でも、製造工程が増加するのを抑制しながら、溝部20を形成することができる。

【0047】

また、本実施形態では、溝部20をエッチングにより形成することによって、溝部20を、電流注入領域70を挟んで対向するとともに、素子部50の上面からGaAs基板1に達する深さを有し、かつ、矢印Y方向に延びるように形成する場合でも、エッチングにより、容易に溝部20を形成することができる。

【0048】

また、本実施形態では、素子分離を行う際に、一対の溝部20の外側に、溝部20と平行に延びるように、溝部30を形成し、GaAs基板1の裏面であって、溝部30の底面の真下に位置する領域に、溝部30と平行に延びるように、スクライブライン40を設け、かつ、スクライブライン40を起点としてGaAs基板1を分割することによって、素子分離を行う部分の厚みを小さくすることができるので、素子分離工程の際に、容易に、スクライブライン40を起点としてGaAs基板1を分割することができる。これにより、GaAs基板1を分割する際に、溝部20に割れおよび欠けなどが発生するのを抑制することができるので、溝部20を容易に形成することができるとともに、溝部20に割れおよび欠けなどが発生することに起因して、発光層3に結晶欠陥が引き起こされるのを抑制することができる。

【0049】

また、本実施形態では、溝部30を、溝部20より深く形成することによって、溝部20の底面下部の厚みよりも、素子分離する部分の厚みを小さくすることができるので、素子分離工程の際に、より容易に、スクライブライン40を起点としてGaAs基板1を分割することができる。これにより、GaAs基板1を分割する際に、溝部20に割れおよび欠けなどが発生するのを有効に抑制することができるので、溝部20をより容易に形成することができるとともに、溝部20に割れおよび欠けなどが発生することに起因して、発光層3に結晶欠陥が引き起こされるのを有効に抑制することができる。

【0050】

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

【0051】

たとえば、上記実施形態では、一対の溝部を、素子部の全長にわたって形成した例を示したが、本発明はこれに限らず、一対の溝部は、素子部のほぼ全長にわたって形成されていればよく、一部に溝部が形成されていない部分があってもよい。

【0052】

また、上記実施形態では、一対の溝部を、素子部の上面からGaAs基板に達する深さまで形成した例を示したが、本発明はこれに限らず、一対の溝部は、発光層よりも深い位置に達していれば、GaAs基板に達していなくてもよい。

【0053】

また、上記実施形態では、素子部の両側端面に段差部を設けるとともに、段差部の底面の位置を、一対の溝部の底面よりも深い位置に設けた例を示したが、本発明はこれに限らず、段差部の底面は、一対の溝部の底面と同一または一対の溝部の底面よりも浅い位置に設けるようにしてもよい。なお、段差部の底面を、一対の溝部の底面と同じ深さ位置に設けた場合には、溝部を形成する工程と同一工程で、段差部となる前の溝部を形成することができるので、製造工程が増加するのを抑制しながら、段差部を設けることができる。

【0054】

また、上記実施形態では、素子部の両側端面に段差部を設けた例を示したが、本発明はこれに限らず、一対の溝部の外側の領域で素子分離が行われれば、素子部の両側端面に段差部を設けない構成にしてもよい。

【0055】

また、上記実施形態では、スクライブラインを、各共振器面からそれぞれ50μm以上離れた位置に設けた例を示したが、本発明はこれに限らず、スクライブラインを、各共振器面に達するように、素子部の全長にわたって設けるようにしてもよい。すなわち、スクライブラインの長さを、素子部の長さと同じ長さに構成してもよい。

【図面の簡単な説明】

【0056】

【図1】本発明の一実施形態による半導体レーザ素子の全体斜視図である。

【図2】図1に示した本発明の一実施形態による半導体レーザ素子の平面図である。

【図3】図2の100−100線に沿った断面図である。

【図4】本発明の一実施形態による半導体レーザ素子の発光層の構造を示した断面図である。

【図5】本発明の一実施形態による半導体レーザ素子のp側電極を省略した斜視図である。

【図6】図1に示した本発明の一実施形態による半導体レーザ素子を裏面側から見た平面図である。

【図7】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図8】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図9】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図10】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図11】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面である。

【図12】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図13】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図14】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図15】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図16】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図17】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図18】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図19】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための断面図である。

【図20】図1に示した本発明の一実施形態による半導体レーザ素子の製造方法を説明するための平面図である。

【符号の説明】

【0057】

1 GaAs基板(基板)

2 n型クラッド層

3 発光層

3a 量子井戸層

3b 障壁層

3c 活性層

3d、3e 光ガイド層

4 p型クラッド層

5 p型コンタクト層

6 p型キャップ層

7 電流ブロック層

8 p側電極(電極)

9 n側電極

10 前面誘電体層

11 後面誘電体層

20 溝部(第1溝部)

30a 段差部

30 溝部(第2溝部)

40 スクライブライン

50 素子部

60 共振器面

70 電流注入領域

【特許請求の範囲】

【請求項1】

基板と、

前記基板の表面上に形成された発光層と前記発光層の電流注入領域を制限する電流ブロック層とを含む素子部と、

前記電流注入領域を挟んで対向するとともに、前記素子部の上面から前記発光層より深い位置に達し、かつ、前記素子部の側端面と平行に延びるように設けられた一対の溝部とを備えることを特徴とする、半導体レーザ素子。

【請求項2】

前記溝部は、前記素子部の側端面と平行に延びるように、前記素子部の全長にわたって設けられていることを特徴とする、請求項1に記載の半導体レーザ素子。

【請求項3】

前記溝部は、前記素子部の上面から前記基板に達する深さに設けられていることを特徴とする、請求項1または2に記載の半導体レーザ素子。

【請求項4】

前記素子部上には、前記発光層に電流を注入するための電極が形成されており、

前記溝部は、平面的に見て、前記電極を挟んで対向するように設けられていることを特徴とする、請求項1〜3のいずれか1項に記載の半導体レーザ素子。

【請求項5】

前記素子部の両側端面には、前記溝部と平行に延びるように、段差部が設けられており、

前記基板の裏面であって、前記段差部の底面の真下に位置する領域には、前記段差部と平行に延びるように、スクライブラインが設けられていることを特徴とする、請求項1〜4のいずれか1項に記載の半導体レーザ素子。

【請求項6】

前記段差部の底面は、前記溝部の底面よりも深い位置に設けられていることを特徴とする、請求項5に記載の半導体レーザ素子。

【請求項7】

基板の表面上に、発光層と前記発光層の電流注入領域を制限する電流ブロック層とを含む素子部を形成する工程と、

前記電流注入領域を挟んで対向するとともに、前記素子部の上面から前記基板に達する深さを有し、かつ、所定の方向に延びるように、一対の第1溝部を形成する工程と、

前記素子部に、前記第1溝部の延びる方向と直交する共振器面を形成する工程と、

前記第1溝部に沿って、一対の前記第1溝部の外側で素子分離を行う工程とを備えることを特徴とする、半導体レーザ素子の製造方法。

【請求項8】

前記第1溝部を形成する工程は、前記素子部に前記共振器面を形成した際に、前記素子部の全長にわたって、前記素子部の前記共振器面と直交する方向に延びるように、前記第1溝部を形成する工程を含むことを特徴とする、請求項7に記載の半導体レーザ素子の製造方法。

【請求項9】

前記第1溝部を形成する工程の前に、

前記素子部上に、前記発光層に電流を注入するための電極を形成する工程を備え、

前記第1溝部を形成する工程は、平面的に見て、前記電極を挟んで対向するように、一対の前記第1溝部を形成する工程を含むことを特徴とする、請求項7または8に記載の半導体レーザ素子の製造方法。

【請求項10】

前記第1溝部を形成する工程は、前記第1溝部をエッチングにより形成する工程を含むことを特徴とする、請求項7〜9のいずれか1項に記載の半導体レーザ素子の製造方法。

【請求項11】

前記素子分離を行う工程は、

一対の前記第1溝部の外側に、前記第1溝部と平行に延びるように、第2溝部を形成する工程と、

前記基板の裏面であって、前記第2溝部の底面の真下に位置する領域に、前記第2溝部と平行に延びるように、スクライブラインを設ける工程と、

前記スクライブラインを起点として前記基板を分割する工程とを含むことを特徴とする、請求項7〜10のいずれか1項に記載の半導体レーザ素子の製造方法。

【請求項12】

前記第2溝部を形成する工程は、前記第2溝部を、前記第1溝部より深く形成する工程を有することを特徴とする、請求項11に記載の半導体レーザ素子の製造方法。

【請求項1】

基板と、

前記基板の表面上に形成された発光層と前記発光層の電流注入領域を制限する電流ブロック層とを含む素子部と、

前記電流注入領域を挟んで対向するとともに、前記素子部の上面から前記発光層より深い位置に達し、かつ、前記素子部の側端面と平行に延びるように設けられた一対の溝部とを備えることを特徴とする、半導体レーザ素子。

【請求項2】

前記溝部は、前記素子部の側端面と平行に延びるように、前記素子部の全長にわたって設けられていることを特徴とする、請求項1に記載の半導体レーザ素子。

【請求項3】

前記溝部は、前記素子部の上面から前記基板に達する深さに設けられていることを特徴とする、請求項1または2に記載の半導体レーザ素子。

【請求項4】

前記素子部上には、前記発光層に電流を注入するための電極が形成されており、

前記溝部は、平面的に見て、前記電極を挟んで対向するように設けられていることを特徴とする、請求項1〜3のいずれか1項に記載の半導体レーザ素子。

【請求項5】

前記素子部の両側端面には、前記溝部と平行に延びるように、段差部が設けられており、

前記基板の裏面であって、前記段差部の底面の真下に位置する領域には、前記段差部と平行に延びるように、スクライブラインが設けられていることを特徴とする、請求項1〜4のいずれか1項に記載の半導体レーザ素子。

【請求項6】

前記段差部の底面は、前記溝部の底面よりも深い位置に設けられていることを特徴とする、請求項5に記載の半導体レーザ素子。

【請求項7】

基板の表面上に、発光層と前記発光層の電流注入領域を制限する電流ブロック層とを含む素子部を形成する工程と、

前記電流注入領域を挟んで対向するとともに、前記素子部の上面から前記基板に達する深さを有し、かつ、所定の方向に延びるように、一対の第1溝部を形成する工程と、

前記素子部に、前記第1溝部の延びる方向と直交する共振器面を形成する工程と、

前記第1溝部に沿って、一対の前記第1溝部の外側で素子分離を行う工程とを備えることを特徴とする、半導体レーザ素子の製造方法。

【請求項8】

前記第1溝部を形成する工程は、前記素子部に前記共振器面を形成した際に、前記素子部の全長にわたって、前記素子部の前記共振器面と直交する方向に延びるように、前記第1溝部を形成する工程を含むことを特徴とする、請求項7に記載の半導体レーザ素子の製造方法。

【請求項9】

前記第1溝部を形成する工程の前に、

前記素子部上に、前記発光層に電流を注入するための電極を形成する工程を備え、

前記第1溝部を形成する工程は、平面的に見て、前記電極を挟んで対向するように、一対の前記第1溝部を形成する工程を含むことを特徴とする、請求項7または8に記載の半導体レーザ素子の製造方法。

【請求項10】

前記第1溝部を形成する工程は、前記第1溝部をエッチングにより形成する工程を含むことを特徴とする、請求項7〜9のいずれか1項に記載の半導体レーザ素子の製造方法。

【請求項11】

前記素子分離を行う工程は、

一対の前記第1溝部の外側に、前記第1溝部と平行に延びるように、第2溝部を形成する工程と、

前記基板の裏面であって、前記第2溝部の底面の真下に位置する領域に、前記第2溝部と平行に延びるように、スクライブラインを設ける工程と、

前記スクライブラインを起点として前記基板を分割する工程とを含むことを特徴とする、請求項7〜10のいずれか1項に記載の半導体レーザ素子の製造方法。

【請求項12】

前記第2溝部を形成する工程は、前記第2溝部を、前記第1溝部より深く形成する工程を有することを特徴とする、請求項11に記載の半導体レーザ素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2008−66571(P2008−66571A)

【公開日】平成20年3月21日(2008.3.21)

【国際特許分類】

【出願番号】特願2006−244064(P2006−244064)

【出願日】平成18年9月8日(2006.9.8)

【出願人】(000001889)三洋電機株式会社 (18,308)

【出願人】(000214892)鳥取三洋電機株式会社 (1,582)

【Fターム(参考)】

【公開日】平成20年3月21日(2008.3.21)

【国際特許分類】

【出願日】平成18年9月8日(2006.9.8)

【出願人】(000001889)三洋電機株式会社 (18,308)

【出願人】(000214892)鳥取三洋電機株式会社 (1,582)

【Fターム(参考)】

[ Back to top ]