半導体素子の測定装置及び半導体素子の測定システム

【課題】測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置を提供する。

【解決手段】カード2上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数のDUT201と、カード2上にあるDUT201のうちの少なくとも1つを選択する選択情報を入力し、選択情報によって選択されたDUT201のみと対応する半導体素子と導通可能にするリレースイッチ203a、203bとでコンタクトカードを構成する。

【解決手段】カード2上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数のDUT201と、カード2上にあるDUT201のうちの少なくとも1つを選択する選択情報を入力し、選択情報によって選択されたDUT201のみと対応する半導体素子と導通可能にするリレースイッチ203a、203bとでコンタクトカードを構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子の測定装置及び半導体素子の測定システムに関する。

【背景技術】

【0002】

製品検査等の工程では、ウェハ上に複数チップ設けられた半導体素子(以下、単に素子とも記す。)をダイシングすることなく測定することがなされている。従来、素子の測定は、プローブと呼ばれる探針を素子の電極にあてて行われている。また、素子を複数同時に測定するため、複数のプローブを備えたプローブカードと呼ばれる測定装置が使用されている。

【0003】

ただし、プローブカードは、プローブを立てるスペースが必要になるために設置できるプローブ数が制限され、一度に測定できる素子数も制限される。このため、プローブカードを使った素子の測定は、一度により多くの素子を測定可能にし、検査工程を効率化するために改良の余地が残るものと言わざるを得なかった。

また、プローブカードによる測定は、プローブまたはウェハを一定の距離ずつx方向、y方向に移動して行われる。しかし、この動作(スキャンと記す。)は、一度に移動する距離の累積誤差がプローブの位置に大きく影響するため、プローブカードまたはウェハを移動させる機械的な制御に高い精度が要求される。

【0004】

さらに、プローブカードによる測定は、素子をいくつかの単位で測定しながらプローブまたはウェハをスキャンするため、すべての素子を測定し終わるのに時間がかかるという欠点がある。

以上の点を解消し、検査工程を効率化するため、プローブの代わりに電極を使って素子を測定するコンタクトカードがある。

【0005】

コンタクトカードでは、一般的に、測定の対象になるチップに合わせて被試験デバイス(DUT:Device Under Test)が予め複数配置されている。そして、すべてのDUTの電極を、それぞれに対応する素子の電極と同時に接触させ、ウェハ上の素子を一括して測定する。このため、コンタクトカードは、プローブカードよりも多くの素子を同時に測定できるうえ、コンタクトカードをウェハ上でスキャンする必要がないという利点を有する。

【0006】

ところが、コンタクトカードでは、多くの素子を同時に測定することから、素子が同時にスイッチングする際に発生するノイズが大きくなる。発生したノイズは、素子に印加される電圧のパルス波形に影響し、素子の測定に使用される装置(プローバ)の誤動作の原因になり得る。

スイッチング時のノイズは、測定のために印加される電圧の周波数を高めることによって大きくなる。このため、コンタクトカードによる測定は、高周波数を印加しての素子の測定がし難いという欠点がある。

【0007】

コンタクトカードにおけるノイズの影響を低減する技術としては、例えば、特許文献1に記載された発明がある。特許文献1に記載された発明を図5に示す。特許文献1に記載された発明は、導電性のゴム504をフレーム503によって支持する。そして、フレーム503と多層配線基板501のGNDや電源のパッド502とを接続することによってノイズを低減している。

【特許文献1】特開2002−33358

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上記した従来技術は、フレーム503を、ゴム504を支持するばかりでなくパッド502との電気的な接続をとることに併用している。このため、フレーム503の形状や構成が複雑化する、あるいは組み立て時にフレーム503とパッド502と正確に位置合わせする必要が生じる。フレーム503の複雑化はコンタクトカードの生産性を低下し、位置合わせの高度化は、コンタクトカードの信頼性を低下させるおそれがある。

【0009】

本発明は、以上の点に鑑みてなされたものであり、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置及び半導体素子の測定システムを提供することを目的とする。

【課題を解決するための手段】

【0010】

以上の課題を解決するため、本発明は、ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、カード本体と、前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力し、該選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、を備えることを特徴とする。

【0011】

このような発明によれば、測定に使用される電極をオペレータが任意に選択することができる。このため、ノイズが発生する位置にある電極同士を同時に測定に使用することを避けることができる。このような発明は、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置を提供することができる。

【0012】

また、本発明は、前記電極ユニットが、半導体素子の電極と接触する接触部が導電性を有するゴム部材でなることを特徴とする。

このような発明によれば、電極が素子の電極を傷つけることを防ぐことができる。

また、本発明の半導体素子の測定装置は、前記電極ユニットが、半導体素子の電極と接触する接触部が半導体素子の電極に沿った凹面を有することを特徴とする。

【0013】

このような発明によれば、半導体素子の電極と電極ユニットとの接触面積を増やし、半導体素子電極、電極ユニット間の導通を安定させることができる。

また、本発明の半導体素子の測定装置は、ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、コンタクトカード本体と、前記コンタクトカード本体上に設けられた複数の被試験デバイスと、複数の前記被試験デバイスのうち少なくとも一つを選択する選択情報を入力し、該選択情報によって選択された被試験デバイスのみを半導体素子の測定が可能な状態に切り換えるスイッチと、を備えることを特徴とする。

【0014】

このような発明によれば、測定に使用される被試験デバイスをオペレータが任意に選択することができる。このため、ノイズが発生する位置にある被試験デバイス同士を同時に測定に使用することを避けることができる。このような発明は、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置を提供することができる。

【0015】

また、本発明の半導体素子の測定システムは、ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定システムであって、カード本体と、前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、複数の前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力する選択情報入力手段と、前記選択情報入力手段によって入力した選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、前記導通素子選択手段によって導通可能になった電極ユニットと導通した半導体素子が出力する電気信号を表示する信号表示手段と、を備えることを特徴とする。

【0016】

このような発明によれば、測定に使用される電極をオペレータが任意に選択することができる。このため、ノイズが発生する位置にある電極同士を同時に測定に使用することを避けることができる。このような発明は、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子の測定システムを提供することができる。

【発明を実施するための最良の形態】

【0017】

以下、図を参照して本発明に係る半導体素子の測定装置及び半導体素子の測定システムの一実施の形態を説明する。

図1は、本実施形態の半導体素子の測定システムを示す図である。本実施形態の測定システムは、コンタクトカードCを使って半導体素子の特性を測定するシステムである。コンタクトカードCは、ウェハW上に形成されている半導体素子を複数チップ一括して測定する測定装置である。

【0018】

なお、測定の対象となるウェハW上の半導体素子は、例えばCSP(Chip Size Package)等のように、ウェハWの片面にバンプや電極を備えたものとする。

コンタクトカードCは、ウェハW上に形成された半導体素子(以下、単に素子と記す。)と一対一に対応する電極ユニットを複数備え、電極ユニットを各々対応する素子の電極に同時に接触させる構成である。コンタクトカードCの詳細な説明については、後述するものとする。

【0019】

図示したシステムは、コンタクトカードCを装着したプローバ101と、プローバ101を制御するPC103とを備えている。システムのオペレータは、PC103からコンタクトカードCにある複数の電極ユニットのうち少なくとも一つを選択する。PC103は、選択に係る情報(選択情報)を生成し、プローバ1に送信する。また、PC103は、選択された電極ユニットに対応する素子が出力した電気信号(測定の結果)を表示するディスプレイ105を備えている。

【0020】

このようなPC103は、本実施形態の選択情報入力手段、信号表示手段として機能する。

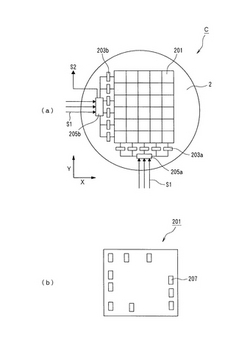

図2(a)、(b)は、本実施形態の測定装置であるコンタクトカードCを説明するための図である。図2のうち、(a)はコンタクトカードCの全体図である。(a)に示すように、コンタクトカードCは、ウェハ上に形成された素子と一対一に対応する電極ユニットであるDUT(Device Under Test)201を複数備えている。図2(b)は、DUT201のみを拡大して示す図である。

【0021】

DUT201は、図2(a)に示すように、コンタクトカード本体(カード本体)であるカード2上に配置されている。また、DUT201は、図2(b)に示すように、素子の電極と電気的に接続(以下コンタクトと記す。)して素子に電圧を印加する電極207を有している。本実施形態の電極207は、異方性導電ゴム製である。

図3は、コンタクトカードC及びウェハWの断面図であって、ウェハWの電極と電極207との関係を説明するための図である。本実施形態のDUT201は、測定される素子のウェハ上の配置に対応して配置されている。さらに、電極207は、各素子の電極(素子の電極をバンプ301として構成した例を示す。)の位置に対応する位置に設けられている。

【0022】

上記した構成のカード2は、ウェハWと所定の距離以下であって、かつバンプ等の電極を備える面に対向して置かれたとき、すべてのDUT201を各々対応する素子の電極に同時に接触させることができる。

また、本実施形態のコンタクトカードCは、DUT201の周辺にリレースイッチを備えている。DUT201の周辺のうち、X方向に配列されたリレースイッチを203aと記し、Y方向に配列されたリレースイッチを203bと記す。リレースイッチ203a、リレースイッチ203bは、PC103から送信された選択信号S1を選択信号S1として入力し、選択されたDUT201のみを対応する半導体素子と導通可能にする導通素子選択手段である。

【0023】

つまり、リレースイッチ203a、203bは、それぞれ選択信号S1として入力する。リレースイッチ203aに入力する選択信号S1は、複数配列されたDUT201のうちDUT201の図中に示すX方向の並び(行)を指定する。また、リレースイッチ203bに入力する選択信号S1は、複数配列されたDUT201のうちDUT201の図中に示すY方向の並び(列)を指定する。

【0024】

この結果、指定された行と列との交点にあるDUT201が対応する素子の電極と導通可能な状態になる。なお、本実施形態では、選択信号S1によって素子の電極と導通可能になるDUT201を指定することを、DUT201を選択するという。

また、本実施形態のコンタクトカードは、すべてのリレースイッチ203aと接続するスイッチ205a、すべてのリレースイッチ203bと接続するスイッチ205bを備えている。スイッチ205a、スイッチ205bは、それぞれ3本の信号線と接続し、3つの選択信号S1を入力する。そして、選択信号S1によって選択された行、あるいは列に対応するリレースイッチに選択信号S1を分配する。

【0025】

スイッチ205a、205bは、コンタクトカード上のDUT201のすべてを選択可能にしながら信号線の本数を制限するために設けられた構成である。本実施形態は、スイッチ205a、205bに3本の信号線を接続し、3つの素子を同時に測定することが可能である。なお、本実施形態の構成は、信号線を3本に限定するものでなく、コンタクトカードやプローバ101の構成や測定の必要に応じて信号線を何本設けてもよい。

【0026】

選択されたDUT201は、電力の供給を受ける(オンする。)。そして、電極207を介して素子の電極に電圧を印加し、素子特性を測定する。測定の結果を示す測定信号S2は、PC103に送信される。

以上述べた本実施形態のコンタクトカードCは、リレースイッチ203a、203bを設け、測定に使用されるDUT201をオペレータが任意に選択することができる。このため、オペレータが互いに離れた位置にあるDUT201をPC103上で選択することにより、ノイズの発生を低減することができる。

【0027】

また、本実施形態のコンタクトカードCは、測定にかかる構成に変更がなく、製造時にかかる負荷が増すことがない。このため、製造時の位置合わせ精度を高めることがなく、接触不良による不良品が発生する割合が低い。したがって、従来技術として挙げた発明よりも製品の信頼性が高い。

しかも、本実施形態は、ウェハ上の素子に一括してコンタクト可能なコンタクトカードCであるため、コンタクトカードCと素子とを一度コンタクトした後、PC上でDUT201の選択を変更することによってウェハ上のすべての素子を順次測定することができる。このため、素子をすべて同時に測定するコンタクトカードよりも測定時間は長くなる。ただし、スキャンにかかる時間は不要であり、全体としてプローブカードよりも測定時間を短縮することができる。

【0028】

また、本実施形態は、以上述べた構成に限定されるものではない。例えば、DUT201の電極207の形状は、図3に示したようにバンプ301と平面で接触するものに限定されるものではない。DUT201の電極の他の形状の例を図4(a)〜(d)に示す。

図4(a)〜(d)のうち、(a)に示す電極401は、基板内に埋め込まれていて、ウェハ側の電極と接する接触面f2が基板面f1と同一面上にある。また、(b)に示す電極402は、基板面f1よりも接触面f2が後退していて、接触面f2に凹面を形成する。さらに、(c)に示す電極403は、基板面f1よりも凸であって、接触面f2が凹面となっている。そして、(d)に示す電極404は、接触面f2が基板面f1よりも後退し、かつ、凹面となっている。

【0029】

(c)、(d)に示した接触面f2の凹面は、バンプの形状に合わせて形成されたものであり、特にバンプとコンタクトすることに適している。

このような実施形態によれば、DUT201と素子の電極との接触面積を増やし、半導体素子の電極、DUT201間の導通を安定させ、測定の信頼性を高めることができる。

【図面の簡単な説明】

【0030】

【図1】半導体素子の測定システムを示す図である。

【図2】本発明の一実施形態のコンタクトカードを説明するための図である。

【図3】図2に示したコンタクトカードの断面を示す図である。

【図4】実施形態で述べたコンタクトカードの他の例を示す図である。

【図5】従来技術を説明するための図である。

【符号の説明】

【0031】

101 プローバ、103 PC、105 ディスプレイ、

203a,203b リレースイッチ、205a,205b スイッチ、

207 電極、301 バンプ、401、402、403、404 電極

f1 基板面、f2 接触面

【技術分野】

【0001】

本発明は、半導体素子の測定装置及び半導体素子の測定システムに関する。

【背景技術】

【0002】

製品検査等の工程では、ウェハ上に複数チップ設けられた半導体素子(以下、単に素子とも記す。)をダイシングすることなく測定することがなされている。従来、素子の測定は、プローブと呼ばれる探針を素子の電極にあてて行われている。また、素子を複数同時に測定するため、複数のプローブを備えたプローブカードと呼ばれる測定装置が使用されている。

【0003】

ただし、プローブカードは、プローブを立てるスペースが必要になるために設置できるプローブ数が制限され、一度に測定できる素子数も制限される。このため、プローブカードを使った素子の測定は、一度により多くの素子を測定可能にし、検査工程を効率化するために改良の余地が残るものと言わざるを得なかった。

また、プローブカードによる測定は、プローブまたはウェハを一定の距離ずつx方向、y方向に移動して行われる。しかし、この動作(スキャンと記す。)は、一度に移動する距離の累積誤差がプローブの位置に大きく影響するため、プローブカードまたはウェハを移動させる機械的な制御に高い精度が要求される。

【0004】

さらに、プローブカードによる測定は、素子をいくつかの単位で測定しながらプローブまたはウェハをスキャンするため、すべての素子を測定し終わるのに時間がかかるという欠点がある。

以上の点を解消し、検査工程を効率化するため、プローブの代わりに電極を使って素子を測定するコンタクトカードがある。

【0005】

コンタクトカードでは、一般的に、測定の対象になるチップに合わせて被試験デバイス(DUT:Device Under Test)が予め複数配置されている。そして、すべてのDUTの電極を、それぞれに対応する素子の電極と同時に接触させ、ウェハ上の素子を一括して測定する。このため、コンタクトカードは、プローブカードよりも多くの素子を同時に測定できるうえ、コンタクトカードをウェハ上でスキャンする必要がないという利点を有する。

【0006】

ところが、コンタクトカードでは、多くの素子を同時に測定することから、素子が同時にスイッチングする際に発生するノイズが大きくなる。発生したノイズは、素子に印加される電圧のパルス波形に影響し、素子の測定に使用される装置(プローバ)の誤動作の原因になり得る。

スイッチング時のノイズは、測定のために印加される電圧の周波数を高めることによって大きくなる。このため、コンタクトカードによる測定は、高周波数を印加しての素子の測定がし難いという欠点がある。

【0007】

コンタクトカードにおけるノイズの影響を低減する技術としては、例えば、特許文献1に記載された発明がある。特許文献1に記載された発明を図5に示す。特許文献1に記載された発明は、導電性のゴム504をフレーム503によって支持する。そして、フレーム503と多層配線基板501のGNDや電源のパッド502とを接続することによってノイズを低減している。

【特許文献1】特開2002−33358

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上記した従来技術は、フレーム503を、ゴム504を支持するばかりでなくパッド502との電気的な接続をとることに併用している。このため、フレーム503の形状や構成が複雑化する、あるいは組み立て時にフレーム503とパッド502と正確に位置合わせする必要が生じる。フレーム503の複雑化はコンタクトカードの生産性を低下し、位置合わせの高度化は、コンタクトカードの信頼性を低下させるおそれがある。

【0009】

本発明は、以上の点に鑑みてなされたものであり、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置及び半導体素子の測定システムを提供することを目的とする。

【課題を解決するための手段】

【0010】

以上の課題を解決するため、本発明は、ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、カード本体と、前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力し、該選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、を備えることを特徴とする。

【0011】

このような発明によれば、測定に使用される電極をオペレータが任意に選択することができる。このため、ノイズが発生する位置にある電極同士を同時に測定に使用することを避けることができる。このような発明は、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置を提供することができる。

【0012】

また、本発明は、前記電極ユニットが、半導体素子の電極と接触する接触部が導電性を有するゴム部材でなることを特徴とする。

このような発明によれば、電極が素子の電極を傷つけることを防ぐことができる。

また、本発明の半導体素子の測定装置は、前記電極ユニットが、半導体素子の電極と接触する接触部が半導体素子の電極に沿った凹面を有することを特徴とする。

【0013】

このような発明によれば、半導体素子の電極と電極ユニットとの接触面積を増やし、半導体素子電極、電極ユニット間の導通を安定させることができる。

また、本発明の半導体素子の測定装置は、ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、コンタクトカード本体と、前記コンタクトカード本体上に設けられた複数の被試験デバイスと、複数の前記被試験デバイスのうち少なくとも一つを選択する選択情報を入力し、該選択情報によって選択された被試験デバイスのみを半導体素子の測定が可能な状態に切り換えるスイッチと、を備えることを特徴とする。

【0014】

このような発明によれば、測定に使用される被試験デバイスをオペレータが任意に選択することができる。このため、ノイズが発生する位置にある被試験デバイス同士を同時に測定に使用することを避けることができる。このような発明は、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子用測定装置を提供することができる。

【0015】

また、本発明の半導体素子の測定システムは、ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定システムであって、カード本体と、前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、複数の前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力する選択情報入力手段と、前記選択情報入力手段によって入力した選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、前記導通素子選択手段によって導通可能になった電極ユニットと導通した半導体素子が出力する電気信号を表示する信号表示手段と、を備えることを特徴とする。

【0016】

このような発明によれば、測定に使用される電極をオペレータが任意に選択することができる。このため、ノイズが発生する位置にある電極同士を同時に測定に使用することを避けることができる。このような発明は、測定時に発生するノイズを低減でき、しかも、製造時の位置合わせ精度を高めることなく信頼性が高い半導体素子の測定システムを提供することができる。

【発明を実施するための最良の形態】

【0017】

以下、図を参照して本発明に係る半導体素子の測定装置及び半導体素子の測定システムの一実施の形態を説明する。

図1は、本実施形態の半導体素子の測定システムを示す図である。本実施形態の測定システムは、コンタクトカードCを使って半導体素子の特性を測定するシステムである。コンタクトカードCは、ウェハW上に形成されている半導体素子を複数チップ一括して測定する測定装置である。

【0018】

なお、測定の対象となるウェハW上の半導体素子は、例えばCSP(Chip Size Package)等のように、ウェハWの片面にバンプや電極を備えたものとする。

コンタクトカードCは、ウェハW上に形成された半導体素子(以下、単に素子と記す。)と一対一に対応する電極ユニットを複数備え、電極ユニットを各々対応する素子の電極に同時に接触させる構成である。コンタクトカードCの詳細な説明については、後述するものとする。

【0019】

図示したシステムは、コンタクトカードCを装着したプローバ101と、プローバ101を制御するPC103とを備えている。システムのオペレータは、PC103からコンタクトカードCにある複数の電極ユニットのうち少なくとも一つを選択する。PC103は、選択に係る情報(選択情報)を生成し、プローバ1に送信する。また、PC103は、選択された電極ユニットに対応する素子が出力した電気信号(測定の結果)を表示するディスプレイ105を備えている。

【0020】

このようなPC103は、本実施形態の選択情報入力手段、信号表示手段として機能する。

図2(a)、(b)は、本実施形態の測定装置であるコンタクトカードCを説明するための図である。図2のうち、(a)はコンタクトカードCの全体図である。(a)に示すように、コンタクトカードCは、ウェハ上に形成された素子と一対一に対応する電極ユニットであるDUT(Device Under Test)201を複数備えている。図2(b)は、DUT201のみを拡大して示す図である。

【0021】

DUT201は、図2(a)に示すように、コンタクトカード本体(カード本体)であるカード2上に配置されている。また、DUT201は、図2(b)に示すように、素子の電極と電気的に接続(以下コンタクトと記す。)して素子に電圧を印加する電極207を有している。本実施形態の電極207は、異方性導電ゴム製である。

図3は、コンタクトカードC及びウェハWの断面図であって、ウェハWの電極と電極207との関係を説明するための図である。本実施形態のDUT201は、測定される素子のウェハ上の配置に対応して配置されている。さらに、電極207は、各素子の電極(素子の電極をバンプ301として構成した例を示す。)の位置に対応する位置に設けられている。

【0022】

上記した構成のカード2は、ウェハWと所定の距離以下であって、かつバンプ等の電極を備える面に対向して置かれたとき、すべてのDUT201を各々対応する素子の電極に同時に接触させることができる。

また、本実施形態のコンタクトカードCは、DUT201の周辺にリレースイッチを備えている。DUT201の周辺のうち、X方向に配列されたリレースイッチを203aと記し、Y方向に配列されたリレースイッチを203bと記す。リレースイッチ203a、リレースイッチ203bは、PC103から送信された選択信号S1を選択信号S1として入力し、選択されたDUT201のみを対応する半導体素子と導通可能にする導通素子選択手段である。

【0023】

つまり、リレースイッチ203a、203bは、それぞれ選択信号S1として入力する。リレースイッチ203aに入力する選択信号S1は、複数配列されたDUT201のうちDUT201の図中に示すX方向の並び(行)を指定する。また、リレースイッチ203bに入力する選択信号S1は、複数配列されたDUT201のうちDUT201の図中に示すY方向の並び(列)を指定する。

【0024】

この結果、指定された行と列との交点にあるDUT201が対応する素子の電極と導通可能な状態になる。なお、本実施形態では、選択信号S1によって素子の電極と導通可能になるDUT201を指定することを、DUT201を選択するという。

また、本実施形態のコンタクトカードは、すべてのリレースイッチ203aと接続するスイッチ205a、すべてのリレースイッチ203bと接続するスイッチ205bを備えている。スイッチ205a、スイッチ205bは、それぞれ3本の信号線と接続し、3つの選択信号S1を入力する。そして、選択信号S1によって選択された行、あるいは列に対応するリレースイッチに選択信号S1を分配する。

【0025】

スイッチ205a、205bは、コンタクトカード上のDUT201のすべてを選択可能にしながら信号線の本数を制限するために設けられた構成である。本実施形態は、スイッチ205a、205bに3本の信号線を接続し、3つの素子を同時に測定することが可能である。なお、本実施形態の構成は、信号線を3本に限定するものでなく、コンタクトカードやプローバ101の構成や測定の必要に応じて信号線を何本設けてもよい。

【0026】

選択されたDUT201は、電力の供給を受ける(オンする。)。そして、電極207を介して素子の電極に電圧を印加し、素子特性を測定する。測定の結果を示す測定信号S2は、PC103に送信される。

以上述べた本実施形態のコンタクトカードCは、リレースイッチ203a、203bを設け、測定に使用されるDUT201をオペレータが任意に選択することができる。このため、オペレータが互いに離れた位置にあるDUT201をPC103上で選択することにより、ノイズの発生を低減することができる。

【0027】

また、本実施形態のコンタクトカードCは、測定にかかる構成に変更がなく、製造時にかかる負荷が増すことがない。このため、製造時の位置合わせ精度を高めることがなく、接触不良による不良品が発生する割合が低い。したがって、従来技術として挙げた発明よりも製品の信頼性が高い。

しかも、本実施形態は、ウェハ上の素子に一括してコンタクト可能なコンタクトカードCであるため、コンタクトカードCと素子とを一度コンタクトした後、PC上でDUT201の選択を変更することによってウェハ上のすべての素子を順次測定することができる。このため、素子をすべて同時に測定するコンタクトカードよりも測定時間は長くなる。ただし、スキャンにかかる時間は不要であり、全体としてプローブカードよりも測定時間を短縮することができる。

【0028】

また、本実施形態は、以上述べた構成に限定されるものではない。例えば、DUT201の電極207の形状は、図3に示したようにバンプ301と平面で接触するものに限定されるものではない。DUT201の電極の他の形状の例を図4(a)〜(d)に示す。

図4(a)〜(d)のうち、(a)に示す電極401は、基板内に埋め込まれていて、ウェハ側の電極と接する接触面f2が基板面f1と同一面上にある。また、(b)に示す電極402は、基板面f1よりも接触面f2が後退していて、接触面f2に凹面を形成する。さらに、(c)に示す電極403は、基板面f1よりも凸であって、接触面f2が凹面となっている。そして、(d)に示す電極404は、接触面f2が基板面f1よりも後退し、かつ、凹面となっている。

【0029】

(c)、(d)に示した接触面f2の凹面は、バンプの形状に合わせて形成されたものであり、特にバンプとコンタクトすることに適している。

このような実施形態によれば、DUT201と素子の電極との接触面積を増やし、半導体素子の電極、DUT201間の導通を安定させ、測定の信頼性を高めることができる。

【図面の簡単な説明】

【0030】

【図1】半導体素子の測定システムを示す図である。

【図2】本発明の一実施形態のコンタクトカードを説明するための図である。

【図3】図2に示したコンタクトカードの断面を示す図である。

【図4】実施形態で述べたコンタクトカードの他の例を示す図である。

【図5】従来技術を説明するための図である。

【符号の説明】

【0031】

101 プローバ、103 PC、105 ディスプレイ、

203a,203b リレースイッチ、205a,205b スイッチ、

207 電極、301 バンプ、401、402、403、404 電極

f1 基板面、f2 接触面

【特許請求の範囲】

【請求項1】

ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、

カード本体と、

前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、

複数の前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力し、該選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、

を備えることを特徴とする半導体素子の測定装置。

【請求項2】

前記電極ユニットは、半導体素子の電極と接触する接触部が導電性を有するゴム部材でなることを特徴とする請求項1に記載の半導体素子の測定装置。

【請求項3】

前記電極ユニットは、半導体素子の電極と接触する接触部が半導体素子の電極に沿った凹面を有することを特徴とする請求項1に記載の半導体素子の測定装置。

【請求項4】

ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、

コンタクトカード本体と、

前記コンタクトカード本体上に設けられた複数の被試験デバイスと、

複数の前記被試験デバイスのうち少なくとも一つを選択する選択情報を入力し、該選択情報によって選択された被試験デバイスのみを半導体素子の測定が可能な状態に切り換えるスイッチと、

を備えることを特徴とする半導体素子の測定装置。

【請求項5】

ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定システムであって、

カード本体と、

前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、

複数の前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力する選択情報入力手段と、

前記選択情報入力手段によって入力した選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、

前記導通素子選択手段によって導通可能になった電極ユニットと導通した半導体素子が出力する電気信号を表示する信号表示手段と、

を備えることを特徴とする半導体素子の測定システム。

【請求項1】

ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、

カード本体と、

前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、

複数の前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力し、該選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、

を備えることを特徴とする半導体素子の測定装置。

【請求項2】

前記電極ユニットは、半導体素子の電極と接触する接触部が導電性を有するゴム部材でなることを特徴とする請求項1に記載の半導体素子の測定装置。

【請求項3】

前記電極ユニットは、半導体素子の電極と接触する接触部が半導体素子の電極に沿った凹面を有することを特徴とする請求項1に記載の半導体素子の測定装置。

【請求項4】

ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定装置であって、

コンタクトカード本体と、

前記コンタクトカード本体上に設けられた複数の被試験デバイスと、

複数の前記被試験デバイスのうち少なくとも一つを選択する選択情報を入力し、該選択情報によって選択された被試験デバイスのみを半導体素子の測定が可能な状態に切り換えるスイッチと、

を備えることを特徴とする半導体素子の測定装置。

【請求項5】

ウェハ上に形成されている複数の半導体素子と一括してコンタクト可能な半導体素子の測定システムであって、

カード本体と、

前記カード本体上にあって、ウェハ上に形成された複数の半導体素子と一対一に対応する複数の電極ユニットと、

複数の前記電極ユニットのうちの少なくとも1つを選択する選択情報を入力する選択情報入力手段と、

前記選択情報入力手段によって入力した選択情報によって選択された前記電極ユニットのみを半導体素子と導通可能にする導通素子選択手段と、

前記導通素子選択手段によって導通可能になった電極ユニットと導通した半導体素子が出力する電気信号を表示する信号表示手段と、

を備えることを特徴とする半導体素子の測定システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2006−41217(P2006−41217A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−219642(P2004−219642)

【出願日】平成16年7月28日(2004.7.28)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月28日(2004.7.28)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]