半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

【発明の詳細な説明】

【技術分野】

【0001】

トランジスタなどの半導体素子を含む回路を有する半導体装置に関する。例えば、電源回路に搭載されるパワーデバイス、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示装置に代表される電気光学装置、発光素子を有する発光表示装置などを部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置は、半導体特性を利用することで機能し得る装置全般を指し、電気光学装置、発光表示装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

液晶表示装置に代表されるように、ガラス基板などに形成されるトランジスタの多くはアモルファスシリコン、多結晶シリコンなどによって構成されている。アモルファスシリコンを用いたトランジスタは電界効果移動度が低いもののガラス基板の大面積化に対応することができる。また、多結晶シリコンを用いたトランジスタの電界効果移動度は高いがガラス基板の大面積化には適していないという欠点を有している。

【0004】

シリコンを用いたトランジスタのほかに、近年は酸化物半導体を用いてトランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体として、酸化亜鉛、In−Ga−Zn−O系酸化物を用いてトランジスタを作製し、表示装置の画素のスイッチング素子などに用いる技術が特許文献1および特許文献2で開示されている。

【0005】

酸化物半導体において、水素の一部はドナーとなり、キャリアである電子を放出する。酸化物半導体のキャリア濃度が高まると、ゲートに電圧を印加しなくてもトランジスタにチャネルが形成されてしまう。即ち、しきい値電圧が負方向にシフトする。酸化物半導体の水素を完全に取り除くことは困難であるため、しきい値電圧の制御も困難となる。

【0006】

特許文献3には、酸化物半導体膜中に水素を添加すると、導電率が4から5桁程度高くなることが示されている。また、酸化物半導体膜に接する絶縁膜から酸化物半導体膜に、水素が拡散していくことが示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−123861号公報

【特許文献2】特開2007−96055号公報

【特許文献3】特開2008−141119号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題とする。

【課題を解決するための手段】

【0009】

本発明の一態様は、酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させることを技術的思想とする。

【0010】

具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

【0011】

なお、酸化物半導体膜と水素捕縛膜との間に水素透過膜を設けることで、酸化物半導体膜の界面近傍の水素濃度を低減することができる。

【発明の効果】

【0012】

酸化物半導体膜を用いるトランジスタに、安定した電気的特性を付与し、信頼性の高い半導体装置を作製することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図2】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図3】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図4】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図5】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図6】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図7】図1に対応する半導体装置の作製方法の一例を示す断面図。

【図8】図2に対応する半導体装置の作製方法の一例を示す断面図。

【図9】図3に対応する半導体装置の作製方法の一例を示す断面図。

【図10】図4に対応する半導体装置の作製方法の一例を示す断面図。

【図11】図5に対応する半導体装置の作製方法の一例を示す断面図。

【図12】図6に対応する半導体装置の作製方法の一例を示す断面図。

【図13】本発明の一態様に係るトランジスタを用いた液晶表示装置の一例を示す回路図およびその電気的特性の一例を示す図。

【図14】本発明の一態様に係るトランジスタを用いた半導体記憶装置の一例を示す回路図およびその電気的特性の一例を示す図。

【図15】本発明の一態様に係るトランジスタを用いた半導体記憶装置の一例を示す回路図。

【図16】本発明の一態様に係るトランジスタを用いたCPUの具体例を示すブロック図およびその一部の回路図。

【図17】本発明の一態様に係る半導体装置を具備した電子機器の一例を示す斜視図。

【図18】SIMSによる水素濃度および窒素濃度の深さ方向分布を示す図。

【発明を実施するための形態】

【0014】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0015】

以下に本発明の説明を行うが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースと呼ぶ。すなわち、電位の高低によって、それらを区別しない。従って、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

【0016】

また、電圧は、ある電位と基準の電位(例えばグラウンド電位)との電位差のことを示す場合が多い。なお、電位を電圧と言い換えることが可能である。

【0017】

本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

【0018】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0019】

(実施の形態1)

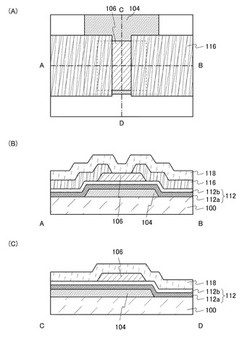

本実施の形態では、本発明の一態様のトランジスタの一例について図1を用いて説明する。

【0020】

図1(A)はトランジスタの上面図である。図1(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図1(B)に示すA−B断面および図1(C)に示すC−D断面に対応する。

【0021】

ここでは、図1(B)に示すA−B断面について詳細に説明する。

【0022】

トランジスタは、基板100と、基板100上のゲート電極104と、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112と、ゲート絶縁膜112を介してゲート電極104上にある酸化物半導体膜106と、酸化物半導体膜106上にあり酸化物半導体膜106と一部が接する一対の電極116と、を有する。なお、酸化物半導体膜106上に層間絶縁膜118を有すると、酸化物半導体膜106が露出しないため好ましい。

【0023】

ここで、第1のゲート絶縁膜112aは水素捕縛膜を、第2のゲート絶縁膜112bは水素透過膜を用いる。なお、酸化物半導体膜と水素捕縛膜との間に水素透過膜を設けることで、酸化物半導体膜の界面近傍の水素濃度を低減することができる。

【0024】

第1のゲート絶縁膜112aは、窒化インジウム(またはインジウム)を含む酸窒化物膜を用いればよい。具体的には、少なくとも窒化インジウムを含み、加えて酸化インジウム、酸化ガリウム、酸化亜鉛、酸化スズ、酸化アルミニウム、酸化タングステン、酸化モリブデン、酸化チタン、酸化タンタルおよび酸化シリコンの少なくとも一種以上を含む化合物材料を用いればよい。なお、酸窒化物とは、酸化物を構成する酸素の一部が窒素で置き換わった化合物をいう。

【0025】

例えば、第1のゲート絶縁膜112aは、窒素濃度が0.01atomic%以上7atomic%未満とすればよい。窒素濃度が0.01atomic%以上7atomic%未満である窒化インジウムを含む酸窒化物膜は、高い絶縁性を有する。または、第1のゲート絶縁膜112aは、7atomic%以上20atomic%以下とすればよい。窒素濃度が7atomic%以上20atomic%以下である窒化インジウムを含む酸窒化物膜は、水素と結合すると高い導電性を有することがある。第1のゲート絶縁膜112aの一部が高い導電性を有するとき、該一部がゲート電極の一部として機能することがある。このとき、高い絶縁性を有する第2のゲート絶縁膜112bを有することで、第1のゲート絶縁膜112aを介した一対の電極116およびゲート電極104からの電荷のリークを防ぐことができる。なお、第1のゲート絶縁膜112aの窒素濃度は、X線光電子分光法(XPS:X−ray Photoelectron Spectroscopy)分析によって定量化できる。

【0026】

窒化インジウムを含む酸窒化物膜中において、水素の一部はキャリアである電子を放出する。電子は負の電荷を有するため、ゲート電極側から負のバイアスが印加されているのと同様に電界を生じ、トランジスタのしきい値電圧を正方向にシフトさせる。なお、酸化物半導体膜を用いたトランジスタは、酸化物半導体膜内の酸素欠損および水素の一部がキャリアである電子を放出することで、しきい値電圧が負方向にシフトしやすい傾向がある。そのため、窒化インジウムを含む酸窒化物膜が有する負の電荷により、トランジスタのしきい値電圧を正方向にシフトさせると好ましい場合がある。なお、第1のゲート絶縁膜112aにおける水素濃度を制御することで、負の電荷量を調整することができる。第1のゲート絶縁膜112aにおける水素濃度は、第1のゲート絶縁膜112aの窒素濃度により調整することができる。

【0027】

第1のゲート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下とする。なお、第1のゲート絶縁膜112aの水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)によって定量化できる。

【0028】

第2のゲート絶縁膜112bは、高い絶縁性を有する酸化物膜を用いる。例えば、酸化シリコン膜または酸化窒化シリコン膜を用いればよい。なお、第2のゲート絶縁膜112bは、厚さが0.5nm以上15nm以下、好ましくは2nm以上5nm以下とする。第2のゲート絶縁膜112bの厚さが薄いほど、より低温で水素を拡散することが可能となる。

【0029】

ここで、酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものであって、好ましくは、酸素が50atomic%以上70atomic%以下、窒素が0.5atomic%以上15atomic%以下、シリコンが25atomic%以上35atomic%以下、水素が0atomic%以上10atomic%以下の範囲で含まれるものをいう。ただし、上記範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward scattering Spectrometry)を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100atomic%を超えない値をとる。

【0030】

酸化物半導体膜106の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下とする。酸化物半導体膜106中の水素濃度は、SIMSによって定量化できる。

【0031】

ここで、アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちナトリウム(Na)は、酸化物半導体膜に接する絶縁膜中に拡散してNa+となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、または、その結合中に割り込む。その結果、例えば、しきい値電圧が負方向にシフトすることによるノーマリオン化、電界効果移動度の低下などの、トランジスタの電気的特性の劣化が起こり、加えて、トランジスタの電気的特性のばらつきも生じる。この不純物によりもたらされるトランジスタの電気的特性の劣化と、トランジスタの電気的特性のばらつきは、酸化物半導体膜中の水素濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体膜中の水素濃度が1×1018cm−3以下、または1×1017cm−3以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、Na濃度の測定値は、5×1016cm−3以下、好ましくは1×1016cm−3以下、更に好ましくは1×1015cm−3以下とするとよい。同様に、リチウム(Li)濃度の測定値は、5×1015cm−3以下、好ましくは1×1015cm−3以下とするとよい。同様に、カリウム(K)濃度の測定値は、5×1015cm−3以下、好ましくは1×1015cm−3以下とするとよい。

【0032】

以上に示した酸化物半導体膜106を用いたトランジスタは、オフ電流を極めて小さくできる。例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電流は、1×10−18A以下、または1×10−21A以下、または1×10−24A以下となる。

【0033】

酸化物半導体膜106は、例えば、In、Ga、ZnおよびSnから選ばれた二種以上を含む材料を用いればよい。

【0034】

酸化物半導体膜106は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは3.0eV以上の材料を選択する。

【0035】

酸化物半導体膜106は、例えば、In−Sn−Ga−Zn−O系の材料や、In−Ga−Zn−O系の材料、In−Sn−Zn−O系の材料、In−Al−Zn−O系の材料、Sn−Ga−Zn−O系の材料、Al−Ga−Zn−O系の材料、Sn−Al−Zn−O系の材料や、In−Zn−O系の材料、Sn−Zn−O系の材料、Al−Zn−O系の材料、Zn−Mg−O系の材料、Sn−Mg−O系の材料、In−Mg−O系の材料、In−Ga−O系の材料や、In−O系の材料、Sn−O系の材料、Zn−O系の材料などを用いればよい。ここで、例えば、In−Ga−Zn−O系の材料は、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。このとき、酸化物半導体膜106の化学量論的組成比に対し、Oを過剰にすると好ましい。Oを過剰にすることで酸化物半導体膜106の酸素欠損に起因するキャリアの生成を抑制することができる。

【0036】

なお、酸化物半導体膜106の一例としてIn−Zn−O系の材料を用いる場合、原子数比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さらに好ましくはIn/Zn=1.5以上15以下とする。Znの原子数比を前述の範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい。

【0037】

酸化物半導体膜106として、化学式InMO3(ZnO)m(m>0)で表記される材料を用いてもよい。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGaおよびCoなどを用いてもよい。

【0038】

酸化物半導体膜106は、第1のゲート絶縁膜112aを構成する金属元素と同じ金属元素を有する材料で形成すると好ましい。これは、スパッタリング法で成膜する場合、同一ターゲットを用いて成膜ガスによって作り分けすることが可能となり、材料コストおよび装置コストを低減できるためである。例えば、酸化物半導体膜106としてIn−Ga−Zn−O膜を用いた場合、第1のゲート絶縁膜112aとしてIn−Ga−Zn−O−N膜を用いればよい。

【0039】

酸化物半導体膜106は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

【0040】

好ましくは、酸化物半導体膜106は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0041】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0042】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0043】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0044】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0045】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0046】

層間絶縁膜118は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、ポリイミドおよびアクリルなどを、単層で、または積層して用いればよく、例えば、プラズマCVD法、スパッタリング法およびスピンコート法などで形成する。また、層間絶縁膜118は、加熱処理により酸素を放出する膜を用いると好ましい。加熱処理により酸素を放出する膜を用いることで、酸化物半導体膜106に生じる酸素欠損を修復することができ、トランジスタの電気的特性の劣化を抑制できる。

【0047】

ここで、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものであって、好ましくは、酸素が5atomic%以上30atomic%以下、窒素が20atomic%以上55atomic%以下、シリコンが25atomic%以上35atomic%以下、水素が10atomic%以上25atomic%以下の範囲で含まれるものをいう。但し、上記範囲は、RBSや、HFSを用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100atomic%を超えない値をとる。

【0048】

「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018cm−3以上、または1.0×1020cm−3以上であることをいう。

【0049】

ここで、TDS分析にて、酸素の放出量の測定方法について、以下に説明する。

【0050】

TDS分析したときの気体の放出量は、イオン強度の積分値に比例する。このため、測定したイオン強度の積分値と、標準試料の基準値との比により、気体の放出量を計算することができる。標準試料の基準値とは、所定の密度の原子を含む試料において、当該原子に相当するイオン強度の積分値に対する当該原子の密度の割合である。

【0051】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、数式1で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0052】

NO2=NH2/SH2×SO2×α (数式1)

【0053】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのイオン強度の積分値である。αは、TDS分析におけるイオン強度に影響する係数である。数式1の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016cm−3の水素原子を含むシリコンウェハを用いて測定した。

【0054】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量について見積もることができる。

【0055】

なお、NO2は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0056】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものをいう。単位体積当たりのシリコン原子数および酸素原子数は、RBSにより測定した値である。

【0057】

層間絶縁膜118から酸化物半導体膜106に酸素が供給されること(酸素が移動するともいう。)で酸化物半導体膜106と層間絶縁膜118との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜106と層間絶縁膜118との界面にキャリアが捕獲されることを抑制することができ、電気的特性の劣化の少ないトランジスタを得ることができる。

【0058】

さらに、酸化物半導体膜106の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧が負方向へシフトしてしまう。層間絶縁膜118から酸化物半導体膜106に酸素が十分に供給されることにより、しきい値電圧が負方向へシフトする要因である、酸化物半導体膜106の酸素欠損を低減することができる。

【0059】

即ち、層間絶縁膜118に、加熱処理により酸素を放出する膜を設けることで、酸化物半導体膜106と層間絶縁膜118との界面の界面準位密度、ならびに酸化物半導体膜106の酸素欠損を低減し、酸化物半導体膜106と層間絶縁膜118との界面におけるキャリア捕獲の影響を小さくすることができる。

【0060】

このように、トランジスタのしきい値電圧が負方向へシフトする要因をできる限り除いた上で、酸化物半導体膜106に含まれる水素濃度を低減させることが好ましい。

【0061】

基板100に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI(Silicon On Insulator)基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

【0062】

基板100として、可とう性基板を用いてもよい。その場合は、可とう性基板上に直接トランジスタを作製すればよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。

【0063】

ゲート電極104は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一以上選択し、単層でまたは積層して用いればよい。

【0064】

なお、図1ではゲート電極104が酸化物半導体膜106よりも縦、横ともに大きい形状にすることで酸化物半導体膜106の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜106がゲート電極104よりも、上面図において縦、横ともに大きい形状にしても構わない。

【0065】

一対の電極116は、ゲート電極104で示した金属膜、金属窒化物膜、金属酸化物膜または合金膜などを単層でまたは積層して用いればよい。

【0066】

一対の電極116にCuを含む膜を用いると、配線の抵抗を低減でき、大型表示装置などでも配線遅延などの発生を低減することができる。一対の電極116にCuを用いる場合、基板100の材質によっては密着性が悪くなるため、基板100と密着性のよい膜との積層構造にすることが好ましい。基板100と密着性のよい膜として、Ti、Mo、Mn、CuまたはAlなどを含む膜を用いればよい。例えば、Cu−Mn−Al合金を用いてもよい。

【0067】

次に、図1に示したトランジスタの作製方法について、図7を用いて説明する。

【0068】

まず、基板100上に導電膜をスパッタリング法または蒸着法などで成膜し、加工してゲート電極104を形成する。次に、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112を形成する(図7(A)参照。)。

【0069】

第1のゲート絶縁膜112aは、プラズマCVD法、スパッタリング法、PLD(Pulse Laser Deposition)法、ALD(Atomic Layer Deposition)法などを用いて成膜すればよい。例えば、スパッタリング法を用いる場合、少なくとも酸化インジウムを含むターゲットを用いる。酸化インジウムに加えて酸化ガリウム、酸化亜鉛、酸化スズ、酸化アルミニウム、酸化タングステン、酸化モリブデン、酸化チタン、酸化タンタルおよび酸化シリコンの少なくとも一種以上を含む材料をターゲットに用いても構わない。成膜ガスには少なくとも窒素を含ませればよい。また成膜ガスとして、希ガス(ヘリウム、ネオン、アルゴン、クリプトン、キセノンなど)および酸素のいずれか一種以上を用いても構わない。このような方法で成膜することにより、窒素濃度が0.01atomic%以上7atomic%未満または7atomic%以上20atomic%以下である、少なくとも窒化インジウムを含む第1のゲート絶縁膜112aを成膜することができる。

【0070】

第2のゲート絶縁膜112bは、プラズマCVD法、スパッタリング法、PLD法、ALD法などを用いて、酸化シリコン膜または酸化窒化シリコン膜を成膜すればよい。

【0071】

次に、ゲート絶縁膜112を介してゲート電極104上に酸化物半導体膜136を成膜する(図7(B)参照。)。酸化物半導体膜136は、前述の材料を用い、スパッタリング法、PLD法、ALD法などを用いて成膜すればよい。

【0072】

次に、酸化物半導体膜136を加工して酸化物半導体膜106を形成する(図7(C)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜106から脱離した水素を、第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ移動させる。移動した水素は、第1のゲート絶縁膜112aで捕縛される。このとき、酸化物半導体膜106の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0073】

次に、導電膜をスパッタリング法または蒸着法などで成膜し、加工して酸化物半導体膜106と少なくとも一部が接する一対の電極116を形成する。次に、酸化物半導体膜106および一対の電極116上に層間絶縁膜118を形成してもよい(図7(D)参照。)。なお、酸化物半導体膜106を形成した後に行う加熱処理に代えて、層間絶縁膜118の形成後に同様の加熱処理を行っても構わない。

【0074】

以上のように、酸化物半導体膜106から第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ水素を移動させ、移動した水素を第1のゲート絶縁膜112aで捕縛することにより、高純度化された酸化物半導体膜106を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0075】

また、第1のゲート絶縁膜112aは、捕縛した水素の一部に起因して生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0076】

以上の工程によって、図1に示したトランジスタを作製することができる。

【0077】

続いて、図1に示したトランジスタとは異なる構造のトランジスタについて図2を用いて説明する。

【0078】

図2はトランジスタの上面図および断面図である。図2(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図2(B)に示すA−B断面および図2(C)に示すC−D断面に対応する。

【0079】

以下に、図2(B)に示すA−B断面について詳細に説明する。

【0080】

図2に示すトランジスタは、基板100と、基板100上のゲート電極104と、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112と、ゲート絶縁膜112上の一対の電極216と、ゲート絶縁膜112を介してゲート電極104上にあり、一対の電極216と一部が接する酸化物半導体膜206と、を有する。なお、ゲート絶縁膜112、一対の電極216および酸化物半導体膜206上に層間絶縁膜218を有すると、酸化物半導体膜206が露出しないため好ましい。ここで、一対の電極216、酸化物半導体膜206および層間絶縁膜218は、それぞれ一対の電極116、酸化物半導体膜106および層間絶縁膜118と同様の方法および同様の材料により形成する。

【0081】

なお、図2ではゲート電極104が酸化物半導体膜206よりも縦、横ともに大きい形状にすることで酸化物半導体膜206の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜206がゲート電極104よりも、上面図において縦、横ともに大きい形状としても構わない。

【0082】

次に、図2に示したトランジスタの作製方法について、図8を用いて説明する。

【0083】

まず、基板100上にゲート電極104を形成する。次に、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112を形成する。次に、ゲート絶縁膜112上に一対の電極216を形成する(図8(A)参照。)。

【0084】

次に、ゲート絶縁膜112を介してゲート電極104上に酸化物半導体膜236を成膜する(図8(B)参照。)。なお、酸化物半導体膜236は、酸化物半導体膜136と同様の方法および同様の材料により形成する。

【0085】

次に、酸化物半導体膜236を加工して一対の電極216と一部が接する酸化物半導体膜206を形成する(図8(C)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜206から脱離した水素を、第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ移動させる。移動した水素は、第1のゲート絶縁膜112aで捕縛される。このとき、酸化物半導体膜206の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0086】

次に、酸化物半導体膜206、一対の電極216上に層間絶縁膜218を形成してもよい(図8(D)参照。)。なお、酸化物半導体膜206を形成した後に行う加熱処理に代えて、層間絶縁膜218の形成後に同様の加熱処理を行っても構わない。

【0087】

以上のように、酸化物半導体膜206から第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ水素を移動させ、移動した水素を第1のゲート絶縁膜112aで捕縛することにより、高純度化された酸化物半導体膜206を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0088】

また、第1のゲート絶縁膜112aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。そのため、トランジスタの電気的特性をノーマリーオフ、またはノーマリーオフに近づけることができる。

【0089】

以上の工程によって、図2に示したトランジスタを作製することができる。

【0090】

続いて、図1および図2に示したトランジスタとは異なる構造のトランジスタについて図3を用いて説明する。

【0091】

図3はトランジスタの上面図および断面図である。図3(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図3(B)に示すA−B断面および図3(C)に示すC−D断面に対応する。

【0092】

以下に、図3(B)に示すA−B断面について詳細に説明する。

【0093】

図3に示すトランジスタは、基板100と、基板100上の下地絶縁膜302と、下地絶縁膜302上の酸化物半導体膜306と、酸化物半導体膜306上にあり酸化物半導体膜306と一部が接する一対の電極316と、酸化物半導体膜306および一対の電極316上の、第2のゲート絶縁膜312b、および第2のゲート絶縁膜312b上の第1のゲート絶縁膜312aからなるゲート絶縁膜312と、ゲート絶縁膜312を介して酸化物半導体膜306上にあるゲート電極304と、を有する。なお、基板100の表面状態によっては、下地絶縁膜302を設けない構成としても構わない。ここで、一対の電極316、酸化物半導体膜306、ゲート電極304およびゲート絶縁膜312は、それぞれ一対の電極116、酸化物半導体膜106、ゲート電極104およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0094】

また、下地絶縁膜302は、層間絶縁膜118の説明を参酌すればよい。

【0095】

なお、図3ではゲート電極304が酸化物半導体膜306よりも縦、横ともに大きい形状にすることで酸化物半導体膜306の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜306がゲート電極304よりも、上面図において縦、横ともに大きい形状としても構わない。

【0096】

次に、図3に示したトランジスタの作製方法について、図9を用いて説明する。

【0097】

まず、基板100上に下地絶縁膜302を形成する。次に、下地絶縁膜302上に酸化物半導体膜306を形成する。次に、酸化物半導体膜306上に、酸化物半導体膜306と少なくとも一部が接する一対の電極316を形成する(図9(A)参照。)。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

【0098】

次に、酸化物半導体膜306および一対の電極316上に、第2のゲート絶縁膜312b、および第2のゲート絶縁膜312b上の第1のゲート絶縁膜312aからなるゲート絶縁膜312を形成する(図9(B)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜306から脱離した水素を、第2のゲート絶縁膜312bを介して第1のゲート絶縁膜312aへ移動させる。移動した水素は、第1のゲート絶縁膜312aで捕縛される。このとき、酸化物半導体膜306の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜312aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0099】

次に、ゲート絶縁膜312を介して酸化物半導体膜306に重畳するゲート電極304を形成する(図9(C)参照。)。なお、ゲート絶縁膜312を形成した後に行う加熱処理に代えて、ゲート電極304の形成後に同様の加熱処理を行っても構わない。

【0100】

以上のように、酸化物半導体膜306から第2のゲート絶縁膜312bを介して第1のゲート絶縁膜312aへ水素を移動させ、移動した水素を第1のゲート絶縁膜312aで捕縛することにより、高純度化された酸化物半導体膜306を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0101】

また、第1のゲート絶縁膜312aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0102】

以上の工程によって、図3に示したトランジスタを作製することができる。

【0103】

続いて、図1乃至図3に示したトランジスタとは異なる構造のトランジスタについて図4を用いて説明する。

【0104】

図4はトランジスタの上面図および断面図である。図4(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図4(B)に示すA−B断面および図4(C)に示すC−D断面に対応する。

【0105】

以下に、図4(B)に示すA−B断面について詳細に説明する。

【0106】

図4に示すトランジスタは、基板100と、基板100上の下地絶縁膜302と、下地絶縁膜302上の一対の電極416と、一対の電極416上にあり一対の電極416と一部が接する酸化物半導体膜406と、酸化物半導体膜406および一対の電極416上の、第2のゲート絶縁膜412b、および第2のゲート絶縁膜412b上の第1のゲート絶縁膜412aからなるゲート絶縁膜412と、ゲート絶縁膜412を介して酸化物半導体膜406上にあるゲート電極404と、を有する。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。ここで、一対の電極416、酸化物半導体膜406、ゲート電極404およびゲート絶縁膜412は、それぞれ一対の電極116、酸化物半導体膜106、ゲート電極104およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0107】

なお、図4ではゲート電極404が酸化物半導体膜406よりも縦、横ともに大きい形状にすることで酸化物半導体膜406の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜406がゲート電極404よりも、上面図において縦、横ともに大きい形状としても構わない。

【0108】

次に、図4に示したトランジスタの作製方法について、図10を用いて説明する。

【0109】

まず、基板100上に下地絶縁膜302を形成する。次に、下地絶縁膜302上に一対の電極416を形成する(図10(A)参照。)。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

【0110】

次に、一対の電極416上に、一対の電極416と一部が接する酸化物半導体膜406を形成する(図10(B)参照。)。

【0111】

次に、酸化物半導体膜406、一対の電極416上に、第2のゲート絶縁膜412b、および第2のゲート絶縁膜412b上の第1のゲート絶縁膜412aからなるゲート絶縁膜412を形成する(図10(C)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜406から脱離した水素を、第2のゲート絶縁膜412bを介して第1のゲート絶縁膜412aへ移動させる。移動した水素は、第1のゲート絶縁膜412aで捕縛される。このとき、酸化物半導体膜406の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜412aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0112】

次に、ゲート絶縁膜412を介して酸化物半導体膜406に重畳するゲート電極404を形成する(図10(D)参照。)。なお、ゲート絶縁膜412を形成した後に行う加熱処理に代えて、ゲート電極404の形成後に同様の加熱処理を行っても構わない。

【0113】

以上のように、酸化物半導体膜406から第2のゲート絶縁膜412bを介して第1のゲート絶縁膜412aへ水素を移動させ、移動した水素を第1のゲート絶縁膜412aで捕縛することにより、高純度化された酸化物半導体膜406を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0114】

また、第1のゲート絶縁膜412aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0115】

以上の工程によって、図4に示したトランジスタを作製することができる。

【0116】

続いて、図1乃至図4に示したトランジスタとは異なる構造のトランジスタについて図5を用いて説明する。

【0117】

図5はトランジスタの上面図および断面図である。図5(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図5(B)に示すA−B断面および図5(C)に示すC−D断面に対応する。

【0118】

以下に、図5(B)に示すA−B断面について詳細に説明する。

【0119】

図5に示すトランジスタは、基板100と、基板100上の下地絶縁膜302と、下地絶縁膜302上のチャネル領域505、ソース領域507aおよびドレイン領域507bを有する酸化物半導体膜506と、酸化物半導体膜506上の、第2のゲート絶縁膜512b、および第2のゲート絶縁膜512b上の第1のゲート絶縁膜512aからなるゲート絶縁膜512と、ゲート絶縁膜512を介してチャネル領域505と重畳するゲート電極504と、酸化物半導体膜506およびゲート電極504上の層間絶縁膜518と、ゲート絶縁膜512および層間絶縁膜518に設けられた開口部を介して酸化物半導体膜506と接する一対の電極516と、を有する。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。ここで、一対の電極516、酸化物半導体膜506、ゲート電極504、層間絶縁膜518およびゲート絶縁膜512は、それぞれ一対の電極116、酸化物半導体膜106、ゲート電極104、層間絶縁膜118およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0120】

ここで、図示しないが、ゲート絶縁膜512およびゲート電極504は概略同一の上面形状としてもよい。この形状は、ゲート電極504およびゲート絶縁膜512を同一のマスクを用いて加工することで得られる。または、ゲート電極504をマスクに用いてゲート絶縁膜512を加工することによって得られる。

【0121】

なお、図5ではゲート絶縁膜512および層間絶縁膜518に設けられた開口部の上面形状は円形であるが、これに限定されるものではない。該開口部は、ソース領域507aおよびドレイン領域507bを露出するものであれば、形状は問わない。

【0122】

チャネル領域505は、ゲート電極504と概略同一の上面形状としてもよい。なお、ソース領域507aおよびドレイン領域507bは、窒素、リン、水素、または希ガスなどを含む。

【0123】

なお、チャネル領域505は高抵抗領域であり、ソース領域507aおよびドレイン領域507bは低抵抗領域である。

【0124】

次に、図5に示したトランジスタの作製方法について、図11を用いて説明する。

【0125】

まず、基板100上に下地絶縁膜302を形成する。次に、下地絶縁膜302上に酸化物半導体膜506を形成する。次に、下地絶縁膜302および酸化物半導体膜506上に、第2のゲート絶縁膜512b、および第2のゲート絶縁膜512b上の第1のゲート絶縁膜512aからなるゲート絶縁膜512を形成する(図11(A)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜506から脱離した水素を、第2のゲート絶縁膜512bを介して第1のゲート絶縁膜512aへ移動させる。移動した水素は、第1のゲート絶縁膜512aで捕縛される。このとき、酸化物半導体膜506の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜512aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

【0126】

次に、ゲート絶縁膜512を介して酸化物半導体膜506上にゲート電極504を形成する。なお、ゲート電極504を形成後、プラズマ処理または薬液処理によってゲート電極504の幅を細くしても構わない。

【0127】

次に、ゲート電極504をマスクに、酸化物半導体膜506の一部に窒素、リン、水素または希ガスを添加する。該添加、または該添加に加えて加熱処理を行うことにより、酸化物半導体膜506の、ゲート電極504と重畳しない領域を低抵抗化し、チャネル領域505、ソース領域507aおよびドレイン領域507bを形成する(図11(B)参照。)。なお、ここで行う加熱処理を、ゲート絶縁膜512を形成した後に行う加熱処理に代えることができる。

【0128】

次に、ゲート絶縁膜512およびゲート電極504上に層間絶縁膜518を形成し(図11(C)参照。)、ソース領域507aおよびドレイン領域507bをそれぞれ露出する開口部をゲート絶縁膜512および層間絶縁膜518に形成する。次に、酸化物半導体膜506と接する一対の電極516を形成する(図11(D)参照。)。なお、ゲート絶縁膜512を形成した後に行う加熱処理、ソース領域507aおよびドレイン領域507bを形成するための加熱処理に代えて、層間絶縁膜518または一対の電極516の形成後に同様の加熱処理を行っても構わない。

【0129】

以上のように、酸化物半導体膜506から第2のゲート絶縁膜512bを介して第1のゲート絶縁膜512aへ水素を移動させ、移動した水素を第1のゲート絶縁膜512aで捕縛することにより、高純度化された酸化物半導体膜506を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0130】

また、第1のゲート絶縁膜512aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0131】

なお、図11ではゲート絶縁膜512および層間絶縁膜518に設けられた開口部の上面形状は円形であるが、これに限定されるものではない。該開口部は、ソース領域507aおよびドレイン領域507bを露出するものであれば、形状は問わない。

【0132】

以上の工程によって、図5に示したトランジスタを作製することができる。

【0133】

続いて、図1乃至図5に示したトランジスタとは異なる構造のトランジスタについて図6を用いて説明する。

【0134】

図6はトランジスタの上面図および断面図である。図6(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図6(B)に示すA−B断面および図6(C)に示すC−D断面に対応する。

【0135】

以下に、図6(B)に示すA−B断面について詳細に説明する。

【0136】

図6に示すトランジスタは、基板100と、基板100上のゲート電極604と、ゲート電極604を覆う、第1のゲート絶縁膜612a、および第1のゲート絶縁膜612a上の第2のゲート絶縁膜612bからなるゲート絶縁膜612と、ゲート絶縁膜612を介してゲート電極604上にあり、チャネル領域605、ソース領域607aおよびドレイン領域607bを有する酸化物半導体膜606と、ゲート絶縁膜612および酸化物半導体膜606上の、ソース領域607aおよびドレイン領域607bをそれぞれ露出する開口部を有する層間絶縁膜618と、層間絶縁膜618に設けられた開口部を介して酸化物半導体膜606と接する一対の電極616と、を有する。ここで、一対の電極616、酸化物半導体膜606、ゲート電極604、層間絶縁膜618およびゲート絶縁膜612は、それぞれ示した一対の電極116、酸化物半導体膜106、ゲート電極104、層間絶縁膜118およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0137】

図6は、ゲート電極604とチャネル領域605が概略同一の上面形状として図示されているが、これに限定されない。ゲート電極604とチャネル領域605の形状が異なっていても構わない。

【0138】

なお、ソース領域607aおよびドレイン領域607bは、窒素、リン、水素、または希ガスなどを含む。

【0139】

なお、チャネル領域605は高抵抗領域であり、ソース領域607aおよびドレイン領域607b低抵抗領域である。

【0140】

次に、図6に示したトランジスタの作製方法について、図12を用いて説明する。

【0141】

まず、基板100上にゲート電極604を形成する。次に、ゲート電極604を覆う、第1のゲート絶縁膜612a、および第1のゲート絶縁膜612a上の第2のゲート絶縁膜612bからなるゲート絶縁膜612を形成する(図12(A)参照。)。

【0142】

次に、酸化物半導体膜606を形成する(図12(B)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜606から脱離した水素を、第2のゲート絶縁膜612bを介して第1のゲート絶縁膜612aへ移動させる。移動した水素は、第1のゲート絶縁膜612aで捕縛される。このとき、酸化物半導体膜606の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜612aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0143】

次に、レジストマスクなどを用いて、酸化物半導体膜606の一部に窒素、リン、水素、または希ガスを添加する。該添加、または該添加に加えて加熱処理を行うことにより、酸化物半導体膜606の、ゲート電極604と重畳しない領域を低抵抗化し、チャネル領域605、ソース領域607aおよびドレイン領域607bを形成する(図12(C)参照。)。なお、ここで行う加熱処理を、ゲート絶縁膜612を形成した後に行う加熱処理に代えることができる。なお、レジストマスクなどは、ゲート電極604をマスクに裏面露光技術によって形成しても構わない。その場合、ソース領域607aおよびドレイン領域607bと、ゲート電極604との重畳する面積が小さくできるため寄生容量が低減され、トランジスタの動作速度を高めることができる。また、レジストマスクを形成するためのフォトマスク数が低減できるため、トランジスタの作製コストを低減することができるため好ましい。

【0144】

次に、ゲート絶縁膜612および酸化物半導体膜606上に、ソース領域607aおよびドレイン領域607bをそれぞれ露出する開口部を有する層間絶縁膜618を形成する。次に、導電膜をスパッタリング法、蒸着法などで成膜し、加工して、酸化物半導体膜606と接する一対の電極616を形成する(図12(D)参照。)。

【0145】

以上の工程によって、図6に示したトランジスタを作製することができる。

【0146】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0147】

(実施の形態2)

本実施の形態では、実施の形態1に示したトランジスタを用いて作製した液晶表示装置について説明する。なお、本実施の形態では液晶表示装置に本発明の一形態を適用した例について説明するが、これに限定されるものではない。例えば、発光装置の一つであるEL(Electro Luminescence)表示装置に本発明の一形態を適用することも、当業者であれば容易に想到し得るものである。

【0148】

図13にアクティブマトリクス駆動方式の液晶表示装置の回路図を示す。液晶表示装置は、ソース線SL_1乃至SL_a、ゲート線GL_1乃至GL_bおよび複数の画素2200を有する。画素2200は、トランジスタ2230と、キャパシタ2220と、液晶素子2210と、を含む。こうした画素2200が複数集まって液晶表示装置の画素部を構成する。なお、単にソース線またはゲート線を指す場合には、ソース線SLまたはゲート線GLと記載することもある。

【0149】

トランジスタ2230は、本発明の一態様である実施の形態1で示したトランジスタを用いる。実施の形態1で示したトランジスタは電気的特性が良好な酸化物半導体を用いたトランジスタであるため、表示品位が高く、消費電力が小さい表示装置を得ることができる。

【0150】

ゲート線GLはトランジスタ2230のゲートと接続し、ソース線SLはトランジスタ2230のソースと接続し、トランジスタ2230のドレインは、キャパシタ2220の一方の容量電極および液晶素子2210の一方の画素電極と接続する。キャパシタ2220の他方の容量電極および液晶素子2210の他方の画素電極は、共通電極と接続する。なお、共通電極はゲート線GLと同一層かつ同一材料で設けてもよい。

【0151】

また、ゲート線GLは、ゲート駆動回路と接続される。ゲート駆動回路は、実施の形態1で示したトランジスタを含んでもよい。

【0152】

また、ソース線SLは、ソース駆動回路と接続される。ソース駆動回路は、実施の形態1で示したトランジスタを含んでもよい。

【0153】

なお、ゲート駆動回路およびソース駆動回路のいずれかまたは両方を、別途用意された基板上に形成し、COG(Chip On Glass)、ワイヤボンディング、またはTAB(Tape Automated Bonding)などの方法を用いて接続してもよい。

【0154】

また、トランジスタは静電気などにより破壊されやすいため、保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

【0155】

ゲート線GLにトランジスタ2230のしきい値電圧以上になるように電圧を印加すると、ソース線SLから供給された電荷がトランジスタ2230のドレイン電流となってキャパシタ2220に蓄積される。1行分の充電後、該行にあるトランジスタ2230はオフ状態となり、ソース線SLから電圧が掛からなくなるが、キャパシタ2220に蓄積された電荷によって必要な電圧を維持することができる。その後、次の行のキャパシタ2220の充電に移る。このようにして、1行からb行の充電を行う。ドレイン電流とは、トランジスタにおいてソースからチャネルを介してドレインに流れる電流のことである。ドレイン電流はゲート電圧がしきい値電圧よりも大きいときに流れる。

【0156】

なお、トランジスタ2230にオフ電流の小さなトランジスタを用いる場合、電圧を維持する期間を長くすることができる。この効果によって、動きの少ない画像(静止画を含む。)では、表示の書き換え周波数を低減でき、さらなる消費電力の低減が可能となる。また、キャパシタ2220の容量をさらに小さくすることが可能となるため、充電に必要な消費電力を低減することができる。

【0157】

以上のように、本発明の一態様によって、表示品位が高く、消費電力の小さい液晶表示装置を提供することができる。

【0158】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0159】

(実施の形態3)

本実施の形態では、実施の形態1で示したトランジスタを用いて、半導体記憶装置を作製する例について説明する。

【0160】

揮発性半導体記憶装置の代表的な例としては、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶するDRAM(Dynamic Random Access Memory)、フリップフロップなどの回路を用いて記憶内容を保持するSRAM(Static Random Access Memory)がある。

【0161】

不揮発性半導体記憶装置の代表例としては、トランジスタのゲートとチャネル領域との間にノードを有し、当該ノードに電荷を保持することで記憶を行うフラッシュメモリがある。

【0162】

上述した半導体記憶装置に含まれるトランジスタの一部に実施の形態1で示したトランジスタを適用することができる。

【0163】

まずは、実施の形態1で示したトランジスタを適用した半導体記憶装置を構成するメモリセルについて図14を用いて説明する。

【0164】

メモリセルは、ビット線BLと、ワード線WLと、センスアンプSAmpと、トランジスタTrと、キャパシタCと、を有する(図14(A)参照。)。

【0165】

キャパシタCに保持された電圧の時間変化は、トランジスタTrのオフ電流によって図14(B)に示すように徐々に低減していくことが知られている。当初V0からV1まで充電された電圧は、時間が経過するとdata1を読み出す限界点であるVAまで低減する。この期間を保持期間T_1とする。即ち、2値メモリセルの場合、保持期間T_1の間にリフレッシュをする必要がある。

【0166】

ここで、トランジスタTrに実施の形態1で示したトランジスタを適用すると、オフ電流が小さいため、保持期間T_1を長くすることができる。即ち、リフレッシュの頻度を少なくすることが可能となるため、消費電力を低減することができる。例えば、オフ電流が1×10−21A以下、好ましくは1×10−24A以下となった酸化物半導体膜を用いたトランジスタでメモリセルを構成すると、電力を供給せずに数日間から数十年間に渡ってデータを保持することが可能となる。

【0167】

以上のように、本発明の一態様によって、信頼性が高く、消費電力の小さい半導体記憶装置を得ることができる。

【0168】

次に、実施の形態1で示したトランジスタを適用した半導体記憶装置を構成するメモリセルについて図14と異なる例を図15を用いて説明する。

【0169】

図15(A)は、メモリセルの回路図である。メモリセルは、トランジスタTr_1と、トランジスタTr_1のゲートと接続するゲート線GL_1と、トランジスタTr_1のソースと接続するソース線SL_1と、トランジスタTr_2と、トランジスタTr_2のソースと接続するソース線SL_2と、トランジスタTr_2のドレインと接続するドレイン線DL_2と、キャパシタCと、キャパシタCの一端と接続する容量線CLと、キャパシタCの他端、トランジスタTr_1のドレインおよびトランジスタTr_2のゲートと接続するノードNと、を有する。

【0170】

なお、図15(A)に示すメモリセルは、ノードNの電位に応じて、トランジスタTr_2のしきい値電圧が変動することを利用したものである。例えば、図15(B)は容量線CLの電圧VCLと、トランジスタTr_2を流れるドレイン電流Ids_2との関係を説明する図である。

【0171】

ここで、ノードNは、トランジスタTr_1を介して電圧を調整することができる。例えば、ソース線SL_1の電位をVDDとする。このとき、ゲート線GL_1の電位をトランジスタTr_1のしきい値電圧VthにVDDを加えた電位以上とすることで、ノードNの電位をHIGHにすることができる。また、ゲート線GL_1の電位をトランジスタTr_1のしきい値電圧Vth以下とすることで、ノードNの電位をLOWにすることができる。

【0172】

そのため、N=LOWで示したVCL−Ids_2カーブと、N=HIGHで示したVCL−Ids_2カーブのいずれかを得ることができる。即ち、N=LOWでは、VCL=0VにてIds_2が小さいため、データ0となる。また、N=HIGHでは、VCL=0VにてIds_2が大きいため、データ1となる。このようにして、データを記憶することができる。

【0173】

ここで、トランジスタTr_1に実施の形態1で示したトランジスタを適用すると、該トランジスタはオフ電流を極めて小さくすることができるため、ノードNに蓄積された電荷がトランジスタTr_1のソースおよびドレイン間を意図せずにリークすることを抑制できる。そのため、長期間に渡ってデータを保持することができる。また、本発明の一態様に係るトランジスタTr_1はしきい値電圧が調整されるため、書き込みに必要な電圧を低減することが可能となり、フラッシュメモリなどと比較して消費電力を低減することができる。

【0174】

なお、トランジスタTr_2に、実施の形態1で示したトランジスタを適用しても構わない。

【0175】

以上のように、本発明の一態様によって、長期間の信頼性が高く、消費電力の小さい半導体記憶装置を得ることができる。

【0176】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0177】

(実施の形態4)

実施の形態1で示したトランジスタを少なくとも一部に用いてCPU(Central Processing Unit)を構成することができる。

【0178】

図16(A)は、CPUの具体的な構成を示すブロック図である。図16(A)に示すCPUは、基板1190上に、演算回路(ALU:Arithmetic logic unit)1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース(Bus I/F)1198、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)1189を有している。基板1190には、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図16(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

【0179】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0180】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

【0181】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。

【0182】

図16(A)に示すCPUでは、レジスタ1196に、記憶素子が設けられている。レジスタ1196の記憶素子には、実施の形態3に示す記憶素子を用いることができる。

【0183】

図16(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有する記憶素子において、位相反転素子によるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。位相反転素子によるデータの保持が選択されている場合、レジスタ1196内の記憶素子への、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内の記憶素子への電源電圧の供給を停止することができる。

【0184】

電源停止に関しては、図16(B)または図16(C)に示すように、記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図16(B)および図16(C)の回路の説明を行う。

【0185】

図16(B)および図16(C)では、記憶素子への電源電位の供給を制御するスイッチング素子に、実施の形態1で示したトランジスタを含む記憶回路の構成の一例を示す。

【0186】

図16(B)に示す記憶装置は、スイッチング素子1141と、記憶素子1142を複数有する記憶素子群1143とを有している。具体的に、それぞれの記憶素子1142に、実施の形態3に示す記憶素子を用いることができる。記憶素子群1143が有する各記憶素子1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが供給されている。さらに、記憶素子群1143が有するそれぞれの記憶素子1142に、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

【0187】

図16(B)では、スイッチング素子1141として、実施の形態1で示したオフ電流の極めて小さいトランジスタを用いており、該トランジスタは、そのゲートに与えられる信号SigAによりスイッチングが制御される。

【0188】

なお、図16(B)では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

【0189】

また、図16(C)には、記憶素子群1143が有するそれぞれの記憶素子1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、記憶素子群1143が有するそれぞれの記憶素子1142への、ローレベルの電源電位VSSの供給を制御することができる。

【0190】

記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

【0191】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)などのLSIにも応用可能である。

【0192】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【0193】

(実施の形態5)

本実施の形態では、実施の形態1乃至実施の形態4を適用した電子機器の例について説明する。

【0194】

図17(A)は携帯型情報端末である。図17(A)に示す携帯型情報端末は、筐体9300と、ボタン9301と、マイクロフォン9302と、表示部9303と、スピーカ9304と、カメラ9305と、を具備し、携帯型電話機としての機能を有する。本発明の一態様は、表示部9303およびカメラ9305に適用することができる。また、図示しないが、本体内部にある演算装置、無線回路または記憶回路に本発明の一態様を適用することもできる。

【0195】

図17(B)は、ディスプレイである。図17(B)に示すディスプレイは、筐体9310と、表示部9311と、を具備する。本発明の一態様は、表示部9311に適用することができる。本発明の一態様を用いることで、表示部9311のサイズを大きくしたときにも表示品位が高く、消費電力が小さいディスプレイとすることができる。

【0196】

図17(C)は、デジタルスチルカメラである。図17(C)に示すデジタルスチルカメラは、筐体9320と、ボタン9321と、マイクロフォン9322と、表示部9323と、を具備する。本発明の一態様は、表示部9323に適用することができる。また、図示しないが、記憶回路またはイメージセンサに本発明の一態様を適用することもできる。

【0197】

本発明の一態様を用いることで、電子機器の消費電力を小さくでき、かつ信頼性を高めることができる。

【0198】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【実施例1】

【0199】

本実施例では、酸化物半導体膜から脱離した水素が水素透過膜を介して水素捕縛膜へ移動する具体的な例について、加熱処理を行った試料および加熱処理を行っていない試料のSIMS結果を用いて説明する。

【0200】

石英基板上に酸化物半導体膜(In−Ga−Zn−O膜)を300nmの厚さで成膜し、酸化物半導体膜上に酸化シリコン膜を5nmの厚さで成膜し、酸化シリコン膜上に酸窒化物膜(In−Ga−Zn−O−N膜)を300nmの厚さで成膜した試料を用意した。

【0201】

酸化物半導体膜は、スパッタリング法により、In−Ga−Zn−Oターゲット(mol数比、In2O3:ZnO:Ga2O3=1:1:2)を用い、ターゲット−基板間に印加する電力を500W(DC)、成膜圧力を0.4Pa、成膜ガス流量をアルゴン30sccmおよび酸素15sccmとし、基板表面温度が200℃になるよう加熱処理しながら成膜した。

【0202】

酸化シリコン膜は、スパッタリング法により、合成石英ターゲットを用い、成膜電力を1kW、成膜圧力を0.4Pa、成膜ガス流量をアルゴン25sccmおよび酸素25sccmとし、基板表面温度が100℃になるよう加熱処理しながら成膜した。

【0203】

酸窒化物膜は、スパッタリング法により、In−Ga−Zn−Oターゲット(mol数比、In2O3:ZnO:Ga2O3=1:1:2)を用い、成膜電力を500W、成膜圧力を0.4Pa、成膜ガス流量を窒素40sccmとし、基板表面温度が200℃になるよう加熱処理しながら成膜した。

【0204】

図18(A)はSIMSによる水素濃度の深さ方向分布を、図18(B)はSIMSによる窒素濃度の深さ方向分布を示す。ここで、範囲6001は酸窒化物膜を、範囲6002は酸化シリコン膜を、範囲6003は酸化物半導体膜を、範囲6004は石英基板を示す。ただし、範囲6002は定量化されていない。また、各層の界面近傍はマトリックス効果により正確な定量値が得られていない。なお、SIMSは、CAMECA社製IMS 7fRを用いた。

【0205】

図18(A)において、細線6010は成膜直後の試料の水素濃度分布を示し、太線6020は成膜後に窒素雰囲気にて550℃で1時間の加熱処理を行った試料の水素濃度分布を示す。前述の加熱処理を行うことで、酸化物半導体膜中の水素濃度が低減し、酸窒化物膜中の水素濃度が増大していることがわかる。即ち、前述の加熱処理によって、酸化物半導体膜から酸化シリコン膜を介して酸窒化物膜に水素が移動していることがわかる。

【0206】

図18(B)において、細線6030は成膜直後の試料の窒素濃度分布を示し、太線6040は成膜後に窒素雰囲気にて550℃で1時間の加熱処理を行った試料の窒素濃度分布を示す。前述の加熱処理前後で、試料中の窒素濃度分布はほとんど変動しないことがわかる。

【符号の説明】

【0207】

100 基板

104 ゲート電極

106 酸化物半導体膜

112 ゲート絶縁膜

112a 第1のゲート絶縁膜

112b 第2のゲート絶縁膜

116 一対の電極

118 層間絶縁膜

136 酸化物半導体膜

206 酸化物半導体膜

216 一対の電極

218 層間絶縁膜

236 酸化物半導体膜

302 下地絶縁膜

304 ゲート電極

306 酸化物半導体膜

312 ゲート絶縁膜

312a 第1のゲート絶縁膜

312b 第2のゲート絶縁膜

316 一対の電極

404 ゲート電極

406 酸化物半導体膜

412 ゲート絶縁膜

412a 第1のゲート絶縁膜

412b 第2のゲート絶縁膜

416 一対の電極

504 ゲート電極

505 チャネル領域

506 酸化物半導体膜

507a ソース領域

507b ドレイン領域

512 ゲート絶縁膜

512a 第1のゲート絶縁膜

512b 第2のゲート絶縁膜

516 一対の電極

518 層間絶縁膜

604 ゲート電極

605 チャネル領域

606 酸化物半導体膜

607a ソース領域

607b ドレイン領域

612 ゲート絶縁膜

612a 第1のゲート絶縁膜

612b 第2のゲート絶縁膜

616 一対の電極

618 層間絶縁膜

1141 スイッチング素子

1142 記憶素子

1143 記憶素子群

1189 ROMインターフェース

1190 基板

1191 ALU

1192 ALUコントローラ

1193 インストラクションデコーダ

1194 インタラプトコントローラ

1195 タイミングコントローラ

1196 レジスタ

1197 レジスタコントローラ

1198 バスインターフェース

1199 ROM

2200 画素

2210 液晶素子

2220 キャパシタ

2230 トランジスタ

6001 範囲

6002 範囲

6003 範囲

6004 範囲

6010 細線

6020 太線

6030 細線

6040 太線

9300 筐体

9301 ボタン

9302 マイクロフォン

9303 表示部

9304 スピーカ

9305 カメラ

9310 筐体

9311 表示部

9320 筐体

9321 ボタン

9322 マイクロフォン

9323 表示部

【技術分野】

【0001】

トランジスタなどの半導体素子を含む回路を有する半導体装置に関する。例えば、電源回路に搭載されるパワーデバイス、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示装置に代表される電気光学装置、発光素子を有する発光表示装置などを部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置は、半導体特性を利用することで機能し得る装置全般を指し、電気光学装置、発光表示装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

液晶表示装置に代表されるように、ガラス基板などに形成されるトランジスタの多くはアモルファスシリコン、多結晶シリコンなどによって構成されている。アモルファスシリコンを用いたトランジスタは電界効果移動度が低いもののガラス基板の大面積化に対応することができる。また、多結晶シリコンを用いたトランジスタの電界効果移動度は高いがガラス基板の大面積化には適していないという欠点を有している。

【0004】

シリコンを用いたトランジスタのほかに、近年は酸化物半導体を用いてトランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体として、酸化亜鉛、In−Ga−Zn−O系酸化物を用いてトランジスタを作製し、表示装置の画素のスイッチング素子などに用いる技術が特許文献1および特許文献2で開示されている。

【0005】

酸化物半導体において、水素の一部はドナーとなり、キャリアである電子を放出する。酸化物半導体のキャリア濃度が高まると、ゲートに電圧を印加しなくてもトランジスタにチャネルが形成されてしまう。即ち、しきい値電圧が負方向にシフトする。酸化物半導体の水素を完全に取り除くことは困難であるため、しきい値電圧の制御も困難となる。

【0006】

特許文献3には、酸化物半導体膜中に水素を添加すると、導電率が4から5桁程度高くなることが示されている。また、酸化物半導体膜に接する絶縁膜から酸化物半導体膜に、水素が拡散していくことが示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−123861号公報

【特許文献2】特開2007−96055号公報

【特許文献3】特開2008−141119号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題とする。

【課題を解決するための手段】

【0009】

本発明の一態様は、酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させることを技術的思想とする。

【0010】

具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

【0011】

なお、酸化物半導体膜と水素捕縛膜との間に水素透過膜を設けることで、酸化物半導体膜の界面近傍の水素濃度を低減することができる。

【発明の効果】

【0012】

酸化物半導体膜を用いるトランジスタに、安定した電気的特性を付与し、信頼性の高い半導体装置を作製することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図2】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図3】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図4】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図5】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図6】本発明の一態様に係る半導体装置の一例を示す上面図および断面図。

【図7】図1に対応する半導体装置の作製方法の一例を示す断面図。

【図8】図2に対応する半導体装置の作製方法の一例を示す断面図。

【図9】図3に対応する半導体装置の作製方法の一例を示す断面図。

【図10】図4に対応する半導体装置の作製方法の一例を示す断面図。

【図11】図5に対応する半導体装置の作製方法の一例を示す断面図。

【図12】図6に対応する半導体装置の作製方法の一例を示す断面図。

【図13】本発明の一態様に係るトランジスタを用いた液晶表示装置の一例を示す回路図およびその電気的特性の一例を示す図。

【図14】本発明の一態様に係るトランジスタを用いた半導体記憶装置の一例を示す回路図およびその電気的特性の一例を示す図。

【図15】本発明の一態様に係るトランジスタを用いた半導体記憶装置の一例を示す回路図。

【図16】本発明の一態様に係るトランジスタを用いたCPUの具体例を示すブロック図およびその一部の回路図。

【図17】本発明の一態様に係る半導体装置を具備した電子機器の一例を示す斜視図。

【図18】SIMSによる水素濃度および窒素濃度の深さ方向分布を示す図。

【発明を実施するための形態】

【0014】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0015】

以下に本発明の説明を行うが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースと呼ぶ。すなわち、電位の高低によって、それらを区別しない。従って、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

【0016】

また、電圧は、ある電位と基準の電位(例えばグラウンド電位)との電位差のことを示す場合が多い。なお、電位を電圧と言い換えることが可能である。

【0017】

本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

【0018】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0019】

(実施の形態1)

本実施の形態では、本発明の一態様のトランジスタの一例について図1を用いて説明する。

【0020】

図1(A)はトランジスタの上面図である。図1(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図1(B)に示すA−B断面および図1(C)に示すC−D断面に対応する。

【0021】

ここでは、図1(B)に示すA−B断面について詳細に説明する。

【0022】

トランジスタは、基板100と、基板100上のゲート電極104と、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112と、ゲート絶縁膜112を介してゲート電極104上にある酸化物半導体膜106と、酸化物半導体膜106上にあり酸化物半導体膜106と一部が接する一対の電極116と、を有する。なお、酸化物半導体膜106上に層間絶縁膜118を有すると、酸化物半導体膜106が露出しないため好ましい。

【0023】

ここで、第1のゲート絶縁膜112aは水素捕縛膜を、第2のゲート絶縁膜112bは水素透過膜を用いる。なお、酸化物半導体膜と水素捕縛膜との間に水素透過膜を設けることで、酸化物半導体膜の界面近傍の水素濃度を低減することができる。

【0024】

第1のゲート絶縁膜112aは、窒化インジウム(またはインジウム)を含む酸窒化物膜を用いればよい。具体的には、少なくとも窒化インジウムを含み、加えて酸化インジウム、酸化ガリウム、酸化亜鉛、酸化スズ、酸化アルミニウム、酸化タングステン、酸化モリブデン、酸化チタン、酸化タンタルおよび酸化シリコンの少なくとも一種以上を含む化合物材料を用いればよい。なお、酸窒化物とは、酸化物を構成する酸素の一部が窒素で置き換わった化合物をいう。

【0025】

例えば、第1のゲート絶縁膜112aは、窒素濃度が0.01atomic%以上7atomic%未満とすればよい。窒素濃度が0.01atomic%以上7atomic%未満である窒化インジウムを含む酸窒化物膜は、高い絶縁性を有する。または、第1のゲート絶縁膜112aは、7atomic%以上20atomic%以下とすればよい。窒素濃度が7atomic%以上20atomic%以下である窒化インジウムを含む酸窒化物膜は、水素と結合すると高い導電性を有することがある。第1のゲート絶縁膜112aの一部が高い導電性を有するとき、該一部がゲート電極の一部として機能することがある。このとき、高い絶縁性を有する第2のゲート絶縁膜112bを有することで、第1のゲート絶縁膜112aを介した一対の電極116およびゲート電極104からの電荷のリークを防ぐことができる。なお、第1のゲート絶縁膜112aの窒素濃度は、X線光電子分光法(XPS:X−ray Photoelectron Spectroscopy)分析によって定量化できる。

【0026】

窒化インジウムを含む酸窒化物膜中において、水素の一部はキャリアである電子を放出する。電子は負の電荷を有するため、ゲート電極側から負のバイアスが印加されているのと同様に電界を生じ、トランジスタのしきい値電圧を正方向にシフトさせる。なお、酸化物半導体膜を用いたトランジスタは、酸化物半導体膜内の酸素欠損および水素の一部がキャリアである電子を放出することで、しきい値電圧が負方向にシフトしやすい傾向がある。そのため、窒化インジウムを含む酸窒化物膜が有する負の電荷により、トランジスタのしきい値電圧を正方向にシフトさせると好ましい場合がある。なお、第1のゲート絶縁膜112aにおける水素濃度を制御することで、負の電荷量を調整することができる。第1のゲート絶縁膜112aにおける水素濃度は、第1のゲート絶縁膜112aの窒素濃度により調整することができる。

【0027】

第1のゲート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下とする。なお、第1のゲート絶縁膜112aの水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)によって定量化できる。

【0028】

第2のゲート絶縁膜112bは、高い絶縁性を有する酸化物膜を用いる。例えば、酸化シリコン膜または酸化窒化シリコン膜を用いればよい。なお、第2のゲート絶縁膜112bは、厚さが0.5nm以上15nm以下、好ましくは2nm以上5nm以下とする。第2のゲート絶縁膜112bの厚さが薄いほど、より低温で水素を拡散することが可能となる。

【0029】

ここで、酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものであって、好ましくは、酸素が50atomic%以上70atomic%以下、窒素が0.5atomic%以上15atomic%以下、シリコンが25atomic%以上35atomic%以下、水素が0atomic%以上10atomic%以下の範囲で含まれるものをいう。ただし、上記範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward scattering Spectrometry)を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100atomic%を超えない値をとる。

【0030】

酸化物半導体膜106の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下とする。酸化物半導体膜106中の水素濃度は、SIMSによって定量化できる。

【0031】

ここで、アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちナトリウム(Na)は、酸化物半導体膜に接する絶縁膜中に拡散してNa+となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、または、その結合中に割り込む。その結果、例えば、しきい値電圧が負方向にシフトすることによるノーマリオン化、電界効果移動度の低下などの、トランジスタの電気的特性の劣化が起こり、加えて、トランジスタの電気的特性のばらつきも生じる。この不純物によりもたらされるトランジスタの電気的特性の劣化と、トランジスタの電気的特性のばらつきは、酸化物半導体膜中の水素濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体膜中の水素濃度が1×1018cm−3以下、または1×1017cm−3以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、Na濃度の測定値は、5×1016cm−3以下、好ましくは1×1016cm−3以下、更に好ましくは1×1015cm−3以下とするとよい。同様に、リチウム(Li)濃度の測定値は、5×1015cm−3以下、好ましくは1×1015cm−3以下とするとよい。同様に、カリウム(K)濃度の測定値は、5×1015cm−3以下、好ましくは1×1015cm−3以下とするとよい。

【0032】

以上に示した酸化物半導体膜106を用いたトランジスタは、オフ電流を極めて小さくできる。例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電流は、1×10−18A以下、または1×10−21A以下、または1×10−24A以下となる。

【0033】

酸化物半導体膜106は、例えば、In、Ga、ZnおよびSnから選ばれた二種以上を含む材料を用いればよい。

【0034】

酸化物半導体膜106は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは3.0eV以上の材料を選択する。

【0035】

酸化物半導体膜106は、例えば、In−Sn−Ga−Zn−O系の材料や、In−Ga−Zn−O系の材料、In−Sn−Zn−O系の材料、In−Al−Zn−O系の材料、Sn−Ga−Zn−O系の材料、Al−Ga−Zn−O系の材料、Sn−Al−Zn−O系の材料や、In−Zn−O系の材料、Sn−Zn−O系の材料、Al−Zn−O系の材料、Zn−Mg−O系の材料、Sn−Mg−O系の材料、In−Mg−O系の材料、In−Ga−O系の材料や、In−O系の材料、Sn−O系の材料、Zn−O系の材料などを用いればよい。ここで、例えば、In−Ga−Zn−O系の材料は、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。このとき、酸化物半導体膜106の化学量論的組成比に対し、Oを過剰にすると好ましい。Oを過剰にすることで酸化物半導体膜106の酸素欠損に起因するキャリアの生成を抑制することができる。

【0036】

なお、酸化物半導体膜106の一例としてIn−Zn−O系の材料を用いる場合、原子数比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さらに好ましくはIn/Zn=1.5以上15以下とする。Znの原子数比を前述の範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい。

【0037】

酸化物半導体膜106として、化学式InMO3(ZnO)m(m>0)で表記される材料を用いてもよい。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGaおよびCoなどを用いてもよい。

【0038】

酸化物半導体膜106は、第1のゲート絶縁膜112aを構成する金属元素と同じ金属元素を有する材料で形成すると好ましい。これは、スパッタリング法で成膜する場合、同一ターゲットを用いて成膜ガスによって作り分けすることが可能となり、材料コストおよび装置コストを低減できるためである。例えば、酸化物半導体膜106としてIn−Ga−Zn−O膜を用いた場合、第1のゲート絶縁膜112aとしてIn−Ga−Zn−O−N膜を用いればよい。

【0039】

酸化物半導体膜106は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

【0040】

好ましくは、酸化物半導体膜106は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0041】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0042】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0043】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0044】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0045】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0046】

層間絶縁膜118は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、ポリイミドおよびアクリルなどを、単層で、または積層して用いればよく、例えば、プラズマCVD法、スパッタリング法およびスピンコート法などで形成する。また、層間絶縁膜118は、加熱処理により酸素を放出する膜を用いると好ましい。加熱処理により酸素を放出する膜を用いることで、酸化物半導体膜106に生じる酸素欠損を修復することができ、トランジスタの電気的特性の劣化を抑制できる。

【0047】

ここで、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものであって、好ましくは、酸素が5atomic%以上30atomic%以下、窒素が20atomic%以上55atomic%以下、シリコンが25atomic%以上35atomic%以下、水素が10atomic%以上25atomic%以下の範囲で含まれるものをいう。但し、上記範囲は、RBSや、HFSを用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100atomic%を超えない値をとる。

【0048】

「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018cm−3以上、または1.0×1020cm−3以上であることをいう。

【0049】

ここで、TDS分析にて、酸素の放出量の測定方法について、以下に説明する。

【0050】

TDS分析したときの気体の放出量は、イオン強度の積分値に比例する。このため、測定したイオン強度の積分値と、標準試料の基準値との比により、気体の放出量を計算することができる。標準試料の基準値とは、所定の密度の原子を含む試料において、当該原子に相当するイオン強度の積分値に対する当該原子の密度の割合である。

【0051】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、数式1で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0052】

NO2=NH2/SH2×SO2×α (数式1)

【0053】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのイオン強度の積分値である。αは、TDS分析におけるイオン強度に影響する係数である。数式1の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016cm−3の水素原子を含むシリコンウェハを用いて測定した。

【0054】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量について見積もることができる。

【0055】

なお、NO2は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0056】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものをいう。単位体積当たりのシリコン原子数および酸素原子数は、RBSにより測定した値である。

【0057】

層間絶縁膜118から酸化物半導体膜106に酸素が供給されること(酸素が移動するともいう。)で酸化物半導体膜106と層間絶縁膜118との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜106と層間絶縁膜118との界面にキャリアが捕獲されることを抑制することができ、電気的特性の劣化の少ないトランジスタを得ることができる。

【0058】

さらに、酸化物半導体膜106の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧が負方向へシフトしてしまう。層間絶縁膜118から酸化物半導体膜106に酸素が十分に供給されることにより、しきい値電圧が負方向へシフトする要因である、酸化物半導体膜106の酸素欠損を低減することができる。

【0059】

即ち、層間絶縁膜118に、加熱処理により酸素を放出する膜を設けることで、酸化物半導体膜106と層間絶縁膜118との界面の界面準位密度、ならびに酸化物半導体膜106の酸素欠損を低減し、酸化物半導体膜106と層間絶縁膜118との界面におけるキャリア捕獲の影響を小さくすることができる。

【0060】

このように、トランジスタのしきい値電圧が負方向へシフトする要因をできる限り除いた上で、酸化物半導体膜106に含まれる水素濃度を低減させることが好ましい。

【0061】

基板100に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI(Silicon On Insulator)基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

【0062】

基板100として、可とう性基板を用いてもよい。その場合は、可とう性基板上に直接トランジスタを作製すればよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。

【0063】

ゲート電極104は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一以上選択し、単層でまたは積層して用いればよい。

【0064】

なお、図1ではゲート電極104が酸化物半導体膜106よりも縦、横ともに大きい形状にすることで酸化物半導体膜106の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜106がゲート電極104よりも、上面図において縦、横ともに大きい形状にしても構わない。

【0065】

一対の電極116は、ゲート電極104で示した金属膜、金属窒化物膜、金属酸化物膜または合金膜などを単層でまたは積層して用いればよい。

【0066】

一対の電極116にCuを含む膜を用いると、配線の抵抗を低減でき、大型表示装置などでも配線遅延などの発生を低減することができる。一対の電極116にCuを用いる場合、基板100の材質によっては密着性が悪くなるため、基板100と密着性のよい膜との積層構造にすることが好ましい。基板100と密着性のよい膜として、Ti、Mo、Mn、CuまたはAlなどを含む膜を用いればよい。例えば、Cu−Mn−Al合金を用いてもよい。

【0067】

次に、図1に示したトランジスタの作製方法について、図7を用いて説明する。

【0068】

まず、基板100上に導電膜をスパッタリング法または蒸着法などで成膜し、加工してゲート電極104を形成する。次に、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112を形成する(図7(A)参照。)。

【0069】

第1のゲート絶縁膜112aは、プラズマCVD法、スパッタリング法、PLD(Pulse Laser Deposition)法、ALD(Atomic Layer Deposition)法などを用いて成膜すればよい。例えば、スパッタリング法を用いる場合、少なくとも酸化インジウムを含むターゲットを用いる。酸化インジウムに加えて酸化ガリウム、酸化亜鉛、酸化スズ、酸化アルミニウム、酸化タングステン、酸化モリブデン、酸化チタン、酸化タンタルおよび酸化シリコンの少なくとも一種以上を含む材料をターゲットに用いても構わない。成膜ガスには少なくとも窒素を含ませればよい。また成膜ガスとして、希ガス(ヘリウム、ネオン、アルゴン、クリプトン、キセノンなど)および酸素のいずれか一種以上を用いても構わない。このような方法で成膜することにより、窒素濃度が0.01atomic%以上7atomic%未満または7atomic%以上20atomic%以下である、少なくとも窒化インジウムを含む第1のゲート絶縁膜112aを成膜することができる。

【0070】

第2のゲート絶縁膜112bは、プラズマCVD法、スパッタリング法、PLD法、ALD法などを用いて、酸化シリコン膜または酸化窒化シリコン膜を成膜すればよい。

【0071】

次に、ゲート絶縁膜112を介してゲート電極104上に酸化物半導体膜136を成膜する(図7(B)参照。)。酸化物半導体膜136は、前述の材料を用い、スパッタリング法、PLD法、ALD法などを用いて成膜すればよい。

【0072】

次に、酸化物半導体膜136を加工して酸化物半導体膜106を形成する(図7(C)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜106から脱離した水素を、第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ移動させる。移動した水素は、第1のゲート絶縁膜112aで捕縛される。このとき、酸化物半導体膜106の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0073】

次に、導電膜をスパッタリング法または蒸着法などで成膜し、加工して酸化物半導体膜106と少なくとも一部が接する一対の電極116を形成する。次に、酸化物半導体膜106および一対の電極116上に層間絶縁膜118を形成してもよい(図7(D)参照。)。なお、酸化物半導体膜106を形成した後に行う加熱処理に代えて、層間絶縁膜118の形成後に同様の加熱処理を行っても構わない。

【0074】

以上のように、酸化物半導体膜106から第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ水素を移動させ、移動した水素を第1のゲート絶縁膜112aで捕縛することにより、高純度化された酸化物半導体膜106を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0075】

また、第1のゲート絶縁膜112aは、捕縛した水素の一部に起因して生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0076】

以上の工程によって、図1に示したトランジスタを作製することができる。

【0077】

続いて、図1に示したトランジスタとは異なる構造のトランジスタについて図2を用いて説明する。

【0078】

図2はトランジスタの上面図および断面図である。図2(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図2(B)に示すA−B断面および図2(C)に示すC−D断面に対応する。

【0079】

以下に、図2(B)に示すA−B断面について詳細に説明する。

【0080】

図2に示すトランジスタは、基板100と、基板100上のゲート電極104と、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112と、ゲート絶縁膜112上の一対の電極216と、ゲート絶縁膜112を介してゲート電極104上にあり、一対の電極216と一部が接する酸化物半導体膜206と、を有する。なお、ゲート絶縁膜112、一対の電極216および酸化物半導体膜206上に層間絶縁膜218を有すると、酸化物半導体膜206が露出しないため好ましい。ここで、一対の電極216、酸化物半導体膜206および層間絶縁膜218は、それぞれ一対の電極116、酸化物半導体膜106および層間絶縁膜118と同様の方法および同様の材料により形成する。

【0081】

なお、図2ではゲート電極104が酸化物半導体膜206よりも縦、横ともに大きい形状にすることで酸化物半導体膜206の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜206がゲート電極104よりも、上面図において縦、横ともに大きい形状としても構わない。

【0082】

次に、図2に示したトランジスタの作製方法について、図8を用いて説明する。

【0083】

まず、基板100上にゲート電極104を形成する。次に、ゲート電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート絶縁膜112を形成する。次に、ゲート絶縁膜112上に一対の電極216を形成する(図8(A)参照。)。

【0084】

次に、ゲート絶縁膜112を介してゲート電極104上に酸化物半導体膜236を成膜する(図8(B)参照。)。なお、酸化物半導体膜236は、酸化物半導体膜136と同様の方法および同様の材料により形成する。

【0085】

次に、酸化物半導体膜236を加工して一対の電極216と一部が接する酸化物半導体膜206を形成する(図8(C)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜206から脱離した水素を、第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ移動させる。移動した水素は、第1のゲート絶縁膜112aで捕縛される。このとき、酸化物半導体膜206の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0086】

次に、酸化物半導体膜206、一対の電極216上に層間絶縁膜218を形成してもよい(図8(D)参照。)。なお、酸化物半導体膜206を形成した後に行う加熱処理に代えて、層間絶縁膜218の形成後に同様の加熱処理を行っても構わない。

【0087】

以上のように、酸化物半導体膜206から第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ水素を移動させ、移動した水素を第1のゲート絶縁膜112aで捕縛することにより、高純度化された酸化物半導体膜206を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0088】

また、第1のゲート絶縁膜112aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。そのため、トランジスタの電気的特性をノーマリーオフ、またはノーマリーオフに近づけることができる。

【0089】

以上の工程によって、図2に示したトランジスタを作製することができる。

【0090】

続いて、図1および図2に示したトランジスタとは異なる構造のトランジスタについて図3を用いて説明する。

【0091】

図3はトランジスタの上面図および断面図である。図3(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図3(B)に示すA−B断面および図3(C)に示すC−D断面に対応する。

【0092】

以下に、図3(B)に示すA−B断面について詳細に説明する。

【0093】

図3に示すトランジスタは、基板100と、基板100上の下地絶縁膜302と、下地絶縁膜302上の酸化物半導体膜306と、酸化物半導体膜306上にあり酸化物半導体膜306と一部が接する一対の電極316と、酸化物半導体膜306および一対の電極316上の、第2のゲート絶縁膜312b、および第2のゲート絶縁膜312b上の第1のゲート絶縁膜312aからなるゲート絶縁膜312と、ゲート絶縁膜312を介して酸化物半導体膜306上にあるゲート電極304と、を有する。なお、基板100の表面状態によっては、下地絶縁膜302を設けない構成としても構わない。ここで、一対の電極316、酸化物半導体膜306、ゲート電極304およびゲート絶縁膜312は、それぞれ一対の電極116、酸化物半導体膜106、ゲート電極104およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0094】

また、下地絶縁膜302は、層間絶縁膜118の説明を参酌すればよい。

【0095】

なお、図3ではゲート電極304が酸化物半導体膜306よりも縦、横ともに大きい形状にすることで酸化物半導体膜306の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜306がゲート電極304よりも、上面図において縦、横ともに大きい形状としても構わない。

【0096】

次に、図3に示したトランジスタの作製方法について、図9を用いて説明する。

【0097】

まず、基板100上に下地絶縁膜302を形成する。次に、下地絶縁膜302上に酸化物半導体膜306を形成する。次に、酸化物半導体膜306上に、酸化物半導体膜306と少なくとも一部が接する一対の電極316を形成する(図9(A)参照。)。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

【0098】

次に、酸化物半導体膜306および一対の電極316上に、第2のゲート絶縁膜312b、および第2のゲート絶縁膜312b上の第1のゲート絶縁膜312aからなるゲート絶縁膜312を形成する(図9(B)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜306から脱離した水素を、第2のゲート絶縁膜312bを介して第1のゲート絶縁膜312aへ移動させる。移動した水素は、第1のゲート絶縁膜312aで捕縛される。このとき、酸化物半導体膜306の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜312aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0099】

次に、ゲート絶縁膜312を介して酸化物半導体膜306に重畳するゲート電極304を形成する(図9(C)参照。)。なお、ゲート絶縁膜312を形成した後に行う加熱処理に代えて、ゲート電極304の形成後に同様の加熱処理を行っても構わない。

【0100】

以上のように、酸化物半導体膜306から第2のゲート絶縁膜312bを介して第1のゲート絶縁膜312aへ水素を移動させ、移動した水素を第1のゲート絶縁膜312aで捕縛することにより、高純度化された酸化物半導体膜306を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0101】

また、第1のゲート絶縁膜312aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0102】

以上の工程によって、図3に示したトランジスタを作製することができる。

【0103】

続いて、図1乃至図3に示したトランジスタとは異なる構造のトランジスタについて図4を用いて説明する。

【0104】

図4はトランジスタの上面図および断面図である。図4(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図4(B)に示すA−B断面および図4(C)に示すC−D断面に対応する。

【0105】

以下に、図4(B)に示すA−B断面について詳細に説明する。

【0106】

図4に示すトランジスタは、基板100と、基板100上の下地絶縁膜302と、下地絶縁膜302上の一対の電極416と、一対の電極416上にあり一対の電極416と一部が接する酸化物半導体膜406と、酸化物半導体膜406および一対の電極416上の、第2のゲート絶縁膜412b、および第2のゲート絶縁膜412b上の第1のゲート絶縁膜412aからなるゲート絶縁膜412と、ゲート絶縁膜412を介して酸化物半導体膜406上にあるゲート電極404と、を有する。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。ここで、一対の電極416、酸化物半導体膜406、ゲート電極404およびゲート絶縁膜412は、それぞれ一対の電極116、酸化物半導体膜106、ゲート電極104およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0107】

なお、図4ではゲート電極404が酸化物半導体膜406よりも縦、横ともに大きい形状にすることで酸化物半導体膜406の光による劣化、電荷の発生を抑制しているが、これに限定されるものではない。例えば、酸化物半導体膜406がゲート電極404よりも、上面図において縦、横ともに大きい形状としても構わない。

【0108】

次に、図4に示したトランジスタの作製方法について、図10を用いて説明する。

【0109】

まず、基板100上に下地絶縁膜302を形成する。次に、下地絶縁膜302上に一対の電極416を形成する(図10(A)参照。)。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

【0110】

次に、一対の電極416上に、一対の電極416と一部が接する酸化物半導体膜406を形成する(図10(B)参照。)。

【0111】

次に、酸化物半導体膜406、一対の電極416上に、第2のゲート絶縁膜412b、および第2のゲート絶縁膜412b上の第1のゲート絶縁膜412aからなるゲート絶縁膜412を形成する(図10(C)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜406から脱離した水素を、第2のゲート絶縁膜412bを介して第1のゲート絶縁膜412aへ移動させる。移動した水素は、第1のゲート絶縁膜412aで捕縛される。このとき、酸化物半導体膜406の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜412aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0112】

次に、ゲート絶縁膜412を介して酸化物半導体膜406に重畳するゲート電極404を形成する(図10(D)参照。)。なお、ゲート絶縁膜412を形成した後に行う加熱処理に代えて、ゲート電極404の形成後に同様の加熱処理を行っても構わない。

【0113】

以上のように、酸化物半導体膜406から第2のゲート絶縁膜412bを介して第1のゲート絶縁膜412aへ水素を移動させ、移動した水素を第1のゲート絶縁膜412aで捕縛することにより、高純度化された酸化物半導体膜406を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0114】

また、第1のゲート絶縁膜412aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0115】

以上の工程によって、図4に示したトランジスタを作製することができる。

【0116】

続いて、図1乃至図4に示したトランジスタとは異なる構造のトランジスタについて図5を用いて説明する。

【0117】

図5はトランジスタの上面図および断面図である。図5(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図5(B)に示すA−B断面および図5(C)に示すC−D断面に対応する。

【0118】

以下に、図5(B)に示すA−B断面について詳細に説明する。

【0119】

図5に示すトランジスタは、基板100と、基板100上の下地絶縁膜302と、下地絶縁膜302上のチャネル領域505、ソース領域507aおよびドレイン領域507bを有する酸化物半導体膜506と、酸化物半導体膜506上の、第2のゲート絶縁膜512b、および第2のゲート絶縁膜512b上の第1のゲート絶縁膜512aからなるゲート絶縁膜512と、ゲート絶縁膜512を介してチャネル領域505と重畳するゲート電極504と、酸化物半導体膜506およびゲート電極504上の層間絶縁膜518と、ゲート絶縁膜512および層間絶縁膜518に設けられた開口部を介して酸化物半導体膜506と接する一対の電極516と、を有する。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。ここで、一対の電極516、酸化物半導体膜506、ゲート電極504、層間絶縁膜518およびゲート絶縁膜512は、それぞれ一対の電極116、酸化物半導体膜106、ゲート電極104、層間絶縁膜118およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0120】

ここで、図示しないが、ゲート絶縁膜512およびゲート電極504は概略同一の上面形状としてもよい。この形状は、ゲート電極504およびゲート絶縁膜512を同一のマスクを用いて加工することで得られる。または、ゲート電極504をマスクに用いてゲート絶縁膜512を加工することによって得られる。

【0121】

なお、図5ではゲート絶縁膜512および層間絶縁膜518に設けられた開口部の上面形状は円形であるが、これに限定されるものではない。該開口部は、ソース領域507aおよびドレイン領域507bを露出するものであれば、形状は問わない。

【0122】

チャネル領域505は、ゲート電極504と概略同一の上面形状としてもよい。なお、ソース領域507aおよびドレイン領域507bは、窒素、リン、水素、または希ガスなどを含む。

【0123】

なお、チャネル領域505は高抵抗領域であり、ソース領域507aおよびドレイン領域507bは低抵抗領域である。

【0124】

次に、図5に示したトランジスタの作製方法について、図11を用いて説明する。

【0125】

まず、基板100上に下地絶縁膜302を形成する。次に、下地絶縁膜302上に酸化物半導体膜506を形成する。次に、下地絶縁膜302および酸化物半導体膜506上に、第2のゲート絶縁膜512b、および第2のゲート絶縁膜512b上の第1のゲート絶縁膜512aからなるゲート絶縁膜512を形成する(図11(A)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜506から脱離した水素を、第2のゲート絶縁膜512bを介して第1のゲート絶縁膜512aへ移動させる。移動した水素は、第1のゲート絶縁膜512aで捕縛される。このとき、酸化物半導体膜506の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜512aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。なお、基板100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

【0126】

次に、ゲート絶縁膜512を介して酸化物半導体膜506上にゲート電極504を形成する。なお、ゲート電極504を形成後、プラズマ処理または薬液処理によってゲート電極504の幅を細くしても構わない。

【0127】

次に、ゲート電極504をマスクに、酸化物半導体膜506の一部に窒素、リン、水素または希ガスを添加する。該添加、または該添加に加えて加熱処理を行うことにより、酸化物半導体膜506の、ゲート電極504と重畳しない領域を低抵抗化し、チャネル領域505、ソース領域507aおよびドレイン領域507bを形成する(図11(B)参照。)。なお、ここで行う加熱処理を、ゲート絶縁膜512を形成した後に行う加熱処理に代えることができる。

【0128】

次に、ゲート絶縁膜512およびゲート電極504上に層間絶縁膜518を形成し(図11(C)参照。)、ソース領域507aおよびドレイン領域507bをそれぞれ露出する開口部をゲート絶縁膜512および層間絶縁膜518に形成する。次に、酸化物半導体膜506と接する一対の電極516を形成する(図11(D)参照。)。なお、ゲート絶縁膜512を形成した後に行う加熱処理、ソース領域507aおよびドレイン領域507bを形成するための加熱処理に代えて、層間絶縁膜518または一対の電極516の形成後に同様の加熱処理を行っても構わない。

【0129】

以上のように、酸化物半導体膜506から第2のゲート絶縁膜512bを介して第1のゲート絶縁膜512aへ水素を移動させ、移動した水素を第1のゲート絶縁膜512aで捕縛することにより、高純度化された酸化物半導体膜506を形成することができる。そのため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高い半導体装置を作製することができる。

【0130】

また、第1のゲート絶縁膜512aは、捕縛した水素の一部から生じた負の電荷により、トランジスタのしきい値電圧を正方向へシフトさせることができる。

【0131】

なお、図11ではゲート絶縁膜512および層間絶縁膜518に設けられた開口部の上面形状は円形であるが、これに限定されるものではない。該開口部は、ソース領域507aおよびドレイン領域507bを露出するものであれば、形状は問わない。

【0132】

以上の工程によって、図5に示したトランジスタを作製することができる。

【0133】

続いて、図1乃至図5に示したトランジスタとは異なる構造のトランジスタについて図6を用いて説明する。

【0134】

図6はトランジスタの上面図および断面図である。図6(A)に示した一点鎖線A−Bおよび一点鎖線C−Dにおける断面は、それぞれ図6(B)に示すA−B断面および図6(C)に示すC−D断面に対応する。

【0135】

以下に、図6(B)に示すA−B断面について詳細に説明する。

【0136】

図6に示すトランジスタは、基板100と、基板100上のゲート電極604と、ゲート電極604を覆う、第1のゲート絶縁膜612a、および第1のゲート絶縁膜612a上の第2のゲート絶縁膜612bからなるゲート絶縁膜612と、ゲート絶縁膜612を介してゲート電極604上にあり、チャネル領域605、ソース領域607aおよびドレイン領域607bを有する酸化物半導体膜606と、ゲート絶縁膜612および酸化物半導体膜606上の、ソース領域607aおよびドレイン領域607bをそれぞれ露出する開口部を有する層間絶縁膜618と、層間絶縁膜618に設けられた開口部を介して酸化物半導体膜606と接する一対の電極616と、を有する。ここで、一対の電極616、酸化物半導体膜606、ゲート電極604、層間絶縁膜618およびゲート絶縁膜612は、それぞれ示した一対の電極116、酸化物半導体膜106、ゲート電極104、層間絶縁膜118およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

【0137】

図6は、ゲート電極604とチャネル領域605が概略同一の上面形状として図示されているが、これに限定されない。ゲート電極604とチャネル領域605の形状が異なっていても構わない。

【0138】

なお、ソース領域607aおよびドレイン領域607bは、窒素、リン、水素、または希ガスなどを含む。

【0139】

なお、チャネル領域605は高抵抗領域であり、ソース領域607aおよびドレイン領域607b低抵抗領域である。

【0140】

次に、図6に示したトランジスタの作製方法について、図12を用いて説明する。

【0141】

まず、基板100上にゲート電極604を形成する。次に、ゲート電極604を覆う、第1のゲート絶縁膜612a、および第1のゲート絶縁膜612a上の第2のゲート絶縁膜612bからなるゲート絶縁膜612を形成する(図12(A)参照。)。

【0142】

次に、酸化物半導体膜606を形成する(図12(B)参照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜606から脱離した水素を、第2のゲート絶縁膜612bを介して第1のゲート絶縁膜612aへ移動させる。移動した水素は、第1のゲート絶縁膜612aで捕縛される。このとき、酸化物半導体膜606の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜612aの水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

【0143】

次に、レジストマスクなどを用いて、酸化物半導体膜606の一部に窒素、リン、水素、または希ガスを添加する。該添加、または該添加に加えて加熱処理を行うことにより、酸化物半導体膜606の、ゲート電極604と重畳しない領域を低抵抗化し、チャネル領域605、ソース領域607aおよびドレイン領域607bを形成する(図12(C)参照。)。なお、ここで行う加熱処理を、ゲート絶縁膜612を形成した後に行う加熱処理に代えることができる。なお、レジストマスクなどは、ゲート電極604をマスクに裏面露光技術によって形成しても構わない。その場合、ソース領域607aおよびドレイン領域607bと、ゲート電極604との重畳する面積が小さくできるため寄生容量が低減され、トランジスタの動作速度を高めることができる。また、レジストマスクを形成するためのフォトマスク数が低減できるため、トランジスタの作製コストを低減することができるため好ましい。

【0144】

次に、ゲート絶縁膜612および酸化物半導体膜606上に、ソース領域607aおよびドレイン領域607bをそれぞれ露出する開口部を有する層間絶縁膜618を形成する。次に、導電膜をスパッタリング法、蒸着法などで成膜し、加工して、酸化物半導体膜606と接する一対の電極616を形成する(図12(D)参照。)。

【0145】

以上の工程によって、図6に示したトランジスタを作製することができる。

【0146】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0147】

(実施の形態2)

本実施の形態では、実施の形態1に示したトランジスタを用いて作製した液晶表示装置について説明する。なお、本実施の形態では液晶表示装置に本発明の一形態を適用した例について説明するが、これに限定されるものではない。例えば、発光装置の一つであるEL(Electro Luminescence)表示装置に本発明の一形態を適用することも、当業者であれば容易に想到し得るものである。

【0148】

図13にアクティブマトリクス駆動方式の液晶表示装置の回路図を示す。液晶表示装置は、ソース線SL_1乃至SL_a、ゲート線GL_1乃至GL_bおよび複数の画素2200を有する。画素2200は、トランジスタ2230と、キャパシタ2220と、液晶素子2210と、を含む。こうした画素2200が複数集まって液晶表示装置の画素部を構成する。なお、単にソース線またはゲート線を指す場合には、ソース線SLまたはゲート線GLと記載することもある。

【0149】

トランジスタ2230は、本発明の一態様である実施の形態1で示したトランジスタを用いる。実施の形態1で示したトランジスタは電気的特性が良好な酸化物半導体を用いたトランジスタであるため、表示品位が高く、消費電力が小さい表示装置を得ることができる。

【0150】

ゲート線GLはトランジスタ2230のゲートと接続し、ソース線SLはトランジスタ2230のソースと接続し、トランジスタ2230のドレインは、キャパシタ2220の一方の容量電極および液晶素子2210の一方の画素電極と接続する。キャパシタ2220の他方の容量電極および液晶素子2210の他方の画素電極は、共通電極と接続する。なお、共通電極はゲート線GLと同一層かつ同一材料で設けてもよい。

【0151】

また、ゲート線GLは、ゲート駆動回路と接続される。ゲート駆動回路は、実施の形態1で示したトランジスタを含んでもよい。

【0152】

また、ソース線SLは、ソース駆動回路と接続される。ソース駆動回路は、実施の形態1で示したトランジスタを含んでもよい。

【0153】

なお、ゲート駆動回路およびソース駆動回路のいずれかまたは両方を、別途用意された基板上に形成し、COG(Chip On Glass)、ワイヤボンディング、またはTAB(Tape Automated Bonding)などの方法を用いて接続してもよい。

【0154】

また、トランジスタは静電気などにより破壊されやすいため、保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

【0155】

ゲート線GLにトランジスタ2230のしきい値電圧以上になるように電圧を印加すると、ソース線SLから供給された電荷がトランジスタ2230のドレイン電流となってキャパシタ2220に蓄積される。1行分の充電後、該行にあるトランジスタ2230はオフ状態となり、ソース線SLから電圧が掛からなくなるが、キャパシタ2220に蓄積された電荷によって必要な電圧を維持することができる。その後、次の行のキャパシタ2220の充電に移る。このようにして、1行からb行の充電を行う。ドレイン電流とは、トランジスタにおいてソースからチャネルを介してドレインに流れる電流のことである。ドレイン電流はゲート電圧がしきい値電圧よりも大きいときに流れる。

【0156】

なお、トランジスタ2230にオフ電流の小さなトランジスタを用いる場合、電圧を維持する期間を長くすることができる。この効果によって、動きの少ない画像(静止画を含む。)では、表示の書き換え周波数を低減でき、さらなる消費電力の低減が可能となる。また、キャパシタ2220の容量をさらに小さくすることが可能となるため、充電に必要な消費電力を低減することができる。

【0157】

以上のように、本発明の一態様によって、表示品位が高く、消費電力の小さい液晶表示装置を提供することができる。

【0158】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0159】

(実施の形態3)

本実施の形態では、実施の形態1で示したトランジスタを用いて、半導体記憶装置を作製する例について説明する。

【0160】

揮発性半導体記憶装置の代表的な例としては、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶するDRAM(Dynamic Random Access Memory)、フリップフロップなどの回路を用いて記憶内容を保持するSRAM(Static Random Access Memory)がある。

【0161】

不揮発性半導体記憶装置の代表例としては、トランジスタのゲートとチャネル領域との間にノードを有し、当該ノードに電荷を保持することで記憶を行うフラッシュメモリがある。

【0162】

上述した半導体記憶装置に含まれるトランジスタの一部に実施の形態1で示したトランジスタを適用することができる。

【0163】

まずは、実施の形態1で示したトランジスタを適用した半導体記憶装置を構成するメモリセルについて図14を用いて説明する。

【0164】

メモリセルは、ビット線BLと、ワード線WLと、センスアンプSAmpと、トランジスタTrと、キャパシタCと、を有する(図14(A)参照。)。

【0165】

キャパシタCに保持された電圧の時間変化は、トランジスタTrのオフ電流によって図14(B)に示すように徐々に低減していくことが知られている。当初V0からV1まで充電された電圧は、時間が経過するとdata1を読み出す限界点であるVAまで低減する。この期間を保持期間T_1とする。即ち、2値メモリセルの場合、保持期間T_1の間にリフレッシュをする必要がある。

【0166】

ここで、トランジスタTrに実施の形態1で示したトランジスタを適用すると、オフ電流が小さいため、保持期間T_1を長くすることができる。即ち、リフレッシュの頻度を少なくすることが可能となるため、消費電力を低減することができる。例えば、オフ電流が1×10−21A以下、好ましくは1×10−24A以下となった酸化物半導体膜を用いたトランジスタでメモリセルを構成すると、電力を供給せずに数日間から数十年間に渡ってデータを保持することが可能となる。

【0167】

以上のように、本発明の一態様によって、信頼性が高く、消費電力の小さい半導体記憶装置を得ることができる。

【0168】

次に、実施の形態1で示したトランジスタを適用した半導体記憶装置を構成するメモリセルについて図14と異なる例を図15を用いて説明する。

【0169】

図15(A)は、メモリセルの回路図である。メモリセルは、トランジスタTr_1と、トランジスタTr_1のゲートと接続するゲート線GL_1と、トランジスタTr_1のソースと接続するソース線SL_1と、トランジスタTr_2と、トランジスタTr_2のソースと接続するソース線SL_2と、トランジスタTr_2のドレインと接続するドレイン線DL_2と、キャパシタCと、キャパシタCの一端と接続する容量線CLと、キャパシタCの他端、トランジスタTr_1のドレインおよびトランジスタTr_2のゲートと接続するノードNと、を有する。

【0170】

なお、図15(A)に示すメモリセルは、ノードNの電位に応じて、トランジスタTr_2のしきい値電圧が変動することを利用したものである。例えば、図15(B)は容量線CLの電圧VCLと、トランジスタTr_2を流れるドレイン電流Ids_2との関係を説明する図である。

【0171】

ここで、ノードNは、トランジスタTr_1を介して電圧を調整することができる。例えば、ソース線SL_1の電位をVDDとする。このとき、ゲート線GL_1の電位をトランジスタTr_1のしきい値電圧VthにVDDを加えた電位以上とすることで、ノードNの電位をHIGHにすることができる。また、ゲート線GL_1の電位をトランジスタTr_1のしきい値電圧Vth以下とすることで、ノードNの電位をLOWにすることができる。

【0172】

そのため、N=LOWで示したVCL−Ids_2カーブと、N=HIGHで示したVCL−Ids_2カーブのいずれかを得ることができる。即ち、N=LOWでは、VCL=0VにてIds_2が小さいため、データ0となる。また、N=HIGHでは、VCL=0VにてIds_2が大きいため、データ1となる。このようにして、データを記憶することができる。

【0173】

ここで、トランジスタTr_1に実施の形態1で示したトランジスタを適用すると、該トランジスタはオフ電流を極めて小さくすることができるため、ノードNに蓄積された電荷がトランジスタTr_1のソースおよびドレイン間を意図せずにリークすることを抑制できる。そのため、長期間に渡ってデータを保持することができる。また、本発明の一態様に係るトランジスタTr_1はしきい値電圧が調整されるため、書き込みに必要な電圧を低減することが可能となり、フラッシュメモリなどと比較して消費電力を低減することができる。

【0174】

なお、トランジスタTr_2に、実施の形態1で示したトランジスタを適用しても構わない。

【0175】

以上のように、本発明の一態様によって、長期間の信頼性が高く、消費電力の小さい半導体記憶装置を得ることができる。

【0176】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0177】

(実施の形態4)

実施の形態1で示したトランジスタを少なくとも一部に用いてCPU(Central Processing Unit)を構成することができる。

【0178】

図16(A)は、CPUの具体的な構成を示すブロック図である。図16(A)に示すCPUは、基板1190上に、演算回路(ALU:Arithmetic logic unit)1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース(Bus I/F)1198、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)1189を有している。基板1190には、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図16(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

【0179】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0180】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

【0181】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。

【0182】

図16(A)に示すCPUでは、レジスタ1196に、記憶素子が設けられている。レジスタ1196の記憶素子には、実施の形態3に示す記憶素子を用いることができる。

【0183】

図16(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有する記憶素子において、位相反転素子によるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。位相反転素子によるデータの保持が選択されている場合、レジスタ1196内の記憶素子への、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内の記憶素子への電源電圧の供給を停止することができる。

【0184】

電源停止に関しては、図16(B)または図16(C)に示すように、記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図16(B)および図16(C)の回路の説明を行う。

【0185】

図16(B)および図16(C)では、記憶素子への電源電位の供給を制御するスイッチング素子に、実施の形態1で示したトランジスタを含む記憶回路の構成の一例を示す。

【0186】

図16(B)に示す記憶装置は、スイッチング素子1141と、記憶素子1142を複数有する記憶素子群1143とを有している。具体的に、それぞれの記憶素子1142に、実施の形態3に示す記憶素子を用いることができる。記憶素子群1143が有する各記憶素子1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが供給されている。さらに、記憶素子群1143が有するそれぞれの記憶素子1142に、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

【0187】

図16(B)では、スイッチング素子1141として、実施の形態1で示したオフ電流の極めて小さいトランジスタを用いており、該トランジスタは、そのゲートに与えられる信号SigAによりスイッチングが制御される。

【0188】

なお、図16(B)では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

【0189】

また、図16(C)には、記憶素子群1143が有するそれぞれの記憶素子1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、記憶素子群1143が有するそれぞれの記憶素子1142への、ローレベルの電源電位VSSの供給を制御することができる。

【0190】

記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

【0191】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)などのLSIにも応用可能である。

【0192】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【0193】

(実施の形態5)

本実施の形態では、実施の形態1乃至実施の形態4を適用した電子機器の例について説明する。

【0194】

図17(A)は携帯型情報端末である。図17(A)に示す携帯型情報端末は、筐体9300と、ボタン9301と、マイクロフォン9302と、表示部9303と、スピーカ9304と、カメラ9305と、を具備し、携帯型電話機としての機能を有する。本発明の一態様は、表示部9303およびカメラ9305に適用することができる。また、図示しないが、本体内部にある演算装置、無線回路または記憶回路に本発明の一態様を適用することもできる。

【0195】

図17(B)は、ディスプレイである。図17(B)に示すディスプレイは、筐体9310と、表示部9311と、を具備する。本発明の一態様は、表示部9311に適用することができる。本発明の一態様を用いることで、表示部9311のサイズを大きくしたときにも表示品位が高く、消費電力が小さいディスプレイとすることができる。

【0196】

図17(C)は、デジタルスチルカメラである。図17(C)に示すデジタルスチルカメラは、筐体9320と、ボタン9321と、マイクロフォン9322と、表示部9323と、を具備する。本発明の一態様は、表示部9323に適用することができる。また、図示しないが、記憶回路またはイメージセンサに本発明の一態様を適用することもできる。

【0197】

本発明の一態様を用いることで、電子機器の消費電力を小さくでき、かつ信頼性を高めることができる。

【0198】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【実施例1】

【0199】

本実施例では、酸化物半導体膜から脱離した水素が水素透過膜を介して水素捕縛膜へ移動する具体的な例について、加熱処理を行った試料および加熱処理を行っていない試料のSIMS結果を用いて説明する。

【0200】

石英基板上に酸化物半導体膜(In−Ga−Zn−O膜)を300nmの厚さで成膜し、酸化物半導体膜上に酸化シリコン膜を5nmの厚さで成膜し、酸化シリコン膜上に酸窒化物膜(In−Ga−Zn−O−N膜)を300nmの厚さで成膜した試料を用意した。

【0201】

酸化物半導体膜は、スパッタリング法により、In−Ga−Zn−Oターゲット(mol数比、In2O3:ZnO:Ga2O3=1:1:2)を用い、ターゲット−基板間に印加する電力を500W(DC)、成膜圧力を0.4Pa、成膜ガス流量をアルゴン30sccmおよび酸素15sccmとし、基板表面温度が200℃になるよう加熱処理しながら成膜した。

【0202】

酸化シリコン膜は、スパッタリング法により、合成石英ターゲットを用い、成膜電力を1kW、成膜圧力を0.4Pa、成膜ガス流量をアルゴン25sccmおよび酸素25sccmとし、基板表面温度が100℃になるよう加熱処理しながら成膜した。

【0203】

酸窒化物膜は、スパッタリング法により、In−Ga−Zn−Oターゲット(mol数比、In2O3:ZnO:Ga2O3=1:1:2)を用い、成膜電力を500W、成膜圧力を0.4Pa、成膜ガス流量を窒素40sccmとし、基板表面温度が200℃になるよう加熱処理しながら成膜した。

【0204】

図18(A)はSIMSによる水素濃度の深さ方向分布を、図18(B)はSIMSによる窒素濃度の深さ方向分布を示す。ここで、範囲6001は酸窒化物膜を、範囲6002は酸化シリコン膜を、範囲6003は酸化物半導体膜を、範囲6004は石英基板を示す。ただし、範囲6002は定量化されていない。また、各層の界面近傍はマトリックス効果により正確な定量値が得られていない。なお、SIMSは、CAMECA社製IMS 7fRを用いた。

【0205】

図18(A)において、細線6010は成膜直後の試料の水素濃度分布を示し、太線6020は成膜後に窒素雰囲気にて550℃で1時間の加熱処理を行った試料の水素濃度分布を示す。前述の加熱処理を行うことで、酸化物半導体膜中の水素濃度が低減し、酸窒化物膜中の水素濃度が増大していることがわかる。即ち、前述の加熱処理によって、酸化物半導体膜から酸化シリコン膜を介して酸窒化物膜に水素が移動していることがわかる。

【0206】

図18(B)において、細線6030は成膜直後の試料の窒素濃度分布を示し、太線6040は成膜後に窒素雰囲気にて550℃で1時間の加熱処理を行った試料の窒素濃度分布を示す。前述の加熱処理前後で、試料中の窒素濃度分布はほとんど変動しないことがわかる。

【符号の説明】

【0207】

100 基板

104 ゲート電極

106 酸化物半導体膜

112 ゲート絶縁膜

112a 第1のゲート絶縁膜

112b 第2のゲート絶縁膜

116 一対の電極

118 層間絶縁膜

136 酸化物半導体膜

206 酸化物半導体膜

216 一対の電極

218 層間絶縁膜

236 酸化物半導体膜

302 下地絶縁膜

304 ゲート電極

306 酸化物半導体膜

312 ゲート絶縁膜

312a 第1のゲート絶縁膜

312b 第2のゲート絶縁膜

316 一対の電極

404 ゲート電極

406 酸化物半導体膜

412 ゲート絶縁膜

412a 第1のゲート絶縁膜

412b 第2のゲート絶縁膜

416 一対の電極

504 ゲート電極

505 チャネル領域

506 酸化物半導体膜

507a ソース領域

507b ドレイン領域

512 ゲート絶縁膜

512a 第1のゲート絶縁膜

512b 第2のゲート絶縁膜

516 一対の電極

518 層間絶縁膜

604 ゲート電極

605 チャネル領域

606 酸化物半導体膜

607a ソース領域

607b ドレイン領域

612 ゲート絶縁膜

612a 第1のゲート絶縁膜

612b 第2のゲート絶縁膜

616 一対の電極

618 層間絶縁膜

1141 スイッチング素子

1142 記憶素子

1143 記憶素子群

1189 ROMインターフェース

1190 基板

1191 ALU

1192 ALUコントローラ

1193 インストラクションデコーダ

1194 インタラプトコントローラ

1195 タイミングコントローラ

1196 レジスタ

1197 レジスタコントローラ

1198 バスインターフェース

1199 ROM

2200 画素

2210 液晶素子

2220 キャパシタ

2230 トランジスタ

6001 範囲

6002 範囲

6003 範囲

6004 範囲

6010 細線

6020 太線

6030 細線

6040 太線

9300 筐体

9301 ボタン

9302 マイクロフォン

9303 表示部

9304 スピーカ

9305 カメラ

9310 筐体

9311 表示部

9320 筐体

9321 ボタン

9322 マイクロフォン

9323 表示部

【特許請求の範囲】

【請求項1】

ゲート電極を形成し、

前記ゲート電極を覆って、水素捕縛膜と水素透過膜がこの順に積層されたゲート絶縁膜を形成し、

前記ゲート絶縁膜上に酸化物半導体膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記酸化物半導体膜上に、前記酸化物半導体膜と少なくとも一部を接して一対の電極を形成することを特徴とする半導体装置の作製方法。

【請求項2】

ゲート電極を形成し、

前記ゲート電極を覆って、水素捕縛膜と水素透過膜がこの順に積層されたゲート絶縁膜を形成し、

前記ゲート絶縁膜上に一対の電極を形成し、

前記ゲート絶縁膜および前記一対の電極上に、前記一対の電極と少なくとも一部を接して酸化物半導体膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させることを特徴とする半導体装置の作製方法。

【請求項3】

酸化物半導体膜を形成し、

前記酸化物半導体膜上に、前記酸化物半導体膜と少なくとも一部を接して一対の電極を形成し、

前記酸化物半導体膜および前記一対の電極上に、水素透過膜と水素捕縛膜がこの順に積層されたゲート絶縁膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記ゲート絶縁膜を介して前記酸化物半導体膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

【請求項4】

一対の電極を形成し、

前記一対の電極上に、前記一対の電極と少なくとも一部を接して酸化物半導体膜を形成し、

前記一対の電極および前記酸化物半導体膜上に、水素透過膜と水素捕縛膜がこの順に積層されたゲート絶縁膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記ゲート絶縁膜を介して前記酸化物半導体膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

【請求項5】

酸化物半導体膜を形成し、

前記酸化物半導体膜上に、水素透過膜と水素捕縛膜がこの順に積層されたゲート絶縁膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記ゲート絶縁膜を介して前記酸化物半導体膜上にゲート電極を形成し、

前記ゲート電極をマスクに、前記酸化物半導体膜の一部に前記酸化物半導体膜を低抵抗化する不純物を添加し、

前記ゲート絶縁膜および前記ゲート電極上に層間絶縁膜を形成し、

前記ゲート絶縁膜および前記層間絶縁膜に、前記酸化物半導体膜の前記一部を露出する開口部を形成し、

前記層間絶縁膜上に、前記開口部を介して前記酸化物半導体膜と接する一対の電極を形成することを特徴とする半導体装置の作製方法。

【請求項6】

ゲート電極を形成し、

前記ゲート電極を覆って、水素捕縛膜と水素透過膜がこの順に積層されたゲート絶縁膜を形成し、

前記ゲート絶縁膜を介して前記ゲート電極上に酸化物半導体膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記酸化物半導体膜上にマスクを形成し、前記酸化物半導体膜の一部に前記酸化物半導体膜を低抵抗化する不純物を添加し、

前記ゲート絶縁膜および前記酸化物半導体膜上に層間絶縁膜を形成し、

前記層間絶縁膜に前記酸化物半導体膜の前記一部を露出する開口部を形成し、

前記層間絶縁膜上に、前記開口部を介して前記酸化物半導体膜と接する一対の電極を形成することを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至請求項6のいずれか一において、

前記水素捕縛膜を構成する金属元素と前記酸化物半導体膜を構成する金属元素が一致しており、

前記水素透過膜は、前記金属元素を含まないことを特徴とする半導体装置の作製方法。

【請求項8】

請求項1乃至請求項7のいずれか一において、

前記水素捕縛膜はインジウムを含む酸窒化物膜であり、

前記水素透過膜は酸化シリコン膜または酸化窒化シリコン膜であることを特徴とする半導体装置の作製方法。

【請求項9】

請求項8において、

前記酸化物半導体膜がIn−Ga−Zn−O膜であり、

前記インジウムを含む酸窒化物膜がIn−Ga−Zn−O−N膜であることを特徴とする半導体装置の作製方法。

【請求項10】

請求項8または請求項9において、

前記酸化シリコン膜または前記酸化窒化シリコン膜の厚さが5nm以下であることを特徴とする半導体装置の作製方法。

【請求項11】

請求項1乃至請求項10のいずれか一において、

前記加熱処理の温度が450℃超過基板の歪み点未満であることを特徴とする半導体装置の作製方法。

【請求項12】

ゲート電極と、

前記ゲート電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜と、

前記酸化物半導体膜の少なくとも一部に接して設けられた一対の電極と、を有し、

前記ゲート絶縁膜は、前記ゲート電極側から水素捕縛膜と水素透過膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項13】

酸化物半導体膜と、

前記酸化物半導体膜の少なくとも一部に接して設けられた一対の電極と、

前記酸化物半導体膜および前記一対の電極上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記酸化物半導体膜上に設けられたゲート電極と、を有し、

前記ゲート絶縁膜は、前記酸化物半導体膜側から水素透過膜と水素捕縛膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項14】

低抵抗領域および高抵抗領域を有する酸化物半導体膜と、

ゲート絶縁膜と、

前記ゲート絶縁膜を介して前記酸化物半導体膜と重畳するゲート電極と、

少なくとも前記ゲート絶縁膜上に設けられ、前記低抵抗領域を露出する開口部を有する層間絶縁膜と、

前記層間絶縁膜上に設けられ、前記開口部を介して前記酸化物半導体膜と接する一対の電極と、を有し、

前記ゲート絶縁膜は、前記酸化物半導体膜側から水素透過膜と水素捕縛膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項15】

請求項12乃至請求項14のいずれか一において、

前記ゲート絶縁膜は、前記ゲート電極側からインジウムを含む酸窒化物膜と酸化シリコン膜または酸化窒化シリコン膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項16】

請求項15において、

前記酸化物半導体膜がIn−Ga−Zn−O膜であり、

前記インジウムを含む酸窒化物膜がIn−Ga−Zn−O−N膜であることを特徴とする半導体装置。

【請求項17】

請求項15または請求項16において、

前記酸化シリコン膜または前記酸化窒化シリコン膜の厚さは5nm以下であることを特徴とする半導体装置。

【請求項1】

ゲート電極を形成し、

前記ゲート電極を覆って、水素捕縛膜と水素透過膜がこの順に積層されたゲート絶縁膜を形成し、

前記ゲート絶縁膜上に酸化物半導体膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記酸化物半導体膜上に、前記酸化物半導体膜と少なくとも一部を接して一対の電極を形成することを特徴とする半導体装置の作製方法。

【請求項2】

ゲート電極を形成し、

前記ゲート電極を覆って、水素捕縛膜と水素透過膜がこの順に積層されたゲート絶縁膜を形成し、

前記ゲート絶縁膜上に一対の電極を形成し、

前記ゲート絶縁膜および前記一対の電極上に、前記一対の電極と少なくとも一部を接して酸化物半導体膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させることを特徴とする半導体装置の作製方法。

【請求項3】

酸化物半導体膜を形成し、

前記酸化物半導体膜上に、前記酸化物半導体膜と少なくとも一部を接して一対の電極を形成し、

前記酸化物半導体膜および前記一対の電極上に、水素透過膜と水素捕縛膜がこの順に積層されたゲート絶縁膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記ゲート絶縁膜を介して前記酸化物半導体膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

【請求項4】

一対の電極を形成し、

前記一対の電極上に、前記一対の電極と少なくとも一部を接して酸化物半導体膜を形成し、

前記一対の電極および前記酸化物半導体膜上に、水素透過膜と水素捕縛膜がこの順に積層されたゲート絶縁膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記ゲート絶縁膜を介して前記酸化物半導体膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

【請求項5】

酸化物半導体膜を形成し、

前記酸化物半導体膜上に、水素透過膜と水素捕縛膜がこの順に積層されたゲート絶縁膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記ゲート絶縁膜を介して前記酸化物半導体膜上にゲート電極を形成し、

前記ゲート電極をマスクに、前記酸化物半導体膜の一部に前記酸化物半導体膜を低抵抗化する不純物を添加し、

前記ゲート絶縁膜および前記ゲート電極上に層間絶縁膜を形成し、

前記ゲート絶縁膜および前記層間絶縁膜に、前記酸化物半導体膜の前記一部を露出する開口部を形成し、

前記層間絶縁膜上に、前記開口部を介して前記酸化物半導体膜と接する一対の電極を形成することを特徴とする半導体装置の作製方法。

【請求項6】

ゲート電極を形成し、

前記ゲート電極を覆って、水素捕縛膜と水素透過膜がこの順に積層されたゲート絶縁膜を形成し、

前記ゲート絶縁膜を介して前記ゲート電極上に酸化物半導体膜を形成した後、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させ、

前記酸化物半導体膜上にマスクを形成し、前記酸化物半導体膜の一部に前記酸化物半導体膜を低抵抗化する不純物を添加し、

前記ゲート絶縁膜および前記酸化物半導体膜上に層間絶縁膜を形成し、

前記層間絶縁膜に前記酸化物半導体膜の前記一部を露出する開口部を形成し、

前記層間絶縁膜上に、前記開口部を介して前記酸化物半導体膜と接する一対の電極を形成することを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至請求項6のいずれか一において、

前記水素捕縛膜を構成する金属元素と前記酸化物半導体膜を構成する金属元素が一致しており、

前記水素透過膜は、前記金属元素を含まないことを特徴とする半導体装置の作製方法。

【請求項8】

請求項1乃至請求項7のいずれか一において、

前記水素捕縛膜はインジウムを含む酸窒化物膜であり、

前記水素透過膜は酸化シリコン膜または酸化窒化シリコン膜であることを特徴とする半導体装置の作製方法。

【請求項9】

請求項8において、

前記酸化物半導体膜がIn−Ga−Zn−O膜であり、

前記インジウムを含む酸窒化物膜がIn−Ga−Zn−O−N膜であることを特徴とする半導体装置の作製方法。

【請求項10】

請求項8または請求項9において、

前記酸化シリコン膜または前記酸化窒化シリコン膜の厚さが5nm以下であることを特徴とする半導体装置の作製方法。

【請求項11】

請求項1乃至請求項10のいずれか一において、

前記加熱処理の温度が450℃超過基板の歪み点未満であることを特徴とする半導体装置の作製方法。

【請求項12】

ゲート電極と、

前記ゲート電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜と、

前記酸化物半導体膜の少なくとも一部に接して設けられた一対の電極と、を有し、

前記ゲート絶縁膜は、前記ゲート電極側から水素捕縛膜と水素透過膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項13】

酸化物半導体膜と、

前記酸化物半導体膜の少なくとも一部に接して設けられた一対の電極と、

前記酸化物半導体膜および前記一対の電極上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記酸化物半導体膜上に設けられたゲート電極と、を有し、

前記ゲート絶縁膜は、前記酸化物半導体膜側から水素透過膜と水素捕縛膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項14】

低抵抗領域および高抵抗領域を有する酸化物半導体膜と、

ゲート絶縁膜と、

前記ゲート絶縁膜を介して前記酸化物半導体膜と重畳するゲート電極と、

少なくとも前記ゲート絶縁膜上に設けられ、前記低抵抗領域を露出する開口部を有する層間絶縁膜と、

前記層間絶縁膜上に設けられ、前記開口部を介して前記酸化物半導体膜と接する一対の電極と、を有し、

前記ゲート絶縁膜は、前記酸化物半導体膜側から水素透過膜と水素捕縛膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項15】

請求項12乃至請求項14のいずれか一において、

前記ゲート絶縁膜は、前記ゲート電極側からインジウムを含む酸窒化物膜と酸化シリコン膜または酸化窒化シリコン膜がこの順に積層して設けられた膜であることを特徴とする半導体装置。

【請求項16】

請求項15において、