半導体装置およびその製造方法

【課題】トンネルトランジスタのトンネルオフリーク電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、MOSFETを越える高性能化、低消費電力化を目指して、トンネルトランジスタが精力的に研究されている。トンネルトランジスタでは、サブスレショルド領域のゲート電圧に対するドレイン電流の勾配(サブスレショルドスロープ)が、MOSFETにおける勾配の理論的限界値を超えることが可能であり、MOSFETを超える低消費電力化をもたらすことが期待されている。一方、トンネルトランジスタでは、ドレイン領域でのトンネルオフリーク電流の低減が課題とされており、いかにサブスレショルドスロープが急峻であろうと、このリーク電流を低減しなければ低消費電力化は困難である。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】F. Mayer et al., “Impact of SOI, Si1-xGexOI and GeOI substrates on CMOS compatible Tunnel FET performance”, IEDM, 163-166 (2008)

【発明の概要】

【発明が解決しようとする課題】

【0004】

トンネルトランジスタのトンネルオフリーク電流を低減することが可能な半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

一の実施形態による半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

【図面の簡単な説明】

【0006】

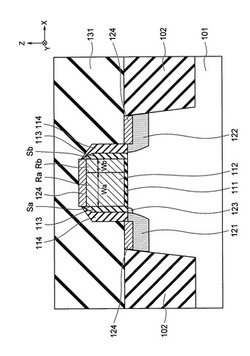

【図1】第1実施形態の半導体装置の構造を示す断面図である。

【図2】第1実施形態の半導体装置の製造方法を示す断面図(1/4)である。

【図3】第1実施形態の半導体装置の製造方法を示す断面図(2/4)である。

【図4】第1実施形態の半導体装置の製造方法を示す断面図(3/4)である。

【図5】第1実施形態の半導体装置の製造方法を示す断面図(4/4)である。

【図6】第1実施形態の変形例の半導体装置の製造方法を示す断面図である。

【図7】第2実施形態の半導体装置の構造を示す断面図である。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施形態を、図面を参照して説明する。

【0008】

(第1実施形態)

図1は、第1実施形態の半導体装置の構造を示す断面図である。

【0009】

図1の半導体装置は、トンネルトランジスタの構成要素として、半導体基板101と、素子分離絶縁膜102と、ゲート絶縁膜111と、ゲート電極112と、第1の側壁絶縁膜113と、第2の側壁絶縁膜114と、ソース領域121と、ドレイン領域122と、ソースエクステンション領域123と、シリサイド層124と、層間絶縁膜131とを備えている。

【0010】

半導体基板101は、例えばシリコン基板である。図1には、半導体基板101の主面に平行で、互いに垂直なX方向およびY方向と、半導体基板101の主面に垂直なZ方向が示されている。X方向とY方向はそれぞれ、トンネルトランジスタのゲート長方向と、チャネル幅方向に相当する。

【0011】

素子分離絶縁膜102は、トンネルトランジスタ同士を電気的に分離するよう、半導体基板101内に形成されている。素子分離絶縁膜102は、例えばシリコン酸化膜(SiO2)である。本実施形態の素子分離絶縁膜102は、STI(Shallow Trench Isolation)絶縁膜に相当する。

【0012】

ゲート電極112は、素子分離絶縁膜102間の半導体基板101上に、ゲート絶縁膜111を介して形成されている。ゲート絶縁膜111は、例えばシリコン酸化膜である。また、ゲート電極112は、例えばポリシリコン層である。符号Saは、ゲート電極112におけるソース領域121側の第1側面を示し、符号Sbは、ゲート電極112におけるドレイン領域122側の第2側面を示す。

【0013】

第1の側壁絶縁膜113は、ゲート電極112の第1、第2側面Sa、Sbに形成されている。第1の側壁絶縁膜113は、例えばシリコン酸化膜である。また、第2の側壁絶縁膜114は、ゲート電極112の第1、第2側面Sa、Sbに、第1の側壁絶縁膜113を介して形成されている。第2の側壁絶縁膜114は、例えばシリコン酸化膜である。

【0014】

ソース領域121とドレイン領域122は、半導体基板101内に、ゲート電極112を挟むように形成されている。本実施形態では、ソース領域121はP型領域であり、ドレイン領域122はN型領域である。P導電型は、第1導電型の例であり、N導電型は、第1導電型とは逆導電型の第2導電型の例である。

【0015】

ソースエクステンション領域123は、ソース領域121とドレイン領域122との間において、ソース領域121に隣接して形成されている。本実施形態では、ソースエクステンション領域123は、P型領域である。なお、本実施形態では、ドレイン領域122でのトンネルオフリーク電流を低減するため、ドレインエクステンション領域は形成していない。

【0016】

シリサイド層124は、ゲート電極122、ソース領域121、ドレイン領域122内の上部に形成されている。シリサイド層124の例としては、NiSi(ニッケルシリサイド)層や、CoSi(コバルトシリサイド)層などが挙げられる。

【0017】

層間絶縁膜131は、半導体基板101上に、トンネルトランジスタを覆うように形成されている。層間絶膜膜131は、例えばシリコン酸化膜である。

【0018】

なお、図1のトンネルトランジスタは、N型トランジスタであるが、P型トランジスタとしてもよい。この場合、ソース領域111とソースエクステンション領域113は、N型領域となり、ドレイン領域112は、P型領域となる。

【0019】

(1)ゲート電極112の構造

次に、引き続き図1を参照し、ゲート電極112の構造について説明する。

【0020】

本実施形態のゲート電極112は、ゲート電極112内のソース領域121側に形成された第1領域Raと、ゲート電極112内のドレイン領域122側に形成された第2領域Rbとを有している。

【0021】

第1領域Raは、P型不純物を含有するP型領域である。第1領域Raは、本実施形態では概ねP型不純物のみを含有しているが、P型不純物の濃度がN型不純物の濃度よりも高ければ、P型不純物とN型不純物の両方を含有していてもよい。

【0022】

第2領域Rbは、P型不純物とN型不純物の両方を含有する領域である。第2領域Rbは、P型領域でもN型領域でもよい。ただし、第2領域Rbでは、P型不純物の濃度CPからN型不純物の濃度CNを引いた値ΔC(=CP−CN)を、第1領域Raに比べて低く設定する。よって、第1、第2領域Ra、Rbの値ΔCをそれぞれΔCa、ΔCbで表す場合、ΔCa>ΔCbの関係が成り立つ。

【0023】

よって、第1、第2領域Ra、Rbが共にP型領域の場合(即ちΔCa、ΔCb>0の場合)、第1領域RaはP+型領域となり、第2領域RbはP−型領域となる。

【0024】

また、第1、第2領域Ra、RbがそれぞれP型、N型領域の場合(即ちΔCa>0、ΔCb<0の場合)、ΔCbの絶対値は、ΔCaの絶対値より小さくても大きくてもよいし、ΔCaの絶対値と等しくてもよい。

【0025】

本実施形態では、ゲート電極112内に上記のような第1、第2領域Ra、Rbを形成することで、第1領域Raと第2領域Rbとの境界付近に空乏層が形成される。よって、本実施形態によれば、ゲート電極112内のドレイン領域122側の部分からチャネルへのゲート支配力を弱めて、トンネルトランジスタの非駆動時のトンネルオフリーク電流を低減することが可能となる。

【0026】

図1に示す符号Wa、Wbはそれぞれ、第1、第2領域Ra、Rbのゲート長方向の幅を示す。本実施形態では、第2領域Rbの幅Wbを、10nm以上に設定する。理由は、第2領域Rbの幅Wbを10nm以上に設定することで、空乏層の幅を、電子やホールのトンネリングを防止可能な10nm以上とすることが可能となるからである。同様の理由から、本実施形態では、第1領域Raの幅Waも、10nm以上に設定する。

【0027】

本実施形態では、Wa>Wbとなるよう幅Wa、Wbが設定されており、具体的には、幅Waは10nmより大きい値、幅Wbは10nm程度に設定されている。幅Waを10nmよりも大きく設定する理由は、ゲート電極112内のソース領域121側に非空乏層を設けるためである。

【0028】

なお、本実施形態では、図1の半導体装置を製造する際、アニーリング等により、第1領域Raから第2領域Rbへの不純物拡散や、第2領域Rbから第1領域Raへの不純物拡散が生じる。よって、第1領域Raと第2領域Rbとの境界付近では、P型不純物やN型不純物の濃度がなだらかに変化している。

【0029】

(2)半導体装置の製造方法

次に、図2〜図5を参照し、第1実施形態の半導体装置の製造方法を説明する。図2〜図5は、第1実施形態の半導体装置の製造方法を示す断面図である。

【0030】

まず、半導体基板101を用意する(図2(a))。次に、半導体基板101内に素子分離絶縁膜102を形成する(図2(a))。

【0031】

次に、図2(b)に示すように、熱酸化法により、素子分離絶縁膜102間の半導体基板101上に、ゲート絶縁膜111用の絶縁膜を形成する。次に、図2(b)に示すように、CVD(Chemical Vapor Deposition)により、半導体基板101上の全面に、ゲート電極112用の電極材を堆積する。

【0032】

次に、例えばイオン注入法により、図2(b)の電極材中にP型不純物を導入する。この際、イオン種としては、例えばB(ボロン)を使用する。また、イオン注入の際の加速電圧、ドース量はそれぞれ、例えば2keV、5×1015cm−2に設定する。

【0033】

次に、図3(a)に示すように、リソグラフィとRIE(Reactive Ion Etching)により、電極材をゲート電極112に加工する。こうして、半導体基板101上に、ゲート絶縁膜111を介して、P導電型のゲート電極112が形成される。

【0034】

次に、図3(b)に示すように、ゲート電極112の側面に、第1の側壁絶縁膜113を形成する。第1の側壁絶縁膜113は例えば、CVDにより半導体基板101上の全面に第1の側壁絶縁膜113用の絶縁膜を堆積し、RIEによりこの絶縁膜を異方的にエッチングすることで形成される。この絶縁膜の膜厚は、例えば5nmである。

【0035】

次に、図4(a)に示すように、ドレイン領域122を形成予定の領域を、レジスト膜201で覆う。次に、レジスト膜201をマスクとして、ソースエクステンション領域123を形成するためのイオン注入を行う。その結果、その後のアニーリング等により、半導体基板101内にソースエクステンション領域123が形成される。なお、このイオン注入では、イオン種として、例えばBF2を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば0.5keV、1×1015cm−2に設定する。

【0036】

なお、本実施形態では、ゲート電極112とソースエクステンション領域123に、同じ導電型の不純物(P型不純物)が導入される。よって、レジスト膜201は、ドレイン領域122を形成予定の領域さえ覆っていれば、ゲート電極112は覆っていても覆っていなくてもよい。図4(a)に示す例では、レジスト膜201は、ゲート電極112の一部のみを覆っている。レジスト膜201は、図4(a)のイオン注入後に除去する。

【0037】

次に、図4(b)に示すように、ゲート電極112の側面に、第1の側壁絶縁膜113を介して、第2の側壁絶縁膜114を形成する。第2の側壁絶縁膜114は例えば、CVDにより半導体基板101上の全面に第2の側壁絶縁膜114用の絶縁膜を堆積し、RIEによりこの絶縁膜を異方的にエッチングすることで形成される。この絶縁膜の膜厚は、例えば30nmである。

【0038】

次に、図5(a)に示すように、ドレイン領域122を形成予定の領域を、レジスト膜202で覆う。次に、レジスト膜202をマスクとして、ソース領域121を形成するためのイオン注入を行う。その結果、その後のアニーリング等により、半導体基板101内にソース領域121が形成される。なお、このイオン注入では、イオン種として、例えばBF2を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば15keV、3×1015cm−2に設定する。

【0039】

なお、本実施形態では、ゲート電極112とソース領域121に、同じ導電型の不純物が導入される。よって、レジスト膜202は、ドレイン領域122を形成予定の領域さえ覆っていれば、ゲート電極112は覆っていても覆っていなくてもよい。図5(a)に示す例では、レジスト膜202は、ゲート電極112の全体を覆っている。レジスト膜202は、図5(a)のイオン注入後に除去する。

【0040】

次に、図5(b)に示すように、ソース領域121に相当する領域を、レジスト膜203で覆う。次に、レジスト膜203をマスクとして、ドレイン領域122を形成するためのイオン注入を行う。その結果、その後のアニーリング等により、半導体基板101内にドレイン領域122が形成される。なお、このイオン注入では、イオン種として、例えばAs(ヒ素)を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば2.5keV、3×1015cm−2に設定する。

【0041】

なお、本実施形態では、レジスト膜203を、第1、第2領域Ra、Rbのうちの第1領域Raのみを覆うように形成する。その結果、N型不純物が、これらの領域Ra、Rbのうちの第2領域Rb内のみに注入される。よって、第1領域Raは、P型領域となり、第2領域Rbは、P型不純物およびN型不純物を含有する領域となる。本実施形態では、図5(b)に示す幅Wbを、例えば10nm程度に設定する。レジスト膜203は、図5(b)のイオン注入後に除去する。

【0042】

その後、本実施形態では、不純物を活性化するためのアニール工程において、例えば1025℃のスパイクアニールを実行する。また、サリサイド工程により、図1のシリサイド層124を自己整合的に形成する。さらには、半導体基板101上に、層間絶縁膜、コンタクトプラグ、ビアプラグ、配線層などを形成する。こうして、図1の半導体装置が製造される。

【0043】

なお、本実施形態では、第2領域Rb内へのN型不純物の導入を、ドレイン領域122内へのN型不純物の導入と同時に行っているが、ドレイン領域122内へのN型不純物の導入と別個に行ってもよい。前者には、工程数が少なくて済むという利点がある。一方、後者には、第2領域Rb内の不純物濃度を、ドレイン領域122内の不純物濃度と独立に設定できるという利点がある。後者の場合には、第2領域Rb用のイオン種として、例えばP(リン)を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば5keV、5×1015cm−2に設定する。

【0044】

(3)半導体装置の製造方法の変形例

次に、図6を参照し、第1実施形態の変形例の半導体装置の製造方法を説明する。図6は、第1実施形態の変形例の半導体装置の製造方法を示す断面図である。

【0045】

上述の第2領域Rbは、P型領域やN型領域とする代わりに、i型(イントリンシック型)領域としてもよい。これにより、図1の構造と同様に、ゲート電極112内のドレイン領域122側の部分からチャネルへのゲート支配力を弱めて、トンネルトランジスタの非駆動時のトンネルオフリーク電流を低減することが可能となる。

【0046】

i型の第2領域Rbを有する半導体装置は、例えば、図2(a)〜図5(b)の工程により製造可能である。ただし、図2(b)の工程において、電極材中へのP型不純物の導入は不要である。よって、図3(a)のゲート電極112は、i型電極となる。また、図5(b)の工程の代わりに、図6(a)と図6(b)の工程を実行する。以下、図6(a)と図6(b)の工程について説明する。

【0047】

まず、図6(a)に示すように、ソース領域121に相当する領域と、ゲート電極112の全体を、レジスト膜204で覆う。次に、レジスト膜204をマスクとして、ドレイン領域122を形成するためのイオン注入を行う。このイオン注入では、イオン種として、例えばAs(ヒ素)を使用する。その結果、その後のアニーリング等により、半導体基板101内にN型のドレイン領域122が形成される。

【0048】

次に、図6(b)に示すように、ソース領域121およびドレイン領域122に相当する領域と、ゲート電極112の一部を、レジスト膜205で覆う。具体的には、第1、第2領域Ra、Rbのうちの第2領域Rbのみを、レジスト膜205で覆う。次に、レジスト膜205をマスクとして、第1領域Ra内へのイオン注入を行う。このイオン注入では、イオン種として、例えばB(ボロン)を使用する。その結果、P型不純物が、これらの領域Ra、Rbのうちの第1領域Ra内のみに注入される。よって、その後のアニーリング等により、第1領域RaはP型領域となるが、第2領域Rbはi型領域のままとなる。

【0049】

なお、本実施形態では、第1領域Ra内へのP型不純物の導入を、ソース領域121内へのP型不純物の導入と別個に行っている。理由は、これらのP型不純物の導入を同時に行うと、ソース領域121が、ゲート電極112下の領域の内側に入りすぎるおそれがあるからである。ただし、この問題を回避可能であれば、第1領域Ra内へのP型不純物の導入を、ソース領域121内へのP型不純物の導入と同時に行ってもよい。

【0050】

(4)第1実施形態の効果

最後に、第1実施形態の効果について説明する。

【0051】

以上のように、本実施形態のゲート電極112は、ゲート電極112内のソース領域121側に形成された第1導電型の第1領域Raと、ゲート電極112内のドレイン領域122側に形成され、第1領域Raに比べて、第1導電型の不純物濃度から第2導電型の不純物濃度を引いた値が低い第2領域Rbとを有している。

【0052】

よって、本実施形態によれば、ゲート電極112内のドレイン領域122側の部分からチャネルへのゲート支配力が、ドレイン領域122側に近付くにつれて徐々に弱まる構造を実現することができる。その結果、トンネルトランジスタのトンネルオフリーク電流を低減することが可能となる。

【0053】

(第2実施形態)

図7は、第2実施形態の半導体装置の構造を示す断面図である。

【0054】

図7では、半導体基板101が、SOI(Semiconductor On Insulator)基板301に置き換えられている。SOI基板301は、半導体基板311と、半導体基板311上の埋め込み絶縁膜312と、埋め込み絶縁膜312上の半導体層313とを含んでいる。半導体基板311、埋め込み絶縁膜312、半導体層313はそれぞれ、例えばシリコン基板、シリコン酸化膜、シリコン層である。

【0055】

図7では、素子分離絶縁膜102が、埋め込み絶縁膜312を貫通しており、素子分離絶縁膜102の底面が、半導体基板301の上面よりも低い位置にある。よって、本実施形態では、トンネルトランジスタ同士が、素子分離絶縁膜102と埋め込み絶縁膜312により電気的に分離されている。ソース領域121、ドレイン領域122、ソースエクステンション領域123は、半導体層313内に形成されている。

【0056】

本実施形態によれば、トンネルトランジスタ同士が、素子分離絶縁膜102と埋め込み絶縁膜312により電気的に分離されるため、第1実施形態に比べて、パンチスルーを効果的に抑制することが可能となる。

【0057】

以上、第1及び第2実施形態について説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することを意図したものではない。これらの実施形態は、その他の様々な形態で実施することができる。また、これらの実施形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことにより、様々な変形例を得ることもできる。これらの形態や変形例は、発明の範囲や要旨に含まれており、特許請求の範囲及びこれに均等な範囲には、これらの形態や変形例が含まれる。

【符号の説明】

【0058】

101:半導体基板、102:素子分離絶縁膜、

111:ゲート絶縁膜、112:ゲート電極、

113:第1の側壁絶縁膜、114:第2の側壁絶縁膜、

121:ソース領域、122:ドレイン領域、

123:ソースエクステンション領域、124:シリサイド層、

131:層間絶縁膜、201〜205:レジスト膜、301:SOI基板、

311:半導体基板、312:埋め込み絶縁膜、313:半導体層

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、MOSFETを越える高性能化、低消費電力化を目指して、トンネルトランジスタが精力的に研究されている。トンネルトランジスタでは、サブスレショルド領域のゲート電圧に対するドレイン電流の勾配(サブスレショルドスロープ)が、MOSFETにおける勾配の理論的限界値を超えることが可能であり、MOSFETを超える低消費電力化をもたらすことが期待されている。一方、トンネルトランジスタでは、ドレイン領域でのトンネルオフリーク電流の低減が課題とされており、いかにサブスレショルドスロープが急峻であろうと、このリーク電流を低減しなければ低消費電力化は困難である。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】F. Mayer et al., “Impact of SOI, Si1-xGexOI and GeOI substrates on CMOS compatible Tunnel FET performance”, IEDM, 163-166 (2008)

【発明の概要】

【発明が解決しようとする課題】

【0004】

トンネルトランジスタのトンネルオフリーク電流を低減することが可能な半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

一の実施形態による半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

【図面の簡単な説明】

【0006】

【図1】第1実施形態の半導体装置の構造を示す断面図である。

【図2】第1実施形態の半導体装置の製造方法を示す断面図(1/4)である。

【図3】第1実施形態の半導体装置の製造方法を示す断面図(2/4)である。

【図4】第1実施形態の半導体装置の製造方法を示す断面図(3/4)である。

【図5】第1実施形態の半導体装置の製造方法を示す断面図(4/4)である。

【図6】第1実施形態の変形例の半導体装置の製造方法を示す断面図である。

【図7】第2実施形態の半導体装置の構造を示す断面図である。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施形態を、図面を参照して説明する。

【0008】

(第1実施形態)

図1は、第1実施形態の半導体装置の構造を示す断面図である。

【0009】

図1の半導体装置は、トンネルトランジスタの構成要素として、半導体基板101と、素子分離絶縁膜102と、ゲート絶縁膜111と、ゲート電極112と、第1の側壁絶縁膜113と、第2の側壁絶縁膜114と、ソース領域121と、ドレイン領域122と、ソースエクステンション領域123と、シリサイド層124と、層間絶縁膜131とを備えている。

【0010】

半導体基板101は、例えばシリコン基板である。図1には、半導体基板101の主面に平行で、互いに垂直なX方向およびY方向と、半導体基板101の主面に垂直なZ方向が示されている。X方向とY方向はそれぞれ、トンネルトランジスタのゲート長方向と、チャネル幅方向に相当する。

【0011】

素子分離絶縁膜102は、トンネルトランジスタ同士を電気的に分離するよう、半導体基板101内に形成されている。素子分離絶縁膜102は、例えばシリコン酸化膜(SiO2)である。本実施形態の素子分離絶縁膜102は、STI(Shallow Trench Isolation)絶縁膜に相当する。

【0012】

ゲート電極112は、素子分離絶縁膜102間の半導体基板101上に、ゲート絶縁膜111を介して形成されている。ゲート絶縁膜111は、例えばシリコン酸化膜である。また、ゲート電極112は、例えばポリシリコン層である。符号Saは、ゲート電極112におけるソース領域121側の第1側面を示し、符号Sbは、ゲート電極112におけるドレイン領域122側の第2側面を示す。

【0013】

第1の側壁絶縁膜113は、ゲート電極112の第1、第2側面Sa、Sbに形成されている。第1の側壁絶縁膜113は、例えばシリコン酸化膜である。また、第2の側壁絶縁膜114は、ゲート電極112の第1、第2側面Sa、Sbに、第1の側壁絶縁膜113を介して形成されている。第2の側壁絶縁膜114は、例えばシリコン酸化膜である。

【0014】

ソース領域121とドレイン領域122は、半導体基板101内に、ゲート電極112を挟むように形成されている。本実施形態では、ソース領域121はP型領域であり、ドレイン領域122はN型領域である。P導電型は、第1導電型の例であり、N導電型は、第1導電型とは逆導電型の第2導電型の例である。

【0015】

ソースエクステンション領域123は、ソース領域121とドレイン領域122との間において、ソース領域121に隣接して形成されている。本実施形態では、ソースエクステンション領域123は、P型領域である。なお、本実施形態では、ドレイン領域122でのトンネルオフリーク電流を低減するため、ドレインエクステンション領域は形成していない。

【0016】

シリサイド層124は、ゲート電極122、ソース領域121、ドレイン領域122内の上部に形成されている。シリサイド層124の例としては、NiSi(ニッケルシリサイド)層や、CoSi(コバルトシリサイド)層などが挙げられる。

【0017】

層間絶縁膜131は、半導体基板101上に、トンネルトランジスタを覆うように形成されている。層間絶膜膜131は、例えばシリコン酸化膜である。

【0018】

なお、図1のトンネルトランジスタは、N型トランジスタであるが、P型トランジスタとしてもよい。この場合、ソース領域111とソースエクステンション領域113は、N型領域となり、ドレイン領域112は、P型領域となる。

【0019】

(1)ゲート電極112の構造

次に、引き続き図1を参照し、ゲート電極112の構造について説明する。

【0020】

本実施形態のゲート電極112は、ゲート電極112内のソース領域121側に形成された第1領域Raと、ゲート電極112内のドレイン領域122側に形成された第2領域Rbとを有している。

【0021】

第1領域Raは、P型不純物を含有するP型領域である。第1領域Raは、本実施形態では概ねP型不純物のみを含有しているが、P型不純物の濃度がN型不純物の濃度よりも高ければ、P型不純物とN型不純物の両方を含有していてもよい。

【0022】

第2領域Rbは、P型不純物とN型不純物の両方を含有する領域である。第2領域Rbは、P型領域でもN型領域でもよい。ただし、第2領域Rbでは、P型不純物の濃度CPからN型不純物の濃度CNを引いた値ΔC(=CP−CN)を、第1領域Raに比べて低く設定する。よって、第1、第2領域Ra、Rbの値ΔCをそれぞれΔCa、ΔCbで表す場合、ΔCa>ΔCbの関係が成り立つ。

【0023】

よって、第1、第2領域Ra、Rbが共にP型領域の場合(即ちΔCa、ΔCb>0の場合)、第1領域RaはP+型領域となり、第2領域RbはP−型領域となる。

【0024】

また、第1、第2領域Ra、RbがそれぞれP型、N型領域の場合(即ちΔCa>0、ΔCb<0の場合)、ΔCbの絶対値は、ΔCaの絶対値より小さくても大きくてもよいし、ΔCaの絶対値と等しくてもよい。

【0025】

本実施形態では、ゲート電極112内に上記のような第1、第2領域Ra、Rbを形成することで、第1領域Raと第2領域Rbとの境界付近に空乏層が形成される。よって、本実施形態によれば、ゲート電極112内のドレイン領域122側の部分からチャネルへのゲート支配力を弱めて、トンネルトランジスタの非駆動時のトンネルオフリーク電流を低減することが可能となる。

【0026】

図1に示す符号Wa、Wbはそれぞれ、第1、第2領域Ra、Rbのゲート長方向の幅を示す。本実施形態では、第2領域Rbの幅Wbを、10nm以上に設定する。理由は、第2領域Rbの幅Wbを10nm以上に設定することで、空乏層の幅を、電子やホールのトンネリングを防止可能な10nm以上とすることが可能となるからである。同様の理由から、本実施形態では、第1領域Raの幅Waも、10nm以上に設定する。

【0027】

本実施形態では、Wa>Wbとなるよう幅Wa、Wbが設定されており、具体的には、幅Waは10nmより大きい値、幅Wbは10nm程度に設定されている。幅Waを10nmよりも大きく設定する理由は、ゲート電極112内のソース領域121側に非空乏層を設けるためである。

【0028】

なお、本実施形態では、図1の半導体装置を製造する際、アニーリング等により、第1領域Raから第2領域Rbへの不純物拡散や、第2領域Rbから第1領域Raへの不純物拡散が生じる。よって、第1領域Raと第2領域Rbとの境界付近では、P型不純物やN型不純物の濃度がなだらかに変化している。

【0029】

(2)半導体装置の製造方法

次に、図2〜図5を参照し、第1実施形態の半導体装置の製造方法を説明する。図2〜図5は、第1実施形態の半導体装置の製造方法を示す断面図である。

【0030】

まず、半導体基板101を用意する(図2(a))。次に、半導体基板101内に素子分離絶縁膜102を形成する(図2(a))。

【0031】

次に、図2(b)に示すように、熱酸化法により、素子分離絶縁膜102間の半導体基板101上に、ゲート絶縁膜111用の絶縁膜を形成する。次に、図2(b)に示すように、CVD(Chemical Vapor Deposition)により、半導体基板101上の全面に、ゲート電極112用の電極材を堆積する。

【0032】

次に、例えばイオン注入法により、図2(b)の電極材中にP型不純物を導入する。この際、イオン種としては、例えばB(ボロン)を使用する。また、イオン注入の際の加速電圧、ドース量はそれぞれ、例えば2keV、5×1015cm−2に設定する。

【0033】

次に、図3(a)に示すように、リソグラフィとRIE(Reactive Ion Etching)により、電極材をゲート電極112に加工する。こうして、半導体基板101上に、ゲート絶縁膜111を介して、P導電型のゲート電極112が形成される。

【0034】

次に、図3(b)に示すように、ゲート電極112の側面に、第1の側壁絶縁膜113を形成する。第1の側壁絶縁膜113は例えば、CVDにより半導体基板101上の全面に第1の側壁絶縁膜113用の絶縁膜を堆積し、RIEによりこの絶縁膜を異方的にエッチングすることで形成される。この絶縁膜の膜厚は、例えば5nmである。

【0035】

次に、図4(a)に示すように、ドレイン領域122を形成予定の領域を、レジスト膜201で覆う。次に、レジスト膜201をマスクとして、ソースエクステンション領域123を形成するためのイオン注入を行う。その結果、その後のアニーリング等により、半導体基板101内にソースエクステンション領域123が形成される。なお、このイオン注入では、イオン種として、例えばBF2を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば0.5keV、1×1015cm−2に設定する。

【0036】

なお、本実施形態では、ゲート電極112とソースエクステンション領域123に、同じ導電型の不純物(P型不純物)が導入される。よって、レジスト膜201は、ドレイン領域122を形成予定の領域さえ覆っていれば、ゲート電極112は覆っていても覆っていなくてもよい。図4(a)に示す例では、レジスト膜201は、ゲート電極112の一部のみを覆っている。レジスト膜201は、図4(a)のイオン注入後に除去する。

【0037】

次に、図4(b)に示すように、ゲート電極112の側面に、第1の側壁絶縁膜113を介して、第2の側壁絶縁膜114を形成する。第2の側壁絶縁膜114は例えば、CVDにより半導体基板101上の全面に第2の側壁絶縁膜114用の絶縁膜を堆積し、RIEによりこの絶縁膜を異方的にエッチングすることで形成される。この絶縁膜の膜厚は、例えば30nmである。

【0038】

次に、図5(a)に示すように、ドレイン領域122を形成予定の領域を、レジスト膜202で覆う。次に、レジスト膜202をマスクとして、ソース領域121を形成するためのイオン注入を行う。その結果、その後のアニーリング等により、半導体基板101内にソース領域121が形成される。なお、このイオン注入では、イオン種として、例えばBF2を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば15keV、3×1015cm−2に設定する。

【0039】

なお、本実施形態では、ゲート電極112とソース領域121に、同じ導電型の不純物が導入される。よって、レジスト膜202は、ドレイン領域122を形成予定の領域さえ覆っていれば、ゲート電極112は覆っていても覆っていなくてもよい。図5(a)に示す例では、レジスト膜202は、ゲート電極112の全体を覆っている。レジスト膜202は、図5(a)のイオン注入後に除去する。

【0040】

次に、図5(b)に示すように、ソース領域121に相当する領域を、レジスト膜203で覆う。次に、レジスト膜203をマスクとして、ドレイン領域122を形成するためのイオン注入を行う。その結果、その後のアニーリング等により、半導体基板101内にドレイン領域122が形成される。なお、このイオン注入では、イオン種として、例えばAs(ヒ素)を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば2.5keV、3×1015cm−2に設定する。

【0041】

なお、本実施形態では、レジスト膜203を、第1、第2領域Ra、Rbのうちの第1領域Raのみを覆うように形成する。その結果、N型不純物が、これらの領域Ra、Rbのうちの第2領域Rb内のみに注入される。よって、第1領域Raは、P型領域となり、第2領域Rbは、P型不純物およびN型不純物を含有する領域となる。本実施形態では、図5(b)に示す幅Wbを、例えば10nm程度に設定する。レジスト膜203は、図5(b)のイオン注入後に除去する。

【0042】

その後、本実施形態では、不純物を活性化するためのアニール工程において、例えば1025℃のスパイクアニールを実行する。また、サリサイド工程により、図1のシリサイド層124を自己整合的に形成する。さらには、半導体基板101上に、層間絶縁膜、コンタクトプラグ、ビアプラグ、配線層などを形成する。こうして、図1の半導体装置が製造される。

【0043】

なお、本実施形態では、第2領域Rb内へのN型不純物の導入を、ドレイン領域122内へのN型不純物の導入と同時に行っているが、ドレイン領域122内へのN型不純物の導入と別個に行ってもよい。前者には、工程数が少なくて済むという利点がある。一方、後者には、第2領域Rb内の不純物濃度を、ドレイン領域122内の不純物濃度と独立に設定できるという利点がある。後者の場合には、第2領域Rb用のイオン種として、例えばP(リン)を使用する。また、この際の加速電圧、ドース量はそれぞれ、例えば5keV、5×1015cm−2に設定する。

【0044】

(3)半導体装置の製造方法の変形例

次に、図6を参照し、第1実施形態の変形例の半導体装置の製造方法を説明する。図6は、第1実施形態の変形例の半導体装置の製造方法を示す断面図である。

【0045】

上述の第2領域Rbは、P型領域やN型領域とする代わりに、i型(イントリンシック型)領域としてもよい。これにより、図1の構造と同様に、ゲート電極112内のドレイン領域122側の部分からチャネルへのゲート支配力を弱めて、トンネルトランジスタの非駆動時のトンネルオフリーク電流を低減することが可能となる。

【0046】

i型の第2領域Rbを有する半導体装置は、例えば、図2(a)〜図5(b)の工程により製造可能である。ただし、図2(b)の工程において、電極材中へのP型不純物の導入は不要である。よって、図3(a)のゲート電極112は、i型電極となる。また、図5(b)の工程の代わりに、図6(a)と図6(b)の工程を実行する。以下、図6(a)と図6(b)の工程について説明する。

【0047】

まず、図6(a)に示すように、ソース領域121に相当する領域と、ゲート電極112の全体を、レジスト膜204で覆う。次に、レジスト膜204をマスクとして、ドレイン領域122を形成するためのイオン注入を行う。このイオン注入では、イオン種として、例えばAs(ヒ素)を使用する。その結果、その後のアニーリング等により、半導体基板101内にN型のドレイン領域122が形成される。

【0048】

次に、図6(b)に示すように、ソース領域121およびドレイン領域122に相当する領域と、ゲート電極112の一部を、レジスト膜205で覆う。具体的には、第1、第2領域Ra、Rbのうちの第2領域Rbのみを、レジスト膜205で覆う。次に、レジスト膜205をマスクとして、第1領域Ra内へのイオン注入を行う。このイオン注入では、イオン種として、例えばB(ボロン)を使用する。その結果、P型不純物が、これらの領域Ra、Rbのうちの第1領域Ra内のみに注入される。よって、その後のアニーリング等により、第1領域RaはP型領域となるが、第2領域Rbはi型領域のままとなる。

【0049】

なお、本実施形態では、第1領域Ra内へのP型不純物の導入を、ソース領域121内へのP型不純物の導入と別個に行っている。理由は、これらのP型不純物の導入を同時に行うと、ソース領域121が、ゲート電極112下の領域の内側に入りすぎるおそれがあるからである。ただし、この問題を回避可能であれば、第1領域Ra内へのP型不純物の導入を、ソース領域121内へのP型不純物の導入と同時に行ってもよい。

【0050】

(4)第1実施形態の効果

最後に、第1実施形態の効果について説明する。

【0051】

以上のように、本実施形態のゲート電極112は、ゲート電極112内のソース領域121側に形成された第1導電型の第1領域Raと、ゲート電極112内のドレイン領域122側に形成され、第1領域Raに比べて、第1導電型の不純物濃度から第2導電型の不純物濃度を引いた値が低い第2領域Rbとを有している。

【0052】

よって、本実施形態によれば、ゲート電極112内のドレイン領域122側の部分からチャネルへのゲート支配力が、ドレイン領域122側に近付くにつれて徐々に弱まる構造を実現することができる。その結果、トンネルトランジスタのトンネルオフリーク電流を低減することが可能となる。

【0053】

(第2実施形態)

図7は、第2実施形態の半導体装置の構造を示す断面図である。

【0054】

図7では、半導体基板101が、SOI(Semiconductor On Insulator)基板301に置き換えられている。SOI基板301は、半導体基板311と、半導体基板311上の埋め込み絶縁膜312と、埋め込み絶縁膜312上の半導体層313とを含んでいる。半導体基板311、埋め込み絶縁膜312、半導体層313はそれぞれ、例えばシリコン基板、シリコン酸化膜、シリコン層である。

【0055】

図7では、素子分離絶縁膜102が、埋め込み絶縁膜312を貫通しており、素子分離絶縁膜102の底面が、半導体基板301の上面よりも低い位置にある。よって、本実施形態では、トンネルトランジスタ同士が、素子分離絶縁膜102と埋め込み絶縁膜312により電気的に分離されている。ソース領域121、ドレイン領域122、ソースエクステンション領域123は、半導体層313内に形成されている。

【0056】

本実施形態によれば、トンネルトランジスタ同士が、素子分離絶縁膜102と埋め込み絶縁膜312により電気的に分離されるため、第1実施形態に比べて、パンチスルーを効果的に抑制することが可能となる。

【0057】

以上、第1及び第2実施形態について説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することを意図したものではない。これらの実施形態は、その他の様々な形態で実施することができる。また、これらの実施形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことにより、様々な変形例を得ることもできる。これらの形態や変形例は、発明の範囲や要旨に含まれており、特許請求の範囲及びこれに均等な範囲には、これらの形態や変形例が含まれる。

【符号の説明】

【0058】

101:半導体基板、102:素子分離絶縁膜、

111:ゲート絶縁膜、112:ゲート電極、

113:第1の側壁絶縁膜、114:第2の側壁絶縁膜、

121:ソース領域、122:ドレイン領域、

123:ソースエクステンション領域、124:シリサイド層、

131:層間絶縁膜、201〜205:レジスト膜、301:SOI基板、

311:半導体基板、312:埋め込み絶縁膜、313:半導体層

【特許請求の範囲】

【請求項1】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域と、

前記ソース領域と前記ドレイン領域との間において、前記ソース領域に隣接して形成された前記第1導電型のソースエクステンション領域とを備え、

前記ゲート電極は、

前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、

前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有し、

前記第2領域は、前記第1導電型の不純物と第2導電型の不純物の両方を含有する、またはイントリンシック型であり、

前記第1領域の幅は、前記第2領域の幅よりも長い、

半導体装置。

【請求項2】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域とを備え、

前記ゲート電極は、

前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、

前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域と、

を有する半導体装置。

【請求項3】

前記第2領域は、前記第1導電型の不純物と第2導電型の不純物の両方を含有する、またはイントリンシック型である、請求項2に記載の半導体装置。

【請求項4】

前記第1領域の幅は、前記第2領域の幅よりも長い、請求項2または3に記載の半導体装置。

【請求項5】

さらに、前記ソース領域と前記ドレイン領域との間において、前記ソース領域に隣接して形成された前記第1導電型のソースエクステンション領域を備える、請求項2から4のいずれか1項に記載の半導体装置。

【請求項6】

基板上に、ゲート絶縁膜を介して、第1導電型のゲート電極を形成し、

前記基板内に、前記ゲート電極を挟むように前記第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を形成し、

前記ゲート電極内の前記ソース領域側に位置する第1領域と、前記ゲート電極内の前記ドレイン領域側に位置する第2領域のうち、前記第2領域内のみに前記第2導電型の不純物を導入する、

半導体装置の製造方法。

【請求項7】

前記第2領域内への前記第2導電型の不純物の導入は、前記ドレイン領域内への前記第2導電型の不純物の導入と同時に行われる、請求項6に記載の半導体装置の製造方法。

【請求項8】

基板上に、ゲート絶縁膜を介して、イントリンシック型のゲート電極を形成し、

前記基板内に、前記ゲート電極を挟むように第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を形成し、

前記ゲート電極内の前記ソース領域側に位置する第1領域と、前記ゲート電極内の前記ドレイン領域側に位置する第2領域のうち、前記第1領域内のみに前記第1導電型の不純物を導入する、

半導体装置の製造方法。

【請求項9】

前記第1領域内への前記第1導電型の不純物の導入は、前記ソース領域内への前記第1導電型の不純物の導入とは別個に行われる、請求項8に記載の半導体装置の製造方法。

【請求項1】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域と、

前記ソース領域と前記ドレイン領域との間において、前記ソース領域に隣接して形成された前記第1導電型のソースエクステンション領域とを備え、

前記ゲート電極は、

前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、

前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有し、

前記第2領域は、前記第1導電型の不純物と第2導電型の不純物の両方を含有する、またはイントリンシック型であり、

前記第1領域の幅は、前記第2領域の幅よりも長い、

半導体装置。

【請求項2】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域とを備え、

前記ゲート電極は、

前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、

前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域と、

を有する半導体装置。

【請求項3】

前記第2領域は、前記第1導電型の不純物と第2導電型の不純物の両方を含有する、またはイントリンシック型である、請求項2に記載の半導体装置。

【請求項4】

前記第1領域の幅は、前記第2領域の幅よりも長い、請求項2または3に記載の半導体装置。

【請求項5】

さらに、前記ソース領域と前記ドレイン領域との間において、前記ソース領域に隣接して形成された前記第1導電型のソースエクステンション領域を備える、請求項2から4のいずれか1項に記載の半導体装置。

【請求項6】

基板上に、ゲート絶縁膜を介して、第1導電型のゲート電極を形成し、

前記基板内に、前記ゲート電極を挟むように前記第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を形成し、

前記ゲート電極内の前記ソース領域側に位置する第1領域と、前記ゲート電極内の前記ドレイン領域側に位置する第2領域のうち、前記第2領域内のみに前記第2導電型の不純物を導入する、

半導体装置の製造方法。

【請求項7】

前記第2領域内への前記第2導電型の不純物の導入は、前記ドレイン領域内への前記第2導電型の不純物の導入と同時に行われる、請求項6に記載の半導体装置の製造方法。

【請求項8】

基板上に、ゲート絶縁膜を介して、イントリンシック型のゲート電極を形成し、

前記基板内に、前記ゲート電極を挟むように第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を形成し、

前記ゲート電極内の前記ソース領域側に位置する第1領域と、前記ゲート電極内の前記ドレイン領域側に位置する第2領域のうち、前記第1領域内のみに前記第1導電型の不純物を導入する、

半導体装置の製造方法。

【請求項9】

前記第1領域内への前記第1導電型の不純物の導入は、前記ソース領域内への前記第1導電型の不純物の導入とは別個に行われる、請求項8に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−105838(P2013−105838A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−247644(P2011−247644)

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]