半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

窒化ガリウム(GaN)などの窒化物半導体を用いた高電子移動度トランジスタ(HEMT)などのFET(Field Effect Transistor)は、高周波かつ高出力で動作するパワー素子として用いられている。また、近年、窒化物半導体を用いたエンハンスメントモードFETとデプリーションモードFETとを集積化させた半導体装置が提案されている(例えば、非特許文献1)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Electron Device Meeting(IEDM)、2010 IEEE International 2010年12月6−8日、pp30.4.1−30.4.4

【発明の概要】

【発明が解決しようとする課題】

【0004】

窒化物半導体を用いたHEMTでは、高濃度の2次元電子ガスが生成されて抵抗の増大が抑制されるように、ゲート電極を電子供給層に埋め込んだ構造とすることが望ましい。このような、埋め込み型のゲート電極を形成する方法として、電子供給層をエッチングし、そのエッチングした領域に、ゲート電極を埋め込んで形成する方法がある。

【0005】

また、窒化物半導体を用いたHEMTでは、ピエゾ電荷の影響でデプリーションモードとなる。エンハンスメントモードとするには、電子供給層を薄くすることになる。このため、同じ基板上に電子供給層の厚さの異なるエンハンスメントモードFETとデプリーションモードFETとを集積化することは難しい。例えば、非特許文献1では、エンハンスメントモードFETのゲート電極を、電子供給層をエッチングした領域に埋め込んで形成している。

【0006】

電子供給層をエッチングした領域にゲート電極を埋め込んで形成する場合、エッチングの深さを精度良く制御することが難しく、ゲート電極下の電子供給層の膜厚がばらついてしまう。この結果、閾値電圧がばらついてしまい、閾値電圧を精度良く制御することが難しい。

【0007】

本発明は、上記課題に鑑みなされたものであり、埋め込み型のゲート電極を有する場合において、閾値電圧を精度良く制御することが可能な半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明は、基板上に、窒化物半導体からなるチャネル層と、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、を順次形成する工程と、前記第1窒化物半導体層上であって、ゲート電極を形成すべき領域にダミーゲートを形成する工程と、前記ダミーゲートを形成した後、前記第1窒化物半導体層上の前記ダミーゲート以外の領域に、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層を再成長する工程と、前記ダミーゲートを除去した後、前記ダミーゲートを除去した領域の前記第1窒化物半導体層上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法である。本発明によれば、閾値電圧を精度良く制御することが可能となる。

【0009】

上記構成において、前記ダミーゲートは、前記ゲート電極の幅よりも広い幅となるように形成し、前記ゲート電極は、前記第2窒化物半導体層と接しないように形成する構成とすることができる。この構成によれば、寄生容量の増大を抑制することができる。

【0010】

上記構成において、前記ダミーゲートは、エンハンスメントモードFETのゲート電極を形成すべき領域に形成し、前記ダミーゲートを除去した領域の前記第1窒化物半導体層上に前記エンハンスメントモードFETのゲート電極を形成し、前記第2窒化物半導体層上にデプリーションモードFETのゲート電極を形成する工程を有する構成とすることができる。この構成によれば、エンハンスメントモードFETとデプリーションモードFETとを容易に集積化することができる。

【0011】

上記構成において、前記エンハンスメントモードFETのゲート電極と前記デプリーションモードFETのゲート電極とは、同じ工程で同時に形成される構成とすることができる。

【0012】

上記構成において、前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせに係る前記第1窒化物半導体層と前記第2窒化物半導体層とを形成する構成とすることができる。

【0013】

上記構成において、前記ダミーゲートを、ウエットエッチング法により、前記第1窒化物半導体層および前記第2窒化物半導体層に対して選択的に除去する構成とすることができる。

【0014】

上記構成において、前記ダミーゲートは、酸化シリコンまたは窒化シリコンからなる構成とすることができる。

【0015】

上記構成において、前記第2窒化物半導体層上に保護層を形成する工程と、前記ゲート電極を形成する前に、前記ゲート電極を形成すべき領域の前記保護層をドライエッチング法により除去する工程と、を有し、前記保護層は、前記第1窒化物半導体層及び前記第2窒化物半導体層に対して選択的に除去される構成とすることができる。

【0016】

上記構成において、前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有する構成とすることができる。

【0017】

上記構成において、前記ゲート電極を形成する工程は、エンハンスメントモードFETのゲート電極を形成する工程あるいはデプリーションモードFETのゲート電極を形成する工程である構成とすることができる。

【0018】

上記構成において、前記第2窒化物半導体層を再成長する工程は、MOCVD法により行われる構成とすることができる。

【0019】

本発明は、基板と、前記基板上に設けられた窒化物半導体からなるチャネル層と、前記チャネル層上に設けられ、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、前記第1窒化物半導体層上に互いに離間して選択的に設けられた、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層と、前記第2窒化物半導体層が離間した領域における前記第1窒化物半導体層上に設けられたゲート電極と、を備え、前記ゲート電極はデプリーションモードFETのゲート電極であることを特徴とする半導体装置である。本発明によれば、閾値電圧を精度良く制御することが可能となる。

【0020】

上記構成において、前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有する構成とすることができる。

【0021】

上記構成において、前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせからなる構成とすることができる。

【発明の効果】

【0022】

本発明によれば、閾値電圧を精度良く制御することが可能となる。

【図面の簡単な説明】

【0023】

【図1】図1は、実施例1に係る半導体装置の断面模式図の例である。

【図2】図2(a)から図2(c)は、実施例1に係る半導体装置の製造方法を示す断面模式図(その1)の例である。

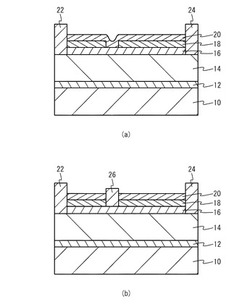

【図3】図3(a)及び図3(b)は、実施例1に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

【図4】図4は、実施例2に係る半導体装置の断面模式図の例である。

【図5】図5(a)から図5(c)は、実施例2に係る半導体装置の製造方法を示す断面模式図(その1)の例である。

【図6】図6(a)及び図6(b)は、実施例2に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

【図7】図7は、実施例3に係る半導体装置の断面模式図の例である。

【図8】図8(a)から図8(c)は、実施例3に係る半導体装置の製造方法を示す断面模式図(その1)の例である。

【図9】図9(a)及び図9(b)は、実施例3に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

【図10】図10は、実施例3に係る半導体装置を用いたインバータ回路の回路図である。

【図11】図11は、実施例4に係るスイッチ回路を示す回路図の例である。

【発明を実施するための形態】

【0024】

以下、図面を参照して、本発明の実施例を説明する。

【実施例1】

【0025】

実施例1では、デプリーションモードFET(以下において、DモードFETと称す)の半導体装置の例について説明する。図1は、実施例1に係る半導体装置の断面模式図の例である。図1を参照に、SiC基板からなる基板10上に、バッファ層12、チャネル層14、第1窒化物半導体層16、第2窒化物半導体層18及び保護層20が順次設けられている。バッファ層12は、例えば膜厚が300nmのAlNからなる。チャネル層14は、例えば膜厚が1000nmのGaNからなる。第1窒化物半導体層16は、例えば膜厚が25nmで、Al組成比が25%のAlGaNからなる。第2窒化物半導体層18は、例えば膜厚が25nmで、Al組成比が25%のAlGaNからなる。保護層20は、例えば窒化シリコンからなる。

【0026】

第1窒化物半導体層16、第2窒化物半導体層18及び保護層20にリセスが形成され、リセスに埋め込まれてソース電極22及びドレイン電極24が設けられている。ソース電極22及びドレイン電極24は、例えばチャネル層14の上面に接して設けられている。ソース電極22及びドレイン電極24は、基板10側からTa層とAl層とが順次積層されている。また、ソース電極22とドレイン電極24との間であって、第2窒化物半導体層18及び保護層20にリセスが形成され、リセスに埋め込まれてゲート電極26が設けられている。ゲート電極26は、例えば第1窒化物半導体層16の上面に接して設けられている。ゲート電極26は、基板10側からNi層とAu層とが順次積層されている。

【0027】

第1窒化物半導体層16及び第2窒化物半導体層18は電子供給層として機能し、チャネル層14の第1窒化物半導体層16との界面に2次元電子ガス28が生成される。ソース電極22から2次元電子ガス28を通りドレイン電極24に至る電子の流れをゲート電極26により制御することで、FETとして機能する。この場合に、Dモードの閾値電圧が得られるように、ゲート電極26下の第1窒化物半導体層16の厚さを、例えば25nmのように厚くすることで、DモードFETとすることができる。

【0028】

次に、実施例1に係る半導体装置の製造方法を説明する。図2(a)から図3(b)は、実施例1に係る半導体装置の製造方法を示す断面模式図の例である。図2(a)を参照に、SiC基板からなる基板10上に、例えばMOCVD(Metal Organic Chemical Vapor Deposition)法を用いて、AlNからなるバッファ層12を成長させる。バッファ層12の成長条件は以下である。なお、結晶成長では、特に注釈をしない限り、キャリアガスとしては水素を用いる。

原料ガス:TMA(トリメチルアルミニウム)、NH3(アンモニア)

成長温度:1000℃

膜厚 :300nm

【0029】

バッファ層12上に、例えばMOCVD法を用いて、GaNからなるチャネル層14を成長させる。チャネル層14の成長条件は以下である。

原料ガス:TMG(トリメチルガリウム)、NH3

成長温度:1000℃

膜厚 :1000nm

【0030】

チャネル層14上に、例えばMOCVD法を用いて、AlGaNからなる第1窒化物半導体層16を成長させる。第1窒化物半導体層16は、例えばチャネル層14の上面に接して形成される。第1窒化物半導体層16の成長条件は以下である。

原料ガス :TMA、TMG、NH3

成長温度 :1000℃

Al組成比:25%

膜厚 :25nm

第1窒化物半導体層16はAl組成比25%のAlGaNからなるため、GaNからなるチャネル層14よりもバンドギャップエネルギー(以下、Egと称す)が大きい。

【0031】

図2(b)を参照に、第1窒化物半導体層16上に、例えばスパッタ法を用いて酸化シリコンを成膜する。その後、ゲート電極26を形成すべき領域以外の領域の酸化シリコンを除去して、ゲート電極26を形成すべき領域に、酸化シリコンからなるダミーゲート30を形成する。

【0032】

ダミーゲート30を形成した後、例えばMOCVD法を用いて、AlGaNからなる第2窒化物半導体層18を再成長させる。これにより、第1窒化物半導体層16上のダミーゲート30以外の領域に選択的に第2窒化物半導体層18が形成される。第2窒化物半導体層18は、例えば第1窒化物半導体層16の上面に接して形成される。第2窒化物半導体層18の成長条件は以下である。

原料ガス :TMA、TMG、NH3

成長温度 :1000℃

Al組成比:25%

膜厚 :25nm

第2窒化物半導体層18はAl組成比25%のAlGaNからなるため、GaNからなるチャネル層14よりもEgが大きい。

【0033】

図2(c)を参照に、ダミーゲート30を、例えばフッ酸を用いたウエットエッチングによって、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去する。その後、第2窒化物半導体層18上に、例えばスパッタ法を用いて、窒化シリコンからなる保護層20を成膜する。ダミーゲート30を除去した領域にも保護層20は形成される。

【0034】

図3(a)を参照に、保護層20上に、例えば酸化シリコンからなるマスク層を形成し、パターニングをする。マスク層のパターニングは、ソース電極22及びドレイン電極24が形成されるべき領域の保護層20の上面が露出されるように行う。マスク層をマスクとして、例えばドライエッチング法を用いて、保護層20、第2窒化物半導体層18及び第1窒化物半導体層16をエッチングして、チャネル層14の上面が露出したリセスを形成する。保護層20をエッチングする際のエッチングガスとして例えばCF4、CHF3、C2F6、SF6などのフッ素系ガスを用いる。第2窒化物半導体層18及び第1窒化物半導体層16をエッチングする際のエッチングガスとして例えばCl2、BCl3、SiCl4などの塩素系ガスを用いる。その後、例えば蒸着法及びリフトオフ法を用いて、リセス内にTa層とAl層とが順次積層されたソース電極22とドレイン電極24とを形成する。

【0035】

図3(b)を参照に、保護層20上に、例えば酸化シリコンからなるマスク層を再び形成し、パターニングをする。マスク層のパターニングは、ゲート電極26が形成されるべき領域の保護層20の上面が露出されるように行う。マスク層をマスクとして、例えばフッ素系ガスを用いたドライエッチング法により、保護層20をエッチングして、第1窒化物半導体層16の上面が露出したリセスを形成する。その後、例えば蒸着法及びリフトオフ法を用いて、リセス内にNi層とAu層とが順次積層された、ゲート電極26を形成する。

【0036】

以上説明してきたように、実施例1によれば、基板10上にチャネル層14と第1窒化物半導体層16とを順次形成した後、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上のダミーゲート30以外の領域に第2窒化物半導体層18を再成長させる。そして、ダミーゲート30を除去した後、ダミーゲート30を除去した領域の第1窒化物半導体層16上にゲート電極26を形成する。このような製造方法を用いて製造することで、図1に示す半導体装置が得られる。この半導体装置は、基板10上にチャネル層14と第1窒化物半導体層16とが順次設けられ、第1窒化物半導体層16上に、互いに離間して選択的に第2窒化物半導体層18が設けられている。そして、第2窒化物半導体層18の離間した領域における第1窒化物半導体層16上に、デプリーションモードFETのゲート電極26が設けられている。このように、ゲート電極26は、第2窒化物半導体層18の電子供給層に埋め込まれた構造となる。したがって、電子供給層をエッチングすることなく、埋め込み型のゲート電極26を得ることができる。

【0037】

例えば、埋め込み型のゲート電極26を、電子供給層をエッチングして形成する場合、以下の製造方法を用いることが考えられる。まず、第1窒化物半導体層16と第2窒化物半導体層18とを順次形成する。その後、第2窒化物半導体層18をエッチングし、そのエッチングした領域にゲート電極26を埋め込んで形成する。この場合、第2窒化物半導体層18は、通常、塩素系ガスを用いたドライエッチング法でエッチングするため、第1窒化物半導体層16との選択比が大きく取れずに、第1窒化物半導体層16までエッチングされてしまう。この結果、ゲート電極26直下の第1窒化物半導体層16の厚さがばらついてしまい、閾値電圧を安定してコントロールすることが難しい。一方、実施例1では、エッチングを用いずに再成長法を用いて埋め込み型のゲート電極26を形成している。このため、ゲート電極26直下の第1窒化物半導体層16の厚さの制御を精度良くできるようになり、閾値電圧を精度良く制御することが可能となる。

【0038】

また、ゲート電極26を第2窒化物半導体層18に埋め込まれた構造とすることで、ゲート電極26直下以外の領域の電子供給層を厚くすることができるため、高濃度の2次元電子ガス28を得ることができる。これにより、抵抗を低減させることができる。さらに、ゲート電極26直下以外の領域の2次元電子ガス28を電子供給層の表面から遠ざけることができる。これにより、電子供給層の表面におけるトラップが2次元電子ガス28に与える影響を小さくでき、電流コラプスを低減させることができる。

【0039】

図2(c)で説明したように、ダミーゲート30を、ウエットエッチング法を用いて、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去する場合が好ましい。なお、選択的に除去するとは、ダミーゲート30と第1窒化物半導体層16及び第2窒化物半導体層18とは、エッチングの選択比が取れることをいう。これにより、ダミーゲート30を除去する際に、第1窒化物半導体層16や第2窒化物半導体層18がエッチングされることを抑制できる。よって、ゲート電極26直下の第1窒化物半導体層16の厚さを精度良く制御することができる。このように、ウエットエッチング法により、第1窒化物半導体層16及び第2窒化物半導体層18に対してダミーゲート30を選択的に除去するために、ダミーゲート30は、酸化シリコンまたは窒化シリコンからなる場合が好ましい。

【0040】

図2(c)で説明したように、第2窒化物半導体層18上に保護層20を形成する。第2窒化物半導体層18がAlGaNのようにAlを含んでいる場合、第2窒化物半導体層18が最表面になると、酸化が進み易く、部分的かつ経時的に酸化アルミニウムが形成されてしまう。これによりデバイス不良が発生してしまう。したがって、第2窒化物半導体層18上に保護層20を形成することで、デバイス不良の発生を抑制することができる。

【0041】

第2窒化物半導体層18上に保護層20を形成した場合、図3(b)で説明したように、ゲート電極26を形成する前に、ゲート電極26を形成すべき領域の保護層20を除去する。この際、ゲート電極の幅などを精度よく制御する点から、ドライエッチング法により保護層20を除去する。ここで、保護層20は窒化シリコンからなるため、フッ素系ガスを用いたドライエッチング法により除去する。AlGaNのドライエッチングでは塩素系ガスが用いられるため、フッ素系ガスを用いて保護層20をエッチングする場合、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択比を大きく取る事ができる。つまり、第1窒化物半導体層16及び第2窒化物半導体層18に対して保護層20を選択的にエッチングすることができ、第1窒化物半導体層16及び第2窒化物半導体層18はほとんどエッチングされない。このため、閾値電圧に与える影響は小さくて済む。

【実施例2】

【0042】

実施例2は、ワイドリセスにゲート電極を埋め込んだ場合の半導体装置の例である。図4は、実施例2に係る半導体装置の断面模式図の例である。図4を参照に、実施例1と異なる点は、ゲート電極26がワイドリセスに埋め込まれていて、ゲート電極26の側面が第2窒化物半導体層18と接していない点である。その他の構成については、実施例1と同じであるため、ここでは説明を省略する。

【0043】

次に、実施例2に係る半導体装置の製造方法を説明する。図5(a)から図6(b)は、実施例2に係る半導体装置の製造方法を示す断面模式図の例である。図5(a)を参照に、基板10上に、例えばMOCVD法を用いて、バッファ層12、チャネル層14、第1窒化物半導体層16を順次成長させる。各層の成長条件は、実施例1に示した成長条件を用いる。

【0044】

図5(b)を参照に、第1窒化物半導体層16上に、例えばスパッタ法を用いて酸化シリコンを成膜する。その後、ゲート電極26を形成すべき領域よりも広い幅の領域の酸化シリコンを残存させ、その他の領域の酸化シリコンを除去することで、酸化シリコンからなるダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上に、例えばMOCVD法を用いて、第2窒化物半導体層18を再成長させる。第2窒化物半導体層18の成長条件は、実施例1に示した成長条件を用いる。

【0045】

図5(c)を参照に、ダミーゲート30をウエットエッチングによって第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去した後、第2窒化物半導体層18上に保護層20を形成する。

【0046】

図6(a)を参照に、ソース電極22及びドレイン電極24を形成すべき領域の保護層20、第2窒化物半導体層18及び第1窒化物半導体層16をドライエッチングしてリセスを形成する。その後、リセス内にソース電極22とドレイン電極24とを形成する。

【0047】

図6(b)を参照に、ゲート電極26を形成すべき領域よりも広い幅の領域であって、第2窒化物半導体層18が形成されていない領域の保護層20をドライエッチングしてワイドリセスを形成する。その後、ワイドリセス内であって、第2窒化物半導体層18の側面に接しないように、ゲート電極26を形成する。

【0048】

以上説明してきたように、実施例2によれば、第1窒化物半導体層16上であって、ゲート電極26の幅よりも広い幅となるようなダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上のダミーゲート30以外の領域に第2窒化物半導体層18を再成長させる。そして、ダミーゲート30を除去した後、ダミーゲートを除去した領域に、第2窒化物半導体層18と接しないようにゲート電極26を形成する。ゲート電極26を埋め込み型とした場合、ゲート電極26の側面が第2窒化物半導体層18に接すると、寄生容量が増大することが考えられる。そこで、実施例2のように、ゲート電極26の側面を第2窒化物半導体層18と接しないようにすることで、寄生容量が増大することを抑制できる。

【0049】

実施例1及び実施例2では、第1窒化物半導体層16はAlGaN(Al組成比:25%)からなり、第2窒化物半導体層18もAlGaN(Al組成比:25%)からなる場合を例に示したが、この場合に限られる訳ではない。第1窒化物半導体層16は、チャネル層14よりもバンドギャップエネルギーの大きい窒化物半導体層からなる場合であればよい。第2窒化物半導体層18は、チャネル層14のバンドギャップエネルギー以上の大きさのエネルギーバンドギャップを有する窒化物半導体層からなる場合であればよい。

【0050】

ここで、窒化物半導体とは、窒素を含む半導体であり、例えばGaN、InN、AlN、InGaN、AlGaN、InAlN、AlInGaNなどが挙げられる。チャネル層14がGaNからなる場合、第1窒化物半導体層16と第2窒化物半導体層18の組み合わせとしては、表1に示すように、実施例1に示したAlGaNとAlGaNの組み合わせの他に、AlGaNとGaN、InAlNとInAlNの組み合わせの場合でもよい。

【表1】

【0051】

表1に関して詳しく説明する。表1を参照に、第1窒化物半導体層16がAlGaNで、第2窒化物半導体層18がGaNである場合(ケース2、ケース4の場合)、第1窒化物半導体層16は電子供給層として機能し、第2窒化物半導体層18はキャップ層として機能する。この場合、Dモードの閾値電圧が得られるように第1窒化物半導体層16の膜厚は例えば25nmとすることができ、第2窒化物半導体層18の膜厚は例えば5nmとすることができる。また、ケース3、ケース4のように、チャネル層14と第1窒化物半導体層16との間に、スペーサ層として例えば膜厚1nmのAlNを挿入してもよい。AlNを挿入することにより、AlNとGaNとの伝導帯の大きな不連続により高濃度の2次元電子ガスが得られる。これにより、高電流化、高出力化が可能となる。

【0052】

さらに、AlNのスペーサ層を挿入し、第1窒化物半導体層16をInAlN、第2窒化物半導体層18もInAlNとする場合(ケース5)でもよい。この場合、第1窒化物半導体層16及び第2窒化物半導体層18は電子供給層として機能する(ケース1、ケース3も同じ)。AlNの膜厚は例えば1.5nmとすることができる。Dモードの閾値電圧が得られるように第1窒化物半導体層16の膜厚は例えば3.5nmとし、第2窒化物半導体層18の膜厚は例えば10nmとすることができる。ここで、電子供給層としてInAlNを用いる理由を説明する。HEMTにおいて、電力密度を高めるため、より多くの電流が流れるように、より高濃度の2次元電子ガスを発生させることが求められている。電子供給層としてAlGaNを用いた場合、Al組成比を上げてより高濃度の2次元電子ガスを発生させることが考えられるが、高Al組成のAlGaNはGaNに対して格子不整合が大きくなるため、高結晶品質を保って形成することが難しい。一方、電子供給層としてInAlNを用いた場合、InAlNはGaNと格子整合すると共に、InAlNとGaNとの大きな自発分極差と伝導帯の大きな不連続により、高濃度の2次元電子ガスが得られるためである。また、AlNをスペーサ層として挿入することで、GaNとInAlNとを物理的に離すことができ、2次元電子ガスの移動度を向上できる。

【0053】

実施例1及び実施例2では、DモードFETの場合を例に示したが、ゲート電極26下の第1窒化物半導体層16の厚さを変えることで、エンハンスメントモードFET(以下において、EモードFETと称す)を形成することもできる。つまり、ゲート電極26として、DモードFETのゲート電極あるいはEモードFETのゲート電極を形成することができる。

【実施例3】

【0054】

実施例3は、同じ基板上にEモードFETとDモードFETとを集積化させた半導体装置の場合の例である。図7は、実施例3に係る半導体装置の断面模式図の例である。図7を参照に、実施例1と異なる点は、第1窒化物半導体層16が例えば膜厚1.5nmのAlNからなり、第2窒化物半導体層18が例えば膜厚3.5nm、In組成比17%のInAlNからなる点である。また、EモードFETとDモードFETとが集積していて、それぞれのソース電極22、ドレイン電極24及びゲート電極(EモードFETのゲート電極を第1ゲート電極26a、DモードFETのゲート電極を第2ゲート電極26bと称す)が設けられている点である。EモードFETの第1ゲート電極26aは、第1窒化物半導体層16の上面に接して設けられ、DモードFETの第2ゲート電極26bは、第2窒化物半導体層18の上面に接して設けられている。その他の構成については、実施例1と同じであるため、ここでは説明を省略する。また、後述するが、表2は、実施例3に関する第1窒化物半導体層16、第2窒化物半導体層18の組み合わせを示している。

【0055】

次に、実施例3に係る半導体装置の製造方法を説明する。図8(a)から図9(b)は、実施例3に係る半導体装置の製造方法を示す断面模式図の例である。図8(a)を参照に、基板10上に、例えばMOCVD法を用いて、バッファ層12及びチャネル層14を順次成長させる。バッファ層12及びチャネル層14の成長条件は、実施例1に示した成長条件を用いる。チャネル層14上に、例えばMOCVD法を用いて、AlNからなる第1窒化物半導体層16を成長させる。第1窒化物半導体層16の成長条件は以下である。

原料ガス:TMA、NH3

成長温度:1000℃

膜厚 :1.5nm

第1窒化物半導体層16はAlNからなるため、GaNからなるチャネル層14よりもEgが大きい。AlNからなる第1窒化物半導体層16はスペーサ層として機能する。

【0056】

図8(b)を参照に、第1窒化物半導体層16上に、例えばスパッタ法を用いて酸化シリコンを成膜する。その後、EモードFETの第1ゲート電極26aを形成すべき領域に酸化シリコンを残存させ、その他の領域の酸化シリコンを除去することで、酸化シリコンからなるダミーゲート30を形成する。ダミーゲート30を形成した後、キャリアガスを水素から窒素に変え、第1窒化物半導体層16上に、例えばMOCVD法を用いて、InAlNからなる第2窒化物半導体層18を再成長させる。第2窒化物半導体層18の成長条件は以下である。

原料ガス :TMI(トリメチルインジウム)、TMA、NH3

成長温度 :800℃

In組成比:17%

膜厚 :3.5nm

第2窒化物半導体層18はIn組成比17%のInAlNからなるため、GaNからなるチャネル層14よりもEgが大きい。InAlNからなる第2窒化物半導体層18は電子供給層として機能する。

【0057】

図8(c)を参照に、ダミーゲート30をウエットエッチングによって第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去した後、第2窒化物半導体層18上に保護層20を形成する。

【0058】

図9(a)を参照に、EモードFETとDモードFETとのそれぞれのソース電極22及びドレイン電極24を形成すべき領域の保護層20、第2窒化物半導体層18及び第1窒化物半導体層16をドライエッチングしてリセスを形成する。保護層20のエッチングガスにはフッ素系ガスを用い、第1窒化物半導体層16及び第2窒化物半導体層18のエッチングガスには塩素系ガスを用いる。その後、リセス内にソース電極22とドレイン電極24とを形成する。

【0059】

図9(b)を参照に、EモードFETの第1ゲート電極26a及びDモードFETの第2ゲート電極26bを形成すべき領域の保護層20を、フッ素系ガスを用いてドライエッチングし、リセスを形成する。その後、リセス内にEモードFETの第1ゲート電極26aとDモードFETの第2ゲート電極26bとを形成する。

【0060】

以上説明してきたように、実施例3によれば、第1窒化物半導体層16上であって、EモードFETの第1ゲート電極26aを形成すべき領域にダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上のダミーゲート30以外の領域に第2窒化物半導体層18を再成長させる。そして、ダミーゲート30を除去した後、ダミーゲート30を除去した領域の第1窒化物半導体層16上にEモードFETの第1ゲート電極26aを、第2窒化物半導体層18上にDモードFETの第2ゲート電極26bを形成する。これにより、EモードFETの第1ゲート電極26aは、第1窒化物半導体層16の上面に形成される。一方、DモードFETの第2ゲート電極26bは、第2窒化物半導体層18の上面に形成される。よって、DモードFETの閾値電圧をEモードFETよりも深くすることができる。また、EモードFETの第1ゲート電極26aは、埋め込み型のゲート電極であるが、エッチング法を用いずに再成長法を用いて形成しているため、閾値電圧の安定したEモードFETが得られる。したがって、実施例3によれば、EモードFETとDモードFETとを容易に集積化することができる。

【0061】

図9(b)で説明したように、EモードFETの第1ゲート電極26aとDモードFETの第2ゲート電極26bとは、同じ工程で同時に形成される場合が好ましい。これにより、製造工数を削減することができる。

【0062】

実施例3では、第1窒化物半導体層16はAlNからなり、第2窒化物半導体層18はInAlN(In組成比:17%)からなる場合を例に示したが、この場合に限られる訳ではない。第1窒化物半導体層16は、チャネル層14よりもバンドギャップエネルギーの大きい窒化物半導体層からなる場合であればよい。第2窒化物半導体層18は、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する窒化物半導体層からなる場合であればよい。したがって、表2に示すように、第1窒化物半導体層16がAlGaNで、第2窒化物半導体層18もAlGaNである場合(ケース2)でもよい。この場合、第1窒化物半導体層16及び第2窒化物半導体層18は、電子供給層として機能する。第1窒化物半導体層16は、例えば膜厚8nm、Al組成比25%とし、第2窒化物半導体層18は、例えば膜厚17nm、Al組成比25%とすることができる。

【0063】

また、第1窒化物半導体層16がAlGaNで、第2窒化物半導体層18がGaNである場合(ケース3)でもよい。この場合、第1窒化物半導体層16は電子供給層として機能し、第2窒化物半導体層18はキャップ層として機能する。第1窒化物半導体層16は、例えば膜厚8nm、Al組成比25%とし、第2窒化物半導体層18は、例えば膜厚5nmとすることができる。

【表2】

【0064】

図9(a)及び図9(b)で説明したように、保護層20をフッ素系のエッチングガスを用いてドライエッチングするため、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択比を大きく取る事ができる。このため、第1窒化物半導体層16と第2窒化物半導体層18とは、ほとんどエッチングされない。したがって、EモードFETの第1ゲート電極26a直下の第1窒化物半導体層16の厚さ、並びにDモードFETの第2ゲート電極26b直下の第1窒化物半導体層16及び第2窒化物半導体層18の厚さを精度良く制御することができる。

【0065】

実施例1から3では、保護層20は窒化シリコンからなる場合を例に示したが、この場合に限られる訳ではない。保護層20をドライエッチング法により除去する際に、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去することが可能であれば、保護層20はその他の材料からなる場合でも良い。

【0066】

表1及び表2で説明したように、第1窒化物半導体層16は電子供給層あるいはスペーサ層としての機能を有し、第2窒化物半導体層18は電子供給層あるいはキャップ層としての機能を有することとすることができる。より具体的には、第1窒化物半導体層16は電子供給層あるいはスペーサ層としての機能を有し、第2窒化物半導体層18は、第1窒化物半導体層16が電子供給層として機能する場合は電子供給層あるいはキャップ層としての機能を有し、第1窒化物半導体層16がスペーサ層として機能する場合は電子供給層としての機能を有することとすることができる。

【0067】

基板10はSiC基板である場合を例に示したが、この場合に限られず、例えばSi基板、GaN基板、サファイア基板、Ga2O3基板を用いてもよい。また、成長に用いる原料は、上述した原料の他に、Al原料としてTEA(トリエチルアルミニウム)、Ga原料としてTEG(トリエチルガリウム)を用いてもよい。さらに、MOCVD法を用いて結晶成長する場合を例に示したが、この場合に限られず、その他の方法により結晶成長する場合でもよい。

【0068】

ゲート電極26は、基板10側からNi層とAu層とが順次積層された構造である場合を例に説明したが、この場合に限られる訳ではない。ゲート電極26は、基板10側から例えばNi層とPd層とAu層とが順次積層された構造の場合でもよい。

【実施例4】

【0069】

実施例4は、実施例3をスイッチ回路に適用した場合の例である。図10は、実施例3に係る半導体装置を用いたインバータ回路の回路図である。図10を参照に、実施例3に係る半導体装置のEモードFET40のソースが接地され、ゲートが入力端子Inに接続され、ドレインがノードN1に接続されている。実施例3に係る半導体装置のDモードFET42のソースがノードN1に接続され、ゲートもノードN1に接続され、ドレインが電源VDDに接続されている。このように、EモードFET40とDモードFET42とを用いDCFL(Drain Coupled FET Logic)回路を形成することができる。

【0070】

図11は、実施例4に係るスイッチ回路を示す回路図の例である。図11を参照に、スイッチ回路60は、インバータ回路50、スイッチSW1及びスイッチSW2を有する。スイッチSW1は、複数の実施例3に係るDモードFET44が直列に接続されている。一端のDモードFET44のソース又はドレインは入力端子Inに接続される。他端のDモードFET44のソース又はドレインは出力端子Out1に接続される。スイッチSW2は、複数の実施例3に係るDモードFET46が直列に接続されている。一端のDモードFET46のソース又はドレインは入力端子Inに接続される。他端のDモードFET46のソース又はドレインは出力端子Out2に接続される。インバータ回路50の入力は制御端子Contに接続されている。制御端子Contは、スイッチSW1を構成するDモードFET44のゲートに抵抗R1を介し接続されてもいる。インバータ回路50の出力は、スイッチSW2を構成するDモードFET46のゲートに抵抗R2を介し接続されている。

【0071】

以上の構成により、制御端子Contにハイが入力すると、スイッチSW1はオンし、スイッチSW2はオフする。制御端子Contにローが入力すると、スイッチSW1はオフし、スイッチSW2はオンする。このように、窒化物半導体を用いたEモードFET40とDモードFET42とを有するインバータ回路50をスイッチSW1及びスイッチSW2と同じ基板に集積化することができる。

【0072】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0073】

10 基板

12 バッファ層

14 チャネル層

16 第1窒化物半導体層

18 第2窒化物半導体層

20 保護層

22 ソース電極

24 ドレイン電極

26 ゲート電極

26a 第1ゲート電極

26b 第2ゲート電極

28 2次元電子ガス

30 ダミーゲート

40 EモードFET

42 DモードFET

44 DモードFET

46 DモードFET

50 インバータ回路

60 スイッチ回路

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

窒化ガリウム(GaN)などの窒化物半導体を用いた高電子移動度トランジスタ(HEMT)などのFET(Field Effect Transistor)は、高周波かつ高出力で動作するパワー素子として用いられている。また、近年、窒化物半導体を用いたエンハンスメントモードFETとデプリーションモードFETとを集積化させた半導体装置が提案されている(例えば、非特許文献1)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Electron Device Meeting(IEDM)、2010 IEEE International 2010年12月6−8日、pp30.4.1−30.4.4

【発明の概要】

【発明が解決しようとする課題】

【0004】

窒化物半導体を用いたHEMTでは、高濃度の2次元電子ガスが生成されて抵抗の増大が抑制されるように、ゲート電極を電子供給層に埋め込んだ構造とすることが望ましい。このような、埋め込み型のゲート電極を形成する方法として、電子供給層をエッチングし、そのエッチングした領域に、ゲート電極を埋め込んで形成する方法がある。

【0005】

また、窒化物半導体を用いたHEMTでは、ピエゾ電荷の影響でデプリーションモードとなる。エンハンスメントモードとするには、電子供給層を薄くすることになる。このため、同じ基板上に電子供給層の厚さの異なるエンハンスメントモードFETとデプリーションモードFETとを集積化することは難しい。例えば、非特許文献1では、エンハンスメントモードFETのゲート電極を、電子供給層をエッチングした領域に埋め込んで形成している。

【0006】

電子供給層をエッチングした領域にゲート電極を埋め込んで形成する場合、エッチングの深さを精度良く制御することが難しく、ゲート電極下の電子供給層の膜厚がばらついてしまう。この結果、閾値電圧がばらついてしまい、閾値電圧を精度良く制御することが難しい。

【0007】

本発明は、上記課題に鑑みなされたものであり、埋め込み型のゲート電極を有する場合において、閾値電圧を精度良く制御することが可能な半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明は、基板上に、窒化物半導体からなるチャネル層と、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、を順次形成する工程と、前記第1窒化物半導体層上であって、ゲート電極を形成すべき領域にダミーゲートを形成する工程と、前記ダミーゲートを形成した後、前記第1窒化物半導体層上の前記ダミーゲート以外の領域に、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層を再成長する工程と、前記ダミーゲートを除去した後、前記ダミーゲートを除去した領域の前記第1窒化物半導体層上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法である。本発明によれば、閾値電圧を精度良く制御することが可能となる。

【0009】

上記構成において、前記ダミーゲートは、前記ゲート電極の幅よりも広い幅となるように形成し、前記ゲート電極は、前記第2窒化物半導体層と接しないように形成する構成とすることができる。この構成によれば、寄生容量の増大を抑制することができる。

【0010】

上記構成において、前記ダミーゲートは、エンハンスメントモードFETのゲート電極を形成すべき領域に形成し、前記ダミーゲートを除去した領域の前記第1窒化物半導体層上に前記エンハンスメントモードFETのゲート電極を形成し、前記第2窒化物半導体層上にデプリーションモードFETのゲート電極を形成する工程を有する構成とすることができる。この構成によれば、エンハンスメントモードFETとデプリーションモードFETとを容易に集積化することができる。

【0011】

上記構成において、前記エンハンスメントモードFETのゲート電極と前記デプリーションモードFETのゲート電極とは、同じ工程で同時に形成される構成とすることができる。

【0012】

上記構成において、前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせに係る前記第1窒化物半導体層と前記第2窒化物半導体層とを形成する構成とすることができる。

【0013】

上記構成において、前記ダミーゲートを、ウエットエッチング法により、前記第1窒化物半導体層および前記第2窒化物半導体層に対して選択的に除去する構成とすることができる。

【0014】

上記構成において、前記ダミーゲートは、酸化シリコンまたは窒化シリコンからなる構成とすることができる。

【0015】

上記構成において、前記第2窒化物半導体層上に保護層を形成する工程と、前記ゲート電極を形成する前に、前記ゲート電極を形成すべき領域の前記保護層をドライエッチング法により除去する工程と、を有し、前記保護層は、前記第1窒化物半導体層及び前記第2窒化物半導体層に対して選択的に除去される構成とすることができる。

【0016】

上記構成において、前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有する構成とすることができる。

【0017】

上記構成において、前記ゲート電極を形成する工程は、エンハンスメントモードFETのゲート電極を形成する工程あるいはデプリーションモードFETのゲート電極を形成する工程である構成とすることができる。

【0018】

上記構成において、前記第2窒化物半導体層を再成長する工程は、MOCVD法により行われる構成とすることができる。

【0019】

本発明は、基板と、前記基板上に設けられた窒化物半導体からなるチャネル層と、前記チャネル層上に設けられ、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、前記第1窒化物半導体層上に互いに離間して選択的に設けられた、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層と、前記第2窒化物半導体層が離間した領域における前記第1窒化物半導体層上に設けられたゲート電極と、を備え、前記ゲート電極はデプリーションモードFETのゲート電極であることを特徴とする半導体装置である。本発明によれば、閾値電圧を精度良く制御することが可能となる。

【0020】

上記構成において、前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有する構成とすることができる。

【0021】

上記構成において、前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせからなる構成とすることができる。

【発明の効果】

【0022】

本発明によれば、閾値電圧を精度良く制御することが可能となる。

【図面の簡単な説明】

【0023】

【図1】図1は、実施例1に係る半導体装置の断面模式図の例である。

【図2】図2(a)から図2(c)は、実施例1に係る半導体装置の製造方法を示す断面模式図(その1)の例である。

【図3】図3(a)及び図3(b)は、実施例1に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

【図4】図4は、実施例2に係る半導体装置の断面模式図の例である。

【図5】図5(a)から図5(c)は、実施例2に係る半導体装置の製造方法を示す断面模式図(その1)の例である。

【図6】図6(a)及び図6(b)は、実施例2に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

【図7】図7は、実施例3に係る半導体装置の断面模式図の例である。

【図8】図8(a)から図8(c)は、実施例3に係る半導体装置の製造方法を示す断面模式図(その1)の例である。

【図9】図9(a)及び図9(b)は、実施例3に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

【図10】図10は、実施例3に係る半導体装置を用いたインバータ回路の回路図である。

【図11】図11は、実施例4に係るスイッチ回路を示す回路図の例である。

【発明を実施するための形態】

【0024】

以下、図面を参照して、本発明の実施例を説明する。

【実施例1】

【0025】

実施例1では、デプリーションモードFET(以下において、DモードFETと称す)の半導体装置の例について説明する。図1は、実施例1に係る半導体装置の断面模式図の例である。図1を参照に、SiC基板からなる基板10上に、バッファ層12、チャネル層14、第1窒化物半導体層16、第2窒化物半導体層18及び保護層20が順次設けられている。バッファ層12は、例えば膜厚が300nmのAlNからなる。チャネル層14は、例えば膜厚が1000nmのGaNからなる。第1窒化物半導体層16は、例えば膜厚が25nmで、Al組成比が25%のAlGaNからなる。第2窒化物半導体層18は、例えば膜厚が25nmで、Al組成比が25%のAlGaNからなる。保護層20は、例えば窒化シリコンからなる。

【0026】

第1窒化物半導体層16、第2窒化物半導体層18及び保護層20にリセスが形成され、リセスに埋め込まれてソース電極22及びドレイン電極24が設けられている。ソース電極22及びドレイン電極24は、例えばチャネル層14の上面に接して設けられている。ソース電極22及びドレイン電極24は、基板10側からTa層とAl層とが順次積層されている。また、ソース電極22とドレイン電極24との間であって、第2窒化物半導体層18及び保護層20にリセスが形成され、リセスに埋め込まれてゲート電極26が設けられている。ゲート電極26は、例えば第1窒化物半導体層16の上面に接して設けられている。ゲート電極26は、基板10側からNi層とAu層とが順次積層されている。

【0027】

第1窒化物半導体層16及び第2窒化物半導体層18は電子供給層として機能し、チャネル層14の第1窒化物半導体層16との界面に2次元電子ガス28が生成される。ソース電極22から2次元電子ガス28を通りドレイン電極24に至る電子の流れをゲート電極26により制御することで、FETとして機能する。この場合に、Dモードの閾値電圧が得られるように、ゲート電極26下の第1窒化物半導体層16の厚さを、例えば25nmのように厚くすることで、DモードFETとすることができる。

【0028】

次に、実施例1に係る半導体装置の製造方法を説明する。図2(a)から図3(b)は、実施例1に係る半導体装置の製造方法を示す断面模式図の例である。図2(a)を参照に、SiC基板からなる基板10上に、例えばMOCVD(Metal Organic Chemical Vapor Deposition)法を用いて、AlNからなるバッファ層12を成長させる。バッファ層12の成長条件は以下である。なお、結晶成長では、特に注釈をしない限り、キャリアガスとしては水素を用いる。

原料ガス:TMA(トリメチルアルミニウム)、NH3(アンモニア)

成長温度:1000℃

膜厚 :300nm

【0029】

バッファ層12上に、例えばMOCVD法を用いて、GaNからなるチャネル層14を成長させる。チャネル層14の成長条件は以下である。

原料ガス:TMG(トリメチルガリウム)、NH3

成長温度:1000℃

膜厚 :1000nm

【0030】

チャネル層14上に、例えばMOCVD法を用いて、AlGaNからなる第1窒化物半導体層16を成長させる。第1窒化物半導体層16は、例えばチャネル層14の上面に接して形成される。第1窒化物半導体層16の成長条件は以下である。

原料ガス :TMA、TMG、NH3

成長温度 :1000℃

Al組成比:25%

膜厚 :25nm

第1窒化物半導体層16はAl組成比25%のAlGaNからなるため、GaNからなるチャネル層14よりもバンドギャップエネルギー(以下、Egと称す)が大きい。

【0031】

図2(b)を参照に、第1窒化物半導体層16上に、例えばスパッタ法を用いて酸化シリコンを成膜する。その後、ゲート電極26を形成すべき領域以外の領域の酸化シリコンを除去して、ゲート電極26を形成すべき領域に、酸化シリコンからなるダミーゲート30を形成する。

【0032】

ダミーゲート30を形成した後、例えばMOCVD法を用いて、AlGaNからなる第2窒化物半導体層18を再成長させる。これにより、第1窒化物半導体層16上のダミーゲート30以外の領域に選択的に第2窒化物半導体層18が形成される。第2窒化物半導体層18は、例えば第1窒化物半導体層16の上面に接して形成される。第2窒化物半導体層18の成長条件は以下である。

原料ガス :TMA、TMG、NH3

成長温度 :1000℃

Al組成比:25%

膜厚 :25nm

第2窒化物半導体層18はAl組成比25%のAlGaNからなるため、GaNからなるチャネル層14よりもEgが大きい。

【0033】

図2(c)を参照に、ダミーゲート30を、例えばフッ酸を用いたウエットエッチングによって、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去する。その後、第2窒化物半導体層18上に、例えばスパッタ法を用いて、窒化シリコンからなる保護層20を成膜する。ダミーゲート30を除去した領域にも保護層20は形成される。

【0034】

図3(a)を参照に、保護層20上に、例えば酸化シリコンからなるマスク層を形成し、パターニングをする。マスク層のパターニングは、ソース電極22及びドレイン電極24が形成されるべき領域の保護層20の上面が露出されるように行う。マスク層をマスクとして、例えばドライエッチング法を用いて、保護層20、第2窒化物半導体層18及び第1窒化物半導体層16をエッチングして、チャネル層14の上面が露出したリセスを形成する。保護層20をエッチングする際のエッチングガスとして例えばCF4、CHF3、C2F6、SF6などのフッ素系ガスを用いる。第2窒化物半導体層18及び第1窒化物半導体層16をエッチングする際のエッチングガスとして例えばCl2、BCl3、SiCl4などの塩素系ガスを用いる。その後、例えば蒸着法及びリフトオフ法を用いて、リセス内にTa層とAl層とが順次積層されたソース電極22とドレイン電極24とを形成する。

【0035】

図3(b)を参照に、保護層20上に、例えば酸化シリコンからなるマスク層を再び形成し、パターニングをする。マスク層のパターニングは、ゲート電極26が形成されるべき領域の保護層20の上面が露出されるように行う。マスク層をマスクとして、例えばフッ素系ガスを用いたドライエッチング法により、保護層20をエッチングして、第1窒化物半導体層16の上面が露出したリセスを形成する。その後、例えば蒸着法及びリフトオフ法を用いて、リセス内にNi層とAu層とが順次積層された、ゲート電極26を形成する。

【0036】

以上説明してきたように、実施例1によれば、基板10上にチャネル層14と第1窒化物半導体層16とを順次形成した後、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上のダミーゲート30以外の領域に第2窒化物半導体層18を再成長させる。そして、ダミーゲート30を除去した後、ダミーゲート30を除去した領域の第1窒化物半導体層16上にゲート電極26を形成する。このような製造方法を用いて製造することで、図1に示す半導体装置が得られる。この半導体装置は、基板10上にチャネル層14と第1窒化物半導体層16とが順次設けられ、第1窒化物半導体層16上に、互いに離間して選択的に第2窒化物半導体層18が設けられている。そして、第2窒化物半導体層18の離間した領域における第1窒化物半導体層16上に、デプリーションモードFETのゲート電極26が設けられている。このように、ゲート電極26は、第2窒化物半導体層18の電子供給層に埋め込まれた構造となる。したがって、電子供給層をエッチングすることなく、埋め込み型のゲート電極26を得ることができる。

【0037】

例えば、埋め込み型のゲート電極26を、電子供給層をエッチングして形成する場合、以下の製造方法を用いることが考えられる。まず、第1窒化物半導体層16と第2窒化物半導体層18とを順次形成する。その後、第2窒化物半導体層18をエッチングし、そのエッチングした領域にゲート電極26を埋め込んで形成する。この場合、第2窒化物半導体層18は、通常、塩素系ガスを用いたドライエッチング法でエッチングするため、第1窒化物半導体層16との選択比が大きく取れずに、第1窒化物半導体層16までエッチングされてしまう。この結果、ゲート電極26直下の第1窒化物半導体層16の厚さがばらついてしまい、閾値電圧を安定してコントロールすることが難しい。一方、実施例1では、エッチングを用いずに再成長法を用いて埋め込み型のゲート電極26を形成している。このため、ゲート電極26直下の第1窒化物半導体層16の厚さの制御を精度良くできるようになり、閾値電圧を精度良く制御することが可能となる。

【0038】

また、ゲート電極26を第2窒化物半導体層18に埋め込まれた構造とすることで、ゲート電極26直下以外の領域の電子供給層を厚くすることができるため、高濃度の2次元電子ガス28を得ることができる。これにより、抵抗を低減させることができる。さらに、ゲート電極26直下以外の領域の2次元電子ガス28を電子供給層の表面から遠ざけることができる。これにより、電子供給層の表面におけるトラップが2次元電子ガス28に与える影響を小さくでき、電流コラプスを低減させることができる。

【0039】

図2(c)で説明したように、ダミーゲート30を、ウエットエッチング法を用いて、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去する場合が好ましい。なお、選択的に除去するとは、ダミーゲート30と第1窒化物半導体層16及び第2窒化物半導体層18とは、エッチングの選択比が取れることをいう。これにより、ダミーゲート30を除去する際に、第1窒化物半導体層16や第2窒化物半導体層18がエッチングされることを抑制できる。よって、ゲート電極26直下の第1窒化物半導体層16の厚さを精度良く制御することができる。このように、ウエットエッチング法により、第1窒化物半導体層16及び第2窒化物半導体層18に対してダミーゲート30を選択的に除去するために、ダミーゲート30は、酸化シリコンまたは窒化シリコンからなる場合が好ましい。

【0040】

図2(c)で説明したように、第2窒化物半導体層18上に保護層20を形成する。第2窒化物半導体層18がAlGaNのようにAlを含んでいる場合、第2窒化物半導体層18が最表面になると、酸化が進み易く、部分的かつ経時的に酸化アルミニウムが形成されてしまう。これによりデバイス不良が発生してしまう。したがって、第2窒化物半導体層18上に保護層20を形成することで、デバイス不良の発生を抑制することができる。

【0041】

第2窒化物半導体層18上に保護層20を形成した場合、図3(b)で説明したように、ゲート電極26を形成する前に、ゲート電極26を形成すべき領域の保護層20を除去する。この際、ゲート電極の幅などを精度よく制御する点から、ドライエッチング法により保護層20を除去する。ここで、保護層20は窒化シリコンからなるため、フッ素系ガスを用いたドライエッチング法により除去する。AlGaNのドライエッチングでは塩素系ガスが用いられるため、フッ素系ガスを用いて保護層20をエッチングする場合、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択比を大きく取る事ができる。つまり、第1窒化物半導体層16及び第2窒化物半導体層18に対して保護層20を選択的にエッチングすることができ、第1窒化物半導体層16及び第2窒化物半導体層18はほとんどエッチングされない。このため、閾値電圧に与える影響は小さくて済む。

【実施例2】

【0042】

実施例2は、ワイドリセスにゲート電極を埋め込んだ場合の半導体装置の例である。図4は、実施例2に係る半導体装置の断面模式図の例である。図4を参照に、実施例1と異なる点は、ゲート電極26がワイドリセスに埋め込まれていて、ゲート電極26の側面が第2窒化物半導体層18と接していない点である。その他の構成については、実施例1と同じであるため、ここでは説明を省略する。

【0043】

次に、実施例2に係る半導体装置の製造方法を説明する。図5(a)から図6(b)は、実施例2に係る半導体装置の製造方法を示す断面模式図の例である。図5(a)を参照に、基板10上に、例えばMOCVD法を用いて、バッファ層12、チャネル層14、第1窒化物半導体層16を順次成長させる。各層の成長条件は、実施例1に示した成長条件を用いる。

【0044】

図5(b)を参照に、第1窒化物半導体層16上に、例えばスパッタ法を用いて酸化シリコンを成膜する。その後、ゲート電極26を形成すべき領域よりも広い幅の領域の酸化シリコンを残存させ、その他の領域の酸化シリコンを除去することで、酸化シリコンからなるダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上に、例えばMOCVD法を用いて、第2窒化物半導体層18を再成長させる。第2窒化物半導体層18の成長条件は、実施例1に示した成長条件を用いる。

【0045】

図5(c)を参照に、ダミーゲート30をウエットエッチングによって第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去した後、第2窒化物半導体層18上に保護層20を形成する。

【0046】

図6(a)を参照に、ソース電極22及びドレイン電極24を形成すべき領域の保護層20、第2窒化物半導体層18及び第1窒化物半導体層16をドライエッチングしてリセスを形成する。その後、リセス内にソース電極22とドレイン電極24とを形成する。

【0047】

図6(b)を参照に、ゲート電極26を形成すべき領域よりも広い幅の領域であって、第2窒化物半導体層18が形成されていない領域の保護層20をドライエッチングしてワイドリセスを形成する。その後、ワイドリセス内であって、第2窒化物半導体層18の側面に接しないように、ゲート電極26を形成する。

【0048】

以上説明してきたように、実施例2によれば、第1窒化物半導体層16上であって、ゲート電極26の幅よりも広い幅となるようなダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上のダミーゲート30以外の領域に第2窒化物半導体層18を再成長させる。そして、ダミーゲート30を除去した後、ダミーゲートを除去した領域に、第2窒化物半導体層18と接しないようにゲート電極26を形成する。ゲート電極26を埋め込み型とした場合、ゲート電極26の側面が第2窒化物半導体層18に接すると、寄生容量が増大することが考えられる。そこで、実施例2のように、ゲート電極26の側面を第2窒化物半導体層18と接しないようにすることで、寄生容量が増大することを抑制できる。

【0049】

実施例1及び実施例2では、第1窒化物半導体層16はAlGaN(Al組成比:25%)からなり、第2窒化物半導体層18もAlGaN(Al組成比:25%)からなる場合を例に示したが、この場合に限られる訳ではない。第1窒化物半導体層16は、チャネル層14よりもバンドギャップエネルギーの大きい窒化物半導体層からなる場合であればよい。第2窒化物半導体層18は、チャネル層14のバンドギャップエネルギー以上の大きさのエネルギーバンドギャップを有する窒化物半導体層からなる場合であればよい。

【0050】

ここで、窒化物半導体とは、窒素を含む半導体であり、例えばGaN、InN、AlN、InGaN、AlGaN、InAlN、AlInGaNなどが挙げられる。チャネル層14がGaNからなる場合、第1窒化物半導体層16と第2窒化物半導体層18の組み合わせとしては、表1に示すように、実施例1に示したAlGaNとAlGaNの組み合わせの他に、AlGaNとGaN、InAlNとInAlNの組み合わせの場合でもよい。

【表1】

【0051】

表1に関して詳しく説明する。表1を参照に、第1窒化物半導体層16がAlGaNで、第2窒化物半導体層18がGaNである場合(ケース2、ケース4の場合)、第1窒化物半導体層16は電子供給層として機能し、第2窒化物半導体層18はキャップ層として機能する。この場合、Dモードの閾値電圧が得られるように第1窒化物半導体層16の膜厚は例えば25nmとすることができ、第2窒化物半導体層18の膜厚は例えば5nmとすることができる。また、ケース3、ケース4のように、チャネル層14と第1窒化物半導体層16との間に、スペーサ層として例えば膜厚1nmのAlNを挿入してもよい。AlNを挿入することにより、AlNとGaNとの伝導帯の大きな不連続により高濃度の2次元電子ガスが得られる。これにより、高電流化、高出力化が可能となる。

【0052】

さらに、AlNのスペーサ層を挿入し、第1窒化物半導体層16をInAlN、第2窒化物半導体層18もInAlNとする場合(ケース5)でもよい。この場合、第1窒化物半導体層16及び第2窒化物半導体層18は電子供給層として機能する(ケース1、ケース3も同じ)。AlNの膜厚は例えば1.5nmとすることができる。Dモードの閾値電圧が得られるように第1窒化物半導体層16の膜厚は例えば3.5nmとし、第2窒化物半導体層18の膜厚は例えば10nmとすることができる。ここで、電子供給層としてInAlNを用いる理由を説明する。HEMTにおいて、電力密度を高めるため、より多くの電流が流れるように、より高濃度の2次元電子ガスを発生させることが求められている。電子供給層としてAlGaNを用いた場合、Al組成比を上げてより高濃度の2次元電子ガスを発生させることが考えられるが、高Al組成のAlGaNはGaNに対して格子不整合が大きくなるため、高結晶品質を保って形成することが難しい。一方、電子供給層としてInAlNを用いた場合、InAlNはGaNと格子整合すると共に、InAlNとGaNとの大きな自発分極差と伝導帯の大きな不連続により、高濃度の2次元電子ガスが得られるためである。また、AlNをスペーサ層として挿入することで、GaNとInAlNとを物理的に離すことができ、2次元電子ガスの移動度を向上できる。

【0053】

実施例1及び実施例2では、DモードFETの場合を例に示したが、ゲート電極26下の第1窒化物半導体層16の厚さを変えることで、エンハンスメントモードFET(以下において、EモードFETと称す)を形成することもできる。つまり、ゲート電極26として、DモードFETのゲート電極あるいはEモードFETのゲート電極を形成することができる。

【実施例3】

【0054】

実施例3は、同じ基板上にEモードFETとDモードFETとを集積化させた半導体装置の場合の例である。図7は、実施例3に係る半導体装置の断面模式図の例である。図7を参照に、実施例1と異なる点は、第1窒化物半導体層16が例えば膜厚1.5nmのAlNからなり、第2窒化物半導体層18が例えば膜厚3.5nm、In組成比17%のInAlNからなる点である。また、EモードFETとDモードFETとが集積していて、それぞれのソース電極22、ドレイン電極24及びゲート電極(EモードFETのゲート電極を第1ゲート電極26a、DモードFETのゲート電極を第2ゲート電極26bと称す)が設けられている点である。EモードFETの第1ゲート電極26aは、第1窒化物半導体層16の上面に接して設けられ、DモードFETの第2ゲート電極26bは、第2窒化物半導体層18の上面に接して設けられている。その他の構成については、実施例1と同じであるため、ここでは説明を省略する。また、後述するが、表2は、実施例3に関する第1窒化物半導体層16、第2窒化物半導体層18の組み合わせを示している。

【0055】

次に、実施例3に係る半導体装置の製造方法を説明する。図8(a)から図9(b)は、実施例3に係る半導体装置の製造方法を示す断面模式図の例である。図8(a)を参照に、基板10上に、例えばMOCVD法を用いて、バッファ層12及びチャネル層14を順次成長させる。バッファ層12及びチャネル層14の成長条件は、実施例1に示した成長条件を用いる。チャネル層14上に、例えばMOCVD法を用いて、AlNからなる第1窒化物半導体層16を成長させる。第1窒化物半導体層16の成長条件は以下である。

原料ガス:TMA、NH3

成長温度:1000℃

膜厚 :1.5nm

第1窒化物半導体層16はAlNからなるため、GaNからなるチャネル層14よりもEgが大きい。AlNからなる第1窒化物半導体層16はスペーサ層として機能する。

【0056】

図8(b)を参照に、第1窒化物半導体層16上に、例えばスパッタ法を用いて酸化シリコンを成膜する。その後、EモードFETの第1ゲート電極26aを形成すべき領域に酸化シリコンを残存させ、その他の領域の酸化シリコンを除去することで、酸化シリコンからなるダミーゲート30を形成する。ダミーゲート30を形成した後、キャリアガスを水素から窒素に変え、第1窒化物半導体層16上に、例えばMOCVD法を用いて、InAlNからなる第2窒化物半導体層18を再成長させる。第2窒化物半導体層18の成長条件は以下である。

原料ガス :TMI(トリメチルインジウム)、TMA、NH3

成長温度 :800℃

In組成比:17%

膜厚 :3.5nm

第2窒化物半導体層18はIn組成比17%のInAlNからなるため、GaNからなるチャネル層14よりもEgが大きい。InAlNからなる第2窒化物半導体層18は電子供給層として機能する。

【0057】

図8(c)を参照に、ダミーゲート30をウエットエッチングによって第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去した後、第2窒化物半導体層18上に保護層20を形成する。

【0058】

図9(a)を参照に、EモードFETとDモードFETとのそれぞれのソース電極22及びドレイン電極24を形成すべき領域の保護層20、第2窒化物半導体層18及び第1窒化物半導体層16をドライエッチングしてリセスを形成する。保護層20のエッチングガスにはフッ素系ガスを用い、第1窒化物半導体層16及び第2窒化物半導体層18のエッチングガスには塩素系ガスを用いる。その後、リセス内にソース電極22とドレイン電極24とを形成する。

【0059】

図9(b)を参照に、EモードFETの第1ゲート電極26a及びDモードFETの第2ゲート電極26bを形成すべき領域の保護層20を、フッ素系ガスを用いてドライエッチングし、リセスを形成する。その後、リセス内にEモードFETの第1ゲート電極26aとDモードFETの第2ゲート電極26bとを形成する。

【0060】

以上説明してきたように、実施例3によれば、第1窒化物半導体層16上であって、EモードFETの第1ゲート電極26aを形成すべき領域にダミーゲート30を形成する。ダミーゲート30を形成した後、第1窒化物半導体層16上のダミーゲート30以外の領域に第2窒化物半導体層18を再成長させる。そして、ダミーゲート30を除去した後、ダミーゲート30を除去した領域の第1窒化物半導体層16上にEモードFETの第1ゲート電極26aを、第2窒化物半導体層18上にDモードFETの第2ゲート電極26bを形成する。これにより、EモードFETの第1ゲート電極26aは、第1窒化物半導体層16の上面に形成される。一方、DモードFETの第2ゲート電極26bは、第2窒化物半導体層18の上面に形成される。よって、DモードFETの閾値電圧をEモードFETよりも深くすることができる。また、EモードFETの第1ゲート電極26aは、埋め込み型のゲート電極であるが、エッチング法を用いずに再成長法を用いて形成しているため、閾値電圧の安定したEモードFETが得られる。したがって、実施例3によれば、EモードFETとDモードFETとを容易に集積化することができる。

【0061】

図9(b)で説明したように、EモードFETの第1ゲート電極26aとDモードFETの第2ゲート電極26bとは、同じ工程で同時に形成される場合が好ましい。これにより、製造工数を削減することができる。

【0062】

実施例3では、第1窒化物半導体層16はAlNからなり、第2窒化物半導体層18はInAlN(In組成比:17%)からなる場合を例に示したが、この場合に限られる訳ではない。第1窒化物半導体層16は、チャネル層14よりもバンドギャップエネルギーの大きい窒化物半導体層からなる場合であればよい。第2窒化物半導体層18は、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する窒化物半導体層からなる場合であればよい。したがって、表2に示すように、第1窒化物半導体層16がAlGaNで、第2窒化物半導体層18もAlGaNである場合(ケース2)でもよい。この場合、第1窒化物半導体層16及び第2窒化物半導体層18は、電子供給層として機能する。第1窒化物半導体層16は、例えば膜厚8nm、Al組成比25%とし、第2窒化物半導体層18は、例えば膜厚17nm、Al組成比25%とすることができる。

【0063】

また、第1窒化物半導体層16がAlGaNで、第2窒化物半導体層18がGaNである場合(ケース3)でもよい。この場合、第1窒化物半導体層16は電子供給層として機能し、第2窒化物半導体層18はキャップ層として機能する。第1窒化物半導体層16は、例えば膜厚8nm、Al組成比25%とし、第2窒化物半導体層18は、例えば膜厚5nmとすることができる。

【表2】

【0064】

図9(a)及び図9(b)で説明したように、保護層20をフッ素系のエッチングガスを用いてドライエッチングするため、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択比を大きく取る事ができる。このため、第1窒化物半導体層16と第2窒化物半導体層18とは、ほとんどエッチングされない。したがって、EモードFETの第1ゲート電極26a直下の第1窒化物半導体層16の厚さ、並びにDモードFETの第2ゲート電極26b直下の第1窒化物半導体層16及び第2窒化物半導体層18の厚さを精度良く制御することができる。

【0065】

実施例1から3では、保護層20は窒化シリコンからなる場合を例に示したが、この場合に限られる訳ではない。保護層20をドライエッチング法により除去する際に、第1窒化物半導体層16及び第2窒化物半導体層18に対して選択的に除去することが可能であれば、保護層20はその他の材料からなる場合でも良い。

【0066】

表1及び表2で説明したように、第1窒化物半導体層16は電子供給層あるいはスペーサ層としての機能を有し、第2窒化物半導体層18は電子供給層あるいはキャップ層としての機能を有することとすることができる。より具体的には、第1窒化物半導体層16は電子供給層あるいはスペーサ層としての機能を有し、第2窒化物半導体層18は、第1窒化物半導体層16が電子供給層として機能する場合は電子供給層あるいはキャップ層としての機能を有し、第1窒化物半導体層16がスペーサ層として機能する場合は電子供給層としての機能を有することとすることができる。

【0067】

基板10はSiC基板である場合を例に示したが、この場合に限られず、例えばSi基板、GaN基板、サファイア基板、Ga2O3基板を用いてもよい。また、成長に用いる原料は、上述した原料の他に、Al原料としてTEA(トリエチルアルミニウム)、Ga原料としてTEG(トリエチルガリウム)を用いてもよい。さらに、MOCVD法を用いて結晶成長する場合を例に示したが、この場合に限られず、その他の方法により結晶成長する場合でもよい。

【0068】

ゲート電極26は、基板10側からNi層とAu層とが順次積層された構造である場合を例に説明したが、この場合に限られる訳ではない。ゲート電極26は、基板10側から例えばNi層とPd層とAu層とが順次積層された構造の場合でもよい。

【実施例4】

【0069】

実施例4は、実施例3をスイッチ回路に適用した場合の例である。図10は、実施例3に係る半導体装置を用いたインバータ回路の回路図である。図10を参照に、実施例3に係る半導体装置のEモードFET40のソースが接地され、ゲートが入力端子Inに接続され、ドレインがノードN1に接続されている。実施例3に係る半導体装置のDモードFET42のソースがノードN1に接続され、ゲートもノードN1に接続され、ドレインが電源VDDに接続されている。このように、EモードFET40とDモードFET42とを用いDCFL(Drain Coupled FET Logic)回路を形成することができる。

【0070】

図11は、実施例4に係るスイッチ回路を示す回路図の例である。図11を参照に、スイッチ回路60は、インバータ回路50、スイッチSW1及びスイッチSW2を有する。スイッチSW1は、複数の実施例3に係るDモードFET44が直列に接続されている。一端のDモードFET44のソース又はドレインは入力端子Inに接続される。他端のDモードFET44のソース又はドレインは出力端子Out1に接続される。スイッチSW2は、複数の実施例3に係るDモードFET46が直列に接続されている。一端のDモードFET46のソース又はドレインは入力端子Inに接続される。他端のDモードFET46のソース又はドレインは出力端子Out2に接続される。インバータ回路50の入力は制御端子Contに接続されている。制御端子Contは、スイッチSW1を構成するDモードFET44のゲートに抵抗R1を介し接続されてもいる。インバータ回路50の出力は、スイッチSW2を構成するDモードFET46のゲートに抵抗R2を介し接続されている。

【0071】

以上の構成により、制御端子Contにハイが入力すると、スイッチSW1はオンし、スイッチSW2はオフする。制御端子Contにローが入力すると、スイッチSW1はオフし、スイッチSW2はオンする。このように、窒化物半導体を用いたEモードFET40とDモードFET42とを有するインバータ回路50をスイッチSW1及びスイッチSW2と同じ基板に集積化することができる。

【0072】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0073】

10 基板

12 バッファ層

14 チャネル層

16 第1窒化物半導体層

18 第2窒化物半導体層

20 保護層

22 ソース電極

24 ドレイン電極

26 ゲート電極

26a 第1ゲート電極

26b 第2ゲート電極

28 2次元電子ガス

30 ダミーゲート

40 EモードFET

42 DモードFET

44 DモードFET

46 DモードFET

50 インバータ回路

60 スイッチ回路

【特許請求の範囲】

【請求項1】

基板上に、窒化物半導体からなるチャネル層と、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、を順次形成する工程と、

前記第1窒化物半導体層上であって、ゲート電極を形成すべき領域にダミーゲートを形成する工程と、

前記ダミーゲートを形成した後、前記第1窒化物半導体層上の前記ダミーゲート以外の領域に、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層を再成長する工程と、

前記ダミーゲートを除去した後、前記ダミーゲートを除去した領域の前記第1窒化物半導体層上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ダミーゲートは、前記ゲート電極の幅よりも広い幅となるように形成し、

前記ゲート電極は、前記第2窒化物半導体層と接しないように形成することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記ダミーゲートは、エンハンスメントモードFETのゲート電極を形成すべき領域に形成し、

前記ダミーゲートを除去した領域の前記第1窒化物半導体層上に前記エンハンスメントモードFETのゲート電極を形成し、

前記第2窒化物半導体層上にデプリーションモードFETのゲート電極を形成する工程を有することを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記エンハンスメントモードFETのゲート電極と前記デプリーションモードFETのゲート電極とは、同じ工程で同時に形成されることを特徴とする請求項3記載の半導体装置の製造方法。

【請求項5】

前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせに係る前記第1窒化物半導体層と前記第2窒化物半導体層とを形成することを特徴とする請求項1から4のいずれか一項記載の半導体装置の製造方法。

【請求項6】

前記ダミーゲートを、ウエットエッチング法により、前記第1窒化物半導体層および前記第2窒化物半導体層に対して選択的に除去することを特徴とする請求項1から5のいずれか一項記載の半導体装置の製造方法。

【請求項7】

前記ダミーゲートは、酸化シリコンまたは窒化シリコンからなることを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

前記第2窒化物半導体層上に保護層を形成する工程と、

前記ゲート電極を形成する前に、前記ゲート電極を形成すべき領域の前記保護層をドライエッチング法により除去する工程と、を有し、

前記保護層は、前記第1窒化物半導体層及び前記第2窒化物半導体層に対して選択的に除去されることを特徴とする請求項1から7のいずれか一項記載の半導体装置の製造方法。

【請求項9】

前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有することを特徴とする請求項1から8のいずれか一項記載の半導体装置の製造方法。

【請求項10】

前記ゲート電極を形成する工程は、エンハンスメントモードFETのゲート電極を形成する工程あるいはデプリーションモードFETのゲート電極を形成する工程であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項11】

前記第2窒化物半導体層を再成長する工程は、MOCVD法により行われることを特徴とする請求項1から10のいずれか一項記載の半導体装置の製造方法。

【請求項12】

基板と、

前記基板上に設けられた窒化物半導体からなるチャネル層と、

前記チャネル層上に設けられ、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、

前記第1窒化物半導体層上に互いに離間して選択的に設けられた、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層と、

前記第2窒化物半導体層が離間した領域における前記第1窒化物半導体層上に設けられたゲート電極と、を備え、

前記ゲート電極はデプリーションモードFETのゲート電極であることを特徴とする半導体装置。

【請求項13】

前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有することを特徴とする請求項12記載の半導体装置。

【請求項14】

前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせからなることを特徴とする請求項12または13記載の半導体装置。

【請求項1】

基板上に、窒化物半導体からなるチャネル層と、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、を順次形成する工程と、

前記第1窒化物半導体層上であって、ゲート電極を形成すべき領域にダミーゲートを形成する工程と、

前記ダミーゲートを形成した後、前記第1窒化物半導体層上の前記ダミーゲート以外の領域に、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層を再成長する工程と、

前記ダミーゲートを除去した後、前記ダミーゲートを除去した領域の前記第1窒化物半導体層上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ダミーゲートは、前記ゲート電極の幅よりも広い幅となるように形成し、

前記ゲート電極は、前記第2窒化物半導体層と接しないように形成することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記ダミーゲートは、エンハンスメントモードFETのゲート電極を形成すべき領域に形成し、

前記ダミーゲートを除去した領域の前記第1窒化物半導体層上に前記エンハンスメントモードFETのゲート電極を形成し、

前記第2窒化物半導体層上にデプリーションモードFETのゲート電極を形成する工程を有することを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記エンハンスメントモードFETのゲート電極と前記デプリーションモードFETのゲート電極とは、同じ工程で同時に形成されることを特徴とする請求項3記載の半導体装置の製造方法。

【請求項5】

前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせに係る前記第1窒化物半導体層と前記第2窒化物半導体層とを形成することを特徴とする請求項1から4のいずれか一項記載の半導体装置の製造方法。

【請求項6】

前記ダミーゲートを、ウエットエッチング法により、前記第1窒化物半導体層および前記第2窒化物半導体層に対して選択的に除去することを特徴とする請求項1から5のいずれか一項記載の半導体装置の製造方法。

【請求項7】

前記ダミーゲートは、酸化シリコンまたは窒化シリコンからなることを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

前記第2窒化物半導体層上に保護層を形成する工程と、

前記ゲート電極を形成する前に、前記ゲート電極を形成すべき領域の前記保護層をドライエッチング法により除去する工程と、を有し、

前記保護層は、前記第1窒化物半導体層及び前記第2窒化物半導体層に対して選択的に除去されることを特徴とする請求項1から7のいずれか一項記載の半導体装置の製造方法。

【請求項9】

前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有することを特徴とする請求項1から8のいずれか一項記載の半導体装置の製造方法。

【請求項10】

前記ゲート電極を形成する工程は、エンハンスメントモードFETのゲート電極を形成する工程あるいはデプリーションモードFETのゲート電極を形成する工程であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項11】

前記第2窒化物半導体層を再成長する工程は、MOCVD法により行われることを特徴とする請求項1から10のいずれか一項記載の半導体装置の製造方法。

【請求項12】

基板と、

前記基板上に設けられた窒化物半導体からなるチャネル層と、

前記チャネル層上に設けられ、前記チャネル層よりもバンドギャップエネルギーの大きい第1窒化物半導体層と、

前記第1窒化物半導体層上に互いに離間して選択的に設けられた、前記チャネル層のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層と、

前記第2窒化物半導体層が離間した領域における前記第1窒化物半導体層上に設けられたゲート電極と、を備え、

前記ゲート電極はデプリーションモードFETのゲート電極であることを特徴とする半導体装置。

【請求項13】

前記第1窒化物半導体層は、電子供給層あるいはスペーサ層としての機能を有し、前記第2窒化物半導体層は、電子供給層あるいはキャップ層としての機能を有することを特徴とする請求項12記載の半導体装置。

【請求項14】

前記チャネル層がGaNである場合に、前記第1窒化物半導体層と前記第2窒化物半導体層との組み合わせとして、AlGaNとAlGaN、AlGaNとGaN、InAlNとInAlN、AlNとInAlNのいずれかの組み合わせからなることを特徴とする請求項12または13記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−77635(P2013−77635A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−215422(P2011−215422)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

[ Back to top ]