半導体装置およびその製造方法

【目的】 ゲート抵抗を低減し、かつ、パンチスルーストッパによる寄生容量を減少させたMOSFETの構造およびその製造方法を提供する。

【構成】 素子分離酸化膜2で囲まれた基板1の領域に、基板と同じ導電型の不純物領域4、LDD用拡散層12、ソース・ドレイン用拡散層14を形成すると共に、ゲート酸化膜5上には3層のタングステン膜6、10、15からなるゲート電極を形成する。パンチスルーストッパ11は、ゲート電極端の直下の限られた部分に形成し、拡散層14の表面にもタングステン膜15を形成する。

【効果】 従来のシリサイドを用いたゲート電極に比べてゲート抵抗を1/10以下に低減できると共に、パンチスルーストッパによる寄生容量も1/10程度に低減できる結果、動作速度が大幅に向上する。

【構成】 素子分離酸化膜2で囲まれた基板1の領域に、基板と同じ導電型の不純物領域4、LDD用拡散層12、ソース・ドレイン用拡散層14を形成すると共に、ゲート酸化膜5上には3層のタングステン膜6、10、15からなるゲート電極を形成する。パンチスルーストッパ11は、ゲート電極端の直下の限られた部分に形成し、拡散層14の表面にもタングステン膜15を形成する。

【効果】 従来のシリサイドを用いたゲート電極に比べてゲート抵抗を1/10以下に低減できると共に、パンチスルーストッパによる寄生容量も1/10程度に低減できる結果、動作速度が大幅に向上する。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は半導体装置およびその製造方法に係り、特にゲート電極抵抗の低抵抗化と接合容量の低減により高性能化を図った金属−酸化膜−半導体型の電界効果トランジスタを有する(Metal Oxide Semiconductor Field Effect Transistor;以下、MOSFETと略す)半導体装置とその製造方法に関する。

【0002】

【従来の技術】シリコンを用いた集積回路の代表例であるダイナミック・ランダム・アクセス・メモリは、現在、0.8ミクロンの技術を用いて、4メガビットの量産が行われている。また、次世代の0.5ミクロン技術を使用する16メガビットの量産化も始まっている。今後も、微細加工技術の進歩と相俟って、半導体素子が縮小され、集積度の向上と高性能化が実現されるのは間違いない。

【0003】しかし、チャネル長がハーフミクロン以下の領域になると、MOSFETのチャネル領域を流れる電子もしくは正孔は、速度が完全に飽和した状態になっており、このため、微細化しても、これまでのようには、チャネル長に反比例して電流が大きくなることは期待できない。また、微細化を進めるために、基板濃度が上昇しており、その結果、電子もしくは正孔の移動度が減少している。さらには、基板濃度の増加は接合容量の増加を招き、ゲート電極の微細化はゲート抵抗の増加を招く。以上のような要因が、MOSFETの微細化による性能向上という利点を損なう原因となる。

【0004】このような課題が発生するMOSFETの構造的問題点を、図4を用いて説明する。図4は、従来技術により作製したチャネル長がハーフミクロン以下の微細なMOSFETを有する半導体装置の断面図であり、同一半導体基板上に導電型の異なるMOSFETが混在する相補型の半導体装置(CMOS;Complementary MOS)を示している。図4において、参照符号1は半導体基板を示し、半導体基板1にはp型領域21とn型領域22が形成されており、p型領域21にチャネル長がハーフミクロン以下のn型MOSFETが作製され、n型領域22にチャネル長がハーフミクロン以下のp型MOSFETが作製される。

【0005】チャネル長がハーフミクロン以下の従来のMOSFETに特徴的な構造は、パンチスルーストッパ31、31’と、導電型の異なるゲート電極30、30’と不純物領域12、12’,14、14’およびゲート電極30、30’を被うシリサイド膜35、35’とを有することである。

【0006】パンチスルーストッパ31はp型領域21と同じ導電型で高濃度な不純物領域であり、パンチスルーストッパ31’はn型領域22と同じn型であるがより不純物濃度が高い領域である。パンチスルーストッパ31、31’は、それぞれ不純物領域12、12’の接合から広がる空乏層がチャネル領域に張り出すのを防ぎ、接合間の干渉によるリーク電流の発生を抑える。このパンチスルーストッパ31、31’は、不純物領域14、14’の接合界面の近傍に濃度のピークが位置するように、不純物濃度分布が設定されている。

【0007】不純物領域14、14’上やゲート電極30、30’上のシリサイド膜35、35’は、これらの導電層の抵抗を下げる効果がある。不純物領域14、14’の接合深さはMOSFETの微細化に伴って浅くなっており、同じ不純物濃度であっても、抵抗は増加する。これまでは、チャネル抵抗に比べて不純物領域14、14’の拡散抵抗は十分小さかったので、MOSFETの電流には直接的に影響を及ぼすことはなかった。しかし、チャネル長の減少とともにチャネル抵抗も小さくなるが、不純物領域14、14’の拡散抵抗は増加するために、これらの抵抗が同程度の大きさになってくる。その結果、不純物領域14、14’による電圧降下が顕著に見え始め、MOSFETの本来の性能が引き出せなくなる。これを防ぐために、シリサイド膜35、35’が用いられる。シリサイド膜35、35’は、公知のシリサイド技術を用いることにより、ゲート電極30、30’と不純物領域14、14’上の両方に形成することができる。

【0008】また、導電型の異なるゲート電極30、30’を用いるのは、n型MOSFETとp型MOSFETの両方を、以下に述べるように、表面チャネル型にする必要があるためである。すなわち、これまでp型MOSFETは、n型MOSFETと同様に、ゲート電極にn型の不純物を高濃度で含む多結晶シリコンを用いてきた。しかし、p型MOSFETでは、基板との仕事関数差が小さいために、MOSFETをオンさせるためのゲート電圧(しきい電圧)が大きくなる。そこで、チャネル領域に、基板とは導電型の異なる不純物(具体的にはボロン)を導入し、表面近傍をp型にして、しきい電圧の調整を行ってきた。このような不純物分布になると、正孔は基板の内部を流れるようになるので、埋め込みチャネル型MOSFETと呼ばれている。埋め込みチャネル型のMOSFETでは、電子や正孔がゲート酸化膜界面での散乱を受ける確率が低くなるために、表面チャネル型に比べて移動度が大きいが、チャネル領域がゲート電極から離れているために、接合間の干渉が起こり易くリーク電流も流れ易い問題点があった。しかし、この問題点は、p型MOSFETのゲート電極をp型の多結晶シリコンとすることにより、n型MOSFETと同様の表面チャネル型となるので、解決することができる。

【0009】このように、従来から様々な工夫を加えることでMOSFETを微細化し、性能向上を図ってきた。なお、前述したようなパンチスルーストッパ、シリサイド膜、異なる導電型の多結晶シリコンゲートを有する相補型の半導体装置については、例えば、テクニカル・ダイジェスト アイ・イー・イー・イー インターナショナル・エレクトロン・デバイセズ・ミーティング 1993年 第127頁から130頁(Technical Digest. IEEE International Electron Devices Meeting, pp.127-130, 1993)に記載されている。

【0010】

【発明が解決しようとする課題】しかしながら、前述した従来の半導体装置における対策は、さらに微細なMOSFETを実現するには、依然として以下に述べるような、性能向上を阻害し、製造工程を複雑にする側面を合わせ持っている。

【0011】例えば、短チャネル効果に伴うリーク電流の発生を抑制するために設けたパンチスルーストッパ31、31’は、チャネル領域を高濃度化するために、電子や正孔の移動度を減少させ、ひいては、電流の減少を招いてしまう。また、チャネル領域の高濃度化は接合容量を増加させるので、信号の遅延時間が長くなってしまう問題がある。これまでは、このような問題は寸法の微細化による電流の増加でカバーしてきたが、前述したように、電子や正孔の速度は飽和しており、チャネル長を小さくしても必ずしも電流の増加が期待できない状況では、移動度の減少や接合容量の増加は、性能の低下を招くだけである。

【0012】さらに、シリサイドを表面近傍に成長させたゲート電極30、30’にも、微細化に伴って低抵抗化に限界が現れて来る。これは、ゲート電極の寸法が小さくなると共に、シリサイド反応が微細なパターンにおいて抑制されるからである。ゲート電極よりは遥かに面積の大きな接合でも、別の意味でシリサイド化の限界がある。それは、接合が浅くなるのに伴って、十分に厚いシリサイド層を形成することができなくなるからである。また、シリサイド膜35、35’は、半導体基板内部に形成されるために、不純物を高濃度で含む領域がシリサイド化する。このため、残された不純物領域は不純物濃度が低い領域であり、不純物領域の低抵抗化にとってシリサイド化は必ずしも好ましいことではない。

【0013】従って、この不純物領域及びゲート電極の高抵抗化の問題に加えて、従来の多結晶シリコンを用いるゲート電極構成では、表面チャネル型の相補型MOSFETを形成するために導電型の異なる多結晶シリコンを使用しなければならず、製造工程が増加するという問題点があった。このゲート電極形成工程の増加は、結果としてLSIのコスト上昇および歩留まりの低下を招いていた。

【0014】そこで、本発明の目的は、不純物領域及びゲート電極の低抵抗化により高性能化を図った微細なMOSFETを有する半導体装置を提供すること、並びに、不純物領域及びゲート電極の低抵抗化を図ることができると共にゲート電極形成工程数の低減を図ることができる半導体装置の製造方法を提供することにある。

【0015】

【課題を解決するための手段】上記目的を達成するために、本発明の請求項1に係る半導体装置は、素子間分離用絶縁膜で囲まれた半導体基板の第1の領域に、所定の間隔で形成された該第1の領域の導電型とは導電型が異なる一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とを具備する電界効果型の半導体装置において、上記ゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記ゲート電極の上記2つの側壁絶縁膜のそれぞれの下の第1の領域に、ゲート幅と同じ長さで局在する上記第1の領域と同じ導電型の2つの高濃度不純物領域を有するよう構成することを特徴とする。具体的に、実施例に対応する図1を用いて説明すれば、本発明に係る半導体装置は、タングステン膜6、10、15から成る3層構造のゲート電極と、このゲート電極の両端付近のゲート酸化膜下の半導体基板領域にゲート幅と同じ長さで局在する半導体基板1と同じ導電型の高濃度不純物領域、すなわちゲート電極端の直下に存在し不純物領域12、14とは僅かな領域だけで接するパンチスルーストッパ11を有するように構成されている。なお、図1において、参照符号2は素子分離酸化膜、4は素子分離特性を向上させるための高不純物濃度層、5はゲート絶縁膜、13はゲート電極の側壁絶縁膜、16は層間絶縁膜、17はコンタクト孔を埋めるプラグ金属、そして、18は配線金属である。

【0016】また、請求項2に係る半導体装置は、素子間分離用絶縁膜でそれぞれ囲まれた半導体基板の第1の領域および該第1の領域の導電型と異なる第2の領域に、それぞれの領域の導電型とは導電型が異なると共に所定間隔で形成された一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とをそれぞれ具備する相補型の電界効果型半導体装置において、上記それぞれのゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記それぞれのゲート電極の上記2つの側壁絶縁膜の下のそれぞれの第1および第2の領域に、ゲート幅と同じ長さで局在する上記それぞれの領域と同じ導電型の2つの高濃度不純物領域を有するように構成することを特徴とする。この相補型の本発明に係る半導体装置を具体的に図3を用いて説明すれば、図1に示した半導体装置をCMOSの場合に適用したものであり、同一半導体基板1上の素子間分離用絶縁膜2で囲まれた半導体基板1に、それぞれ導電型が異なる第1及び第2の領域すなわちウエル領域21、22、ソース、ドレイン領域である高濃度の拡散による不純物領域(以下、拡散による不純物領域を拡散層と呼ぶ)14、14’、素子分離特性を向上させる高濃度層41、42、それぞれのゲート電極の両端付近の直下に局在するパンチスルーストッパ11、11’を有している。

【0017】前記半導体装置において、ゲート電極は高融点金属とすることができ、高融点金属の中でもタングステンであれば好適である。

【0018】さらに、前記半導体装置のいずれかにおいて、少なくとも2層構造からなるゲート電極の、ゲート絶縁膜に接触している最下層のゲート電極は、上層のゲート電極より張り出すよう構成することができる。このとき、最下層ゲート電極の張り出した部分の下の領域に、前記一対の不純物領域と同じ導電型で、かつ、一対の不純物領域の不純物濃度よりも低い不純物濃度の拡散による不純物領域を有すれば更に好適である。具体的に図2を用いて説明すれば、ゲート電極を構成する第1層目のタングステン膜6が第2層目のタングステン膜10より張り出した構成となっており、更に張り出した第1層目のタングステン膜6の下の基板中に低濃度の拡散層12が形成されている。

【0019】本発明に係る半導体装置の製造方法は、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、この絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程10と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程11と、工程10で残した第1及び第2の導電膜の側壁に側壁絶縁膜を形成する工程12と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程13と、工程13で形成した不純物領域の表面および工程10で残した導電膜の表面に第3の導電膜を成長させる工程14と、半導体基板表面を層間絶縁膜で被う工程15と、層間絶縁膜にコンタクト孔を開口する工程16と、配線層を形成する工程17とからなることを特徴とする。

【0020】また、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程10と、工程6で形成した第2の導電膜の側壁に側壁絶縁膜を形成する工程11と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程12と、工程12で残した導電膜の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程12で残した導電膜の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18とからなる半導体装置の製造方法とすることもできる。

【0021】更に、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に多結晶シリコン膜を形成する工程2と、多結晶シリコン膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して多結晶シリコン膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した多結晶シリコン膜を第1の導電膜に置換する工程6と、第1の導電膜の表面に第2の導電膜を成長させる工程7と、側壁絶縁膜を除去する工程8と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程9と、絶縁膜を除去する工程10と、工程2で形成した多結晶シリコン膜と並びに工程7で形成した第2の導電膜のゲート電極になる部分以外の導電膜とを除去する工程11と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程12と、工程11で形成したゲート電極の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程11で形成したゲート電極の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18とからなる半導体装置の製造方法であっても良い。

【0022】前記半導体装置の製造方法において、第1乃至第3の導電膜は高融点金属の膜とすることができ、高融点金属の中でもタングステンであれば好適である。或いは、第1及び第2の導電膜をタングステン膜とし、第3の導電膜をチタンからなる膜としても良い。

【0023】

【作用】本発明に係る半導体装置によれば、ゲート電極の両端付近の半導体基板領域にゲート幅と同じ長さで局在する半導体基板領域と同じ導電型の高濃度不純物領域、すなわち、ゲート電極端の直下に存在する局所パンチスルーストッパ11,11’は、ソース及びドレインとなる拡散層と僅かな領域だけで接するため、従来のパンチスルーストッパ31,31’と比べて接触部分が少なくなり、接合容量が大幅に低減する。また、この局所パンチスルーストッパは、ゲート電極の端に局在するのでゲート電極下の大部分の領域は低不純物濃度の状態に保たれたままにでき、電子や正孔が流れるチャネル領域における垂直方向電界(基板に対して)が小さい。従って、チャネル領域全体にパンチスルーストッパが形成される従来の構造に比べて、移動度が高くでき電流が大きくなる。

【0024】少なくとも2層構造で構成されるゲート電極は、高融点金属を用いた構造であるため、従来のシリサイド化したゲート電極に比べてゲート電極抵抗が減少する。特に、高融点金属としてタングステンを用いれば、従来のシリサイド化したゲート電極のシート抵抗10Ω/□に対して1Ω/□と1/10に低減する。タングステンのゲート電極を用いること自体は、従来構造のMOSFETでも可能であるが、一般的に、タングステンのような金属の加工を、ゲート絶縁膜のように薄い絶縁膜(具体的には5nm程度)の上で行うのは非常に困難であり、通常では、ゲート絶縁膜が完全に除去されて基板まで削れてしまう。本発明では、実施例において詳細に説明するように、実際に加工するタングステンの膜を薄くすることで、この問題を解決している。

【0025】また、ソース及びドレイン拡散層の電極は高融点金属を用いた構造としたため、従来のシリサイド化電極を用いる構造の場合のようにシリサイド化によって拡散層の高不純物濃度領域を侵食することがなく、拡散層の低抵抗化が図れる。

【0026】さらに、少なくとも2層構造で構成されるゲート電極の最下層のゲート電極を上層のゲート電極より張り出した構造は、低濃度拡散層と重なることによりゲートオーバーラップドレイン構造を構成し、抵抗の増加を抑えると共に、ホットキャリアの発生を抑制するのでデバイスの信頼性が向上する。

【0027】本発明に係る半導体装置の製造方法によれば、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成し、次いでゲート絶縁膜上に第1の導電膜を形成し、第1の導電膜上に絶縁膜を形成した後、この絶縁膜のゲート電極を形成する部分に溝を形成して第1の導電膜の表面の一部を露出させ、溝の側壁に側壁絶縁膜を形成して露出した第1の導電膜上に第2の導電膜を形成し、側壁絶縁膜を除去し、この除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入することにより、ゲート電極の両端付近の半導体基板領域にゲート幅と同じ長さで局在する半導体基板領域と同じ導電型の高濃度不純物領域、すなわち、ゲート電極端の直下に存在する局所パンチスルーストッパを形成することができる。

【0028】また、上記パンチスルーストッパ形成後、絶縁膜を除去し、第1の導電膜及び第2の導電膜のゲート電極となる部分を残してこれら導電膜を除去し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入した後、ゲート電極となる第1及び第2の導電膜の側壁に側壁絶縁膜を形成し、更に前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、この不純物領域の表面と前記残した第1及び第2の導電膜の表面に第3の導電膜を成長させることにより、少なくとも2層のゲート電極、この場合は3層構造のゲート電極が形成されると同時に、ソースおよびドレインの拡散上の電極もゲート電極を構成する第3の導電膜で形成される。

【0029】或いは、上記製造方法において、パンチスルーストッパ形成後、絶縁膜を除去し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入した後、第2の導電膜の側壁に側壁絶縁膜を形成し、次いで第1及び第2の導電膜のゲート電極となる部分を残してこれら導電膜を除去し、この残した導電膜の側壁に側壁絶縁膜を形成し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、この不純物領域の表面と前記残した第1及び第2の導電膜の表面に第3の導電膜を成長させることにより、少なくとも2層のゲート電極、この場合は3層構造のゲート電極で第1層が上層より張り出したゲート電極が形成されると同時に、ソースおよびドレインの拡散上の電極がゲート電極を構成する第3の導電膜で形成される。

【0030】更にまた、請求項9に係る半導体装置の製造方法によれば、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成し、次いでゲート絶縁膜上に多結晶シリコン膜を形成した後、多結晶シリコン膜上に絶縁膜を形成し、この絶縁膜のゲート電極を形成する部分に溝を形成して多結晶シリコン膜の表面の一部を露出させ、溝の側壁に側壁絶縁膜を形成した後、露出した多結晶シリコン膜を第1の導電膜に置換し、第1の表面に第2の導電膜を成長させた後、側壁絶縁膜を除去し、この除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入することによってパンチスルーストッパを形成する。この後、絶縁膜を除去し、更に多結晶シリコン膜と並びに第2の導電膜のゲート電極になる部分以外の導電膜とを除去し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、ゲート電極になる第1及び第2の導電膜の側壁に側壁絶縁膜を形成し、次いで前記半導体基板領域中に半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、この不純物領域の表面と第1及び第2の導電膜で構成されるゲート電極の表面に第3の導電膜を成長させることにより、少なくとも2層のゲート電極、この場合は3層構造のゲート電極が形成されると同時に、ソース及びドレインの拡散上の電極もゲート電極を構成する第3の導電膜で形成される。

【0031】

【実施例】以下、本発明に係る半導体装置およびその製造方法の好適な幾つかの実施例につき、図5乃至図16を用いて詳細に説明する。

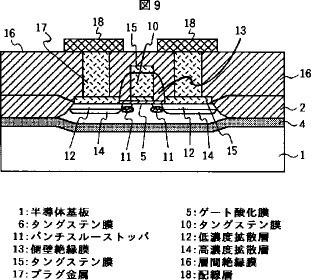

【0032】<実施例1>図5乃至図9は、本発明に係る半導体装置およびその製造方法の一実施例を示す断面構造図であり、主要工程順に順を追って示したものである。なお、説明の便宜上、ここではn型のMOSFETを一例に説明する。

【0033】まず、図5の(A)において、参照符号1は半導体基板を示し、この半導体基板1に対し公知の選択酸化法を用いて素子分離酸化膜2を成長させる。具体的には、p型の半導体基板1の表面に20nm程度の酸化膜3を成長させ、さらに、その上に窒化膜(不図示)を公知の低圧気相成長法により堆積した後に、この窒化膜を所望の形状に加工し、その後、水蒸気を含んだ1100℃の雰囲気で30分間酸化する。このとき、窒化膜で被われていない領域にのみ酸化膜2が成長する。そして、酸化のマスクとなった窒化膜を180℃程度に加熱したリン酸溶液で除去することにより、図5の(A)の構造が得られる。なお、成長させた酸化膜2の厚さは約300nmである。

【0034】次に、酸化膜2を成長させただけでは十分な素子分離特性が得られないので、図5の(B)に矢印で示したように、半導体基板全面に公知のイオン打ち込み法を用いてイオン打ち込みを行い、基板1と同じ導電型の不純物領域4を形成する。具体的には、ボロンを100KeVで5×1013/cm2打ち込み、不純物濃度のピークが酸化膜2と基板1の界面近傍に位置するように条件を設定する。酸化膜2と基板1ではイオンの阻止能力が違うために、図に示したように、酸化膜2がないところでは、不純物領域4のピーク位置が深くなる。ここで、選択酸化の際の酸化膜3を残したままでイオン打込みを行うのは、イオン打ち込みの際に汚染が基板内部に入るのを防ぐためである。勿論、選択酸化後に酸化膜3を除去して新たな酸化膜を形成してこれを用いても良い。なお、基板1がn型でp型MOSFETを形成する場合は、通常、リンをイオン打ち込みする。

【0035】次に、図5の(C)に示したように、ゲート酸化膜5を成長させる。具体的には、チャネル長0.1〜0.2μmのMOSFETを形成する場合、ゲート酸化膜5の膜厚は約5〜7nmであり、酸化温度は800℃である。なお、このゲート酸化膜5の成長の前に、イオン打ち込みに伴う表面の汚染を除去するための洗浄を行ったり、打ち込まれたイオンを活性化するための熱処理を行うことは言うまでもない。

【0036】次に、図5の(D)に示したように、ゲート電極の一部となる最下層のタングステン膜6を堆積する。この高融点金属の一つであるタングステンの膜厚は、後述するように、加工に際してゲート酸化膜5を削らないようにするために、チャネル長0.1〜0.2μmのMOSFETを形成する場合で20〜40nm程度と薄膜にする。また、ゲート酸化膜5との接着性を良くするために、タングステン膜6の堆積には公知のスパッタ法を用いる。

【0037】次に、図6の(A)に示したように、タングステン膜6の上に窒化膜7を堆積する。本実施例では、プラズマによって反応を促進させる、プラズマCVD(Chemical Vapor Deposition)法を用いて、約200nmの窒化膜を堆積させた。そしてさらに、公知のリソグラフィ技術を用いて、窒化膜7上のレジスト膜8に溝状のパターンを形成する。

【0038】次に、図6の(B)に示したように、上記レジスト膜8をエッチングマスクにして公知のドライエッチ技術により窒化膜7をエッチングし、最下層のタングステン膜6に達する溝を窒化膜7に形成する。そして、レジスト膜8を除去し、さらに、同図中に示したように、公知の側壁絶縁膜形成技術を用いて、溝の側壁に絶縁膜9を形成する。具体的には、溝を有する基板全面に酸化膜を堆積し(不図示)、これを公知の異方性ドライエッチ法、例えば反応性イオンエッチング(RIE)により全面エッチングを行うと、溝の側壁にのみ酸化膜が残る。側壁酸化膜9の厚さtは100nm程度である。溝の幅からこの側壁酸化膜9の2倍の厚さ2tを引いた長さがゲート電極長であり、ほぼチャネル長に対応する。従って、所望のチャネル長を得るように、溝の幅及び側壁酸化膜の厚さを設定すればよい。このようにチャネル長が側壁酸化膜9の厚さtにより決定できるので、この側壁酸化膜9の厚さを適当に選べば、ゲート電極寸法をリソグラフィ限界以下にすることも可能である。

【0039】次に、公知のタングステン選択成長技術を用いると、図6の(C)に示したように、溝の底に露出しているタングステン膜6の表面を核にして、溝の内部を埋めるように第2層目のタングステン膜10が成長する。成長させる第2層目のタングステン膜10の厚さは、成長時間で調整するが、本実施例では150〜200nm成長させた。なお、タングステン膜の成長としては、選択成長技術の他に、全面にスパッタによりメタル接着層を形成し、更に全面にタングステン膜を気相成長法で形成した後、エッチバック工程等でエッチングして溝の内部にのみタングステンを形成する方法も用いることができる。

【0040】ところで、タングステン膜は多結晶シリコン膜などと異なり、結晶粒が柱状であるため、従来の方法でゲート電極状に加工すると、たとえマスクとなるレジスト膜の側壁が平滑であっても、結晶粒界に起因する凹凸が側面にも発生する。このため、一本のゲート電極でもその寸法がばらつく原因となる。これは、ゲート電極の幅が小さくなるほど深刻な問題である。一方、本発明の方法によれば、第2層目のタングステン膜10の横方向への成長は、溝の側壁酸化膜9によって制限されており、しかも、側壁酸化膜9は滑らかである。非晶質である窒化膜7には側壁が滑らかな溝を形成することが可能であり、そこに形成した側壁酸化膜9も滑らかとなるからである。従って、滑らかな側壁酸化膜9により制限されるタングステン膜10の側壁も平滑となるので、側壁が平滑なゲート電極を得ることができ、上記問題は解決される。

【0041】次に、図6の(D)に示したように、ゲート電極となる第2層目のタングステン膜10と、窒化膜7の間にある側壁酸化膜9を除去する。このとき、酸化膜の除去にはフッ酸溶液を用いるが、タングステンと窒化膜はフッ酸溶液ではエッチングされない。

【0042】次に、図7の(A)に示したように、この側壁酸化膜9の除去後の隙間を通して窒化膜7をマスクに不純物イオンを打ち込み、ゲート電極端の近傍直下にパンチスルーストッパ11を形成する。本実施例では、20〜30KeVのエネルギで、1×1012〜1×1013/cm2のボロンを打ち込んだ。なお、p型MOSFETの場合には、ヒ素を100〜140KeV、1×1012〜1×1013/cm2打ち込んでパンチスルーストッパを形成すればよい。

【0043】次に、図7の(B)に示したように、溝が形成されていた窒化膜7を180℃程度に加熱したリン酸溶液で除去する。このとき、タングステン膜6、7は、加熱したリン酸液には溶解しない。

【0044】次に、図7の(C)に示したように、基板表面を被っている20〜40nm程度の第1層目のタングステン膜6を除去して、素子分離酸化膜2、および、ゲート酸化膜5の一部を露出させる。このタングステン膜の除去にも公知のドライエッチ法を用いるが、その際、除去する第1層目のタングステン膜6の厚さが、下地となるゲート酸化膜5の削れに大きな影響を及ぼす。それは、加工する膜が厚くなるほど、エッチングの均一性を向上させるためのオーバーエッチ時間が長くなり、下地のゲート酸化膜5がエッチングにさらされる時間が増えるためである。本実施例では、除去するタングステン膜は20〜40nm程度なので、5〜7nmのゲート酸化膜5上でも、均一性を維持しながらエッチングを止めることができる。勿論、このとき第2層目のタングステン膜10もエッチングされる。

【0045】このタングステン膜の加工によって、ゲート電極端のゲート酸化膜5に損傷が入るので、それを回復させるための熱処理を行い、さらに、図7の(D)に示したように、拡散層12を形成するイオン打ち込みを行う。この工程では、公知のLDD(Lightly Doped Drain)構造の低濃度拡散層12を作るため、打ち込む不純物の量は、1×1013〜1×1014/cm2とした。不純物はリンもしくはヒ素である。なお、損傷を回復させる熱処理として、本実施例においては、酸素と水蒸気の分圧を調整することで、シリコン基板を酸化しながら、タングステン膜は酸化しない技術を用いる。例えば、800℃で10%水蒸気を含む酸素雰囲気中で15分間程度の熱処理を行う。

【0046】次に、図8の(A)に示したように、公知の側壁絶縁膜形成技術を用いて、ゲート電極となるタングステン膜10、6の側壁にのみ絶縁膜13を形成する。具体的には、プラズマCVDで堆積した酸化膜を、異方性ドライエッチ法で全面エッチングする。さらに、リンもしくはヒ素を1×1015/cm2以上打ち込み、高濃度拡散層14を形成する。

【0047】次に、図8の(B)に示したように、シリコンが露出している拡散層14の表面と、ゲート電極の第2層目のタングステン膜10の表面に第3層目のタングステン膜15を選択的に成長させ、拡散層14の低抵抗化をはかる。このように、ゲート電極は3層のタングステン膜6、10、15から構成される。

【0048】次に、図8の(C)に示したように、基板全面を層間絶縁膜16で被い、さらに、公知のリソグラフィ技術およびドライエッチ技術を用いて、拡散層14の表面やゲート電極の表面のタングステン15に達するコンタクト孔を開口する。

【0049】最後に、コンタクト孔を公知のプラグ技術を用いてプラグ金属17で埋め戻した(具体的にはタングステンを選択成長させた)後に、アルミを主体とする金属で配線層18を形成すれば、図9に示した構造の半導体装置、すなわち図1に示した半導体装置が得られる。なお、配線が複数層に渡って必要な場合には、層間絶縁膜の形成、コンタクト孔の開口、その埋め戻し、および、配線層の形成とを繰り返せばよい。また、本実施例では、n型のMOSFETを形成する場合について説明したが、半導体基板1や不純物領域4、11、12、14の導電型を逆にすれば、p型のMOSFETを形成できることは云うまでもない。更に、本実施例では、ゲート電極は3層のタングステン膜からなり、第1層目はゲート絶縁膜との接着性に優れたスパッタ法で堆積したタングステン膜6であり、第2層目はスパッタタングステンの表面に選択的に成長させたタングステン膜10であり、第3層目は拡散層14の表面にタングステンを成長させた際にゲート電極の第2層目のタングステン膜上に成長したタングステン膜15であるが、ソース・ドレインの抵抗が問題とならない場合には、勿論、第3層目のタングステン膜の代わりにチタンシリサイドを形成してもよい。なお、ゲート電極の第2層目のタングステン膜上にはチタンシリサイドを形成しないように、図8の(A)の後の工程で酸化膜を堆積して公知のホトリソグラフィ技術により拡散層14上の酸化膜だけに孔を開けてチタンシリサイドを形成してもよい。その場合は、ゲート電極は2層のタングステン膜から構成される。

【0050】<実施例2>前記実施例1では、図6の(C)に示したように、ゲート電極を構成する選択成長で形成した第2層目のタングステン膜10の下層には、ゲート酸化膜5に接触するタングステン膜6があり、しかも、これが基板全面を被っている。この最下層のタングステン膜6は、実施例1の場合、選択成長させた第2層目のタングステン膜10の直下のみを残して除去していたが、側壁絶縁膜の形成技術を用いることで、公知のゲートオーバーラップドレイン構造を作ることができる。

【0051】以下、図10及び図11を用いて、実施例2としてゲートオーバラップドレイン構造を有する本発明に係る半導体装置およびその製造方法を説明する。図1010及び図11は、本発明に係る半導体装置の製造工程の主要工程順に沿って示した断面構造図である。なお、本実施例でも、説明の便宜上、n型のMOSFETを一例に説明する。

【0052】先ず、実施例1における図5から図7の(B)までの製造工程を経た基板、すなわち、図10の(A)に示したように、下層のタングステン膜6上に選択成長により形成した第2層目のタングステン膜10と局所パンチスルーストッパ11を有する基板を用意する。

【0053】そして、図10の(B)に示したように、下層のタングステン膜6の一部を除去する前に、低濃度拡散層12をイオン打ち込みで形成する。条件は実施例1と同じであり、不純物はリンもしくはヒ素を用い、打込み量は1×1013〜1×1014/cm2である。

【0054】次に、図10の(C)に示したように、ゲート電極となる第2層目のタングステン膜10の側壁に公知の側壁絶縁膜形成技術を用いて側壁絶縁膜13を形成し、さらに、この側壁絶縁膜13をマスクにして下層のタングステン膜6を除去する。その後、リンもしくはヒ素を1×1015/cm2以上打込み、高濃度拡散層14を形成する。このようにすることによって、下層のタングステン膜6のゲート長方向の寸法は上層のタングステン膜10よりも広くなり、しかも、その下の基板領域に形成された低濃度の拡散層12上に張り出した構造とすることができる。なお、第1層目のタングステン膜6を除去する際に、第2層目のタングステン膜10の表面の一部も同時に除去されて、図に示したように、側壁絶縁膜13の角が残る。

【0055】本実施例に示したMOSFETの場合は、低濃度拡散層12がゲート電極を構成する第1層目のタングステン膜6の張出し部分と重なることにより、第1層目のタングステン膜6と低濃度拡散層12との重なりが少ない実施例1に示したMOSFETの場合に比べ、LDD構造の寄生抵抗の増加が押さえられるので、電流が増加する利点がある。このような構造はゲートオーバーラップドレイン構造と呼ばれ、すでに公知の技術であるが、本発明のMOSFETでは、ゲート電極となる第2層目のタングステン膜10を選択成長を用いて形成しているので、側壁絶縁膜13の形成工程を加えるだけで、ゲートオーバーラップドレイン構造を簡単に実現することができる。

【0056】次に、図10の(D)に示したように、側壁絶縁膜13’を再び形成し、拡散層14の表面とタングステン膜10の表面にタングステン膜15を成長させる。側壁酸化膜13’は、張り出した第1層目のタングステン膜6と拡散層14上のタングステン膜15の短絡を防ぐ役目を果たす。また、拡散層14の表面とゲート電極となる第2層目のタングステン膜10の表面への第3層目のタングステン膜15の選択成長は、実施例1とまったく同じ条件で行えばよい。このとき、図10の(C)に示したように、残っている側壁絶縁膜13の角は第2層目のタングステン膜10の表面より飛び出しているために、この角が第3層目のタングステン膜15を選択成長した時に、拡散層14上と第2層目のタングステン膜10上に成長した第3層目のタングステン15がつながってしまうのを効果的に抑制する。

【0057】最後に、実施例1と全く同様に、コンタクト孔を公知のプラグ技術を用いてプラグ金属17で埋め戻した(具体的にはタングステンを選択成長させた)後に、アルミを主体とする金属で配線層18を形成すれば、図11に示した構造の半導体装置、すなわち図2に示した半導体装置が得られる。

【0058】また、本実施例においても、n型のMOSFETを形成する場合について説明したが、実施例1と同様に半導体基板や不純物領域の導電型を逆にすれば、p型のMOSFETを形成できることは言うまでもない。

【0059】<実施例3>図12乃至図14を用いて、本発明に係る半導体装置およびその製造方法の第3の実施例を詳細に説明する。図12乃至図14は、本発明に係る半導体装置の製造方法を示す断面構造図であり、主要工程順に順を追って示したものである。なお、説明の便宜上、ここではn型のMOSFETを一例に説明する。

【0060】まず、実施例1の図5の(A)において説明した工程を経た基板、すなわち、図12の(A)に示したように、選択酸化法を用いて形成した素子間分離酸化膜2と酸化膜3を有する半導体基板を用意する。

【0061】次に、図12の(B)に示したように、ゲート酸化膜5を成長させた後、多結晶シリコン膜6’をCVD法を用いて堆積する。チャネル長0.1〜0.2μmのMOSFETを形成する場合、ゲート酸化膜5の膜厚は約5〜7nmであり、多結晶シリコン膜6’の膜厚は20〜40nm程度である。そして、窒化膜7をプラズマCVD法を用いて約200nm堆積した後、リソグラフィ技術を用いて溝を形成し、この溝の側壁に側壁酸化膜9を形成する。なお、ゲート酸化膜5を成長させる前に、酸化膜3は表面を洗浄する際に除去しておく。

【0062】次に、図12の(C)に示したように、露出している多結晶シリコン膜6’の表面をタングステン膜6に置換する。具体的には、WF6ガスを供給するとシリコンとの反応が起こり、シリコンは揮発性のガスであるSiF4となって除去されてW(タングステン)が残る。WF6ガスは酸化膜とは反応しないので、溝側壁の側壁酸化膜9はそのままであり、また、多結晶シリコン膜6’との置換反応が進んでも、ゲート酸化膜5がタングステン膜6と反応するということもない。

【0063】次に、図12の(D)に示したように、置換した第1層目のタングステン膜6の表面に、実施例1の図6の(C)で説明した方法により、第2層目のタングステン膜10を選択成長させる。

【0064】次に、図13の(A)に示したように、側壁酸化膜9を除去後、ゲート電極となる第2層目のタングステン膜10と窒化膜7との隙間を通してイオン打込みを行い、パンチスルーストッパ11を形成する。本実施例の場合、不純物イオンは多結晶シリコン膜6’を通して打ち込まれる。

【0065】次に、図13の(B)に示したように、溝が形成されていた窒化膜7を除去し、更に基板全面を被っていた多結晶シリコン膜6’をエッチングにより除去する。これまでの実施例では、第1層目のタングステン膜6を除去していたが、本実施例では、多結晶シリコン膜6’が除去される。多結晶シリコン膜6’は下地のゲート酸化膜5との間に選択比を確保し易いという特徴がある。これまでの実施例でも、除去される第1層目のタングステン膜6を薄くすることで、ゲート酸化膜5上でのタングステン膜の加工を行ってきたが、本実施例では、よりエッチングし易い多結晶シリコン6’を用いることで、ゲート電極加工上の問題がなくなる利点もある。

【0066】以下、図13の(C)から図14までの工程は、それぞれ実施例1で図7の(D)から図9までを用いて説明した方法とまったく同じ方法により形成できるので、詳細な説明は省略する。

【0067】本実施例ではパンチスルーストッパ11は多結晶シリコン膜6’を通して形成し、その後、その多結晶シリコン膜6’をタングステン膜6に置換するという方法を用いたことにより、前記実施例1及び実施例2のように、ゲート酸化膜5に接したタングステン膜6を通してイオン打込みを行い、パンチスルーストッパ11を形成する場合に比べて、基板表面がタングステンによって汚染されるいわゆる重金属汚染の可能性がなくなったので、汚染によるキャリア寿命の低下や接合リークの増加を招くおそれがなくなり、信頼性が向上する。なお、多結晶シリコン膜6’をゲート電極の一部としてそのまま使用することも可能であるが、従来技術の問題点のひとつとして指摘したように、表面チャネル型の微細なMOSFETを実現するためには、ゲート電極の導電型を変えなければならないという工程数の増加する問題があるので、ここでは、タングステン膜6に置換した例について説明した。

【0068】<実施例4>図15乃至図16を用いて、本発明に係る半導体装置およびその製造方法の第4の実施例を詳細に説明する。図15乃至図16は、本発明に係る半導体装置の製造方法を示す断面構造図であり、主要工程順に順を追って示したものである。なお、本実施例は実施例1で説明した半導体装置を用いて、図3に示したCMOSを形成した場合の例である。

【0069】既に述べてきたように、本発明の半導体装置は、拡散層などの導電型を変えるだけで、容易にn型およびp型のMOSFETを作ることができる。この点は、従来構造のMOSFETとまったく同じである。従って、CMOSを形成するためには、従来と同じように、導電型の異なる領域を有する基板を用意し、交互にn型とp型の半導体装置を作って行けばよい。

【0070】まず、図15の(A)に示したように、半導体基板1に導電型の異なる領域21と22を有し、かつ、素子分離酸化膜2が成長されている基板を用意する。ここでは、説明の便宜上、領域21をn型MOSFETが形成されるp型領域、領域22をp型MOSFETが形成されるn型領域とする。

【0071】次に、図15の(B)に示したように、それぞれの領域21、22に対して、素子分離特性を改善するためのイオン打ち込みをレジスト膜8をマスクにして交互に行い、不純物領域41、42を形成する。p型領域21の不純物領域42に対してはボロンが導入され、n型領域22の不純物領域41に対してはリンが導入される。

【0072】次に、図15の(C)に示したように、ゲート酸化膜5を全面に成長させ、さらに、ゲート電極の一部となる第1層目のタングステン膜6を形成し、実施例1において図6の(A)〜(C)を用いて説明したように、窒化膜7への溝の形成、側壁酸化膜9の形成、第2層目のタングステン膜10の成長を行う。

【0073】そして、図15の(D)に示したように、側壁酸化膜9を除去し、パンチスルーストッパ11、11’の形成を行う。パンチスルーストッパ11はボロンのイオン打ち込みで形成し、パンチスルーストッパ11’はヒ素のイオン打ち込みで形成する。

【0074】次に、図16の(A)に示したように、窒化膜7を加熱したリン酸溶液で除去後、基板表面を被う第1層目のタングステン膜6をドライエッチ法により除去し、図16の(B)に示したように、低濃度拡散層12、12’、側壁酸化膜13、高濃度拡散層14、14’を形成する。実施例1で図7の(D)から図8の(A)までを用いて説明した方法により形成できるので詳細な説明は省略する。両MOSFETにおいて、導電型が異なるのは言うまでもない。

【0075】そして、図16の(C)に示したように、拡散層14の表面とゲート電極となる第2層目のタングステン膜10の表面での第3層目のタングステン膜15の成長を行い、層間絶縁膜16で覆った後、層間絶縁膜16にコンタクト孔を開け、最後に、図16の(D)に示したように、コンタクト孔をプラグ金属17(具体的にはタングステン)で埋め戻した後、アルミを主体とする金属で配線18を形成してCMOS、すなわち図3で示したCMOSが完成する。なお、第3層目のタングステン膜15から配線18を形成するまでは、実施例1で図8の(B)から図9までを用いて説明した方法によって形成できるので、詳細な説明は省略した。

【0076】以上、本発明の好適な実施例について説明したが、本発明は前記実施例に限定されることなく、例えば、高融点金属材料としてタングステンを用いたが、チタンなど他の材料を用いてもよく、本発明の精神を逸脱しない範囲内で種々の設計変更をなし得ることは勿論である。

【0077】

【発明の効果】以上、前述した実施例から明らかなように、本発明に係る半導体装置およびその製造方法によれば、タングステンという抵抗が低く、かつ、熱処理にも耐えることができる高融点金属材料を、ゲート酸化膜が非常に薄いMOSFETのゲート電極として使用することが可能となる。ゲート電極に、高融点金属であるタングステンを使用できることにより、従来のシリサイド化したゲート電極の抵抗がシート抵抗で10Ω/□であるのに対して、ゲート電極抵抗を1Ω/□と低減でき、動作速度を向上させることができる。

【0078】また、タングステンを用いることで、従来の多結晶シリコンゲートを用いてCMOSを形成する場合のように、導電型の異なるゲート電極を形成する必要がなくなり、ゲート電極形成工程の工程数の削減が可能となる。

【0079】更に、拡散層の表面とゲート電極の表面にタングステンを成長させる製造方法は、シリサイド化する方法と比べて、拡散層の高濃度不純物領域を侵食することがないために、拡散層の抵抗をよりいっそう低下させる利点もある。

【0080】また更に、溝を用いたゲート電極の形成は、パンチスルーストッパを局所的に形成することを可能とする。このため、パンチスルーストッパによる寄生の接合容量が大幅に低減する。例えば、チャネル長が0.2ミクロン程度のMOSFETでは、パンチスルーストッパのピーク濃度は1018/cm3弱であり、接合容量は2fF/μm2程度になるのに対して、本発明に係る局所パンチスルーストッパ構造を有するMOSFETでは、接合容量は1/10程度に低減する。この接合容量の低減の結果、ゲート抵抗の低下と相俟って、素子性能の向上に多いに寄与し、信号の伝達速度の向上を図ることができる。

【0081】更に、この局所パンチスルーストッパは、ゲート電極端付近の領域に局在しており、ゲート電極の直下は低濃度の状態に保たれている。このため、電子や正孔が流れるチャネル領域における、垂直方向電界(基板に対して)が小さく、チャネル領域全体にパンチスルーストッパが形成されている従来構造のMOSFETに比べて、高い移動度が実現され、電流が大きくなる効果がある。

【0082】また更に、本発明に係る半導体装置は、製造工程をわずかに追加もしくは変更することで、ゲートオーバーラップ構造にしたり、ゲート電極寸法をリソグラフィ限界以下にすることができ、これらも素子性能の向上に寄与するところ大である。

【0083】以上述べてきたように、局所パンチスルーストッパ構造は、接合容量を大幅に低減しながら、電子や正孔の移動度が低下するのを抑えることができ、タングステンゲート電極によってゲート抵抗は減少する。また、拡散層上で成長させたタングステンは、拡散層抵抗を減少させる。さらに、タングステンゲートは、ゲート電極形成工程を単純にし、その結果、低コストで、かつ、高性能なMOSFETを実現でき、ひいては、LSIの高性能化を達成することができる。

【図面の簡単な説明】

【図1】本発明に係る半導体装置の第1の実施例を示す断面図。

【図2】本発明に係る半導体装置の第2の実施例を示す断面図。

【図3】本発明に係る半導体装置によるCMOSの実施例を示す断面図。

【図4】従来の半導体装置におけるCMOSの断面図。

【図5】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図6】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図5R>5の次の工程を示す図。

【図7】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図6R>6の次の工程を示す図。

【図8】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図7R>7の次の工程を示す図。

【図9】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図8R>8の次の工程を示す図。

【図10】本発明に係る半導体装置の第2の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図11】本発明に係る半導体装置の第2の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図10の次の工程を示す図。

【図12】本発明に係る半導体装置の第3の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図13】本発明に係る半導体装置の第3の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図12の次の工程を示す図。

【図14】本発明に係る半導体装置の第3の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図13の次の工程を示す図。

【図15】本発明に係る半導体装置の第4の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図16】本発明に係る半導体装置の第4の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図15の次の工程を示す図。

【符号の説明】

1…半導体基板

2…素子分離酸化膜

3…酸化膜

4、41、42…不純物領域

5…ゲート酸化膜

6…タングステン膜

6’…多結晶シリコン膜

7…窒化膜

8…レジスト膜

9…側壁酸化膜

10…タングステン膜

11、11’…パンチスルーストッパ

12、12’…低濃度拡散層

13…側壁絶縁膜

14、14’…高濃度拡散層

15、15’…タングステン膜

16…層間絶縁膜

17…プラグ金属

18…配線金属

21…p型領域

22…n型領域

30、30’…ゲート電極

35、35’…シリサイド膜

【0001】

【産業上の利用分野】本発明は半導体装置およびその製造方法に係り、特にゲート電極抵抗の低抵抗化と接合容量の低減により高性能化を図った金属−酸化膜−半導体型の電界効果トランジスタを有する(Metal Oxide Semiconductor Field Effect Transistor;以下、MOSFETと略す)半導体装置とその製造方法に関する。

【0002】

【従来の技術】シリコンを用いた集積回路の代表例であるダイナミック・ランダム・アクセス・メモリは、現在、0.8ミクロンの技術を用いて、4メガビットの量産が行われている。また、次世代の0.5ミクロン技術を使用する16メガビットの量産化も始まっている。今後も、微細加工技術の進歩と相俟って、半導体素子が縮小され、集積度の向上と高性能化が実現されるのは間違いない。

【0003】しかし、チャネル長がハーフミクロン以下の領域になると、MOSFETのチャネル領域を流れる電子もしくは正孔は、速度が完全に飽和した状態になっており、このため、微細化しても、これまでのようには、チャネル長に反比例して電流が大きくなることは期待できない。また、微細化を進めるために、基板濃度が上昇しており、その結果、電子もしくは正孔の移動度が減少している。さらには、基板濃度の増加は接合容量の増加を招き、ゲート電極の微細化はゲート抵抗の増加を招く。以上のような要因が、MOSFETの微細化による性能向上という利点を損なう原因となる。

【0004】このような課題が発生するMOSFETの構造的問題点を、図4を用いて説明する。図4は、従来技術により作製したチャネル長がハーフミクロン以下の微細なMOSFETを有する半導体装置の断面図であり、同一半導体基板上に導電型の異なるMOSFETが混在する相補型の半導体装置(CMOS;Complementary MOS)を示している。図4において、参照符号1は半導体基板を示し、半導体基板1にはp型領域21とn型領域22が形成されており、p型領域21にチャネル長がハーフミクロン以下のn型MOSFETが作製され、n型領域22にチャネル長がハーフミクロン以下のp型MOSFETが作製される。

【0005】チャネル長がハーフミクロン以下の従来のMOSFETに特徴的な構造は、パンチスルーストッパ31、31’と、導電型の異なるゲート電極30、30’と不純物領域12、12’,14、14’およびゲート電極30、30’を被うシリサイド膜35、35’とを有することである。

【0006】パンチスルーストッパ31はp型領域21と同じ導電型で高濃度な不純物領域であり、パンチスルーストッパ31’はn型領域22と同じn型であるがより不純物濃度が高い領域である。パンチスルーストッパ31、31’は、それぞれ不純物領域12、12’の接合から広がる空乏層がチャネル領域に張り出すのを防ぎ、接合間の干渉によるリーク電流の発生を抑える。このパンチスルーストッパ31、31’は、不純物領域14、14’の接合界面の近傍に濃度のピークが位置するように、不純物濃度分布が設定されている。

【0007】不純物領域14、14’上やゲート電極30、30’上のシリサイド膜35、35’は、これらの導電層の抵抗を下げる効果がある。不純物領域14、14’の接合深さはMOSFETの微細化に伴って浅くなっており、同じ不純物濃度であっても、抵抗は増加する。これまでは、チャネル抵抗に比べて不純物領域14、14’の拡散抵抗は十分小さかったので、MOSFETの電流には直接的に影響を及ぼすことはなかった。しかし、チャネル長の減少とともにチャネル抵抗も小さくなるが、不純物領域14、14’の拡散抵抗は増加するために、これらの抵抗が同程度の大きさになってくる。その結果、不純物領域14、14’による電圧降下が顕著に見え始め、MOSFETの本来の性能が引き出せなくなる。これを防ぐために、シリサイド膜35、35’が用いられる。シリサイド膜35、35’は、公知のシリサイド技術を用いることにより、ゲート電極30、30’と不純物領域14、14’上の両方に形成することができる。

【0008】また、導電型の異なるゲート電極30、30’を用いるのは、n型MOSFETとp型MOSFETの両方を、以下に述べるように、表面チャネル型にする必要があるためである。すなわち、これまでp型MOSFETは、n型MOSFETと同様に、ゲート電極にn型の不純物を高濃度で含む多結晶シリコンを用いてきた。しかし、p型MOSFETでは、基板との仕事関数差が小さいために、MOSFETをオンさせるためのゲート電圧(しきい電圧)が大きくなる。そこで、チャネル領域に、基板とは導電型の異なる不純物(具体的にはボロン)を導入し、表面近傍をp型にして、しきい電圧の調整を行ってきた。このような不純物分布になると、正孔は基板の内部を流れるようになるので、埋め込みチャネル型MOSFETと呼ばれている。埋め込みチャネル型のMOSFETでは、電子や正孔がゲート酸化膜界面での散乱を受ける確率が低くなるために、表面チャネル型に比べて移動度が大きいが、チャネル領域がゲート電極から離れているために、接合間の干渉が起こり易くリーク電流も流れ易い問題点があった。しかし、この問題点は、p型MOSFETのゲート電極をp型の多結晶シリコンとすることにより、n型MOSFETと同様の表面チャネル型となるので、解決することができる。

【0009】このように、従来から様々な工夫を加えることでMOSFETを微細化し、性能向上を図ってきた。なお、前述したようなパンチスルーストッパ、シリサイド膜、異なる導電型の多結晶シリコンゲートを有する相補型の半導体装置については、例えば、テクニカル・ダイジェスト アイ・イー・イー・イー インターナショナル・エレクトロン・デバイセズ・ミーティング 1993年 第127頁から130頁(Technical Digest. IEEE International Electron Devices Meeting, pp.127-130, 1993)に記載されている。

【0010】

【発明が解決しようとする課題】しかしながら、前述した従来の半導体装置における対策は、さらに微細なMOSFETを実現するには、依然として以下に述べるような、性能向上を阻害し、製造工程を複雑にする側面を合わせ持っている。

【0011】例えば、短チャネル効果に伴うリーク電流の発生を抑制するために設けたパンチスルーストッパ31、31’は、チャネル領域を高濃度化するために、電子や正孔の移動度を減少させ、ひいては、電流の減少を招いてしまう。また、チャネル領域の高濃度化は接合容量を増加させるので、信号の遅延時間が長くなってしまう問題がある。これまでは、このような問題は寸法の微細化による電流の増加でカバーしてきたが、前述したように、電子や正孔の速度は飽和しており、チャネル長を小さくしても必ずしも電流の増加が期待できない状況では、移動度の減少や接合容量の増加は、性能の低下を招くだけである。

【0012】さらに、シリサイドを表面近傍に成長させたゲート電極30、30’にも、微細化に伴って低抵抗化に限界が現れて来る。これは、ゲート電極の寸法が小さくなると共に、シリサイド反応が微細なパターンにおいて抑制されるからである。ゲート電極よりは遥かに面積の大きな接合でも、別の意味でシリサイド化の限界がある。それは、接合が浅くなるのに伴って、十分に厚いシリサイド層を形成することができなくなるからである。また、シリサイド膜35、35’は、半導体基板内部に形成されるために、不純物を高濃度で含む領域がシリサイド化する。このため、残された不純物領域は不純物濃度が低い領域であり、不純物領域の低抵抗化にとってシリサイド化は必ずしも好ましいことではない。

【0013】従って、この不純物領域及びゲート電極の高抵抗化の問題に加えて、従来の多結晶シリコンを用いるゲート電極構成では、表面チャネル型の相補型MOSFETを形成するために導電型の異なる多結晶シリコンを使用しなければならず、製造工程が増加するという問題点があった。このゲート電極形成工程の増加は、結果としてLSIのコスト上昇および歩留まりの低下を招いていた。

【0014】そこで、本発明の目的は、不純物領域及びゲート電極の低抵抗化により高性能化を図った微細なMOSFETを有する半導体装置を提供すること、並びに、不純物領域及びゲート電極の低抵抗化を図ることができると共にゲート電極形成工程数の低減を図ることができる半導体装置の製造方法を提供することにある。

【0015】

【課題を解決するための手段】上記目的を達成するために、本発明の請求項1に係る半導体装置は、素子間分離用絶縁膜で囲まれた半導体基板の第1の領域に、所定の間隔で形成された該第1の領域の導電型とは導電型が異なる一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とを具備する電界効果型の半導体装置において、上記ゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記ゲート電極の上記2つの側壁絶縁膜のそれぞれの下の第1の領域に、ゲート幅と同じ長さで局在する上記第1の領域と同じ導電型の2つの高濃度不純物領域を有するよう構成することを特徴とする。具体的に、実施例に対応する図1を用いて説明すれば、本発明に係る半導体装置は、タングステン膜6、10、15から成る3層構造のゲート電極と、このゲート電極の両端付近のゲート酸化膜下の半導体基板領域にゲート幅と同じ長さで局在する半導体基板1と同じ導電型の高濃度不純物領域、すなわちゲート電極端の直下に存在し不純物領域12、14とは僅かな領域だけで接するパンチスルーストッパ11を有するように構成されている。なお、図1において、参照符号2は素子分離酸化膜、4は素子分離特性を向上させるための高不純物濃度層、5はゲート絶縁膜、13はゲート電極の側壁絶縁膜、16は層間絶縁膜、17はコンタクト孔を埋めるプラグ金属、そして、18は配線金属である。

【0016】また、請求項2に係る半導体装置は、素子間分離用絶縁膜でそれぞれ囲まれた半導体基板の第1の領域および該第1の領域の導電型と異なる第2の領域に、それぞれの領域の導電型とは導電型が異なると共に所定間隔で形成された一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とをそれぞれ具備する相補型の電界効果型半導体装置において、上記それぞれのゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記それぞれのゲート電極の上記2つの側壁絶縁膜の下のそれぞれの第1および第2の領域に、ゲート幅と同じ長さで局在する上記それぞれの領域と同じ導電型の2つの高濃度不純物領域を有するように構成することを特徴とする。この相補型の本発明に係る半導体装置を具体的に図3を用いて説明すれば、図1に示した半導体装置をCMOSの場合に適用したものであり、同一半導体基板1上の素子間分離用絶縁膜2で囲まれた半導体基板1に、それぞれ導電型が異なる第1及び第2の領域すなわちウエル領域21、22、ソース、ドレイン領域である高濃度の拡散による不純物領域(以下、拡散による不純物領域を拡散層と呼ぶ)14、14’、素子分離特性を向上させる高濃度層41、42、それぞれのゲート電極の両端付近の直下に局在するパンチスルーストッパ11、11’を有している。

【0017】前記半導体装置において、ゲート電極は高融点金属とすることができ、高融点金属の中でもタングステンであれば好適である。

【0018】さらに、前記半導体装置のいずれかにおいて、少なくとも2層構造からなるゲート電極の、ゲート絶縁膜に接触している最下層のゲート電極は、上層のゲート電極より張り出すよう構成することができる。このとき、最下層ゲート電極の張り出した部分の下の領域に、前記一対の不純物領域と同じ導電型で、かつ、一対の不純物領域の不純物濃度よりも低い不純物濃度の拡散による不純物領域を有すれば更に好適である。具体的に図2を用いて説明すれば、ゲート電極を構成する第1層目のタングステン膜6が第2層目のタングステン膜10より張り出した構成となっており、更に張り出した第1層目のタングステン膜6の下の基板中に低濃度の拡散層12が形成されている。

【0019】本発明に係る半導体装置の製造方法は、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、この絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程10と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程11と、工程10で残した第1及び第2の導電膜の側壁に側壁絶縁膜を形成する工程12と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程13と、工程13で形成した不純物領域の表面および工程10で残した導電膜の表面に第3の導電膜を成長させる工程14と、半導体基板表面を層間絶縁膜で被う工程15と、層間絶縁膜にコンタクト孔を開口する工程16と、配線層を形成する工程17とからなることを特徴とする。

【0020】また、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程10と、工程6で形成した第2の導電膜の側壁に側壁絶縁膜を形成する工程11と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程12と、工程12で残した導電膜の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程12で残した導電膜の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18とからなる半導体装置の製造方法とすることもできる。

【0021】更に、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に多結晶シリコン膜を形成する工程2と、多結晶シリコン膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して多結晶シリコン膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した多結晶シリコン膜を第1の導電膜に置換する工程6と、第1の導電膜の表面に第2の導電膜を成長させる工程7と、側壁絶縁膜を除去する工程8と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程9と、絶縁膜を除去する工程10と、工程2で形成した多結晶シリコン膜と並びに工程7で形成した第2の導電膜のゲート電極になる部分以外の導電膜とを除去する工程11と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程12と、工程11で形成したゲート電極の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程11で形成したゲート電極の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18とからなる半導体装置の製造方法であっても良い。

【0022】前記半導体装置の製造方法において、第1乃至第3の導電膜は高融点金属の膜とすることができ、高融点金属の中でもタングステンであれば好適である。或いは、第1及び第2の導電膜をタングステン膜とし、第3の導電膜をチタンからなる膜としても良い。

【0023】

【作用】本発明に係る半導体装置によれば、ゲート電極の両端付近の半導体基板領域にゲート幅と同じ長さで局在する半導体基板領域と同じ導電型の高濃度不純物領域、すなわち、ゲート電極端の直下に存在する局所パンチスルーストッパ11,11’は、ソース及びドレインとなる拡散層と僅かな領域だけで接するため、従来のパンチスルーストッパ31,31’と比べて接触部分が少なくなり、接合容量が大幅に低減する。また、この局所パンチスルーストッパは、ゲート電極の端に局在するのでゲート電極下の大部分の領域は低不純物濃度の状態に保たれたままにでき、電子や正孔が流れるチャネル領域における垂直方向電界(基板に対して)が小さい。従って、チャネル領域全体にパンチスルーストッパが形成される従来の構造に比べて、移動度が高くでき電流が大きくなる。

【0024】少なくとも2層構造で構成されるゲート電極は、高融点金属を用いた構造であるため、従来のシリサイド化したゲート電極に比べてゲート電極抵抗が減少する。特に、高融点金属としてタングステンを用いれば、従来のシリサイド化したゲート電極のシート抵抗10Ω/□に対して1Ω/□と1/10に低減する。タングステンのゲート電極を用いること自体は、従来構造のMOSFETでも可能であるが、一般的に、タングステンのような金属の加工を、ゲート絶縁膜のように薄い絶縁膜(具体的には5nm程度)の上で行うのは非常に困難であり、通常では、ゲート絶縁膜が完全に除去されて基板まで削れてしまう。本発明では、実施例において詳細に説明するように、実際に加工するタングステンの膜を薄くすることで、この問題を解決している。

【0025】また、ソース及びドレイン拡散層の電極は高融点金属を用いた構造としたため、従来のシリサイド化電極を用いる構造の場合のようにシリサイド化によって拡散層の高不純物濃度領域を侵食することがなく、拡散層の低抵抗化が図れる。

【0026】さらに、少なくとも2層構造で構成されるゲート電極の最下層のゲート電極を上層のゲート電極より張り出した構造は、低濃度拡散層と重なることによりゲートオーバーラップドレイン構造を構成し、抵抗の増加を抑えると共に、ホットキャリアの発生を抑制するのでデバイスの信頼性が向上する。

【0027】本発明に係る半導体装置の製造方法によれば、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成し、次いでゲート絶縁膜上に第1の導電膜を形成し、第1の導電膜上に絶縁膜を形成した後、この絶縁膜のゲート電極を形成する部分に溝を形成して第1の導電膜の表面の一部を露出させ、溝の側壁に側壁絶縁膜を形成して露出した第1の導電膜上に第2の導電膜を形成し、側壁絶縁膜を除去し、この除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入することにより、ゲート電極の両端付近の半導体基板領域にゲート幅と同じ長さで局在する半導体基板領域と同じ導電型の高濃度不純物領域、すなわち、ゲート電極端の直下に存在する局所パンチスルーストッパを形成することができる。

【0028】また、上記パンチスルーストッパ形成後、絶縁膜を除去し、第1の導電膜及び第2の導電膜のゲート電極となる部分を残してこれら導電膜を除去し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入した後、ゲート電極となる第1及び第2の導電膜の側壁に側壁絶縁膜を形成し、更に前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、この不純物領域の表面と前記残した第1及び第2の導電膜の表面に第3の導電膜を成長させることにより、少なくとも2層のゲート電極、この場合は3層構造のゲート電極が形成されると同時に、ソースおよびドレインの拡散上の電極もゲート電極を構成する第3の導電膜で形成される。

【0029】或いは、上記製造方法において、パンチスルーストッパ形成後、絶縁膜を除去し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入した後、第2の導電膜の側壁に側壁絶縁膜を形成し、次いで第1及び第2の導電膜のゲート電極となる部分を残してこれら導電膜を除去し、この残した導電膜の側壁に側壁絶縁膜を形成し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、この不純物領域の表面と前記残した第1及び第2の導電膜の表面に第3の導電膜を成長させることにより、少なくとも2層のゲート電極、この場合は3層構造のゲート電極で第1層が上層より張り出したゲート電極が形成されると同時に、ソースおよびドレインの拡散上の電極がゲート電極を構成する第3の導電膜で形成される。

【0030】更にまた、請求項9に係る半導体装置の製造方法によれば、素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成し、次いでゲート絶縁膜上に多結晶シリコン膜を形成した後、多結晶シリコン膜上に絶縁膜を形成し、この絶縁膜のゲート電極を形成する部分に溝を形成して多結晶シリコン膜の表面の一部を露出させ、溝の側壁に側壁絶縁膜を形成した後、露出した多結晶シリコン膜を第1の導電膜に置換し、第1の表面に第2の導電膜を成長させた後、側壁絶縁膜を除去し、この除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入することによってパンチスルーストッパを形成する。この後、絶縁膜を除去し、更に多結晶シリコン膜と並びに第2の導電膜のゲート電極になる部分以外の導電膜とを除去し、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、ゲート電極になる第1及び第2の導電膜の側壁に側壁絶縁膜を形成し、次いで前記半導体基板領域中に半導体基板領域とは導電型の異なる領域を作るために不純物を導入し、この不純物領域の表面と第1及び第2の導電膜で構成されるゲート電極の表面に第3の導電膜を成長させることにより、少なくとも2層のゲート電極、この場合は3層構造のゲート電極が形成されると同時に、ソース及びドレインの拡散上の電極もゲート電極を構成する第3の導電膜で形成される。

【0031】

【実施例】以下、本発明に係る半導体装置およびその製造方法の好適な幾つかの実施例につき、図5乃至図16を用いて詳細に説明する。

【0032】<実施例1>図5乃至図9は、本発明に係る半導体装置およびその製造方法の一実施例を示す断面構造図であり、主要工程順に順を追って示したものである。なお、説明の便宜上、ここではn型のMOSFETを一例に説明する。

【0033】まず、図5の(A)において、参照符号1は半導体基板を示し、この半導体基板1に対し公知の選択酸化法を用いて素子分離酸化膜2を成長させる。具体的には、p型の半導体基板1の表面に20nm程度の酸化膜3を成長させ、さらに、その上に窒化膜(不図示)を公知の低圧気相成長法により堆積した後に、この窒化膜を所望の形状に加工し、その後、水蒸気を含んだ1100℃の雰囲気で30分間酸化する。このとき、窒化膜で被われていない領域にのみ酸化膜2が成長する。そして、酸化のマスクとなった窒化膜を180℃程度に加熱したリン酸溶液で除去することにより、図5の(A)の構造が得られる。なお、成長させた酸化膜2の厚さは約300nmである。

【0034】次に、酸化膜2を成長させただけでは十分な素子分離特性が得られないので、図5の(B)に矢印で示したように、半導体基板全面に公知のイオン打ち込み法を用いてイオン打ち込みを行い、基板1と同じ導電型の不純物領域4を形成する。具体的には、ボロンを100KeVで5×1013/cm2打ち込み、不純物濃度のピークが酸化膜2と基板1の界面近傍に位置するように条件を設定する。酸化膜2と基板1ではイオンの阻止能力が違うために、図に示したように、酸化膜2がないところでは、不純物領域4のピーク位置が深くなる。ここで、選択酸化の際の酸化膜3を残したままでイオン打込みを行うのは、イオン打ち込みの際に汚染が基板内部に入るのを防ぐためである。勿論、選択酸化後に酸化膜3を除去して新たな酸化膜を形成してこれを用いても良い。なお、基板1がn型でp型MOSFETを形成する場合は、通常、リンをイオン打ち込みする。

【0035】次に、図5の(C)に示したように、ゲート酸化膜5を成長させる。具体的には、チャネル長0.1〜0.2μmのMOSFETを形成する場合、ゲート酸化膜5の膜厚は約5〜7nmであり、酸化温度は800℃である。なお、このゲート酸化膜5の成長の前に、イオン打ち込みに伴う表面の汚染を除去するための洗浄を行ったり、打ち込まれたイオンを活性化するための熱処理を行うことは言うまでもない。

【0036】次に、図5の(D)に示したように、ゲート電極の一部となる最下層のタングステン膜6を堆積する。この高融点金属の一つであるタングステンの膜厚は、後述するように、加工に際してゲート酸化膜5を削らないようにするために、チャネル長0.1〜0.2μmのMOSFETを形成する場合で20〜40nm程度と薄膜にする。また、ゲート酸化膜5との接着性を良くするために、タングステン膜6の堆積には公知のスパッタ法を用いる。

【0037】次に、図6の(A)に示したように、タングステン膜6の上に窒化膜7を堆積する。本実施例では、プラズマによって反応を促進させる、プラズマCVD(Chemical Vapor Deposition)法を用いて、約200nmの窒化膜を堆積させた。そしてさらに、公知のリソグラフィ技術を用いて、窒化膜7上のレジスト膜8に溝状のパターンを形成する。

【0038】次に、図6の(B)に示したように、上記レジスト膜8をエッチングマスクにして公知のドライエッチ技術により窒化膜7をエッチングし、最下層のタングステン膜6に達する溝を窒化膜7に形成する。そして、レジスト膜8を除去し、さらに、同図中に示したように、公知の側壁絶縁膜形成技術を用いて、溝の側壁に絶縁膜9を形成する。具体的には、溝を有する基板全面に酸化膜を堆積し(不図示)、これを公知の異方性ドライエッチ法、例えば反応性イオンエッチング(RIE)により全面エッチングを行うと、溝の側壁にのみ酸化膜が残る。側壁酸化膜9の厚さtは100nm程度である。溝の幅からこの側壁酸化膜9の2倍の厚さ2tを引いた長さがゲート電極長であり、ほぼチャネル長に対応する。従って、所望のチャネル長を得るように、溝の幅及び側壁酸化膜の厚さを設定すればよい。このようにチャネル長が側壁酸化膜9の厚さtにより決定できるので、この側壁酸化膜9の厚さを適当に選べば、ゲート電極寸法をリソグラフィ限界以下にすることも可能である。

【0039】次に、公知のタングステン選択成長技術を用いると、図6の(C)に示したように、溝の底に露出しているタングステン膜6の表面を核にして、溝の内部を埋めるように第2層目のタングステン膜10が成長する。成長させる第2層目のタングステン膜10の厚さは、成長時間で調整するが、本実施例では150〜200nm成長させた。なお、タングステン膜の成長としては、選択成長技術の他に、全面にスパッタによりメタル接着層を形成し、更に全面にタングステン膜を気相成長法で形成した後、エッチバック工程等でエッチングして溝の内部にのみタングステンを形成する方法も用いることができる。

【0040】ところで、タングステン膜は多結晶シリコン膜などと異なり、結晶粒が柱状であるため、従来の方法でゲート電極状に加工すると、たとえマスクとなるレジスト膜の側壁が平滑であっても、結晶粒界に起因する凹凸が側面にも発生する。このため、一本のゲート電極でもその寸法がばらつく原因となる。これは、ゲート電極の幅が小さくなるほど深刻な問題である。一方、本発明の方法によれば、第2層目のタングステン膜10の横方向への成長は、溝の側壁酸化膜9によって制限されており、しかも、側壁酸化膜9は滑らかである。非晶質である窒化膜7には側壁が滑らかな溝を形成することが可能であり、そこに形成した側壁酸化膜9も滑らかとなるからである。従って、滑らかな側壁酸化膜9により制限されるタングステン膜10の側壁も平滑となるので、側壁が平滑なゲート電極を得ることができ、上記問題は解決される。

【0041】次に、図6の(D)に示したように、ゲート電極となる第2層目のタングステン膜10と、窒化膜7の間にある側壁酸化膜9を除去する。このとき、酸化膜の除去にはフッ酸溶液を用いるが、タングステンと窒化膜はフッ酸溶液ではエッチングされない。

【0042】次に、図7の(A)に示したように、この側壁酸化膜9の除去後の隙間を通して窒化膜7をマスクに不純物イオンを打ち込み、ゲート電極端の近傍直下にパンチスルーストッパ11を形成する。本実施例では、20〜30KeVのエネルギで、1×1012〜1×1013/cm2のボロンを打ち込んだ。なお、p型MOSFETの場合には、ヒ素を100〜140KeV、1×1012〜1×1013/cm2打ち込んでパンチスルーストッパを形成すればよい。

【0043】次に、図7の(B)に示したように、溝が形成されていた窒化膜7を180℃程度に加熱したリン酸溶液で除去する。このとき、タングステン膜6、7は、加熱したリン酸液には溶解しない。

【0044】次に、図7の(C)に示したように、基板表面を被っている20〜40nm程度の第1層目のタングステン膜6を除去して、素子分離酸化膜2、および、ゲート酸化膜5の一部を露出させる。このタングステン膜の除去にも公知のドライエッチ法を用いるが、その際、除去する第1層目のタングステン膜6の厚さが、下地となるゲート酸化膜5の削れに大きな影響を及ぼす。それは、加工する膜が厚くなるほど、エッチングの均一性を向上させるためのオーバーエッチ時間が長くなり、下地のゲート酸化膜5がエッチングにさらされる時間が増えるためである。本実施例では、除去するタングステン膜は20〜40nm程度なので、5〜7nmのゲート酸化膜5上でも、均一性を維持しながらエッチングを止めることができる。勿論、このとき第2層目のタングステン膜10もエッチングされる。

【0045】このタングステン膜の加工によって、ゲート電極端のゲート酸化膜5に損傷が入るので、それを回復させるための熱処理を行い、さらに、図7の(D)に示したように、拡散層12を形成するイオン打ち込みを行う。この工程では、公知のLDD(Lightly Doped Drain)構造の低濃度拡散層12を作るため、打ち込む不純物の量は、1×1013〜1×1014/cm2とした。不純物はリンもしくはヒ素である。なお、損傷を回復させる熱処理として、本実施例においては、酸素と水蒸気の分圧を調整することで、シリコン基板を酸化しながら、タングステン膜は酸化しない技術を用いる。例えば、800℃で10%水蒸気を含む酸素雰囲気中で15分間程度の熱処理を行う。

【0046】次に、図8の(A)に示したように、公知の側壁絶縁膜形成技術を用いて、ゲート電極となるタングステン膜10、6の側壁にのみ絶縁膜13を形成する。具体的には、プラズマCVDで堆積した酸化膜を、異方性ドライエッチ法で全面エッチングする。さらに、リンもしくはヒ素を1×1015/cm2以上打ち込み、高濃度拡散層14を形成する。

【0047】次に、図8の(B)に示したように、シリコンが露出している拡散層14の表面と、ゲート電極の第2層目のタングステン膜10の表面に第3層目のタングステン膜15を選択的に成長させ、拡散層14の低抵抗化をはかる。このように、ゲート電極は3層のタングステン膜6、10、15から構成される。

【0048】次に、図8の(C)に示したように、基板全面を層間絶縁膜16で被い、さらに、公知のリソグラフィ技術およびドライエッチ技術を用いて、拡散層14の表面やゲート電極の表面のタングステン15に達するコンタクト孔を開口する。

【0049】最後に、コンタクト孔を公知のプラグ技術を用いてプラグ金属17で埋め戻した(具体的にはタングステンを選択成長させた)後に、アルミを主体とする金属で配線層18を形成すれば、図9に示した構造の半導体装置、すなわち図1に示した半導体装置が得られる。なお、配線が複数層に渡って必要な場合には、層間絶縁膜の形成、コンタクト孔の開口、その埋め戻し、および、配線層の形成とを繰り返せばよい。また、本実施例では、n型のMOSFETを形成する場合について説明したが、半導体基板1や不純物領域4、11、12、14の導電型を逆にすれば、p型のMOSFETを形成できることは云うまでもない。更に、本実施例では、ゲート電極は3層のタングステン膜からなり、第1層目はゲート絶縁膜との接着性に優れたスパッタ法で堆積したタングステン膜6であり、第2層目はスパッタタングステンの表面に選択的に成長させたタングステン膜10であり、第3層目は拡散層14の表面にタングステンを成長させた際にゲート電極の第2層目のタングステン膜上に成長したタングステン膜15であるが、ソース・ドレインの抵抗が問題とならない場合には、勿論、第3層目のタングステン膜の代わりにチタンシリサイドを形成してもよい。なお、ゲート電極の第2層目のタングステン膜上にはチタンシリサイドを形成しないように、図8の(A)の後の工程で酸化膜を堆積して公知のホトリソグラフィ技術により拡散層14上の酸化膜だけに孔を開けてチタンシリサイドを形成してもよい。その場合は、ゲート電極は2層のタングステン膜から構成される。

【0050】<実施例2>前記実施例1では、図6の(C)に示したように、ゲート電極を構成する選択成長で形成した第2層目のタングステン膜10の下層には、ゲート酸化膜5に接触するタングステン膜6があり、しかも、これが基板全面を被っている。この最下層のタングステン膜6は、実施例1の場合、選択成長させた第2層目のタングステン膜10の直下のみを残して除去していたが、側壁絶縁膜の形成技術を用いることで、公知のゲートオーバーラップドレイン構造を作ることができる。

【0051】以下、図10及び図11を用いて、実施例2としてゲートオーバラップドレイン構造を有する本発明に係る半導体装置およびその製造方法を説明する。図1010及び図11は、本発明に係る半導体装置の製造工程の主要工程順に沿って示した断面構造図である。なお、本実施例でも、説明の便宜上、n型のMOSFETを一例に説明する。

【0052】先ず、実施例1における図5から図7の(B)までの製造工程を経た基板、すなわち、図10の(A)に示したように、下層のタングステン膜6上に選択成長により形成した第2層目のタングステン膜10と局所パンチスルーストッパ11を有する基板を用意する。

【0053】そして、図10の(B)に示したように、下層のタングステン膜6の一部を除去する前に、低濃度拡散層12をイオン打ち込みで形成する。条件は実施例1と同じであり、不純物はリンもしくはヒ素を用い、打込み量は1×1013〜1×1014/cm2である。

【0054】次に、図10の(C)に示したように、ゲート電極となる第2層目のタングステン膜10の側壁に公知の側壁絶縁膜形成技術を用いて側壁絶縁膜13を形成し、さらに、この側壁絶縁膜13をマスクにして下層のタングステン膜6を除去する。その後、リンもしくはヒ素を1×1015/cm2以上打込み、高濃度拡散層14を形成する。このようにすることによって、下層のタングステン膜6のゲート長方向の寸法は上層のタングステン膜10よりも広くなり、しかも、その下の基板領域に形成された低濃度の拡散層12上に張り出した構造とすることができる。なお、第1層目のタングステン膜6を除去する際に、第2層目のタングステン膜10の表面の一部も同時に除去されて、図に示したように、側壁絶縁膜13の角が残る。

【0055】本実施例に示したMOSFETの場合は、低濃度拡散層12がゲート電極を構成する第1層目のタングステン膜6の張出し部分と重なることにより、第1層目のタングステン膜6と低濃度拡散層12との重なりが少ない実施例1に示したMOSFETの場合に比べ、LDD構造の寄生抵抗の増加が押さえられるので、電流が増加する利点がある。このような構造はゲートオーバーラップドレイン構造と呼ばれ、すでに公知の技術であるが、本発明のMOSFETでは、ゲート電極となる第2層目のタングステン膜10を選択成長を用いて形成しているので、側壁絶縁膜13の形成工程を加えるだけで、ゲートオーバーラップドレイン構造を簡単に実現することができる。

【0056】次に、図10の(D)に示したように、側壁絶縁膜13’を再び形成し、拡散層14の表面とタングステン膜10の表面にタングステン膜15を成長させる。側壁酸化膜13’は、張り出した第1層目のタングステン膜6と拡散層14上のタングステン膜15の短絡を防ぐ役目を果たす。また、拡散層14の表面とゲート電極となる第2層目のタングステン膜10の表面への第3層目のタングステン膜15の選択成長は、実施例1とまったく同じ条件で行えばよい。このとき、図10の(C)に示したように、残っている側壁絶縁膜13の角は第2層目のタングステン膜10の表面より飛び出しているために、この角が第3層目のタングステン膜15を選択成長した時に、拡散層14上と第2層目のタングステン膜10上に成長した第3層目のタングステン15がつながってしまうのを効果的に抑制する。

【0057】最後に、実施例1と全く同様に、コンタクト孔を公知のプラグ技術を用いてプラグ金属17で埋め戻した(具体的にはタングステンを選択成長させた)後に、アルミを主体とする金属で配線層18を形成すれば、図11に示した構造の半導体装置、すなわち図2に示した半導体装置が得られる。

【0058】また、本実施例においても、n型のMOSFETを形成する場合について説明したが、実施例1と同様に半導体基板や不純物領域の導電型を逆にすれば、p型のMOSFETを形成できることは言うまでもない。

【0059】<実施例3>図12乃至図14を用いて、本発明に係る半導体装置およびその製造方法の第3の実施例を詳細に説明する。図12乃至図14は、本発明に係る半導体装置の製造方法を示す断面構造図であり、主要工程順に順を追って示したものである。なお、説明の便宜上、ここではn型のMOSFETを一例に説明する。

【0060】まず、実施例1の図5の(A)において説明した工程を経た基板、すなわち、図12の(A)に示したように、選択酸化法を用いて形成した素子間分離酸化膜2と酸化膜3を有する半導体基板を用意する。

【0061】次に、図12の(B)に示したように、ゲート酸化膜5を成長させた後、多結晶シリコン膜6’をCVD法を用いて堆積する。チャネル長0.1〜0.2μmのMOSFETを形成する場合、ゲート酸化膜5の膜厚は約5〜7nmであり、多結晶シリコン膜6’の膜厚は20〜40nm程度である。そして、窒化膜7をプラズマCVD法を用いて約200nm堆積した後、リソグラフィ技術を用いて溝を形成し、この溝の側壁に側壁酸化膜9を形成する。なお、ゲート酸化膜5を成長させる前に、酸化膜3は表面を洗浄する際に除去しておく。

【0062】次に、図12の(C)に示したように、露出している多結晶シリコン膜6’の表面をタングステン膜6に置換する。具体的には、WF6ガスを供給するとシリコンとの反応が起こり、シリコンは揮発性のガスであるSiF4となって除去されてW(タングステン)が残る。WF6ガスは酸化膜とは反応しないので、溝側壁の側壁酸化膜9はそのままであり、また、多結晶シリコン膜6’との置換反応が進んでも、ゲート酸化膜5がタングステン膜6と反応するということもない。

【0063】次に、図12の(D)に示したように、置換した第1層目のタングステン膜6の表面に、実施例1の図6の(C)で説明した方法により、第2層目のタングステン膜10を選択成長させる。

【0064】次に、図13の(A)に示したように、側壁酸化膜9を除去後、ゲート電極となる第2層目のタングステン膜10と窒化膜7との隙間を通してイオン打込みを行い、パンチスルーストッパ11を形成する。本実施例の場合、不純物イオンは多結晶シリコン膜6’を通して打ち込まれる。

【0065】次に、図13の(B)に示したように、溝が形成されていた窒化膜7を除去し、更に基板全面を被っていた多結晶シリコン膜6’をエッチングにより除去する。これまでの実施例では、第1層目のタングステン膜6を除去していたが、本実施例では、多結晶シリコン膜6’が除去される。多結晶シリコン膜6’は下地のゲート酸化膜5との間に選択比を確保し易いという特徴がある。これまでの実施例でも、除去される第1層目のタングステン膜6を薄くすることで、ゲート酸化膜5上でのタングステン膜の加工を行ってきたが、本実施例では、よりエッチングし易い多結晶シリコン6’を用いることで、ゲート電極加工上の問題がなくなる利点もある。

【0066】以下、図13の(C)から図14までの工程は、それぞれ実施例1で図7の(D)から図9までを用いて説明した方法とまったく同じ方法により形成できるので、詳細な説明は省略する。

【0067】本実施例ではパンチスルーストッパ11は多結晶シリコン膜6’を通して形成し、その後、その多結晶シリコン膜6’をタングステン膜6に置換するという方法を用いたことにより、前記実施例1及び実施例2のように、ゲート酸化膜5に接したタングステン膜6を通してイオン打込みを行い、パンチスルーストッパ11を形成する場合に比べて、基板表面がタングステンによって汚染されるいわゆる重金属汚染の可能性がなくなったので、汚染によるキャリア寿命の低下や接合リークの増加を招くおそれがなくなり、信頼性が向上する。なお、多結晶シリコン膜6’をゲート電極の一部としてそのまま使用することも可能であるが、従来技術の問題点のひとつとして指摘したように、表面チャネル型の微細なMOSFETを実現するためには、ゲート電極の導電型を変えなければならないという工程数の増加する問題があるので、ここでは、タングステン膜6に置換した例について説明した。

【0068】<実施例4>図15乃至図16を用いて、本発明に係る半導体装置およびその製造方法の第4の実施例を詳細に説明する。図15乃至図16は、本発明に係る半導体装置の製造方法を示す断面構造図であり、主要工程順に順を追って示したものである。なお、本実施例は実施例1で説明した半導体装置を用いて、図3に示したCMOSを形成した場合の例である。

【0069】既に述べてきたように、本発明の半導体装置は、拡散層などの導電型を変えるだけで、容易にn型およびp型のMOSFETを作ることができる。この点は、従来構造のMOSFETとまったく同じである。従って、CMOSを形成するためには、従来と同じように、導電型の異なる領域を有する基板を用意し、交互にn型とp型の半導体装置を作って行けばよい。

【0070】まず、図15の(A)に示したように、半導体基板1に導電型の異なる領域21と22を有し、かつ、素子分離酸化膜2が成長されている基板を用意する。ここでは、説明の便宜上、領域21をn型MOSFETが形成されるp型領域、領域22をp型MOSFETが形成されるn型領域とする。

【0071】次に、図15の(B)に示したように、それぞれの領域21、22に対して、素子分離特性を改善するためのイオン打ち込みをレジスト膜8をマスクにして交互に行い、不純物領域41、42を形成する。p型領域21の不純物領域42に対してはボロンが導入され、n型領域22の不純物領域41に対してはリンが導入される。

【0072】次に、図15の(C)に示したように、ゲート酸化膜5を全面に成長させ、さらに、ゲート電極の一部となる第1層目のタングステン膜6を形成し、実施例1において図6の(A)〜(C)を用いて説明したように、窒化膜7への溝の形成、側壁酸化膜9の形成、第2層目のタングステン膜10の成長を行う。

【0073】そして、図15の(D)に示したように、側壁酸化膜9を除去し、パンチスルーストッパ11、11’の形成を行う。パンチスルーストッパ11はボロンのイオン打ち込みで形成し、パンチスルーストッパ11’はヒ素のイオン打ち込みで形成する。

【0074】次に、図16の(A)に示したように、窒化膜7を加熱したリン酸溶液で除去後、基板表面を被う第1層目のタングステン膜6をドライエッチ法により除去し、図16の(B)に示したように、低濃度拡散層12、12’、側壁酸化膜13、高濃度拡散層14、14’を形成する。実施例1で図7の(D)から図8の(A)までを用いて説明した方法により形成できるので詳細な説明は省略する。両MOSFETにおいて、導電型が異なるのは言うまでもない。

【0075】そして、図16の(C)に示したように、拡散層14の表面とゲート電極となる第2層目のタングステン膜10の表面での第3層目のタングステン膜15の成長を行い、層間絶縁膜16で覆った後、層間絶縁膜16にコンタクト孔を開け、最後に、図16の(D)に示したように、コンタクト孔をプラグ金属17(具体的にはタングステン)で埋め戻した後、アルミを主体とする金属で配線18を形成してCMOS、すなわち図3で示したCMOSが完成する。なお、第3層目のタングステン膜15から配線18を形成するまでは、実施例1で図8の(B)から図9までを用いて説明した方法によって形成できるので、詳細な説明は省略した。

【0076】以上、本発明の好適な実施例について説明したが、本発明は前記実施例に限定されることなく、例えば、高融点金属材料としてタングステンを用いたが、チタンなど他の材料を用いてもよく、本発明の精神を逸脱しない範囲内で種々の設計変更をなし得ることは勿論である。

【0077】

【発明の効果】以上、前述した実施例から明らかなように、本発明に係る半導体装置およびその製造方法によれば、タングステンという抵抗が低く、かつ、熱処理にも耐えることができる高融点金属材料を、ゲート酸化膜が非常に薄いMOSFETのゲート電極として使用することが可能となる。ゲート電極に、高融点金属であるタングステンを使用できることにより、従来のシリサイド化したゲート電極の抵抗がシート抵抗で10Ω/□であるのに対して、ゲート電極抵抗を1Ω/□と低減でき、動作速度を向上させることができる。

【0078】また、タングステンを用いることで、従来の多結晶シリコンゲートを用いてCMOSを形成する場合のように、導電型の異なるゲート電極を形成する必要がなくなり、ゲート電極形成工程の工程数の削減が可能となる。

【0079】更に、拡散層の表面とゲート電極の表面にタングステンを成長させる製造方法は、シリサイド化する方法と比べて、拡散層の高濃度不純物領域を侵食することがないために、拡散層の抵抗をよりいっそう低下させる利点もある。

【0080】また更に、溝を用いたゲート電極の形成は、パンチスルーストッパを局所的に形成することを可能とする。このため、パンチスルーストッパによる寄生の接合容量が大幅に低減する。例えば、チャネル長が0.2ミクロン程度のMOSFETでは、パンチスルーストッパのピーク濃度は1018/cm3弱であり、接合容量は2fF/μm2程度になるのに対して、本発明に係る局所パンチスルーストッパ構造を有するMOSFETでは、接合容量は1/10程度に低減する。この接合容量の低減の結果、ゲート抵抗の低下と相俟って、素子性能の向上に多いに寄与し、信号の伝達速度の向上を図ることができる。

【0081】更に、この局所パンチスルーストッパは、ゲート電極端付近の領域に局在しており、ゲート電極の直下は低濃度の状態に保たれている。このため、電子や正孔が流れるチャネル領域における、垂直方向電界(基板に対して)が小さく、チャネル領域全体にパンチスルーストッパが形成されている従来構造のMOSFETに比べて、高い移動度が実現され、電流が大きくなる効果がある。

【0082】また更に、本発明に係る半導体装置は、製造工程をわずかに追加もしくは変更することで、ゲートオーバーラップ構造にしたり、ゲート電極寸法をリソグラフィ限界以下にすることができ、これらも素子性能の向上に寄与するところ大である。

【0083】以上述べてきたように、局所パンチスルーストッパ構造は、接合容量を大幅に低減しながら、電子や正孔の移動度が低下するのを抑えることができ、タングステンゲート電極によってゲート抵抗は減少する。また、拡散層上で成長させたタングステンは、拡散層抵抗を減少させる。さらに、タングステンゲートは、ゲート電極形成工程を単純にし、その結果、低コストで、かつ、高性能なMOSFETを実現でき、ひいては、LSIの高性能化を達成することができる。

【図面の簡単な説明】

【図1】本発明に係る半導体装置の第1の実施例を示す断面図。

【図2】本発明に係る半導体装置の第2の実施例を示す断面図。

【図3】本発明に係る半導体装置によるCMOSの実施例を示す断面図。

【図4】従来の半導体装置におけるCMOSの断面図。

【図5】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図6】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図5R>5の次の工程を示す図。

【図7】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図6R>6の次の工程を示す図。

【図8】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図7R>7の次の工程を示す図。

【図9】本発明に係る半導体装置の第1の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図8R>8の次の工程を示す図。

【図10】本発明に係る半導体装置の第2の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図11】本発明に係る半導体装置の第2の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図10の次の工程を示す図。

【図12】本発明に係る半導体装置の第3の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図13】本発明に係る半導体装置の第3の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図12の次の工程を示す図。

【図14】本発明に係る半導体装置の第3の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図13の次の工程を示す図。

【図15】本発明に係る半導体装置の第4の実施例の製造方法を主要工程順に断面図で示す製造工程図。

【図16】本発明に係る半導体装置の第4の実施例の製造方法を主要工程順に断面図で示す製造工程図であり、図15の次の工程を示す図。

【符号の説明】

1…半導体基板

2…素子分離酸化膜

3…酸化膜

4、41、42…不純物領域

5…ゲート酸化膜

6…タングステン膜

6’…多結晶シリコン膜

7…窒化膜

8…レジスト膜

9…側壁酸化膜

10…タングステン膜

11、11’…パンチスルーストッパ

12、12’…低濃度拡散層

13…側壁絶縁膜

14、14’…高濃度拡散層

15、15’…タングステン膜

16…層間絶縁膜

17…プラグ金属

18…配線金属

21…p型領域

22…n型領域

30、30’…ゲート電極

35、35’…シリサイド膜

【特許請求の範囲】

【請求項1】素子間分離用絶縁膜で囲まれた半導体基板の第1の領域に、所定の間隔で形成された該第1の領域の導電型とは導電型が異なる一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とを具備する電界効果型の半導体装置において、上記ゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記ゲート電極の上記2つの側壁絶縁膜のそれぞれの下の第1の領域に、ゲート幅と同じ長さで局在する上記第1の領域と同じ導電型の2つの高濃度不純物領域を有することを特徴とする半導体装置。

【請求項2】素子間分離用絶縁膜でそれぞれ囲まれた半導体基板の第1の領域および該第1の領域の導電型と異なる第2の領域に、それぞれの領域の導電型とは導電型が異なると共に所定間隔で形成された一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とをそれぞれ具備する相補型の電界効果型半導体装置において、上記それぞれのゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記それぞれのゲート電極の上記2つの側壁絶縁膜の下のそれぞれの第1および第2の領域に、ゲート幅と同じ長さで局在する上記それぞれの領域と同じ導電型の2つの高濃度不純物領域を有することを特徴とする半導体装置。

【請求項3】前記ゲート電極は高融点金属である請求項1または請求項2に記載の半導体装置。

【請求項4】前記高融点金属はタングステンである請求項3に記載の半導体装置。

【請求項5】前記ゲート電極は少なくとも2層構造からなると共に、ゲート絶縁膜に接する最下層のゲート電極は、上層のゲート電極より張り出して成る請求項1乃至請求項4のいずれか一に記載の半導体装置。

【請求項6】最下層ゲート電極の張り出した部分のゲート絶縁膜の下の領域に、前記一対の不純物領域と同じ導電型で、かつ、一対の不純物領域の不純物濃度よりも低い不純物濃度の拡散による不純物領域を有して成る請求項5に記載の半導体装置。

【請求項7】素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、この絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程10と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程11と、工程10で残した第1及び第2の導電膜の側壁に側壁絶縁膜を形成する工程12と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程13と、工程13で形成した不純物領域の表面および工程10で残した導電膜の表面に第3の導電膜を成長させる工程14と、半導体基板表面を層間絶縁膜で被う工程15と、層間絶縁膜にコンタクト孔を開口する工程16と、配線層を形成する工程17と、からなることを特徴とする半導体装置の製造方法。

【請求項8】素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程10と、工程6で形成した第2の導電膜の側壁に側壁絶縁膜を形成する工程11と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程12と、工程12で残した導電膜の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程12で残した導電膜の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18と、からなることを特徴とする半導体装置の製造方法。

【請求項9】素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に多結晶シリコン膜を形成する工程2と、多結晶シリコン膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して多結晶シリコン膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した多結晶シリコン膜を第1の導電膜に置換する工程6と、第1の導電膜の表面に第2の導電膜を成長させる工程7と、側壁絶縁膜を除去する工程8と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程9と、絶縁膜を除去する工程10と、工程2で形成した多結晶シリコン膜と並びに工程7で形成した第2の導電膜のゲート電極になる部分以外の導電膜とを除去する工程11と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程12と、工程11で形成したゲート電極の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程11で形成したゲート電極の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18と、からなることを特徴とする半導体装置の製造方法。

【請求項10】前記第1乃至第3の導電膜は高融点金属の膜である請求項7乃至請求項9のいずれか一に記載の半導体装置の製造方法。

【請求項11】前記高融点金属の膜はタングステン膜である請求項10に記載の半導体装置の製造方法。

【請求項12】第3の導電膜は、第1及び第2の同電膜と同じかもしくは異なる高融点金属からなる膜である請求項7乃至請求項9のいずれか一に記載の半導体装置の製造方法。

【請求項13】前記同じ高融点金属の膜はタングステン膜であり、異なる高融点金属の膜はチタンからなる膜である請求項12に記載の半導体装置の製造方法。

【請求項1】素子間分離用絶縁膜で囲まれた半導体基板の第1の領域に、所定の間隔で形成された該第1の領域の導電型とは導電型が異なる一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とを具備する電界効果型の半導体装置において、上記ゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記ゲート電極の上記2つの側壁絶縁膜のそれぞれの下の第1の領域に、ゲート幅と同じ長さで局在する上記第1の領域と同じ導電型の2つの高濃度不純物領域を有することを特徴とする半導体装置。

【請求項2】素子間分離用絶縁膜でそれぞれ囲まれた半導体基板の第1の領域および該第1の領域の導電型と異なる第2の領域に、それぞれの領域の導電型とは導電型が異なると共に所定間隔で形成された一対の不純物領域と、該一対の不純物領域間上にゲート絶縁膜を介して接するゲート電極とをそれぞれ具備する相補型の電界効果型半導体装置において、上記それぞれのゲート電極の2つの側壁を覆う2つの側壁絶縁膜をさらに具備し、上記それぞれのゲート電極の上記2つの側壁絶縁膜の下のそれぞれの第1および第2の領域に、ゲート幅と同じ長さで局在する上記それぞれの領域と同じ導電型の2つの高濃度不純物領域を有することを特徴とする半導体装置。

【請求項3】前記ゲート電極は高融点金属である請求項1または請求項2に記載の半導体装置。

【請求項4】前記高融点金属はタングステンである請求項3に記載の半導体装置。

【請求項5】前記ゲート電極は少なくとも2層構造からなると共に、ゲート絶縁膜に接する最下層のゲート電極は、上層のゲート電極より張り出して成る請求項1乃至請求項4のいずれか一に記載の半導体装置。

【請求項6】最下層ゲート電極の張り出した部分のゲート絶縁膜の下の領域に、前記一対の不純物領域と同じ導電型で、かつ、一対の不純物領域の不純物濃度よりも低い不純物濃度の拡散による不純物領域を有して成る請求項5に記載の半導体装置。

【請求項7】素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、この絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程10と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程11と、工程10で残した第1及び第2の導電膜の側壁に側壁絶縁膜を形成する工程12と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程13と、工程13で形成した不純物領域の表面および工程10で残した導電膜の表面に第3の導電膜を成長させる工程14と、半導体基板表面を層間絶縁膜で被う工程15と、層間絶縁膜にコンタクト孔を開口する工程16と、配線層を形成する工程17と、からなることを特徴とする半導体装置の製造方法。

【請求項8】素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に第1の導電膜を形成する工程2と、第1の導電膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して第1の導電膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した第1の導電膜上に第2の導電膜を形成する工程6と、側壁絶縁膜を除去する工程7と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程8と、絶縁膜を除去する工程9と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程10と、工程6で形成した第2の導電膜の側壁に側壁絶縁膜を形成する工程11と、工程2で形成した第1の導電膜および工程6で形成した第2の導電膜の所要部分を残して導電膜を除去する工程12と、工程12で残した導電膜の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程12で残した導電膜の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18と、からなることを特徴とする半導体装置の製造方法。

【請求項9】素子間分離用絶縁膜を有する半導体基板表面にゲート絶縁膜を形成する工程1と、ゲート絶縁膜上に多結晶シリコン膜を形成する工程2と、多結晶シリコン膜上に絶縁膜を形成する工程3と、絶縁膜の所要部分に溝を形成して多結晶シリコン膜の表面の一部を露出させる工程4と、溝の側壁に側壁絶縁膜を形成する工程5と、露出した多結晶シリコン膜を第1の導電膜に置換する工程6と、第1の導電膜の表面に第2の導電膜を成長させる工程7と、側壁絶縁膜を除去する工程8と、除去された側壁絶縁膜の隙間を通して素子間分離用絶縁膜で囲まれた半導体基板領域の内部に不純物を導入する工程9と、絶縁膜を除去する工程10と、工程2で形成した多結晶シリコン膜と並びに工程7で形成した第2の導電膜のゲート電極になる部分以外の導電膜とを除去する工程11と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程12と、工程11で形成したゲート電極の側壁に側壁絶縁膜を形成する工程13と、前記半導体基板領域中に該半導体基板領域とは導電型の異なる領域を作るために不純物を導入する工程14と、工程14で形成した不純物領域の表面および工程11で形成したゲート電極の表面に第3の導電膜を成長させる工程15と、半導体基板表面を層間絶縁膜で被う工程16と、層間絶縁膜にコンタクト孔を開口する工程17と、配線層を形成する工程18と、からなることを特徴とする半導体装置の製造方法。

【請求項10】前記第1乃至第3の導電膜は高融点金属の膜である請求項7乃至請求項9のいずれか一に記載の半導体装置の製造方法。

【請求項11】前記高融点金属の膜はタングステン膜である請求項10に記載の半導体装置の製造方法。

【請求項12】第3の導電膜は、第1及び第2の同電膜と同じかもしくは異なる高融点金属からなる膜である請求項7乃至請求項9のいずれか一に記載の半導体装置の製造方法。

【請求項13】前記同じ高融点金属の膜はタングステン膜であり、異なる高融点金属の膜はチタンからなる膜である請求項12に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図14】

【図7】

【図8】

【図11】

【図12】

【図10】

【図13】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図14】

【図7】

【図8】

【図11】

【図12】

【図10】

【図13】

【図15】

【図16】

【公開番号】特開平7−263679

【公開日】平成7年(1995)10月13日

【国際特許分類】

【出願番号】特願平6−50086

【出願日】平成6年(1994)3月22日

【出願人】(000005108)株式会社日立製作所 (27,607)

【公開日】平成7年(1995)10月13日

【国際特許分類】

【出願日】平成6年(1994)3月22日

【出願人】(000005108)株式会社日立製作所 (27,607)

[ Back to top ]