半導体装置の製造方法

【課題】電解めっき工程において、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーの、前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、前記第1の導電層の上にレジスト層を形成する工程と、前記第2の領域の前記第1の導電層の第1の部分の上の第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上の第2レジスト層を除去するパターニング工程と、電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、を有する。

【解決手段】本発明に係る半導体装置の製造方法は、集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーの、前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、前記第1の導電層の上にレジスト層を形成する工程と、前記第2の領域の前記第1の導電層の第1の部分の上の第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上の第2レジスト層を除去するパターニング工程と、電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

給電部であるリング状電極を有し、その電極とめっき液とを遮断するためのシーリング部材を有した半導体ウエハー用のめっき治具が知られている(特許文献1)。めっき治具には、外部端子が設けられ、そこから供給された電流は、めっき治具内に埋め込まれた配線を経由してリング状電極に給電される。

【0003】

例えば、WCSP(Wafer Level Chip Size Package)構造を有する半導体装置の製造工程において、このようなめっき治具を用いて半導体ウエハーに電解めっき処理を行う場合、半導体ウエハー上に導電層を形成し、電解めっき用のレジスト層を形成し、リング状電極と導電層とを接触させるために外周部分のレジスト層を除去して導電層を露出させ、めっき治具のリング状電極と外周部分の導電層とを接触させて給電を行う(特許文献1)。

【0004】

しかしながら、上述のようにリング電極には、配線を経由して電流が給電されるため、リング電極の配線との電気的接続部に電流が集中しやすく、リング電極の電気的接続部周辺のめっき成長が促進され、めっき膜厚が部分的に厚くなってしまい、膜厚の均一性を担保することが難しかった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−287648号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、以上のような問題点に鑑みてなされたものであり、本発明のいくつかの態様によれば、電解めっき工程において、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供することができる。

【課題を解決するための手段】

【0007】

(1)本形態に係る半導体装置の製造方法は、集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーを用意する工程と、前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、前記第1の導電層の上にレジスト層を形成する工程と、前記第2の領域の前記第1の導電層の第1の部分の上に位置する、前記レジスト層の一部である第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上に位置する、前記レジスト層の一部である第2レジスト層を除去するパターニング工程と、電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、前記半導体ウエハー及び前記治具をめっき液中に配置し、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、を有する。

【0008】

本発明によれば、電解めっき工程において、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供することができる。

【0009】

(2)本形態に係る半導体装置の製造方法において、治具70は基板と、前記電極と前記基板との間に配置された弾性層と、を更に有し、前記第2の領域の前記第1の導電層の第2の部分は、押圧されて前記電極と接触してもよい。

【0010】

これによれば、より安定的に第1の導電層の第2の部分を治具の電極に接触させることができる。

【0011】

(3)本形態に係る半導体装置の製造方法において、前記半導体ウエハーは、切断ラインによって区画される複数の個別チップ領域を有し、前記パターニング工程において、前記第1レジストは、前記第2の領域の複数の個別チップ領域の上方に残るようにパターニングされてもよい。

【0012】

(4)本形態に係る半導体装置の製造方法において、前記パターニング工程において、前記レジスト層は、前記第1の領域において所望の形状にパターニングされ、前記第2の導電層は、前記第1の領域の前記第1の導電層の上に形成されてもよい。

【図面の簡単な説明】

【0013】

【図1】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図2】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図3】めっき治具を模式的に説明する図。

【図4】めっき治具を模式的に説明する図。

【図5】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図6】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図7】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図8】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図9】本実施形態に係る半導体装置の製造方法の変形例を模式的に説明する図。

【図10】本実施形態に係る半導体装置の製造方法の変形例を模式的に説明する図。

【発明を実施するための形態】

【0014】

以下に、本発明を適用した実施の形態について図面を参照して説明する。ただし、本発明は以下の実施の形態のみに限定されるものではない。本発明は、以下の実施の形態及び変形例を自由に組み合わせたものを含むものとする。

【0015】

以下、図面を参照して、本実施の形態に係る半導体装置の製造及び半導体ウエハーについて説明する。

【0016】

図1、2、5〜8は、本実施の形態に係る半導体装置の製造方法を模式的に説明する図である。図3及び4は、本実施形態に係る半導体装置の製造方法に用いるめっき治具を模式的に説明する図である。

【0017】

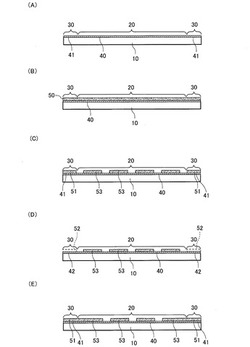

ここで、図1(A)は半導体ウエハー10の平面図であり、図1(B)は図1(A)のIB−IB線断面図である。図2(A)〜図2(E)は、図1(B)に対応し、半導体装置の製造方法を説明する断面図である。

【0018】

なお、本実施形態の説明において、「平面図」という文言は、半導体ウエハーの電極や配線などが形成される面を法線方向から見た場合の平面図という意味で用いる。

【0019】

本実施の形態に係る半導体装置の製造方法は、集積回路5が形成された第1の領域20と、第1の領域20を囲む第2の領域30と、を有する半導体ウエハー10を用意する工程と、第1の領域20及び第2の領域30に第1の導電層40を形成する工程と、第1の導電層40の上にレジスト層50を形成する工程と、第2の領域30の第1の導電層40の第1の部分41の上の第1レジスト層51を残し、第2の領域30の第1の導電層40の第2の部分42の上の第2レジスト層52を除去するパターニング工程と、電極73と、電極73の電気的接続部73aに連続し、電極73に電流を供給する配線75と、を有する治具70、80を、電気的接続部73aが第1レジスト層51と接するように配置する工程と、半導体ウエハー10及び治具70、80をめっき液中に配置し、電極73に前記電流を供給して、電解めっきにより第1の導電層40の上に第2の導電層120を形成する工程と、を有する。

【0020】

半導体ウエハーを用意する工程において用意される半導体ウエハー10は、例えば、シリコンウエハーからなる半導体基板10であってもよい。半導体ウエハー10の平面形状は、例えば、略円形であってもよい。図1(A)に示すように、一部が切り欠かれていてもよい。また、半導体ウエハー10は、複数に分割されてなる分割基板であってもよい(図示せず)。

【0021】

半導体ウエハー10は、図1(A)に示すように、有効チップ領域である第1の領域20(図1(A)の灰色で示された領域)と、第1の領域20を囲む第2の領域30(図1(A)の白色で示された領域)と、を有する。

【0022】

第1の領域20は、有効チップ領域であって、製品となる半導体チップを含む領域であってよい。また、第1の領域20には、集積回路5が形成されている。図1(B)に示すように、第1の領域20には複数の集積回路5が形成されていてもよい。図1(B)に示すように、第1の領域20は、半導体ウエハー10の中央部に形成してもよい。図1(A)に示すように、切断ラインLは、隣り合った半導体チップとなる部分の境界線を示すものである。半導体ウエハー10は、切断ラインLによって区画された複数の個別チップ領域11を有する。よって、第1の領域20の切断ラインLによって区画された1つの個別チップ領域11は、切断されて半導体チップとなる領域である。それぞれの個別チップ領域11において、一つの集積回路5及び図示されない保護膜16(パッシベーション膜)、集積回路5に接続される電極14等の構造体を含んでいてもよい(図9、10参照)。

【0023】

第2の領域30は、図1(A)及び図1(B)に示すように、第1の領域20を囲む領域である。第2の領域30は、製品とならない半導体チップを含む領域であってもよい。図1(A)に示すように、第2の領域30においても、複数の個別チップ領域11が形成される。なお、半導体ウエハー10の第1の領域20及び第2の領域30の配置は、半導体装置のデザインの際に適宜決定される設計事項である。

【0024】

次に、図2(A)に示すように、半導体ウエハー10の第1の領域20及び第2の領域30に第1の導電層40を形成する。第1の導電層40は、公知のいずれかの成膜方法によって形成されてもよい。例えば、第1の導電層40は、スパッタリング法等を用いて形成されてもよい。第1の導電層40は、半導体ウエハー10の全面に形成されてもよい。また、第1の導電層40は、所望の形状にパターニングされていてもよい(図示せず)。第1の導電層40は、導電性の膜であれば特に限定されない。第1の導電層40は、例えば、銅(Cu)、チタンタングステン(TiW)、クロム(Cr)、チタン(Ti)、ニッケル(Ni)、金(Au)、アルミニウム(Al)、ニッケルバナジウム(NiV)、タングステン(W)のうちいずれか1つ又は複数を積層することで、形成されてもよい。

【0025】

図2(A)に示すように、第2の領域30の第1の導電層40の一部を第1の部分41とする。第1の部分41は、後述されるパターニング工程において、第1レジスト51が形成される部分である。図示はされないが、第2の部分42は、第2の領域30の第1の導電層40第1の部分41を除く部分である。

【0026】

第2の領域30における第1の部分41の配置は、特に限定されず、後述されるめっき治具の電極73の電気的接続部73aの配置に対応して適宜決定される。第1の部分41は、半導体ウエハー10がめっき治具70に装着される場合に電極73の電気的接続部73aと対向する箇所(以下、「対向箇所」とも言う。)を、少なくとも含む部分である。例えば、対向箇所が上方に位置する個別チップ領域11の上に形成された第1の導電層40を第1の部分41としてもよい。また、例えば、第1の導電層40の対向箇所が上方に位置する個別チップ領域11と、該個別チップ領域11周辺の複数の個別チップ領域11の上に形成された第1の導電層40を第1の部分41としてもよい。

【0027】

図2(B)に示すように、第1の導電層40の上にレジスト層50(例えばソルダーレジスト層)を形成する。レジスト層50は、感光性の樹脂であってもよい。レジスト層50は、めっき用レジストであってもよい。レジスト層50は、第1の領域20及び第2の領域30を覆うように形成される。

【0028】

次に、図2(C)及び図2(D)に示すように、レジスト層50をパターニングする。パターニング工程においては、第2の領域30の第1の導電層40の第1の部分41の上に位置する、レジスト層50の一部である第1レジスト層51を残し、第2の領域30の第1の導電層40の第2の部分42の上に位置するレジスト層50の一部である第2レジスト層52を除去する。言い換えれば、図2(C)に示すように、第1の部分41は、第1レジスト層51によって覆われる。また、図2(D)に示すように、第2の部分42は、第2レジスト層52が除去され、露出する。

【0029】

レジスト層50をパターニングする方法は特に限定されず、例えば、露光処理及び現像処理によってエッチングされ、パターニングされてもよい。ここで、第1の領域20に形成されたレジスト層50は、所望の形状にパターニングされ、第3レジスト層53が形成される。

【0030】

ここで、図2(C)に示すように、第1レジスト層51と第3レジスト層53は、不連続に形成されていてもよい。また、図2(E)に示すように、第1レジスト層51と第3レジスト層53は、連続するように形成されていてもよい。

【0031】

次に、第1の導電層40に給電して、電解めっきにより第1の導電層40の上に第2の導電層120を形成する電解めっき工程が実施される。

【0032】

図3〜図8はめっき治具70、80と、半導体ウエハー10を電解めっきする工程を説明する図である。

【0033】

なお、図3及び図4は模式的にめっき治具70、80を示すものであり、形状はこれに限定されるものではない。めっき治具70、80は、大略すると図3に示されるマスク治具70と、図4に示される裏蓋治具80とにより構成される。図3(A)は、マスク治具70の正面図であり、図3(B)は、マスク治具70の断面図である。また、図4(A)は、裏蓋治具80の正面図であり、図4(B)は裏蓋治具80の断面図である。

【0034】

図3(A)及び図3(B)に示すように、マスク治具70は、例えば、基板71の中央下部に開口部71aが形成される。開口部71aの周縁部には環状形状を有した弾性部材72が形成される。弾性部材72は、弾性を有する材料からなる部材であれば特に限定されず、例えばシリコンゴムであってもよい。弾性部材72は、電極73と基板71との間に配置された弾性層72aと、弾性層72aから突出し、リング状の形状を有するシーリング部72bとを有する。シーリング部72bは、液体のシーリング機能を有していればよく、シールゴムやOリングであってもよい。シーリング部72bの周囲であって、弾性層72aの上には、リング状の給電用端子である電極73が形成される。電極73は、図3(A)に示すように、環状形状を有していてもよいし、不連続に複数形成されていてもよい(図示せず)。電極73は、例えば、マスク治具70の上部に形成された外部接続端子74と配線75を介して電気的に接続されている。図3(A)に示すように、電極73に配線75が接続する部分を電気的接続部73aとする。電極73を囲むように、開口部71aと同心円の壁部76が電極73と離間して形成される。更に、開口部71aの外周と離間した位置には、複数のネジ孔77が形成されてもよい。ネジ孔77は、後述される裏蓋治具80をネジによって固定する際に用いることができる。

【0035】

図4(A)に示すように、例えば、裏蓋治具80は、大略すると蓋体81と複数(本実施形態では2本)の固定フレーム82とにより構成されていてよい。蓋体81は円盤状の部材であり、その大きさは半導体ウエハー3の直径よりも大きな直径を有していてもよい。固定フレーム82は、それぞれ貫通孔83が形成されてもよい。また、図4(B)に示すように、蓋体81の固定フレーム82が形成された面の反対の面には、シールゴム84が配置されてもよい。

【0036】

図5(A)〜図5(C)は、パターニング工程を経た半導体ウエハー10をめっき治具70に装着する工程を模式的に説明する図である。図5(A)に示すように、半導体ウエハー10の第1の導電層40、第1レジスト層51及び第3レジスト層53が形成された面をマスク治具70に向けて位置合わせをし、半導体ウエハー10をマスク治具70に装着する。位置合わせでは、図5(B)に示すように、電極73の電気的接続部73aが第1レジスト層51と接するように配置する。また、図5(C)に示すように、電極73は、第1の導電層40の第2の部分42と接することで、給電を行うことができる。詳細は後述される。位置合わせした後、図5(B)及び図5(C)に示すように、半導体ウエハー10をマスク治具70に搭載し、半導体ウエハー10をマスク治具70と裏蓋治具80とで固定する。図示はしないが、例えば、図示しないネジを用いてマスク治具70と半導体ウエハー10と裏蓋治具80とを固定する。このとき、図示されないネジを、裏蓋治具80の貫通孔83とマスク治具70のネジ孔77とを貫通さることによって裏蓋治具80を固定してもよい。しかしながら固定する方法は、これに限定されるものではない。

【0037】

半導体ウエハー10をマスク治具70と裏蓋治具80とで固定する工程は、半導体ウエハー10にマスク治具70を押し当てるように押圧する工程を含む。これにより、第2の領域30の第1の導電層40の第2の部分42は、押圧されて電極73と確実に接触する。例えば、ネジ孔77を所定のトルクで締め付けることによって、所定の押圧力を加えることができる。過剰な押圧力は、マスク治具70の弾性部材72や、裏蓋治具80のシールゴム84によって吸収される。

【0038】

図6は、半導体ウエハー10をマスク治具70に搭載した際の要部の積層構造を模式的に説明する図である。なお、図6は、半導体ウエハー10の側面側から見た場合の積層構造を示す。

【0039】

図6に示すように、第1の導電層40の第1の部分41には、第1レジスト層51が形成されている。したがって、電極73の電気的接続部73aとは接触しないため、第1の部分41と電気的接続部73aとは電気的には接続されない。第1レジスト層51の厚み分、電極73は基板71側に押され、弾性層72aが圧縮される。第1の導電層40の第2の部分42は、レジスト層50が設けられていないため、電極73と接触し、給電される。つまりは、電極73は、部分的に撓むことで第2の部分42と電気的に接続される。

【0040】

以上の工程により、第2の部分42と給電用端子である電極73とが確実に接触し、半導体ウエハー10はめっき治具70、80内に装着された半導体ウエハー100となる。

【0041】

次に、図7及び図8に示すように、半導体ウエハー100及びめっき治具70、80をめっき液中に配置し、電極73に電流を供給して、電解めっきにより第1の導電層40の上に第2の導電層120を形成する。

【0042】

電解めっき工程は、図7に示すように、めっき装置110を用いる。めっき装置110は、例えば、めっき液111が充填されためっき槽112と、電源113と、カソード電極114と、アノード電極115とを含む。例えば、銅めっきを行う場合、めっき液111は銅イオンを含み、アノード電極115は銅から構成される。図7に示すように、めっき液111にめっき治具70、80を浸し、めっき治具70、80の外部接続端子74とカソード電極114とを電気的に接続し、電源113から、カソード電極114、外部接続端子74、及び電極73を介して、電極73と接触している第1の導電層40の第2の部分42に給電される。つまりは、半導体ウエハー100の第1の領域20内の第1の導電層40に対して給電される。

【0043】

電解めっき工程により、図8(A)に示すように、第1の導電層40の上のレジスト層50が除去された部分に第2の導電層120が電解めっきによって形成される。第2の導電層120は、導電性の膜であれば特に限定されない。第2の導電層120は、例えば、銅(Cu)、チタンタングステン(TiW)、クロム(Cr)、チタン(Ti)、ニッケル(Ni)、金(Au)、アルミニウム(Al)、ニッケルバナジウム(NiV)、タングステン(W)のうちいずれか1つ又は複数を積層することで、形成されてもよい。

【0044】

図8(B)に示すように、第2の導電層120を形成した後、第3レジスト層53を除去してもよい。

【0045】

本実施の形態に係る半導体装置の製造方法は、例えば、以下の特徴を有する。

【0046】

本実施の形態に係る半導体装置の製造方法は、第2の領域30の第1の導電層40の第1の部分41の上の第1レジスト層51を残し、第2の領域30の第1の導電層40の第2の部分42の上の第2レジスト層52を除去するパターニング工程と、電極73と、電極73の電気的接続部73aに連続し、電極73に電流を供給する配線75と、を有する治具70、80を、電気的接続部73aが第1レジスト層51と接するように配置する工程と、を有する。これによれば、めっき治具70の電気的接続部73aが第1の導電層40と接触する部分を無くすことができる。電気的接続部73aは、カソード電極114と接続された外部接続端子74から延びる配線75が電極73に接続する部分であり、電流が集中しやすい箇所である。第1の導電層40の、この電気的接続部73aに対向する箇所を第1レジスト層51で覆うことにより、電気的接続部73a周辺においてめっき膜厚が厚くなる部分が形成されることを防ぐことができるため、めっき膜である第2の導電層120の膜厚が不均一に形成される不具合を低減することができる。したがって、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供することができる。

【0047】

(変形例)

以下、図面を参照して、本実施形態に係る半導体装置の製造方法の変形例の一例について説明する。図9及び図10は、本発明の実施の形態に係る半導体装置の製造方法の変形例の一例を模式的に説明する図である。

【0048】

まず、図9(A)に示すように、集積回路5を有する半導体ウエハー10を準備する。図9(A)は、複数の集積回路5が形成された半導体ウエハー10の第1の領域20の一部を拡大して示す断面図である。ここで、図9(A)に示すように、半導体ウエハー10の一方の面を第1の面12とする。

【0049】

半導体ウエハー10は、図9(A)に示すように、半導体ウエハー10の第1の面12の上に電極14を有してもよい。電極14は、半導体ウエハー10の内部に形成された集積回路5と内部配線(図示せず)によって電気的に接続されていてもよい。電極14は、半導体ウエハー10の内部配線の一部であってもよい。電極14が形成される領域は特に限定されるものではなく、図9(A)に示すように、第1の面12の下方に集積回路5が形成されていない領域において、形成されていてもよい。また、図示はしないが、電極14は、集積回路5とオーバーラップするように形成されていてもよい。電極14は、アルミニウム(Al)又は銅(Cu)等の金属で形成されていてもよい。また、図9(A)に示すように、半導体ウエハー10は、複数の電極14を含んでいてもよい。

【0050】

半導体ウエハー10は、図9(A)に示すように、絶縁膜16を有していてもよい。絶縁膜16はパッシベーション膜であってもよい。絶縁膜16は、電極14の少なくとも一部を露出させるように形成されていてもよい。絶縁膜16は、図9(A)に示すように、電極14を露出させる開口部16aを有する。絶縁膜16は、例えば、SiO2やSiN等の無機絶縁膜であってもよい。あるいは、絶縁膜16は、ポリイミド樹脂などの有機絶縁膜であってもよい。

【0051】

図9(A)に示すように、半導体ウエハー10の絶縁膜16の所望の領域に樹脂層141を形成してもよい。例えば、図9(A)に示すように、樹脂層141は、絶縁膜16の上であって、集積回路5とオーバーラップするように形成されてもよい。また、樹脂層141は、電極14の少なくとも一部が露出するように形成されていればよい。よって、図示はされないが、樹脂層141は、絶縁膜16の開口部16a内の電極14の一部とオーバーラップするように形成されてもよい。樹脂層141は、公知のいずれかの方法によって形成されてもよい。樹脂層141は、例えば、感光性の樹脂層を半導体ウエハー10上に形成した後、露光処理などによって所望の形状にパターンニングされて形成されてもよい(図示せず)。

【0052】

樹脂層141は、応力緩和機能を有していてもよい。樹脂層141は、例えば、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、ベンゾシクロブテン(BCB;benzocyclobutene),ポリベンゾオキサゾール(PBO;polybenzoxazole)などの樹脂で形成されていてもよい。

【0053】

次に、図2(A)及び図9(B)に示すように、第1の領域20及び第2の領域30に第1の導電層40を形成する。このとき、図9(B)に示すように、第1の領域20において、第1の導電層40は、半導体ウエハー10の電極14、絶縁膜16及び、樹脂層141を連続して覆うことができる。なお、第1の導電層40の詳細は上述されているため、省略する。

【0054】

次に、図2(B)及び図9(C)に示すように、第1の導電層40の上にレジスト層50(例えばソルダーレジスト層)を形成する。次に、図3(C)及び図3(D)に示すように、レジスト層50をパターニングする。ここで、図9(D)に示すように、後述される電解めっき処理により第2の導電層120を形成したい部分において第1の導電層40が露出するように、レジスト層50を除去し、第3レジスト層53を形成する。ここで、図9(D)に示すように、第1の導電層40の電極14の上から樹脂層141の上に至るように延びる部分が露出するように、レジスト層50を除去してもよい。

【0055】

次に、図5から図7に示すように、半導体ウエハー100は、本実施形態に係るめっき治具70、80に搭載され、電解めっき処理される。めっき治具70、80の詳細、搭載工程及び電解めっき工程は上述されているため省略する。

【0056】

本実施形態に係る半導体装置の製造方法によって、図10(A)に示すように、第1の領域20に第2の導電層120が形成される。ここで、図10(A)に示すように、第1の領域20において、第1の導電層40の露出した部分に第2の導電層120が形成される。第2の導電層120の材質は特に限定されないが、例えばCuからなる導電層であってもよい。また、電解めっき工程の時間等を調整することにより、所望の膜厚有するように第2の導電層120を形成してもよい。

【0057】

次に、図10(B)に示すように、第3レジスト層53を除去する。図10(B)に示すように、第3レジスト層53が除去された後、第1の領域20には、第1の導電層40のみが形成されている部分と第1の導電層40と第2の導電層120との積層となっている部分が形成される。次に、第2の導電層120をエッチングマスクとして、第1の導電層40が露出している部分を除去してもよい。言い換えれば、第2の導電層120が上方に形成されていない第1の導電層40をエッチングにより除去してもよい。これによって、図10(C)に示すように、第1の導電層40及び第2の導電層120の積層からなる第3の導電層130を形成してもよい。図10(C)に示すように、第3の導電層130は、絶縁膜16の開口部16a内に形成された電極14と電気的に接続し、電極14の上から樹脂層141の上面に至るように連続して形成されていてもよい。言い換えれば、第3の導電層130は、電極14に電気的に接続された配線であってもよい。図10(C)に示すように、第3の導電層130は、電極14と電気的に接続されている限りその形状は限定されず、電極14の露出面を全て覆っていてもよいし、電極14の露出面の一部とのみ電気的に接続されていてもよい(図示せず)。

【0058】

次に、図10(D)に示すように、第3の導電層130、樹脂層141、及び絶縁層16の上に所望の形状にパターニングされたソルダーレジスト層140を形成する。ソルダーレジスト層140の形状は特に限定されない。例えば、樹脂層141の上に形成された第3の導電層130の少なくとも一部が露出するように、ソルダーレジスト層140をパターニングしてもよい。ここで、図10(D)に示すように、第3の導電層130のソルダーレジスト層140に覆われていない部分は、ランド部131であってもよい。ここでソルダーレジスト層140は、絶縁性を有する封止剤であれば特に限定されるものではない。例えば、ソルダーレジスト層140は公知の樹脂から形成されていてもよい。具体的には、ソルダーレジスト層140は、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、ベンゾシクロブテン(BCB;benzocyclobutene)、ポリベンゾオキサゾール(PBO;polybenzoxazole)、フェノール樹脂等の樹脂で形成されていてもよい。

【0059】

また、図10(D)に示すように、ランド部131の上に外部端子150が形成されてもよい。外部端子150は、導電性を有する材料であれば特に限定されるものではなく、例えば半田ペーストから形成された半田バンプ(ソルダーボール)であってもよい。以上により、半導体装置1000を製造することができる。

【0060】

本実施形態に係る半導体装置の製造方法の変形例は以上のいずれかの構成をとることができる。

【0061】

本実施形態に係る半導体装置の製造方法の変形例によれば、電解めっき工程において、めっき治具70、80の電気的接続部73aが第1の導電層40と接触しない。これによれば、第2の導電層120(第3の導電層130)の膜厚を均一に形成することができるため、半導体装置1000の製造工程の歩留まりを向上させることができる。

【0062】

上記のように、本発明の実施の形態について詳細に説明したが、本発明の新規事項及び効果から実体的に逸脱しない多くの変形が可能であることは、当業者には容易に理解できよう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。

【符号の説明】

【0063】

5 集積回路、10(100) 半導体ウエハー、11 個別チップ領域、

12 第1の面、14 電極、16 絶縁膜、16a 開口部、20 第1の領域、

30 第2の領域、40 第1の導電層、41 第1の部分、42 第2の部分、

50 レジスト層、51 第1レジスト層、52 第2レジスト層、

53 第3レジスト層、70、80 めっき治具、70 マスク治具、71 基板、

71a 開口部、72 弾性部材、72a 弾性層、72b シーリング部、

73 電極、73a 電気的接続部、74 外部接続端子、75 配線、76 壁部、

77 ネジ孔、80 裏蓋治具、81 蓋体、82 固定フレーム、83 貫通孔、

84 シールゴム、110 めっき装置、111 めっき液、112 めっき槽、

113 電源、114 カソード電極、115 アノード電極、120 第2の導電層、130 第3の導電層、131 ランド部、140 ソルダーレジスト層、

150 外部端子、1000 半導体装置。

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

給電部であるリング状電極を有し、その電極とめっき液とを遮断するためのシーリング部材を有した半導体ウエハー用のめっき治具が知られている(特許文献1)。めっき治具には、外部端子が設けられ、そこから供給された電流は、めっき治具内に埋め込まれた配線を経由してリング状電極に給電される。

【0003】

例えば、WCSP(Wafer Level Chip Size Package)構造を有する半導体装置の製造工程において、このようなめっき治具を用いて半導体ウエハーに電解めっき処理を行う場合、半導体ウエハー上に導電層を形成し、電解めっき用のレジスト層を形成し、リング状電極と導電層とを接触させるために外周部分のレジスト層を除去して導電層を露出させ、めっき治具のリング状電極と外周部分の導電層とを接触させて給電を行う(特許文献1)。

【0004】

しかしながら、上述のようにリング電極には、配線を経由して電流が給電されるため、リング電極の配線との電気的接続部に電流が集中しやすく、リング電極の電気的接続部周辺のめっき成長が促進され、めっき膜厚が部分的に厚くなってしまい、膜厚の均一性を担保することが難しかった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−287648号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、以上のような問題点に鑑みてなされたものであり、本発明のいくつかの態様によれば、電解めっき工程において、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供することができる。

【課題を解決するための手段】

【0007】

(1)本形態に係る半導体装置の製造方法は、集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーを用意する工程と、前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、前記第1の導電層の上にレジスト層を形成する工程と、前記第2の領域の前記第1の導電層の第1の部分の上に位置する、前記レジスト層の一部である第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上に位置する、前記レジスト層の一部である第2レジスト層を除去するパターニング工程と、電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、前記半導体ウエハー及び前記治具をめっき液中に配置し、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、を有する。

【0008】

本発明によれば、電解めっき工程において、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供することができる。

【0009】

(2)本形態に係る半導体装置の製造方法において、治具70は基板と、前記電極と前記基板との間に配置された弾性層と、を更に有し、前記第2の領域の前記第1の導電層の第2の部分は、押圧されて前記電極と接触してもよい。

【0010】

これによれば、より安定的に第1の導電層の第2の部分を治具の電極に接触させることができる。

【0011】

(3)本形態に係る半導体装置の製造方法において、前記半導体ウエハーは、切断ラインによって区画される複数の個別チップ領域を有し、前記パターニング工程において、前記第1レジストは、前記第2の領域の複数の個別チップ領域の上方に残るようにパターニングされてもよい。

【0012】

(4)本形態に係る半導体装置の製造方法において、前記パターニング工程において、前記レジスト層は、前記第1の領域において所望の形状にパターニングされ、前記第2の導電層は、前記第1の領域の前記第1の導電層の上に形成されてもよい。

【図面の簡単な説明】

【0013】

【図1】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図2】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図3】めっき治具を模式的に説明する図。

【図4】めっき治具を模式的に説明する図。

【図5】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図6】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図7】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図8】本実施形態に係る半導体装置の製造方法を模式的に説明する図。

【図9】本実施形態に係る半導体装置の製造方法の変形例を模式的に説明する図。

【図10】本実施形態に係る半導体装置の製造方法の変形例を模式的に説明する図。

【発明を実施するための形態】

【0014】

以下に、本発明を適用した実施の形態について図面を参照して説明する。ただし、本発明は以下の実施の形態のみに限定されるものではない。本発明は、以下の実施の形態及び変形例を自由に組み合わせたものを含むものとする。

【0015】

以下、図面を参照して、本実施の形態に係る半導体装置の製造及び半導体ウエハーについて説明する。

【0016】

図1、2、5〜8は、本実施の形態に係る半導体装置の製造方法を模式的に説明する図である。図3及び4は、本実施形態に係る半導体装置の製造方法に用いるめっき治具を模式的に説明する図である。

【0017】

ここで、図1(A)は半導体ウエハー10の平面図であり、図1(B)は図1(A)のIB−IB線断面図である。図2(A)〜図2(E)は、図1(B)に対応し、半導体装置の製造方法を説明する断面図である。

【0018】

なお、本実施形態の説明において、「平面図」という文言は、半導体ウエハーの電極や配線などが形成される面を法線方向から見た場合の平面図という意味で用いる。

【0019】

本実施の形態に係る半導体装置の製造方法は、集積回路5が形成された第1の領域20と、第1の領域20を囲む第2の領域30と、を有する半導体ウエハー10を用意する工程と、第1の領域20及び第2の領域30に第1の導電層40を形成する工程と、第1の導電層40の上にレジスト層50を形成する工程と、第2の領域30の第1の導電層40の第1の部分41の上の第1レジスト層51を残し、第2の領域30の第1の導電層40の第2の部分42の上の第2レジスト層52を除去するパターニング工程と、電極73と、電極73の電気的接続部73aに連続し、電極73に電流を供給する配線75と、を有する治具70、80を、電気的接続部73aが第1レジスト層51と接するように配置する工程と、半導体ウエハー10及び治具70、80をめっき液中に配置し、電極73に前記電流を供給して、電解めっきにより第1の導電層40の上に第2の導電層120を形成する工程と、を有する。

【0020】

半導体ウエハーを用意する工程において用意される半導体ウエハー10は、例えば、シリコンウエハーからなる半導体基板10であってもよい。半導体ウエハー10の平面形状は、例えば、略円形であってもよい。図1(A)に示すように、一部が切り欠かれていてもよい。また、半導体ウエハー10は、複数に分割されてなる分割基板であってもよい(図示せず)。

【0021】

半導体ウエハー10は、図1(A)に示すように、有効チップ領域である第1の領域20(図1(A)の灰色で示された領域)と、第1の領域20を囲む第2の領域30(図1(A)の白色で示された領域)と、を有する。

【0022】

第1の領域20は、有効チップ領域であって、製品となる半導体チップを含む領域であってよい。また、第1の領域20には、集積回路5が形成されている。図1(B)に示すように、第1の領域20には複数の集積回路5が形成されていてもよい。図1(B)に示すように、第1の領域20は、半導体ウエハー10の中央部に形成してもよい。図1(A)に示すように、切断ラインLは、隣り合った半導体チップとなる部分の境界線を示すものである。半導体ウエハー10は、切断ラインLによって区画された複数の個別チップ領域11を有する。よって、第1の領域20の切断ラインLによって区画された1つの個別チップ領域11は、切断されて半導体チップとなる領域である。それぞれの個別チップ領域11において、一つの集積回路5及び図示されない保護膜16(パッシベーション膜)、集積回路5に接続される電極14等の構造体を含んでいてもよい(図9、10参照)。

【0023】

第2の領域30は、図1(A)及び図1(B)に示すように、第1の領域20を囲む領域である。第2の領域30は、製品とならない半導体チップを含む領域であってもよい。図1(A)に示すように、第2の領域30においても、複数の個別チップ領域11が形成される。なお、半導体ウエハー10の第1の領域20及び第2の領域30の配置は、半導体装置のデザインの際に適宜決定される設計事項である。

【0024】

次に、図2(A)に示すように、半導体ウエハー10の第1の領域20及び第2の領域30に第1の導電層40を形成する。第1の導電層40は、公知のいずれかの成膜方法によって形成されてもよい。例えば、第1の導電層40は、スパッタリング法等を用いて形成されてもよい。第1の導電層40は、半導体ウエハー10の全面に形成されてもよい。また、第1の導電層40は、所望の形状にパターニングされていてもよい(図示せず)。第1の導電層40は、導電性の膜であれば特に限定されない。第1の導電層40は、例えば、銅(Cu)、チタンタングステン(TiW)、クロム(Cr)、チタン(Ti)、ニッケル(Ni)、金(Au)、アルミニウム(Al)、ニッケルバナジウム(NiV)、タングステン(W)のうちいずれか1つ又は複数を積層することで、形成されてもよい。

【0025】

図2(A)に示すように、第2の領域30の第1の導電層40の一部を第1の部分41とする。第1の部分41は、後述されるパターニング工程において、第1レジスト51が形成される部分である。図示はされないが、第2の部分42は、第2の領域30の第1の導電層40第1の部分41を除く部分である。

【0026】

第2の領域30における第1の部分41の配置は、特に限定されず、後述されるめっき治具の電極73の電気的接続部73aの配置に対応して適宜決定される。第1の部分41は、半導体ウエハー10がめっき治具70に装着される場合に電極73の電気的接続部73aと対向する箇所(以下、「対向箇所」とも言う。)を、少なくとも含む部分である。例えば、対向箇所が上方に位置する個別チップ領域11の上に形成された第1の導電層40を第1の部分41としてもよい。また、例えば、第1の導電層40の対向箇所が上方に位置する個別チップ領域11と、該個別チップ領域11周辺の複数の個別チップ領域11の上に形成された第1の導電層40を第1の部分41としてもよい。

【0027】

図2(B)に示すように、第1の導電層40の上にレジスト層50(例えばソルダーレジスト層)を形成する。レジスト層50は、感光性の樹脂であってもよい。レジスト層50は、めっき用レジストであってもよい。レジスト層50は、第1の領域20及び第2の領域30を覆うように形成される。

【0028】

次に、図2(C)及び図2(D)に示すように、レジスト層50をパターニングする。パターニング工程においては、第2の領域30の第1の導電層40の第1の部分41の上に位置する、レジスト層50の一部である第1レジスト層51を残し、第2の領域30の第1の導電層40の第2の部分42の上に位置するレジスト層50の一部である第2レジスト層52を除去する。言い換えれば、図2(C)に示すように、第1の部分41は、第1レジスト層51によって覆われる。また、図2(D)に示すように、第2の部分42は、第2レジスト層52が除去され、露出する。

【0029】

レジスト層50をパターニングする方法は特に限定されず、例えば、露光処理及び現像処理によってエッチングされ、パターニングされてもよい。ここで、第1の領域20に形成されたレジスト層50は、所望の形状にパターニングされ、第3レジスト層53が形成される。

【0030】

ここで、図2(C)に示すように、第1レジスト層51と第3レジスト層53は、不連続に形成されていてもよい。また、図2(E)に示すように、第1レジスト層51と第3レジスト層53は、連続するように形成されていてもよい。

【0031】

次に、第1の導電層40に給電して、電解めっきにより第1の導電層40の上に第2の導電層120を形成する電解めっき工程が実施される。

【0032】

図3〜図8はめっき治具70、80と、半導体ウエハー10を電解めっきする工程を説明する図である。

【0033】

なお、図3及び図4は模式的にめっき治具70、80を示すものであり、形状はこれに限定されるものではない。めっき治具70、80は、大略すると図3に示されるマスク治具70と、図4に示される裏蓋治具80とにより構成される。図3(A)は、マスク治具70の正面図であり、図3(B)は、マスク治具70の断面図である。また、図4(A)は、裏蓋治具80の正面図であり、図4(B)は裏蓋治具80の断面図である。

【0034】

図3(A)及び図3(B)に示すように、マスク治具70は、例えば、基板71の中央下部に開口部71aが形成される。開口部71aの周縁部には環状形状を有した弾性部材72が形成される。弾性部材72は、弾性を有する材料からなる部材であれば特に限定されず、例えばシリコンゴムであってもよい。弾性部材72は、電極73と基板71との間に配置された弾性層72aと、弾性層72aから突出し、リング状の形状を有するシーリング部72bとを有する。シーリング部72bは、液体のシーリング機能を有していればよく、シールゴムやOリングであってもよい。シーリング部72bの周囲であって、弾性層72aの上には、リング状の給電用端子である電極73が形成される。電極73は、図3(A)に示すように、環状形状を有していてもよいし、不連続に複数形成されていてもよい(図示せず)。電極73は、例えば、マスク治具70の上部に形成された外部接続端子74と配線75を介して電気的に接続されている。図3(A)に示すように、電極73に配線75が接続する部分を電気的接続部73aとする。電極73を囲むように、開口部71aと同心円の壁部76が電極73と離間して形成される。更に、開口部71aの外周と離間した位置には、複数のネジ孔77が形成されてもよい。ネジ孔77は、後述される裏蓋治具80をネジによって固定する際に用いることができる。

【0035】

図4(A)に示すように、例えば、裏蓋治具80は、大略すると蓋体81と複数(本実施形態では2本)の固定フレーム82とにより構成されていてよい。蓋体81は円盤状の部材であり、その大きさは半導体ウエハー3の直径よりも大きな直径を有していてもよい。固定フレーム82は、それぞれ貫通孔83が形成されてもよい。また、図4(B)に示すように、蓋体81の固定フレーム82が形成された面の反対の面には、シールゴム84が配置されてもよい。

【0036】

図5(A)〜図5(C)は、パターニング工程を経た半導体ウエハー10をめっき治具70に装着する工程を模式的に説明する図である。図5(A)に示すように、半導体ウエハー10の第1の導電層40、第1レジスト層51及び第3レジスト層53が形成された面をマスク治具70に向けて位置合わせをし、半導体ウエハー10をマスク治具70に装着する。位置合わせでは、図5(B)に示すように、電極73の電気的接続部73aが第1レジスト層51と接するように配置する。また、図5(C)に示すように、電極73は、第1の導電層40の第2の部分42と接することで、給電を行うことができる。詳細は後述される。位置合わせした後、図5(B)及び図5(C)に示すように、半導体ウエハー10をマスク治具70に搭載し、半導体ウエハー10をマスク治具70と裏蓋治具80とで固定する。図示はしないが、例えば、図示しないネジを用いてマスク治具70と半導体ウエハー10と裏蓋治具80とを固定する。このとき、図示されないネジを、裏蓋治具80の貫通孔83とマスク治具70のネジ孔77とを貫通さることによって裏蓋治具80を固定してもよい。しかしながら固定する方法は、これに限定されるものではない。

【0037】

半導体ウエハー10をマスク治具70と裏蓋治具80とで固定する工程は、半導体ウエハー10にマスク治具70を押し当てるように押圧する工程を含む。これにより、第2の領域30の第1の導電層40の第2の部分42は、押圧されて電極73と確実に接触する。例えば、ネジ孔77を所定のトルクで締め付けることによって、所定の押圧力を加えることができる。過剰な押圧力は、マスク治具70の弾性部材72や、裏蓋治具80のシールゴム84によって吸収される。

【0038】

図6は、半導体ウエハー10をマスク治具70に搭載した際の要部の積層構造を模式的に説明する図である。なお、図6は、半導体ウエハー10の側面側から見た場合の積層構造を示す。

【0039】

図6に示すように、第1の導電層40の第1の部分41には、第1レジスト層51が形成されている。したがって、電極73の電気的接続部73aとは接触しないため、第1の部分41と電気的接続部73aとは電気的には接続されない。第1レジスト層51の厚み分、電極73は基板71側に押され、弾性層72aが圧縮される。第1の導電層40の第2の部分42は、レジスト層50が設けられていないため、電極73と接触し、給電される。つまりは、電極73は、部分的に撓むことで第2の部分42と電気的に接続される。

【0040】

以上の工程により、第2の部分42と給電用端子である電極73とが確実に接触し、半導体ウエハー10はめっき治具70、80内に装着された半導体ウエハー100となる。

【0041】

次に、図7及び図8に示すように、半導体ウエハー100及びめっき治具70、80をめっき液中に配置し、電極73に電流を供給して、電解めっきにより第1の導電層40の上に第2の導電層120を形成する。

【0042】

電解めっき工程は、図7に示すように、めっき装置110を用いる。めっき装置110は、例えば、めっき液111が充填されためっき槽112と、電源113と、カソード電極114と、アノード電極115とを含む。例えば、銅めっきを行う場合、めっき液111は銅イオンを含み、アノード電極115は銅から構成される。図7に示すように、めっき液111にめっき治具70、80を浸し、めっき治具70、80の外部接続端子74とカソード電極114とを電気的に接続し、電源113から、カソード電極114、外部接続端子74、及び電極73を介して、電極73と接触している第1の導電層40の第2の部分42に給電される。つまりは、半導体ウエハー100の第1の領域20内の第1の導電層40に対して給電される。

【0043】

電解めっき工程により、図8(A)に示すように、第1の導電層40の上のレジスト層50が除去された部分に第2の導電層120が電解めっきによって形成される。第2の導電層120は、導電性の膜であれば特に限定されない。第2の導電層120は、例えば、銅(Cu)、チタンタングステン(TiW)、クロム(Cr)、チタン(Ti)、ニッケル(Ni)、金(Au)、アルミニウム(Al)、ニッケルバナジウム(NiV)、タングステン(W)のうちいずれか1つ又は複数を積層することで、形成されてもよい。

【0044】

図8(B)に示すように、第2の導電層120を形成した後、第3レジスト層53を除去してもよい。

【0045】

本実施の形態に係る半導体装置の製造方法は、例えば、以下の特徴を有する。

【0046】

本実施の形態に係る半導体装置の製造方法は、第2の領域30の第1の導電層40の第1の部分41の上の第1レジスト層51を残し、第2の領域30の第1の導電層40の第2の部分42の上の第2レジスト層52を除去するパターニング工程と、電極73と、電極73の電気的接続部73aに連続し、電極73に電流を供給する配線75と、を有する治具70、80を、電気的接続部73aが第1レジスト層51と接するように配置する工程と、を有する。これによれば、めっき治具70の電気的接続部73aが第1の導電層40と接触する部分を無くすことができる。電気的接続部73aは、カソード電極114と接続された外部接続端子74から延びる配線75が電極73に接続する部分であり、電流が集中しやすい箇所である。第1の導電層40の、この電気的接続部73aに対向する箇所を第1レジスト層51で覆うことにより、電気的接続部73a周辺においてめっき膜厚が厚くなる部分が形成されることを防ぐことができるため、めっき膜である第2の導電層120の膜厚が不均一に形成される不具合を低減することができる。したがって、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供することができる。

【0047】

(変形例)

以下、図面を参照して、本実施形態に係る半導体装置の製造方法の変形例の一例について説明する。図9及び図10は、本発明の実施の形態に係る半導体装置の製造方法の変形例の一例を模式的に説明する図である。

【0048】

まず、図9(A)に示すように、集積回路5を有する半導体ウエハー10を準備する。図9(A)は、複数の集積回路5が形成された半導体ウエハー10の第1の領域20の一部を拡大して示す断面図である。ここで、図9(A)に示すように、半導体ウエハー10の一方の面を第1の面12とする。

【0049】

半導体ウエハー10は、図9(A)に示すように、半導体ウエハー10の第1の面12の上に電極14を有してもよい。電極14は、半導体ウエハー10の内部に形成された集積回路5と内部配線(図示せず)によって電気的に接続されていてもよい。電極14は、半導体ウエハー10の内部配線の一部であってもよい。電極14が形成される領域は特に限定されるものではなく、図9(A)に示すように、第1の面12の下方に集積回路5が形成されていない領域において、形成されていてもよい。また、図示はしないが、電極14は、集積回路5とオーバーラップするように形成されていてもよい。電極14は、アルミニウム(Al)又は銅(Cu)等の金属で形成されていてもよい。また、図9(A)に示すように、半導体ウエハー10は、複数の電極14を含んでいてもよい。

【0050】

半導体ウエハー10は、図9(A)に示すように、絶縁膜16を有していてもよい。絶縁膜16はパッシベーション膜であってもよい。絶縁膜16は、電極14の少なくとも一部を露出させるように形成されていてもよい。絶縁膜16は、図9(A)に示すように、電極14を露出させる開口部16aを有する。絶縁膜16は、例えば、SiO2やSiN等の無機絶縁膜であってもよい。あるいは、絶縁膜16は、ポリイミド樹脂などの有機絶縁膜であってもよい。

【0051】

図9(A)に示すように、半導体ウエハー10の絶縁膜16の所望の領域に樹脂層141を形成してもよい。例えば、図9(A)に示すように、樹脂層141は、絶縁膜16の上であって、集積回路5とオーバーラップするように形成されてもよい。また、樹脂層141は、電極14の少なくとも一部が露出するように形成されていればよい。よって、図示はされないが、樹脂層141は、絶縁膜16の開口部16a内の電極14の一部とオーバーラップするように形成されてもよい。樹脂層141は、公知のいずれかの方法によって形成されてもよい。樹脂層141は、例えば、感光性の樹脂層を半導体ウエハー10上に形成した後、露光処理などによって所望の形状にパターンニングされて形成されてもよい(図示せず)。

【0052】

樹脂層141は、応力緩和機能を有していてもよい。樹脂層141は、例えば、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、ベンゾシクロブテン(BCB;benzocyclobutene),ポリベンゾオキサゾール(PBO;polybenzoxazole)などの樹脂で形成されていてもよい。

【0053】

次に、図2(A)及び図9(B)に示すように、第1の領域20及び第2の領域30に第1の導電層40を形成する。このとき、図9(B)に示すように、第1の領域20において、第1の導電層40は、半導体ウエハー10の電極14、絶縁膜16及び、樹脂層141を連続して覆うことができる。なお、第1の導電層40の詳細は上述されているため、省略する。

【0054】

次に、図2(B)及び図9(C)に示すように、第1の導電層40の上にレジスト層50(例えばソルダーレジスト層)を形成する。次に、図3(C)及び図3(D)に示すように、レジスト層50をパターニングする。ここで、図9(D)に示すように、後述される電解めっき処理により第2の導電層120を形成したい部分において第1の導電層40が露出するように、レジスト層50を除去し、第3レジスト層53を形成する。ここで、図9(D)に示すように、第1の導電層40の電極14の上から樹脂層141の上に至るように延びる部分が露出するように、レジスト層50を除去してもよい。

【0055】

次に、図5から図7に示すように、半導体ウエハー100は、本実施形態に係るめっき治具70、80に搭載され、電解めっき処理される。めっき治具70、80の詳細、搭載工程及び電解めっき工程は上述されているため省略する。

【0056】

本実施形態に係る半導体装置の製造方法によって、図10(A)に示すように、第1の領域20に第2の導電層120が形成される。ここで、図10(A)に示すように、第1の領域20において、第1の導電層40の露出した部分に第2の導電層120が形成される。第2の導電層120の材質は特に限定されないが、例えばCuからなる導電層であってもよい。また、電解めっき工程の時間等を調整することにより、所望の膜厚有するように第2の導電層120を形成してもよい。

【0057】

次に、図10(B)に示すように、第3レジスト層53を除去する。図10(B)に示すように、第3レジスト層53が除去された後、第1の領域20には、第1の導電層40のみが形成されている部分と第1の導電層40と第2の導電層120との積層となっている部分が形成される。次に、第2の導電層120をエッチングマスクとして、第1の導電層40が露出している部分を除去してもよい。言い換えれば、第2の導電層120が上方に形成されていない第1の導電層40をエッチングにより除去してもよい。これによって、図10(C)に示すように、第1の導電層40及び第2の導電層120の積層からなる第3の導電層130を形成してもよい。図10(C)に示すように、第3の導電層130は、絶縁膜16の開口部16a内に形成された電極14と電気的に接続し、電極14の上から樹脂層141の上面に至るように連続して形成されていてもよい。言い換えれば、第3の導電層130は、電極14に電気的に接続された配線であってもよい。図10(C)に示すように、第3の導電層130は、電極14と電気的に接続されている限りその形状は限定されず、電極14の露出面を全て覆っていてもよいし、電極14の露出面の一部とのみ電気的に接続されていてもよい(図示せず)。

【0058】

次に、図10(D)に示すように、第3の導電層130、樹脂層141、及び絶縁層16の上に所望の形状にパターニングされたソルダーレジスト層140を形成する。ソルダーレジスト層140の形状は特に限定されない。例えば、樹脂層141の上に形成された第3の導電層130の少なくとも一部が露出するように、ソルダーレジスト層140をパターニングしてもよい。ここで、図10(D)に示すように、第3の導電層130のソルダーレジスト層140に覆われていない部分は、ランド部131であってもよい。ここでソルダーレジスト層140は、絶縁性を有する封止剤であれば特に限定されるものではない。例えば、ソルダーレジスト層140は公知の樹脂から形成されていてもよい。具体的には、ソルダーレジスト層140は、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、ベンゾシクロブテン(BCB;benzocyclobutene)、ポリベンゾオキサゾール(PBO;polybenzoxazole)、フェノール樹脂等の樹脂で形成されていてもよい。

【0059】

また、図10(D)に示すように、ランド部131の上に外部端子150が形成されてもよい。外部端子150は、導電性を有する材料であれば特に限定されるものではなく、例えば半田ペーストから形成された半田バンプ(ソルダーボール)であってもよい。以上により、半導体装置1000を製造することができる。

【0060】

本実施形態に係る半導体装置の製造方法の変形例は以上のいずれかの構成をとることができる。

【0061】

本実施形態に係る半導体装置の製造方法の変形例によれば、電解めっき工程において、めっき治具70、80の電気的接続部73aが第1の導電層40と接触しない。これによれば、第2の導電層120(第3の導電層130)の膜厚を均一に形成することができるため、半導体装置1000の製造工程の歩留まりを向上させることができる。

【0062】

上記のように、本発明の実施の形態について詳細に説明したが、本発明の新規事項及び効果から実体的に逸脱しない多くの変形が可能であることは、当業者には容易に理解できよう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。

【符号の説明】

【0063】

5 集積回路、10(100) 半導体ウエハー、11 個別チップ領域、

12 第1の面、14 電極、16 絶縁膜、16a 開口部、20 第1の領域、

30 第2の領域、40 第1の導電層、41 第1の部分、42 第2の部分、

50 レジスト層、51 第1レジスト層、52 第2レジスト層、

53 第3レジスト層、70、80 めっき治具、70 マスク治具、71 基板、

71a 開口部、72 弾性部材、72a 弾性層、72b シーリング部、

73 電極、73a 電気的接続部、74 外部接続端子、75 配線、76 壁部、

77 ネジ孔、80 裏蓋治具、81 蓋体、82 固定フレーム、83 貫通孔、

84 シールゴム、110 めっき装置、111 めっき液、112 めっき槽、

113 電源、114 カソード電極、115 アノード電極、120 第2の導電層、130 第3の導電層、131 ランド部、140 ソルダーレジスト層、

150 外部端子、1000 半導体装置。

【特許請求の範囲】

【請求項1】

集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーを用意する工程と、

前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、

前記第1の導電層の上にレジスト層を形成する工程と、

前記第2の領域の前記第1の導電層の第1の部分の上に位置する、前記レジスト層の一部である第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上に位置する、前記レジスト層の一部である第2レジスト層を除去するパターニング工程と、

電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、

前記半導体ウエハー及び前記治具をめっき液中に配置し、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、

を有する、半導体装置の製造方法。

【請求項2】

請求項1において、

前記治具は基板と、前記電極と前記基板との間に配置された弾性層と、を更に有し、

前記第2の領域の前記第1の導電層の第2の部分は、押圧されて前記電極と接触する、半導体装置の製造方法。

【請求項3】

請求項1又は2において、

前記半導体ウエハーは、切断ラインによって区画される複数の個別チップ領域を有し、

前記パターニング工程において、前記第1レジストは、前記第2の領域の複数の個別チップ領域の上方に残るようにパターニングされる、半導体装置の製造方法。

【請求項4】

請求項1から3のいずれか1項において、

前記パターニング工程において、前記レジスト層は、前記第1の領域において所望の形状にパターニングされ、

前記第2の導電層は、前記第1の領域の前記第1の導電層の上に形成される、半導体装置の製造方法。

【請求項1】

集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーを用意する工程と、

前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、

前記第1の導電層の上にレジスト層を形成する工程と、

前記第2の領域の前記第1の導電層の第1の部分の上に位置する、前記レジスト層の一部である第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上に位置する、前記レジスト層の一部である第2レジスト層を除去するパターニング工程と、

電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、

前記半導体ウエハー及び前記治具をめっき液中に配置し、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、

を有する、半導体装置の製造方法。

【請求項2】

請求項1において、

前記治具は基板と、前記電極と前記基板との間に配置された弾性層と、を更に有し、

前記第2の領域の前記第1の導電層の第2の部分は、押圧されて前記電極と接触する、半導体装置の製造方法。

【請求項3】

請求項1又は2において、

前記半導体ウエハーは、切断ラインによって区画される複数の個別チップ領域を有し、

前記パターニング工程において、前記第1レジストは、前記第2の領域の複数の個別チップ領域の上方に残るようにパターニングされる、半導体装置の製造方法。

【請求項4】

請求項1から3のいずれか1項において、

前記パターニング工程において、前記レジスト層は、前記第1の領域において所望の形状にパターニングされ、

前記第2の導電層は、前記第1の領域の前記第1の導電層の上に形成される、半導体装置の製造方法。

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図1】

【公開番号】特開2012−193426(P2012−193426A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−59051(P2011−59051)

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]