半導体装置の製造方法

【課題】膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

LSIの微細化に伴い、露光プロセスのマージンが不足してきている。これを補うには、レジスト膜の膜厚を薄くして解像性を向上させることが有効である。しかし、一方でレジスト膜の膜厚を薄くすると被加工膜のエッチングに必要なレジスト膜厚を確保できなくなるという問題が生じる。かかる問題に対して、例えば、被加工膜上に下層膜、上層膜およびレジスト膜を形成し、レジストパターンを上層膜および下層膜に順次転写して膜パターンを形成した後、下層膜の膜パターンをエッチングマスクとして被加工膜の加工を行う手法が知られている。このように、レジスト膜とその他の上層膜および下層膜による多層マスクを用いて所望の膜をエッチングする手法において、下層膜はエッチングマスクとして作用する必要があり、スパッタリングされにくく、エッチング耐性がある炭素原子を多く含む材料が好ましい。そのため、多層マスクの下層膜として、カーボン膜(SOC:Spin On Carbon膜)を用いる場合がある。また、さらに、かかる下層膜の膜パターンを芯材として側壁に別の膜パターンを形成し、上述した下層膜ではなく、かかる側壁の膜パターンをエッチングマスクとした被加工膜の加工を行なうこともある。

【0003】

しかしながら、かかるカーボン膜を例えば微細なライン状の膜パターンとして残したときに、カーボン膜の膜パターンが倒れてしまう場合があるといった問題があった。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−205755号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、上述した問題点を克服し、膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

【図面の簡単な説明】

【0007】

【図1】第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図2】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図3】第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力について説明するための概念図である。

【図4】第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力による問題点について説明するための概念図である。

【図5】第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の膜パターンの倒れた状態の一例を示す図である。

【図6】被加工膜上に低ガラス転移温度膜を形成した場合の残留応力について説明するための概念図である。

【図7】被加工膜上に低ガラス転移温度膜を形成した場合の膜パターンの倒れのない状態の一例を示す図である。

【図8】第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合の問題点を説明するための概念図である。

【図9】第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合のクラックが発生した状態の一例を示す図である。

【図10】高ガラス転移温度膜上にSOG膜を形成した場合の様子を説明するための概念図である。

【図11】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図12】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図13】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図14】第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの断面を撮像した図である。

【図15】第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの幅寸法の変化の一例を示すグラフである。

【発明を実施するための形態】

【0008】

(第1の実施形態)

以下、図面を用いて説明する。

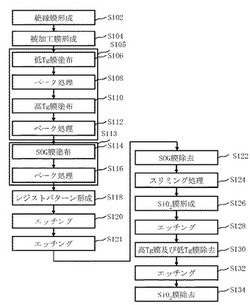

図1に、第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図が示されている。図1において、第1の実施形態における半導体装置の製造方法は、絶縁膜形成工程(S102)と、被加工膜形成工程(S104)と、積層膜形成工程(S105)と、SOG(Spin On Glass)膜形成工程(S113)と、レジストパターン形成工程(S118)と、エッチング工程(S120)と、エッチング工程(S121)と、SOG膜除去工程(S122)と、スリミング処理工程(S124)と、SiO2膜形成工程(S126)と、エッチバック処理工程(S128)と、高ガラス転移温度(高Tg)膜および低ガラス転移温度(低Tg)膜除去工程(S130)と、エッチング工程(S132)と、SiO2膜除去工程(S134)と、いう一連の工程を実施する。

【0009】

また、積層膜形成工程(S105)の内部工程として、低ガラス転移温度(低Tg)材料塗布工程(S106)と、ベーク処理工程(S108)と、高ガラス転移温度(高Tg)材料塗布工程(S110)と、ベーク処理工程(S112)と、いう一連の工程を実施する。

【0010】

また、SOG膜形成工程(S113)は、その内部工程として、SOG材料塗布工程(S114)と、ベーク処理工程(S116)と、いう一連の工程を実施する。

【0011】

図2に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図2では、図1の絶縁膜形成工程(S102)からベーク処理工程(S112)までを示している。それ以降の工程は後述する。

【0012】

図2(a)において、絶縁膜形成工程(S102)として、半導体基板200上に、絶縁膜210を例えば100〜300nmの膜厚で形成する。形成方法は、例えば、化学気相成長(CVD)法により形成すると好適である。但し、これに限るものではなくその他の手法であっても構わない。絶縁膜210として、例えば、シリコン酸化膜(SiO2膜)を形成する。SiO2膜として、例えば、TEOS膜を形成する。かかる絶縁膜210は、後述する被加工膜の下地膜となる。ここでは、被加工膜の下地膜として絶縁膜210を形成する例を示したが、これに限るものではなく、絶縁膜210は無くても構わない。また、半導体基板200として、例えば、直径300ミリのシリコンウェハを用いる。半導体基板200には、図示しないデバイス部分や配線等が形成されていてもよい。

【0013】

図2(b)において、被加工膜形成工程(S104)として、絶縁膜210上に、被加工膜212を例えば50〜200nmの膜厚で形成する。形成方法は、例えば、CVD法により形成すると好適である。但し、これに限るものではなくその他の手法であっても構わない。被加工膜212として、例えば、アモルファスシリコン(α−Si)膜、窒化シリコン(SiN)膜、或いはSiO2膜を形成する。ここでは、例えば、α−Si膜を形成する。

【0014】

次に、積層膜形成工程(S105)として、かかる被加工膜212が形成された基板上に例えば50〜200nmの膜厚の積層膜224を形成する。積層膜224を構成する各膜は、それぞれ炭素(カーボン)を主成分として多く含む膜(カーボン膜:SOC膜ともいう)が用いられるとよい。以下、積層膜形成工程(S105)の内部工程を説明する。

【0015】

図2(c)において、低Tg材料塗布工程(S106)として、塗布法を用いて、被加工膜212が形成された基板上に、低ガラス転移温度(低Tg)材料を用いた低Tg膜220(低ガラス転移温度材料膜)を形成する。例えば、ガラス転移温度(Tg)が100℃程度の材料を用いると好適である。低Tg膜220の材料としては、芳香環を主鎖に有さない樹脂が好適である。例えば、ビニル系樹脂、オレフィン系樹脂、或いはアクリル系樹脂等が好適である。或いはこれらを混合して使用しても好適である。基板を回転させながらかかる低Tg材料を塗布して所定の膜厚に形成すればよい。

【0016】

次に、ベーク処理工程(S108)として、低Tg膜220が塗布された基板を加熱する。例えば、300℃でベーク処理することで架橋反応を起こさせる。

【0017】

次に、図2(d)において、高Tg材料塗布工程(S110)として、塗布法を用いて、架橋反応後の低Tg膜220が形成された基板上に、高ガラス転移温度(高Tg)材料を用いた高Tg膜222(高ガラス転移温度材料膜)を形成する。例えば、ガラス転移温度(Tg)が250℃程度の材料を用いると好適である。高Tg膜222の材料としては、芳香環を主鎖に有する樹脂が好適である。例えば、ノボラック系樹脂、シアネート系樹脂、ポリイミド系樹脂、或いはポリエステル系樹脂等が好適である。或いはこれらを混合して使用しても好適である。基板を回転させながらかかる高Tg材料を塗布して所定の膜厚に形成すればよい。

【0018】

次に、ベーク処理工程(S112)として、高Tg膜222が塗布された基板を加熱する。例えば、300℃でベーク処理することで架橋反応を起こさせる。

【0019】

以上のようにして、低Tg膜220と高Tg膜222との積層膜224が形成される。ここで、積層膜ではなく、被加工膜212上に高Tg膜222だけを形成した場合の問題点について説明する。

【0020】

図3に、第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力について説明するための概念図が示されている。図3(a)に示すように被加工膜212上に高Tg膜222を塗布し、例えば300℃でベーク処理をおこなうと、まず図3(b)に示すようにガラス転移温度(例えば250℃)付近で高Tg膜222のガラス転移が生じ、さらに図3(c)に示すようにガラス転移温度から50℃高い300℃でベーク処理される。その際、ガラス転移温度(例えば250℃)からベーク温度(300℃)までの差が50℃しかないため、樹脂の流動が小さい。そのため、ひずみの大きい構造で架橋反応が進むことになる。その結果、図3(d)に示すように冷却後は、高Tg膜222に大きな残留応力が生じてしまう。

【0021】

さらに、図4に、第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力による問題点について説明するための概念図が示されている。図4(a)に示すように高Tg膜222に大きな残留応力が生じているため、応力緩和のために高Tg膜222の膜の一部が剥がれ、空隙20が生じてしまう。そして、図4(b)に示すように多層マスクプロセスにおいて高Tg膜222で膜パターンを形成後、後述するウェット処理を行うと、ウェット処理の薬液が高Tg膜222の剥がれた空隙20部分に染み込みやすくなる。そのため、高Tg膜222の膜パターンに倒れが発生してしまうといった問題が生じる。

【0022】

図5には、第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の膜パターンの倒れた状態の一例を示す。図5(a)では、ライン状に形成された高Tg膜222の膜パターンが倒れた様子の一例を斜め上方から撮影した結果が示されている。図5(b)では、ライン状に形成された高Tg膜222の膜パターンが倒れた様子の一例を断面で撮影した結果が示されている。以上のように、被加工膜上に直接高ガラス転移温度の材料を用いた高Tg膜222を形成してしまうと、高Tg膜222の膜パターンが形成された状態でウェット処理を行うことにより膜パターンの倒れが発生してしまうといった問題が生じる。

【0023】

これに対し、図6に、被加工膜上に低ガラス転移温度膜を形成した場合の残留応力について説明するための概念図が示されている。図6(a)に示すように被加工膜212上に低Tg膜220を塗布し、例えば300℃でベーク処理をおこなうと、まず図6(b)に示すようにガラス転移温度(例えば100℃)付近で低Tg膜220のガラス転移が生じ、さらに図6(c)に示すようにガラス転移温度から200℃高い300℃でベーク処理される。その際、ガラス転移温度(例えば100℃)からベーク温度(300℃)までの差が200℃あるため、樹脂の流動性が大きい。そのため、ひずみの少ない構造で架橋反応が進むことになる。その結果、図6(d)に示すように冷却後は、低Tg膜220に生じる残留応力は小さくできる。よって、図4で示したような膜の剥がれを抑制或いは防止でき、結果として、被加工膜212と接触する低Tg膜220の膜パターンの倒れを抑制或いは防止できる。

【0024】

図7には、被加工膜上に低ガラス転移温度膜を形成した場合の膜パターンの倒れのない状態の一例を示す。図7(b)では、ライン状に形成された低Tg膜220の膜パターンが倒れていない様子の一例を斜め上方から撮影した結果が示されている。図7(a)では、ライン状に形成された低Tg膜220の膜パターンが倒れていない様子の一例を断面で撮影した結果が示されている。以上のように、被加工膜上に直接低ガラス転移温度の材料を用いた低Tg膜220を形成することで、低Tg膜220の膜パターンが形成された状態でウェット処理を行っても膜パターンの倒れを抑制できることがわかる。

【0025】

しかしながら、第1の実施形態のような積層膜ではなく、被加工膜212上に低Tg膜220だけを形成した場合、次のような問題が生じる。以下、かかる問題点について説明する。

【0026】

図8に、第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合の問題点を説明するための概念図が示されている。図8(a)に示す低Tg膜220上に、図8(b)に示すように後述するSOG膜230を塗布し、図8(c)に示すように例えば300℃でベーク処理をおこなうと、SOG膜230はベークによって熱硬化が起こり収縮する。一方、低Tg膜220はベーク処理によって大きく熱膨張する。そのため、SOG膜230と低Tg膜220との間に大きな熱膨張差が生じる。その結果、図8(d)に示すようにSOG膜230にクラックが発生してしまうという問題が生じ得る。

【0027】

図9には、第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合のクラックが発生した状態の一例を示す。図9(b)では、SOG膜230にクラックが発生してSOG膜230上のレジストパターンに欠けが生じた様子の一例を上方から撮影した結果が示されている。図9(a)では、SOG膜230にクラックが発生してSOG膜230上のレジストパターンに欠けが生じた様子の一例を断面で撮影した結果が示されている。低Tg膜220上にSOG膜230を塗布し、その後ベーク処理を行うと、図9に示すように、SOG膜230にクラックが発生し、SOG膜230上にレジストによるラインアンドスペースを形成した際に、パターンの一部の欠けてしまっている。以上のように、低Tg膜220の膜上に直接SOG膜230を形成してしまうと、SOG膜230のベーク処理によってSOG膜230にクラックが発生してしまうといった問題が生じる。

【0028】

これに対し、図10に、高ガラス転移温度膜上にSOG膜を形成した場合の様子を説明するための概念図が示されている。図10(a)に示す高Tg膜222上に、図10(b)に示すように後述するSOG膜230を塗布し、図10(c)に示すように例えば300℃でベーク処理をおこなうと、上述したようにSOG膜230はベークによって熱硬化が起こり収縮する。一方、高Tg膜222はベークしても熱膨張がそれほど大きくならない。そのため、SOG膜230と高Tg膜222との間に大きな熱膨張差が生じない。その結果、図10(d)に示すようにSOG膜230にクラックを発生させないことができる。

【0029】

以上のように、被加工膜212上に、低Tg膜220を下層とし、高Tg膜222を上層とした積層膜224を形成し、積層膜224上にSOG膜230を形成することで、膜パターンの倒れを抑制できると共にSOG膜230へのクラックの発生を抑制できる。

【0030】

ここで、上述した例では、ガラス転移温度が250℃の材料を高Tg材料とし、ガラス転移温度が100℃の材料を低Tg材料としたが、これに限るものではなく、その他の温度の組み合わせでも構わない。かかる積層膜224は、相対的により低いTg材料で下層膜を形成し、相対的により高いTg材料で上層膜を形成すればよい。

【0031】

また、低Tg膜220と高Tg膜222の各膜厚は、膜パターン倒れとクラック発生とのうち、重要視する問題に合わせて適宜調整すればよい。例えば、クラック発生の解消をより重要視する場合には、高Tg膜222を低Tg膜220よりも相対的に厚い膜厚にすればよい。一方、例えば、膜パターン倒れの解消をより重要視する場合には、低Tg膜220を高Tg膜222よりも相対的に厚い膜厚にすればよい。

【0032】

図11に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図11では、図1のSOG膜形成工程(S113)からエッチング工程(S121)までを示している。それ以降の工程は後述する。

【0033】

図11(a)において、SOG膜形成工程(S113)として、低Tg膜220と高Tg膜222の積層膜224上に、加熱下で、積層膜224をエッチングするためのマスク材となるSOG膜230(上層膜)を例えば20〜100nmの膜厚で形成する。

【0034】

まず、SOG材料塗布工程(S114)として、低Tg膜220と高Tg膜222の積層膜224上に、SOG(Spin On Glass)材料(所定の膜材料)を所定の膜厚で塗布する。

【0035】

次に、ベーク処理工程(S116)として、塗布されたSOG材料膜を例えば300℃でベークする。上述したように、SOG膜230は、ベークによって熱収縮するが、下地が高Tg膜222であるためクラックの発生を抑制できる。

【0036】

積層膜224をエッチングするためのマスク材として、ここでは、塗布膜であるSOG膜230を形成しているが、これに限るものではなく、SOG膜230の代わりに、プラズマCVD法によりα−Si膜を形成してもよい。或いは、加熱下でのCVD法によりその他のCVD膜を形成してもよい。

【0037】

図11(b)において、レジストパターン形成工程(S118)として、図示しないリソグラフィ技術を用いて、SOG膜230上にレジスト膜を形成後、パターンを露光し、現像処理を行うことでSOG膜230上にレジストパターン240を形成する。ここでは、例えば、1:1のラインアンドスペースパターンを形成する。

【0038】

図11(c)において、エッチング工程(S120)として、ドライエッチング法により、レジストパターン240をマスクとして、露出したSOG膜230をエッチングする。これにより、SOG膜230をパターニングする。例えば、異方性エッチング法により露出したSOG膜230をエッチングすればよい。例えば、反応性イオンエッチング法を用いればよい。

【0039】

そして、エッチング工程(S121)として、ドライエッチング法により、露出した低Tg膜220及び高Tg膜222の積層膜224を連続して一緒にエッチングする。このとき、低Tg膜220及び高Tg膜222と同様に炭素を多く含む膜であるレジストパターン240はエッチング除去されるので、図11(c)に示すようにSOG膜230がマスクとなる。これにより、低Tg膜220及び高Tg膜222の積層膜224をパターニングする。例えば、異方性エッチング法により露出した積層膜224をエッチングすればよい。例えば、反応性イオンエッチング法を用いればよい。その際、低Tg膜220の方が、エッチング耐性が低く、エッチングレートが速いため高Tg膜222よりもより多くエッチングされる。ガラス転移温度が高い方が、結合力が強く、エッチングし難いためである。その結果、図11(c)に示すように、上層の高Tg膜222の線幅がより太く、下層の低Tg膜220の線幅がより細くなる上広がりのテーパ状の膜パターンに形成できる。かかる形状は、後述するように側壁パターンの形状に影響を与える。

【0040】

図12に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図12では、図1のSOG膜除去工程(S122)からエッチバック処理工程(S128)までを示している。それ以降の工程は後述する。

【0041】

図12(a)において、SOG膜除去工程(S122)として、低Tg膜220及び高Tg膜222の積層膜224による膜パターン上のSOG膜230をウェットエッチング処理により除去する。第1の実施形態では、被加工膜212上の膜パターンが低Tg膜220で形成されているため、上述したように膜パターン倒れを抑制できる。

【0042】

図12(b)において、スリミング処理工程(S124)として、エッチバック等により低Tg膜220及び高Tg膜222の積層膜224による膜パターンの線幅をスリミング処理して、例えば、半分の線幅に形成する。これにより、例えば、1:3のラインアンドスペースパターンが形成できる。

【0043】

図12(c)において、SiO2膜形成工程(S126)として、スリミング処理された積層膜224による膜パターン上に、側壁パターンの基となるSiO2膜250をコンフォーマルに形成する。かかる側壁パターンは、被加工膜212をエッチングするためのマスクとなる。なお、SiO2膜250の代わりにSiN膜であっても好適である。

【0044】

図12(d)において、エッチバック処理工程(S128)として、被加工膜212及び高Tg膜222が露出するまでSiO2膜250をエッチバックして、低Tg膜220及び高Tg膜222の積層膜224の膜パターンを芯材としてその両側の側壁にSiO2膜250の膜パターンを形成する。

【0045】

図13に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図13では、図1の高Tg膜および低Tg膜除去工程(S130)からSiO2膜除去工程(S134)までを示している。

【0046】

図13(a)において、高Tg膜および低Tg膜除去工程(S130)として、表面が露出した高Tg膜222とその下層の低Tg膜220を一緒に除去する。これにより、例えば、スリミング処理する前の低Tg膜220及び高Tg膜222の積層膜224の膜パターンによる1:1のラインアンドスペースパターンに比べてピッチが半分に狭まったSiO2膜250の膜パターンによる1:1のラインアンドスペースパターンを形成できる。その結果、リソグラフィの解像限界を超えたピッチと線幅でのマスクパターンを形成できる。

【0047】

図14に、第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの断面を撮像した図が示されている。第1の実施形態のように低Tg膜220及び高Tg膜222の積層膜224の膜パターンを形成しないで、単層のカーボン膜で同様の膜パターンを形成した場合には、以下のような問題が生じる。図14(a)では、単層のカーボン膜で形成された膜パターンの断面を示している。ここでは、側壁パターンを形成するために単層のカーボン膜の膜パターンをスリミング処理した後の状態を示している。そして、膜パターンの幅寸法を上部(TOP)位置と底部(Bottom)位置と、その間の中間部(Middle)位置とで測定した。図14(b)では、単層のカーボン膜の膜パターンを芯材として、かかる膜パターン上に、側壁パターンの基となるSiO2膜をコンフォーマルに形成した場合の断面を示している。そして、同様に、芯材の膜パターンの幅寸法を上部(TOP)位置と底部(Bottom)位置と、その間の中間部(Middle)位置とで測定した。

【0048】

図15に、第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの幅寸法の変化の一例を示すグラフが示されている。かかる例において、膜パターンの幅寸法は、TOP位置において、側壁パターンの基となるSiO2膜を単層のカーボン膜の膜パターン上にコンフォーマルに形成する前の段階では37.02nmとなる。そして、側壁パターンの基となるSiO2膜をコンフォーマルに形成した段階では23.58nmと細くなる。そして、SiO2膜をエッチバックしてSiO2膜の側壁パターンを形成後、芯材の単層のカーボン膜の膜パターンを除去した後の単層のカーボン膜の膜パターンがあった部分のスペース幅は31.43nmと多少太くなる。このように、芯材の単層のカーボン膜の膜パターンは、側壁パターンの基となるSiO2膜によって押しつぶされてしまい、先端部分(Top)の線幅が細くなってしまう。そして、芯材除去後も寸法がSiO2膜形成前までは戻らないことがわかる。

【0049】

次に、膜パターンの幅寸法は、Middle位置において、側壁パターンの基となるSiO2膜を単層のカーボン膜の膜パターン上にコンフォーマルに形成する前の段階では35.97nmとなる。そして、側壁パターンの基となるSiO2膜をコンフォーマルに形成した段階では22.7nmと細くなる。そして、SiO2膜をエッチバックしてSiO2膜の側壁パターンを形成後、芯材の単層のカーボン膜の膜パターンを除去した後の単層のカーボン膜の膜パターンがあった部分のスペース幅は30.48nmと多少太くなる。このように、芯材の単層のカーボン膜の膜パターンは、側壁パターンの基となるSiO2膜によって押しつぶされてしまい、Middle位置の線幅が細くなってしまう。そして、芯材除去後も寸法がSiO2膜形成前までは戻らないことがわかる。

【0050】

次に、膜パターンの幅寸法は、Bottom位置において、側壁パターンの基となるSiO2膜を単層のカーボン膜の膜パターン上にコンフォーマルに形成する前の段階では34.03nmとなる。そして、側壁パターンの基となるSiO2膜をコンフォーマルに形成した段階では31.53nmと多少細くなる。そして、SiO2膜をエッチバックしてSiO2膜の側壁パターンを形成後、芯材の単層のカーボン膜の膜パターンを除去した後の単層のカーボン膜の膜パターンがあった部分のスペース幅は31.03nmとほとんど変化しない。このように、芯材の単層のカーボン膜の膜パターンは、側壁パターンの基となるSiO2膜によって多少押しつぶされるが、SiO2膜形成時と芯材除去時の寸法においてはほとんど変化しないことがわかる。

【0051】

以上の結果から、単層のカーボン膜の膜パターンを芯材として使用した場合、側壁パターンの基となるSiO2膜によって押しつぶされてしまい、膜パターンの先端部分と中間部位置の幅寸法が細くなってしまう。そして、芯材除去後の寸法は、Bottom位置に比べてTOP位置の方が細くなってしまう。そのため、芯材を除去した後に残るSiO2膜の側壁パターンを垂直に形成することが困難になってしまうといった問題が生じる。

【0052】

これに対して、第1の実施形態では、図11(c)に示したように、エッチング工程(S121)において、上層の高Tg膜222の線幅がより太く、低Tg膜220の線幅がより細くなる上広がりのテーパ状の膜パターンに形成できる。よって、あえて上部を太らせた、かかる上広がりのテーパ状の膜パターンを芯材として使用することで、SiO2膜によって押しつぶされて線幅が狭まったとしても、芯材を除去した後に残る側壁のSiO2膜の膜パターンを実質的に垂直に形成できる。

【0053】

図13(b)において、エッチング工程(S132)として、SiO2膜250の膜パターンをマスクとして、被加工膜212をエッチングする。例えば、異方性エッチング法により露出した被加工膜212をエッチングすればよい。例えば、反応性イオンエッチング法を用いればよい。これにより、略垂直にパターンを形成できる。

【0054】

図13(c)において、SiO2膜除去工程(S134)として、エッチング法により、SiO2膜250を除去する。以上により、リソグラフィ時のパターンピッチよりも狭いピッチで被加工膜212の膜パターンを形成できる。

【0055】

以上、具体例を参照しつつ実施形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。上述した実施形態では、被加工膜212上に積層膜224を形成しているがこれに限るものではなく、被加工膜212と積層膜224との間に他の膜を挟んでもよい。他の膜として、被加工膜212とは異なる、例えば、SiN膜、α−Si膜、或いはSiO2膜等が好適である。さらに、上述した実施形態では、積層膜224による膜パターンを形成後、この膜パターンに対しスリミング処理を行なったが、これに代えてレジストパターン240のスリミング処理を行ってもよいし、或いはレジストパターン240をSOG膜230及び積層膜224に順次転写する際に膜パターンの線幅が細められるような条件でエッチングを行ってもよく、さらにはこれらを組み合わせて積層膜224による膜パターンを所望の線幅で形成することもできる。

【0056】

また、層間絶縁膜の膜厚や、開口部のサイズ、形状、数などについても、半導体集積回路や各種の半導体素子において必要とされるものを適宜選択して用いることができる。

【0057】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体装置の製造方法に代表される電子部品の製造方法は、本発明の範囲に包含される。

【0058】

また、説明の簡便化のために、半導体産業で通常用いられる手法、例えば、フォトリソグラフィプロセス、処理前後のクリーニング等は省略しているが、それらの手法が含まれ得ることは言うまでもない。

【符号の説明】

【0059】

200 半導体基板、212 被加工膜、220 低Tg膜、222 高Tg膜、224 積層膜、230 SOG膜、240 レジストパターン、250 SiO2膜

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

LSIの微細化に伴い、露光プロセスのマージンが不足してきている。これを補うには、レジスト膜の膜厚を薄くして解像性を向上させることが有効である。しかし、一方でレジスト膜の膜厚を薄くすると被加工膜のエッチングに必要なレジスト膜厚を確保できなくなるという問題が生じる。かかる問題に対して、例えば、被加工膜上に下層膜、上層膜およびレジスト膜を形成し、レジストパターンを上層膜および下層膜に順次転写して膜パターンを形成した後、下層膜の膜パターンをエッチングマスクとして被加工膜の加工を行う手法が知られている。このように、レジスト膜とその他の上層膜および下層膜による多層マスクを用いて所望の膜をエッチングする手法において、下層膜はエッチングマスクとして作用する必要があり、スパッタリングされにくく、エッチング耐性がある炭素原子を多く含む材料が好ましい。そのため、多層マスクの下層膜として、カーボン膜(SOC:Spin On Carbon膜)を用いる場合がある。また、さらに、かかる下層膜の膜パターンを芯材として側壁に別の膜パターンを形成し、上述した下層膜ではなく、かかる側壁の膜パターンをエッチングマスクとした被加工膜の加工を行なうこともある。

【0003】

しかしながら、かかるカーボン膜を例えば微細なライン状の膜パターンとして残したときに、カーボン膜の膜パターンが倒れてしまう場合があるといった問題があった。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−205755号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、上述した問題点を克服し、膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

【図面の簡単な説明】

【0007】

【図1】第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図2】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図3】第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力について説明するための概念図である。

【図4】第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力による問題点について説明するための概念図である。

【図5】第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の膜パターンの倒れた状態の一例を示す図である。

【図6】被加工膜上に低ガラス転移温度膜を形成した場合の残留応力について説明するための概念図である。

【図7】被加工膜上に低ガラス転移温度膜を形成した場合の膜パターンの倒れのない状態の一例を示す図である。

【図8】第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合の問題点を説明するための概念図である。

【図9】第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合のクラックが発生した状態の一例を示す図である。

【図10】高ガラス転移温度膜上にSOG膜を形成した場合の様子を説明するための概念図である。

【図11】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図12】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図13】第1の実施形態における半導体装置の製造方法の工程断面図である。

【図14】第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの断面を撮像した図である。

【図15】第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの幅寸法の変化の一例を示すグラフである。

【発明を実施するための形態】

【0008】

(第1の実施形態)

以下、図面を用いて説明する。

図1に、第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図が示されている。図1において、第1の実施形態における半導体装置の製造方法は、絶縁膜形成工程(S102)と、被加工膜形成工程(S104)と、積層膜形成工程(S105)と、SOG(Spin On Glass)膜形成工程(S113)と、レジストパターン形成工程(S118)と、エッチング工程(S120)と、エッチング工程(S121)と、SOG膜除去工程(S122)と、スリミング処理工程(S124)と、SiO2膜形成工程(S126)と、エッチバック処理工程(S128)と、高ガラス転移温度(高Tg)膜および低ガラス転移温度(低Tg)膜除去工程(S130)と、エッチング工程(S132)と、SiO2膜除去工程(S134)と、いう一連の工程を実施する。

【0009】

また、積層膜形成工程(S105)の内部工程として、低ガラス転移温度(低Tg)材料塗布工程(S106)と、ベーク処理工程(S108)と、高ガラス転移温度(高Tg)材料塗布工程(S110)と、ベーク処理工程(S112)と、いう一連の工程を実施する。

【0010】

また、SOG膜形成工程(S113)は、その内部工程として、SOG材料塗布工程(S114)と、ベーク処理工程(S116)と、いう一連の工程を実施する。

【0011】

図2に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図2では、図1の絶縁膜形成工程(S102)からベーク処理工程(S112)までを示している。それ以降の工程は後述する。

【0012】

図2(a)において、絶縁膜形成工程(S102)として、半導体基板200上に、絶縁膜210を例えば100〜300nmの膜厚で形成する。形成方法は、例えば、化学気相成長(CVD)法により形成すると好適である。但し、これに限るものではなくその他の手法であっても構わない。絶縁膜210として、例えば、シリコン酸化膜(SiO2膜)を形成する。SiO2膜として、例えば、TEOS膜を形成する。かかる絶縁膜210は、後述する被加工膜の下地膜となる。ここでは、被加工膜の下地膜として絶縁膜210を形成する例を示したが、これに限るものではなく、絶縁膜210は無くても構わない。また、半導体基板200として、例えば、直径300ミリのシリコンウェハを用いる。半導体基板200には、図示しないデバイス部分や配線等が形成されていてもよい。

【0013】

図2(b)において、被加工膜形成工程(S104)として、絶縁膜210上に、被加工膜212を例えば50〜200nmの膜厚で形成する。形成方法は、例えば、CVD法により形成すると好適である。但し、これに限るものではなくその他の手法であっても構わない。被加工膜212として、例えば、アモルファスシリコン(α−Si)膜、窒化シリコン(SiN)膜、或いはSiO2膜を形成する。ここでは、例えば、α−Si膜を形成する。

【0014】

次に、積層膜形成工程(S105)として、かかる被加工膜212が形成された基板上に例えば50〜200nmの膜厚の積層膜224を形成する。積層膜224を構成する各膜は、それぞれ炭素(カーボン)を主成分として多く含む膜(カーボン膜:SOC膜ともいう)が用いられるとよい。以下、積層膜形成工程(S105)の内部工程を説明する。

【0015】

図2(c)において、低Tg材料塗布工程(S106)として、塗布法を用いて、被加工膜212が形成された基板上に、低ガラス転移温度(低Tg)材料を用いた低Tg膜220(低ガラス転移温度材料膜)を形成する。例えば、ガラス転移温度(Tg)が100℃程度の材料を用いると好適である。低Tg膜220の材料としては、芳香環を主鎖に有さない樹脂が好適である。例えば、ビニル系樹脂、オレフィン系樹脂、或いはアクリル系樹脂等が好適である。或いはこれらを混合して使用しても好適である。基板を回転させながらかかる低Tg材料を塗布して所定の膜厚に形成すればよい。

【0016】

次に、ベーク処理工程(S108)として、低Tg膜220が塗布された基板を加熱する。例えば、300℃でベーク処理することで架橋反応を起こさせる。

【0017】

次に、図2(d)において、高Tg材料塗布工程(S110)として、塗布法を用いて、架橋反応後の低Tg膜220が形成された基板上に、高ガラス転移温度(高Tg)材料を用いた高Tg膜222(高ガラス転移温度材料膜)を形成する。例えば、ガラス転移温度(Tg)が250℃程度の材料を用いると好適である。高Tg膜222の材料としては、芳香環を主鎖に有する樹脂が好適である。例えば、ノボラック系樹脂、シアネート系樹脂、ポリイミド系樹脂、或いはポリエステル系樹脂等が好適である。或いはこれらを混合して使用しても好適である。基板を回転させながらかかる高Tg材料を塗布して所定の膜厚に形成すればよい。

【0018】

次に、ベーク処理工程(S112)として、高Tg膜222が塗布された基板を加熱する。例えば、300℃でベーク処理することで架橋反応を起こさせる。

【0019】

以上のようにして、低Tg膜220と高Tg膜222との積層膜224が形成される。ここで、積層膜ではなく、被加工膜212上に高Tg膜222だけを形成した場合の問題点について説明する。

【0020】

図3に、第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力について説明するための概念図が示されている。図3(a)に示すように被加工膜212上に高Tg膜222を塗布し、例えば300℃でベーク処理をおこなうと、まず図3(b)に示すようにガラス転移温度(例えば250℃)付近で高Tg膜222のガラス転移が生じ、さらに図3(c)に示すようにガラス転移温度から50℃高い300℃でベーク処理される。その際、ガラス転移温度(例えば250℃)からベーク温度(300℃)までの差が50℃しかないため、樹脂の流動が小さい。そのため、ひずみの大きい構造で架橋反応が進むことになる。その結果、図3(d)に示すように冷却後は、高Tg膜222に大きな残留応力が生じてしまう。

【0021】

さらに、図4に、第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の残留応力による問題点について説明するための概念図が示されている。図4(a)に示すように高Tg膜222に大きな残留応力が生じているため、応力緩和のために高Tg膜222の膜の一部が剥がれ、空隙20が生じてしまう。そして、図4(b)に示すように多層マスクプロセスにおいて高Tg膜222で膜パターンを形成後、後述するウェット処理を行うと、ウェット処理の薬液が高Tg膜222の剥がれた空隙20部分に染み込みやすくなる。そのため、高Tg膜222の膜パターンに倒れが発生してしまうといった問題が生じる。

【0022】

図5には、第1の実施形態の比較例となる、被加工膜上に高ガラス転移温度膜を形成した場合の膜パターンの倒れた状態の一例を示す。図5(a)では、ライン状に形成された高Tg膜222の膜パターンが倒れた様子の一例を斜め上方から撮影した結果が示されている。図5(b)では、ライン状に形成された高Tg膜222の膜パターンが倒れた様子の一例を断面で撮影した結果が示されている。以上のように、被加工膜上に直接高ガラス転移温度の材料を用いた高Tg膜222を形成してしまうと、高Tg膜222の膜パターンが形成された状態でウェット処理を行うことにより膜パターンの倒れが発生してしまうといった問題が生じる。

【0023】

これに対し、図6に、被加工膜上に低ガラス転移温度膜を形成した場合の残留応力について説明するための概念図が示されている。図6(a)に示すように被加工膜212上に低Tg膜220を塗布し、例えば300℃でベーク処理をおこなうと、まず図6(b)に示すようにガラス転移温度(例えば100℃)付近で低Tg膜220のガラス転移が生じ、さらに図6(c)に示すようにガラス転移温度から200℃高い300℃でベーク処理される。その際、ガラス転移温度(例えば100℃)からベーク温度(300℃)までの差が200℃あるため、樹脂の流動性が大きい。そのため、ひずみの少ない構造で架橋反応が進むことになる。その結果、図6(d)に示すように冷却後は、低Tg膜220に生じる残留応力は小さくできる。よって、図4で示したような膜の剥がれを抑制或いは防止でき、結果として、被加工膜212と接触する低Tg膜220の膜パターンの倒れを抑制或いは防止できる。

【0024】

図7には、被加工膜上に低ガラス転移温度膜を形成した場合の膜パターンの倒れのない状態の一例を示す。図7(b)では、ライン状に形成された低Tg膜220の膜パターンが倒れていない様子の一例を斜め上方から撮影した結果が示されている。図7(a)では、ライン状に形成された低Tg膜220の膜パターンが倒れていない様子の一例を断面で撮影した結果が示されている。以上のように、被加工膜上に直接低ガラス転移温度の材料を用いた低Tg膜220を形成することで、低Tg膜220の膜パターンが形成された状態でウェット処理を行っても膜パターンの倒れを抑制できることがわかる。

【0025】

しかしながら、第1の実施形態のような積層膜ではなく、被加工膜212上に低Tg膜220だけを形成した場合、次のような問題が生じる。以下、かかる問題点について説明する。

【0026】

図8に、第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合の問題点を説明するための概念図が示されている。図8(a)に示す低Tg膜220上に、図8(b)に示すように後述するSOG膜230を塗布し、図8(c)に示すように例えば300℃でベーク処理をおこなうと、SOG膜230はベークによって熱硬化が起こり収縮する。一方、低Tg膜220はベーク処理によって大きく熱膨張する。そのため、SOG膜230と低Tg膜220との間に大きな熱膨張差が生じる。その結果、図8(d)に示すようにSOG膜230にクラックが発生してしまうという問題が生じ得る。

【0027】

図9には、第1の実施形態の比較例となる、低ガラス転移温度膜上にSOG膜を形成した場合のクラックが発生した状態の一例を示す。図9(b)では、SOG膜230にクラックが発生してSOG膜230上のレジストパターンに欠けが生じた様子の一例を上方から撮影した結果が示されている。図9(a)では、SOG膜230にクラックが発生してSOG膜230上のレジストパターンに欠けが生じた様子の一例を断面で撮影した結果が示されている。低Tg膜220上にSOG膜230を塗布し、その後ベーク処理を行うと、図9に示すように、SOG膜230にクラックが発生し、SOG膜230上にレジストによるラインアンドスペースを形成した際に、パターンの一部の欠けてしまっている。以上のように、低Tg膜220の膜上に直接SOG膜230を形成してしまうと、SOG膜230のベーク処理によってSOG膜230にクラックが発生してしまうといった問題が生じる。

【0028】

これに対し、図10に、高ガラス転移温度膜上にSOG膜を形成した場合の様子を説明するための概念図が示されている。図10(a)に示す高Tg膜222上に、図10(b)に示すように後述するSOG膜230を塗布し、図10(c)に示すように例えば300℃でベーク処理をおこなうと、上述したようにSOG膜230はベークによって熱硬化が起こり収縮する。一方、高Tg膜222はベークしても熱膨張がそれほど大きくならない。そのため、SOG膜230と高Tg膜222との間に大きな熱膨張差が生じない。その結果、図10(d)に示すようにSOG膜230にクラックを発生させないことができる。

【0029】

以上のように、被加工膜212上に、低Tg膜220を下層とし、高Tg膜222を上層とした積層膜224を形成し、積層膜224上にSOG膜230を形成することで、膜パターンの倒れを抑制できると共にSOG膜230へのクラックの発生を抑制できる。

【0030】

ここで、上述した例では、ガラス転移温度が250℃の材料を高Tg材料とし、ガラス転移温度が100℃の材料を低Tg材料としたが、これに限るものではなく、その他の温度の組み合わせでも構わない。かかる積層膜224は、相対的により低いTg材料で下層膜を形成し、相対的により高いTg材料で上層膜を形成すればよい。

【0031】

また、低Tg膜220と高Tg膜222の各膜厚は、膜パターン倒れとクラック発生とのうち、重要視する問題に合わせて適宜調整すればよい。例えば、クラック発生の解消をより重要視する場合には、高Tg膜222を低Tg膜220よりも相対的に厚い膜厚にすればよい。一方、例えば、膜パターン倒れの解消をより重要視する場合には、低Tg膜220を高Tg膜222よりも相対的に厚い膜厚にすればよい。

【0032】

図11に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図11では、図1のSOG膜形成工程(S113)からエッチング工程(S121)までを示している。それ以降の工程は後述する。

【0033】

図11(a)において、SOG膜形成工程(S113)として、低Tg膜220と高Tg膜222の積層膜224上に、加熱下で、積層膜224をエッチングするためのマスク材となるSOG膜230(上層膜)を例えば20〜100nmの膜厚で形成する。

【0034】

まず、SOG材料塗布工程(S114)として、低Tg膜220と高Tg膜222の積層膜224上に、SOG(Spin On Glass)材料(所定の膜材料)を所定の膜厚で塗布する。

【0035】

次に、ベーク処理工程(S116)として、塗布されたSOG材料膜を例えば300℃でベークする。上述したように、SOG膜230は、ベークによって熱収縮するが、下地が高Tg膜222であるためクラックの発生を抑制できる。

【0036】

積層膜224をエッチングするためのマスク材として、ここでは、塗布膜であるSOG膜230を形成しているが、これに限るものではなく、SOG膜230の代わりに、プラズマCVD法によりα−Si膜を形成してもよい。或いは、加熱下でのCVD法によりその他のCVD膜を形成してもよい。

【0037】

図11(b)において、レジストパターン形成工程(S118)として、図示しないリソグラフィ技術を用いて、SOG膜230上にレジスト膜を形成後、パターンを露光し、現像処理を行うことでSOG膜230上にレジストパターン240を形成する。ここでは、例えば、1:1のラインアンドスペースパターンを形成する。

【0038】

図11(c)において、エッチング工程(S120)として、ドライエッチング法により、レジストパターン240をマスクとして、露出したSOG膜230をエッチングする。これにより、SOG膜230をパターニングする。例えば、異方性エッチング法により露出したSOG膜230をエッチングすればよい。例えば、反応性イオンエッチング法を用いればよい。

【0039】

そして、エッチング工程(S121)として、ドライエッチング法により、露出した低Tg膜220及び高Tg膜222の積層膜224を連続して一緒にエッチングする。このとき、低Tg膜220及び高Tg膜222と同様に炭素を多く含む膜であるレジストパターン240はエッチング除去されるので、図11(c)に示すようにSOG膜230がマスクとなる。これにより、低Tg膜220及び高Tg膜222の積層膜224をパターニングする。例えば、異方性エッチング法により露出した積層膜224をエッチングすればよい。例えば、反応性イオンエッチング法を用いればよい。その際、低Tg膜220の方が、エッチング耐性が低く、エッチングレートが速いため高Tg膜222よりもより多くエッチングされる。ガラス転移温度が高い方が、結合力が強く、エッチングし難いためである。その結果、図11(c)に示すように、上層の高Tg膜222の線幅がより太く、下層の低Tg膜220の線幅がより細くなる上広がりのテーパ状の膜パターンに形成できる。かかる形状は、後述するように側壁パターンの形状に影響を与える。

【0040】

図12に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図12では、図1のSOG膜除去工程(S122)からエッチバック処理工程(S128)までを示している。それ以降の工程は後述する。

【0041】

図12(a)において、SOG膜除去工程(S122)として、低Tg膜220及び高Tg膜222の積層膜224による膜パターン上のSOG膜230をウェットエッチング処理により除去する。第1の実施形態では、被加工膜212上の膜パターンが低Tg膜220で形成されているため、上述したように膜パターン倒れを抑制できる。

【0042】

図12(b)において、スリミング処理工程(S124)として、エッチバック等により低Tg膜220及び高Tg膜222の積層膜224による膜パターンの線幅をスリミング処理して、例えば、半分の線幅に形成する。これにより、例えば、1:3のラインアンドスペースパターンが形成できる。

【0043】

図12(c)において、SiO2膜形成工程(S126)として、スリミング処理された積層膜224による膜パターン上に、側壁パターンの基となるSiO2膜250をコンフォーマルに形成する。かかる側壁パターンは、被加工膜212をエッチングするためのマスクとなる。なお、SiO2膜250の代わりにSiN膜であっても好適である。

【0044】

図12(d)において、エッチバック処理工程(S128)として、被加工膜212及び高Tg膜222が露出するまでSiO2膜250をエッチバックして、低Tg膜220及び高Tg膜222の積層膜224の膜パターンを芯材としてその両側の側壁にSiO2膜250の膜パターンを形成する。

【0045】

図13に、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図13では、図1の高Tg膜および低Tg膜除去工程(S130)からSiO2膜除去工程(S134)までを示している。

【0046】

図13(a)において、高Tg膜および低Tg膜除去工程(S130)として、表面が露出した高Tg膜222とその下層の低Tg膜220を一緒に除去する。これにより、例えば、スリミング処理する前の低Tg膜220及び高Tg膜222の積層膜224の膜パターンによる1:1のラインアンドスペースパターンに比べてピッチが半分に狭まったSiO2膜250の膜パターンによる1:1のラインアンドスペースパターンを形成できる。その結果、リソグラフィの解像限界を超えたピッチと線幅でのマスクパターンを形成できる。

【0047】

図14に、第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの断面を撮像した図が示されている。第1の実施形態のように低Tg膜220及び高Tg膜222の積層膜224の膜パターンを形成しないで、単層のカーボン膜で同様の膜パターンを形成した場合には、以下のような問題が生じる。図14(a)では、単層のカーボン膜で形成された膜パターンの断面を示している。ここでは、側壁パターンを形成するために単層のカーボン膜の膜パターンをスリミング処理した後の状態を示している。そして、膜パターンの幅寸法を上部(TOP)位置と底部(Bottom)位置と、その間の中間部(Middle)位置とで測定した。図14(b)では、単層のカーボン膜の膜パターンを芯材として、かかる膜パターン上に、側壁パターンの基となるSiO2膜をコンフォーマルに形成した場合の断面を示している。そして、同様に、芯材の膜パターンの幅寸法を上部(TOP)位置と底部(Bottom)位置と、その間の中間部(Middle)位置とで測定した。

【0048】

図15に、第1の実施形態の比較例となる、単層のカーボン膜の膜パターンの幅寸法の変化の一例を示すグラフが示されている。かかる例において、膜パターンの幅寸法は、TOP位置において、側壁パターンの基となるSiO2膜を単層のカーボン膜の膜パターン上にコンフォーマルに形成する前の段階では37.02nmとなる。そして、側壁パターンの基となるSiO2膜をコンフォーマルに形成した段階では23.58nmと細くなる。そして、SiO2膜をエッチバックしてSiO2膜の側壁パターンを形成後、芯材の単層のカーボン膜の膜パターンを除去した後の単層のカーボン膜の膜パターンがあった部分のスペース幅は31.43nmと多少太くなる。このように、芯材の単層のカーボン膜の膜パターンは、側壁パターンの基となるSiO2膜によって押しつぶされてしまい、先端部分(Top)の線幅が細くなってしまう。そして、芯材除去後も寸法がSiO2膜形成前までは戻らないことがわかる。

【0049】

次に、膜パターンの幅寸法は、Middle位置において、側壁パターンの基となるSiO2膜を単層のカーボン膜の膜パターン上にコンフォーマルに形成する前の段階では35.97nmとなる。そして、側壁パターンの基となるSiO2膜をコンフォーマルに形成した段階では22.7nmと細くなる。そして、SiO2膜をエッチバックしてSiO2膜の側壁パターンを形成後、芯材の単層のカーボン膜の膜パターンを除去した後の単層のカーボン膜の膜パターンがあった部分のスペース幅は30.48nmと多少太くなる。このように、芯材の単層のカーボン膜の膜パターンは、側壁パターンの基となるSiO2膜によって押しつぶされてしまい、Middle位置の線幅が細くなってしまう。そして、芯材除去後も寸法がSiO2膜形成前までは戻らないことがわかる。

【0050】

次に、膜パターンの幅寸法は、Bottom位置において、側壁パターンの基となるSiO2膜を単層のカーボン膜の膜パターン上にコンフォーマルに形成する前の段階では34.03nmとなる。そして、側壁パターンの基となるSiO2膜をコンフォーマルに形成した段階では31.53nmと多少細くなる。そして、SiO2膜をエッチバックしてSiO2膜の側壁パターンを形成後、芯材の単層のカーボン膜の膜パターンを除去した後の単層のカーボン膜の膜パターンがあった部分のスペース幅は31.03nmとほとんど変化しない。このように、芯材の単層のカーボン膜の膜パターンは、側壁パターンの基となるSiO2膜によって多少押しつぶされるが、SiO2膜形成時と芯材除去時の寸法においてはほとんど変化しないことがわかる。

【0051】

以上の結果から、単層のカーボン膜の膜パターンを芯材として使用した場合、側壁パターンの基となるSiO2膜によって押しつぶされてしまい、膜パターンの先端部分と中間部位置の幅寸法が細くなってしまう。そして、芯材除去後の寸法は、Bottom位置に比べてTOP位置の方が細くなってしまう。そのため、芯材を除去した後に残るSiO2膜の側壁パターンを垂直に形成することが困難になってしまうといった問題が生じる。

【0052】

これに対して、第1の実施形態では、図11(c)に示したように、エッチング工程(S121)において、上層の高Tg膜222の線幅がより太く、低Tg膜220の線幅がより細くなる上広がりのテーパ状の膜パターンに形成できる。よって、あえて上部を太らせた、かかる上広がりのテーパ状の膜パターンを芯材として使用することで、SiO2膜によって押しつぶされて線幅が狭まったとしても、芯材を除去した後に残る側壁のSiO2膜の膜パターンを実質的に垂直に形成できる。

【0053】

図13(b)において、エッチング工程(S132)として、SiO2膜250の膜パターンをマスクとして、被加工膜212をエッチングする。例えば、異方性エッチング法により露出した被加工膜212をエッチングすればよい。例えば、反応性イオンエッチング法を用いればよい。これにより、略垂直にパターンを形成できる。

【0054】

図13(c)において、SiO2膜除去工程(S134)として、エッチング法により、SiO2膜250を除去する。以上により、リソグラフィ時のパターンピッチよりも狭いピッチで被加工膜212の膜パターンを形成できる。

【0055】

以上、具体例を参照しつつ実施形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。上述した実施形態では、被加工膜212上に積層膜224を形成しているがこれに限るものではなく、被加工膜212と積層膜224との間に他の膜を挟んでもよい。他の膜として、被加工膜212とは異なる、例えば、SiN膜、α−Si膜、或いはSiO2膜等が好適である。さらに、上述した実施形態では、積層膜224による膜パターンを形成後、この膜パターンに対しスリミング処理を行なったが、これに代えてレジストパターン240のスリミング処理を行ってもよいし、或いはレジストパターン240をSOG膜230及び積層膜224に順次転写する際に膜パターンの線幅が細められるような条件でエッチングを行ってもよく、さらにはこれらを組み合わせて積層膜224による膜パターンを所望の線幅で形成することもできる。

【0056】

また、層間絶縁膜の膜厚や、開口部のサイズ、形状、数などについても、半導体集積回路や各種の半導体素子において必要とされるものを適宜選択して用いることができる。

【0057】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体装置の製造方法に代表される電子部品の製造方法は、本発明の範囲に包含される。

【0058】

また、説明の簡便化のために、半導体産業で通常用いられる手法、例えば、フォトリソグラフィプロセス、処理前後のクリーニング等は省略しているが、それらの手法が含まれ得ることは言うまでもない。

【符号の説明】

【0059】

200 半導体基板、212 被加工膜、220 低Tg膜、222 高Tg膜、224 積層膜、230 SOG膜、240 レジストパターン、250 SiO2膜

【特許請求の範囲】

【請求項1】

基板上に、芳香環を主鎖に有さない樹脂を用いた低ガラス転移温度材料膜と、芳香環を主鎖に有する樹脂を用いた高ガラス転移温度材料膜と、の積層膜を形成する工程と、

前記積層膜上に、膜材料を塗布して加熱することによって上層膜を形成する工程と、

前記上層膜をパターニングする工程と、

前記上層膜をマスクとして前記積層膜をパターニングする工程と、

前記上層膜をウェットエッチング処理により除去する工程と、

前記上層膜を除去した後、前記積層膜を芯材として、前記積層膜の側壁に膜パターンを形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、

前記積層膜上に加熱下で上層膜を形成する工程と、

前記上層膜をパターニングする工程と、

前記上層膜をマスクとして前記積層膜をパターニングする工程と、

前記上層膜をウェットエッチング処理により除去する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項3】

前記高ガラス転移温度材料膜の材料として、芳香環を主鎖に有する樹脂が用いられることを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

前記低ガラス転移温度材料膜の材料として、芳香環を主鎖に有さない樹脂が用いられることを特徴とする請求項2又は3記載の半導体装置の製造方法。

【請求項5】

基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、

前記積層膜をエッチングして、上層の線幅が太く下層の線幅が細いパターンにパターニングする工程と、

パターニングされた積層膜を芯材として、前記積層膜の側壁に膜パターンを形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項1】

基板上に、芳香環を主鎖に有さない樹脂を用いた低ガラス転移温度材料膜と、芳香環を主鎖に有する樹脂を用いた高ガラス転移温度材料膜と、の積層膜を形成する工程と、

前記積層膜上に、膜材料を塗布して加熱することによって上層膜を形成する工程と、

前記上層膜をパターニングする工程と、

前記上層膜をマスクとして前記積層膜をパターニングする工程と、

前記上層膜をウェットエッチング処理により除去する工程と、

前記上層膜を除去した後、前記積層膜を芯材として、前記積層膜の側壁に膜パターンを形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、

前記積層膜上に加熱下で上層膜を形成する工程と、

前記上層膜をパターニングする工程と、

前記上層膜をマスクとして前記積層膜をパターニングする工程と、

前記上層膜をウェットエッチング処理により除去する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項3】

前記高ガラス転移温度材料膜の材料として、芳香環を主鎖に有する樹脂が用いられることを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

前記低ガラス転移温度材料膜の材料として、芳香環を主鎖に有さない樹脂が用いられることを特徴とする請求項2又は3記載の半導体装置の製造方法。

【請求項5】

基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、

前記積層膜をエッチングして、上層の線幅が太く下層の線幅が細いパターンにパターニングする工程と、

パターニングされた積層膜を芯材として、前記積層膜の側壁に膜パターンを形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図6】

【図8】

【図10】

【図11】

【図12】

【図13】

【図15】

【図5】

【図7】

【図9】

【図14】

【図2】

【図3】

【図4】

【図6】

【図8】

【図10】

【図11】

【図12】

【図13】

【図15】

【図5】

【図7】

【図9】

【図14】

【公開番号】特開2013−102038(P2013−102038A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−244505(P2011−244505)

【出願日】平成23年11月8日(2011.11.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月8日(2011.11.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]