半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、グラフェンを用いた半導体装置の製造方法に関する。

【背景技術】

【0002】

シリコンを利用したCMOS技術は微細化の限界に近づきつつあり、その寿命を延ばすためのチャネル代替材料が模索されている。その最有力候補として、カーボンナノチューブやグラフェンを代表とするナノカーボン材料が注目されており、種々の研究・開発が行われている。

【0003】

ナノカーボン材料を用いたデバイスの一例として、電界効果トランジスタのチャネル領域にグラフェンを用いたグラフェントランジスタが挙げられる。グラフェンはシリコンと比較してキャリア移動度が高いため、グラフェンによりチャネルを形成することにより高速トランジスタを実現することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第2008/108383号パンフレット

【非特許文献】

【0005】

【非特許文献1】Y. Wang et al., "Scalable synthesis of graphene on patterned Ni and transfer", IEEE trans. Electron Devices, Vol. 57, No. 12, 2010

【発明の概要】

【発明が解決しようとする課題】

【0006】

グラフェンによりチャネルを形成するためには、絶縁膜上にグラフェンを形成することが求められる。しかしながら、グラフェンの合成には触媒が必要であり、合成したグラフェンの下地には触媒金属膜が存在する。そこで、別の基板上に合成したグラフェンを絶縁膜上に転写するプロセスが提案されているが、転写の際にグラフェンに皺や曲がり、レジスト残渣などのダメージが導入されたりすることがあり、所望のデバイス特性を安定して得ることが困難であった。

【0007】

本発明の目的は、絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0008】

実施形態の一観点によれば、第1の基板上に、第1の触媒金属膜を形成する工程と、前記第1の触媒金属膜上に、前記第1の触媒金属膜を触媒として、第1のグラフェンを形成する工程と、前記第1のグラフェン上に、第1の絶縁膜を形成する工程と、前記第1の絶縁膜上に、第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、前記第1の基板を除去する工程とを有する半導体装置の製造方法が提供される。

【0009】

また、実施形態の他の観点によれば、第1の基板上に、触媒金属膜を形成する工程と、前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、前記グラフェン上に、第1の金属膜を形成する工程と、前記第1の金属膜及び前記グラフェンをパターニングし、前記グラフェンよりなるグラフェン配線を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、前記第1の基板を除去する工程と、前記触媒金属膜を除去する工程とを有する半導体装置の製造方法が提供される。

【0010】

また、実施形態の更に他の観点によれば、第1の基板上に、触媒金属膜を形成する工程と、前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、前記グラフェン上に、第1の絶縁膜を形成する工程と、第2の基板上に第2の絶縁膜を形成する工程と、前記第1の絶縁膜の表面と前記第2の絶縁膜の表面とを対向させ、前記第1の絶縁膜と前記第2の絶縁膜とを接合する工程と、前記第1の基板を除去する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0011】

開示の半導体装置の製造方法によれば、グラフェン上に絶縁膜及び金属膜が状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【図面の簡単な説明】

【0012】

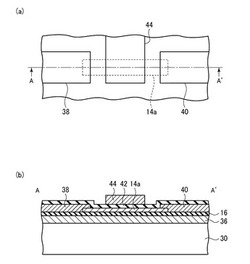

【図1】図1は、第1実施形態による半導体装置の構造を示す平面図及び概略断面図である。

【図2】図2は、第1実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図3】図3は、第1実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図4】図4は、第1実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図5】図5は、第1実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図6】図6は、第2実施形態による半導体装置の構造を示す平面図及び概略断面図である。

【図7】図7は、第2実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図8】図8は、第2実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図9】図9は、第2実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図10】図10は、第2実施形態の変形例による半導体装置の構造を示す平面図(その1)である。

【図11】図11は、第2実施形態の変形例による半導体装置の構造を示す平面図(その2)である。

【図12】図12は、第3実施形態による半導体装置の構造を示す平面図及び概略断面図である。

【図13】図13は、第3実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図14】図14は、第3実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図15】図15は、第3実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図16】図16は、第3実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図17】図17は、第4実施形態による半導体装置の構造を示す概略断面図である。

【図18】図18は、第4実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図19】図19は、第4実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図20】図20は、第5実施形態による半導体装置の構造を示す概略断面図である。

【図21】図21は、第5実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図22】図22は、第5実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図23】図23は、第6実施形態による半導体装置の構造を示す概略断面図である。

【図24】図24は、第6実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図25】図25は、第6実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図26】図26は、第7実施形態による半導体装置の構造を示す概略断面図である。

【図27】図27は、第7実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図28】図28は、第7実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図29】図29は、第7実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図30】図30は、第7実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図31】図31は、第7実施形態による半導体装置の製造方法を示す工程断面図(その5)である。

【図32】図32は、第7実施形態による半導体装置の製造方法を示す工程断面図(その6)である。

【発明を実施するための形態】

【0013】

[第1実施形態]

第1実施形態による半導体装置及びその製造方法について図1乃至図5を用いて説明する。

【0014】

図1は、本実施形態による半導体装置の構造を示す平面図及び概略断面図である。図2乃至図5は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0015】

はじめに、本実施形態による半導体装置の構造について図1を用いて説明する。図1(a)は平面図であり、図1(b)は図1(a)のA−A′線断面図である。

【0016】

基板30上には、金属膜36が形成されている。金属膜36上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。絶縁膜16上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0017】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜16を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0018】

次に、本実施形態による半導体装置の製造方法について図2乃至図5を用いて説明する。

【0019】

まず、基板10を用意する。基板10は、グラフェンを合成するための下地として用いるものであり、少なくとも表面に、グラフェン及びグラフェンの触媒材料(触媒金属膜12)に対して選択的にエッチングが可能な材料により形成されている基板であれば、特に限定されるものではない。例えば、表面に膜厚が300nmのシリコン酸化膜が形成されたシリコン基板を適用することができる。

【0020】

次いで、基板10上に、例えばスパッタ法により、例えば膜厚500nmの鉄(Fe)を堆積し、鉄よりなる触媒金属膜12を形成する(図2(a))。触媒金属膜12は、グラフェンを成長する際の触媒として機能する材料であれば、特に限定されるものではない。

【0021】

次いで、例えば熱CVD法により、触媒金属膜12を触媒としてグラフェン14を合成する(図2(b))。例えば、成長温度を590℃、原料ガスにアセチレン・アルゴンの混合ガスを用い、更にアルゴンで希釈し、アルゴン:アセチレンの流量比を1000:0.1とした条件により、グラフェン14を合成する。グラフェン14の厚さは、単層又は数層(2層〜5層程度)であればよい。上記条件で5分間の合成を行うことにより、単層のグラフェン14を合成することができる。

【0022】

次いで、例えばALD(原子層堆積:Atomic Layer Deposition)法により、例えば膜厚10nmのアルミニウム酸化膜(AlO)を堆積し、アルミニウム酸化膜よりなる絶縁膜16を形成する(図2(c))。絶縁膜16は、グラフェンチャネルとバックゲート電極とを隔てるゲート絶縁膜となる膜である。アルミニウム酸化膜以外にも、チタン酸化膜、ハフニウム酸化膜、ジルコニウム酸化膜等を用いることも可能である。ALD法のほか、例えば、電子ビーム蒸着法により堆積したアルミナ(Al2O3)、シリカ(SiO2)、アルミニウム(Al)や、CVD法により堆積したTEOSなどのシリコン酸化膜を用いることも可能である。

【0023】

次いで、絶縁膜16上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜18を形成する(図3(a))。

【0024】

次いで、例えば弗酸水溶液を用い、基板10表面のシリコン酸化膜をウェットエッチングし、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18の積層構造体22を、基板10から剥離する(図3(b))。なお、基板10の除去は、後述する図4(a)の工程の後、図4(b)の工程の前に行うようにしてもよい。

【0025】

また、積層構造体22の製造とは別に、基板10とは異なる別の基板30を用意する。基板30は、グラフェントランジスタを形成する下地となるものであり、特に限定されるものではない。例えば、表面にシリコン酸化膜等の絶縁膜が形成されたシリコン基板等を適用することができる。トランジスタ等の素子や配線層が形成されたシリコン基板上に絶縁膜が形成されたものでもよい。

【0026】

次いで、基板30上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜32を形成する(図3(c))。

【0027】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように積層構造体22を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図4(a))。接合した金属膜18/32は、以後、金属膜36と表す。

【0028】

金属膜32と金属膜18との接合には、例えばフリップチップボンダを用い、例えば300℃の温度下で、単位面積(mm2)当たり0.1N〜1N程度の圧力をかけることにより、圧着を行う。なお、熱圧着の際の温度及び圧力は、基板サイズや金属種に応じて適宜選択することが望ましい。

【0029】

なお、上記の例では金熱圧着により金属膜32と金属膜18とを接合したが、圧着法は金−金による圧着に限定されるものではない。金のほか、例えば、銅(Cu)、銀(Ag)、ニッケル(Ni)、チタンシリサイド(TiSix)、シリコン(Si)、白金(Pt)等を用いることも可能である。また、プラズマ処理等によって膜表面を活性化した後に熱圧着するようにしてもよい。

【0030】

本実施形態では、グラフェン14を触媒金属膜12と絶縁膜16及び金属膜18との間に挟持した状態で基板30上に転写するため、転写の際にグラフェン14に皺や曲がりが生じることを防止できる。また、レジストなど、転写するための部材をグラフェン14に直に接触することはなく、レジスト残渣等によるグラフェン14へのダメージの導入も防止することができる。

【0031】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図4(b))。

【0032】

次いで、グラフェン14をパターニングし、グラフェンチャネル14aを形成する(図4(c))。パターニングの際のマスクとなるレジスト膜の形成には、フォトリソグラフィや電子線リソグラフィを用いることができる。グラフェン14のエッチングは、酸素プラズマ処理や、酸素雰囲気中で加熱することにより行うことができる。

【0033】

酸素プラズマ処理によるグラフェン14のエッチングでは、例えば、大気圧程度の酸素雰囲気中において300W程度のプラズマ中に試料を設置し、数分から数十分の処理を行うことにより、チャネル部以外のグラフェンを除去することができる。

【0034】

酸素雰囲気中で加熱することによるグラフェンのエッチングでは、例えば、1kPaの酸素雰囲気中で500℃から600℃程度の温度で適切な時間処理することにより、チャネル部以外のグラフェンを除去することができる。

【0035】

グラフェン14のエッチング条件は、グラフェンの質や層数等に応じて、適宜設定することが望ましい。

【0036】

グラフェンチャネル14aの形状は、用途により変化するものであり、特に限定されるものではない。典型的には、チャネル長が0.5nm〜500nm程度、チャネル幅が0.5nm〜1000nm程度の範囲である。特に、チャネル長5nm〜500nm程度、チャネル幅1nm〜50nm程度が特に好ましい。

【0037】

本実施形態では、基板10上の全面に合成したグラフェン14を基板30上に転写した後、このグラフェン14をパターニングしてグラフェンチャネル14aを形成するため、触媒の埋め込みや研磨といった複雑なプロセスは不要である。また、基板10上の全面に合成することから、均一性に優れた良質のグラフェン14を合成することができる。

【0038】

次いで、必要に応じて、下層の絶縁膜16及び金属膜36をパターニングし、金属膜36よりなる電極パターンや配線パターンを形成するようにしてもよい。

【0039】

次いで、全面に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜を形成する。

【0040】

次いで、リソグラフィ及びドライエッチングにより、この金属膜をパターニングし、パターニングしたグラフェンチャネル14aの両端部にそれぞれ接するソース電極38及びドレイン電極40を形成する(図5(a))。ソース電極38及びドレイン電極40の形成方法は、特に限定されるものではなく、リフトオフ法等により形成してもよい。

【0041】

次いで、例えばALD法により、例えば膜厚10nmのアルミナを堆積し、アルミナよりなる絶縁膜42を形成する(図5(b))。絶縁膜42は、グラフェンチャネル14aとトップゲート電極とを隔てるゲート絶縁膜となる膜である。

【0042】

次いで、絶縁膜42上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタンと膜厚200nmの金とを順次堆積し、Au/Ti構造の金属膜を形成する。

【0043】

次いで、リソグラフィ及びドライエッチングにより、この金属膜をパターニングし、ゲート電極44を形成する(図5(c))。ゲート電極44の形成方法は、特に限定されるものではなく、リフトオフ法等により形成してもよい。

【0044】

この後、必要に応じて、所定の素子、配線層、パッシベーション膜等を形成し、本実施形態による半導体装置を完成する。

【0045】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0046】

[第2実施形態]

第2実施形態による半導体装置及びその製造方法について図6乃至図9を用いて説明する。図1乃至図5に示す第1実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0047】

図6は、本実施形態による半導体装置の構造を示す平面図及び概略断面図である。図7乃至図9は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0048】

はじめに、本実施形態による半導体装置の構造について図6を用いて説明する。図6(a)は平面図であり、図6(b)は図6(a)のA−A′線断面図である。

【0049】

基板30上には、金属膜36が形成されている。金属膜36が形成された基板30上には、絶縁膜46が形成されている。絶縁膜46上には、グラフェンチャネル14aが形成されている。絶縁膜46上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0050】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜46を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0051】

本実施形態による半導体装置では、図1に示す第1実施形態による半導体装置とは異なり、金属膜36が所定のバックゲート電極の形状にパターニングされている。図6の例では、グラフェンチャネル14aのパターンを包含するようにバックゲート電極のパターンを形成しているが、バックゲート電極のパターンは、これに限定されるものではない。ゲート電極44と同様、グラフェンチャネル14aの一部の領域に重なるように、バックゲート電極のパターンを形成してもよい。

【0052】

次に、本実施形態による半導体装置の製造方法について図7乃至図9を用いて説明する。

【0053】

まず、図2(a)乃至図3(a)に示す第1実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18を形成する(図7(a))。

【0054】

次いで、リソグラフィ及びドライエッチングにより、金属膜18を、所定の形状(ここではバックゲート電極のパターン)にパターニングする(図7(b))。

【0055】

次いで、全面に、例えばALD法によりアルミナを堆積後、例えばCMP(化学的機械的研磨:Chemical Mechanical Polishing)法により、金属膜18が露出するまでこのアルミナを研磨する。これにより、金属膜18が形成されていない領域の絶縁膜16上に、アルミナよりなる絶縁膜20を形成する(図7(c))。

【0056】

次いで、例えば弗酸水溶液を用い、基板10表面のシリコン酸化膜をウェットエッチングし、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18/絶縁膜20の積層構造体22を、基板10から剥離する。

【0057】

また、図3(c)に示す第1実施形態による半導体装置の製造方法と同様にして、基板30上に、金属膜32を形成する(図8(a))。

【0058】

次いで、リソグラフィ及びドライエッチングにより、金属膜32を、所定の形状(ここではバックゲート電極のパターン)にパターニングする(図8(b))。

【0059】

次いで、全面に、例えばALD法によりアルミナを堆積後、例えばCMP法により、金属膜32が露出するまでこのアルミナを研磨する。これにより、金属膜32が形成されていない領域の基板30上に、アルミナよりなる絶縁膜34を形成する(図8(c))。

【0060】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように積層構造体22を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図9(a))。接合した金属膜18/32は、以後、金属膜36と表す。また、絶縁膜16,20,34は、以後、絶縁膜46と表す。

【0061】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図9(b))。

【0062】

次いで、図4(c)乃至図5(c)に示す第1実施形態による半導体装置の製造方法と同様にして、グラフェン14をパターニングしてグラフェンチャネル14aを形成し、ソース電極38、ドレイン電極40、ゲート絶縁膜42及びゲート電極44を形成する(図9(c))。

【0063】

なお、上記の例では、所定形状にパターニングされたバックゲート電極を、金属膜18と金属膜32とを接合した金属膜36により形成している。しかしながら、金属膜18と金属膜32との接合部分が電極部や配線部のみでは、基板の表面全体に対する接合面積の割合が不十分となり、確実に貼り合わせることが困難になることも考えられる。このような場合には、金属膜18及び金属膜32に、実デバイスに使用される電極パターンや配線パターンのほかに、貼り合わせ用のダミー電極パターンを設けるようにしてもよい。

【0064】

例えば図10に示すように、金属膜36により、バックゲート電極36Aと、トランジスタの周囲に配置された貼り合わせ用ダミー電極パターン36Bとを設けるようにしてもよい。

【0065】

或いは、例えば図11に示すように、金属膜36により、バックゲート電極36A、貼り合わせ用ダミー電極パターン36B、ソース電極38用のコンタクトパッド部36C、ドレイン電極40用のコンタクトパッド部36D等を設けるようにしてもよい。

【0066】

これにより、基板の表面全体に対する接合面積の割合を増加することができ、基板10上に積層構造体22を確実に貼り合わせることができる。

【0067】

貼り合わせ用ダミー電極パターン36Bを設ける場合、金属膜18,32により形成する電極パターンや配線パターンは、必ずしもこれらの積層体である金属膜36により形成する必要はない。例えば、図10,11の例では、バックゲート電極36Aの全体又は一部を、金属膜18又は金属膜32のみにより形成するようにしてもよい。例えば、グラフェンチャネル14a直下のバックゲート電極36Aの機能部を金属膜18のみにより形成し、これに接続されるコンタクトパッド部を金属膜36により形成することができる。

【0068】

金属膜36により形成する電極パターン、配線パターン、貼り合わせ用ダミー電極パターンは、上記配置に限定されるものではなく、必要に応じて適宜変更が可能である。また、電極パターンや配線パターンについては、前述の通り、金属膜36により形成してもよいし、金属膜18又は金属膜32のいずれかのみで形成してもよい。

【0069】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0070】

[第3実施形態]

第3実施形態による半導体装置及びその製造方法について図12乃至図16を用いて説明する。図1乃至図11に示す第1及び第2実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0071】

図12は、本実施形態による半導体装置の構造を示す平面図及び概略断面図である。図13乃至図16は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0072】

はじめに、本実施形態による半導体装置の構造について図10を用いて説明する。図12(a)は平面図であり、図12(b)は図12(a)のA−A′線断面図である。

【0073】

基板30上には、金属膜36が形成されている。金属膜36上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。金属膜36、絶縁膜16及びグラフェンチャネル16aは、同じ形状にパターニングされており、側壁部分には絶縁膜48が形成されている。基板30上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0074】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜16を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0075】

本実施形態による半導体装置では、図1に示す第1実施形態による半導体装置とは異なり、金属膜36がグラフェンチャネル14aと同じ形状のバックゲート電極の形状にパターニングされている。図12の例では、金属膜36により形成されたバックゲート電極の引き出し線を、金属膜32により形成している。

【0076】

次に、本実施形態による半導体装置の製造方法について図11乃至図14を用いて説明する。

【0077】

まず、図2(a)乃至図3(a)に示す第1実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18を形成する(図13(a))。

【0078】

次いで、リソグラフィ及びドライエッチングにより、金属膜18、絶縁膜16、グラフェン14及び触媒金属膜12を、形成しようとするグラフェンチャネル14aの形状にパターニングする。このパターニングにより、グラフェン14よりなるグラフェンチャネル14aが形成される(図13(b))。なお、本パターニング工程では、必ずしも触媒金属膜12までパターニングする必要はない。少なくとも、金属膜18、絶縁膜16及びグラフェン14を所定形状にパターニングすればよい。

【0079】

本実施形態では、絶縁膜16及び金属膜18が覆われた状態でグラフェン14をパターニングするため、グラフェン14が直にレジスト膜が塗布されたり、グラフェン14がレジスト膜の除去雰囲気に曝されたりすることはない。したがって、第1及び第2実施形態の場合と比較して、グラフェン14に導入されるダメージを低減することができる。

【0080】

なお、貼り合わせ用ダミー電極パターンを配置して接合面積を増加する場合は、貼り合わせ用ダミー電極パターンの形成領域にも金属膜18、絶縁膜16、グラフェン14及び触媒金属膜12の積層構造体が残存するように、パターニングを行う。

【0081】

また、図3(c)に示す第1実施形態による半導体装置の製造方法と同様にして、基板30上に、金属膜32を形成する(図14(a))。

【0082】

次いで、リソグラフィ及びドライエッチングにより、金属膜32を、所定の形状にパターニングする(図8(b))。ここでは、金属膜32により、バックゲート電極のパターン32Aと、ソース電極38用のコンタクトパッド部のパターン32Bと、ドレイン電極40用のコンタクトパッド部のパターン32Cとを形成するものとする。貼り合わせ用ダミー電極パターンを配置して接合面積を増加する場合は、貼り合わせ用ダミー電極パターンの形成領域にも金属膜32が残存するように、パターニングを行う。

【0083】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように積層構造体22を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図15(a))。接合した部分の金属膜18/32は、以後、金属膜36と表す。

【0084】

この際、例えば基板10,30のオリエンテーションフラットを利用して位置合わせを行えば所望の箇所で圧着できるようにパターンを配置しておくことにより、基板10,30の位置合わせを容易に行うことができる。

【0085】

なお、本実施形態では、金属膜18,32の周囲が絶縁膜によって平坦化されていないため、接合する金属膜18のパターンと金属膜32のパターンとが異なっていると、金属膜18又は金属膜32のいずれか一方が形成されていない領域には空隙が形成される。かかる観点から、金属膜18のパターンと金属膜32のパターンとは、互いに鏡像のような関係であることが望ましい。

【0086】

次いで、例えば弗酸水溶液を用い、基板10表面のシリコン酸化膜をウェットエッチングし、基板10を触媒金属膜12上から剥離する(図15(b))。

【0087】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図15(c))。

【0088】

次いで、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に、選択的に絶縁膜48を形成する(図16(a))。例えば、全面に例えばALD法によりアルミナを堆積後、このアルミナをパターニングし、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に選択的に絶縁膜48を残存させる。或いは、全面に例えばALD法によりアルミナを堆積後、このアルミナをエッチバックし、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に選択的に絶縁膜48を残存させる。

【0089】

絶縁膜48は、金属膜36の側壁部分を覆いソース電極38及びドレイン電極40から金属膜36を分離するためのものである。絶縁膜48は、この目的を達成しうるものであれば、如何なる方法を用いて形成してもよい。

【0090】

絶縁膜48を形成する工程は、図15(b)の工程の後、図15(c)の工程の前に行ってもよい。この場合、絶縁膜48のエッチバックやパターニングの際にはグラフェンチャネル14aが触媒金属膜12により覆われているため、グラフェンチャネル14aに導入されるダメージを低減することができる。

【0091】

次いで、図5(a)に示す第1実施形態による半導体装置の製造方法と同様にして、グラフェンチャネル14aに接続されたソース電極38及びドレイン電極40を形成する(図16(b))

次いで、図5(b)乃至図5(c)に示す第1実施形態による半導体装置の製造方法と同様にして、ゲート絶縁膜42及びゲート電極44を形成する(図16(c))。

【0092】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0093】

[第4実施形態]

第4実施形態による半導体装置及びその製造方法について図17乃至図19を用いて説明する。図1乃至図16に示す第1乃至第3実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0094】

図17は、本実施形態による半導体装置の構造を示す概略断面図である。図18及び図19は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0095】

はじめに、本実施形態による半導体装置の構造について図17を用いて説明する。

【0096】

基板30上には、金属膜36が形成されている。金属膜36上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。金属膜36、絶縁膜16及びグラフェンチャネル16aは、同じ形状にパターニングされており、側壁部分には絶縁膜48が形成されている。基板30上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜50が形成されている。グラフェンチャネル14a上の絶縁膜50上には、ゲート電極44が形成されている。

【0097】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜16を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜50を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0098】

本実施形態による半導体装置では、絶縁膜50が、グラフェンチャネル14aを合成する際に用いた触媒金属材料の絶縁性化合物により形成されているほかは、図12に示す第3実施形態による半導体装置と基本的に同じである。

【0099】

次に、本実施形態による半導体装置の製造方法について図18及び図19を用いて説明する。図13(a)乃至図15(b)に示す第3実施形態による半導体装置の製造方法と同様にして、金属膜32が形成された基板30上に、金属膜18、絶縁膜16、グラフェンチャネル14a及び触媒金属膜12の積層構造体を転写する(図18(a))。

【0100】

次いで、例えばドライエッチングにより、触媒金属膜12を研磨或いはドライエッチングし、触媒金属膜12の膜厚が例えば20nm程度になるまで薄膜化する(図18(b))。

【0101】

次いで、薄膜化した触媒金属膜12を酸化し、触媒金属膜12を形成する触媒金属材料の酸化物よりなる絶縁膜50を形成する(図18(c))。例えば、圧力1Pa程度の酸素雰囲気中で200W程度のプラズマに触媒金属膜12を10分間曝すことにより、絶縁膜50を形成することができる。

【0102】

この際、露出している部分は耐酸化性の強い金や絶縁膜により形成されており、酸化による影響を受けることはほとんどない。グラフェンチャネル14aの側壁部分が反応することもあるが、影響は軽微である。

【0103】

触媒金属膜12を薄膜化する工程では、薄膜化した触媒金属膜12を酸化することにより得られる絶縁膜50の膜厚がゲート絶縁膜として所望の膜厚となるように、触媒金属膜12の残膜厚を適宜設定する。

【0104】

なお、絶縁膜50の形成は、触媒金属膜12の総てを酸化ないしは窒化して絶縁膜50を形成した後、絶縁膜50を所望の膜厚に薄膜化してもよい。ただし、触媒金属膜12を薄膜化してから酸化ないしは窒化して絶縁膜50を形成する方が、酸化雰囲気に曝されることによるダメージは軽減される。

【0105】

ゲート絶縁膜として適用可能な酸化物ないしは窒化物を形成する触媒金属材料としては、例えば、アルミニウム(Al)、ハフニウム(Hf)、ジルコニウム(Zr)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、シリコン(Si)、鉄(Fe)、銅(Cu)、コバルト(Co)又はこれらを少なくとも1種以上含む合金が挙げられる。

【0106】

次いで、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に、図16(a)に示す第3実施形態による半導体装置の製造方法と同様にして、絶縁膜48を形成する(図19(a))。

【0107】

次いで、リソグラフィ及びエッチングにより、絶縁膜50をパターニングし、グラフェンチャネル14aの両端部を露出する(図19(b))。

【0108】

次いで、図16(b)乃至図16(c)に示す第3実施形態による半導体装置の製造方法と同様にして、ソース電極38、ドレイン電極40、ゲート絶縁膜42及びゲート電極44を形成する(図19(c))。

【0109】

本実施形態の方法では、一連の製造プロセスを通してグラフェンチャネル14aが基板表面に露出されず、グラフェンチャネル14aに物理的或いは化学的な処理が施されることはない。これにより、グラフェンチャネル14aに与えるダメージを最小限に抑えることができる。

【0110】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0111】

[第5実施形態]

第5実施形態による半導体装置及びその製造方法について図20乃至図22を用いて説明する。図1乃至図19に示す第1乃至第4実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0112】

図20は、本実施形態による半導体装置の構造を示す概略断面図である。図21及び図22は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0113】

はじめに、本実施形態による半導体装置の構造について図20を用いて説明する。

【0114】

基板30上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。絶縁膜16上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0115】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。

【0116】

次に、本実施形態による半導体装置の製造方法について図21及び図22を用いて説明する。

【0117】

まず、図2(a)乃至図2(c)に示す第1実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14及び絶縁膜16を形成する(図21(a))。なお、ここでは、絶縁膜16をシリコン酸化膜により形成するものとする。

【0118】

また、基板10とは別に、表面にシリコン酸化膜の絶縁膜が形成された基板30を用意する。

【0119】

次いで、基板30上に、適宜位置合わせを行いながら、基板30側に絶縁膜16が向き合うように基板10を重ね合わせる。

【0120】

次いで、基板30と基板10との間に圧力をかけながら、窒素雰囲気中で、例えば800℃〜1000℃程度の温度で1時間程度の熱処理を行う。これにより、基板30表面のシリコン酸化膜と絶縁膜16とが接合される(図21(b))。

【0121】

シリコン酸化膜同士を圧着する際の温度や時間は、圧着面積、基板の反り状況等に応じて変化するため、適宜設定することが望ましい。ここでは、圧着する絶縁膜としてシリコン酸化膜を用いているが、シリコン窒化膜やアルミナ等の絶縁物や酸化物であれば特に制限はない。

【0122】

本実施形態では、グラフェン14を触媒金属膜12と絶縁膜16との間に挟持した状態で基板30上に転写するため、転写の際にグラフェン14に皺や曲がりが生じることを防止できる。また、レジストなど、転写するための部材をグラフェン14に直に接触することはなく、レジスト残渣等によるグラフェン14へのダメージの導入も防止することができる。

【0123】

なお、第3実施形態と同様に、絶縁膜16、グラフェン14及び触媒金属膜12を所定形状にパターニングした後、基板10と基板30とを接合するようにしてもよい。

【0124】

次いで、例えば弗酸水溶液を用いて基板10表面のシリコン酸化膜をウェットエッチングし、基板10を除去する。

【0125】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図22(a))。なお、基板10を除去する工程を別途行わずに、触媒金属膜12をエッチングすることによって基板10を同時に除去するようにしてもよい。

【0126】

次いで、グラフェン14をパターニングし、グラフェンチャネル14aを形成する(図22(b))。

【0127】

次いで、図5(a)乃至図5(c)に示す第1実施形態による半導体装置の製造方法と同様にして、ソース電極38、ドレイン電極40、絶縁膜42及びゲート電極44を形成する(図22(c))。

【0128】

このように、本実施形態によれば、グラフェン上に絶縁膜が形成された状態で、絶縁膜が形成された別の基板上に、絶縁膜同士の圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0129】

[第6実施形態]

第6実施形態による半導体装置及びその製造方法について図23乃至図25を用いて説明する。図1乃至図22に示す第1乃至第5実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0130】

図23は、本実施形態による半導体装置の構造を示す概略断面図である。図24及び図25は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0131】

はじめに、本実施形態による半導体装置の構造について図23を用いて説明する。

【0132】

基板30上には、金属膜36が形成されている。金属膜36が形成された基板30上には、絶縁膜46が形成されている。絶縁膜46上には、グラフェンチャネル14aが形成されている。絶縁膜46上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0133】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜46を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0134】

次に、本実施形態による半導体装置の製造方法について図24及び図25を用いて説明する。

【0135】

まず、図7(a)乃至図7(c)に示す第2実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14、絶縁膜16、金属膜18及び絶縁膜20を形成する(図24(a))。

【0136】

また、基板30上に、表面部に金属膜32が埋め込まれた絶縁膜34を形成する(図24(b))。

【0137】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように、また、絶縁膜34と絶縁膜20とが向き合うように、基板10を重ね合わせる。

【0138】

次いで、基板30と基板10との間に単位面積(mm2)当たり0.1N〜1N程度の圧力をかけながら、窒素雰囲気中で、例えば200℃〜800℃程度の温度で1時間程度の熱処理を行う。これにより、金属膜32と金属膜18とが接合され、絶縁膜34と絶縁膜20とが接合される(図24(c))。接合した金属膜18/32は、以後、金属膜36と表す。また、絶縁膜16,20,34は、絶縁膜46と表す。

【0139】

次いで、例えば弗酸水溶液を用いて基板10表面のシリコン酸化膜をウェットエッチングし、基板10を除去する。

【0140】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図25(a))。なお、基板10を除去する工程を別途行わずに、触媒金属膜12をエッチングすることによって基板10を同時に除去するようにしてもよい。

【0141】

次いで、グラフェン14をパターニングし、グラフェンチャネル14aを形成する(図25(b))。

【0142】

次いで、図9(c)に示す第2実施形態による半導体装置の製造方法と同様にして、ソース電極38、ドレイン電極40、絶縁膜42及びゲート電極44を形成する(図25(c))。

【0143】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜同士及び絶縁膜同士の圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0144】

[第7実施形態]

第7実施形態による半導体装置及びその製造方法について図26乃至図32を用いて説明する。図1乃至図25に示す第1乃至第6実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0145】

図26は、本実施形態による半導体装置の構造を示す概略断面図である。図27及び図32は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0146】

はじめに、本実施形態による半導体装置の構造について図26を用いて説明する。

【0147】

基板30上には、金属膜36が形成されている。金属膜36が形成された基板30上には、絶縁膜46が形成されている。絶縁膜46上には、グラフェンチャネル14aが形成されている。絶縁膜46上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。ソース電極38上及びドレイン電極40上には、触媒金属膜52が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極を兼ねる触媒金属膜52が形成されている。こうして、基板30上には、金属膜36をバックゲート電極とし、絶縁膜42上の触媒金属膜54をトップゲート電極としたダブルゲートトランジスタが形成されている。

【0148】

グラフェントランジスタが形成された基板30上には、層間絶縁膜56が形成されている。層間絶縁膜56には、ゲート電極(触媒金属膜52)、ソース電極38及びドレイン電極に電気的に接続されたカーボンナノチューブ束よりなるビア配線54が埋め込まれている。ビア配線54が埋め込まれ層間絶縁膜54上には、ビア配線54に接続して、金属膜68,70に挟持されたグラフェン配線64aが形成されている。

【0149】

グラフェン配線64aが形成された層間絶縁膜56上には、層間絶縁膜74が形成されている。層間絶縁膜74には、グラフェン配線64aに電気的に接続されたカーボンナノチューブ束よりなるビア配線72が埋め込まれている。ビア配線72が埋め込まれた層間絶縁膜74上には、ビア配線72に接続して、下面側に金属膜76が形成されたグラフェン配線78が形成されている。

【0150】

このように、本実施形態による半導体装置は、配線層をグラフェン配線54,74により形成したものである。配線層をグラフェンにより形成することにより、配線層を容易に低抵抗化することができる。グラフェン配線54,74は、後述するように、グラフェンチャネル14aと同様のプロセスを用いて形成することができる。

【0151】

また、本実施形態による半導体装置では、ビア配線をカーボンナノチューブ束により形成している。ビア配線をカーボンナノチューブ束により形成することにより、ビア配線を容易に低抵抗化することができる。なお、ビア配線は、必ずしもカーボンナノチューブ束により形成する必要はなく、通常のビア配線形成プロセスを適用することも可能である。

【0152】

次に、本実施形態による半導体装置の製造方法について図27乃至図32を用いて説明する。

【0153】

まず、図7(a)乃至図9(c)に示す第2実施形態による半導体装置の製造方法と同様にして、基板30上に、金属膜36、絶縁膜46、グラフェンチャネル14a、ソース電極38、ドレイン電極40及び絶縁膜42を形成する(図27(a))。

【0154】

なお、本実施形態では、下地のトランジスタ構造として第2実施形態の構造を適用した例を示すが、下地のトランジスタ構造は、これに限定されるものではない。第2実施形態の構造の代わりに、第1、第3乃至第6実施形態のいずれかの構造を適用してもよいし、他のトランジスタ構造を適用してもよい。また、図27(a)ではゲート電極44を形成していないが、図9(c)と同様にして、絶縁膜42上にゲート電極44を形成してもよい。

【0155】

次いで、リソグラフィ及びエッチングにより、絶縁膜42をパターニングし、ソース電極38及びドレイン電極40の表面を露出する(図27(b))。

【0156】

次いで、例えばリフトオフ法により、ソース電極38及びドレイン電極40上のコンタクト形成部、並びに、絶縁膜42上のゲート電極の形成部に、触媒金属膜52を形成する(図27(b))。絶縁膜42上の触媒金属膜52は、ゲート電極として用いることができる。絶縁膜42上にゲート電極44を形成している場合は、ゲート電極44上のコンタクト形成部に、触媒金属膜52を形成する。なお、触媒金属膜52の形成方法は、リフトオフ法に限定されるものではない。

【0157】

触媒金属膜52は、例えば、膜厚5nmのタンタル(Ta)膜と、膜厚5nmの窒化チタン(TiN)膜と、膜厚1nmのコバルト(Co)膜とを、スパッタ法により順次堆積することにより形成する。コバルトは触媒材料であり、窒化チタンは合成を促進するサポート材料であり、タンタルは下地の金属の拡散を防止する膜である。

【0158】

触媒材料としては、コバルトのほか、例えば、鉄(Fe)、ニッケル(Ni)、銅(Cu)、金(Au)、白金(Pt)、又はこれらのうちの少なくとも1種を含む合金や、これらの酸化物・窒化物等の化合物を適用することができる。

【0159】

サポート材料としては、窒化チタンのほか、例えば、アルミニウム(Al)、ハフニウム(Hf)、ジルコニウム(Zr)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、シリコン(Si)、チタンシリサイド(TiSix)、バナジウム(V)、ニオブ(Nb)、ルテニウム(Ru)又はこれらのうちの少なくとも1種を含む合金や、これらの酸化物・窒化物等の化合物を適用することができる。

【0160】

拡散防止膜としては、タンタルのほか、例えば、チタン(Ti)、ルテニウム(Ru)又はこれらのうちの少なくとも1種を含む合金や、これらの酸化物・窒化物等の化合物を適用することができる。

【0161】

次いで、例えば熱CVD法により、触媒金属膜52を触媒としてカーボンナノチューブを合成し、触媒金属膜52上にカーボンナノチューブの束よりなるビア配線54形成する(図28(a))。例えば、原料ガスにアセチレン・アルゴンの混合ガスを用い(アセチレンガスはアルゴンの0.1%以下)、圧力1kPa、基板温度450℃の条件で、長さ500nm程度のカーボンナノチューブを成長する。

【0162】

次いで、例えばCVD法により、例えばシリコン酸化膜を堆積し、シリコン酸化膜

の層間絶縁膜56を形成する(図28(b))。

【0163】

次いで、例えばCMP法により、層間絶縁膜56の表面を研磨し、層間絶縁膜56の表面にビア配線54の上端部を露出させる(図29(a))。

【0164】

次いで、層間絶縁膜56上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜58を形成する。

【0165】

次いで、リソグラフィ及びエッチングにより金属膜58をパターニングし、ビア配線54に接続された所定の配線パターンを形成する(図29(b))。

【0166】

また、基板10,30とは別に、基板60を用意する。基板60は、グラフェンを合成するための下地として用いるものであり、少なくとも表面に、グラフェン及びグラフェンの触媒材料(触媒金属膜62)に対して選択的にエッチングが可能な材料により形成されている基板であれば、特に限定されるものではない。例えば、表面に膜厚が300nmのシリコン酸化膜が形成されたシリコン基板を適用することができる。

【0167】

次いで、基板60上に、例えばスパッタ法により、例えば膜厚500nmの鉄(Fe)を堆積し、鉄よりなる触媒金属膜62を形成する。

【0168】

次いで、グラフェン14の合成と同様にして、触媒金属膜62を触媒としてグラフェン64を合成する。このグラフェン64は、配線として用いるものであり、層数は配線抵抗の要求等に応じて適宜増減することができる。

【0169】

次いで、グラフェン64上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜66を形成する(図30(a))。

【0170】

次いで、リソグラフィ及びエッチングにより、金属膜66、グラフェン64及び触媒金属膜62を、金属膜58の配線パターンに対応した所定の形状にパターニングする(図30(b))。このパターニングにより、グラフェン64よりなるグラフェン配線64aを形成する。なお、本パターニング工程では、必ずしも触媒金属膜62までパターニングする必要はない。少なくとも、金属膜66及びグラフェン64を所定形状にパターニングすればよい。

【0171】

次いで、金属膜58が形成された絶縁膜56上に、適宜位置合わせを行いながら、金属膜58と金属膜66とが向き合うように基板60を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図31(a))。接合した金属膜66/58は、以後、金属膜68と表す。

【0172】

次いで、例えば弗酸水溶液を用いて基板60表面のシリコン酸化膜をウェットエッチングし、基板60を除去する。

【0173】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜62を選択的に除去する(図31(b))。

【0174】

こうして、グラフェントランジスタのゲート電極(触媒金属膜52)、ソース電極38及びドレイン電極40に、カーボンナノチューブ束のビア配線54を介して電気的に接続されたグラフェン配線64aを形成する。

【0175】

なお、図29(b)の工程の後、触媒金属膜を堆積し、これを触媒としてグラフェン配線を直に形成することも考えられる。本実施形態のメリットとしては、グラフェン配線の下地となる金属膜が触媒金属材料に限定されない点が挙げられる。

【0176】

次いで、必要に応じて、グラフェン配線64a上に、図27(c)乃至図31(b)の工程と同様にして、触媒金属膜70、ビア配線72、層間絶縁膜74、金属膜76及びグラフェン配線78を繰り返し形成し、多層配線構造を形成する(図32)。

【0177】

このように、本実施形態によれば、グラフェン上に金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0178】

[変形実施形態]

上記実施形態に限らず種々の変形が可能である。

【0179】

例えば、上記実施形態では、熱CVD法によりグラフェンを合成する方法を示したが、熱CVD法に限らず、リモートプラズマCVD法、プラズマCVD法等を用いてもよい。また、原料ガスとしては、アセチレンに限らず、エチレンガス、メタンガスなどの炭化水素ガス、エタノールなどのアルコール、ベンゼン等を用いてもよい。

【0180】

また、グラフェンの合成に用いる触媒も、鉄に限定されるものではなく、グラフェン合成の触媒として機能する他の材料を用いてもよい。例えば、Co(コバルト)、Ni(ニッケル)、Cu(銅)、Pt(プラチナ)、Au(金)等の金属、これらを少なくとも一種含む合金、炭化物、酸化物、窒化物等を用いてもよい。

【0181】

触媒金属膜12の成膜方法についても特に限定されるものではなく、スパッタ法に限らず、電子ビーム蒸着法、分子線エピタキシー法等を用いてもよい。

【0182】

グラフェンの他の合成方法としては、例えば、スパッタ法により熱酸化膜付きのシリコン基板上に堆積した膜厚500nmの銅薄膜を触媒として、熱CVD法によりグラフェンを合成する方法が挙げられる。この場合は、例えば、原料ガスとしてメタンを用い、ガスの分圧を、希釈用アルゴンガス900sccmに対して、水素100sccm、メタン10sccmとし、温度900℃でグラフェンを合成することができる。

【0183】

また、上記第7実施形態では、熱CVD法によりカーボンナノチューブを合成する方法を示したが、熱CVD法に限らず、リモートプラズマCVD法、プラズマCVD法等を用いてもよい。また、原料ガスとしては、アセチレンに限らず、エチレンガス、メタンガスなどの炭化水素ガス、エタノールなどのアルコール、ベンゼン等を用いてもよい。

【0184】

また、上記第1、第2、第3、第4、第6及び第7実施形態では、ダブルゲート構造のトランジスタを示し、上記第5実施形態では、トップゲート構造のトランジスタを示したが、トランジスタ構造は、これに限定されるものではない。

【0185】

例えば、上記第1、第2、第3、第4、第6及び第7実施形態では、必ずしもゲート電極44を必要はなく、バックゲート電極のみを有するバックゲート構造のトランジスタとしてもよい。或いは、上記第2及び第6実施形態では、必ずしもバックゲート電極を形成する必要はなく、ゲート電極44のみを有するトップゲート構造のトランジスタとしてもよい。或いは、金属膜36とグラフェンチャネル14aとを隔てる絶縁膜16,46の膜厚を厚膜化し、金属膜36が実質的にバックゲート電極として機能しないようにしてもよい。或いは、第1乃至第6実施形態に記載のグラフェンチャネル14aをグラフェン配線としてもよい。

【0186】

また、各実施形態に記載した構造や製造方法は、任意に組み合わせることができる。例えば、触媒金属膜12を酸化してゲート絶縁膜を形成する第4実施形態のプロセスを、第1、第2、第3、第5又は第6実施形態に適用してもよい。また、第7実施形態の配線構造を、第1乃至第6実施形態に適用してもよい。

【0187】

また、上記実施形態に記載した半導体装置の構造、構造パラメータ、構成材料、製造条件等は、一例を示したものにすぎず、当業者の技術常識等に応じて適宜修正や変更が可能である。

【0188】

また、上記実施形態では、グラフェンチャネルトランジスタやグラフェン配線に適用した例を示したが、これらに限定されるものではなく、グラフェンを有する種々のデバイスや構造体に適用することができる。

【符号の説明】

【0189】

10,30,60…基板

12,52,62,70…触媒金属膜

14,64…グラフェン

14a…グラフェンチャネル

16,20,34,42,46,48,50…絶縁膜

18,32,36,58,66,68,76…金属膜

22…積層構造体

38…ソース電極

40…ドレイン電極

44…ゲート電極

54,72…ビア配線

56,74…層間絶縁膜

64a,78…グラフェン配線

【技術分野】

【0001】

本発明は、グラフェンを用いた半導体装置の製造方法に関する。

【背景技術】

【0002】

シリコンを利用したCMOS技術は微細化の限界に近づきつつあり、その寿命を延ばすためのチャネル代替材料が模索されている。その最有力候補として、カーボンナノチューブやグラフェンを代表とするナノカーボン材料が注目されており、種々の研究・開発が行われている。

【0003】

ナノカーボン材料を用いたデバイスの一例として、電界効果トランジスタのチャネル領域にグラフェンを用いたグラフェントランジスタが挙げられる。グラフェンはシリコンと比較してキャリア移動度が高いため、グラフェンによりチャネルを形成することにより高速トランジスタを実現することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第2008/108383号パンフレット

【非特許文献】

【0005】

【非特許文献1】Y. Wang et al., "Scalable synthesis of graphene on patterned Ni and transfer", IEEE trans. Electron Devices, Vol. 57, No. 12, 2010

【発明の概要】

【発明が解決しようとする課題】

【0006】

グラフェンによりチャネルを形成するためには、絶縁膜上にグラフェンを形成することが求められる。しかしながら、グラフェンの合成には触媒が必要であり、合成したグラフェンの下地には触媒金属膜が存在する。そこで、別の基板上に合成したグラフェンを絶縁膜上に転写するプロセスが提案されているが、転写の際にグラフェンに皺や曲がり、レジスト残渣などのダメージが導入されたりすることがあり、所望のデバイス特性を安定して得ることが困難であった。

【0007】

本発明の目的は、絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0008】

実施形態の一観点によれば、第1の基板上に、第1の触媒金属膜を形成する工程と、前記第1の触媒金属膜上に、前記第1の触媒金属膜を触媒として、第1のグラフェンを形成する工程と、前記第1のグラフェン上に、第1の絶縁膜を形成する工程と、前記第1の絶縁膜上に、第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、前記第1の基板を除去する工程とを有する半導体装置の製造方法が提供される。

【0009】

また、実施形態の他の観点によれば、第1の基板上に、触媒金属膜を形成する工程と、前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、前記グラフェン上に、第1の金属膜を形成する工程と、前記第1の金属膜及び前記グラフェンをパターニングし、前記グラフェンよりなるグラフェン配線を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、前記第1の基板を除去する工程と、前記触媒金属膜を除去する工程とを有する半導体装置の製造方法が提供される。

【0010】

また、実施形態の更に他の観点によれば、第1の基板上に、触媒金属膜を形成する工程と、前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、前記グラフェン上に、第1の絶縁膜を形成する工程と、第2の基板上に第2の絶縁膜を形成する工程と、前記第1の絶縁膜の表面と前記第2の絶縁膜の表面とを対向させ、前記第1の絶縁膜と前記第2の絶縁膜とを接合する工程と、前記第1の基板を除去する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0011】

開示の半導体装置の製造方法によれば、グラフェン上に絶縁膜及び金属膜が状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【図面の簡単な説明】

【0012】

【図1】図1は、第1実施形態による半導体装置の構造を示す平面図及び概略断面図である。

【図2】図2は、第1実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図3】図3は、第1実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図4】図4は、第1実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図5】図5は、第1実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図6】図6は、第2実施形態による半導体装置の構造を示す平面図及び概略断面図である。

【図7】図7は、第2実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図8】図8は、第2実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図9】図9は、第2実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図10】図10は、第2実施形態の変形例による半導体装置の構造を示す平面図(その1)である。

【図11】図11は、第2実施形態の変形例による半導体装置の構造を示す平面図(その2)である。

【図12】図12は、第3実施形態による半導体装置の構造を示す平面図及び概略断面図である。

【図13】図13は、第3実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図14】図14は、第3実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図15】図15は、第3実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図16】図16は、第3実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図17】図17は、第4実施形態による半導体装置の構造を示す概略断面図である。

【図18】図18は、第4実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図19】図19は、第4実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図20】図20は、第5実施形態による半導体装置の構造を示す概略断面図である。

【図21】図21は、第5実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図22】図22は、第5実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図23】図23は、第6実施形態による半導体装置の構造を示す概略断面図である。

【図24】図24は、第6実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図25】図25は、第6実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図26】図26は、第7実施形態による半導体装置の構造を示す概略断面図である。

【図27】図27は、第7実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図28】図28は、第7実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図29】図29は、第7実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図30】図30は、第7実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図31】図31は、第7実施形態による半導体装置の製造方法を示す工程断面図(その5)である。

【図32】図32は、第7実施形態による半導体装置の製造方法を示す工程断面図(その6)である。

【発明を実施するための形態】

【0013】

[第1実施形態]

第1実施形態による半導体装置及びその製造方法について図1乃至図5を用いて説明する。

【0014】

図1は、本実施形態による半導体装置の構造を示す平面図及び概略断面図である。図2乃至図5は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0015】

はじめに、本実施形態による半導体装置の構造について図1を用いて説明する。図1(a)は平面図であり、図1(b)は図1(a)のA−A′線断面図である。

【0016】

基板30上には、金属膜36が形成されている。金属膜36上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。絶縁膜16上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0017】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜16を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0018】

次に、本実施形態による半導体装置の製造方法について図2乃至図5を用いて説明する。

【0019】

まず、基板10を用意する。基板10は、グラフェンを合成するための下地として用いるものであり、少なくとも表面に、グラフェン及びグラフェンの触媒材料(触媒金属膜12)に対して選択的にエッチングが可能な材料により形成されている基板であれば、特に限定されるものではない。例えば、表面に膜厚が300nmのシリコン酸化膜が形成されたシリコン基板を適用することができる。

【0020】

次いで、基板10上に、例えばスパッタ法により、例えば膜厚500nmの鉄(Fe)を堆積し、鉄よりなる触媒金属膜12を形成する(図2(a))。触媒金属膜12は、グラフェンを成長する際の触媒として機能する材料であれば、特に限定されるものではない。

【0021】

次いで、例えば熱CVD法により、触媒金属膜12を触媒としてグラフェン14を合成する(図2(b))。例えば、成長温度を590℃、原料ガスにアセチレン・アルゴンの混合ガスを用い、更にアルゴンで希釈し、アルゴン:アセチレンの流量比を1000:0.1とした条件により、グラフェン14を合成する。グラフェン14の厚さは、単層又は数層(2層〜5層程度)であればよい。上記条件で5分間の合成を行うことにより、単層のグラフェン14を合成することができる。

【0022】

次いで、例えばALD(原子層堆積:Atomic Layer Deposition)法により、例えば膜厚10nmのアルミニウム酸化膜(AlO)を堆積し、アルミニウム酸化膜よりなる絶縁膜16を形成する(図2(c))。絶縁膜16は、グラフェンチャネルとバックゲート電極とを隔てるゲート絶縁膜となる膜である。アルミニウム酸化膜以外にも、チタン酸化膜、ハフニウム酸化膜、ジルコニウム酸化膜等を用いることも可能である。ALD法のほか、例えば、電子ビーム蒸着法により堆積したアルミナ(Al2O3)、シリカ(SiO2)、アルミニウム(Al)や、CVD法により堆積したTEOSなどのシリコン酸化膜を用いることも可能である。

【0023】

次いで、絶縁膜16上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜18を形成する(図3(a))。

【0024】

次いで、例えば弗酸水溶液を用い、基板10表面のシリコン酸化膜をウェットエッチングし、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18の積層構造体22を、基板10から剥離する(図3(b))。なお、基板10の除去は、後述する図4(a)の工程の後、図4(b)の工程の前に行うようにしてもよい。

【0025】

また、積層構造体22の製造とは別に、基板10とは異なる別の基板30を用意する。基板30は、グラフェントランジスタを形成する下地となるものであり、特に限定されるものではない。例えば、表面にシリコン酸化膜等の絶縁膜が形成されたシリコン基板等を適用することができる。トランジスタ等の素子や配線層が形成されたシリコン基板上に絶縁膜が形成されたものでもよい。

【0026】

次いで、基板30上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜32を形成する(図3(c))。

【0027】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように積層構造体22を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図4(a))。接合した金属膜18/32は、以後、金属膜36と表す。

【0028】

金属膜32と金属膜18との接合には、例えばフリップチップボンダを用い、例えば300℃の温度下で、単位面積(mm2)当たり0.1N〜1N程度の圧力をかけることにより、圧着を行う。なお、熱圧着の際の温度及び圧力は、基板サイズや金属種に応じて適宜選択することが望ましい。

【0029】

なお、上記の例では金熱圧着により金属膜32と金属膜18とを接合したが、圧着法は金−金による圧着に限定されるものではない。金のほか、例えば、銅(Cu)、銀(Ag)、ニッケル(Ni)、チタンシリサイド(TiSix)、シリコン(Si)、白金(Pt)等を用いることも可能である。また、プラズマ処理等によって膜表面を活性化した後に熱圧着するようにしてもよい。

【0030】

本実施形態では、グラフェン14を触媒金属膜12と絶縁膜16及び金属膜18との間に挟持した状態で基板30上に転写するため、転写の際にグラフェン14に皺や曲がりが生じることを防止できる。また、レジストなど、転写するための部材をグラフェン14に直に接触することはなく、レジスト残渣等によるグラフェン14へのダメージの導入も防止することができる。

【0031】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図4(b))。

【0032】

次いで、グラフェン14をパターニングし、グラフェンチャネル14aを形成する(図4(c))。パターニングの際のマスクとなるレジスト膜の形成には、フォトリソグラフィや電子線リソグラフィを用いることができる。グラフェン14のエッチングは、酸素プラズマ処理や、酸素雰囲気中で加熱することにより行うことができる。

【0033】

酸素プラズマ処理によるグラフェン14のエッチングでは、例えば、大気圧程度の酸素雰囲気中において300W程度のプラズマ中に試料を設置し、数分から数十分の処理を行うことにより、チャネル部以外のグラフェンを除去することができる。

【0034】

酸素雰囲気中で加熱することによるグラフェンのエッチングでは、例えば、1kPaの酸素雰囲気中で500℃から600℃程度の温度で適切な時間処理することにより、チャネル部以外のグラフェンを除去することができる。

【0035】

グラフェン14のエッチング条件は、グラフェンの質や層数等に応じて、適宜設定することが望ましい。

【0036】

グラフェンチャネル14aの形状は、用途により変化するものであり、特に限定されるものではない。典型的には、チャネル長が0.5nm〜500nm程度、チャネル幅が0.5nm〜1000nm程度の範囲である。特に、チャネル長5nm〜500nm程度、チャネル幅1nm〜50nm程度が特に好ましい。

【0037】

本実施形態では、基板10上の全面に合成したグラフェン14を基板30上に転写した後、このグラフェン14をパターニングしてグラフェンチャネル14aを形成するため、触媒の埋め込みや研磨といった複雑なプロセスは不要である。また、基板10上の全面に合成することから、均一性に優れた良質のグラフェン14を合成することができる。

【0038】

次いで、必要に応じて、下層の絶縁膜16及び金属膜36をパターニングし、金属膜36よりなる電極パターンや配線パターンを形成するようにしてもよい。

【0039】

次いで、全面に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜を形成する。

【0040】

次いで、リソグラフィ及びドライエッチングにより、この金属膜をパターニングし、パターニングしたグラフェンチャネル14aの両端部にそれぞれ接するソース電極38及びドレイン電極40を形成する(図5(a))。ソース電極38及びドレイン電極40の形成方法は、特に限定されるものではなく、リフトオフ法等により形成してもよい。

【0041】

次いで、例えばALD法により、例えば膜厚10nmのアルミナを堆積し、アルミナよりなる絶縁膜42を形成する(図5(b))。絶縁膜42は、グラフェンチャネル14aとトップゲート電極とを隔てるゲート絶縁膜となる膜である。

【0042】

次いで、絶縁膜42上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタンと膜厚200nmの金とを順次堆積し、Au/Ti構造の金属膜を形成する。

【0043】

次いで、リソグラフィ及びドライエッチングにより、この金属膜をパターニングし、ゲート電極44を形成する(図5(c))。ゲート電極44の形成方法は、特に限定されるものではなく、リフトオフ法等により形成してもよい。

【0044】

この後、必要に応じて、所定の素子、配線層、パッシベーション膜等を形成し、本実施形態による半導体装置を完成する。

【0045】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0046】

[第2実施形態]

第2実施形態による半導体装置及びその製造方法について図6乃至図9を用いて説明する。図1乃至図5に示す第1実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0047】

図6は、本実施形態による半導体装置の構造を示す平面図及び概略断面図である。図7乃至図9は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0048】

はじめに、本実施形態による半導体装置の構造について図6を用いて説明する。図6(a)は平面図であり、図6(b)は図6(a)のA−A′線断面図である。

【0049】

基板30上には、金属膜36が形成されている。金属膜36が形成された基板30上には、絶縁膜46が形成されている。絶縁膜46上には、グラフェンチャネル14aが形成されている。絶縁膜46上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0050】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜46を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0051】

本実施形態による半導体装置では、図1に示す第1実施形態による半導体装置とは異なり、金属膜36が所定のバックゲート電極の形状にパターニングされている。図6の例では、グラフェンチャネル14aのパターンを包含するようにバックゲート電極のパターンを形成しているが、バックゲート電極のパターンは、これに限定されるものではない。ゲート電極44と同様、グラフェンチャネル14aの一部の領域に重なるように、バックゲート電極のパターンを形成してもよい。

【0052】

次に、本実施形態による半導体装置の製造方法について図7乃至図9を用いて説明する。

【0053】

まず、図2(a)乃至図3(a)に示す第1実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18を形成する(図7(a))。

【0054】

次いで、リソグラフィ及びドライエッチングにより、金属膜18を、所定の形状(ここではバックゲート電極のパターン)にパターニングする(図7(b))。

【0055】

次いで、全面に、例えばALD法によりアルミナを堆積後、例えばCMP(化学的機械的研磨:Chemical Mechanical Polishing)法により、金属膜18が露出するまでこのアルミナを研磨する。これにより、金属膜18が形成されていない領域の絶縁膜16上に、アルミナよりなる絶縁膜20を形成する(図7(c))。

【0056】

次いで、例えば弗酸水溶液を用い、基板10表面のシリコン酸化膜をウェットエッチングし、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18/絶縁膜20の積層構造体22を、基板10から剥離する。

【0057】

また、図3(c)に示す第1実施形態による半導体装置の製造方法と同様にして、基板30上に、金属膜32を形成する(図8(a))。

【0058】

次いで、リソグラフィ及びドライエッチングにより、金属膜32を、所定の形状(ここではバックゲート電極のパターン)にパターニングする(図8(b))。

【0059】

次いで、全面に、例えばALD法によりアルミナを堆積後、例えばCMP法により、金属膜32が露出するまでこのアルミナを研磨する。これにより、金属膜32が形成されていない領域の基板30上に、アルミナよりなる絶縁膜34を形成する(図8(c))。

【0060】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように積層構造体22を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図9(a))。接合した金属膜18/32は、以後、金属膜36と表す。また、絶縁膜16,20,34は、以後、絶縁膜46と表す。

【0061】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図9(b))。

【0062】

次いで、図4(c)乃至図5(c)に示す第1実施形態による半導体装置の製造方法と同様にして、グラフェン14をパターニングしてグラフェンチャネル14aを形成し、ソース電極38、ドレイン電極40、ゲート絶縁膜42及びゲート電極44を形成する(図9(c))。

【0063】

なお、上記の例では、所定形状にパターニングされたバックゲート電極を、金属膜18と金属膜32とを接合した金属膜36により形成している。しかしながら、金属膜18と金属膜32との接合部分が電極部や配線部のみでは、基板の表面全体に対する接合面積の割合が不十分となり、確実に貼り合わせることが困難になることも考えられる。このような場合には、金属膜18及び金属膜32に、実デバイスに使用される電極パターンや配線パターンのほかに、貼り合わせ用のダミー電極パターンを設けるようにしてもよい。

【0064】

例えば図10に示すように、金属膜36により、バックゲート電極36Aと、トランジスタの周囲に配置された貼り合わせ用ダミー電極パターン36Bとを設けるようにしてもよい。

【0065】

或いは、例えば図11に示すように、金属膜36により、バックゲート電極36A、貼り合わせ用ダミー電極パターン36B、ソース電極38用のコンタクトパッド部36C、ドレイン電極40用のコンタクトパッド部36D等を設けるようにしてもよい。

【0066】

これにより、基板の表面全体に対する接合面積の割合を増加することができ、基板10上に積層構造体22を確実に貼り合わせることができる。

【0067】

貼り合わせ用ダミー電極パターン36Bを設ける場合、金属膜18,32により形成する電極パターンや配線パターンは、必ずしもこれらの積層体である金属膜36により形成する必要はない。例えば、図10,11の例では、バックゲート電極36Aの全体又は一部を、金属膜18又は金属膜32のみにより形成するようにしてもよい。例えば、グラフェンチャネル14a直下のバックゲート電極36Aの機能部を金属膜18のみにより形成し、これに接続されるコンタクトパッド部を金属膜36により形成することができる。

【0068】

金属膜36により形成する電極パターン、配線パターン、貼り合わせ用ダミー電極パターンは、上記配置に限定されるものではなく、必要に応じて適宜変更が可能である。また、電極パターンや配線パターンについては、前述の通り、金属膜36により形成してもよいし、金属膜18又は金属膜32のいずれかのみで形成してもよい。

【0069】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0070】

[第3実施形態]

第3実施形態による半導体装置及びその製造方法について図12乃至図16を用いて説明する。図1乃至図11に示す第1及び第2実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0071】

図12は、本実施形態による半導体装置の構造を示す平面図及び概略断面図である。図13乃至図16は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0072】

はじめに、本実施形態による半導体装置の構造について図10を用いて説明する。図12(a)は平面図であり、図12(b)は図12(a)のA−A′線断面図である。

【0073】

基板30上には、金属膜36が形成されている。金属膜36上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。金属膜36、絶縁膜16及びグラフェンチャネル16aは、同じ形状にパターニングされており、側壁部分には絶縁膜48が形成されている。基板30上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0074】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜16を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0075】

本実施形態による半導体装置では、図1に示す第1実施形態による半導体装置とは異なり、金属膜36がグラフェンチャネル14aと同じ形状のバックゲート電極の形状にパターニングされている。図12の例では、金属膜36により形成されたバックゲート電極の引き出し線を、金属膜32により形成している。

【0076】

次に、本実施形態による半導体装置の製造方法について図11乃至図14を用いて説明する。

【0077】

まず、図2(a)乃至図3(a)に示す第1実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14、絶縁膜16及び金属膜18を形成する(図13(a))。

【0078】

次いで、リソグラフィ及びドライエッチングにより、金属膜18、絶縁膜16、グラフェン14及び触媒金属膜12を、形成しようとするグラフェンチャネル14aの形状にパターニングする。このパターニングにより、グラフェン14よりなるグラフェンチャネル14aが形成される(図13(b))。なお、本パターニング工程では、必ずしも触媒金属膜12までパターニングする必要はない。少なくとも、金属膜18、絶縁膜16及びグラフェン14を所定形状にパターニングすればよい。

【0079】

本実施形態では、絶縁膜16及び金属膜18が覆われた状態でグラフェン14をパターニングするため、グラフェン14が直にレジスト膜が塗布されたり、グラフェン14がレジスト膜の除去雰囲気に曝されたりすることはない。したがって、第1及び第2実施形態の場合と比較して、グラフェン14に導入されるダメージを低減することができる。

【0080】

なお、貼り合わせ用ダミー電極パターンを配置して接合面積を増加する場合は、貼り合わせ用ダミー電極パターンの形成領域にも金属膜18、絶縁膜16、グラフェン14及び触媒金属膜12の積層構造体が残存するように、パターニングを行う。

【0081】

また、図3(c)に示す第1実施形態による半導体装置の製造方法と同様にして、基板30上に、金属膜32を形成する(図14(a))。

【0082】

次いで、リソグラフィ及びドライエッチングにより、金属膜32を、所定の形状にパターニングする(図8(b))。ここでは、金属膜32により、バックゲート電極のパターン32Aと、ソース電極38用のコンタクトパッド部のパターン32Bと、ドレイン電極40用のコンタクトパッド部のパターン32Cとを形成するものとする。貼り合わせ用ダミー電極パターンを配置して接合面積を増加する場合は、貼り合わせ用ダミー電極パターンの形成領域にも金属膜32が残存するように、パターニングを行う。

【0083】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように積層構造体22を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図15(a))。接合した部分の金属膜18/32は、以後、金属膜36と表す。

【0084】

この際、例えば基板10,30のオリエンテーションフラットを利用して位置合わせを行えば所望の箇所で圧着できるようにパターンを配置しておくことにより、基板10,30の位置合わせを容易に行うことができる。

【0085】

なお、本実施形態では、金属膜18,32の周囲が絶縁膜によって平坦化されていないため、接合する金属膜18のパターンと金属膜32のパターンとが異なっていると、金属膜18又は金属膜32のいずれか一方が形成されていない領域には空隙が形成される。かかる観点から、金属膜18のパターンと金属膜32のパターンとは、互いに鏡像のような関係であることが望ましい。

【0086】

次いで、例えば弗酸水溶液を用い、基板10表面のシリコン酸化膜をウェットエッチングし、基板10を触媒金属膜12上から剥離する(図15(b))。

【0087】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図15(c))。

【0088】

次いで、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に、選択的に絶縁膜48を形成する(図16(a))。例えば、全面に例えばALD法によりアルミナを堆積後、このアルミナをパターニングし、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に選択的に絶縁膜48を残存させる。或いは、全面に例えばALD法によりアルミナを堆積後、このアルミナをエッチバックし、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に選択的に絶縁膜48を残存させる。

【0089】

絶縁膜48は、金属膜36の側壁部分を覆いソース電極38及びドレイン電極40から金属膜36を分離するためのものである。絶縁膜48は、この目的を達成しうるものであれば、如何なる方法を用いて形成してもよい。

【0090】

絶縁膜48を形成する工程は、図15(b)の工程の後、図15(c)の工程の前に行ってもよい。この場合、絶縁膜48のエッチバックやパターニングの際にはグラフェンチャネル14aが触媒金属膜12により覆われているため、グラフェンチャネル14aに導入されるダメージを低減することができる。

【0091】

次いで、図5(a)に示す第1実施形態による半導体装置の製造方法と同様にして、グラフェンチャネル14aに接続されたソース電極38及びドレイン電極40を形成する(図16(b))

次いで、図5(b)乃至図5(c)に示す第1実施形態による半導体装置の製造方法と同様にして、ゲート絶縁膜42及びゲート電極44を形成する(図16(c))。

【0092】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0093】

[第4実施形態]

第4実施形態による半導体装置及びその製造方法について図17乃至図19を用いて説明する。図1乃至図16に示す第1乃至第3実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0094】

図17は、本実施形態による半導体装置の構造を示す概略断面図である。図18及び図19は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0095】

はじめに、本実施形態による半導体装置の構造について図17を用いて説明する。

【0096】

基板30上には、金属膜36が形成されている。金属膜36上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。金属膜36、絶縁膜16及びグラフェンチャネル16aは、同じ形状にパターニングされており、側壁部分には絶縁膜48が形成されている。基板30上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜50が形成されている。グラフェンチャネル14a上の絶縁膜50上には、ゲート電極44が形成されている。

【0097】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜16を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜50を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0098】

本実施形態による半導体装置では、絶縁膜50が、グラフェンチャネル14aを合成する際に用いた触媒金属材料の絶縁性化合物により形成されているほかは、図12に示す第3実施形態による半導体装置と基本的に同じである。

【0099】

次に、本実施形態による半導体装置の製造方法について図18及び図19を用いて説明する。図13(a)乃至図15(b)に示す第3実施形態による半導体装置の製造方法と同様にして、金属膜32が形成された基板30上に、金属膜18、絶縁膜16、グラフェンチャネル14a及び触媒金属膜12の積層構造体を転写する(図18(a))。

【0100】

次いで、例えばドライエッチングにより、触媒金属膜12を研磨或いはドライエッチングし、触媒金属膜12の膜厚が例えば20nm程度になるまで薄膜化する(図18(b))。

【0101】

次いで、薄膜化した触媒金属膜12を酸化し、触媒金属膜12を形成する触媒金属材料の酸化物よりなる絶縁膜50を形成する(図18(c))。例えば、圧力1Pa程度の酸素雰囲気中で200W程度のプラズマに触媒金属膜12を10分間曝すことにより、絶縁膜50を形成することができる。

【0102】

この際、露出している部分は耐酸化性の強い金や絶縁膜により形成されており、酸化による影響を受けることはほとんどない。グラフェンチャネル14aの側壁部分が反応することもあるが、影響は軽微である。

【0103】

触媒金属膜12を薄膜化する工程では、薄膜化した触媒金属膜12を酸化することにより得られる絶縁膜50の膜厚がゲート絶縁膜として所望の膜厚となるように、触媒金属膜12の残膜厚を適宜設定する。

【0104】

なお、絶縁膜50の形成は、触媒金属膜12の総てを酸化ないしは窒化して絶縁膜50を形成した後、絶縁膜50を所望の膜厚に薄膜化してもよい。ただし、触媒金属膜12を薄膜化してから酸化ないしは窒化して絶縁膜50を形成する方が、酸化雰囲気に曝されることによるダメージは軽減される。

【0105】

ゲート絶縁膜として適用可能な酸化物ないしは窒化物を形成する触媒金属材料としては、例えば、アルミニウム(Al)、ハフニウム(Hf)、ジルコニウム(Zr)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、シリコン(Si)、鉄(Fe)、銅(Cu)、コバルト(Co)又はこれらを少なくとも1種以上含む合金が挙げられる。

【0106】

次いで、金属膜36、絶縁膜16及びグラフェンチャネル14aの側壁部分に、図16(a)に示す第3実施形態による半導体装置の製造方法と同様にして、絶縁膜48を形成する(図19(a))。

【0107】

次いで、リソグラフィ及びエッチングにより、絶縁膜50をパターニングし、グラフェンチャネル14aの両端部を露出する(図19(b))。

【0108】

次いで、図16(b)乃至図16(c)に示す第3実施形態による半導体装置の製造方法と同様にして、ソース電極38、ドレイン電極40、ゲート絶縁膜42及びゲート電極44を形成する(図19(c))。

【0109】

本実施形態の方法では、一連の製造プロセスを通してグラフェンチャネル14aが基板表面に露出されず、グラフェンチャネル14aに物理的或いは化学的な処理が施されることはない。これにより、グラフェンチャネル14aに与えるダメージを最小限に抑えることができる。

【0110】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0111】

[第5実施形態]

第5実施形態による半導体装置及びその製造方法について図20乃至図22を用いて説明する。図1乃至図19に示す第1乃至第4実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0112】

図20は、本実施形態による半導体装置の構造を示す概略断面図である。図21及び図22は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0113】

はじめに、本実施形態による半導体装置の構造について図20を用いて説明する。

【0114】

基板30上には、絶縁膜16が形成されている。絶縁膜16上には、グラフェンチャネル14aが形成されている。絶縁膜16上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0115】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。

【0116】

次に、本実施形態による半導体装置の製造方法について図21及び図22を用いて説明する。

【0117】

まず、図2(a)乃至図2(c)に示す第1実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14及び絶縁膜16を形成する(図21(a))。なお、ここでは、絶縁膜16をシリコン酸化膜により形成するものとする。

【0118】

また、基板10とは別に、表面にシリコン酸化膜の絶縁膜が形成された基板30を用意する。

【0119】

次いで、基板30上に、適宜位置合わせを行いながら、基板30側に絶縁膜16が向き合うように基板10を重ね合わせる。

【0120】

次いで、基板30と基板10との間に圧力をかけながら、窒素雰囲気中で、例えば800℃〜1000℃程度の温度で1時間程度の熱処理を行う。これにより、基板30表面のシリコン酸化膜と絶縁膜16とが接合される(図21(b))。

【0121】

シリコン酸化膜同士を圧着する際の温度や時間は、圧着面積、基板の反り状況等に応じて変化するため、適宜設定することが望ましい。ここでは、圧着する絶縁膜としてシリコン酸化膜を用いているが、シリコン窒化膜やアルミナ等の絶縁物や酸化物であれば特に制限はない。

【0122】

本実施形態では、グラフェン14を触媒金属膜12と絶縁膜16との間に挟持した状態で基板30上に転写するため、転写の際にグラフェン14に皺や曲がりが生じることを防止できる。また、レジストなど、転写するための部材をグラフェン14に直に接触することはなく、レジスト残渣等によるグラフェン14へのダメージの導入も防止することができる。

【0123】

なお、第3実施形態と同様に、絶縁膜16、グラフェン14及び触媒金属膜12を所定形状にパターニングした後、基板10と基板30とを接合するようにしてもよい。

【0124】

次いで、例えば弗酸水溶液を用いて基板10表面のシリコン酸化膜をウェットエッチングし、基板10を除去する。

【0125】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図22(a))。なお、基板10を除去する工程を別途行わずに、触媒金属膜12をエッチングすることによって基板10を同時に除去するようにしてもよい。

【0126】

次いで、グラフェン14をパターニングし、グラフェンチャネル14aを形成する(図22(b))。

【0127】

次いで、図5(a)乃至図5(c)に示す第1実施形態による半導体装置の製造方法と同様にして、ソース電極38、ドレイン電極40、絶縁膜42及びゲート電極44を形成する(図22(c))。

【0128】

このように、本実施形態によれば、グラフェン上に絶縁膜が形成された状態で、絶縁膜が形成された別の基板上に、絶縁膜同士の圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0129】

[第6実施形態]

第6実施形態による半導体装置及びその製造方法について図23乃至図25を用いて説明する。図1乃至図22に示す第1乃至第5実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0130】

図23は、本実施形態による半導体装置の構造を示す概略断面図である。図24及び図25は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0131】

はじめに、本実施形態による半導体装置の構造について図23を用いて説明する。

【0132】

基板30上には、金属膜36が形成されている。金属膜36が形成された基板30上には、絶縁膜46が形成されている。絶縁膜46上には、グラフェンチャネル14aが形成されている。絶縁膜46上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極44が形成されている。

【0133】

このように、本実施形態による半導体装置は、グラフェンチャネル14aをチャネルとするグラフェントランジスタである。グラフェンチャネル14aの下方には、絶縁膜46を介して金属膜36が形成されている。また、グラフェンチャネル14aの上方には、絶縁膜42を介してゲート電極44が形成されている。これにより、金属膜36をバックゲート電極とし、ゲート電極44をトップゲート電極としたダブルゲートトランジスタとして動作することができる。絶縁膜16を厚膜化してグラフェンチャネル14aと金属膜36との間隔を広げれば、シングルゲートトランジスタとして動作することもできる。

【0134】

次に、本実施形態による半導体装置の製造方法について図24及び図25を用いて説明する。

【0135】

まず、図7(a)乃至図7(c)に示す第2実施形態による半導体装置の製造方法と同様にして、基板10上に、触媒金属膜12、グラフェン14、絶縁膜16、金属膜18及び絶縁膜20を形成する(図24(a))。

【0136】

また、基板30上に、表面部に金属膜32が埋め込まれた絶縁膜34を形成する(図24(b))。

【0137】

次いで、金属膜32が形成された基板30上に、適宜位置合わせを行いながら、金属膜32と金属膜18とが向き合うように、また、絶縁膜34と絶縁膜20とが向き合うように、基板10を重ね合わせる。

【0138】

次いで、基板30と基板10との間に単位面積(mm2)当たり0.1N〜1N程度の圧力をかけながら、窒素雰囲気中で、例えば200℃〜800℃程度の温度で1時間程度の熱処理を行う。これにより、金属膜32と金属膜18とが接合され、絶縁膜34と絶縁膜20とが接合される(図24(c))。接合した金属膜18/32は、以後、金属膜36と表す。また、絶縁膜16,20,34は、絶縁膜46と表す。

【0139】

次いで、例えば弗酸水溶液を用いて基板10表面のシリコン酸化膜をウェットエッチングし、基板10を除去する。

【0140】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜12を選択的に除去する(図25(a))。なお、基板10を除去する工程を別途行わずに、触媒金属膜12をエッチングすることによって基板10を同時に除去するようにしてもよい。

【0141】

次いで、グラフェン14をパターニングし、グラフェンチャネル14aを形成する(図25(b))。

【0142】

次いで、図9(c)に示す第2実施形態による半導体装置の製造方法と同様にして、ソース電極38、ドレイン電極40、絶縁膜42及びゲート電極44を形成する(図25(c))。

【0143】

このように、本実施形態によれば、グラフェン上に絶縁膜及び金属膜が形成された状態で、金属膜同士及び絶縁膜同士の圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0144】

[第7実施形態]

第7実施形態による半導体装置及びその製造方法について図26乃至図32を用いて説明する。図1乃至図25に示す第1乃至第6実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0145】

図26は、本実施形態による半導体装置の構造を示す概略断面図である。図27及び図32は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0146】

はじめに、本実施形態による半導体装置の構造について図26を用いて説明する。

【0147】

基板30上には、金属膜36が形成されている。金属膜36が形成された基板30上には、絶縁膜46が形成されている。絶縁膜46上には、グラフェンチャネル14aが形成されている。絶縁膜46上には、また、グラフェンチャネル14aの両端部にそれぞれ接続して、ソース電極38及びドレイン電極40が形成されている。グラフェンチャネル14a上には、絶縁膜42が形成されている。ソース電極38上及びドレイン電極40上には、触媒金属膜52が形成されている。グラフェンチャネル14a上の絶縁膜42上には、ゲート電極を兼ねる触媒金属膜52が形成されている。こうして、基板30上には、金属膜36をバックゲート電極とし、絶縁膜42上の触媒金属膜54をトップゲート電極としたダブルゲートトランジスタが形成されている。

【0148】

グラフェントランジスタが形成された基板30上には、層間絶縁膜56が形成されている。層間絶縁膜56には、ゲート電極(触媒金属膜52)、ソース電極38及びドレイン電極に電気的に接続されたカーボンナノチューブ束よりなるビア配線54が埋め込まれている。ビア配線54が埋め込まれ層間絶縁膜54上には、ビア配線54に接続して、金属膜68,70に挟持されたグラフェン配線64aが形成されている。

【0149】

グラフェン配線64aが形成された層間絶縁膜56上には、層間絶縁膜74が形成されている。層間絶縁膜74には、グラフェン配線64aに電気的に接続されたカーボンナノチューブ束よりなるビア配線72が埋め込まれている。ビア配線72が埋め込まれた層間絶縁膜74上には、ビア配線72に接続して、下面側に金属膜76が形成されたグラフェン配線78が形成されている。

【0150】

このように、本実施形態による半導体装置は、配線層をグラフェン配線54,74により形成したものである。配線層をグラフェンにより形成することにより、配線層を容易に低抵抗化することができる。グラフェン配線54,74は、後述するように、グラフェンチャネル14aと同様のプロセスを用いて形成することができる。

【0151】

また、本実施形態による半導体装置では、ビア配線をカーボンナノチューブ束により形成している。ビア配線をカーボンナノチューブ束により形成することにより、ビア配線を容易に低抵抗化することができる。なお、ビア配線は、必ずしもカーボンナノチューブ束により形成する必要はなく、通常のビア配線形成プロセスを適用することも可能である。

【0152】

次に、本実施形態による半導体装置の製造方法について図27乃至図32を用いて説明する。

【0153】

まず、図7(a)乃至図9(c)に示す第2実施形態による半導体装置の製造方法と同様にして、基板30上に、金属膜36、絶縁膜46、グラフェンチャネル14a、ソース電極38、ドレイン電極40及び絶縁膜42を形成する(図27(a))。

【0154】

なお、本実施形態では、下地のトランジスタ構造として第2実施形態の構造を適用した例を示すが、下地のトランジスタ構造は、これに限定されるものではない。第2実施形態の構造の代わりに、第1、第3乃至第6実施形態のいずれかの構造を適用してもよいし、他のトランジスタ構造を適用してもよい。また、図27(a)ではゲート電極44を形成していないが、図9(c)と同様にして、絶縁膜42上にゲート電極44を形成してもよい。

【0155】

次いで、リソグラフィ及びエッチングにより、絶縁膜42をパターニングし、ソース電極38及びドレイン電極40の表面を露出する(図27(b))。

【0156】

次いで、例えばリフトオフ法により、ソース電極38及びドレイン電極40上のコンタクト形成部、並びに、絶縁膜42上のゲート電極の形成部に、触媒金属膜52を形成する(図27(b))。絶縁膜42上の触媒金属膜52は、ゲート電極として用いることができる。絶縁膜42上にゲート電極44を形成している場合は、ゲート電極44上のコンタクト形成部に、触媒金属膜52を形成する。なお、触媒金属膜52の形成方法は、リフトオフ法に限定されるものではない。

【0157】

触媒金属膜52は、例えば、膜厚5nmのタンタル(Ta)膜と、膜厚5nmの窒化チタン(TiN)膜と、膜厚1nmのコバルト(Co)膜とを、スパッタ法により順次堆積することにより形成する。コバルトは触媒材料であり、窒化チタンは合成を促進するサポート材料であり、タンタルは下地の金属の拡散を防止する膜である。

【0158】

触媒材料としては、コバルトのほか、例えば、鉄(Fe)、ニッケル(Ni)、銅(Cu)、金(Au)、白金(Pt)、又はこれらのうちの少なくとも1種を含む合金や、これらの酸化物・窒化物等の化合物を適用することができる。

【0159】

サポート材料としては、窒化チタンのほか、例えば、アルミニウム(Al)、ハフニウム(Hf)、ジルコニウム(Zr)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、シリコン(Si)、チタンシリサイド(TiSix)、バナジウム(V)、ニオブ(Nb)、ルテニウム(Ru)又はこれらのうちの少なくとも1種を含む合金や、これらの酸化物・窒化物等の化合物を適用することができる。

【0160】

拡散防止膜としては、タンタルのほか、例えば、チタン(Ti)、ルテニウム(Ru)又はこれらのうちの少なくとも1種を含む合金や、これらの酸化物・窒化物等の化合物を適用することができる。

【0161】

次いで、例えば熱CVD法により、触媒金属膜52を触媒としてカーボンナノチューブを合成し、触媒金属膜52上にカーボンナノチューブの束よりなるビア配線54形成する(図28(a))。例えば、原料ガスにアセチレン・アルゴンの混合ガスを用い(アセチレンガスはアルゴンの0.1%以下)、圧力1kPa、基板温度450℃の条件で、長さ500nm程度のカーボンナノチューブを成長する。

【0162】

次いで、例えばCVD法により、例えばシリコン酸化膜を堆積し、シリコン酸化膜

の層間絶縁膜56を形成する(図28(b))。

【0163】

次いで、例えばCMP法により、層間絶縁膜56の表面を研磨し、層間絶縁膜56の表面にビア配線54の上端部を露出させる(図29(a))。

【0164】

次いで、層間絶縁膜56上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜58を形成する。

【0165】

次いで、リソグラフィ及びエッチングにより金属膜58をパターニングし、ビア配線54に接続された所定の配線パターンを形成する(図29(b))。

【0166】

また、基板10,30とは別に、基板60を用意する。基板60は、グラフェンを合成するための下地として用いるものであり、少なくとも表面に、グラフェン及びグラフェンの触媒材料(触媒金属膜62)に対して選択的にエッチングが可能な材料により形成されている基板であれば、特に限定されるものではない。例えば、表面に膜厚が300nmのシリコン酸化膜が形成されたシリコン基板を適用することができる。

【0167】

次いで、基板60上に、例えばスパッタ法により、例えば膜厚500nmの鉄(Fe)を堆積し、鉄よりなる触媒金属膜62を形成する。

【0168】

次いで、グラフェン14の合成と同様にして、触媒金属膜62を触媒としてグラフェン64を合成する。このグラフェン64は、配線として用いるものであり、層数は配線抵抗の要求等に応じて適宜増減することができる。

【0169】

次いで、グラフェン64上に、例えば電子ビーム蒸着法により、例えば膜厚10nmのチタン(Ti)と膜厚200nmの金(Au)とを順次堆積し、Au/Ti構造の金属膜66を形成する(図30(a))。

【0170】

次いで、リソグラフィ及びエッチングにより、金属膜66、グラフェン64及び触媒金属膜62を、金属膜58の配線パターンに対応した所定の形状にパターニングする(図30(b))。このパターニングにより、グラフェン64よりなるグラフェン配線64aを形成する。なお、本パターニング工程では、必ずしも触媒金属膜62までパターニングする必要はない。少なくとも、金属膜66及びグラフェン64を所定形状にパターニングすればよい。

【0171】

次いで、金属膜58が形成された絶縁膜56上に、適宜位置合わせを行いながら、金属膜58と金属膜66とが向き合うように基板60を重ね合わせ、金熱圧着法により金属膜32と金属膜18とを接合する(図31(a))。接合した金属膜66/58は、以後、金属膜68と表す。

【0172】

次いで、例えば弗酸水溶液を用いて基板60表面のシリコン酸化膜をウェットエッチングし、基板60を除去する。

【0173】

次いで、例えば塩酸や塩化鉄溶液等を用いたウェットエッチングにより、触媒金属膜62を選択的に除去する(図31(b))。

【0174】

こうして、グラフェントランジスタのゲート電極(触媒金属膜52)、ソース電極38及びドレイン電極40に、カーボンナノチューブ束のビア配線54を介して電気的に接続されたグラフェン配線64aを形成する。

【0175】

なお、図29(b)の工程の後、触媒金属膜を堆積し、これを触媒としてグラフェン配線を直に形成することも考えられる。本実施形態のメリットとしては、グラフェン配線の下地となる金属膜が触媒金属材料に限定されない点が挙げられる。

【0176】

次いで、必要に応じて、グラフェン配線64a上に、図27(c)乃至図31(b)の工程と同様にして、触媒金属膜70、ビア配線72、層間絶縁膜74、金属膜76及びグラフェン配線78を繰り返し形成し、多層配線構造を形成する(図32)。

【0177】

このように、本実施形態によれば、グラフェン上に金属膜が形成された状態で、金属膜が形成された別の基板上に、金属膜同士の熱圧着を用いてグラフェンを転写するので、転写の際にグラフェンに皺や曲がりが生じるのを防止することができる。また、レジストなど、転写するための部材をグラフェンに直に接触することはなく、レジスト残渣等によるグラフェンへのダメージの導入も防止することができる。

【0178】

[変形実施形態]

上記実施形態に限らず種々の変形が可能である。

【0179】

例えば、上記実施形態では、熱CVD法によりグラフェンを合成する方法を示したが、熱CVD法に限らず、リモートプラズマCVD法、プラズマCVD法等を用いてもよい。また、原料ガスとしては、アセチレンに限らず、エチレンガス、メタンガスなどの炭化水素ガス、エタノールなどのアルコール、ベンゼン等を用いてもよい。

【0180】

また、グラフェンの合成に用いる触媒も、鉄に限定されるものではなく、グラフェン合成の触媒として機能する他の材料を用いてもよい。例えば、Co(コバルト)、Ni(ニッケル)、Cu(銅)、Pt(プラチナ)、Au(金)等の金属、これらを少なくとも一種含む合金、炭化物、酸化物、窒化物等を用いてもよい。

【0181】

触媒金属膜12の成膜方法についても特に限定されるものではなく、スパッタ法に限らず、電子ビーム蒸着法、分子線エピタキシー法等を用いてもよい。

【0182】

グラフェンの他の合成方法としては、例えば、スパッタ法により熱酸化膜付きのシリコン基板上に堆積した膜厚500nmの銅薄膜を触媒として、熱CVD法によりグラフェンを合成する方法が挙げられる。この場合は、例えば、原料ガスとしてメタンを用い、ガスの分圧を、希釈用アルゴンガス900sccmに対して、水素100sccm、メタン10sccmとし、温度900℃でグラフェンを合成することができる。

【0183】

また、上記第7実施形態では、熱CVD法によりカーボンナノチューブを合成する方法を示したが、熱CVD法に限らず、リモートプラズマCVD法、プラズマCVD法等を用いてもよい。また、原料ガスとしては、アセチレンに限らず、エチレンガス、メタンガスなどの炭化水素ガス、エタノールなどのアルコール、ベンゼン等を用いてもよい。

【0184】

また、上記第1、第2、第3、第4、第6及び第7実施形態では、ダブルゲート構造のトランジスタを示し、上記第5実施形態では、トップゲート構造のトランジスタを示したが、トランジスタ構造は、これに限定されるものではない。

【0185】

例えば、上記第1、第2、第3、第4、第6及び第7実施形態では、必ずしもゲート電極44を必要はなく、バックゲート電極のみを有するバックゲート構造のトランジスタとしてもよい。或いは、上記第2及び第6実施形態では、必ずしもバックゲート電極を形成する必要はなく、ゲート電極44のみを有するトップゲート構造のトランジスタとしてもよい。或いは、金属膜36とグラフェンチャネル14aとを隔てる絶縁膜16,46の膜厚を厚膜化し、金属膜36が実質的にバックゲート電極として機能しないようにしてもよい。或いは、第1乃至第6実施形態に記載のグラフェンチャネル14aをグラフェン配線としてもよい。

【0186】

また、各実施形態に記載した構造や製造方法は、任意に組み合わせることができる。例えば、触媒金属膜12を酸化してゲート絶縁膜を形成する第4実施形態のプロセスを、第1、第2、第3、第5又は第6実施形態に適用してもよい。また、第7実施形態の配線構造を、第1乃至第6実施形態に適用してもよい。

【0187】

また、上記実施形態に記載した半導体装置の構造、構造パラメータ、構成材料、製造条件等は、一例を示したものにすぎず、当業者の技術常識等に応じて適宜修正や変更が可能である。

【0188】

また、上記実施形態では、グラフェンチャネルトランジスタやグラフェン配線に適用した例を示したが、これらに限定されるものではなく、グラフェンを有する種々のデバイスや構造体に適用することができる。

【符号の説明】

【0189】

10,30,60…基板

12,52,62,70…触媒金属膜

14,64…グラフェン

14a…グラフェンチャネル

16,20,34,42,46,48,50…絶縁膜

18,32,36,58,66,68,76…金属膜

22…積層構造体

38…ソース電極

40…ドレイン電極

44…ゲート電極

54,72…ビア配線

56,74…層間絶縁膜

64a,78…グラフェン配線

【特許請求の範囲】

【請求項1】

第1の基板上に、第1の触媒金属膜を形成する工程と、

前記第1の触媒金属膜上に、前記第1の触媒金属膜を触媒として、第1のグラフェンを形成する工程と、

前記第1のグラフェン上に、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上に、第1の金属膜を形成する工程と、

第2の基板上に、第2の金属膜を形成する工程と、

前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、

前記第1の基板を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項2】

請求項1記載の半導体装置の製造方法において、

前記第1の基板を除去する工程の後、前記第1の触媒金属膜を除去する工程と、前記第1のグラフェンをパターニングし、前記第1のグラフェンよりなるグラフェンチャネルを形成する工程とを更に有する

ことを特徴とする半導体装置の製造方法。

【請求項3】

請求項1記載の半導体装置の製造方法において、

前記第1の金属膜を形成する工程の後、前記第1の金属膜、前記第1の絶縁膜及び前記第1のグラフェンをパターニングし、前記第1のグラフェンよりなるグラフェンチャネルを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項4】

請求項3記載の半導体装置の製造方法において、

前記グラフェンチャネルを形成する工程の後、前記第1の触媒金属膜を除去する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項5】

請求項3記載の半導体装置の製造方法において、

前記第1の基板を除去する工程の後、前記第1の触媒金属膜を酸化して第3の絶縁膜を形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項6】

請求項2乃至5のいずれか1項に記載の半導体装置の製造方法において、

前記グラフェンチャネルを形成する工程の後、前記グラフェンチャネルに接続されたソース電極及びドレイン電極を形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項7】

請求項6記載の半導体装置の製造方法において、

前記ソース電極上及び前記ドレイン電極上に、第2の触媒金属膜を形成する工程と、

前記第2の触媒金属上に、前記第2の触媒金属膜を触媒としてカーボンナノチューブを成長し、カーボンナノチューブ束のビア配線を形成する工程と

を更に有することを特徴とする半導体装置の製造方法。

【請求項8】

請求項6記載の半導体装置の製造方法において、

第3の基板上に、第3の触媒金属膜を形成する工程と、

前記第3の触媒金属膜上に、前記第3の触媒金属膜を触媒として、第2のグラフェンを形成する工程と、

前記第2のグラフェン上に、第3の金属膜を形成する工程と、

前記第3の金属膜及び前記第2のグラフェンをパターニングし、前記第2のグラフェンよりなるグラフェン配線を形成する工程と、

前記ビア配線上に、第4の金属膜を形成する工程と、

前記第3の金属膜の表面と前記第4の金属膜の表面とを対向させ、前記第3の金属膜と前記第4の金属膜とを接合する工程と、

前記第3の基板を除去する工程と、

前記第2の触媒金属膜を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項9】

請求項1乃至8のいずれか1項に記載の半導体装置の製造方法において、

前記第1の金属膜を形成する工程では、前記第1の絶縁膜の表面部に埋め込まれた前記第1の金属膜を形成し、

前記第2の金属膜を形成する工程では、前記第2の絶縁膜の表面部に埋め込まれた前記第2の金属膜を形成し、

前記第1の金属膜と前記第2の金属膜とを接合する工程では、前記第1の金属膜と前記第2の金属膜とを接合するとともに、前記第1の絶縁膜と前記第2の絶縁膜とを接合する

ことを特徴とする半導体装置の製造方法。

【請求項10】

請求項1乃至9のいずれか1項に記載の半導体装置の製造方法において、

前記第1の金属膜と前記第2の金属膜は、熱圧着により接合する

ことを特徴とする半導体装置の製造方法。

【請求項11】

第1の基板上に、触媒金属膜を形成する工程と、

前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、

前記グラフェン上に、第1の金属膜を形成する工程と、

前記第1の金属膜及び前記グラフェンをパターニングし、前記グラフェンよりなるグラフェン配線を形成する工程と、

第2の基板上に、第2の金属膜を形成する工程と、

前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、

前記第1の基板を除去する工程と、

前記触媒金属膜を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項12】

第1の基板上に、触媒金属膜を形成する工程と、

前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、

前記グラフェン上に、第1の絶縁膜を形成する工程と、

第2の基板上に第2の絶縁膜を形成する工程と、

前記第1の絶縁膜の表面と前記第2の絶縁膜の表面とを対向させ、前記第1の絶縁膜と前記第2の絶縁膜とを接合する工程と、

前記第1の基板を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項13】

請求項12記載の半導体装置の製造方法において、

前記第1の絶縁膜を形成する工程の後、前記第1の絶縁膜及び前記グラフェンをパターニングする工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項1】

第1の基板上に、第1の触媒金属膜を形成する工程と、

前記第1の触媒金属膜上に、前記第1の触媒金属膜を触媒として、第1のグラフェンを形成する工程と、

前記第1のグラフェン上に、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上に、第1の金属膜を形成する工程と、

第2の基板上に、第2の金属膜を形成する工程と、

前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、

前記第1の基板を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項2】

請求項1記載の半導体装置の製造方法において、

前記第1の基板を除去する工程の後、前記第1の触媒金属膜を除去する工程と、前記第1のグラフェンをパターニングし、前記第1のグラフェンよりなるグラフェンチャネルを形成する工程とを更に有する

ことを特徴とする半導体装置の製造方法。

【請求項3】

請求項1記載の半導体装置の製造方法において、

前記第1の金属膜を形成する工程の後、前記第1の金属膜、前記第1の絶縁膜及び前記第1のグラフェンをパターニングし、前記第1のグラフェンよりなるグラフェンチャネルを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項4】

請求項3記載の半導体装置の製造方法において、

前記グラフェンチャネルを形成する工程の後、前記第1の触媒金属膜を除去する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項5】

請求項3記載の半導体装置の製造方法において、

前記第1の基板を除去する工程の後、前記第1の触媒金属膜を酸化して第3の絶縁膜を形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項6】

請求項2乃至5のいずれか1項に記載の半導体装置の製造方法において、

前記グラフェンチャネルを形成する工程の後、前記グラフェンチャネルに接続されたソース電極及びドレイン電極を形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項7】

請求項6記載の半導体装置の製造方法において、

前記ソース電極上及び前記ドレイン電極上に、第2の触媒金属膜を形成する工程と、

前記第2の触媒金属上に、前記第2の触媒金属膜を触媒としてカーボンナノチューブを成長し、カーボンナノチューブ束のビア配線を形成する工程と

を更に有することを特徴とする半導体装置の製造方法。

【請求項8】

請求項6記載の半導体装置の製造方法において、

第3の基板上に、第3の触媒金属膜を形成する工程と、

前記第3の触媒金属膜上に、前記第3の触媒金属膜を触媒として、第2のグラフェンを形成する工程と、

前記第2のグラフェン上に、第3の金属膜を形成する工程と、

前記第3の金属膜及び前記第2のグラフェンをパターニングし、前記第2のグラフェンよりなるグラフェン配線を形成する工程と、

前記ビア配線上に、第4の金属膜を形成する工程と、

前記第3の金属膜の表面と前記第4の金属膜の表面とを対向させ、前記第3の金属膜と前記第4の金属膜とを接合する工程と、

前記第3の基板を除去する工程と、

前記第2の触媒金属膜を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項9】

請求項1乃至8のいずれか1項に記載の半導体装置の製造方法において、

前記第1の金属膜を形成する工程では、前記第1の絶縁膜の表面部に埋め込まれた前記第1の金属膜を形成し、

前記第2の金属膜を形成する工程では、前記第2の絶縁膜の表面部に埋め込まれた前記第2の金属膜を形成し、

前記第1の金属膜と前記第2の金属膜とを接合する工程では、前記第1の金属膜と前記第2の金属膜とを接合するとともに、前記第1の絶縁膜と前記第2の絶縁膜とを接合する

ことを特徴とする半導体装置の製造方法。

【請求項10】

請求項1乃至9のいずれか1項に記載の半導体装置の製造方法において、

前記第1の金属膜と前記第2の金属膜は、熱圧着により接合する

ことを特徴とする半導体装置の製造方法。

【請求項11】

第1の基板上に、触媒金属膜を形成する工程と、

前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、

前記グラフェン上に、第1の金属膜を形成する工程と、

前記第1の金属膜及び前記グラフェンをパターニングし、前記グラフェンよりなるグラフェン配線を形成する工程と、

第2の基板上に、第2の金属膜を形成する工程と、

前記第1の金属膜の表面と前記第2の金属膜の表面とを対向させ、前記第1の金属膜と前記第2の金属膜とを接合する工程と、

前記第1の基板を除去する工程と、

前記触媒金属膜を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項12】

第1の基板上に、触媒金属膜を形成する工程と、

前記触媒金属膜上に、前記触媒金属膜を触媒として、グラフェンを形成する工程と、

前記グラフェン上に、第1の絶縁膜を形成する工程と、

第2の基板上に第2の絶縁膜を形成する工程と、

前記第1の絶縁膜の表面と前記第2の絶縁膜の表面とを対向させ、前記第1の絶縁膜と前記第2の絶縁膜とを接合する工程と、

前記第1の基板を除去する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項13】

請求項12記載の半導体装置の製造方法において、

前記第1の絶縁膜を形成する工程の後、前記第1の絶縁膜及び前記グラフェンをパターニングする工程を更に有する

ことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【公開番号】特開2013−110246(P2013−110246A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253635(P2011−253635)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

[ Back to top ]