半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の分野において、半導体装置の微細化及び高速化が要求されている。微細化及び高速化を実現している半導体装置として、例えば、特許文献1に記載のものが挙げられる。

【0003】

特許文献1に記載の半導体装置は、同一基板上に論理回路及び記憶回路が混載された混載回路を有する。論理回路を構成する多層配線層の同層に、記憶回路を構成する容量素子が埋設されている。容量素子の上には、上層配線層が形成されている。上層配線層の配線(第5層配線55)が、ワード線裏打ち配線として利用されている(特許文献1の段落0123)。ワード線裏打ち配線は、ワード線の抵抗を低減するものである。

【0004】

また、特許文献2には、容量素子の上層にビット線が配置されている半導体装置が記載されている。ビット線は、コンタクトを介して、トランジスタの拡散層と電気的に接続する。コンタクトは、容量素子同士の間に隣接して配置されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−54920号公報

【特許文献2】特開2009−105149号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に記載の半導体装置の製造方法は、容量素子の上層の配線層をワード線裏打ち配線に利用するものである。このため、容量素子の上層の配線層の設計自由度は、上層配線をワード線裏打ち配線とするという前提条件が必須となるために、低下していた。

【課題を解決するための手段】

【0007】

本発明によれば、

基板と、

前記基板上に設けられた層間絶縁層と、

前記基板に設けられており、前記層間絶縁層内に埋め込まれた第1トランジスタと、

前記層間絶縁層上に設けられた多層配線層と、

前記多層配線層内に設けられた容量素子と、

前記第1トランジスタを構成するゲート電極及び拡散層と、

前記ゲート電極の上面と接しており、前記ゲート電極と同一方向に延在しており、かつ前記層間絶縁層内に埋設された金属配線と、

前記第1トランジスタの拡散層に接続しており、前記層間絶縁層内に埋設された第1コンタクトと、を備え、

前記金属配線は、前記第1コンタクトと同じ材料で構成されている、

半導体装置が提供される。

【0008】

金属配線は、ゲート電極の抵抗を低減するものである。金属配線は、容量素子の下層の層間絶縁層にされる。このため、容量素子の上層の配線層の設計は、金属配線の利用に限定されないので、自由度が高まるものである。

【0009】

また、本発明によれば、

基板に、ゲート電極及び第1拡散層を備える第1トランジスタを形成する工程と、

前記第1トランジスタ上に層間絶縁層を形成する工程と、

前記ゲート電極上の前記層間絶縁層に、前記ゲート電極と同一方向に延在する配線溝を形成するとともに、前記第1拡散層上の前記層間絶縁層に、コンタクトを埋設するための第1コンタクト孔を形成する工程と、

前記配線溝及び第1コンタクト孔に同じ金属層を埋設する工程と、

前記第1層間絶縁層上に絶縁層を形成する工程と、

前記絶縁層内に、容量素子を埋設する工程と、を有する、

半導体装置の製造方法が提供される。

【発明の効果】

【0010】

本発明によれば、容量素子上の配線層の設計自由度に優れた半導体装置が提供される。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態における半導体装置を模式的に示す上面図である。

【図2】第1の実施の形態の記憶素子の周辺を模式的に示す上面図である。

【図3】図2のA−A´線断面図である。

【図4】図2のB−B´線断面図である。

【図5】図2のC−C´線断面図である。

【図6】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図7】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図8】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図9】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図10】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図11】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図12】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図13】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図14】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図15】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図16】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図17】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図18】第2の実施の形態における半導体装置を模式的に示す断面図である。

【図19】第3の実施の形態における半導体装置を模式的に示す断面図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0013】

(第1の実施の形態)

第1の実施の形態の半導体装置について説明する。

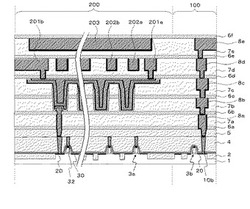

図1及び図2は、第1の実施の形態における半導体装置を模式的に示す上面図である。図3〜図5は、図2に示されたA−A´線断面図、B−B´線断面図、及びC−C´線断面図である。

【0014】

本実施の形態の半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板(半導体基板1)上には、層間絶縁層(コンタクト層間絶縁膜4、5)が設けられている。第1トランジスタ(能動素子3a)は、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極(ゲート電極32)及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線内に設けられている。金属配線(ゲート裏打ち配線30)は、ゲート電極32の上面と接しており、ゲート電極32と同一方向に延在しており、かつ層間絶縁層(コンタクト層間絶縁膜4)内に埋設されている。第1コンタクト(セルコンタクト10a)は、第1トランジスタ(能動素子3a)の拡散層(図示せず)に接続しており、層間絶縁層(コンタクト層間絶縁膜4)内に埋設される。

本実施の形態において、金属配線(ゲート裏打ち配線30)は、第1コンタクト(セルコンタクト10a)と同じ材料で構成されている。

【0015】

本実施の形態のゲート裏打ち配線30は、容量素子19の上層の配線層ではなく、容量素子19の下層に形成される。このため、容量素子19の上層の配線層の設計は、ゲート裏打ち配線30の利用に限定されないので、自由度が高まる。また、ゲート裏打ち配線30を形成することにより、ワード線(ゲート電極32)の抵抗を低下させることが可能となる。

【0016】

以下、本実施の形態の各構成について詳述する。

【0017】

本実施の形態の半導体装置は、混載DRAM(Dynamic Random Access Memory)、または、汎用DRAMのいずれにも適用できる。図1は、混載DRAMの半導体装置を示す。この半導体装置は、記憶回路と論理回路とを同一基板上に備える。すなわち、図1に示すように、半導体基板110上に、容量素子210を含む記憶回路200と半導体素子が形成される論理回路100とが混載されている。論理回路100は、記憶回路200中の容量素子210の周辺回路220ではなく、記憶回路200とは異なる領域に形成されたものである。たとえば、論理回路領域は、CPU(Central Processing Unit)等の高速ロジック回路が形成された領域である。なお、汎用DRAMは、記憶回路を有し、論理回路を有さないものである。

【0018】

図2は、記憶回路200のレイアウトの一例を示す。

記憶回路200は、容量素子19、ゲート電極32、ビット線34を含む。容量素子19は、六角形の拡散層上に2つ形成される。容量素子19は、容量コンタクト13(容量素子接続コンタクト)を介して拡散層に接続される。ゲート電極32は、複数の拡散層に亘って形成される。ビット線34は、ゲート裏打ち配線30とは略直交する方向に形成される。ビット線34は、セルコンタクト10c(ビット線接続コンタクト)を介して拡散層に接続される。

【0019】

図2において、A−A´線は、容量素子19を横断しビット線34を横断しない線である。B−B´線は、ビット線34を横断する線である。C−C´線は、ゲート電極32を横断し、ビット線34を横断しない線である。

【0020】

半導体基板1の表面には、素子分離膜2が形成されている。素子分離膜2は、記憶回路領域と論理回路領域とを区画する。記憶回路領域には記憶回路200が形成される。論理回路領域には、論理回路100が形成される。記憶回路200は、能動素子3aを有する。論理回路100は、能動素子3bを有する。能動素子3a、3bは、たとえば、トランジスタである。素子分離膜2は、たとえば、シリコン酸化膜で構成される。

【0021】

半導体基板1上にはコンタクト層間絶縁膜4が形成されている。コンタクト層間絶縁膜4には、能動素子3a、3b、ゲート裏打ち配線30、セルコンタクト10a、10b、10c、ビットコンタクト36が埋設されている。

【0022】

トランジスタ(能動素子3a、3b)は、基板の表層に形成された拡散層(ソースドレイン領域)、基板上に設けられたゲート絶縁膜、ゲート電極32を有する。ゲート電極32は、特に限定されないが、ポリシリコン電極、金属電極のいずれでもよい。ポリシリコン電極上には、たとえば、TiNなどの金属層が形成されていてもよい。また、ゲート電極は、一般にメタルゲートと呼称される、例えば、ニッケル、プラチナ、コバルト、ジルコニウム、タングステン、チタン、ハフニウム、タンタル、アルミ、ルテニウム、パラジウム、などの金属材料を含む材料により形成されていても良い。このように、金属電極及び金属層は、複数種の金属膜が積層されていてもよいが、単層の金属層で構成されていてもよい。本実施の形態では、拡散層の表層にシリサイド層20が形成されていてもよい。

【0023】

記憶回路領域に位置するゲート電極32上には、ゲート裏打ち配線30が形成されている。ゲート裏打ち配線30は、ゲート電極32とは異なる部材で構成されており、ゲート電極32と同じ層間絶縁層(コンタクト層間絶縁膜4)内に埋設されている。ゲート裏打ち配線30は、少なくとも同一トランジスタのソース・ドレイン拡散層に跨って形成されていることが好ましい。ゲート裏打ち配線30の下面の全面又は一部がゲート電極32の上面に接していてもよい。ゲート裏打ち配線30の上面は、コンタクト層間絶縁膜4の上面と同一面を構成してもよい。

【0024】

本実施の形態において、同一面とは、下記の測定方法で測定したとき、表面の平均高さに対する凹凸の高さのバラツキの最大値が好ましくは30nm以下であり、より好ましくは20nm以下であり、更に好ましくは10nm以下である平面をいう。こうした測定方法としては、例えば、SEM(Scanning Electron Microscope)やTEM(Transmission Electron Microscope)を用いて上部接続配線18の上面および配線8bの上面を含む断面画像を取得し、この断面画像から段差の高さのバラツキを測定する方法や、半導体装置の製造工程における検査工程に広く用いられている段差計により、平面方向の高さのプロファイルを測定する方法、等が挙げられる。

【0025】

ゲート裏打ち配線30は、能動素子3aの拡散層に接続するセルコンタクト10aと同じ材料で構成されていることが好ましい。ゲート裏打ち配線30は、たとえば、W、Cu、Alなどのいずれかを含む金属材料で構成されていることが好ましく、Wを主成分として含む、又はWからなる金属材料で構成されることが好ましい。本実施の形態において、同じ材料とは、同じ成分組成である、又は、主要な成分が同じであることを意味する。また、本実施の形態において、主成分として含むとは、たとえば、90質量%以上含むことを意味する。

【0026】

ゲート裏打ち配線30がセルコンタクト10aと同じ材料で構成されるので、ゲート裏打ち配線30とセルコンタクト10aとは同一工程で構成されることになる。このため、製造プロセスの簡略化を図ることが可能となる。また、ゲート裏打ち配線30がWを含む金属材料で構成されているので、ゲート裏打ち配線30の金属成分が層間絶縁膜内に拡散することを抑制することができる。

【0027】

また、ゲート裏打ち配線30は、能動素子3bの拡散層に接続するセルコンタクト10bと同じ材料で構成されていてもよい。能動素子3b(第2トランジスタ)は、半導体基板1に設けられており、第1トランジスタ(能動素子3a)を含む記憶回路領域とは異なる領域である論理回路領域に位置する。能動素子3aと第1配線とを第2コンタクト(セルコンタクト10b)が接続する。第1配線は、論理回路領域に位置する多層配線層のうち、最下層の配線層に位置する。本実施の形態では、ゲート裏打ち配線30は、記憶回路200領域のセルコンタクト10aと、論理回路100領域のセルコンタクト10bと同一層に形成されている。また、ゲート裏打ち配線30は、セルコンタクト10a、及びセルコンタクト10bと同一材料で構成される。

【0028】

また、ビットコンタクト36は、素子分離膜2で離間される2つの拡散層に跨って形成されてもよい。ビットコンタクト36は、素子搭載面に沿って一方向に延在していてもよい。

【0029】

コンタクト層間絶縁膜4上には、コンタクト層間絶縁膜5、キャップ膜6a、層間絶縁膜7aが形成される。これらの層に、配線8a、ビット線34、配線35及び容量コンタクト13aが埋設される。すなわち、最下層配線の配線8aと同一層に、ビット線34及び容量コンタクト13aが形成される。ビット線34及び容量コンタクト13aは、記憶回路200領域に位置する。配線8aは、論理回路100領域に位置する。なお、本実施の形態では、配線8a、ビット線34及び容量コンタクト13aの側面及び底面に沿ってバリアメタル膜で構成され、その内部に金属膜が埋設されている。

【0030】

また、コンタクト層間絶縁膜4、5のうち少なくとも1層は、シリコン酸化膜を用いてもよいが、シリコン酸化膜よりも低い比誘電率を有する絶縁膜であることが、より好ましい。こうした絶縁膜としては、例えば、シリコン酸化膜の酸素原子を弗素や炭素原子、及び炭化水素基に置換した、一般に低誘電率膜と呼称される絶縁膜か、あるいは、少なくともシリコン、酸素及び炭素を有し、更に絶縁膜中に直径数ナノメートル以下の微細な空孔を有する、いわゆる多孔質膜を用いても良い。これら絶縁膜の比誘電率としては、膜中に微細空孔を有さない絶縁膜の場合には、3.1以下であることが好ましく、更に好ましくは、膜中に微細空孔を有する絶縁膜の場合には、2.6以下であることが好ましい。かかる構造により、前記コンタクトの寄生容量を低減することができ、結果として、記憶回路及び論理回路の遅延を低減し、半導体素子の動作速度を向上させることができる。

【0031】

ビット線34は、セルコンタクト10c又はビットコンタクト36を介して、能動素子3aの拡散層に接続する。ビット線34の上面は、配線8aの上面と同一面を構成してもよい。また、ビット線34は、配線8aとは同一材料で構成されていることが好ましい。ビット線34は、たとえば、W、Cu、Alなどのいずれかを含む金属膜で構成されていることが好ましく、Cuを主成分として含む、又はCuからなる金属膜で構成されることが好ましい。

【0032】

ビット線34が配線8aと同一工程で構成されることにより、製造プロセスの簡略化を図ることが可能となる。また、ビット線34及び配線8aを、Cuを含む金属膜で構成することにより、Wを使用した場合よりも、半導体装置の動作速度を向上させることができる。

【0033】

また、本実施の形態において、ビット線34を最下層配線(配線8a)と同一層に形成できる。このため、論理回路100領域の配線8aとセルコンタクト10bとの間に、コンタクト層を形成することが不要となる。論理回路100領域の層間方向において、コンタクト層が不要となる分、寄生抵抗が小さくなり、半導体装置の動作速度を高めることができる。したがって、本実施の形態の混載DRAMは、ピュアロジック品と同一のデバイスパラメータを用いて設計され得る。

【0034】

また、記憶回路200領域の容量素子19の下層に、論理回路100の配線を利用して、ビット線34を形成することができる。すなわち、ビット線34は、配線8aと同じ材料で構成されるか、又は、ビット線34の上面と最下層配線(配線8a)の上面とを同一面に構成することができる。このため、配線8aを平坦化して形成するときに、記憶回路領域の層間絶縁膜7aの平坦性が向上する。したがって、記憶回路領域の層間絶縁膜7a上に位置する容量素子19の高さのバラツキを抑制できるので、容量のバラツキを低減することが可能となる。

【0035】

なお、容量コンタクト13bは、ビット線34及び配線8aと同一材料で構成されていることが好ましい。

【0036】

また、ゲート裏打ち配線30には、セルアレイの外側に位置するワード線ドライバから信号が入力される。図2は、セルアレイ端の拡大図を示す。たとえば、図5に示すように、ゲート裏打ち配線30は、論理回路100に位置する能動素子3bと配線35を介して電気的に接続される。配線35は、ゲート裏打ち配線30およびセルコンタクト10bとは、ビアを介して接続する。配線35は、配線8aと同一工程で形成されることが好ましい。つまり、配線35は、配線8aと同一部材で構成され得る。

【0037】

ビット線34の上面上には、キャップ膜6bが形成される。キャップ膜6bは、金属拡散防止膜を有してもよい。これにより、ビット線34がCuを含む金属材料で構成される場合であっても、キャップ膜6bは、層間絶縁層内へのCuの拡散を防止することができる。

【0038】

キャップ膜6b上に、層間絶縁膜7b、キャップ膜6c、層間絶縁膜7c、キャップ膜6dが形成される。これらの層には、容量素子19、容量コンタクト13、配線8b、8cが形成される。

【0039】

容量素子19は、下部電極14、容量絶縁膜15、上部電極16を含む。容量素子19は、多層配線層内に形成された凹部(以下、容量素子埋設用凹部という)に埋め込まれている。本実施の形態では、容量素子19は、2層の層間絶縁膜に亘って形成されているが、この態様に限定されず、3層以上に亘って形成されてもよい。

【0040】

下部電極14および上部電極16は、容量絶縁膜15を挟み込んで平行平板容量素子とするための電極として機能する。下部電極14および上部電極16の材料としては、例えば、チタン、タンタル等の高融点金属や、或いはそれらの窒化物等により形成することがより好ましく、容量絶縁膜15の結晶性を向上させることができる材料を用いることが好ましい。

【0041】

容量絶縁膜15の材料としては、例えば、二酸化ジルコニウム(ZrO2)、ジルコニウムアルミネート(ZrAlOx)、更には、前記二酸化ジルコニウムにTb、Er、Yb等のランタノイドを添加した膜等の、シリコン窒化膜よりも高い比誘電率を有することがより好ましい。容量絶縁膜15の比誘電率を高くすることにより、容量素子19の静電容量を増加させることができる。

【0042】

容量素子埋設用凹部の底部及び側壁に沿って、下部電極14、容量絶縁膜15及び上部電極16が積層されている。本実施の形態では、容量素子埋設用凹部のうち、下部電極14、容量絶縁膜15及び上部電極16が埋設された残りの部分に、埋設電極18bが埋設されている。埋設電極18bの上に引出配線部18aが形成されている。また、引出配線部18aは、容量素子埋設用凹部の上端の外側に連続して延在している配線溝(以下、上部配線溝という)内に形成される。埋設電極18b及び引出配線部18aは、本実施の形態においては、埋設電極18bと引出配線部18aとは同一の材料かつ、同一工程で構成されている。

【0043】

また、容量素子19と能動素子3aとは容量コンタクト13で接続される。容量コンタクト13は、セルコンタクト10a、容量コンタクト13a、及び容量コンタクト13b、を含む。すなわち、容量コンタクト13は、層間方向に配列された、少なくとも3以上のコンタクトを有する。3つのコンタクトのうち、少なくとも中間のコンタクトは、端部のコンタクトと異なる材料で構成されてもよい。たとえば、中間のコンタクトは、Cuを含む金属で構成され、端部のコンタクトは、Wを含む金属で構成される。容量コンタクト13aは、セルコンタクト10aを介して能動素子3aの拡散層に接続する。容量コンタクト13bは、下部電極14と容量コンタクト13aとを電気的に接続する。

【0044】

また、容量素子19の下端部は、容量コンタクト13bを覆うように構成されている。容量コンタクト13bは、容量素子19の下端と同じ層間絶縁膜7bに位置している上端部を有する。すなわち、容量素子19の下部電極14は、容量コンタクト13bの上面及び側壁の少なくとも上部を覆うものである。言い換えると、容量コンタクト13bは、キャップ膜6bの上面から上方に向かって突出する突出部と、該突出部と容量コンタクト13aとを接続するビア部とを有する。本実施の形態では、たとえば、容量コンタクト13bの突出部の表面全体が下部電極14のみに覆われている。

【0045】

本実施の形態では、下部電極14が容量コンタクト13bの突出部を覆うようにすることにより、容量素子19の電極面積を増加させて、静電容量を向上させることが可能となる。

【0046】

なお、本実施の形態では、上部電極16と埋設電極18bとの間に、ハードマスク31及びバリアメタル膜17が形成されていてもよい。また、互いに隣接する容量素子19は、容量絶縁膜15、及び上部電極16を共通化してもよい。すなわち、隣接する容量素子埋設用凹部の内壁及び上部配線溝に亘って、連続して容量絶縁膜15及び上部電極16が形成されてもよい。また、容量素子19の側壁上には、層間絶縁膜との間に側壁保護層が形成されていてもよい。側壁保護層は、層間絶縁膜よりも緻密な膜である。このため、隣接した容量素子19の下部電極14間のリーク電流の低減や、長期絶縁信頼性の向上という効果が得られる。

【0047】

なお、層間絶縁層の材料は、シリコン酸化膜や、シリコン酸化膜に弗素や炭素等を含有させた、一般に低誘電率の絶縁膜であっても良いし、絶縁膜内に微細な空孔を形成した、いわゆる多孔質膜であっても良い。本実施の形態では、配線が埋設された層間絶縁膜7a〜7eは、低誘電率膜であることが好ましい。なお、層間絶縁層としては、Siを含み、C、O、Hの中から少なくとも1つ以上の元素を含有する絶縁性材料や、これらの構成元素を用いてかつ膜内に空孔を含有する材料を用いる。ここで用いる絶縁性材料には、あとで形成する容量素子形成工程中の金属電極や容量絶縁膜の成膜で用いる気相原料が膜中に浸透しないよう、空孔サイズが小さいことが望まれる。気相原料の多くが0.5〜1nmのサイズであることに鑑み、空孔サイズは1nm以下である必要があり、望ましくは0.5nm以下がよい。論理回路100、記憶回路200に限らず、配線間の寄生容量を低減するためには、層間絶縁層の比誘電率は、シリコン酸化膜よりも低いことがより好ましい。これにより、配線間の寄生容量を低減し、回路動作の遅延を低減することができる。また、層間絶縁層のうち容量素子19と同一層の層間絶縁層のすべてが、低誘電率膜で構成されることが好ましい。たとえば、容量素子19と同一層である複数の配線層のすべての絶縁層が、シリコン酸化膜よりも低い比誘電率を有する絶縁層であることがこのましい。これにより、配線間やコンタクト間の寄生容量を低減させることができ、半導体装置の動作速度を高めることができる。

【0048】

キャップ層は、シリコン、炭素、窒素、からなる絶縁膜か、或いはそれらを有する膜の積層構造からなる、金属に対して拡散耐性を有する膜(金属拡散防止膜)であることがより好ましい。キャップ層の一例は、SiC膜又はSiON膜、及びSiCN膜、或いはそれらの積層膜等である。

【0049】

配線8a〜8cは、半導体装置の多層配線の形成方法として通常用いられる、デュアルダマシン法により形成されることがより好ましい。これにより、配線の製造コストを低減し、配線と、異層に存在する配線との間を接続するビア抵抗を低減することができる。なお、図3に示す配線8b、8cにおいては、各々の下層の配線8a、8bに対して接続するためのビアも含めて、配線として符号付けを行っている。すなわち、本実施の形態においては、特に明示しない限りは、ダマシン方法で形成された配線にはビアを含む。そして、各配線8a〜8cの周囲には、バリアメタル膜が形成されている。本実施の形態では、すべての配線がデュアルダマシン構造を有していることが好ましい。バリアメタル膜は、たとえば、チタン、タンタル、ルテニウムや、或いはそれらの窒化物、更にはそれらの積層膜等である。

【0050】

また、キャップ膜6d上に、層間絶縁膜7d、キャップ膜6e、層間絶縁膜7e、キャップ膜6fが形成される。これらの層には、固定電位を有する配線201a、201b、信号配線202a、202bなどのグローバルビット配線202、電源・グラウンド配線203、及び配線8d、8eが形成される。本実施の形態では、容量素子19の上層の配線層は、ゲート裏打ち配線以外の、グローバルビット配線202などの機能配線に利用され得る。

【0051】

以下、第1の実施の形態の作用効果について説明する。

第1の実施の形態では、論理回路領域において、最下層配線とセルコンタクト10bとを接続するコンタクト層が不要となる。この場合、論理回路領域の多層配線層は一段下がることになるので、記憶回路領域の設計において、配線層一層分のリソースが不足することになる。

【0052】

これに対して、本実施の形態では、ゲート電極上にゲート裏打ち配線を形成することができる。このため、容量素子の上層の設計自由度を配線層一層分増加させることができる。すなわち、容量素子の上層配線層を、ゲート裏打ち配線以外に利用できる。言い換えると、従来裏打ち配線として用いていた金属配線層を、記憶回路を構成する配線として使用することができる。

【0053】

したがって、本実施の形態では、不足した配線層のリソースを、ゲート裏打ち配線の配置位置を制御することにより、補完することが可能となる。ゆえに、本実施の形態では、コンタクト層が無い論理回路の設計を、配線層を増加させずに、そのまま利用することが可能となる。

【0054】

また、本実施の形態では、ゲート裏打ち配線を、容量素子の上層ではなく、下層に形成することができる。このため、容量素子の下層から上層に亘って、ゲート裏打ち配線とゲート電極とを接続するコンタクトが不要となる。さらに、本実施の形態では、ビット線も、容量素子の下層に形成されている。したがって、記憶回路領域において、容量素子同士の間にコンタクトを形成することが不要となるので、容量素子の間を狭くすることができる。これにより、容量素子の配置密度を高めることができる。

【0055】

次いで、第1の実施の形態の半導体装置の製造方法について、説明する。

図6〜図17は、第1の実施の形態の半導体装置の製造方法の工程手順を示す図である。図6〜図17において、WLはワード線の長手方向の断面部分を示し、BLはビット線の長手方向の断面部分を示す。これらの図は、説明しやすいように、1つの図面中に、多方向の断面図が含まれているものである。

【0056】

本実施の形態の半導体装置の製造方法は、以下の工程を含む。まず、基板(半導体基板1)に、ゲート電極32及び第1拡散層を備える第1トランジスタ(能動素子3a)を形成する。続いて、能動素子3a上に層間絶縁層(コンタクト層間絶縁膜4)を形成する。続いて、ゲート電極32上のコンタクト層間絶縁膜4に、ゲート電極32と同一方向に延在する配線溝(裏打ち配線溝42)を形成するとともに、第1拡散層上のコンタクト層間絶縁膜4に、コンタクトを埋設するための第1コンタクト孔(コンタクト孔44)を形成する。裏打ち配線溝42及びコンタクト孔44に同じ金属層(ゲート裏打ち配線30、及びセルコンタクト10a)を埋設する。コンタクト層間絶縁膜4上に絶縁層(層間絶縁膜7b、7c)を形成する。絶縁層内に、容量素子19を埋設する。

以下、詳細に説明する。

【0057】

まず、図6に示すように、半導体基板1の表面に素子分離膜2を形成する。素子分離膜2で区画された素子領域に能動素子3a、3b等のトランジスタを形成する。トランジスタはゲート電極と拡散層を有する。ゲート電極は、通常用いられるポリシリコン電極や部分的に金属シリサイド化されたポリシリコン電極を用いても良いし、メタルゲート電極を用いても良い。メタルゲート電極の形成方法として、ゲートファースト方式やゲートラスト方式等がある。また、拡散層上にシリサイド層20が形成されていてもよい。シリサイド層20には、例えば、コバルト、ニッケル、プラチナなどの金属とシリコンとの合金が形成されている。

【0058】

能動素子3a、3bの上にコンタクト層間絶縁膜4を形成する。コンタクト層間絶縁膜4を選択的に除去することにより、複数の開口部を形成する。たとえば、コンタクト層間絶縁膜4上にフォトレジストを塗布法等により形成し、所望のパターンをフォトリソグラフィ法により転写して、フォトレジストに開口部を形成する。フォトレジストをマスクとして、反応性イオンエッチング等の方法により、コンタクト層間絶縁膜4に開口部を形成する。その後、フォトレジストを除去する。

ここで、コンタクト層間絶縁膜4に開口部を形成する方法の詳細を説明する。

【0059】

本実施の形態では、同一層のフォトレジストに複数の開口部を形成する手法として、たとえば、ダブルパターニング方法を使用することができる。ダブルパターニング方法の一例を説明する。まず、1回目の露光により、トランジスタの拡散層上のフォトレジストにコンタクト孔のパターンを形成する。2回目の露光により、ゲート電極32上のフォトレジストに裏打ち配線溝のパターンを形成する。

【0060】

順番を分けてパターニングすることにより、コンタクト孔44と裏打ち配線溝42との距離が短い場合でも、露光光が干渉して解像度が低下することを抑制することができる。すなわち、ダブルパターニング方法により、互いに隣接したコンタクト孔44及び裏打ち配線溝42のパターンが精度良く得られる。なお、裏打ち配線溝42のパターン形成の順番が先でもよい。

【0061】

ダブルパターニング方法の露光には、たとえば、液浸ArF(弗化アルゴンレーザー)露光や、EUV(Extreme Ultra Violet)露光、EB(Electron Beam)露光等が用いられる。本実施の形態では、露光の波長を短くし、さらに、隣接するパターンの露光順番を異ならせることにより、コンタクト孔44と裏打ち配線溝42との距離を短くすることができる。

【0062】

ダブルパターニング方法により得られたマスクを用いて、エッチングなどにより、コンタクト層間絶縁膜4に複数の開口部を形成する。すなわち、コンタクト層間絶縁膜4に、裏打ち配線溝42、コンタクト孔41、43、44、及びビットコンタクト孔45が形成される。その後、フォトレジストを除去する。

【0063】

記憶回路領域に位置するコンタクト孔44、43は、論理回路領域に位置するコンタクト孔41(コンタクトを埋設するための第2コンタクト孔)と同時に形成されてもよい。コンタクト孔41は、第2トランジスタ(能動素子3b)の第2拡散層上の層間絶縁層に形成される。また、これらのコンタクト孔41、43、44と同時に、ビットコンタクト孔45が形成されてもよい。

【0064】

続いて、図7に示すように、コンタクト層間絶縁膜4上に金属膜50を堆積する。これにより、コンタクト層間絶縁膜4に形成された複数の開口部に同一の金属膜が埋設される。たとえば、記憶回路領域に位置するコンタクト孔44と裏打ち配線溝42とが同一の金属膜で埋設される。また、論理回路領域に位置するコンタクト孔41と裏打ち配線溝42とが同一の金属膜で埋設される。金属膜50の形成方法としては、CVD(Chemical Vapor Deposition)法、スパッタリング法、ALD(Atomic Layer Deposition)法等、通常半導体装置の形成に用いられる手法が用いられる。本実施の形態では、金属膜50としてWを用いる場合を説明する。

【0065】

続いて、図8に示すように、余剰の金属膜50をCMP(Chemical Mechanical Polishing)法により除去する。これにより、コンタクト層間絶縁膜4に、セルコンタクト10a、10b、ゲート裏打ち配線30、ビットコンタクト36が同時に形成される。

【0066】

続いて、図9に示すように、コンタクト層間絶縁膜4上に、コンタクト層間絶縁膜5、キャップ膜6a、及び層間絶縁膜7aを形成する。

【0067】

続いて、図10に示すように、これらの層に、フォトリソグラフィ法及びエッチングを用いて、ビット線溝46、配線溝47、及びコンタクト孔48が形成される。これらの開口部に対応するフォトレジストのパターンの形成には、一括露光方法を用いてもよいが、前述のダブルパターニング方法を用いてもよい。一括露光方法には、たとえば、ArF露光を用いることができる。また、ダブルパターニング方法には、液浸ArF露光を含むArF露光、EUV露光、EB露光などが用いられる。

【0068】

ビット線溝46の底面に、ビットコンタクト36の上面、及びセルコンタクト10cの上面が露出されている。配線溝47の底面に、セルコンタクト10bの上面が露出される。コンタクト孔48の底面に、セルコンタクト10aの上面が露出される。これらのビット線溝46、配線溝47、コンタクト孔48は、同時に形成されてもよいが、異なるタイミングで形成されてもよい。

【0069】

続いて、図11に示すように、これらの開口部にバリアメタル膜及び金属膜52を堆積する。続いて、図12に示すように、余剰の金属膜をCMPにより除去する。これにより、ビット線34、配線8a、及び容量コンタクト13aが形成される。以上のようにして、配線8aと同一工程でビット線34又は、容量コンタクト13aが形成される。なお、本実施の形態では、金属膜52がCuである場合について説明する。

【0070】

本実施の形態では、論理回路の配線を利用して、記憶回路領域にビット線34を形成することができる。このため、記憶回路領域には、配線と同じ高さのビット線34が形成されることになる。これにより、配線形成にCMPを実施したとしても、ビット線34の周辺の層間絶縁膜7aの平坦性を確保することが可能となる。

【0071】

続いて、図13に示すように、層間絶縁膜7a上にキャップ膜6bを形成する。キャップ膜6bにより、ビット線34、配線8a、及び容量コンタクト13aの上面が覆われる。

【0072】

続いて、図14に示すように、キャップ膜6b上にフォトレジスト54を形成する。フォトレジスト54に孔55を形成する。

【0073】

続いて、図15に示すように、エッチング等により、ビア孔57を形成する。フォトレジスト54を除去した後、キャップ膜6a上に金属膜56を形成する。金属膜56はビア孔57に埋設される。本実施の形態では、金属膜56として、たとえば、Wを用いた例を説明する。金属膜56は、たとえば、CVD法により堆積される。

【0074】

続いて、図16に示すように、フォトリソグラフィ法、反応性イオンエッチング法等により、容量コンタクト13bの先端に突出部を形成する。以後の工程で形成される容量素子19の直下の位置に、容量コンタクト13の突出部が形成されることが好ましい。

【0075】

以後の配線及び容量素子の形成工程は、たとえば、特開2011−54920号公報に記載の手法に沿って行うことができる。

すなわち、引き続いて、キャップ膜6b上に層間絶縁膜7bを形成する。層間絶縁膜7bに、通常用いられるダマシン法により、配線8bを形成する。

【0076】

本実施の形態では、記憶回路領域のキャップ膜6b上には容量コンタクト13の突出部が配列されている。突出部の高さ分だけ、層間絶縁膜7bが盛り上がることになる。このため、配線8bの形成過程において、層間絶縁膜7bがCMPされるとき、記憶回路領域の層間絶縁膜7bは平坦性が低下することが抑制される。これにより、容量のバラツキが抑制され得る。

【0077】

引き続き、少なくとも配線8bの上面を覆うようにキャップ膜6cを堆積する。キャップ膜6c上に層間絶縁膜7cを堆積させる。層間絶縁膜7c上に、ハードマスクとなる絶縁膜を堆積する。ハードマスクは、層間絶縁膜7b、7cを加工する際、層間絶縁膜7b、7cに対して高い選択比を有する絶縁膜が好ましく、例えば、シリコン酸化膜が好ましい。ハードマスク上に、フォトレジストを堆積する。フォトレジストに、フォトリソグラフィ法等の方法により、上部接続配線溝のパターンを形成する。フォトレジストは単一層のフォトレジスト、平坦化有機膜、シリコン酸化膜、反射防止膜、感光性レジスト等の多層フォトレジスト層のいずれかを用いても良い。

【0078】

次いで、フォトレジストをマスクとして、層間絶縁膜7cに、上部接続配線溝を形成する。例えば、反応性イオンエッチング等の微細加工方法を用いることができる。エッチング条件(選択比など)を適切に調節することにより、上部接続配線溝の高さを制御することができる。その後、フォトレジストを除去する。

【0079】

続いて、上部接続配線溝内の層間絶縁膜7c上及びハードマスク上に、多層レジスト層を形成する。多層レジスト層に、フォトリソグラフィ法等の方法により、容量素子埋設用凹部のパターンを形成する。

【0080】

続いて、多層レジスト層をマスクとして、反応性イオンエッチング等の微細加工方法により、層間絶縁膜7b、キャップ膜6c、層間絶縁膜7c内に、容量素子埋設用凹部を形成する。多層レジスト層は、容量素子埋設用凹部の加工中にアッシングを行って除去する。本実施の形態では、容量素子埋設用凹部の底部において、容量コンタクト13bの突出部の少なくとも上面及び側壁が露出している。

【0081】

なお、本実施の形態では、上部接続配線溝を後に容量素子埋設用凹部を形成したが、上部接続配線溝を形成する前に容量素子埋設用凹部を形成してもよい。

【0082】

続いて、少なくとも上部接続配線溝及び容量素子埋設用凹部の底部上及び側壁上に、下部電極14を堆積する。下部電極14を形成する方法としては、CVD法、スパッタリング法、ALD法等、通常半導体装置の形成に用いられる手法を用いれば良い。引き続き、塗布法等により、フォトレジストを、容量素子埋設用凹部内に埋設する。フォトレジストは、容量素子埋設用凹部内にのみ残存し、かつ、容量素子埋設用凹部の上端に達していない高さで形成されていることが好ましく、必要であれば、フォトレジストに対して露光・現像処理を行うことで、不要なフォトレジストを除去しておいても良い。この後、下部電極14を、例えば反応性イオンエッチング法等の方法により、エッチバックする。これにより、容量素子埋設用凹部の上端部に達しない下部電極14を形成することができる。その後、フォトレジストを除去する。

【0083】

続いて、下部電極14の上に、容量絶縁膜15及び上部電極16を堆積する。容量絶縁膜15及び上部電極16は、少なくとも容量素子埋設用凹部の底面上、側壁上および上部接続配線溝の底面上、側壁上に形成される。容量絶縁膜15を形成する方法としては、CVD法、スパッタリング法、ALD法等、通常半導体装置の形成に用いられる手法を用いることができる。また、容量素子の静電容量を向上させるために、数nmの薄膜を均一性良く堆積することができるALD法がより好ましい。なお、容量絶縁膜15を堆積した後、結晶性を向上させるための焼結工程を行っても良い。

【0084】

次いで、例えば塗布法により、フォトレジストを、容量素子埋設用凹部の内部及び上部接続配線溝の内部に形成する。レジストは、論理回路領域に残存したハードマスク上部に残存しないように形成する。必要であれば、フォトレジストに対して露光・現像処理を行うか、あるいは、全面エッチバックを行うことで、論理回路領域に形成された不要なフォトレジストを除去しておく。

【0085】

次いで、上部電極16及び容量絶縁膜15を、反応性イオンエッチング等の方法により、エッチバックする。これにより、ハードマスク上の上部電極16及び容量絶縁膜15を除去できる。続いて、フォトレジストを、アッシング等により除去する。

【0086】

次いで、導電性を有するハードマスク31を、容量素子埋設用凹部の底面上、側壁上および上部接続配線溝の底面上、側壁上に堆積する。ハードマスク31には、例えば、チタン及びチタンの窒化物、タンタル及びタンタルの窒化物、ルテニウム等の、高融点金属及びそれらの窒化物、或いはそれらの積層構造体を用いても良い。ハードマスク31を形成する方法としては、CVD法、スパッタリング法、ALD法等、通常半導体装置の形成に用いられる手法を用いれば良い。ハードマスク31の厚さとしては、後に行う論理回路配線加工を行うのに十分な厚さを有していることが好ましい。ただし、ハードマスク31は、容量素子19の上部電極として残存することがあるため、低い電気抵抗を有することが好ましい。すなわち、容量素子埋設用凹部内部に残存したハードマスク31は上部電極として機能する。従って、ハードマスク31の厚さは、後述する論理回路配線加工後に消失する程度の厚さに設定しても良い。すなわち、ハードマスク31の材料は、上部電極16と同種の材料を用いることができる。ハードマスク31と上部電極16とは、同種の材料で形成されても、異なる材料で形成されてもよいが、同一の材料であることがより好ましい。

【0087】

次いで、論理回路領域に配線8cを埋設するための配線溝を形成する。なお、配線形成工程において、その開口部を形成した後、反応性イオンエッチング等によりハードマスク31を除去しても良い。この方法を用いることにより、容量素子19内に残存するハードマスク31の厚さを薄くして、容量素子の上部電極の抵抗値を低くすることができる。

【0088】

次に、容量素子埋設用凹部、上部接続配線溝及び配線溝にバリアメタル膜17及び導電膜を埋設する。導電膜は、Cu、W、Alを含む金属で構成されてもよいが、このなかでも、Cuを含む材料で構成されることが好ましい。次いで、CMP法などの方法により、導電膜、バリアメタル膜、ハードマスクを除去する。これにより、容量素子19、上部接続配線18、及び配線8cが形成される。上部接続配線18と配線8cとは同一工程で形成されることが好ましいが、別工程で形成されてもよい。すなわち、上部接続配線18は、配線8cの金属膜と同一の材料で構成されてもよいが、異なる材料で構成されてもよい。なお、本実施の形態では、容量素子埋設用凹部形成後に、配線溝を形成したが、この順番に限定されずに、配線溝に金属膜を埋設した後に、容量素子埋設用凹部を形成してもよい。

【0089】

次いで、図17に示すように、上部接続配線18の上面上及び配線8cの上面上にキャップ膜6dを形成する。この後、キャップ膜6d上に、層間絶縁膜7d、キャップ膜6e、層間絶縁膜7e、キャップ膜6fを形成する。また、各絶縁膜に、配線8d、8e、固定電位を有する配線201a、201b、信号配線202a、202b、及び電源・グラウンド配線203を形成する。

以上により、第1の実施の形態の半導体装置が得られる。

【0090】

(第2の実施の形態)

次いで、第2の実施の形態の半導体装置について説明する。

図18は、第2の実施の形態の半導体装置を模式的に示す断面図である。

第2の実施の形態は、容量素子19の下端と、キャップ膜6bとの間に層間絶縁膜7bが形成されている点を除いて、第1の実施の形態と同様である。

以下、詳細に説明する。

【0091】

容量素子19の下端は、少なくとも容量コンタクト13の上面に接していることが好ましい。たとえば、容量素子19の下端は、同一層に位置する配線8cのうち配線部分の下端と同じ位置としてもよい。言い換えると、容量素子埋設用凹部の底面は、同一層の配線層の配線溝の底面と同一面を構成してもよい。また、容量素子埋設用凹部の底面の周囲にストッパ膜が形成されていてもよい。これらにより、容量素子埋設用凹部の底部の位置の制御が容易となる。

【0092】

第2の実施の形態では、容量素子19の下端とビット線34との間の距離を、容量素子19の下端がキャップ膜6bに接している場合と比較して、増加させることが可能となる。これにより、容量素子19とビット線34との間の寄生容量の増加を抑制することができる。

【0093】

第2の実施の形態の半導体装置の製造方法は、以下の工程を有する点が、第1の実施の形態と異なる。すなわち、まず、層間絶縁層(コンタクト層間絶縁膜4)上にキャップ層(キャップ膜6a)を形成する。次いで、キャップ膜6a上に絶縁層(層間絶縁膜7b)を形成する。次いで、層間絶縁膜7bに、キャップ膜6aに到達しない凹部(容量素子埋設用凹部)を形成する。この後、当該凹部に容量素子19を埋設する。

【0094】

凹部の形成工程において、容量素子埋設用凹部の底部には、少なくとも容量コンタクト13bの上面が露出している。一方、容量素子埋設用凹部の底部には、層間絶縁膜7bの下地層が露出していない。下地層は、たとえば、キャップ膜6aである。容量素子埋設用凹部の深さは、エッチング条件や、層間絶縁膜7bの中間にストッパ膜を形成することにより制御することができる。

(第3の実施の形態)

次いで、第3の実施の形態の半導体装置について説明する。

図19は、第3の実施の形態の半導体装置を模式的に示す断面図である。

第3の実施の形態は、ビット線34bの同一層の論理回路領域にコンタクト層が形成されている点を除いて、第1の実施の形態と同様である。

以下、詳細に説明する。

【0095】

論理回路領域には、コンタクト層間絶縁膜4と第1配線層(最下層配線層)との間に、コンタクト層が形成されている。コンタクト層は、コンタクト層間絶縁膜5中に埋設されたセルコンタクト10dを有する。セルコンタクト10dは、第1配線(配線8a)と、セルコンタクト10bとを電気的に接続する。セルコンタクト10bは、論理回路領域のトランジスタ(能動素子3b)の拡散層に接続している。

【0096】

一方、記憶回路領域には、コンタクト層と同一層に、ビット線34bが形成されている。ビット線34bは、Wを含む金属で構成されているのが好ましい。ビット線34bの材料は、配線8a(たとえば、Cu配線)とは異なるものである。ビット線34bの上面は、配線8aの上面より低く形成されている。言い換えると、ビット線34bの上端とキャップ膜6aとは、互いに離間されており、その間にはコンタクト層間絶縁膜5bが配置されている。本実施の形態では、ビット線34bは、例えば、エッチングにより加工されて形成され得るものである。

【0097】

本実施の形態では、容量素子19の下端とビット線34bとの間の距離を、第1の実施の形態よりも確保することができるので、その間の寄生容量の増大を抑制することができる。

また、ゲート裏打ち配線30は、ワード線(ゲート電極32)と接しつつ、同層に形成されているので、ワード線の抵抗を低減させつつ、容量素子19の上層の配線層の設計の自由度を高めることが可能となる。

【0098】

なお、当然ながら、上述した複数の実施の形態は、その内容が相反しない範囲で組み合わせることができる。また、上述した実施の形態では、各部の構造などを具体的に説明したが、その構造などは本願発明を満足する範囲で各種に変更することができる。

【符号の説明】

【0099】

1 半導体基板

2 素子分離膜

3a、3b 能動素子

4 コンタクト層間絶縁膜

5、5a、5b コンタクト層間絶縁膜

6a、6b、6c、6d、6e、6f キャップ膜

7a、7b、7c、7d、7e 層間絶縁膜

8a、8b、8c、8d、8e 配線

10a、10b、10c、10d セルコンタクト

13、13a、13b 容量コンタクト

14 下部電極

15 容量絶縁膜

16 上部電極

17 バリアメタル膜

18 上部接続配線

18a 引出配線部

18b 埋設電極

19 容量素子

20 シリサイド層

30 ゲート裏打ち配線

31 ハードマスク

32 ゲート電極

34、34bビット線

35 配線

36 ビットコンタクト

41 コンタクト孔

42 裏打ち配線溝

43 コンタクト孔

44 コンタクト孔

45 ビットコンタクト孔

46 ビット線溝

47 配線溝

48 コンタクト孔

50 金属膜

52 金属膜

54 フォトレジスト

55 孔

56 金属膜

57 ビア孔

58 フォトレジスト

59 孔

100 論理回路

110 半導体基板

200 記憶回路

201a、201b 固定電位を有する配線

202 グローバルビット配線

202a、202b 信号配線

203 電源・グラウンド配線

210 容量素子

220 周辺回路

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の分野において、半導体装置の微細化及び高速化が要求されている。微細化及び高速化を実現している半導体装置として、例えば、特許文献1に記載のものが挙げられる。

【0003】

特許文献1に記載の半導体装置は、同一基板上に論理回路及び記憶回路が混載された混載回路を有する。論理回路を構成する多層配線層の同層に、記憶回路を構成する容量素子が埋設されている。容量素子の上には、上層配線層が形成されている。上層配線層の配線(第5層配線55)が、ワード線裏打ち配線として利用されている(特許文献1の段落0123)。ワード線裏打ち配線は、ワード線の抵抗を低減するものである。

【0004】

また、特許文献2には、容量素子の上層にビット線が配置されている半導体装置が記載されている。ビット線は、コンタクトを介して、トランジスタの拡散層と電気的に接続する。コンタクトは、容量素子同士の間に隣接して配置されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−54920号公報

【特許文献2】特開2009−105149号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に記載の半導体装置の製造方法は、容量素子の上層の配線層をワード線裏打ち配線に利用するものである。このため、容量素子の上層の配線層の設計自由度は、上層配線をワード線裏打ち配線とするという前提条件が必須となるために、低下していた。

【課題を解決するための手段】

【0007】

本発明によれば、

基板と、

前記基板上に設けられた層間絶縁層と、

前記基板に設けられており、前記層間絶縁層内に埋め込まれた第1トランジスタと、

前記層間絶縁層上に設けられた多層配線層と、

前記多層配線層内に設けられた容量素子と、

前記第1トランジスタを構成するゲート電極及び拡散層と、

前記ゲート電極の上面と接しており、前記ゲート電極と同一方向に延在しており、かつ前記層間絶縁層内に埋設された金属配線と、

前記第1トランジスタの拡散層に接続しており、前記層間絶縁層内に埋設された第1コンタクトと、を備え、

前記金属配線は、前記第1コンタクトと同じ材料で構成されている、

半導体装置が提供される。

【0008】

金属配線は、ゲート電極の抵抗を低減するものである。金属配線は、容量素子の下層の層間絶縁層にされる。このため、容量素子の上層の配線層の設計は、金属配線の利用に限定されないので、自由度が高まるものである。

【0009】

また、本発明によれば、

基板に、ゲート電極及び第1拡散層を備える第1トランジスタを形成する工程と、

前記第1トランジスタ上に層間絶縁層を形成する工程と、

前記ゲート電極上の前記層間絶縁層に、前記ゲート電極と同一方向に延在する配線溝を形成するとともに、前記第1拡散層上の前記層間絶縁層に、コンタクトを埋設するための第1コンタクト孔を形成する工程と、

前記配線溝及び第1コンタクト孔に同じ金属層を埋設する工程と、

前記第1層間絶縁層上に絶縁層を形成する工程と、

前記絶縁層内に、容量素子を埋設する工程と、を有する、

半導体装置の製造方法が提供される。

【発明の効果】

【0010】

本発明によれば、容量素子上の配線層の設計自由度に優れた半導体装置が提供される。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態における半導体装置を模式的に示す上面図である。

【図2】第1の実施の形態の記憶素子の周辺を模式的に示す上面図である。

【図3】図2のA−A´線断面図である。

【図4】図2のB−B´線断面図である。

【図5】図2のC−C´線断面図である。

【図6】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図7】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図8】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図9】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図10】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図11】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図12】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図13】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図14】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図15】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図16】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図17】第1の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図18】第2の実施の形態における半導体装置を模式的に示す断面図である。

【図19】第3の実施の形態における半導体装置を模式的に示す断面図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0013】

(第1の実施の形態)

第1の実施の形態の半導体装置について説明する。

図1及び図2は、第1の実施の形態における半導体装置を模式的に示す上面図である。図3〜図5は、図2に示されたA−A´線断面図、B−B´線断面図、及びC−C´線断面図である。

【0014】

本実施の形態の半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板(半導体基板1)上には、層間絶縁層(コンタクト層間絶縁膜4、5)が設けられている。第1トランジスタ(能動素子3a)は、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極(ゲート電極32)及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線内に設けられている。金属配線(ゲート裏打ち配線30)は、ゲート電極32の上面と接しており、ゲート電極32と同一方向に延在しており、かつ層間絶縁層(コンタクト層間絶縁膜4)内に埋設されている。第1コンタクト(セルコンタクト10a)は、第1トランジスタ(能動素子3a)の拡散層(図示せず)に接続しており、層間絶縁層(コンタクト層間絶縁膜4)内に埋設される。

本実施の形態において、金属配線(ゲート裏打ち配線30)は、第1コンタクト(セルコンタクト10a)と同じ材料で構成されている。

【0015】

本実施の形態のゲート裏打ち配線30は、容量素子19の上層の配線層ではなく、容量素子19の下層に形成される。このため、容量素子19の上層の配線層の設計は、ゲート裏打ち配線30の利用に限定されないので、自由度が高まる。また、ゲート裏打ち配線30を形成することにより、ワード線(ゲート電極32)の抵抗を低下させることが可能となる。

【0016】

以下、本実施の形態の各構成について詳述する。

【0017】

本実施の形態の半導体装置は、混載DRAM(Dynamic Random Access Memory)、または、汎用DRAMのいずれにも適用できる。図1は、混載DRAMの半導体装置を示す。この半導体装置は、記憶回路と論理回路とを同一基板上に備える。すなわち、図1に示すように、半導体基板110上に、容量素子210を含む記憶回路200と半導体素子が形成される論理回路100とが混載されている。論理回路100は、記憶回路200中の容量素子210の周辺回路220ではなく、記憶回路200とは異なる領域に形成されたものである。たとえば、論理回路領域は、CPU(Central Processing Unit)等の高速ロジック回路が形成された領域である。なお、汎用DRAMは、記憶回路を有し、論理回路を有さないものである。

【0018】

図2は、記憶回路200のレイアウトの一例を示す。

記憶回路200は、容量素子19、ゲート電極32、ビット線34を含む。容量素子19は、六角形の拡散層上に2つ形成される。容量素子19は、容量コンタクト13(容量素子接続コンタクト)を介して拡散層に接続される。ゲート電極32は、複数の拡散層に亘って形成される。ビット線34は、ゲート裏打ち配線30とは略直交する方向に形成される。ビット線34は、セルコンタクト10c(ビット線接続コンタクト)を介して拡散層に接続される。

【0019】

図2において、A−A´線は、容量素子19を横断しビット線34を横断しない線である。B−B´線は、ビット線34を横断する線である。C−C´線は、ゲート電極32を横断し、ビット線34を横断しない線である。

【0020】

半導体基板1の表面には、素子分離膜2が形成されている。素子分離膜2は、記憶回路領域と論理回路領域とを区画する。記憶回路領域には記憶回路200が形成される。論理回路領域には、論理回路100が形成される。記憶回路200は、能動素子3aを有する。論理回路100は、能動素子3bを有する。能動素子3a、3bは、たとえば、トランジスタである。素子分離膜2は、たとえば、シリコン酸化膜で構成される。

【0021】

半導体基板1上にはコンタクト層間絶縁膜4が形成されている。コンタクト層間絶縁膜4には、能動素子3a、3b、ゲート裏打ち配線30、セルコンタクト10a、10b、10c、ビットコンタクト36が埋設されている。

【0022】

トランジスタ(能動素子3a、3b)は、基板の表層に形成された拡散層(ソースドレイン領域)、基板上に設けられたゲート絶縁膜、ゲート電極32を有する。ゲート電極32は、特に限定されないが、ポリシリコン電極、金属電極のいずれでもよい。ポリシリコン電極上には、たとえば、TiNなどの金属層が形成されていてもよい。また、ゲート電極は、一般にメタルゲートと呼称される、例えば、ニッケル、プラチナ、コバルト、ジルコニウム、タングステン、チタン、ハフニウム、タンタル、アルミ、ルテニウム、パラジウム、などの金属材料を含む材料により形成されていても良い。このように、金属電極及び金属層は、複数種の金属膜が積層されていてもよいが、単層の金属層で構成されていてもよい。本実施の形態では、拡散層の表層にシリサイド層20が形成されていてもよい。

【0023】

記憶回路領域に位置するゲート電極32上には、ゲート裏打ち配線30が形成されている。ゲート裏打ち配線30は、ゲート電極32とは異なる部材で構成されており、ゲート電極32と同じ層間絶縁層(コンタクト層間絶縁膜4)内に埋設されている。ゲート裏打ち配線30は、少なくとも同一トランジスタのソース・ドレイン拡散層に跨って形成されていることが好ましい。ゲート裏打ち配線30の下面の全面又は一部がゲート電極32の上面に接していてもよい。ゲート裏打ち配線30の上面は、コンタクト層間絶縁膜4の上面と同一面を構成してもよい。

【0024】

本実施の形態において、同一面とは、下記の測定方法で測定したとき、表面の平均高さに対する凹凸の高さのバラツキの最大値が好ましくは30nm以下であり、より好ましくは20nm以下であり、更に好ましくは10nm以下である平面をいう。こうした測定方法としては、例えば、SEM(Scanning Electron Microscope)やTEM(Transmission Electron Microscope)を用いて上部接続配線18の上面および配線8bの上面を含む断面画像を取得し、この断面画像から段差の高さのバラツキを測定する方法や、半導体装置の製造工程における検査工程に広く用いられている段差計により、平面方向の高さのプロファイルを測定する方法、等が挙げられる。

【0025】

ゲート裏打ち配線30は、能動素子3aの拡散層に接続するセルコンタクト10aと同じ材料で構成されていることが好ましい。ゲート裏打ち配線30は、たとえば、W、Cu、Alなどのいずれかを含む金属材料で構成されていることが好ましく、Wを主成分として含む、又はWからなる金属材料で構成されることが好ましい。本実施の形態において、同じ材料とは、同じ成分組成である、又は、主要な成分が同じであることを意味する。また、本実施の形態において、主成分として含むとは、たとえば、90質量%以上含むことを意味する。

【0026】

ゲート裏打ち配線30がセルコンタクト10aと同じ材料で構成されるので、ゲート裏打ち配線30とセルコンタクト10aとは同一工程で構成されることになる。このため、製造プロセスの簡略化を図ることが可能となる。また、ゲート裏打ち配線30がWを含む金属材料で構成されているので、ゲート裏打ち配線30の金属成分が層間絶縁膜内に拡散することを抑制することができる。

【0027】

また、ゲート裏打ち配線30は、能動素子3bの拡散層に接続するセルコンタクト10bと同じ材料で構成されていてもよい。能動素子3b(第2トランジスタ)は、半導体基板1に設けられており、第1トランジスタ(能動素子3a)を含む記憶回路領域とは異なる領域である論理回路領域に位置する。能動素子3aと第1配線とを第2コンタクト(セルコンタクト10b)が接続する。第1配線は、論理回路領域に位置する多層配線層のうち、最下層の配線層に位置する。本実施の形態では、ゲート裏打ち配線30は、記憶回路200領域のセルコンタクト10aと、論理回路100領域のセルコンタクト10bと同一層に形成されている。また、ゲート裏打ち配線30は、セルコンタクト10a、及びセルコンタクト10bと同一材料で構成される。

【0028】

また、ビットコンタクト36は、素子分離膜2で離間される2つの拡散層に跨って形成されてもよい。ビットコンタクト36は、素子搭載面に沿って一方向に延在していてもよい。

【0029】

コンタクト層間絶縁膜4上には、コンタクト層間絶縁膜5、キャップ膜6a、層間絶縁膜7aが形成される。これらの層に、配線8a、ビット線34、配線35及び容量コンタクト13aが埋設される。すなわち、最下層配線の配線8aと同一層に、ビット線34及び容量コンタクト13aが形成される。ビット線34及び容量コンタクト13aは、記憶回路200領域に位置する。配線8aは、論理回路100領域に位置する。なお、本実施の形態では、配線8a、ビット線34及び容量コンタクト13aの側面及び底面に沿ってバリアメタル膜で構成され、その内部に金属膜が埋設されている。

【0030】

また、コンタクト層間絶縁膜4、5のうち少なくとも1層は、シリコン酸化膜を用いてもよいが、シリコン酸化膜よりも低い比誘電率を有する絶縁膜であることが、より好ましい。こうした絶縁膜としては、例えば、シリコン酸化膜の酸素原子を弗素や炭素原子、及び炭化水素基に置換した、一般に低誘電率膜と呼称される絶縁膜か、あるいは、少なくともシリコン、酸素及び炭素を有し、更に絶縁膜中に直径数ナノメートル以下の微細な空孔を有する、いわゆる多孔質膜を用いても良い。これら絶縁膜の比誘電率としては、膜中に微細空孔を有さない絶縁膜の場合には、3.1以下であることが好ましく、更に好ましくは、膜中に微細空孔を有する絶縁膜の場合には、2.6以下であることが好ましい。かかる構造により、前記コンタクトの寄生容量を低減することができ、結果として、記憶回路及び論理回路の遅延を低減し、半導体素子の動作速度を向上させることができる。

【0031】

ビット線34は、セルコンタクト10c又はビットコンタクト36を介して、能動素子3aの拡散層に接続する。ビット線34の上面は、配線8aの上面と同一面を構成してもよい。また、ビット線34は、配線8aとは同一材料で構成されていることが好ましい。ビット線34は、たとえば、W、Cu、Alなどのいずれかを含む金属膜で構成されていることが好ましく、Cuを主成分として含む、又はCuからなる金属膜で構成されることが好ましい。

【0032】

ビット線34が配線8aと同一工程で構成されることにより、製造プロセスの簡略化を図ることが可能となる。また、ビット線34及び配線8aを、Cuを含む金属膜で構成することにより、Wを使用した場合よりも、半導体装置の動作速度を向上させることができる。

【0033】

また、本実施の形態において、ビット線34を最下層配線(配線8a)と同一層に形成できる。このため、論理回路100領域の配線8aとセルコンタクト10bとの間に、コンタクト層を形成することが不要となる。論理回路100領域の層間方向において、コンタクト層が不要となる分、寄生抵抗が小さくなり、半導体装置の動作速度を高めることができる。したがって、本実施の形態の混載DRAMは、ピュアロジック品と同一のデバイスパラメータを用いて設計され得る。

【0034】

また、記憶回路200領域の容量素子19の下層に、論理回路100の配線を利用して、ビット線34を形成することができる。すなわち、ビット線34は、配線8aと同じ材料で構成されるか、又は、ビット線34の上面と最下層配線(配線8a)の上面とを同一面に構成することができる。このため、配線8aを平坦化して形成するときに、記憶回路領域の層間絶縁膜7aの平坦性が向上する。したがって、記憶回路領域の層間絶縁膜7a上に位置する容量素子19の高さのバラツキを抑制できるので、容量のバラツキを低減することが可能となる。

【0035】

なお、容量コンタクト13bは、ビット線34及び配線8aと同一材料で構成されていることが好ましい。

【0036】

また、ゲート裏打ち配線30には、セルアレイの外側に位置するワード線ドライバから信号が入力される。図2は、セルアレイ端の拡大図を示す。たとえば、図5に示すように、ゲート裏打ち配線30は、論理回路100に位置する能動素子3bと配線35を介して電気的に接続される。配線35は、ゲート裏打ち配線30およびセルコンタクト10bとは、ビアを介して接続する。配線35は、配線8aと同一工程で形成されることが好ましい。つまり、配線35は、配線8aと同一部材で構成され得る。

【0037】

ビット線34の上面上には、キャップ膜6bが形成される。キャップ膜6bは、金属拡散防止膜を有してもよい。これにより、ビット線34がCuを含む金属材料で構成される場合であっても、キャップ膜6bは、層間絶縁層内へのCuの拡散を防止することができる。

【0038】

キャップ膜6b上に、層間絶縁膜7b、キャップ膜6c、層間絶縁膜7c、キャップ膜6dが形成される。これらの層には、容量素子19、容量コンタクト13、配線8b、8cが形成される。

【0039】

容量素子19は、下部電極14、容量絶縁膜15、上部電極16を含む。容量素子19は、多層配線層内に形成された凹部(以下、容量素子埋設用凹部という)に埋め込まれている。本実施の形態では、容量素子19は、2層の層間絶縁膜に亘って形成されているが、この態様に限定されず、3層以上に亘って形成されてもよい。

【0040】

下部電極14および上部電極16は、容量絶縁膜15を挟み込んで平行平板容量素子とするための電極として機能する。下部電極14および上部電極16の材料としては、例えば、チタン、タンタル等の高融点金属や、或いはそれらの窒化物等により形成することがより好ましく、容量絶縁膜15の結晶性を向上させることができる材料を用いることが好ましい。

【0041】

容量絶縁膜15の材料としては、例えば、二酸化ジルコニウム(ZrO2)、ジルコニウムアルミネート(ZrAlOx)、更には、前記二酸化ジルコニウムにTb、Er、Yb等のランタノイドを添加した膜等の、シリコン窒化膜よりも高い比誘電率を有することがより好ましい。容量絶縁膜15の比誘電率を高くすることにより、容量素子19の静電容量を増加させることができる。

【0042】

容量素子埋設用凹部の底部及び側壁に沿って、下部電極14、容量絶縁膜15及び上部電極16が積層されている。本実施の形態では、容量素子埋設用凹部のうち、下部電極14、容量絶縁膜15及び上部電極16が埋設された残りの部分に、埋設電極18bが埋設されている。埋設電極18bの上に引出配線部18aが形成されている。また、引出配線部18aは、容量素子埋設用凹部の上端の外側に連続して延在している配線溝(以下、上部配線溝という)内に形成される。埋設電極18b及び引出配線部18aは、本実施の形態においては、埋設電極18bと引出配線部18aとは同一の材料かつ、同一工程で構成されている。

【0043】

また、容量素子19と能動素子3aとは容量コンタクト13で接続される。容量コンタクト13は、セルコンタクト10a、容量コンタクト13a、及び容量コンタクト13b、を含む。すなわち、容量コンタクト13は、層間方向に配列された、少なくとも3以上のコンタクトを有する。3つのコンタクトのうち、少なくとも中間のコンタクトは、端部のコンタクトと異なる材料で構成されてもよい。たとえば、中間のコンタクトは、Cuを含む金属で構成され、端部のコンタクトは、Wを含む金属で構成される。容量コンタクト13aは、セルコンタクト10aを介して能動素子3aの拡散層に接続する。容量コンタクト13bは、下部電極14と容量コンタクト13aとを電気的に接続する。

【0044】

また、容量素子19の下端部は、容量コンタクト13bを覆うように構成されている。容量コンタクト13bは、容量素子19の下端と同じ層間絶縁膜7bに位置している上端部を有する。すなわち、容量素子19の下部電極14は、容量コンタクト13bの上面及び側壁の少なくとも上部を覆うものである。言い換えると、容量コンタクト13bは、キャップ膜6bの上面から上方に向かって突出する突出部と、該突出部と容量コンタクト13aとを接続するビア部とを有する。本実施の形態では、たとえば、容量コンタクト13bの突出部の表面全体が下部電極14のみに覆われている。

【0045】

本実施の形態では、下部電極14が容量コンタクト13bの突出部を覆うようにすることにより、容量素子19の電極面積を増加させて、静電容量を向上させることが可能となる。

【0046】

なお、本実施の形態では、上部電極16と埋設電極18bとの間に、ハードマスク31及びバリアメタル膜17が形成されていてもよい。また、互いに隣接する容量素子19は、容量絶縁膜15、及び上部電極16を共通化してもよい。すなわち、隣接する容量素子埋設用凹部の内壁及び上部配線溝に亘って、連続して容量絶縁膜15及び上部電極16が形成されてもよい。また、容量素子19の側壁上には、層間絶縁膜との間に側壁保護層が形成されていてもよい。側壁保護層は、層間絶縁膜よりも緻密な膜である。このため、隣接した容量素子19の下部電極14間のリーク電流の低減や、長期絶縁信頼性の向上という効果が得られる。

【0047】

なお、層間絶縁層の材料は、シリコン酸化膜や、シリコン酸化膜に弗素や炭素等を含有させた、一般に低誘電率の絶縁膜であっても良いし、絶縁膜内に微細な空孔を形成した、いわゆる多孔質膜であっても良い。本実施の形態では、配線が埋設された層間絶縁膜7a〜7eは、低誘電率膜であることが好ましい。なお、層間絶縁層としては、Siを含み、C、O、Hの中から少なくとも1つ以上の元素を含有する絶縁性材料や、これらの構成元素を用いてかつ膜内に空孔を含有する材料を用いる。ここで用いる絶縁性材料には、あとで形成する容量素子形成工程中の金属電極や容量絶縁膜の成膜で用いる気相原料が膜中に浸透しないよう、空孔サイズが小さいことが望まれる。気相原料の多くが0.5〜1nmのサイズであることに鑑み、空孔サイズは1nm以下である必要があり、望ましくは0.5nm以下がよい。論理回路100、記憶回路200に限らず、配線間の寄生容量を低減するためには、層間絶縁層の比誘電率は、シリコン酸化膜よりも低いことがより好ましい。これにより、配線間の寄生容量を低減し、回路動作の遅延を低減することができる。また、層間絶縁層のうち容量素子19と同一層の層間絶縁層のすべてが、低誘電率膜で構成されることが好ましい。たとえば、容量素子19と同一層である複数の配線層のすべての絶縁層が、シリコン酸化膜よりも低い比誘電率を有する絶縁層であることがこのましい。これにより、配線間やコンタクト間の寄生容量を低減させることができ、半導体装置の動作速度を高めることができる。

【0048】

キャップ層は、シリコン、炭素、窒素、からなる絶縁膜か、或いはそれらを有する膜の積層構造からなる、金属に対して拡散耐性を有する膜(金属拡散防止膜)であることがより好ましい。キャップ層の一例は、SiC膜又はSiON膜、及びSiCN膜、或いはそれらの積層膜等である。

【0049】

配線8a〜8cは、半導体装置の多層配線の形成方法として通常用いられる、デュアルダマシン法により形成されることがより好ましい。これにより、配線の製造コストを低減し、配線と、異層に存在する配線との間を接続するビア抵抗を低減することができる。なお、図3に示す配線8b、8cにおいては、各々の下層の配線8a、8bに対して接続するためのビアも含めて、配線として符号付けを行っている。すなわち、本実施の形態においては、特に明示しない限りは、ダマシン方法で形成された配線にはビアを含む。そして、各配線8a〜8cの周囲には、バリアメタル膜が形成されている。本実施の形態では、すべての配線がデュアルダマシン構造を有していることが好ましい。バリアメタル膜は、たとえば、チタン、タンタル、ルテニウムや、或いはそれらの窒化物、更にはそれらの積層膜等である。

【0050】

また、キャップ膜6d上に、層間絶縁膜7d、キャップ膜6e、層間絶縁膜7e、キャップ膜6fが形成される。これらの層には、固定電位を有する配線201a、201b、信号配線202a、202bなどのグローバルビット配線202、電源・グラウンド配線203、及び配線8d、8eが形成される。本実施の形態では、容量素子19の上層の配線層は、ゲート裏打ち配線以外の、グローバルビット配線202などの機能配線に利用され得る。

【0051】

以下、第1の実施の形態の作用効果について説明する。

第1の実施の形態では、論理回路領域において、最下層配線とセルコンタクト10bとを接続するコンタクト層が不要となる。この場合、論理回路領域の多層配線層は一段下がることになるので、記憶回路領域の設計において、配線層一層分のリソースが不足することになる。

【0052】

これに対して、本実施の形態では、ゲート電極上にゲート裏打ち配線を形成することができる。このため、容量素子の上層の設計自由度を配線層一層分増加させることができる。すなわち、容量素子の上層配線層を、ゲート裏打ち配線以外に利用できる。言い換えると、従来裏打ち配線として用いていた金属配線層を、記憶回路を構成する配線として使用することができる。

【0053】

したがって、本実施の形態では、不足した配線層のリソースを、ゲート裏打ち配線の配置位置を制御することにより、補完することが可能となる。ゆえに、本実施の形態では、コンタクト層が無い論理回路の設計を、配線層を増加させずに、そのまま利用することが可能となる。

【0054】

また、本実施の形態では、ゲート裏打ち配線を、容量素子の上層ではなく、下層に形成することができる。このため、容量素子の下層から上層に亘って、ゲート裏打ち配線とゲート電極とを接続するコンタクトが不要となる。さらに、本実施の形態では、ビット線も、容量素子の下層に形成されている。したがって、記憶回路領域において、容量素子同士の間にコンタクトを形成することが不要となるので、容量素子の間を狭くすることができる。これにより、容量素子の配置密度を高めることができる。

【0055】

次いで、第1の実施の形態の半導体装置の製造方法について、説明する。

図6〜図17は、第1の実施の形態の半導体装置の製造方法の工程手順を示す図である。図6〜図17において、WLはワード線の長手方向の断面部分を示し、BLはビット線の長手方向の断面部分を示す。これらの図は、説明しやすいように、1つの図面中に、多方向の断面図が含まれているものである。

【0056】

本実施の形態の半導体装置の製造方法は、以下の工程を含む。まず、基板(半導体基板1)に、ゲート電極32及び第1拡散層を備える第1トランジスタ(能動素子3a)を形成する。続いて、能動素子3a上に層間絶縁層(コンタクト層間絶縁膜4)を形成する。続いて、ゲート電極32上のコンタクト層間絶縁膜4に、ゲート電極32と同一方向に延在する配線溝(裏打ち配線溝42)を形成するとともに、第1拡散層上のコンタクト層間絶縁膜4に、コンタクトを埋設するための第1コンタクト孔(コンタクト孔44)を形成する。裏打ち配線溝42及びコンタクト孔44に同じ金属層(ゲート裏打ち配線30、及びセルコンタクト10a)を埋設する。コンタクト層間絶縁膜4上に絶縁層(層間絶縁膜7b、7c)を形成する。絶縁層内に、容量素子19を埋設する。

以下、詳細に説明する。

【0057】

まず、図6に示すように、半導体基板1の表面に素子分離膜2を形成する。素子分離膜2で区画された素子領域に能動素子3a、3b等のトランジスタを形成する。トランジスタはゲート電極と拡散層を有する。ゲート電極は、通常用いられるポリシリコン電極や部分的に金属シリサイド化されたポリシリコン電極を用いても良いし、メタルゲート電極を用いても良い。メタルゲート電極の形成方法として、ゲートファースト方式やゲートラスト方式等がある。また、拡散層上にシリサイド層20が形成されていてもよい。シリサイド層20には、例えば、コバルト、ニッケル、プラチナなどの金属とシリコンとの合金が形成されている。

【0058】

能動素子3a、3bの上にコンタクト層間絶縁膜4を形成する。コンタクト層間絶縁膜4を選択的に除去することにより、複数の開口部を形成する。たとえば、コンタクト層間絶縁膜4上にフォトレジストを塗布法等により形成し、所望のパターンをフォトリソグラフィ法により転写して、フォトレジストに開口部を形成する。フォトレジストをマスクとして、反応性イオンエッチング等の方法により、コンタクト層間絶縁膜4に開口部を形成する。その後、フォトレジストを除去する。

ここで、コンタクト層間絶縁膜4に開口部を形成する方法の詳細を説明する。

【0059】

本実施の形態では、同一層のフォトレジストに複数の開口部を形成する手法として、たとえば、ダブルパターニング方法を使用することができる。ダブルパターニング方法の一例を説明する。まず、1回目の露光により、トランジスタの拡散層上のフォトレジストにコンタクト孔のパターンを形成する。2回目の露光により、ゲート電極32上のフォトレジストに裏打ち配線溝のパターンを形成する。

【0060】

順番を分けてパターニングすることにより、コンタクト孔44と裏打ち配線溝42との距離が短い場合でも、露光光が干渉して解像度が低下することを抑制することができる。すなわち、ダブルパターニング方法により、互いに隣接したコンタクト孔44及び裏打ち配線溝42のパターンが精度良く得られる。なお、裏打ち配線溝42のパターン形成の順番が先でもよい。

【0061】

ダブルパターニング方法の露光には、たとえば、液浸ArF(弗化アルゴンレーザー)露光や、EUV(Extreme Ultra Violet)露光、EB(Electron Beam)露光等が用いられる。本実施の形態では、露光の波長を短くし、さらに、隣接するパターンの露光順番を異ならせることにより、コンタクト孔44と裏打ち配線溝42との距離を短くすることができる。

【0062】

ダブルパターニング方法により得られたマスクを用いて、エッチングなどにより、コンタクト層間絶縁膜4に複数の開口部を形成する。すなわち、コンタクト層間絶縁膜4に、裏打ち配線溝42、コンタクト孔41、43、44、及びビットコンタクト孔45が形成される。その後、フォトレジストを除去する。

【0063】

記憶回路領域に位置するコンタクト孔44、43は、論理回路領域に位置するコンタクト孔41(コンタクトを埋設するための第2コンタクト孔)と同時に形成されてもよい。コンタクト孔41は、第2トランジスタ(能動素子3b)の第2拡散層上の層間絶縁層に形成される。また、これらのコンタクト孔41、43、44と同時に、ビットコンタクト孔45が形成されてもよい。

【0064】

続いて、図7に示すように、コンタクト層間絶縁膜4上に金属膜50を堆積する。これにより、コンタクト層間絶縁膜4に形成された複数の開口部に同一の金属膜が埋設される。たとえば、記憶回路領域に位置するコンタクト孔44と裏打ち配線溝42とが同一の金属膜で埋設される。また、論理回路領域に位置するコンタクト孔41と裏打ち配線溝42とが同一の金属膜で埋設される。金属膜50の形成方法としては、CVD(Chemical Vapor Deposition)法、スパッタリング法、ALD(Atomic Layer Deposition)法等、通常半導体装置の形成に用いられる手法が用いられる。本実施の形態では、金属膜50としてWを用いる場合を説明する。

【0065】

続いて、図8に示すように、余剰の金属膜50をCMP(Chemical Mechanical Polishing)法により除去する。これにより、コンタクト層間絶縁膜4に、セルコンタクト10a、10b、ゲート裏打ち配線30、ビットコンタクト36が同時に形成される。

【0066】

続いて、図9に示すように、コンタクト層間絶縁膜4上に、コンタクト層間絶縁膜5、キャップ膜6a、及び層間絶縁膜7aを形成する。

【0067】

続いて、図10に示すように、これらの層に、フォトリソグラフィ法及びエッチングを用いて、ビット線溝46、配線溝47、及びコンタクト孔48が形成される。これらの開口部に対応するフォトレジストのパターンの形成には、一括露光方法を用いてもよいが、前述のダブルパターニング方法を用いてもよい。一括露光方法には、たとえば、ArF露光を用いることができる。また、ダブルパターニング方法には、液浸ArF露光を含むArF露光、EUV露光、EB露光などが用いられる。

【0068】

ビット線溝46の底面に、ビットコンタクト36の上面、及びセルコンタクト10cの上面が露出されている。配線溝47の底面に、セルコンタクト10bの上面が露出される。コンタクト孔48の底面に、セルコンタクト10aの上面が露出される。これらのビット線溝46、配線溝47、コンタクト孔48は、同時に形成されてもよいが、異なるタイミングで形成されてもよい。

【0069】

続いて、図11に示すように、これらの開口部にバリアメタル膜及び金属膜52を堆積する。続いて、図12に示すように、余剰の金属膜をCMPにより除去する。これにより、ビット線34、配線8a、及び容量コンタクト13aが形成される。以上のようにして、配線8aと同一工程でビット線34又は、容量コンタクト13aが形成される。なお、本実施の形態では、金属膜52がCuである場合について説明する。

【0070】

本実施の形態では、論理回路の配線を利用して、記憶回路領域にビット線34を形成することができる。このため、記憶回路領域には、配線と同じ高さのビット線34が形成されることになる。これにより、配線形成にCMPを実施したとしても、ビット線34の周辺の層間絶縁膜7aの平坦性を確保することが可能となる。

【0071】

続いて、図13に示すように、層間絶縁膜7a上にキャップ膜6bを形成する。キャップ膜6bにより、ビット線34、配線8a、及び容量コンタクト13aの上面が覆われる。

【0072】

続いて、図14に示すように、キャップ膜6b上にフォトレジスト54を形成する。フォトレジスト54に孔55を形成する。

【0073】

続いて、図15に示すように、エッチング等により、ビア孔57を形成する。フォトレジスト54を除去した後、キャップ膜6a上に金属膜56を形成する。金属膜56はビア孔57に埋設される。本実施の形態では、金属膜56として、たとえば、Wを用いた例を説明する。金属膜56は、たとえば、CVD法により堆積される。

【0074】

続いて、図16に示すように、フォトリソグラフィ法、反応性イオンエッチング法等により、容量コンタクト13bの先端に突出部を形成する。以後の工程で形成される容量素子19の直下の位置に、容量コンタクト13の突出部が形成されることが好ましい。

【0075】

以後の配線及び容量素子の形成工程は、たとえば、特開2011−54920号公報に記載の手法に沿って行うことができる。

すなわち、引き続いて、キャップ膜6b上に層間絶縁膜7bを形成する。層間絶縁膜7bに、通常用いられるダマシン法により、配線8bを形成する。

【0076】

本実施の形態では、記憶回路領域のキャップ膜6b上には容量コンタクト13の突出部が配列されている。突出部の高さ分だけ、層間絶縁膜7bが盛り上がることになる。このため、配線8bの形成過程において、層間絶縁膜7bがCMPされるとき、記憶回路領域の層間絶縁膜7bは平坦性が低下することが抑制される。これにより、容量のバラツキが抑制され得る。

【0077】

引き続き、少なくとも配線8bの上面を覆うようにキャップ膜6cを堆積する。キャップ膜6c上に層間絶縁膜7cを堆積させる。層間絶縁膜7c上に、ハードマスクとなる絶縁膜を堆積する。ハードマスクは、層間絶縁膜7b、7cを加工する際、層間絶縁膜7b、7cに対して高い選択比を有する絶縁膜が好ましく、例えば、シリコン酸化膜が好ましい。ハードマスク上に、フォトレジストを堆積する。フォトレジストに、フォトリソグラフィ法等の方法により、上部接続配線溝のパターンを形成する。フォトレジストは単一層のフォトレジスト、平坦化有機膜、シリコン酸化膜、反射防止膜、感光性レジスト等の多層フォトレジスト層のいずれかを用いても良い。

【0078】

次いで、フォトレジストをマスクとして、層間絶縁膜7cに、上部接続配線溝を形成する。例えば、反応性イオンエッチング等の微細加工方法を用いることができる。エッチング条件(選択比など)を適切に調節することにより、上部接続配線溝の高さを制御することができる。その後、フォトレジストを除去する。

【0079】

続いて、上部接続配線溝内の層間絶縁膜7c上及びハードマスク上に、多層レジスト層を形成する。多層レジスト層に、フォトリソグラフィ法等の方法により、容量素子埋設用凹部のパターンを形成する。

【0080】

続いて、多層レジスト層をマスクとして、反応性イオンエッチング等の微細加工方法により、層間絶縁膜7b、キャップ膜6c、層間絶縁膜7c内に、容量素子埋設用凹部を形成する。多層レジスト層は、容量素子埋設用凹部の加工中にアッシングを行って除去する。本実施の形態では、容量素子埋設用凹部の底部において、容量コンタクト13bの突出部の少なくとも上面及び側壁が露出している。

【0081】

なお、本実施の形態では、上部接続配線溝を後に容量素子埋設用凹部を形成したが、上部接続配線溝を形成する前に容量素子埋設用凹部を形成してもよい。

【0082】

続いて、少なくとも上部接続配線溝及び容量素子埋設用凹部の底部上及び側壁上に、下部電極14を堆積する。下部電極14を形成する方法としては、CVD法、スパッタリング法、ALD法等、通常半導体装置の形成に用いられる手法を用いれば良い。引き続き、塗布法等により、フォトレジストを、容量素子埋設用凹部内に埋設する。フォトレジストは、容量素子埋設用凹部内にのみ残存し、かつ、容量素子埋設用凹部の上端に達していない高さで形成されていることが好ましく、必要であれば、フォトレジストに対して露光・現像処理を行うことで、不要なフォトレジストを除去しておいても良い。この後、下部電極14を、例えば反応性イオンエッチング法等の方法により、エッチバックする。これにより、容量素子埋設用凹部の上端部に達しない下部電極14を形成することができる。その後、フォトレジストを除去する。

【0083】

続いて、下部電極14の上に、容量絶縁膜15及び上部電極16を堆積する。容量絶縁膜15及び上部電極16は、少なくとも容量素子埋設用凹部の底面上、側壁上および上部接続配線溝の底面上、側壁上に形成される。容量絶縁膜15を形成する方法としては、CVD法、スパッタリング法、ALD法等、通常半導体装置の形成に用いられる手法を用いることができる。また、容量素子の静電容量を向上させるために、数nmの薄膜を均一性良く堆積することができるALD法がより好ましい。なお、容量絶縁膜15を堆積した後、結晶性を向上させるための焼結工程を行っても良い。

【0084】

次いで、例えば塗布法により、フォトレジストを、容量素子埋設用凹部の内部及び上部接続配線溝の内部に形成する。レジストは、論理回路領域に残存したハードマスク上部に残存しないように形成する。必要であれば、フォトレジストに対して露光・現像処理を行うか、あるいは、全面エッチバックを行うことで、論理回路領域に形成された不要なフォトレジストを除去しておく。

【0085】

次いで、上部電極16及び容量絶縁膜15を、反応性イオンエッチング等の方法により、エッチバックする。これにより、ハードマスク上の上部電極16及び容量絶縁膜15を除去できる。続いて、フォトレジストを、アッシング等により除去する。

【0086】

次いで、導電性を有するハードマスク31を、容量素子埋設用凹部の底面上、側壁上および上部接続配線溝の底面上、側壁上に堆積する。ハードマスク31には、例えば、チタン及びチタンの窒化物、タンタル及びタンタルの窒化物、ルテニウム等の、高融点金属及びそれらの窒化物、或いはそれらの積層構造体を用いても良い。ハードマスク31を形成する方法としては、CVD法、スパッタリング法、ALD法等、通常半導体装置の形成に用いられる手法を用いれば良い。ハードマスク31の厚さとしては、後に行う論理回路配線加工を行うのに十分な厚さを有していることが好ましい。ただし、ハードマスク31は、容量素子19の上部電極として残存することがあるため、低い電気抵抗を有することが好ましい。すなわち、容量素子埋設用凹部内部に残存したハードマスク31は上部電極として機能する。従って、ハードマスク31の厚さは、後述する論理回路配線加工後に消失する程度の厚さに設定しても良い。すなわち、ハードマスク31の材料は、上部電極16と同種の材料を用いることができる。ハードマスク31と上部電極16とは、同種の材料で形成されても、異なる材料で形成されてもよいが、同一の材料であることがより好ましい。

【0087】

次いで、論理回路領域に配線8cを埋設するための配線溝を形成する。なお、配線形成工程において、その開口部を形成した後、反応性イオンエッチング等によりハードマスク31を除去しても良い。この方法を用いることにより、容量素子19内に残存するハードマスク31の厚さを薄くして、容量素子の上部電極の抵抗値を低くすることができる。

【0088】

次に、容量素子埋設用凹部、上部接続配線溝及び配線溝にバリアメタル膜17及び導電膜を埋設する。導電膜は、Cu、W、Alを含む金属で構成されてもよいが、このなかでも、Cuを含む材料で構成されることが好ましい。次いで、CMP法などの方法により、導電膜、バリアメタル膜、ハードマスクを除去する。これにより、容量素子19、上部接続配線18、及び配線8cが形成される。上部接続配線18と配線8cとは同一工程で形成されることが好ましいが、別工程で形成されてもよい。すなわち、上部接続配線18は、配線8cの金属膜と同一の材料で構成されてもよいが、異なる材料で構成されてもよい。なお、本実施の形態では、容量素子埋設用凹部形成後に、配線溝を形成したが、この順番に限定されずに、配線溝に金属膜を埋設した後に、容量素子埋設用凹部を形成してもよい。

【0089】

次いで、図17に示すように、上部接続配線18の上面上及び配線8cの上面上にキャップ膜6dを形成する。この後、キャップ膜6d上に、層間絶縁膜7d、キャップ膜6e、層間絶縁膜7e、キャップ膜6fを形成する。また、各絶縁膜に、配線8d、8e、固定電位を有する配線201a、201b、信号配線202a、202b、及び電源・グラウンド配線203を形成する。

以上により、第1の実施の形態の半導体装置が得られる。

【0090】

(第2の実施の形態)

次いで、第2の実施の形態の半導体装置について説明する。

図18は、第2の実施の形態の半導体装置を模式的に示す断面図である。

第2の実施の形態は、容量素子19の下端と、キャップ膜6bとの間に層間絶縁膜7bが形成されている点を除いて、第1の実施の形態と同様である。

以下、詳細に説明する。

【0091】

容量素子19の下端は、少なくとも容量コンタクト13の上面に接していることが好ましい。たとえば、容量素子19の下端は、同一層に位置する配線8cのうち配線部分の下端と同じ位置としてもよい。言い換えると、容量素子埋設用凹部の底面は、同一層の配線層の配線溝の底面と同一面を構成してもよい。また、容量素子埋設用凹部の底面の周囲にストッパ膜が形成されていてもよい。これらにより、容量素子埋設用凹部の底部の位置の制御が容易となる。

【0092】

第2の実施の形態では、容量素子19の下端とビット線34との間の距離を、容量素子19の下端がキャップ膜6bに接している場合と比較して、増加させることが可能となる。これにより、容量素子19とビット線34との間の寄生容量の増加を抑制することができる。

【0093】

第2の実施の形態の半導体装置の製造方法は、以下の工程を有する点が、第1の実施の形態と異なる。すなわち、まず、層間絶縁層(コンタクト層間絶縁膜4)上にキャップ層(キャップ膜6a)を形成する。次いで、キャップ膜6a上に絶縁層(層間絶縁膜7b)を形成する。次いで、層間絶縁膜7bに、キャップ膜6aに到達しない凹部(容量素子埋設用凹部)を形成する。この後、当該凹部に容量素子19を埋設する。

【0094】

凹部の形成工程において、容量素子埋設用凹部の底部には、少なくとも容量コンタクト13bの上面が露出している。一方、容量素子埋設用凹部の底部には、層間絶縁膜7bの下地層が露出していない。下地層は、たとえば、キャップ膜6aである。容量素子埋設用凹部の深さは、エッチング条件や、層間絶縁膜7bの中間にストッパ膜を形成することにより制御することができる。

(第3の実施の形態)

次いで、第3の実施の形態の半導体装置について説明する。

図19は、第3の実施の形態の半導体装置を模式的に示す断面図である。

第3の実施の形態は、ビット線34bの同一層の論理回路領域にコンタクト層が形成されている点を除いて、第1の実施の形態と同様である。

以下、詳細に説明する。

【0095】

論理回路領域には、コンタクト層間絶縁膜4と第1配線層(最下層配線層)との間に、コンタクト層が形成されている。コンタクト層は、コンタクト層間絶縁膜5中に埋設されたセルコンタクト10dを有する。セルコンタクト10dは、第1配線(配線8a)と、セルコンタクト10bとを電気的に接続する。セルコンタクト10bは、論理回路領域のトランジスタ(能動素子3b)の拡散層に接続している。

【0096】

一方、記憶回路領域には、コンタクト層と同一層に、ビット線34bが形成されている。ビット線34bは、Wを含む金属で構成されているのが好ましい。ビット線34bの材料は、配線8a(たとえば、Cu配線)とは異なるものである。ビット線34bの上面は、配線8aの上面より低く形成されている。言い換えると、ビット線34bの上端とキャップ膜6aとは、互いに離間されており、その間にはコンタクト層間絶縁膜5bが配置されている。本実施の形態では、ビット線34bは、例えば、エッチングにより加工されて形成され得るものである。

【0097】

本実施の形態では、容量素子19の下端とビット線34bとの間の距離を、第1の実施の形態よりも確保することができるので、その間の寄生容量の増大を抑制することができる。

また、ゲート裏打ち配線30は、ワード線(ゲート電極32)と接しつつ、同層に形成されているので、ワード線の抵抗を低減させつつ、容量素子19の上層の配線層の設計の自由度を高めることが可能となる。

【0098】

なお、当然ながら、上述した複数の実施の形態は、その内容が相反しない範囲で組み合わせることができる。また、上述した実施の形態では、各部の構造などを具体的に説明したが、その構造などは本願発明を満足する範囲で各種に変更することができる。

【符号の説明】

【0099】

1 半導体基板

2 素子分離膜

3a、3b 能動素子

4 コンタクト層間絶縁膜

5、5a、5b コンタクト層間絶縁膜

6a、6b、6c、6d、6e、6f キャップ膜

7a、7b、7c、7d、7e 層間絶縁膜

8a、8b、8c、8d、8e 配線

10a、10b、10c、10d セルコンタクト

13、13a、13b 容量コンタクト

14 下部電極

15 容量絶縁膜

16 上部電極

17 バリアメタル膜

18 上部接続配線

18a 引出配線部

18b 埋設電極

19 容量素子

20 シリサイド層

30 ゲート裏打ち配線

31 ハードマスク

32 ゲート電極

34、34bビット線

35 配線

36 ビットコンタクト

41 コンタクト孔

42 裏打ち配線溝

43 コンタクト孔

44 コンタクト孔

45 ビットコンタクト孔

46 ビット線溝

47 配線溝

48 コンタクト孔

50 金属膜

52 金属膜

54 フォトレジスト

55 孔

56 金属膜

57 ビア孔

58 フォトレジスト

59 孔

100 論理回路

110 半導体基板

200 記憶回路

201a、201b 固定電位を有する配線

202 グローバルビット配線

202a、202b 信号配線

203 電源・グラウンド配線

210 容量素子

220 周辺回路

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に設けられた層間絶縁層と、

前記基板に設けられており、前記層間絶縁層内に埋め込まれた第1トランジスタと、

前記層間絶縁層上に設けられた多層配線層と、

前記多層配線層内に設けられた容量素子と、

前記第1トランジスタを構成するゲート電極及び拡散層と、

前記ゲート電極の上面と接しており、前記ゲート電極と同一方向に延在しており、かつ前記層間絶縁層内に埋設された金属配線と、

前記第1トランジスタの拡散層に接続しており、前記層間絶縁層内に埋設された第1コンタクトと、を備え、

前記金属配線は、前記第1コンタクトと同じ材料で構成されている、

半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記基板に設けられており、前記第1トランジスタを含む記憶回路領域とは異なる領域である論理回路領域に位置する第2トランジスタと、

前記第2トランジスタと第1配線とを接続する第2コンタクトと、を備えており、

前記第1配線は、前記多層配線層のうち最下層の配線層に位置しており、

前記第2コンタクトは、前記金属配線と同じ材料で構成されている、

半導体装置。

【請求項3】

請求項1または2に記載の半導体装置において、

前記金属配線は、Wを含む材料で構成されている、半導体装置。

【請求項4】

請求項2に記載の半導体装置において、

前記記憶回路領域に位置し、前記第1配線と同一層に設けられており、前記第1トランジスタの前記拡散層に接続するビット線を備える、半導体装置。

【請求項5】

請求項4に記載の半導体装置において、

前記ビット線は、前記第1配線と同じ材料で構成されている、半導体装置。

【請求項6】

請求項1から5のいずれか1項に記載の半導体装置において、

前記第1トランジスタと前記容量素子とを接続する容量コンタクトを備えており、

前記容量素子の下部電極は、前記容量コンタクトの上面及び側壁の少なくとも上部を覆う半導体装置。

【請求項7】

請求項6に記載の半導体装置において、

前記容量コンタクトは、層間方向に配列された、少なくとも3つ以上のコンタクトを有する、半導体装置。

【請求項8】

基板に、ゲート電極及び第1拡散層を備える第1トランジスタを形成する工程と、

前記第1トランジスタ上に層間絶縁層を形成する工程と、

前記ゲート電極上の前記層間絶縁層に、前記ゲート電極と同一方向に延在する配線溝を形成するとともに、前記第1拡散層上の前記層間絶縁層に、コンタクトを埋設するための第1コンタクト孔を形成する工程と、

前記配線溝及び第1コンタクト孔に同じ金属層を埋設する工程と、

前記層間絶縁層上に絶縁層を形成する工程と、

前記絶縁層内に、容量素子を埋設する工程と、を有する、

半導体装置の製造方法。

【請求項9】

請求項8に記載の半導体装置の製造方法において、

前記第1トランジスタを含む記憶回路領域とは異なる領域である論理回路領域に位置する前記基板に、第2拡散層を備える第2トランジスタを形成する工程と、

前記第2トランジスタ上に前記層間絶縁層を形成する工程と、

前記第2拡散層上の前記層間絶縁層にコンタクトを埋設するための第2コンタクト孔を形成する工程と、

前記第2コンタクト孔及び前記配線溝に同じ金属層を埋設する工程と、を有する、

半導体装置の製造方法。

【請求項10】

請求項9に記載の半導体装置の製造方法において、

前記層間絶縁層上に、前記絶縁層の最下層に位置する第1絶縁層を形成する工程と、

前記第1絶縁層に、前記配線溝内の金属層に達するビット線用配線溝を形成するとともに、前記第2コンタクト孔内の金属層に達する第1配線溝を形成する工程と、

前記ビット線用配線溝及び前記第1配線溝に同じ金属層を埋設する工程と、

前記第1絶縁層上の第2絶縁層内に、前記容量素子を埋設する工程と、を有する半導体装置の製造方法。

【請求項11】

請求項8から10のいずれか1項に記載の半導体装置の製造方法において、

前記層間絶縁層上にキャップ層を形成する工程と、

前記キャップ層上に前記絶縁層を形成する工程と、

前記絶縁層に、前記キャップ層に到達しない凹部を形成する工程と、

前記凹部に前記容量素子を埋設する工程と、を有する、半導体装置の製造方法。

【請求項1】

基板と、

前記基板上に設けられた層間絶縁層と、

前記基板に設けられており、前記層間絶縁層内に埋め込まれた第1トランジスタと、

前記層間絶縁層上に設けられた多層配線層と、

前記多層配線層内に設けられた容量素子と、

前記第1トランジスタを構成するゲート電極及び拡散層と、

前記ゲート電極の上面と接しており、前記ゲート電極と同一方向に延在しており、かつ前記層間絶縁層内に埋設された金属配線と、

前記第1トランジスタの拡散層に接続しており、前記層間絶縁層内に埋設された第1コンタクトと、を備え、

前記金属配線は、前記第1コンタクトと同じ材料で構成されている、

半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記基板に設けられており、前記第1トランジスタを含む記憶回路領域とは異なる領域である論理回路領域に位置する第2トランジスタと、

前記第2トランジスタと第1配線とを接続する第2コンタクトと、を備えており、

前記第1配線は、前記多層配線層のうち最下層の配線層に位置しており、

前記第2コンタクトは、前記金属配線と同じ材料で構成されている、

半導体装置。

【請求項3】

請求項1または2に記載の半導体装置において、

前記金属配線は、Wを含む材料で構成されている、半導体装置。

【請求項4】

請求項2に記載の半導体装置において、

前記記憶回路領域に位置し、前記第1配線と同一層に設けられており、前記第1トランジスタの前記拡散層に接続するビット線を備える、半導体装置。

【請求項5】

請求項4に記載の半導体装置において、

前記ビット線は、前記第1配線と同じ材料で構成されている、半導体装置。

【請求項6】

請求項1から5のいずれか1項に記載の半導体装置において、

前記第1トランジスタと前記容量素子とを接続する容量コンタクトを備えており、

前記容量素子の下部電極は、前記容量コンタクトの上面及び側壁の少なくとも上部を覆う半導体装置。

【請求項7】

請求項6に記載の半導体装置において、

前記容量コンタクトは、層間方向に配列された、少なくとも3つ以上のコンタクトを有する、半導体装置。

【請求項8】

基板に、ゲート電極及び第1拡散層を備える第1トランジスタを形成する工程と、

前記第1トランジスタ上に層間絶縁層を形成する工程と、

前記ゲート電極上の前記層間絶縁層に、前記ゲート電極と同一方向に延在する配線溝を形成するとともに、前記第1拡散層上の前記層間絶縁層に、コンタクトを埋設するための第1コンタクト孔を形成する工程と、

前記配線溝及び第1コンタクト孔に同じ金属層を埋設する工程と、

前記層間絶縁層上に絶縁層を形成する工程と、

前記絶縁層内に、容量素子を埋設する工程と、を有する、

半導体装置の製造方法。

【請求項9】

請求項8に記載の半導体装置の製造方法において、

前記第1トランジスタを含む記憶回路領域とは異なる領域である論理回路領域に位置する前記基板に、第2拡散層を備える第2トランジスタを形成する工程と、

前記第2トランジスタ上に前記層間絶縁層を形成する工程と、

前記第2拡散層上の前記層間絶縁層にコンタクトを埋設するための第2コンタクト孔を形成する工程と、

前記第2コンタクト孔及び前記配線溝に同じ金属層を埋設する工程と、を有する、

半導体装置の製造方法。

【請求項10】

請求項9に記載の半導体装置の製造方法において、

前記層間絶縁層上に、前記絶縁層の最下層に位置する第1絶縁層を形成する工程と、

前記第1絶縁層に、前記配線溝内の金属層に達するビット線用配線溝を形成するとともに、前記第2コンタクト孔内の金属層に達する第1配線溝を形成する工程と、

前記ビット線用配線溝及び前記第1配線溝に同じ金属層を埋設する工程と、

前記第1絶縁層上の第2絶縁層内に、前記容量素子を埋設する工程と、を有する半導体装置の製造方法。

【請求項11】

請求項8から10のいずれか1項に記載の半導体装置の製造方法において、

前記層間絶縁層上にキャップ層を形成する工程と、

前記キャップ層上に前記絶縁層を形成する工程と、

前記絶縁層に、前記キャップ層に到達しない凹部を形成する工程と、

前記凹部に前記容量素子を埋設する工程と、を有する、半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−89712(P2013−89712A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−227650(P2011−227650)

【出願日】平成23年10月17日(2011.10.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月17日(2011.10.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]