半導体装置及び地上波デジタル放送受信装置

【課題】CPUの負荷にかかわらず、レシーブデータレジスタ内のデータが上書きされて壊れてしまうのを回避する。

【解決手段】半導体装置はカードインタフェース(39)を含む。このカードインタフェースは、ボーレートジェネレータ(313)と、変換回路(302)と、レシーブデータレジスタ(303)とを含む。さらに上記半導体装置(3)は、レシーブデータレジスタにパラレルデータが存在しない場合には、ボーレートジェネレータからICカードへクロック信号を供給し、レシーブデータレジスタにパラレルデータが存在する場合には、ボーレートジェネレータからICカードへのクロック信号の供給を停止するためのクロック制御回路(310)を含む。上記ICカードへのクロック信号の供給を停止することで、新たなデータがICカード(7)からレシーブデータレジスタ(301)に伝達されるのを回避する。

【解決手段】半導体装置はカードインタフェース(39)を含む。このカードインタフェースは、ボーレートジェネレータ(313)と、変換回路(302)と、レシーブデータレジスタ(303)とを含む。さらに上記半導体装置(3)は、レシーブデータレジスタにパラレルデータが存在しない場合には、ボーレートジェネレータからICカードへクロック信号を供給し、レシーブデータレジスタにパラレルデータが存在する場合には、ボーレートジェネレータからICカードへのクロック信号の供給を停止するためのクロック制御回路(310)を含む。上記ICカードへのクロック信号の供給を停止することで、新たなデータがICカード(7)からレシーブデータレジスタ(301)に伝達されるのを回避する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、さらにはそれにおけるインタフェース技術に関し、例えば携帯端末用に設計された地上デジタル放送受信装置(携帯端末向け地上デジタル放送受信装置)に適用して有効な技術に関する。

【背景技術】

【0002】

特許文献1には、SIM(Subscriber Identity Module)からのシリアルデータ受信時にCPUが直ちにデータリード処理に移行できない場合でも正しい受信データの読込みを可能とするシリアルインタフェース回路が記載されている。このシリアルインタフェース回路は、シリアル受信データSRの1フレーム分の受信毎にCPU3に対し割込信号ISを発生する割込信号発生部14と、割込信号発生時のフレームカウント値FNをCPU3が読出せるよう保持する受信ナンバレジタ12とを含む。

【0003】

特許文献2には、受信データブロック中にデータ長を表すデータを付加し、該データによりDMAバイト長を制御させることにより、受信データを認識するシリアルデータ受信装置が記載されている。このシリアルデータ受信装置では、シリアルに受信するデータブロック内の先頭フラグを検出することにより、ブロック受信動作を開始し、その後に続くデータ長を表すデータを抽出してDMAのバイトカウンタのカウント数として利用する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9−200297号公報

【特許文献2】特開平4−259151号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

地上波デジタル放送には、MPEG2−TS(Transport Stream)が使用される。MPEG2−TSは、映像や音声などのPES(Packetized Elementary Stream)や、セクションと呼ばれるデータが格納される。日本のデジタル放送では著作権保護を目的として映像や音声にスクランブル(暗号化)処理が施されている。映像や音声をデスクランブル(復号化)するためのデスクランブル鍵(Ks)は放送局側で暗号化され、ECM(Entitlement Control Message)セクションとして送られる。ECMセクションは受信機側に接続されているICカード内のセキュリティモジュールによって復号化されデスクランブル鍵として取得できる。携帯端末用に設計された地上デジタル放送受信装置においては、製造コストとの関係で、ICカードアクセス専用のマイクロコンピュータを搭載することが困難であるため、映像や音声のデコード処理制御や出力制御のためのCPUを使ってICカードのアクセスを行うようにしている。

【0006】

このような携帯端末向け地上デジタル放送受信装置において、ICカードからのデータ転送は常に一定間隔で行われる。これに対してCPUは、ICカードのアクセスの他に、映像や音声のデコード処理制御や出力制御を行うことから、CPUがSIMカードインタフェースからデータを読み出すタイミングは必ずしも一定間隔で発生するとは限らない。このため、レシーブデータレジスタ内の1バイト(8ビット)分のデータを、メモリインタフェースを介してメモリに書き込む処理が完了する前に、レシーブデータレジスタの出力データが、シリアル・パラレル変換回路を介してレシーブデータレジスタに伝達されるおそれがあり、かかる場合には、レシーブデータレジスタ内のデータが上書きされて壊れてしまう。

【0007】

本発明の目的は、CPUの負荷にかかわらず、レシーブデータレジスタ内のデータが上書きされて壊れてしまうのを回避するための技術を提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェースを含んで半導体装置を構成する。上記カードインタフェースは、上記ICカードに供給される上記クロック信号を生成するためのボーレートジェネレータと、上記ICカードから伝達されたシリアルデータをパラレルデータに変換するための変換回路と、上記変換回路から出力されたパラレルデータを保持するためのレシーブデータレジスタとを含む。さらに上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在しない場合には、上記ボーレートジェネレータから上記ICカードへ上記クロック信号を供給し、上記レシーブデータレジスタに上記パラレルデータが存在する場合には、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止するためのクロック制御回路を含む。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、CPUの負荷にかかわらず、レシーブデータレジスタ内のデータが上書きされて壊れてしまうのを回避することができる。

【図面の簡単な説明】

【0013】

【図1】本発明にかかるモバイル端末向け地上波デジタル放送受信装置の構成例ブロック図である。

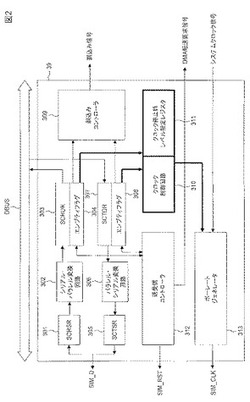

【図2】図1に示されるモバイル端末向け地上波デジタル放送受信装置におけるSIMカードインタフェースの構成例ブロック図である。

【図3】図1及び図2に示される構成における主要部の信号の流れの説明図である。

【図4】図1及び図2に示される構成の比較対象とされる構成における主要部の信号の流れの説明図である。

【図5】図1に示されるモバイル端末向け地上波デジタル放送受信装置におけるDMACの構成例ブロック図である。

【図6】本発明にかかるモバイル端末向け地上波デジタル放送受信装置においてDMACを用いたデータ転送を示すブロック図である。

【図7】図6に示されるモバイル端末向け地上波デジタル放送受信装置における主要部の信号の流れの説明図である。

【図8】ICカードに対するコマンドやICカードからのレスポンスのフォーマットについての説明図である。

【図9】従来技術に従ったDMA転送設定に関するフローチャートである。

【図10】図5に示される構成を採用した場合における主要部の信号の流れの説明図である。

【発明を実施するための形態】

【0014】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0015】

〔1〕本発明の代表的な実施の形態に係る半導体装置(3)は、供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェース(39)を含む。

【0016】

上記カードインタフェースは、上記ICカードに供給される上記クロック信号を生成するためのボーレートジェネレータ(313)と、上記ICカードから伝達されたシリアルデータをパラレルデータに変換するための変換回路(302)と、上記変換回路から出力されたパラレルデータを保持するためのレシーブデータレジスタ(303)とを含む。さらに上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在しない場合には、上記ボーレートジェネレータから上記ICカードへ上記クロック信号を供給し、上記レシーブデータレジスタに上記パラレルデータが存在する場合には、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止するためのクロック制御回路(310)を含む。

【0017】

上記の構成によれば、クロック制御回路310が設けられ、このクロック制御回路310によって、エンプティフラグ304内のエンプティフラグがモニタされ、レシーブデータレジスタ(303)にデータが存在する場合には、クロック制御回路(310)の制御によって、ICカード(7)へのクロック信号の供給が停止される。これによりICカード(7)の動作が停止されるので、新たなデータがICカード(7)からレシーブデータレジスタ(301)に伝達されることはない。これにより、レシーブデータレジスタ(303)内の未転送データが上書きによって壊れてしまうのを回避することができる。

【0018】

〔2〕上記〔1〕において、上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在するか否かの判別を可能とするエンプティフラグ(304)を含み、上記クロック制御回路は、上記エンプティフラグの論理に基づいて、上記レシーブデータレジスタに上記パラレルデータが存在するか否かを判別するように構成することができる。

【0019】

〔3〕上記〔2〕において、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止する際の上記クロック信号の論理を指定するためのレベル指定レジスタ(311)を設けることができる。これにより、クロック信号の供給を停止する際のクロック信号の論理を任意に設定することができる。

【0020】

〔4〕上記〔3〕において、上記半導体装置は、上記レシーブデータレジスタ内のデータを別の記憶媒体(3801)にDMA転送するためのDMAコントローラ(38)を含んで構成することができる。

【0021】

〔5〕上記〔4〕において、上記DMAコントローラによってDMA転送されるデータには、データ長フィールドと、情報フィールドと、最終フィールドとが含まれる。このとき、上記DMAコントローラには、DMA転送における転送回数が設定される転送数指定レジスタ(3809)と、上記データ長フィールドの位置を示すデータ長オフセットレジスタ(3811)と、上記最終フィールドの長さを示す最終データ長レジスタ(3812)とを設けることができる。さらに上記DMAコントローラには、データ長オフセットレジスタの出力に対応するデータ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路(3803)と、その算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路(3802)とを設けることができる。そして上記回数制御回路によって再設定された回数分のDMA転送が行われる。

【0022】

〔6〕上記〔1〕における半導体装置を含んで地上デジタル放送受信装置を構成することができる。モバイル端末用に設計された地上デジタル放送受信装置においては、ICカードアクセス専用のマイクロコンピュータを搭載することが困難であるため、映像や音声のデコード処理制御や出力制御のためのCPUを使ってICカードのアクセスを行うようにしているため、上記〔1〕の作用効果は顕著とされる。

【0023】

〔7〕本発明の代表的な実施の形態に係る半導体装置(3)は、供給されたクロック信号に基づいて所定のデータ処理を行うICカード(7)との間でシリアル通信を行うためのカードインタフェース(39)と、上記カードインタフェースを介して取り込まれたデータを別の記憶媒体(3801)にDMA転送するためのDMAコントローラ(38)とを含む。上記DMAコントローラによってDMA転送されるデータは、データ長フィールド(LEN)と、情報フィールド(INF)と、最終フィールド(EDC)とを含む。上記DMAコントローラは、DMA転送における転送回数が設定される転送数指定レジスタ(3809)と、上記データ長フィールドの位置を示すデータ長オフセットレジスタ(3811)と、上記最終フィールドの長さを示す最終データ長レジスタ(3812)とを含む。さらに上記DMAコントローラは、データ長オフセットレジスタの出力に対応するデータ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路(3803)と、その算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路(3802)とを含む。上記回数制御回路によって再設定された回数分のDMA転送が行われる。

【0024】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0025】

《実施の形態1》

図1には、本発明にかかるモバイル端末向け地上波デジタル放送受信装置の構成例が示される。図1に示されるモバイル端末向け地上波デジタル放送受信装置10は、チューナ2、地上波デジタル放送受信用チップ3、LCD(Liquid Crystal Display;液晶ディスプレイ)4、スピーカ5、メモリ6、及びICカード7を含む。地上波デジタル放送には、MPEG2−TS(Transport Stream)が使用される。チューナ2は、アンテナ1を介してMPEG2−TSを受信する。地上波デジタル放送受信用チップ3は、チューナ2による受信信号を処理する。地上波デジタル放送受信用チップ3での処理結果は、LCD4で画像表示される。また、音声はスピーカ5から出力される。メモリ6は、音声や映像などのES(Elementary Stream)を記憶するのに用いられる。ICカード(integrated circuit card;アイシーカード)7は、接触型ICカードであり、このモバイル端末向け地上波デジタル放送受信装置10に装着される。

【0026】

地上波デジタル放送では著作権保護を目的として映像や音声にスクランブル(暗号化)処理が施されている。映像や音声をデスクランブル(復号化)するためのデスクランブル鍵(Ks)は放送局側で暗号化され、ECMCM(Entitlement Control Message)セクションとして送られる。ECMセクションは、ICカード7内のセキュリティモジュールによって復号化され、デスクランブル鍵として取得できる。

【0027】

地上波デジタル放送受信用チップ3は、公知の半導体集積回路製造技術により、単結晶シリコン基板などの一つの半導体基板上に形成され、以下のような複数のモジュールを含む。すなわち、MSTIF(Multi Stream Interface)31、EMUX(Stream Mux/Demux Unit;MUX/DEMUXユニット)32、CPU(Central Processing Unit)33、LCD制御部34が設けられる。また、音声出力制御部35、MPEG(Moving Picture Experts Group)デコーダ36、メモリインタフェース37、DMAC(Direct Memory Access Controller;DMAコントローラ)38、SIM(Subscriber Identity Module)カードインタフェース39が設けられる。上記複数のモジュールは、データバスDBUSを介して互いに信号のやり取りが可能に結合されている。

【0028】

MSTIF31は、MPEG2−TSをデスクランブル処理する。EMUX32は、MPEG2−TSをPESやセクションなどに分離する。CPU33は、予め設定されたプログラムを実行することによって各部の動作を制御する。LCD制御部34は、LCD4へ画像表示を制御する。音声出力制御部35は、音声信号に基づいてスピーカ5を駆動する。MPEGデコーダ36は、映像や音声をデコードする。メモリインタフェース37は、地上波デジタル放送受信用チップ3とメモリ6との間のデータのやり取りを可能にする。DMAC38は、CPU33を介さずにモジュール間のデータ転送を制御する。SIMカードインタフェース39は、地上波デジタル放送受信用チップ3とICカード7との間のデータ転送を制御する。

尚、本例においては、太線矢印で示されるように、SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33の制御で行うものとする。

【0029】

図2には、SIMカードインタフェース39の構成例が示される。

【0030】

図2に示されるSIMカードインタフェース39は、レシーブシフトレジスタ(SCRSR)301、シリアル・パラレル変換回路302、レシーブデータレジスタ(SCRDR)303、トランスミットシフトレジスタ(SCTSR)305、パラレル・シリアル変換回路306、トランスミットデータレジスタ(SCTDR)307を含む。さらにSIMカードインタフェース39は、割込みコントローラ309、クロック制御回路310、クロック停止時のレベル指定レジスタ311、送受信コントローラ312、ボーレートジェネレータ313を含む。

【0031】

レシーブシフトレジスタ(SCRSR)301は、データ端子SIM_Dを介してICカード7から伝達されたシリアルデータを保持する。シリアル・パラレル変換回路302は、レシーブシフトレジスタ(SCRSR)301から出力されたシリアルデータをパラレルデータに変換して出力する。レシーブデータレジスタ(SCRDR)303は、シリアル・パラレル変換回路302から出力されたパラレルデータを保持する。エンプティフラグ304は、レシーブデータレジスタ(SCRDR)303のデータ保持状態を示す。エンプティフラグ304が論理値‘0’の場合、レシーブデータレジスタ(SCRDR)303にパラレルデータが存在することを意味する。エンプティフラグ304が論理値‘1’の場合、レシーブデータレジスタ(SCRDR)303にパラレルデータが存在しないことを意味する。トランスミットデータレジスタ(SCTDR)307は、データバスDBUSを介してCPU33から伝達されたパラレルデータを保持する。エンプティフラグ308は、トランスミットデータレジスタ(SCTDR)307のデータ保持状態を示すエンプティフラグを保持する。このエンプティフラグ308が論理値‘0’の場合、トランスミットデータレジスタ(SCTDR)307にパラレルデータが存在することを意味する。エンプティフラグ308が論理値‘1’の場合、トランスミットデータレジスタ(SCTDR)307にパラレルデータが存在しないことを意味する。パラレル・シリアル変換回路306は、トランスミットデータレジスタ(SCTDR)307の出力データ(パラレルデータ)をシリアルデータに変換する。トランスミットシフトレジスタ(SCTSR)305は、パラレル・シリアル変換回路306の出力データ(シリアルデータ)を取り込み、それを、データ端子SIM_Dを介してICカード7に送信する。割込みコントローラ309は、エンプティフラグ304が論理値‘0’の場合や、エンプティフラグ308が論理値‘0’の場合に、CPU33に対する割込み信号をアサートする。CPU33は、エンプティフラグ304が論理値‘0’の場合の割込み処理において、レシーブデータレジスタ(SCRDR)303のデータを読出す。このとき、エンプティフラグ304が論理値‘1’にされる。また、CPU33は、エンプティフラグ308が論理値‘0’の場合の割込み処理において、トランスミットデータレジスタ(SCTDR)307に次の8ビット分のデータを書込む。このとき、エンプティフラグ308のエンプティフラグを論理値‘0’にされる。送受信コントローラ312は、ICカード7との間で行われる送受信を制御する。また、後述するように、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38で行う場合には、送受信コントローラ312によってDMA転送要求信号がアサートされるようになっている。ICカード7のリセットは、送受信コントローラ312によりリセット端子SIM_RSTを介して行われる。ボーレートジェネレータ313は、地上波デジタル放送受信用チップ3におけるシステムクロック信号を分周して、ICカード7の動作用クロック信号を形成する。このICカード7の動作用クロック信号は、クロック端子SIM_CLKを介してICカード7に供給される。ICカード7は、伝達されたクロック信号に同期して所定の信号処理(ECMセクションの復号化処理)が行われる。クロック制御回路310は、エンプティフラグ304に基づいて、ボーレートジェネレータ313からICカード7への動作用クロック信号の供給を制御する。すなわち、エンプティフラグ304が論理値‘1’の場合、ボーレートジェネレータ313からICカード7へ動作用クロック信号を供給させ、エンプティフラグレジの動作用クロック信号の供給を停止する。ボーレートジェネレータ313からICカード7への動作用クロック信号の供給を、クロック信号のハイレベルで停止するか、ローレベルで停止するかは、クロック停止時レベル指定レジスタ311に設定することができる。クロック停止時レベル指定レジスタ311への情報設定は、CPU33によって行うことができる。

【0032】

次に、上記のように構成されたモバイル端末向け地上波デジタル放送受信装置10における主要動作を説明する。

【0033】

図3には、CPU33とSIMカードインタフェース39とICカード7との間の信号の流れが示される。

【0034】

送受信コントローラ312によってICカード7がリセットされ、ICカード7から所定の応答信号(ATR)がレシーブシフトレジスタ(SCRSR)301に取り込まれ、それがシリアル・パラレル変換回路302でパラレルデータに変換された後にレシーブデータレジスタ(SCRDR)303に書き込まれる。このとき、エンプティフラグ304が論理値‘0’にされる。すると、割込みコントローラ309は割込み信号をアサートすることで、CPU33に対する割込み要求を発生する。CPU33は、割込みコントローラ309からの割り込み要求に応じた割込み処理により、レシーブデータレジスタ(SCRDR)303内の応答信号(ATR)を取り込む。これにより、CPU33は、ICカード7に対するコマンド発行が可能になる。

【0035】

CPU33は、メモリ6に蓄積されているコマンドデータを1バイト単位に読み出して、それをSIMカードインタフェース39内のトランスミットデータレジスタ(SCTDR)307に書き込む(ステップ1)。SIMカードインタフェース39では、トランスミットデータレジスタ(SCTDR)307のデータがパラレル・シリアル変換回路306でシリアルデータに変換された後に、トランスミットシフトレジスタ(SCTSR)305に伝達されて、ICカード7に送信される(ステップ2)。

【0036】

上記ステップ1,2は、コマンドデータサイズの分だけ繰り返される。コマンド送信が完了すると、ICカード7内で、上記コマンドに応じた復号処理が行われる。そしてICカード7は、SIMカードインタフェース39に対しレスポンス応答を送信する(ステップ3)。SIMカードインタフェース39は、レシーブシフトレジスタ(SCRSR)301に、8ビット分のデータが書き込まれた場合、レシーブシフトレジスタ(SCRSR)301内の8ビット分のデータが、シリアル・パラレル変換回路302でパラレルデータに変換されてからレシーブデータレジスタ(SCRDR)303に書き込まれる(ステップ4)。このとき、エンプティフラグ304が論理値‘0’にされる。エンプティフラグが論理値‘0’にされると、クロック制御回路310の制御によって、ICカード7へのクロック信号の供給が停止される。クロック信号の供給停止は、クロック停止時レベル指定レジスタ311によって指定された論理レベルで行われる。例えばクロック停止時レベル指定レジスタ311に、ローレベル(論理値‘0’)が設定されていた場合、クロック信号の供給停止は、クロック信号がローレベルのときに行われる。クロック信号が供給されない場合には、ICカード7の内部動作が停止される。また、エンプティフラグ304が論理値‘0’にされると、割込みコントローラ309によってCPU33に対する割込み信号がアサートされる。この割込み信号に応じてCPU33は、レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータを、メモリインタフェース37を介してメモリ6に書き込む(ステップ5)。レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータがメモリ6に書き込まれた時点で、エンプティフラグ304が論理値‘1’にされる。これにより、クロック制御回路310は、ICカード7へのクロック信号の供給を再開する。このクロック信号の供給は、クロック停止時レベル指定レジスタ311によって指定された論理レベルから再開される。

【0037】

上記ステップ3〜5の処理は、レスポンスデータサイズの分だけ繰り返される。

【0038】

ここで、従来技術に従えば、クロック制御回路310によるクロック制御は行われない。この場合、図4に示されるように、ICカード7からのデータ転送は常に一定間隔で行われる。これに対してCPU33は、ICカード7のアクセスの他に、映像や音声のデコード処理制御や出力制御を行うことから、CPU33がSIMカードインタフェース39からデータを読み出すタイミングは必ずしも一定間隔で発生するとは限らない。このため、レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータを、メモリインタフェース37を介してメモリ6に書き込む処理が完了する前に、レシーブデータレジスタ(SCRDR)301の出力データが、シリアル・パラレル変換回路302を介してレシーブデータレジスタ(SCRDR)303に伝達されるおそれがある。かかる場合には、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまう。

【0039】

これに対して図2に示される構成によれば、クロック制御回路310が設けられ、このクロック制御回路310によって、エンプティフラグ304内のエンプティフラグがモニタされ、エンプティフラグ304が論理値‘0’の場合(レシーブデータレジスタ(SCRDR)303にデータが存在する場合)には、クロック制御回路310の制御によって、ICカード7へのクロック信号の供給が停止される。これによりICカード7の動作が停止されるので、新たなデータがICカード7からレシーブデータレジスタ(SCRDR)301に伝達されることはないので、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまうのを回避することができる。

【0040】

《実施の形態2》

実施の形態1では、SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33で制御するようにしたが、図6において太線矢印で示されるように、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御によって行うことができる。SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33で制御するか、DMAC38で制御するかは、CPU33の初期設定で決定される。SIMカードインタフェース39の基本的な動作は、実施の形態1で説明した通りであるが、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御する場合、送受信コントローラ312からDMAC38に対するDMA転送要求信号が有効とされる。このとき、割込みコントローラ309の機能は停止される。

【0041】

図5には、DMAC38の構成例が示される。

【0042】

図5に示されるDMAC38は、内部メモリ3801、回数制御回路3802、データ長算出回路3803、レジスタ制御回路3804、起動制御回路3805、要求優先制御回路3806を含む。さらにDMAC38は、転送元アドレス指定レジスタ(SAR)3807、転送先アドレス指定レジスタ(DAR)3808、転送数指定レジスタ(TCR)3809、転送モード指定レジスタ(CHCR)3810、データ長オフセットレジスタ3811、及び最終データ長レジスタ3812を含む。

【0043】

内部メモリ3801は、データバスDBUS及びデータ長算出回路3803に結合される。データバスDBUSを介して内部メモリ3801にデータを書き込むことができる。また、内部メモリ3801内のデータをデータバスDBUSに出力することができる。データ算出回路3803は、内部メモリ3801内のデータを参照してデータ長を算出する。転送元アドレス指定レジスタ(SAR)3807には、DMA転送における転送元アドレスが保持される。転送先アドレス指定レジスタ(DAR)3808には、DMA転送における転送先アドレスが保持される。転送数指定レジスタ(TCR)3809には、DMA転送における転送数が保持される。この転送数指定レジスタ(TCR)3809に設定された回数だけ、DMA転送が行われる。転送モード指定レジスタ(CHCR)3810には、DMA転送における転送モードが保持される。データ長オフセットレジスタ3811には、データ長フィールドのオフセット情報が保持される。最終データ長レジスタ3812には、最終フィールドの長さ情報が保持される。データ長算出回路3803は、DMA転送すべきデータの長さを算出する。つまりデータ長算出回路3803は、データ長オフセットレジスタ3811の出力に対応する上記データ長フィールド(LEN)の値によって上記情報フィールドの長さを把握し、それに上記最終データ長レジスタ3812の出力を加算することによって、DMA転送すべきデータの長さを算出する。回数制御回路3802は、データ長算出回路3803での算出結果に基づいて転送数指定レジスタ(TCR)3809における転送回数を再設定する。レジスタ制御回路3804は、上記各レジスタの動作を制御する。起動制御回路3805は、転送モード指定レジスタ(CHCR)3810に保持された転送モードに従ってDMAC38の起動を制御する。要求優先制御回路3806は、複数のDMA転送要求信号がアサートされた場合に、予め設定された優先度に従って、複数のDMA転送要求を処理する。この要求優先制御回路3806によって、DMA転送アクノリッジ信号やCPU33に対する割込み信号が形成される。

【0044】

図7には、DMA転送処理の流れが示される。

【0045】

CPU33は、DMAC33に対しコマンド送信のためのデータサイズ設定を行う。DMAC33は、SIMカードインタフェース39内のトランスミットデータレジスタ(SCTDR)307に1バイトデータを書き込む。トランスミットデータレジスタ(SCTDR)307のデータは、パラレル・シリアル変換回路306でシリアルデータに変換された後にトランスミットシフトレジスタ(SCTSR)305に伝達されてICカード7に送信される。トランスミットデータレジスタ(SCTDR)307が空になった場合、エンプティフラグ308が論理値“1”にされ、送受信コントローラ312によってDMA転送要求信号がアサートされることで、DMAC33に対し転送要求が行われる。DMAC33はSIMカードインタフェース39に対し1バイトデータを書き込む。

【0046】

以上の処理が繰り返されることによって、ICカード7へのデータ転送が行われる。

【0047】

ICカード7内では、SIMカードインタフェース39から転送されたデータの復号処理が行われる。また、この復号処理と平行して、DMAC33に対してデータ受信のためのデータサイズの設定が行われる。

【0048】

ICカード7は1ビット単位でレシーブシフトレジスタ(SCRSR)301にデータを送信する。レシーブシフトレジスタ(SCRSR)301に8ビット分のデータが書き込まれた場合、それが、シリアル・パラレル変換回路302でパラレルデータに変換されてからレシーブデータレジスタ(SCRDR)303に書き込まれる。そしてエンプティフラグ304が論理値“0”にされる。これにより、DMA転送要求信号がアサートされ、DMAC33に対し転送要求が行われる。DMAC33はSIMカードインタフェース39から1バイトデータを読み出し、それを内部メモリ3801に転送する。そしてエンプティフラグ304におけるエンプティフラグが論理値“1”にされる。また、SIMカードインタフェース39から1バイトデータが内部メモリ3801に転送された場合、CPU33に対する割込み信号をアサートする。これにより、CPU33は、内部メモリ3801内のデータを、メモリインタフェース37を介してメモリ6に転送する。このような処理が繰り返される。

【0049】

図8には、ICカード7に対するコマンドやICカード7からのレスポンスのフォーマットが示される。

【0050】

ICカード7に対するコマンドやICカード7からのレスポンスは、先頭フィールドと、情報フィールド、及び最終フィールドとを含む。先頭フィールドは、ノードアドレス(NAD)、プロトコル制御バイト(PCB)、送受信データの長さ(LEN)を含む。ノードアドレス(NAD)、プロトコル制御バイト(PCB)、長さ(LEN)は、それぞれ1バイトである。情報フィールドは、送受信データ(INF)であり、0〜254バイトの範囲で設定される。この送受信データ(INF)の長さは、先頭フィードにおける長さ(LEN)に反映される。つまり、先頭フィードにおける長さ(LEN)を見れば、情報フィールドにおける送受信データの長さを把握することができる。最終フィールドは、誤り検出符号(EDC)が割り当てられる。誤り検出符号(EDC)は1バイトである。

【0051】

SIMカードインタフェース39を介してやり取りされる送受信データ(INF)は、長さ(LEN)で示される可変サイズとなる。しかし、DMAC38へのデータサイズ指定は固定長となるため、データサイズの再設定等が必要とされる。

【0052】

ここで従来技術に従えば、図9(A)に示されるように、CPUによってデータサイズの再設定が行われる。

【0053】

先ず、CPUはDMACのデータサイズを3バイトとして設定する。次に3バイト受信後にDMA転送完了割込みが通知されたCPUは、3バイト目の長さ(LEN)のサイズから残りのデータサイズを算出してDMACのデータサイズを再設定する。しかしこの手法の場合、DMA転送中にCPUに割込みを行うため、CPUの処理負荷によってはデータ受信が正常に行えない可能性がある。つまり、レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータを、メモリインタフェース37を介してメモリ6に書き込む処理が完了する前に、レシーブデータレジスタ(SCRDR)301の出力データが、シリアル・パラレル変換回路302を介してレシーブデータレジスタ(SCRDR)303に伝達されるおそれがある。かかる場合には、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまう。

【0054】

また、図9(B)に示されるように、CPUによってDMACのデータサイズをレスポンス最大長(例えば258バイト)に設定し、レスポンスデータがなくなった場合に、CPUに対してタイムアウトエラー割込みを発生させ、それをトリガとしてCPUに受信データの処理を実行させることが考えられるが、その場合、タイムアウト発生まのでオーバーヘッドが発生するおそれがある。

【0055】

これに対して、図5に示される構成によれば、図10に示されるように、DMA転送設定により、データ長オフセットレジスタ3811には、データ長フィールドのオフセット情報が保持される。最終データ長レジスタ3812には、最終フィールドの長さ情報が保持される。データ長フィールド(LEN)のオフセット情報は、図8に示される例の場合、3バイト目とされる。つまり、先頭フィールドの3バイト目にデータ長フィールド(LEN)が存在し、それに基づいて、情報フィールドである送受信データ(INF)の長さの把握が可能になる。データ長算出回路3803は、SIMカードインタフェース39から内部メモリ3801に転送されたデータの先頭から3バイト目の情報(LEN)に基づいて、上記情報フィールドの長さを把握し、それに上記最終データ長レジスタ3812の出力を加算することによって、DMA転送すべきデータの長さ(残りのバイト)を算出する。尚、最終フィールドが存在しない場合には、最終データ長レジスタ3812の出力は0バイトとなる。回数制御回路3802は、データ長算出回路3803での算出結果に基づいて、転送数指定レジスタ(TCR)3809における転送回数を再設定する。これにより、DMAC38では、再設定された転送回数に応じたDMA転送制御が行われる。このように図5に示される構成によれば、DMAC38内の演算処理により転送回数の再設定が行われるようになっているので、CPU33の処理負荷にかかわらず、データの受信を正常に行うことができる。これにより、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまうのを回避することができる。また、図5に示される構成によれば、CPUによってDMACのデータサイズをレスポンス最大長(例えば258バイト)に設定し、レスポンスデータがなくなった場合に、CPUに対してタイムアウトエラー割込みを発生させる方式ではないので、タイムアウト発生まのでオーバーヘッドが発生するおそれも無い。

【0056】

さらに、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御によって行う場合でも、クロック制御回路310によって、エンプティフラグ304内のエンプティフラグがモニタされ、エンプティフラグが論理値‘0’の場合(レシーブデータレジスタ(SCRDR)303にデータが存在する場合)には、クロック制御回路310の制御によって、ICカード7へのクロック信号の供給が停止される。これにより、新たなデータがICカード7からレシーブデータレジスタ(SCRDR)301に伝達されることはない。

【0057】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0058】

例えば、図6において太線矢印で示されるように、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御によって行う場合には、SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33で制御する場合に比べてCPU33の負荷が軽減されることから、図2におけるクロック制御回路310やクロック停止時のレベル指定レジスタ311を省略しても良い。

【符号の説明】

【0059】

1 アンテナ

2 チューナ

3 地上波デジタル放送受信用チップ

4 LCD

5 スピーカ

6 メモリ

7 ICカード

10 モバイル端末向け地上波デジタル放送受信装置

31 MSTIF

32 EMUX

33 CPU

34 LCD制御部

35 音声出力制御部

36 デコーダ

37 メモリインタフェース

38 DMAC

39 SIMカードインタフェース

301 レシーブシフトレジスタ(SCRSR)

302 シリアル・パラレル変換回路

303 レシーブデータレジスタ(SCRDR)

304 エンプティフラグ

305 トランスミットシフトレジスタ(SCTSR)

306 パラレル・シリアル変換回路

307 トランスミットデータレジスタ(SCTDR)

308 エンプティフラグ

309 割込みコントローラ

310 クロック制御回路

311 クロック停止時のレベル指定レジスタ

312 送受信コントローラ

313 ボーレートジェネレータ

3801 内部メモリ

3802 回数制御回路

3803 データ長算出回路

3804 レジスタ制御回路

3805 起動制御回路

3806 要求優先制御回路

3807 転送元アドレス指定レジスタ(SAR)

3808 転送先アドレス指定レジスタ(DAR)

3809 転送数指定レジスタ(TCR)

3810 転送モード指定レジスタ(CHCR)

3811 データ長オフセットレジスタ

3812 最終データ長レジスタ

【技術分野】

【0001】

本発明は、半導体装置、さらにはそれにおけるインタフェース技術に関し、例えば携帯端末用に設計された地上デジタル放送受信装置(携帯端末向け地上デジタル放送受信装置)に適用して有効な技術に関する。

【背景技術】

【0002】

特許文献1には、SIM(Subscriber Identity Module)からのシリアルデータ受信時にCPUが直ちにデータリード処理に移行できない場合でも正しい受信データの読込みを可能とするシリアルインタフェース回路が記載されている。このシリアルインタフェース回路は、シリアル受信データSRの1フレーム分の受信毎にCPU3に対し割込信号ISを発生する割込信号発生部14と、割込信号発生時のフレームカウント値FNをCPU3が読出せるよう保持する受信ナンバレジタ12とを含む。

【0003】

特許文献2には、受信データブロック中にデータ長を表すデータを付加し、該データによりDMAバイト長を制御させることにより、受信データを認識するシリアルデータ受信装置が記載されている。このシリアルデータ受信装置では、シリアルに受信するデータブロック内の先頭フラグを検出することにより、ブロック受信動作を開始し、その後に続くデータ長を表すデータを抽出してDMAのバイトカウンタのカウント数として利用する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9−200297号公報

【特許文献2】特開平4−259151号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

地上波デジタル放送には、MPEG2−TS(Transport Stream)が使用される。MPEG2−TSは、映像や音声などのPES(Packetized Elementary Stream)や、セクションと呼ばれるデータが格納される。日本のデジタル放送では著作権保護を目的として映像や音声にスクランブル(暗号化)処理が施されている。映像や音声をデスクランブル(復号化)するためのデスクランブル鍵(Ks)は放送局側で暗号化され、ECM(Entitlement Control Message)セクションとして送られる。ECMセクションは受信機側に接続されているICカード内のセキュリティモジュールによって復号化されデスクランブル鍵として取得できる。携帯端末用に設計された地上デジタル放送受信装置においては、製造コストとの関係で、ICカードアクセス専用のマイクロコンピュータを搭載することが困難であるため、映像や音声のデコード処理制御や出力制御のためのCPUを使ってICカードのアクセスを行うようにしている。

【0006】

このような携帯端末向け地上デジタル放送受信装置において、ICカードからのデータ転送は常に一定間隔で行われる。これに対してCPUは、ICカードのアクセスの他に、映像や音声のデコード処理制御や出力制御を行うことから、CPUがSIMカードインタフェースからデータを読み出すタイミングは必ずしも一定間隔で発生するとは限らない。このため、レシーブデータレジスタ内の1バイト(8ビット)分のデータを、メモリインタフェースを介してメモリに書き込む処理が完了する前に、レシーブデータレジスタの出力データが、シリアル・パラレル変換回路を介してレシーブデータレジスタに伝達されるおそれがあり、かかる場合には、レシーブデータレジスタ内のデータが上書きされて壊れてしまう。

【0007】

本発明の目的は、CPUの負荷にかかわらず、レシーブデータレジスタ内のデータが上書きされて壊れてしまうのを回避するための技術を提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェースを含んで半導体装置を構成する。上記カードインタフェースは、上記ICカードに供給される上記クロック信号を生成するためのボーレートジェネレータと、上記ICカードから伝達されたシリアルデータをパラレルデータに変換するための変換回路と、上記変換回路から出力されたパラレルデータを保持するためのレシーブデータレジスタとを含む。さらに上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在しない場合には、上記ボーレートジェネレータから上記ICカードへ上記クロック信号を供給し、上記レシーブデータレジスタに上記パラレルデータが存在する場合には、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止するためのクロック制御回路を含む。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、CPUの負荷にかかわらず、レシーブデータレジスタ内のデータが上書きされて壊れてしまうのを回避することができる。

【図面の簡単な説明】

【0013】

【図1】本発明にかかるモバイル端末向け地上波デジタル放送受信装置の構成例ブロック図である。

【図2】図1に示されるモバイル端末向け地上波デジタル放送受信装置におけるSIMカードインタフェースの構成例ブロック図である。

【図3】図1及び図2に示される構成における主要部の信号の流れの説明図である。

【図4】図1及び図2に示される構成の比較対象とされる構成における主要部の信号の流れの説明図である。

【図5】図1に示されるモバイル端末向け地上波デジタル放送受信装置におけるDMACの構成例ブロック図である。

【図6】本発明にかかるモバイル端末向け地上波デジタル放送受信装置においてDMACを用いたデータ転送を示すブロック図である。

【図7】図6に示されるモバイル端末向け地上波デジタル放送受信装置における主要部の信号の流れの説明図である。

【図8】ICカードに対するコマンドやICカードからのレスポンスのフォーマットについての説明図である。

【図9】従来技術に従ったDMA転送設定に関するフローチャートである。

【図10】図5に示される構成を採用した場合における主要部の信号の流れの説明図である。

【発明を実施するための形態】

【0014】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0015】

〔1〕本発明の代表的な実施の形態に係る半導体装置(3)は、供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェース(39)を含む。

【0016】

上記カードインタフェースは、上記ICカードに供給される上記クロック信号を生成するためのボーレートジェネレータ(313)と、上記ICカードから伝達されたシリアルデータをパラレルデータに変換するための変換回路(302)と、上記変換回路から出力されたパラレルデータを保持するためのレシーブデータレジスタ(303)とを含む。さらに上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在しない場合には、上記ボーレートジェネレータから上記ICカードへ上記クロック信号を供給し、上記レシーブデータレジスタに上記パラレルデータが存在する場合には、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止するためのクロック制御回路(310)を含む。

【0017】

上記の構成によれば、クロック制御回路310が設けられ、このクロック制御回路310によって、エンプティフラグ304内のエンプティフラグがモニタされ、レシーブデータレジスタ(303)にデータが存在する場合には、クロック制御回路(310)の制御によって、ICカード(7)へのクロック信号の供給が停止される。これによりICカード(7)の動作が停止されるので、新たなデータがICカード(7)からレシーブデータレジスタ(301)に伝達されることはない。これにより、レシーブデータレジスタ(303)内の未転送データが上書きによって壊れてしまうのを回避することができる。

【0018】

〔2〕上記〔1〕において、上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在するか否かの判別を可能とするエンプティフラグ(304)を含み、上記クロック制御回路は、上記エンプティフラグの論理に基づいて、上記レシーブデータレジスタに上記パラレルデータが存在するか否かを判別するように構成することができる。

【0019】

〔3〕上記〔2〕において、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止する際の上記クロック信号の論理を指定するためのレベル指定レジスタ(311)を設けることができる。これにより、クロック信号の供給を停止する際のクロック信号の論理を任意に設定することができる。

【0020】

〔4〕上記〔3〕において、上記半導体装置は、上記レシーブデータレジスタ内のデータを別の記憶媒体(3801)にDMA転送するためのDMAコントローラ(38)を含んで構成することができる。

【0021】

〔5〕上記〔4〕において、上記DMAコントローラによってDMA転送されるデータには、データ長フィールドと、情報フィールドと、最終フィールドとが含まれる。このとき、上記DMAコントローラには、DMA転送における転送回数が設定される転送数指定レジスタ(3809)と、上記データ長フィールドの位置を示すデータ長オフセットレジスタ(3811)と、上記最終フィールドの長さを示す最終データ長レジスタ(3812)とを設けることができる。さらに上記DMAコントローラには、データ長オフセットレジスタの出力に対応するデータ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路(3803)と、その算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路(3802)とを設けることができる。そして上記回数制御回路によって再設定された回数分のDMA転送が行われる。

【0022】

〔6〕上記〔1〕における半導体装置を含んで地上デジタル放送受信装置を構成することができる。モバイル端末用に設計された地上デジタル放送受信装置においては、ICカードアクセス専用のマイクロコンピュータを搭載することが困難であるため、映像や音声のデコード処理制御や出力制御のためのCPUを使ってICカードのアクセスを行うようにしているため、上記〔1〕の作用効果は顕著とされる。

【0023】

〔7〕本発明の代表的な実施の形態に係る半導体装置(3)は、供給されたクロック信号に基づいて所定のデータ処理を行うICカード(7)との間でシリアル通信を行うためのカードインタフェース(39)と、上記カードインタフェースを介して取り込まれたデータを別の記憶媒体(3801)にDMA転送するためのDMAコントローラ(38)とを含む。上記DMAコントローラによってDMA転送されるデータは、データ長フィールド(LEN)と、情報フィールド(INF)と、最終フィールド(EDC)とを含む。上記DMAコントローラは、DMA転送における転送回数が設定される転送数指定レジスタ(3809)と、上記データ長フィールドの位置を示すデータ長オフセットレジスタ(3811)と、上記最終フィールドの長さを示す最終データ長レジスタ(3812)とを含む。さらに上記DMAコントローラは、データ長オフセットレジスタの出力に対応するデータ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路(3803)と、その算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路(3802)とを含む。上記回数制御回路によって再設定された回数分のDMA転送が行われる。

【0024】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0025】

《実施の形態1》

図1には、本発明にかかるモバイル端末向け地上波デジタル放送受信装置の構成例が示される。図1に示されるモバイル端末向け地上波デジタル放送受信装置10は、チューナ2、地上波デジタル放送受信用チップ3、LCD(Liquid Crystal Display;液晶ディスプレイ)4、スピーカ5、メモリ6、及びICカード7を含む。地上波デジタル放送には、MPEG2−TS(Transport Stream)が使用される。チューナ2は、アンテナ1を介してMPEG2−TSを受信する。地上波デジタル放送受信用チップ3は、チューナ2による受信信号を処理する。地上波デジタル放送受信用チップ3での処理結果は、LCD4で画像表示される。また、音声はスピーカ5から出力される。メモリ6は、音声や映像などのES(Elementary Stream)を記憶するのに用いられる。ICカード(integrated circuit card;アイシーカード)7は、接触型ICカードであり、このモバイル端末向け地上波デジタル放送受信装置10に装着される。

【0026】

地上波デジタル放送では著作権保護を目的として映像や音声にスクランブル(暗号化)処理が施されている。映像や音声をデスクランブル(復号化)するためのデスクランブル鍵(Ks)は放送局側で暗号化され、ECMCM(Entitlement Control Message)セクションとして送られる。ECMセクションは、ICカード7内のセキュリティモジュールによって復号化され、デスクランブル鍵として取得できる。

【0027】

地上波デジタル放送受信用チップ3は、公知の半導体集積回路製造技術により、単結晶シリコン基板などの一つの半導体基板上に形成され、以下のような複数のモジュールを含む。すなわち、MSTIF(Multi Stream Interface)31、EMUX(Stream Mux/Demux Unit;MUX/DEMUXユニット)32、CPU(Central Processing Unit)33、LCD制御部34が設けられる。また、音声出力制御部35、MPEG(Moving Picture Experts Group)デコーダ36、メモリインタフェース37、DMAC(Direct Memory Access Controller;DMAコントローラ)38、SIM(Subscriber Identity Module)カードインタフェース39が設けられる。上記複数のモジュールは、データバスDBUSを介して互いに信号のやり取りが可能に結合されている。

【0028】

MSTIF31は、MPEG2−TSをデスクランブル処理する。EMUX32は、MPEG2−TSをPESやセクションなどに分離する。CPU33は、予め設定されたプログラムを実行することによって各部の動作を制御する。LCD制御部34は、LCD4へ画像表示を制御する。音声出力制御部35は、音声信号に基づいてスピーカ5を駆動する。MPEGデコーダ36は、映像や音声をデコードする。メモリインタフェース37は、地上波デジタル放送受信用チップ3とメモリ6との間のデータのやり取りを可能にする。DMAC38は、CPU33を介さずにモジュール間のデータ転送を制御する。SIMカードインタフェース39は、地上波デジタル放送受信用チップ3とICカード7との間のデータ転送を制御する。

尚、本例においては、太線矢印で示されるように、SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33の制御で行うものとする。

【0029】

図2には、SIMカードインタフェース39の構成例が示される。

【0030】

図2に示されるSIMカードインタフェース39は、レシーブシフトレジスタ(SCRSR)301、シリアル・パラレル変換回路302、レシーブデータレジスタ(SCRDR)303、トランスミットシフトレジスタ(SCTSR)305、パラレル・シリアル変換回路306、トランスミットデータレジスタ(SCTDR)307を含む。さらにSIMカードインタフェース39は、割込みコントローラ309、クロック制御回路310、クロック停止時のレベル指定レジスタ311、送受信コントローラ312、ボーレートジェネレータ313を含む。

【0031】

レシーブシフトレジスタ(SCRSR)301は、データ端子SIM_Dを介してICカード7から伝達されたシリアルデータを保持する。シリアル・パラレル変換回路302は、レシーブシフトレジスタ(SCRSR)301から出力されたシリアルデータをパラレルデータに変換して出力する。レシーブデータレジスタ(SCRDR)303は、シリアル・パラレル変換回路302から出力されたパラレルデータを保持する。エンプティフラグ304は、レシーブデータレジスタ(SCRDR)303のデータ保持状態を示す。エンプティフラグ304が論理値‘0’の場合、レシーブデータレジスタ(SCRDR)303にパラレルデータが存在することを意味する。エンプティフラグ304が論理値‘1’の場合、レシーブデータレジスタ(SCRDR)303にパラレルデータが存在しないことを意味する。トランスミットデータレジスタ(SCTDR)307は、データバスDBUSを介してCPU33から伝達されたパラレルデータを保持する。エンプティフラグ308は、トランスミットデータレジスタ(SCTDR)307のデータ保持状態を示すエンプティフラグを保持する。このエンプティフラグ308が論理値‘0’の場合、トランスミットデータレジスタ(SCTDR)307にパラレルデータが存在することを意味する。エンプティフラグ308が論理値‘1’の場合、トランスミットデータレジスタ(SCTDR)307にパラレルデータが存在しないことを意味する。パラレル・シリアル変換回路306は、トランスミットデータレジスタ(SCTDR)307の出力データ(パラレルデータ)をシリアルデータに変換する。トランスミットシフトレジスタ(SCTSR)305は、パラレル・シリアル変換回路306の出力データ(シリアルデータ)を取り込み、それを、データ端子SIM_Dを介してICカード7に送信する。割込みコントローラ309は、エンプティフラグ304が論理値‘0’の場合や、エンプティフラグ308が論理値‘0’の場合に、CPU33に対する割込み信号をアサートする。CPU33は、エンプティフラグ304が論理値‘0’の場合の割込み処理において、レシーブデータレジスタ(SCRDR)303のデータを読出す。このとき、エンプティフラグ304が論理値‘1’にされる。また、CPU33は、エンプティフラグ308が論理値‘0’の場合の割込み処理において、トランスミットデータレジスタ(SCTDR)307に次の8ビット分のデータを書込む。このとき、エンプティフラグ308のエンプティフラグを論理値‘0’にされる。送受信コントローラ312は、ICカード7との間で行われる送受信を制御する。また、後述するように、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38で行う場合には、送受信コントローラ312によってDMA転送要求信号がアサートされるようになっている。ICカード7のリセットは、送受信コントローラ312によりリセット端子SIM_RSTを介して行われる。ボーレートジェネレータ313は、地上波デジタル放送受信用チップ3におけるシステムクロック信号を分周して、ICカード7の動作用クロック信号を形成する。このICカード7の動作用クロック信号は、クロック端子SIM_CLKを介してICカード7に供給される。ICカード7は、伝達されたクロック信号に同期して所定の信号処理(ECMセクションの復号化処理)が行われる。クロック制御回路310は、エンプティフラグ304に基づいて、ボーレートジェネレータ313からICカード7への動作用クロック信号の供給を制御する。すなわち、エンプティフラグ304が論理値‘1’の場合、ボーレートジェネレータ313からICカード7へ動作用クロック信号を供給させ、エンプティフラグレジの動作用クロック信号の供給を停止する。ボーレートジェネレータ313からICカード7への動作用クロック信号の供給を、クロック信号のハイレベルで停止するか、ローレベルで停止するかは、クロック停止時レベル指定レジスタ311に設定することができる。クロック停止時レベル指定レジスタ311への情報設定は、CPU33によって行うことができる。

【0032】

次に、上記のように構成されたモバイル端末向け地上波デジタル放送受信装置10における主要動作を説明する。

【0033】

図3には、CPU33とSIMカードインタフェース39とICカード7との間の信号の流れが示される。

【0034】

送受信コントローラ312によってICカード7がリセットされ、ICカード7から所定の応答信号(ATR)がレシーブシフトレジスタ(SCRSR)301に取り込まれ、それがシリアル・パラレル変換回路302でパラレルデータに変換された後にレシーブデータレジスタ(SCRDR)303に書き込まれる。このとき、エンプティフラグ304が論理値‘0’にされる。すると、割込みコントローラ309は割込み信号をアサートすることで、CPU33に対する割込み要求を発生する。CPU33は、割込みコントローラ309からの割り込み要求に応じた割込み処理により、レシーブデータレジスタ(SCRDR)303内の応答信号(ATR)を取り込む。これにより、CPU33は、ICカード7に対するコマンド発行が可能になる。

【0035】

CPU33は、メモリ6に蓄積されているコマンドデータを1バイト単位に読み出して、それをSIMカードインタフェース39内のトランスミットデータレジスタ(SCTDR)307に書き込む(ステップ1)。SIMカードインタフェース39では、トランスミットデータレジスタ(SCTDR)307のデータがパラレル・シリアル変換回路306でシリアルデータに変換された後に、トランスミットシフトレジスタ(SCTSR)305に伝達されて、ICカード7に送信される(ステップ2)。

【0036】

上記ステップ1,2は、コマンドデータサイズの分だけ繰り返される。コマンド送信が完了すると、ICカード7内で、上記コマンドに応じた復号処理が行われる。そしてICカード7は、SIMカードインタフェース39に対しレスポンス応答を送信する(ステップ3)。SIMカードインタフェース39は、レシーブシフトレジスタ(SCRSR)301に、8ビット分のデータが書き込まれた場合、レシーブシフトレジスタ(SCRSR)301内の8ビット分のデータが、シリアル・パラレル変換回路302でパラレルデータに変換されてからレシーブデータレジスタ(SCRDR)303に書き込まれる(ステップ4)。このとき、エンプティフラグ304が論理値‘0’にされる。エンプティフラグが論理値‘0’にされると、クロック制御回路310の制御によって、ICカード7へのクロック信号の供給が停止される。クロック信号の供給停止は、クロック停止時レベル指定レジスタ311によって指定された論理レベルで行われる。例えばクロック停止時レベル指定レジスタ311に、ローレベル(論理値‘0’)が設定されていた場合、クロック信号の供給停止は、クロック信号がローレベルのときに行われる。クロック信号が供給されない場合には、ICカード7の内部動作が停止される。また、エンプティフラグ304が論理値‘0’にされると、割込みコントローラ309によってCPU33に対する割込み信号がアサートされる。この割込み信号に応じてCPU33は、レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータを、メモリインタフェース37を介してメモリ6に書き込む(ステップ5)。レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータがメモリ6に書き込まれた時点で、エンプティフラグ304が論理値‘1’にされる。これにより、クロック制御回路310は、ICカード7へのクロック信号の供給を再開する。このクロック信号の供給は、クロック停止時レベル指定レジスタ311によって指定された論理レベルから再開される。

【0037】

上記ステップ3〜5の処理は、レスポンスデータサイズの分だけ繰り返される。

【0038】

ここで、従来技術に従えば、クロック制御回路310によるクロック制御は行われない。この場合、図4に示されるように、ICカード7からのデータ転送は常に一定間隔で行われる。これに対してCPU33は、ICカード7のアクセスの他に、映像や音声のデコード処理制御や出力制御を行うことから、CPU33がSIMカードインタフェース39からデータを読み出すタイミングは必ずしも一定間隔で発生するとは限らない。このため、レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータを、メモリインタフェース37を介してメモリ6に書き込む処理が完了する前に、レシーブデータレジスタ(SCRDR)301の出力データが、シリアル・パラレル変換回路302を介してレシーブデータレジスタ(SCRDR)303に伝達されるおそれがある。かかる場合には、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまう。

【0039】

これに対して図2に示される構成によれば、クロック制御回路310が設けられ、このクロック制御回路310によって、エンプティフラグ304内のエンプティフラグがモニタされ、エンプティフラグ304が論理値‘0’の場合(レシーブデータレジスタ(SCRDR)303にデータが存在する場合)には、クロック制御回路310の制御によって、ICカード7へのクロック信号の供給が停止される。これによりICカード7の動作が停止されるので、新たなデータがICカード7からレシーブデータレジスタ(SCRDR)301に伝達されることはないので、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまうのを回避することができる。

【0040】

《実施の形態2》

実施の形態1では、SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33で制御するようにしたが、図6において太線矢印で示されるように、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御によって行うことができる。SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33で制御するか、DMAC38で制御するかは、CPU33の初期設定で決定される。SIMカードインタフェース39の基本的な動作は、実施の形態1で説明した通りであるが、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御する場合、送受信コントローラ312からDMAC38に対するDMA転送要求信号が有効とされる。このとき、割込みコントローラ309の機能は停止される。

【0041】

図5には、DMAC38の構成例が示される。

【0042】

図5に示されるDMAC38は、内部メモリ3801、回数制御回路3802、データ長算出回路3803、レジスタ制御回路3804、起動制御回路3805、要求優先制御回路3806を含む。さらにDMAC38は、転送元アドレス指定レジスタ(SAR)3807、転送先アドレス指定レジスタ(DAR)3808、転送数指定レジスタ(TCR)3809、転送モード指定レジスタ(CHCR)3810、データ長オフセットレジスタ3811、及び最終データ長レジスタ3812を含む。

【0043】

内部メモリ3801は、データバスDBUS及びデータ長算出回路3803に結合される。データバスDBUSを介して内部メモリ3801にデータを書き込むことができる。また、内部メモリ3801内のデータをデータバスDBUSに出力することができる。データ算出回路3803は、内部メモリ3801内のデータを参照してデータ長を算出する。転送元アドレス指定レジスタ(SAR)3807には、DMA転送における転送元アドレスが保持される。転送先アドレス指定レジスタ(DAR)3808には、DMA転送における転送先アドレスが保持される。転送数指定レジスタ(TCR)3809には、DMA転送における転送数が保持される。この転送数指定レジスタ(TCR)3809に設定された回数だけ、DMA転送が行われる。転送モード指定レジスタ(CHCR)3810には、DMA転送における転送モードが保持される。データ長オフセットレジスタ3811には、データ長フィールドのオフセット情報が保持される。最終データ長レジスタ3812には、最終フィールドの長さ情報が保持される。データ長算出回路3803は、DMA転送すべきデータの長さを算出する。つまりデータ長算出回路3803は、データ長オフセットレジスタ3811の出力に対応する上記データ長フィールド(LEN)の値によって上記情報フィールドの長さを把握し、それに上記最終データ長レジスタ3812の出力を加算することによって、DMA転送すべきデータの長さを算出する。回数制御回路3802は、データ長算出回路3803での算出結果に基づいて転送数指定レジスタ(TCR)3809における転送回数を再設定する。レジスタ制御回路3804は、上記各レジスタの動作を制御する。起動制御回路3805は、転送モード指定レジスタ(CHCR)3810に保持された転送モードに従ってDMAC38の起動を制御する。要求優先制御回路3806は、複数のDMA転送要求信号がアサートされた場合に、予め設定された優先度に従って、複数のDMA転送要求を処理する。この要求優先制御回路3806によって、DMA転送アクノリッジ信号やCPU33に対する割込み信号が形成される。

【0044】

図7には、DMA転送処理の流れが示される。

【0045】

CPU33は、DMAC33に対しコマンド送信のためのデータサイズ設定を行う。DMAC33は、SIMカードインタフェース39内のトランスミットデータレジスタ(SCTDR)307に1バイトデータを書き込む。トランスミットデータレジスタ(SCTDR)307のデータは、パラレル・シリアル変換回路306でシリアルデータに変換された後にトランスミットシフトレジスタ(SCTSR)305に伝達されてICカード7に送信される。トランスミットデータレジスタ(SCTDR)307が空になった場合、エンプティフラグ308が論理値“1”にされ、送受信コントローラ312によってDMA転送要求信号がアサートされることで、DMAC33に対し転送要求が行われる。DMAC33はSIMカードインタフェース39に対し1バイトデータを書き込む。

【0046】

以上の処理が繰り返されることによって、ICカード7へのデータ転送が行われる。

【0047】

ICカード7内では、SIMカードインタフェース39から転送されたデータの復号処理が行われる。また、この復号処理と平行して、DMAC33に対してデータ受信のためのデータサイズの設定が行われる。

【0048】

ICカード7は1ビット単位でレシーブシフトレジスタ(SCRSR)301にデータを送信する。レシーブシフトレジスタ(SCRSR)301に8ビット分のデータが書き込まれた場合、それが、シリアル・パラレル変換回路302でパラレルデータに変換されてからレシーブデータレジスタ(SCRDR)303に書き込まれる。そしてエンプティフラグ304が論理値“0”にされる。これにより、DMA転送要求信号がアサートされ、DMAC33に対し転送要求が行われる。DMAC33はSIMカードインタフェース39から1バイトデータを読み出し、それを内部メモリ3801に転送する。そしてエンプティフラグ304におけるエンプティフラグが論理値“1”にされる。また、SIMカードインタフェース39から1バイトデータが内部メモリ3801に転送された場合、CPU33に対する割込み信号をアサートする。これにより、CPU33は、内部メモリ3801内のデータを、メモリインタフェース37を介してメモリ6に転送する。このような処理が繰り返される。

【0049】

図8には、ICカード7に対するコマンドやICカード7からのレスポンスのフォーマットが示される。

【0050】

ICカード7に対するコマンドやICカード7からのレスポンスは、先頭フィールドと、情報フィールド、及び最終フィールドとを含む。先頭フィールドは、ノードアドレス(NAD)、プロトコル制御バイト(PCB)、送受信データの長さ(LEN)を含む。ノードアドレス(NAD)、プロトコル制御バイト(PCB)、長さ(LEN)は、それぞれ1バイトである。情報フィールドは、送受信データ(INF)であり、0〜254バイトの範囲で設定される。この送受信データ(INF)の長さは、先頭フィードにおける長さ(LEN)に反映される。つまり、先頭フィードにおける長さ(LEN)を見れば、情報フィールドにおける送受信データの長さを把握することができる。最終フィールドは、誤り検出符号(EDC)が割り当てられる。誤り検出符号(EDC)は1バイトである。

【0051】

SIMカードインタフェース39を介してやり取りされる送受信データ(INF)は、長さ(LEN)で示される可変サイズとなる。しかし、DMAC38へのデータサイズ指定は固定長となるため、データサイズの再設定等が必要とされる。

【0052】

ここで従来技術に従えば、図9(A)に示されるように、CPUによってデータサイズの再設定が行われる。

【0053】

先ず、CPUはDMACのデータサイズを3バイトとして設定する。次に3バイト受信後にDMA転送完了割込みが通知されたCPUは、3バイト目の長さ(LEN)のサイズから残りのデータサイズを算出してDMACのデータサイズを再設定する。しかしこの手法の場合、DMA転送中にCPUに割込みを行うため、CPUの処理負荷によってはデータ受信が正常に行えない可能性がある。つまり、レシーブデータレジスタ(SCRDR)303内の1バイト(8ビット)分のデータを、メモリインタフェース37を介してメモリ6に書き込む処理が完了する前に、レシーブデータレジスタ(SCRDR)301の出力データが、シリアル・パラレル変換回路302を介してレシーブデータレジスタ(SCRDR)303に伝達されるおそれがある。かかる場合には、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまう。

【0054】

また、図9(B)に示されるように、CPUによってDMACのデータサイズをレスポンス最大長(例えば258バイト)に設定し、レスポンスデータがなくなった場合に、CPUに対してタイムアウトエラー割込みを発生させ、それをトリガとしてCPUに受信データの処理を実行させることが考えられるが、その場合、タイムアウト発生まのでオーバーヘッドが発生するおそれがある。

【0055】

これに対して、図5に示される構成によれば、図10に示されるように、DMA転送設定により、データ長オフセットレジスタ3811には、データ長フィールドのオフセット情報が保持される。最終データ長レジスタ3812には、最終フィールドの長さ情報が保持される。データ長フィールド(LEN)のオフセット情報は、図8に示される例の場合、3バイト目とされる。つまり、先頭フィールドの3バイト目にデータ長フィールド(LEN)が存在し、それに基づいて、情報フィールドである送受信データ(INF)の長さの把握が可能になる。データ長算出回路3803は、SIMカードインタフェース39から内部メモリ3801に転送されたデータの先頭から3バイト目の情報(LEN)に基づいて、上記情報フィールドの長さを把握し、それに上記最終データ長レジスタ3812の出力を加算することによって、DMA転送すべきデータの長さ(残りのバイト)を算出する。尚、最終フィールドが存在しない場合には、最終データ長レジスタ3812の出力は0バイトとなる。回数制御回路3802は、データ長算出回路3803での算出結果に基づいて、転送数指定レジスタ(TCR)3809における転送回数を再設定する。これにより、DMAC38では、再設定された転送回数に応じたDMA転送制御が行われる。このように図5に示される構成によれば、DMAC38内の演算処理により転送回数の再設定が行われるようになっているので、CPU33の処理負荷にかかわらず、データの受信を正常に行うことができる。これにより、レシーブデータレジスタ(SCRDR)303内の未転送データが上書きによって壊れてしまうのを回避することができる。また、図5に示される構成によれば、CPUによってDMACのデータサイズをレスポンス最大長(例えば258バイト)に設定し、レスポンスデータがなくなった場合に、CPUに対してタイムアウトエラー割込みを発生させる方式ではないので、タイムアウト発生まのでオーバーヘッドが発生するおそれも無い。

【0056】

さらに、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御によって行う場合でも、クロック制御回路310によって、エンプティフラグ304内のエンプティフラグがモニタされ、エンプティフラグが論理値‘0’の場合(レシーブデータレジスタ(SCRDR)303にデータが存在する場合)には、クロック制御回路310の制御によって、ICカード7へのクロック信号の供給が停止される。これにより、新たなデータがICカード7からレシーブデータレジスタ(SCRDR)301に伝達されることはない。

【0057】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0058】

例えば、図6において太線矢印で示されるように、SIMカードインタフェース39とメモリ6との間のデータ転送をDMAC38の制御によって行う場合には、SIMカードインタフェース39とメモリ6との間のデータ転送をCPU33で制御する場合に比べてCPU33の負荷が軽減されることから、図2におけるクロック制御回路310やクロック停止時のレベル指定レジスタ311を省略しても良い。

【符号の説明】

【0059】

1 アンテナ

2 チューナ

3 地上波デジタル放送受信用チップ

4 LCD

5 スピーカ

6 メモリ

7 ICカード

10 モバイル端末向け地上波デジタル放送受信装置

31 MSTIF

32 EMUX

33 CPU

34 LCD制御部

35 音声出力制御部

36 デコーダ

37 メモリインタフェース

38 DMAC

39 SIMカードインタフェース

301 レシーブシフトレジスタ(SCRSR)

302 シリアル・パラレル変換回路

303 レシーブデータレジスタ(SCRDR)

304 エンプティフラグ

305 トランスミットシフトレジスタ(SCTSR)

306 パラレル・シリアル変換回路

307 トランスミットデータレジスタ(SCTDR)

308 エンプティフラグ

309 割込みコントローラ

310 クロック制御回路

311 クロック停止時のレベル指定レジスタ

312 送受信コントローラ

313 ボーレートジェネレータ

3801 内部メモリ

3802 回数制御回路

3803 データ長算出回路

3804 レジスタ制御回路

3805 起動制御回路

3806 要求優先制御回路

3807 転送元アドレス指定レジスタ(SAR)

3808 転送先アドレス指定レジスタ(DAR)

3809 転送数指定レジスタ(TCR)

3810 転送モード指定レジスタ(CHCR)

3811 データ長オフセットレジスタ

3812 最終データ長レジスタ

【特許請求の範囲】

【請求項1】

供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェースを含む半導体装置であって、

上記カードインタフェースは、上記ICカードに供給される上記クロック信号を生成するためのボーレートジェネレータと、

上記ICカードから伝達されたシリアルデータをパラレルデータに変換するための変換回路と、

上記変換回路から出力されたパラレルデータを保持するためのレシーブデータレジスタと、

上記レシーブデータレジスタに上記パラレルデータが存在しない場合には、上記ボーレートジェネレータから上記ICカードへ上記クロック信号を供給し、上記レシーブデータレジスタに上記パラレルデータが存在する場合には、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止するためのクロック制御回路と、を含むことを特徴とする半導体装置。

【請求項2】

上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在するか否かの判別を可能とするエンプティフラグを含み、上記クロック制御回路は、上記エンプティフラグの論理に基づいて、上記レシーブデータレジスタに上記パラレルデータが存在するか否かを判別する請求項2記載の半導体装置。

【請求項3】

上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止する際の上記クロック信号の論理を指定するためのレベル指定レジスタを含む請求項2記載の半導体装置。

【請求項4】

上記半導体装置は、上記レシーブデータレジスタ内のデータを別の記憶媒体にDMA転送するためのDMAコントローラを含む請求項3記載の半導体装置。

【請求項5】

上記DMAコントローラによってDMA転送されるデータは、データ長フィールドと、情報フィールドと、最終フィールドとを含み、

上記DMAコントローラは、DMA転送における転送回数が設定される転送数指定レジスタと、

上記データ長フィールドの位置を示すデータ長オフセットレジスタと、

上記最終フィールドの長さを示す最終データ長レジスタと、

上記データ長オフセットレジスタの出力に対応する上記データ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路と、

上記データ長算出回路での算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路と、を含み、上記回数制御回路によって再設定された回数分のDMA転送を行う請求項4記載の半導体装置。

【請求項6】

請求項1記載の半導体装置を含んで成る地上デジタル放送受信装置。

【請求項7】

供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェースと、上記カードインタフェースを介して取り込まれたデータを別の記憶媒体にDMA転送するためのDMAコントローラと、を含む半導体装置であって、

上記DMAコントローラによってDMA転送されるデータは、データ長フィールドと、情報フィールドと、最終フィールドとを含み、

上記DMAコントローラは、DMA転送における転送回数が設定される転送数指定レジスタと、

上記データ長フィールドの位置を示すデータ長オフセットレジスタと、

上記最終フィールドの長さを示す最終データ長レジスタと、

上記データ長オフセットレジスタの出力に対応する上記データ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路と、

上記データ長算出回路での算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路と、を含み、上記回数制御回路によって再設定された回数分のDMA転送を行うことを特徴とする半導体装置。

【請求項1】

供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェースを含む半導体装置であって、

上記カードインタフェースは、上記ICカードに供給される上記クロック信号を生成するためのボーレートジェネレータと、

上記ICカードから伝達されたシリアルデータをパラレルデータに変換するための変換回路と、

上記変換回路から出力されたパラレルデータを保持するためのレシーブデータレジスタと、

上記レシーブデータレジスタに上記パラレルデータが存在しない場合には、上記ボーレートジェネレータから上記ICカードへ上記クロック信号を供給し、上記レシーブデータレジスタに上記パラレルデータが存在する場合には、上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止するためのクロック制御回路と、を含むことを特徴とする半導体装置。

【請求項2】

上記カードインタフェースは、上記レシーブデータレジスタに上記パラレルデータが存在するか否かの判別を可能とするエンプティフラグを含み、上記クロック制御回路は、上記エンプティフラグの論理に基づいて、上記レシーブデータレジスタに上記パラレルデータが存在するか否かを判別する請求項2記載の半導体装置。

【請求項3】

上記ボーレートジェネレータから上記ICカードへのクロック信号の供給を停止する際の上記クロック信号の論理を指定するためのレベル指定レジスタを含む請求項2記載の半導体装置。

【請求項4】

上記半導体装置は、上記レシーブデータレジスタ内のデータを別の記憶媒体にDMA転送するためのDMAコントローラを含む請求項3記載の半導体装置。

【請求項5】

上記DMAコントローラによってDMA転送されるデータは、データ長フィールドと、情報フィールドと、最終フィールドとを含み、

上記DMAコントローラは、DMA転送における転送回数が設定される転送数指定レジスタと、

上記データ長フィールドの位置を示すデータ長オフセットレジスタと、

上記最終フィールドの長さを示す最終データ長レジスタと、

上記データ長オフセットレジスタの出力に対応する上記データ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路と、

上記データ長算出回路での算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路と、を含み、上記回数制御回路によって再設定された回数分のDMA転送を行う請求項4記載の半導体装置。

【請求項6】

請求項1記載の半導体装置を含んで成る地上デジタル放送受信装置。

【請求項7】

供給されたクロック信号に基づいて所定のデータ処理を行うICカードとの間でシリアル通信を行うためのカードインタフェースと、上記カードインタフェースを介して取り込まれたデータを別の記憶媒体にDMA転送するためのDMAコントローラと、を含む半導体装置であって、

上記DMAコントローラによってDMA転送されるデータは、データ長フィールドと、情報フィールドと、最終フィールドとを含み、

上記DMAコントローラは、DMA転送における転送回数が設定される転送数指定レジスタと、

上記データ長フィールドの位置を示すデータ長オフセットレジスタと、

上記最終フィールドの長さを示す最終データ長レジスタと、

上記データ長オフセットレジスタの出力に対応する上記データ長フィールドの値によって上記情報フィールドの長さを求め、それに上記最終データ長レジスタの出力を加算することによって、DMA転送すべきデータの長さを算出するデータ長算出回路と、

上記データ長算出回路での算出結果に基づいて、上記転送数指定レジスタにおける転送回数を再設定する回数制御回路と、を含み、上記回数制御回路によって再設定された回数分のDMA転送を行うことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−247974(P2012−247974A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−118879(P2011−118879)

【出願日】平成23年5月27日(2011.5.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月27日(2011.5.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]