半導体装置

【課題】半導体素子と当該半導体基板が搭載される支持基板との熱膨張係数の違いに基づく応力が半導体素子の凸状外部接続端子と支持基板上の導電層との間に於ける導電性部材部分に集中して、半導体素子の凸状外部接続端子と支持基板上の導電層との電気的接続が破断されてしまうことを防止することができる凸状外部接続端子の配設構造を提供する。

【解決手段】半導体基板101の一方の主面に複数個の外部接続端子パッド102が配設され、当該外部接続パッド102上に複数個の凸状外部接続端子103A、103Bが配設される。凸状外部接続端子を複数個配設することにより、半導体素子の凸状外部接続端子と支持基板上の導電層との間に介在される接続部材との接触面積が増加することから、前記昇温・降温の際に生じるストレスはより広い範囲に分散される。

【解決手段】半導体基板101の一方の主面に複数個の外部接続端子パッド102が配設され、当該外部接続パッド102上に複数個の凸状外部接続端子103A、103Bが配設される。凸状外部接続端子を複数個配設することにより、半導体素子の凸状外部接続端子と支持基板上の導電層との間に介在される接続部材との接触面積が増加することから、前記昇温・降温の際に生じるストレスはより広い範囲に分散される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、より具体的には、支持基板の主面に選択的に配設された導電層に対して、半導体素子の主面上に配設された凸状電極が接続固着されて構成される半導体装置の電極接続構造に関する。

【背景技術】

【0002】

ガラスエポキシ樹脂などの絶縁性樹脂を基材とし、その表面に銅(Cu)などからなる導電層が選択的に配設された配線用基板を複数積層して形成された支持基板を用い、その一方の主面に選択的に配設された導電層に、半導体集積回路素子(以下半導体素子と称する)の主面に配設された凸状電極が接続され、一方、前記支持基板の他方の主面には選択的に形成された導電層の表面に球状電極端子などの外部接続端子が配設されてなる半導体装置がある。即ち、半導体素子は所謂フェイスダウン状態で、支持基板に搭載されている。

【0003】

かかる構成に於いては、前記半導体素子の主面にあって、外部接続用端子パッド上に所謂ボールボンディング法によって金(Au)ボールが圧接固着・接続されて台座部及び当該台座部上に突出する部位からなる凸状の外部接続端子が形成される。尚、当該突出する部位は、必要に応じて平坦化処理がなされる。このように、金線など軟質の金属線を用いて形成され、台座部とその上に突出する部位とからなる端子構造は、スタッドバンプ(Stud bump)と称される。

【0004】

このように、台座部とその上に突出する部位とからなる端子構造は、その表面積が大きいことから、前記支持基板上の導電層に対して、はんだなどの導電性部材をもって容易に接続固着される。

【0005】

このような接続形態は比較的安価に実施することができることから、外部接続端子数が数個〜数百個の比較的小型の半導体素子への適用がなされている。

【特許文献1】特開平2−163950号公報

【特許文献2】特開平10−117065号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述の半導体装置を形成する際には、例えば支持基板の一方の主面に配設された導電層の表面に選択的にはんだなどの導電性部材を配設した後、当該導電性部材上に半導体素子の凸状外部接続端子を接触させ、かかる状態に於いて導電性部材の融点以上の温度に加熱して当該導電性部材を溶融せしめる。

【0007】

しかる後、常温など導電性部材の融点以下の温度とすることにより当該導電性部材は固化し、半導体素子の凸状外部接続端子は、支持基板上の導電層に機械的・電気的に接続される。

【0008】

ところが、この様に昇温・降温工程が執られることから、半導体素子と支持基板との熱膨張係数の違いに基づく応力が半導体素子の凸状外部接続端子と支持基板上の導電層との間に於ける導電性部材部分に集中して、当該導電性部材にクラック(割れ)を生じ、半導体素子の凸状外部接続端子と支持基板上の導電層との電気的接続が破断されてしまう。

【0009】

降温直後にあってはクラックが生じなくとも、半導体素子の凸状外部接続端子と支持基板の導電層との間に於ける導電性部材部分には応力が集中して残存することから、その後の製造工程に於ける温度変化あるいは振動などによりクラックを生じてしまう。

【0010】

更に、製造工程に於いてはクラックを生ずることがなかった場合であっても、半導体装置として実働する際にクラックを生ずる可能性が残り、半導体装置としての信頼性の低下を招来してしまう。

【0011】

前記支持基板として両面配線基板など板厚の薄い基板を用いる場合には、その反り量が大きいことから、クラックの発生を招来する可能性が大きい。

【0012】

そこで、本発明は、上記の点に鑑みてなされたものであって、このような半導体装置に於ける、半導体素子の凸状外部接続端子と支持基板上の導電層との間の機械的・電気的接続を高い信頼性をもって実現することができる半導体装置構造を提供することを本発明の目的とする。

【課題を解決するための手段】

【0013】

本発明の一観点によれば、半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に複数個の凸状外部接続端子が配設されてなる半導体素子が、前記複数個の凸状外部接続端子を共通に被覆する接続部材を介して、支持基板の一方の主面上に配設された導電層に固着されてなることを特徴とする半導体装置が提供される。

【0014】

本発明の別の観点によれば、半導体基板、前記半導体基板の一方の主面に配設された外部接続用端子パッド、及び前記外部接続用端子パッド上に複数個配設された凸状外部接続端子を具備する半導体素子、絶縁性基板、前記絶縁基板の一方の主面に配設された導電層、及び前記絶縁基板の前記一方の主面上に配設されて前記導電層を選択的に被覆する絶縁層を具備する支持基板、前記絶縁層に被覆されない前記導電層に、前記複数個の凸状外部接続端子を共通に被覆して固着する接続部材を具備することを特徴とする半導体装置が提供される。

【0015】

本発明の更に別の観点によれば、半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設されてなる半導体素子と、前記外部接続用端子パッドに対応した複数個の導電層が配設され、当該導電層上に少なくとも一つの第2の凸状外部接続端子が配設されてなる支持基板と、を具備し、前記第1の凸状外部接続端子が接続部材を介して前記導電層に接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記外部接続用端子パッドに接続されてなることを特徴とする半導体装置が提供される。

【0016】

本発明の更に別の観点によれば、支持基板と、前記支持基板の上に実装された配線基板を介して前記支持基板に接続され、前記配線基板の上に実装された半導体素子と、を備えた半導体装置であって、前記半導体素子の半導体基板の主面のうち、前記配線基板に面した側の面に複数個の半導体素子外部接続用端子パッドが配設され、当該半導体素子外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設され、前記配線基板の主面のうち、前記半導体素子に面した側の面に複数個の配線基板外部接続用端子パッドが配設され、当該配線基板外部接続用端子パッド上に少なくとも一つの第2の凸状外部接続端子が配設され、前記第1の凸状外部接続端子が接続部材を介して前記配線基板外部接続用端子パッドに接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記半導体素子外部接続用端子パッドに接続されてなることを特徴とする半導体装置が提供される。

【発明の効果】

【0017】

本発明によれば、半導体素子に於ける一つの外部接続端子パッド上には複数個、即ち少なくとも2個の凸状外部接続端子が配設される。

【0018】

これにより、半導体素子の一つの外部接続端子に於ける凸状外部接続端子と支持基板上の導電層との対向面積が、前記従来技術に比してほぼ倍増する。即ち、半導体素子の凸状外部接続端子と支持基板上の導電層との間に介在される接続部材との接触面積が増加することから、前記昇温・降温の際に生じるストレスが当該凸状外部接続端子と支持基板上の導電層との間に集中し、或いは残存したとしても、当該ストレスはより広い範囲に分散される。

【0019】

この結果、半導体素子の凸状外部接続端子と支持基板上の導電層との間に於ける接続部材の全域に跨がってクラックを生ずる恐れが大きく低減する。

【0020】

従って、当該半導体素子と支持基板との間の電気的・機械的接続が、高い信頼性をもって実現される。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施の形態について説明する。

【実施例1】

【0022】

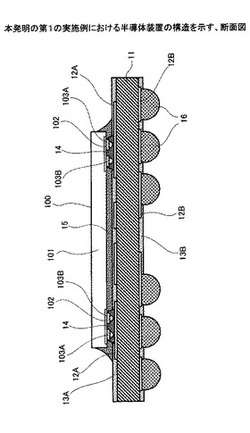

本発明に基づき、半導体素子の凸状外部接続端子と支持基板上の導電層との間の機械的・電気的接続がなされた、本発明の第1の実施例である半導体装置を、図1に示す。

【0023】

同図に於いて、11はガラスエポキシ樹脂などの絶縁性樹脂を基材とし、その表面に銅(Cu)などからなる配線層が選択的に配設された基板が複数積層されて形成された支持基板である。当該支持基板11は、インターポーザー或いは配線基板と称される場合もある。

【0024】

また、12Aは当該支持基板11の一方の主面上に選択的に配設された導電層であって、銅(Cu)層から構成されている。当該導電層12Aは、当該支持基板11に搭載される半導体素子(後述)の外部接続端子が接続される導電層および配線層を含み、当該半導体素子の外部接続端子が接続される領域を除いてソルダーレジスト層13Aにより選択的に被覆されている。即ち、当該ソルダーレジスト層13Aは、導電層12Aに於ける、半導体素子との接続領域を画定している。

【0025】

また、100は、シリコン(Si)半導体基板101を用い、周知の半導体製造プロセスをもって形成された半導体集積回路素子(以下半導体素子と称する)である。

【0026】

勿論、半導体基板として、ガリウム砒素(GaAs)等の化合物半導体を適用した半導体集積回路素子を具備する半導体装置に対しても本発明を適用することができる。

【0027】

本実施例にあっては、当該半導体基板101の一方の主面に選択的に(例えば、当該主面の四辺近傍において当該四辺に沿って、又は対向する二辺近傍において当該二辺に沿って)配設された複数個の外部接続用パッド102には、それぞれ2個の凸状外部接続端子103A、103Bが並設されている。

【0028】

即ち、当該外部接続用パッド102上に於いて、凸状外部接続端子103A、103Bは、半導体素子100の縁部の延びる方向に対して直角方向に並んで配設されている。

【0029】

尚、ここでは、当該半導体素子100にあって、シリコン半導体基板101内に形成された能動素子及び/或いは受動素子、並びに当該一方の主面上に形成された多層配線層及び/或いは再配線層を図示することを省略している。

【0030】

前記外部接続用パッド102は、アルミニューム(Al)、銅(Cu)、及びこれらの合金(例えば、Al95%−Cu5%合金等)等をもって形成されており、また凸状外部接続端子103は、前述の従来技術と同様、所謂ボールボンディング法によって金(Au)ボールが圧接固着・接続されて台座部が形成され、更に当該台座部上に突出する部位からなる凸状の外部接続端子が一体に形成されている。金線の突出部分の頂部は必要に応じて平坦化処理がなされる。

【0031】

なお、外部接続端子パッド102の露出表面(最上層)には、電解めっき法又は蒸着法等により金(Au)層を形成しておくことが望ましい。

【0032】

かかる半導体素子100の凸状外部接続端子103A、103Bと、これに対応する前記支持基板11上の導電層12Aは、はんだ或いは導電性接着剤等からなる接続部材14によって共通に被覆され、機械的・電気的に接続されている。並設された2個の凸状外部接続端子103A、103Bは、広い接触面積をもって、導電層12Aに接続・固着されている。

【0033】

即ち、当該半導体素子100は、支持基板11の一方の主面上にフリップチップ(フェイスダウン)方式をもって搭載・固着されている。

【0034】

そして、当該半導体素子100と支持基板11の一方の主面との間には、エポキシ系樹脂を主体とするアンダーフィル材15が充填されている。

【0035】

一方、前記支持基板11の他方の主面には、外部接続端子16の配設用或いは配線層を含む導電層12Bが選択的に配設されている。当該導電層12Bはソルダーレジスト層13Bにより選択的に被覆されており、当該ソルダーレジスト層13Bは外部接続端子16の配設領域を画定している。当該ソルダーレジスト層13Bにより画定された導電層12Bには、はんだを主体とする外部接続端子16が配設されている。

【0036】

尚、かかる支持基板11に於ける外部接続用端子部の配設構造は、ここに示す形態に特定されるものではない。支持基板11の一方の主面、即ち半導体素子100が搭載される主面に於いて、当該半導体素子100の周囲に外部接続用端子を配設することも可能であり、また外部接続用端子の導出構造もワイヤボンディング法、ボール・グリッド・アレイ(BGA)構造など適宜選択することができる。

【0037】

また、当該支持基板11は、前述の多層構造の配線基板に限られるものではなく、単一の絶縁基板の表裏両面に導電層が配設された所謂両面配線基板、或いは単一の絶縁基板の片面に導電層が配設された片面配線基板を適用することもできる。

【0038】

前記支持基板11の一方の主面に於いて、半導体素子100の凸状外部接続端子103A、103Bが接続される導電層12Aの平面形状を、図2(a)〜(c)に示す。ここでは、導電層12Aが3本(条)並んで配設された状態に於ける形態を示す。

【0039】

同図(a)に示される形態にあっては、ソルダーレジスト層13Aによって半導体素子100の凸状外部接続端子との接続領域200が規定される導電層12Aは、当該ソルダーレジスト層13A下に延在する領域と同一の幅を有している。接続領域200内にあって、円201は、半導体素子100の凸状外部接続端子103A、103Bが接続される部位を示す。

【0040】

また、同図(b)に示される形態にあっては、ソルダーレジスト層13Aによって半導体素子100の凸状外部接続端子との接続領域200が規定される導電層12Aは、当該ソルダーレジスト層13A下に延在する領域よりも幅広とされている。接続領域200内にあって、円201は、半導体素子100の凸状外部接続端子103A、103Bが接続される部位を示す。

【0041】

かかる形態によれば、前記(a)に示す形態に比して、接続領域200に収容可能な接続部材14の量を増加させることができ、凸状外部接続端子103A、103Bと、導電層12Aとの接続をより強固に行うことができる。

【0042】

一方、同図(c)に示される形態にあっては、ソルダーレジスト層13Aによって半導体素子101の凸状外部接続端子との接続領域200が規定される導電層12Aは、当該ソルダーレジスト層13A下に延在する領域よりも幅広とされ、且つ半導体素子100の凸状外部接続端子103A、103Bが接続される部位の間203にあってはその幅を狭く、ソルダーレジスト層13A下に延在する領域と同等の幅とされている。

【0043】

かかる形態によれば、前記(a)に示す形態に比して、接続領域200に収容可能な接続部材14の量を増加させることができ、且つ凸状外部接続端子103A、103Bが接続される部位間にあっては幅狭とされていることにより、接続部材14の量が過多にならないように所定の量に制御することが容易となる。

【0044】

これにより、凸状外部接続端子103A、103Bと導電層12Aとの接続を、より強固に行うことができ、且つ半導体素子100の外部接続用パッド102のパッドピッチが微細になった場合であっても、隣接する外部接続用パッド間での接続部材14のブリッジによる短絡の発生を抑制することができる。

【0045】

このように、図2(a)乃至(c)に示す構成にあっては、支持基板11上に配設された導電層12Aは、半導体素子101の凸状外部接続端子103が接続される接続領域200を表出し、当該接続領域200の周囲はソルダーレジスト層13Aにより被覆された構造を有する。

【0046】

前記支持基板11の一方の主面に於いて、半導体素子100の凸状外部接続端子103A、103Bが接続される導電層12Aを覆うソルダーレジスト13Aの被覆形状は、このような形状に限られるものではない。

【0047】

当該ソルダーレジスト13Aの被覆形状の変形例を、図3に示す。同図(a)乃至(c)に示される導電層12Aの形状は、前記図2(a)乃至(c)に示される導電層の形状に対応している。

【0048】

図3に示される例にあっては、隣接する導電層12Aは、接続領域201から離間した位置に於いて、ソルダーレジスト13Aにより共通に被覆されている。隣接する接続領域201間にはソルダーレジスト13Aは配設されておらず、支持基板11が表出している。

【0049】

この様なソルダーレジストの被覆形態は、導電層12Aの配設される間隔がより狭くされた場合に適用することができる。

【0050】

前記半導体素子100に於いて、一つの外部接続用パッド102上に並設された凸状外部接続端子103A、103Bの形態を図4に示す。同図(a)は当該凸状外部接続端子103A、103Bの配置の平面形状を示し、同図(b)は同図(a)のX−X断面を示す。

【0051】

同図に於いて、101はシリコン半導体基板、104は窒化シリコン(Si3N4)などからなる表面保護膜を示す。 尚、シリコン半導体基板101の主面に於ける他の導電層、絶縁層の表示は省略している。

【0052】

同図に於いて、凸状外部接続端子103A、103Bは、前述の如く、金(Au)ボールが圧接固着・接続されて台座部301及び当該台座部301上に突出する部位302からなり、一体に凸状に形成される。当該突出する部位302は、ボンディングツール(図示せず)の先端部の形状により前記金ボールの一部が整形されて生ずるものであって、必要に応じて平坦化処理がなされるが、ここでは当該平坦化処理を施していない。

【0053】

かかる形態に於いて、凸状外部接続端子103Aと103Bは、できるだけ近接して配置されることが望ましい。

【0054】

前記ボンディングツールの先端部の形状により制限を受けるものであるが、凸状外部接続端子103Aの台座部301Aと凸状外部接続端子103Bの台座部301Bとがより近接して配置されることにより両端子間の空間が減少し、これにより前記接続部材14の回り込みが容易になされ、両端子間に当該接続部材14の未充填領域(ボイド)を生じない。

【0055】

未充填領域を生じないことから、半導体素子100と支持基板11との間隙部にアンダーフィル材15を充填する際に、両端子間にアンダーフィル材15の未充填領域が生じることを抑制することができる。これにより、アンダーフィル材15内に於けるボイドの存在に起因する半導体装置の信頼性の低下を抑制することができる。

【0056】

本実施例に於ける半導体装置の製造工程を、図5に示す。

【0057】

同図(a)は、ボンディングステージ401上に載置・固定された支持基板101と、吸着用治具402に吸着保持された半導体素子100とを対向させた状態を示す。

【0058】

支持基板11の一方の主面に於ける導電層12Aには、予め例えば錫(Sn)を主体とするはんだ(半田)からなる接続部材14が選択的に被覆されている。

【0059】

当該接続部材14は、印刷法、メッキ法或いは蒸着・リフロー法などにより、被着・形成することができ、その厚さは5μm〜70μm程とされる。尚、導電層12Aは厚さ9μm〜25μm程の銅(Cu)から形成されるが、他の材料から適宜選択することができる。

【0060】

また、ソルダーレジスト層13Aは例えば5μm〜25μm程の厚さとされる。

【0061】

尚、支持基板11に於ける外部接続用端子部の構成は、前述の如く種々選択可能であることから、ここでは当該支持基板11の他方の主面に於ける導電層などの表示を省略する。

【0062】

一方、半導体素子100にあっては、シリコン半導体基板101の主面上に形成された多層配線層を含む絶縁層を介して配設された外部接続用端子パッド102上に、本発明思想に従って凸状外部接続端子103A、103Bが配設されている。

【0063】

外部接続用端子パッド102は、厚さ0.4μm〜1.5μm程のアルミニューム(Al)から形成されている。

【0064】

また、凸状外部接続端子103A、103Bは、外部接続用端子パッド102表面に所謂ボールボンディング法によって金(Au)ボールが圧接固着・接続されて、台座部(図4、301)が形成され、更に当該台座部上に突出する部位(図4、302)からなる凸状をもって一体に形成されている。

【0065】

当該台座部の直径は30μm〜60μm、厚さは5μm〜25μm程とされ、一方突出する部位は直径10μm〜50μm、その高さは10μm〜70μm程とされる。

【0066】

これらの寸法は、半導体素子に於ける設計ルールに基づき、端子パッドの面積、隣接する間隔或いは半導体装置として求められる高さなどから、適宜選択される。

【0067】

なお、外部接続用端子パッド102表面への凸状外部接続端子103A、103Bの形成は、上述したボールボンディング法の他、電解めっき法又は無電解めっき法により外部接続用端子パッド102表面に金(Au)、銅(Cu)、ニッケル(Ni)等の金属を析出させるめっき法を用いることで形成してもよい。

【0068】

また、外部接続用端子パッド102の露出表面(最上層)には、電解めっき法又は蒸着法等により金(Au)層を形成しておくことが望ましい。

【0069】

このように、導電層12Aと凸状外部接続端子103A、103Bとが位置合わせされ、対向された状態で、ボンディングステージ401を加熱・昇温して、前記接続部材14の融点以上の温度に加熱すると共に、前記吸着用治具402を降下させて、凸状外部接続端子103A、103Bを溶融状態にある接続部材14中に圧入する。

【0070】

この結果、当該接続部材14は、凸状外部接続端子103A、103Bを覆うと共に、外部接続用端子パッド102の露出表面にも接して、導電層12Aと外部接続用端子パッド102との間を結合する。この時、凸状外部接続端子103Aと103Bとの間の空間も、当該接続部材14により充填される。かかる状態を、同図(b)に示す。

【0071】

尚、ボンディングステージ401を加熱・昇温する代わりに、半導体素子100を、予め所定温度(例えば280℃〜300℃)に加熱された吸着用治具402に吸着・保持し、加熱・昇温された凸状外部接続端子103A、103Bを接続部材14に接触させることにより、当該接続部材14を昇温・溶融させてもよい。

【0072】

また、ボンディングステージ401を予め所定温度(例えば50℃〜100℃)に加熱して、支持基板11に対し予熱を印加しておくことにより、接続部材14をより短時間で昇温させることができる。

【0073】

このように、支持基板11上の導電層12Aに半導体素子100の凸状外部接続端子103A、103Bが接続・固着され、当該支持基板11に半導体素子100が搭載された後、当該支持基板11と半導体素子100との間に、エポキシ系樹脂を主体とするアンダーフィル材15が充填される。かかる状態を、同図(C)に示す。

【0074】

しかる後、支持基板11の前記一方の主面或いは他方の主面に、必要とする外部接続端子を形成する。

【実施例2】

【0075】

本発明の第2の実施例に於ける半導体装置を、図6及び図7に示す。

【0076】

図7は、図6に示される半導体素子150が支持基板11上に搭載された半導体装置構造を示し、図7に於ける半導体素子150は、図6のX−X'断面を示す。

【0077】

尚、前記第1の実施例に於ける構造と対応する部位には同一の符号を付している。

【0078】

図6及び図7を参照するに、当該第2の実施例に於ける半導体装置にあっては、DRAM(Dynamic Random Access Memory)等、複数個の外部接続用パッド152が半導体基板151の中央部に列状に並んで配設された構造を有する半導体素子150が、支持基板11にフリップチップ接続されている。

【0079】

本実施例に於ける半導体装置に於いては、前記第1の実施例に於ける半導体装置と同様に、外部接続用パッド152上に並設された凸状外部接続端子153A、153Bは、当該凸状外部接続端子153A、153Bを共通に被覆する接続部材14を介して、支持基板11の一方の主面上に配設された導電層12Aに固着されている。

【0080】

本実施例に於ける半導体装置にあっては、半導体素子150に於ける複数個の外部接続用パッド152が、半導体基板151の略中央に列状に配設されている。

【0081】

従って、当該半導体装置の製造工程に於いて、或いは当該半導体装置に於いて、半導体素子150の半導体基板151の略中央に配設された凸状外部接続端子153A、153Bと支持基板11上の導電層12Aとの間に於ける接続部材14に、半導体素子150と支持基板11との熱膨張係数の違いに基づく応力が集中して、当該接続部材14にクラックを生じ、凸状外部接続端子153A、153Bと導電層12Aとの電気的接続が破断されてしまう恐れがある。

【0082】

しかしながら、本実施例に於いても、1つの外部接続用パッド152に、2個の凸状外部接続端子153A、153Bが配設され、当該凸状外部接続端子153A、153Bは、当該凸状外部接続端子153A、153Bを共通に被覆する接続部材14を介して、支持基板11の一方の主面上に配設された導電層12Aに接続・固着されている。

【0083】

即ち、当該外部接続用パッド152上に於いて、凸状外部接続端子153A、153Bは、当該パッド配列の延びる方向に対して直角方向に並んで配設されている。

【0084】

従って、半導体素子150の凸状外部接続端子153A、153Bと支持基板11上の導電層12Aとの間に介在される接続部材14との接触面積が増加することから、半導体素子150と支持基板11との熱膨張係数の違いに基づく応力が、当該凸状外部接続端子153A、153Bと導電層12Aとの間に集中したとしても、当該応力はより広い範囲に分散される。

【0085】

従って、半導体素子150の凸状外部接続端子153A、153Bと支持基板11上の導電層12Aとの間に於ける接続部材14の全域に跨がってクラックを生ずる恐れは大きく低減する。このように、本実施例においても、半導体素子150と支持基板11との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0086】

尚、本実施例に於いても、導電層12Aの形状及び配設構造として、前記図2又は図3に示す構造を適用してよく、また凸状外部接続端子153A、153Bの配設形態も前記図4に示す形態を適用することができる。

【0087】

更に、支持基板11上に半導体素子150を実装する際の工程として、前記図5に示した工程を適用することができる。

【実施例3】

【0088】

本発明の第3の実施例に於ける半導体装置について、図8を参照して説明する。尚、前記第1の実施例に於ける構造と対応する部位には同一符号を付している。

【0089】

図8を参照するに、本発明の第3の実施例に於ける半導体装置は、前記第1の実施例に於ける半導体装置の半導体素子100、即ち支持基板11上にフリップチップ接続された半導体素子100(以下、本実施例においては「第1の半導体素子100」と称する)の背面上に、外部接続用パッド161が形成された面を上とした所謂フェイスアップ状態で、第2の半導体素子160が載置されてなる半導体素子積層構造を有する。

【0090】

当該第2の半導体素子160は、接着剤164を介して第1の半導体素子100の背面上に固着されている。接着剤164としては、エポキシ、ポリイミド等のフィルム状又はペースト状の樹脂接着剤を用いることができるが、これに限定されるものではない。

【0091】

そして、当該第2の半導体素子160の上面に配設された外部接続用パッド161と、前記支持基板11の第2半導体素子用導電層162(以下、本実施例においては、前記第1の実施例に於ける導電層12Aを第1半導体素子用導電層12Aと称する。)は、ボンディングワイヤ165により接続されている。

【0092】

また、第1の半導体素子100及び第2の半導体素子160は、支持基板11上に於いて、封止樹脂166によって樹脂封止されている。封止樹脂166としては、シリコン系樹脂、アクリル系樹脂或いはエポキシ系樹脂等を用いることができるが、これらに限定されない。

【0093】

このように、本実施例の半導体装置は、支持基板11上に実装された第1の半導体素子100の上に、第2の半導体素子160が載置・積層された構造を有する。

【0094】

当該半導体装置は、支持基板11上に第1の半導体素子100をフリップチップ実装し、次いで、当該第1の半導体素子100上に第2の半導体素子160を接着固定し、当該第2の半導体素子160の外部接続用パッド161と支持基板11上の第2半導体素子用導電層162とをワイヤボンディングする。

【0095】

次いで、前記支持基板11、第1の半導体素子100及び第2の半導体素子160を、封止樹脂166により樹脂封止し、しかる後支持基板11の他方の主面に外部接続端子16を形成する。

【0096】

この様に、本実施例に於いても、第1の半導体素子100の1つの外部接続用パッド102には2個の凸状外部接続端子103A、103Bが配設され、当該凸状外部接続端子103A、103Bは、当該凸状外部接続端子103A、103Bを共通に被覆する接続部材14を介して支持基板11の一方の主面上に配設された導電層12Aに接続・固着されている。

【0097】

従って、第1の半導体素子100の凸状外部接続端子103A、103Bと支持基板11上の導電層12Aとの間に介在される接続部材14との接触面積が増加する。

尚、外部接続用パッド102に於いて、凸状外部接続端子103A及び凸状外部接続端子103Bは、半導体素子100の縁部の延びる方向に対して直角方向に並んで配設されている。

【0098】

この為、前記製造工程中、印加される熱応力及び/或いは機械的応力等により、或いは第1の半導体素子100と支持基板11との熱膨張係数の相違によって、第1の半導体素子100の半導体基板101に配設された凸状外部接続端子103A、103Bと支持基板11上の導電層12Aとの間に設けられた接続部材14に応力が集中したとしても、当該応力はより広い範囲に分散される。

【0099】

よって、第1の半導体素子100の凸状外部接続端子103A、103Bと支持基板11上の導電層12Aとの間に於ける接続部材14の全域に跨がってクラックを生ずる恐れは大きく低減する。

【0100】

このように、本実施例に於いても、第1の半導体素子100と支持基板11との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0101】

尚、本実施例に於いても、導電層12Aの形状及び配設構造として、前記図2又は図3に示す構造を適用してよく、また凸状外部接続端子103A、103Bの配設形態も前記図4に示す形態を適用することができる。

【0102】

更に、支持基板11上に半導体素子100を実装する際の工程として、前記図5に示した工程を適用することができる。

【実施例4】

【0103】

本発明の第4の実施例に於ける半導体装置を、図9及び図10に示す。当該第4の実施例に於ける半導体装置の断面構造を図9に示し、図9に於いて破線で囲んだ部分を図10に拡大して示す。なお、本実施例の説明に於いて、前記第1乃至第3の実施例に於ける部位と対応する部位については同じ符号を付し、その詳細な説明は省略する。

【0104】

図9を参照するに、本実施例に於ける半導体装置にあっては、支持基板11の上に、配線基板600を介して半導体素子500が搭載されている。

【0105】

当該配線基板600は、支持基板11と半導体素子500とを接続する中継基板(ターミナルチップ)として機能する。

【0106】

前記支持基板11の一方の主面上には、銅(Cu)層からなる導電層112Aが選択的に配設されている。

【0107】

当該導電層112Aは、支持基板11と配線基板600とを接続するボンディングワイヤ265が接続される導電層及び配線層を含み、ボンディングワイヤ265が接続される領域を除いてソルダーレジスト層13Aにより選択的に被覆されている。即ち、当該ソルダーレジスト層13Aは、導電層112Aに於ける、配線基板600との接続領域を画定している。

【0108】

一方、前記配線基板600は、例えばガラスエポキシ、ガラスビスマレイミドトリアジン(BT:Bismaleimide−Triazine)或いはポリイミド等からなる有機絶縁性基板をもって構成され、接着剤164を介して支持基板11上に固着されている。

【0109】

当該配線基板600の上面、即ち半導体素子500が載置される面には、当該半導体素子500の外部接続用パッドに対応して、銅(Cu)から成る外部接続用パッド612Aが複数個配設され、当該外部接続用パッド612Aには、それぞれ一つの凸状外部接続端子603が配設されている。

【0110】

また、配線基板600の上面にあって、前記半導体素子500の周囲に位置して、銅(Cu)から成る外部接続用パッド612Bが複数個配設されている。当該外部接続用パッド612Bは、配線基板600の主面の四辺または対向する二辺の近傍に設けられる。

【0111】

前記外部接続用パッド612Aは、配線基板600の表面或いは内部に形成された配線層(図示せず)をもって、対応する外部接続用パッド612Bに接続されている。

【0112】

当該パッド612A、612Bの表面には、下層側からニッケル(Ni)/金(Au)、或いは下層側から銅(Cu)/ニッケル(Ni)/金(Au)からなるめっき層が形成されていることが好ましい。

【0113】

また、前記半導体素子500は、第1乃至第3の実施例における半導体素子100と同様、シリコン(Si)、或いはガリウム砒素(GaAs)等の半導体基板を用い、周知の半導体製造プロセスをもって形成されている。

【0114】

当該半導体素子500の主面には、複数個の外部接続用パッド502が設けられ、当該外部接続用パッド502上には、一つの凸状外部接続端子503が配設されている。

【0115】

当該半導体素子500は、前記配線基板600上に所謂フリップチップ方式をもって実装される。この時、当該半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503と、配線基板600の外部接続用パッド612A上に設けられた凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされる。当該凸状外部接続端子503、凸状外部接続端子603は、半導体素子500の縁部の延びる方向に対して直角方向に並んで配設されている。

【0116】

加えて、当該凸状外部接続端子503、凸状外部接続端子603は、前記平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向には重畳した(互いに入り込んだ)状態とされる。

【0117】

そして、当該凸状外部接続端子503と凸状外部接続端子603は、はんだ或いは導電性接着剤等からなる接続部材14により機械的・電気的に接続され、また半導体素子500と配線基板600との間にはエポキシ系樹脂を主体とするアンダーフィル材15が充填されて、半導体素子500は配線基板600に固着されている。

【0118】

そして、配線基板600に於ける外部接続用パッド612Bと、前記支持基板11の導電層112Aは、ボンディングワイヤ265により接続されている。

【0119】

更に、前記支持基板11、第1の半導体素子100は、支持基板11上にあって封止樹脂166により樹脂封止され、支持基板11の他方の主面には外部接続端子16が配設されている。

【0120】

この様な構造に於いて、前記配線基板600としては、セラミック、ガラス等の無機絶縁性基板、或いはシリコン(Si)、ガリウム砒素(GaAs)等の半導体基板を適用することができる。

【0121】

配線基板600として、半導体基板を適用した場合には、半導体素子の形成と同様のウエハプロセスを適用し、前記外部接続用パッド612を、アルミニューム(Al)、銅(Cu)、及びこれらの合金(例えば、Al95%−Cu5%合金等)等をもって形成することができる。

【0122】

また配線基板600を、当該配線基板600上に実装される半導体素子500と同じシリコン(Si)により形成することにより、両者の熱膨張係数を略同一にすることができ、半導体素子500の外部接続用パッド502と配線基板600の外部接続用パッド602との間に配設される接続部材14に於ける応力の集中を低減することができる。

【0123】

従って、半導体素子500と配線基板600との間の電気的・機械的接続を高い信頼性をもって実現することができる。

【0124】

ウエハプロセスの適用により、外部接続用パッド502及び外部接続用パッド612Bのピッチをより微細なものとすることができ、半導体装置の小型化及び高集積化を図ることができる。更に、半導体素子500の外部接続用パッド502の配設数を容易に増加させることができ、半導体装置の高機能化及び多ビット化に対応することができる。

【0125】

また、前記配線基板600として半導体基板を適用した場合には、当該配線基板600に半導体集積回路が形成されてもよい。

【0126】

当該配線基板600に半導体集積回路を形成することにより、複数個の半導体素子を3次元に実装してパッケージ化した所謂チップ・オン・チップ(COC:Chip−On−Chip)型の半導体装置を構成することができ、実装面積をより小とすることができる。

【0127】

更に、当該配線基板600には、必要に応じて多層配線構造が適用されてよく、またその表面或いは内層の配線部に、抵抗素子、容量素子或いはインダクタンス素子等の受動素子が搭載、或いは形成されてもよい。

【0128】

前述の如く、本実施例にあっては、半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503と、配線基板600の外部接続用パッド612A上に設けられた凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされ、且つ当該平面に垂直な方向には重畳した(互いに入り込んだ)状態とされて、接続部材14により機械的・電気的に固着・接続されている。

【0129】

かかる凸状外部接続端子503と凸状外部接続端子603との相互接続構造を、図10(A)に拡大して示す。

【0130】

外部接続用パッド502に於ける凸状外部接続端子503の配設箇所と外部接続用パッド612Bに於ける凸状外部接続端子603との配設箇所は、半導体素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされて、図9に於ける横方向即ち半導体素子500或いは配線基板600の幅方向に於いて、互いに異なる位置とされている。

【0131】

加えて、当該凸状外部接続端子503と凸状外部接続端子603は、当該平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向には、寸法Aに相当する高さ分重畳した(互いに入り込んだ)状態とされている。

【0132】

この様な接続・固着構造にあっては、凸状外部接続端子503と凸状外部接続端子603とが横方向に異なる位置に在り、且つその先端部は異なる平面に位置する。

【0133】

従って、熱的或いは機械的ストレスによって、凸状外部接続端子503の先端部と接続部材14との界面及び凸状外部接続端子603の先端部と接続部材14との界面にクラックが生じても、一方の凸状外部接続端子の先端部に於けるクラックが他方の凸状外部接続端子の先端部に於けるクラックに伝搬して連続することは生じない。

【0134】

従って、当該凸状外部接続端子503と凸状外部接続端子603の周囲を覆う接続部材14の全体にわたるクラックの発生、接続部材14の破断を招来せず、強固な固着・接続が維持される。

【0135】

即ち、本実施例に於ける凸状外部接続端子配設構造によれば、接続部材14において、応力が集中する部位、即ち、クラックが発生し得る部位は分散されるため、半導体素子500と配線基板600との間の電気的・機械的接続は高い信頼性をもって実現される。

【0136】

前述の如く、前記半導体基板11、配線基板600、及び半導体素子500は、封止樹脂166により樹脂封止される。

【0137】

従って、本実施例における半導体装置の製造工程中に印加される熱応力及び/或いは機械的応力等により、或いは半導体素子500、配線基板500、及び支持基板11との熱膨張係数の違いに基づき、接続部材14に応力が集中する恐れがある。

【0138】

しかしながら、本実施例に於ける半導体装置にあっては、半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503と、配線基板600の外部接続用パッド612A上に設けられた凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされ、且つ当該平面に垂直な方向には重畳した(互いに入り込んだ)状態とされて、接続部材14により機械的・電気的に固着・接続されている。

【0139】

かかる構成により、応力が集中してクラックが発生し得る部位が分散され、半導体素子500と配線基板600との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0140】

尚、外部接続用パッド502上に設けられた凸状外部接続端子503の先端部と、外部接続用パッド612B上に設けられた凸状外部接続端子603の先端部が、図10(b)に示すように、半導体素子500の厚さ方向(図10に於ける縦方向)において略一致、即ち同一平面上に位置すると、熱的或いは機械的ストレスによって、凸状外部接続端子503と接続部材14との界面及び凸状外部接続端子603の先端部と接続部材14との界面にクラックが生じた場合、一方の凸状外部接続端子の先端部に於けるクラックが他方の凸状外部接続端子の先端部に於けるクラックに容易に伝搬して連続し、当該接続部材14が最終的に破断してしまう可能性が大きい。

【0141】

本実施例の様に、半導体素子の電極パッドとこれに対応する支持基板上の電極パッドとの間を複数個の凸状外部接続端子を用いて接続する構成に於いて、前記図9、図10(a)に示される如く、当該半導体素子の電極パッドと支持基板上の電極パッドのそれぞれに凸状外部接続端子を配設し、且つ当該凸状外部接続端子の位置ならびに高さを設定する構成は、前記第1乃至第3実施例に於ける半導体素子の搭載構造に適用することができる。

【0142】

かかる半導体素子の電極パッドと支持基板上の電極パッドのそれぞれに凸状外部接続端子を配設し、且つ当該凸状外部接続端子の位置ならびに高さを設定する構成を、前記第1実施例に示される半導体装置に適用した例を図11に示す。

【0143】

図11を参照するに、支持基板11の導電層12Aには、凸状外部接続端子19が配設され、一方、半導体素子100の外部接続用パッド102には、凸状外部接続端子119が配設されている。

【0144】

即ち、半導体素子100の外部接続用パッド102上に形成された凸状外部接続端子19と、支持基板11の外部接続用パッド102上に形成された凸状外部接続端子119は、その先端部を対向することなく、即ち当該半導体層素子100の表面或いは支持基板11の表面と平行な平面に於いて位置が異ならしめられた状態とされ、且つ当該平面に垂直な方向には重畳した(互いに入り込んだ)状態とされて、接続部材14により機械的・電気的に固着・接続されている。

【0145】

そして、当該凸状外部接続端子19及び凸状外部接続端子119は、半導体素子100の縁部の延びる方向に対して直角方向に並んで配設されている。

【0146】

かかる構成によれば、接続部材14に於いて応力が集中する部位、即ち、クラックが発生し得る部位が分散されるため、半導体素子100と支持基板11との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0147】

当該第4の実施例における半導体装置の、製造工程の要部について、図12を用いて説明する。

【0148】

同図(a)は、ボンディングステージ401上に載置・固定された配線基板600と、吸着用治具402に吸着保持された半導体素子500とを対向させた状態を示す。

【0149】

半導体素子500の外部接続用パッド502上には凸状外部接続端子503が、また、配線基板600の外部接続用パッド612B上には凸状外部接続端子603が形成されている。

【0150】

外部接続用パッド502及び612Bの周囲は、窒化シリコン(Si3N4)などからなる表面保護膜104により被覆されている。

【0151】

図示されるように、半導体素子500の外部接続用パッド502上に形成された凸状外部接続端子503と、配線基板600の外部接続用パッド602上に形成された凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは支持基板600の表面と平行な平面に於いて位置が異ならしめられて配置される。

【0152】

尚、かかる対向状態とする前に、半導体素子500の凸状外部接続端子503或いは配線基板600の凸状外部接続端子603の少なくとも一方に、予め接続部材14を被着形成しておく。

【0153】

図示される例では、当該接続部材14が半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503の先端に被覆形成されているが、勿論配線基板600の外部接続用パッド612B上に設けられた凸状外部接続端子603の先端に被着形成してもよい。また凸状外部接続端子503及び凸状外部接続端子603の双方に被着形成してもよい。

【0154】

凸状外部接続端子503と凸状外部接続端子603の双方に被着形成することにより、外部接続用パッド502と外部接続用パッド612Bとの間に接続部材14を均一に配設することができる。

【0155】

接続部材14が銀ペースト等の導電性樹脂から成る場合には、当該接続部材14を凸状外部接続端子503及び凸状外部接続端子603の双方に被着することにより、より均一に配設することができる。

【0156】

このように、半導体素子500と配線基板600とを対向させた状態において、ボンディングステージ401を前記接続部材14の融点以上の温度(例えば280℃〜300℃)に加熱すると共に、吸着用治具402を降下させて、溶融した接続部材14中に凸状外部接続端子503及び603を圧入する。

【0157】

尚、この時吸着用治具402も所定温度(例えば80℃〜200℃)に加熱してもよい。

【0158】

この結果、接続部材14は、凸状外部接続端子503又は603を覆うと共に、外部接続用端子パッド502及び612Aの露出表面にも接して、外部接続用端子パッド502及び612A間を結合する。この時、凸状外部接続端子503及び603間の空間も、当該接続部材14により充填される。

【0159】

また、この時、凸状外部接続端子503と凸状外部接続端子603は、当該平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向に、前記図10(a)に示す寸法Aに相当する高さ分重畳した(互いに入り込んだ)状態とされている。かかる状態を、同図(b)に示す。

【0160】

この様に、外部接続用端子パッド502と凸状外部接続端子603とが、また外部接続用端子パッド612Aと凸状外部接続端子503とが、それぞれ接続部材14を介して接続・固着され、当該配線基板600上に半導体素子500が搭載された後、当該配線基板600と半導体素子500との間に、エポキシ系樹脂を主体とするアンダーフィル材15が充填される。かかる状態を、同図(C)に示す。

【0161】

次いで、前記配線基板600を支持基板11上に搭載し、配線基板600上の端子パッド612Bと支持基板11上の導電層112Aとをボンディングワイヤ265により接続する。

【0162】

次いで、支持基板11、配線基板600及び半導体素子500を封止樹脂166により樹脂封止する。

【0163】

しかる後、支持基板11の他方の主面に外部接続端子16を配設して、前記図9に示す半導体装置を形成する。

【実施例5】

【0164】

本発明の第5の実施例に於ける半導体装置を、図13及び図14に示す。

【0165】

当該第5の実施例に於ける半導体装置の断面構造を図13に示し、当該図13に於いて破線で囲んだ部分を拡大して図14に示す。

【0166】

なお、本実施例の説明に於いて、前記第1乃至第4の実施例に於ける部位と対応する部位については同じ符号を付し、その詳細な説明を省略する。

【0167】

図13及び図14を参照するに、本実施例における半導体装置にあっては、半導体素子500の外部接続用パッド502には、そのほぼ中央部に、1つの凸状外部接続端子503が配設されている。

【0168】

一方、配線基板600の外部接続用パッド612B上には、2つの凸状外部接続端子603−1及び603−2が、所定の間隔B(図14参照)をもって離間して配設されている。

【0169】

当該2つの凸状外部接続端子603−1と603−2の相互の間隔Bは、前記半導体素子500の外部接続用パッド502に設けられた凸状外部接続端子503の幅C(図14参照)よりも僅かに大きくされている。

【0170】

この様な凸状外部接続端子の配設構成によって、半導体素子500が配線基板600上にフリップチップ接続・固着される際、半導体素子500の外部接続用パッド502上の凸状外部接続端子503は、その先端部を配線基板600の外部接続用パッド612B上の2つの凸状外部接続端子603−1或いは603−2に対向することなく、当該凸状外部接続端子603−1と603−2との間に受容されている。

【0171】

そして、当該凸状外部接続端子603−1、凸状外部接続端子502及び凸状外部接続端子603−2は、半導体素子500の縁部の延びる方向に対して直角方向に並んで配設されている。

【0172】

また、この時、凸状外部接続端子503と凸状外部接続端子603−1、603−2は、半導体素子500或いは配線基板600の平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向に、寸法A(図14参照)に相当する高さ分重畳した(互いに入り込んだ)状態とされている。

【0173】

この様な接続・固着構造によれば、凸状外部接続端子503に対し、その両側に凸状外部接続端子603−1、603−2が位置することにより、前記実施例に示す構造に比して接続部材14との接触面積が増大し、配線基板600に対する半導体素子500の接続・固着強度を高めることができる。

【0174】

また、この様な接続・固着構造によれば、凸状外部接続端子503と凸状外部接続端子603−1、603−2とが横方向に異なる位置に在り、且つその先端部も異なる平面にあることから、熱的或いは機械的ストレスによって、凸状外部接続端子503の先端部と接続部材14との界面及び凸状外部接続端子603−1或いは603−2の先端部と接続部材14との界面にクラックが生じても、一つの凸状外部接続端子の先端部に於けるクラックが他の凸状外部接続端子の先端部に於けるクラックに伝搬して連続する可能性は極めて低い。即ち、横方向に異なる位置に在り、且つその先端部が互いに異なる平面にある3個の凸状外部接続端子先端部に於けるクラックが全て連続する確率は極めて低い。

【0175】

従って、凸状外部接続端子503と凸状外部接続端子603の周囲を覆う接続部材14の全体にわたるクラックの発生、接続部材14の破断を招来せず、強固な固着・接続が維持される。

【0176】

尚、図13及び図14に示す本実施例にあっては、半導体素子500の外部接続用パッド502に1つの凸状外部接続端子503を設け、配線基板600の外部接続用パッド612Bには2つの凸状外部接続端子603−1及び603−2を設けているが、勿論かかる構成に限定されるものではない。

【0177】

半導体素子500の外部接続用パッド502に複数個の凸状外部接続端子503を設け、配線基板600の外部接続用パッド612Bに一つの凸状外部接続端子603を設けることとしてもよく、また、半導体素子500の外部接続用パッド502並びに配線基板600の外部接続用パッド612A のそれぞれに複数個の凸状外部接続端子を設けてもよい。

【0178】

何れの構成にあっても、半導体素子500の凸状外部接続端子503と配線基板600の凸状外部接続端子603は、相互に横方向に異なる位置に在り、且つその先端部も異なる平面にあることが必要とされる。

【0179】

当該第5の実施例に於ける半導体装置の、製造工程の要部について、図15を用いて説明する。

【0180】

同図(a)は、ボンディングステージ401上に載置・固定された配線基板600と、吸着用治具402に吸着保持された半導体素子500とを対向させた状態を示す。

【0181】

半導体素子500の外部接続用パッド502上には1つの凸状外部接続端子503が、一方配線基板600の外部接続用パッド612B上には2つの凸状外部接続端子603−1及び603−2が間隔Bを有して離間して形成されている。

【0182】

そして、外部接続用パッド502及び612Bの周囲は、窒化シリコン(Si3N4)などからなる表面保護膜104により被覆されている。

【0183】

図示されるように、半導体素子500の外部接続用パッド502上に形成された凸状外部接続端子503と、配線基板600の外部接続用パッド602上に形成された凸状外部接続端子603−1及び603−2は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは支持基板600の表面と平行な平面に於いて位置が異ならしめられて配置され、配線基板600の凸状外部接続端子603−1と603−2との間に、半導体素子500の凸状外部接続端子503が位置している。

【0184】

尚、かかる対向状態とする前に、半導体素子500の凸状外部接続端子503或いは配線基板600の凸状外部接続端子603の少なくとも一方に、予め接続部材14を被着形成しておく。図(a)に示す例にあっては、半導体素子500の凸状外部接続端子503に接続部材14を被着形成している。

【0185】

この様に、半導体素子500と配線基板600とを対向させた状態において、ボンディングステージ401を前記接続部材14の融点以上の温度(例えば280℃〜300℃)に加熱すると共に、吸着用治具402を降下させて、溶融した接続部材14中に凸状外部接続端子503及び603を圧入する。

【0186】

この時、吸着用治具402を所定温度(例えば80℃〜200℃)に加熱してもよい。

【0187】

この結果、接続部材14は、凸状外部接続端子503、603−1及び603−2を覆うと共に、外部接続用端子パッド502及び612Aの露出表面にも接して、外部接続用端子パッド502及び612A間を結合する。凸状外部接続端子503と凸状外部接続端子603−1、603−2間の空間も、当該接続部材14により充填される。

【0188】

この時、凸状外部接続端子503と凸状外部接続端子603は、当該平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向に、前記図10(a)に示す寸法Aに相当する高さ分重畳した(互いに入り込んだ)状態とされている。かかる状態を、同図(b)に示す。

【0189】

この様に、外部接続用端子パッド502と凸状外部接続端子603とが、また外部接続用端子パッド612Aと凸状外部接続端子503とが接続部材14を介して接続・固着され、当該配線基板600上に半導体素子500が搭載された後、当該配線基板600と半導体素子500との間に、エポキシ系樹脂を主体とするアンダーフィル材15が充填される。かかる状態を、同図(C)に示す。

【0190】

次いで、前記配線基板600を、支持基板11上に搭載し、配線基板600上の端子パッド612Bと支持基板11上の導電層112Aとをボンディングワイヤ265により接続する。

【0191】

次いで、支持基板11、配線基板600及び半導体素子500を封止樹脂166により樹脂封止する。

【0192】

しかる後、支持基板11の他方の主面に外部接続端子16を配設して、図13に示す半導体装置を形成する。

【0193】

以上、本発明の実施の形態について詳述したが、本発明は特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形及び変更が可能である。

【0194】

一つに、前記半導体素子の外部接続用パッド上に設けられる凸状外部接続端子は、金、銅、ニッケル又はこれらの合金等から形成され、例えば金属ワイヤを用いたボールボンディング法により形成されるスタッドバンプ、或いはめっき法により形成されるバンプを適用することができる。

【0195】

また、前記配線基板が、ガラスエポキシ、ガラスビスマレイミドトリアジン(BT:Bismaleimide−Triazine)、ポリイミド等の有機絶縁材料或いはセラミック、ガラス等の無機絶縁材料から成る場合には、外部接続用パッドを表面に下層側からニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層が形成された銅(Cu)から形成し、当該外部接続用パッドに対し、金(Au)、銅(Cu)及びこれらの合金等からなる金属ワイヤを用いてボールボンディング法により、凸状外部接続端子503を形成することができる。

【0196】

或いは、銅(Cu)等からなる外部接続用パッド上に、銀(Ag)等からなる凸状外部接続端子を印刷法、転写法、インクジェット法等で形成し、外部接続用パッド及び凸状外部接続端子全体に下層側からニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層を被覆形成してもよい。

【0197】

更には、銅(Cu)等からなる外部接続用パッドにエッチング処理を施し、局所的に凸状外部接続端子を形成し、下層側からニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層を被覆形成してもよい。

【0198】

或いは、銅(Cu)等からなる外部接続用パッド上に局所的に銅(Cu)めっきを施して凸状外部接続端子を形成し、下層よりニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層を被覆形成してもよい。

【0199】

一方、配線基板が、シリコン(Si)、ガリウム砒素(GaAs)等の半導体基板から成る場合には、外部接続用パッドをアルミニューム(Al)、銅(Cu)、及びこれらの合金等から形成し、当該外部接続用パッド上に下層側よりニッケル(Ni)/金(Au)、チタン(Ti)/タングステン(W)/金(Au)、チタン(Ti)/パラジウム(Pd)/金(Au)、或いはチタン(Ti)/ニッケル(Ni)/パラジウム(Pd)/金(Au)等の金属被膜を形成し、当該金属被膜上に、金(Au)、銅(Cu)及びこれらの合金等から成る金属ワイヤを用いてボールボンディングすることにより、凸状外部接続端子を形成することができる。

【0200】

或いは、前記アルミニューム(Al)、銅(Cu)、及びこれらの合金等から成る外部接続用パッド上に、下層側よりチタン(Ti)/タングステン(W)、下層側からチタン(Ti)/タングステン(W)/金(Au)、下層側からチタン(Ti)/パラジウム(Pd)、下層側からチタン(Ti)/パラジウム(Pd)/金(Au)、或いは下層側からチタン(Ti)/ニッケル(Ni)/パラジウム(Pd)等の金属被膜を形成し、当該金属被膜上に電解めっき法により金(Au)、銅(Cu)等から成る凸状外部接続端子を形成してもよい。

【0201】

また、外部接続用パッドに於ける、少なくとも凸状外部接続端子が形成されていない箇所の表面(最上層)には、電解めっき法又は蒸着法等により金(Au)層を形成しておくことが望ましい。

【0202】

かかる金(Au)層を形成しておくことにより、接続部材として半田を用いる場合、当該半田が外部接続用パッドの表面(最上層)において濡れ広がることを確保することができる。

【0203】

また、凸状外部接続端子としてスタッドバンプを適用する場合、当該凸状外部接続端子を形成する箇所の表面(最上層)に、予め金(Au)層を形成しておくことにより、金(Au)線を用いたスタッドバンプを容易に形成することができる。

【0204】

なお、当該下地金(Au)層の形成にあっては、当該金(Au)層と凸状外部接続端子の表面(最上層)との間に、下層としてチタン(Ti)、タングステン(W)、パラジウム(Pd)、ニッケル(Ni)、又はこれらの合金等の金属層を形成することが望ましい。これらの金属層により、外部接続用パッドの腐食を防止することができ、また、層間密着力の向上等を図ることができる。

【0205】

具体的には、当該金(Au)層と凸状外部接続端子の表面(最上層)との間に、外部接続用パッド側からニッケル(Ni)、チタン(Ti)/タングステン(W)、チタン(Ti)/パラジウム(Pd)、或いはチタン(Ti)/ニッケル(Ni)/パラジウム(Pd)を設けることが望ましい。

【0206】

また、前記接続部材としては、錫(Sn)−銀(Ag)、錫(Sn)−銀(Ag)−銅(Cu)、又は錫(Sn)−銀(Sg)−インジウム(In)から成る半田、或いは銀(Ag)、銅(Cu)、銅合金等の金属粒子或いはこれら金属の金属被膜を形成した粒子等を含むエポキシ樹脂等の導電性樹脂を用いることができる。

【0207】

かかる接続部材は、外部接続用パッドの表面への選択的電解めっき法、又は他の基板上に塗布され均一な厚さとされた接続部材層に凸状外部接続端子の先端を接触させて当該先端に接続部材を付着させる転写法、或いはペースト状または微細粒子状の接続部材をマイクロノズルより噴出して凸状外部接続端子の先端に局所的に付着させる方法等により形成することができる。

【0208】

以上の説明に関し、更に以下の項を開示する。

(付記1) 半導体基板の一方の主面に外部接続用端子パッドを具備する半導体素子が、前記外部接続用端子パッド上に配設された凸状外部接続端子及び接続部材を介して、支持基板上の導電層に接続される半導体装置であって、

前記外部接続用端子パッドは複数個の凸状外部接続端子を具備し、前記接続部材は当該複数個の凸状外部接続端子を共通に被覆してなることを特徴とする半導体装置。

(付記2) 半導体基板、前記半導体基板の一方の主面に配設された外部接続用端子パッド、及び前記外部接続用端子パッド上に複数個配設された凸状外部接続端子を具備する半導体素子と、

絶縁性基板、前記絶縁基板の一方の主面に配設された導電層、及び前記絶縁基板の前記一方の主面上に配設されて前記導電層を選択的に被覆する絶縁層を具備する支持基板と、

前記絶縁層に被覆されない前記導電層に、前記複数個の凸状外部接続端子を共通に被覆して固着する接続部材と、を具備することを特徴とする半導体装置。

(付記3) 半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設されてなる半導体素子と、

前記外部接続用端子パッドに対応した複数個の導電層が配設され、当該導電層上に少なくとも一つの第2の凸状外部接続端子が配設されてなる支持基板と、を具備し、

前記第1の凸状外部接続端子が接続部材を介して前記導電層に接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

(付記4) 付記3記載の半導体装置であって、

前記外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記導電層における前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

(付記5) 付記4記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

(付記6) 付記1乃至5いずれか一項記載の半導体装置であって、

前記半導体素子は第1の半導体素子として機能し、

前記第1の半導体素子の上に第2の半導体素子が接着固定されていることを特徴とする半導体装置。

(付記7) 付記1乃至6いずれか一項記載の半導体装置であって、

前記複数個の外部接続端子パッドは、前記半導体基板の略中央において列を形成して配設されえていることを特徴とする半導体装置。

(付記8) 付記6及び7記載の半導体装置であって、

前記第1の半導体素子、前記第2の半導体素子及び前記支持基板は封止樹脂により封止されていることを特徴とする半導体装置。

(付記9) 支持基板と、

前記支持基板の上に実装された配線基板を介して前記支持基板に接続され、前記配線基板の上に実装された半導体素子と、を備えた半導体装置であって、

前記半導体素子の半導体基板の主面のうち、前記配線基板に面した側の面に複数個の半導体素子外部接続用端子パッドが配設され、当該半導体素子外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設され、

前記配線基板の主面のうち、前記半導体素子に面した側の面に複数個の配線基板外部接続用端子パッドが配設され、当該配線基板外部接続用端子パッド上に少なくとも一つの第2の凸状外部接続端子が配設され、

前記第1の凸状外部接続端子が接続部材を介して前記配線基板外部接続用端子パッドに接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記半導体素子外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

(付記10) 付記9記載の半導体装置であって、

前記半導体素子外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記配線基板外部接続用端子パッドにおける前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

(付記11) 付記10記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

(付記12) 付記9乃至11いずれか一項記載の半導体装置であって、

前記配線基板は、有機材料、セラミック、又はガラスから選択される材料から構成されていることを特徴とする半導体装置。

(付記13) 付記9乃至11いずれか一項記載の半導体装置であって、

前記配線基板は、シリコンから成ることを特徴とする半導体装置。

(付記14) 付記13記載の半導体装置であって、

前記配線基板に、半導体集積回路が形成されていることを特徴とする半導体装置。

(付記15) 付記9及び14記載の半導体装置であって、

前記半導体素子、前記配線基板及び前記支持基板は封止樹脂により封止されていることを特徴とする半導体装置。

【図面の簡単な説明】

【0209】

【図1】本発明の第1の実施例における半導体装置の構造を示す、断面図である。

【図2】本発明の第1の実施例における半導体装置に於いて、支持基板の主面に配設される導電層の形状を示す平面図である。

【図3】本発明の第1の実施例における半導体装置に於いて、支持基板の主面に配設される導電層の配設例の変形例を示す平面図である。

【図4】本発明の第1の実施例における半導体装置に於いて、半導体素子の凸状外部接続端子の構成を示す平面図及び断面図である。

【図5】本発明の第1の実施例における半導体装置の製造工程を示す断面図である。

【図6】本発明の第2の実施例における半導体装置に於いて、凸状外部接続端子が配設された半導体素子の主面を示す平面図である。

【図7】本発明の第2の実施例における半導体装置の構造を示す、断面図である。

【図8】本発明の第3の実施例における半導体装置の構造を示す、断面図である。

【図9】本発明の第4の実施例における半導体装置の構造を示す、断面図である。

【図10】図9において点線で囲んだ部分を説明するための図である。

【図11】本発明の第4の実施例の半導体素子の外部接続用パッドと配線基板の外部接続用パッドとの接続構造を、図1に示す半導体装置に適用した場合の、当該半導体装置の断面図である。

【図12】本発明の第4の実施例における半導体装置の製造工程を示す断面図である。

【図13】本発明の第5の実施例における半導体装置の構造を示す、断面図である。

【図14】図13において点線で囲んだ部分の拡大図である。

【図15】本発明の第5の実施例における半導体装置の製造工程を示す断面図である。

【符号の説明】

【0210】

11 支持基板

12 導電層

13 ソルダーレジスト

14 接続部材

15 アンダーフィル材

19、103、119、153、503、603 凸状外部接続端子

100、150、160、500 半導体素子

101、151、161、501 半導体基板

102、152、502、612B 外部接続用パッド

200 接続領域

301 台座部

302 突出する部位

401 ボンディングステージ

402 吸着用治具

600 配線基板

【技術分野】

【0001】

本発明は、半導体装置に関し、より具体的には、支持基板の主面に選択的に配設された導電層に対して、半導体素子の主面上に配設された凸状電極が接続固着されて構成される半導体装置の電極接続構造に関する。

【背景技術】

【0002】

ガラスエポキシ樹脂などの絶縁性樹脂を基材とし、その表面に銅(Cu)などからなる導電層が選択的に配設された配線用基板を複数積層して形成された支持基板を用い、その一方の主面に選択的に配設された導電層に、半導体集積回路素子(以下半導体素子と称する)の主面に配設された凸状電極が接続され、一方、前記支持基板の他方の主面には選択的に形成された導電層の表面に球状電極端子などの外部接続端子が配設されてなる半導体装置がある。即ち、半導体素子は所謂フェイスダウン状態で、支持基板に搭載されている。

【0003】

かかる構成に於いては、前記半導体素子の主面にあって、外部接続用端子パッド上に所謂ボールボンディング法によって金(Au)ボールが圧接固着・接続されて台座部及び当該台座部上に突出する部位からなる凸状の外部接続端子が形成される。尚、当該突出する部位は、必要に応じて平坦化処理がなされる。このように、金線など軟質の金属線を用いて形成され、台座部とその上に突出する部位とからなる端子構造は、スタッドバンプ(Stud bump)と称される。

【0004】

このように、台座部とその上に突出する部位とからなる端子構造は、その表面積が大きいことから、前記支持基板上の導電層に対して、はんだなどの導電性部材をもって容易に接続固着される。

【0005】

このような接続形態は比較的安価に実施することができることから、外部接続端子数が数個〜数百個の比較的小型の半導体素子への適用がなされている。

【特許文献1】特開平2−163950号公報

【特許文献2】特開平10−117065号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述の半導体装置を形成する際には、例えば支持基板の一方の主面に配設された導電層の表面に選択的にはんだなどの導電性部材を配設した後、当該導電性部材上に半導体素子の凸状外部接続端子を接触させ、かかる状態に於いて導電性部材の融点以上の温度に加熱して当該導電性部材を溶融せしめる。

【0007】

しかる後、常温など導電性部材の融点以下の温度とすることにより当該導電性部材は固化し、半導体素子の凸状外部接続端子は、支持基板上の導電層に機械的・電気的に接続される。

【0008】

ところが、この様に昇温・降温工程が執られることから、半導体素子と支持基板との熱膨張係数の違いに基づく応力が半導体素子の凸状外部接続端子と支持基板上の導電層との間に於ける導電性部材部分に集中して、当該導電性部材にクラック(割れ)を生じ、半導体素子の凸状外部接続端子と支持基板上の導電層との電気的接続が破断されてしまう。

【0009】

降温直後にあってはクラックが生じなくとも、半導体素子の凸状外部接続端子と支持基板の導電層との間に於ける導電性部材部分には応力が集中して残存することから、その後の製造工程に於ける温度変化あるいは振動などによりクラックを生じてしまう。

【0010】

更に、製造工程に於いてはクラックを生ずることがなかった場合であっても、半導体装置として実働する際にクラックを生ずる可能性が残り、半導体装置としての信頼性の低下を招来してしまう。

【0011】

前記支持基板として両面配線基板など板厚の薄い基板を用いる場合には、その反り量が大きいことから、クラックの発生を招来する可能性が大きい。

【0012】

そこで、本発明は、上記の点に鑑みてなされたものであって、このような半導体装置に於ける、半導体素子の凸状外部接続端子と支持基板上の導電層との間の機械的・電気的接続を高い信頼性をもって実現することができる半導体装置構造を提供することを本発明の目的とする。

【課題を解決するための手段】

【0013】

本発明の一観点によれば、半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に複数個の凸状外部接続端子が配設されてなる半導体素子が、前記複数個の凸状外部接続端子を共通に被覆する接続部材を介して、支持基板の一方の主面上に配設された導電層に固着されてなることを特徴とする半導体装置が提供される。

【0014】

本発明の別の観点によれば、半導体基板、前記半導体基板の一方の主面に配設された外部接続用端子パッド、及び前記外部接続用端子パッド上に複数個配設された凸状外部接続端子を具備する半導体素子、絶縁性基板、前記絶縁基板の一方の主面に配設された導電層、及び前記絶縁基板の前記一方の主面上に配設されて前記導電層を選択的に被覆する絶縁層を具備する支持基板、前記絶縁層に被覆されない前記導電層に、前記複数個の凸状外部接続端子を共通に被覆して固着する接続部材を具備することを特徴とする半導体装置が提供される。

【0015】

本発明の更に別の観点によれば、半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設されてなる半導体素子と、前記外部接続用端子パッドに対応した複数個の導電層が配設され、当該導電層上に少なくとも一つの第2の凸状外部接続端子が配設されてなる支持基板と、を具備し、前記第1の凸状外部接続端子が接続部材を介して前記導電層に接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記外部接続用端子パッドに接続されてなることを特徴とする半導体装置が提供される。

【0016】

本発明の更に別の観点によれば、支持基板と、前記支持基板の上に実装された配線基板を介して前記支持基板に接続され、前記配線基板の上に実装された半導体素子と、を備えた半導体装置であって、前記半導体素子の半導体基板の主面のうち、前記配線基板に面した側の面に複数個の半導体素子外部接続用端子パッドが配設され、当該半導体素子外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設され、前記配線基板の主面のうち、前記半導体素子に面した側の面に複数個の配線基板外部接続用端子パッドが配設され、当該配線基板外部接続用端子パッド上に少なくとも一つの第2の凸状外部接続端子が配設され、前記第1の凸状外部接続端子が接続部材を介して前記配線基板外部接続用端子パッドに接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記半導体素子外部接続用端子パッドに接続されてなることを特徴とする半導体装置が提供される。

【発明の効果】

【0017】

本発明によれば、半導体素子に於ける一つの外部接続端子パッド上には複数個、即ち少なくとも2個の凸状外部接続端子が配設される。

【0018】

これにより、半導体素子の一つの外部接続端子に於ける凸状外部接続端子と支持基板上の導電層との対向面積が、前記従来技術に比してほぼ倍増する。即ち、半導体素子の凸状外部接続端子と支持基板上の導電層との間に介在される接続部材との接触面積が増加することから、前記昇温・降温の際に生じるストレスが当該凸状外部接続端子と支持基板上の導電層との間に集中し、或いは残存したとしても、当該ストレスはより広い範囲に分散される。

【0019】

この結果、半導体素子の凸状外部接続端子と支持基板上の導電層との間に於ける接続部材の全域に跨がってクラックを生ずる恐れが大きく低減する。

【0020】

従って、当該半導体素子と支持基板との間の電気的・機械的接続が、高い信頼性をもって実現される。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施の形態について説明する。

【実施例1】

【0022】

本発明に基づき、半導体素子の凸状外部接続端子と支持基板上の導電層との間の機械的・電気的接続がなされた、本発明の第1の実施例である半導体装置を、図1に示す。

【0023】

同図に於いて、11はガラスエポキシ樹脂などの絶縁性樹脂を基材とし、その表面に銅(Cu)などからなる配線層が選択的に配設された基板が複数積層されて形成された支持基板である。当該支持基板11は、インターポーザー或いは配線基板と称される場合もある。

【0024】

また、12Aは当該支持基板11の一方の主面上に選択的に配設された導電層であって、銅(Cu)層から構成されている。当該導電層12Aは、当該支持基板11に搭載される半導体素子(後述)の外部接続端子が接続される導電層および配線層を含み、当該半導体素子の外部接続端子が接続される領域を除いてソルダーレジスト層13Aにより選択的に被覆されている。即ち、当該ソルダーレジスト層13Aは、導電層12Aに於ける、半導体素子との接続領域を画定している。

【0025】

また、100は、シリコン(Si)半導体基板101を用い、周知の半導体製造プロセスをもって形成された半導体集積回路素子(以下半導体素子と称する)である。

【0026】

勿論、半導体基板として、ガリウム砒素(GaAs)等の化合物半導体を適用した半導体集積回路素子を具備する半導体装置に対しても本発明を適用することができる。

【0027】

本実施例にあっては、当該半導体基板101の一方の主面に選択的に(例えば、当該主面の四辺近傍において当該四辺に沿って、又は対向する二辺近傍において当該二辺に沿って)配設された複数個の外部接続用パッド102には、それぞれ2個の凸状外部接続端子103A、103Bが並設されている。

【0028】

即ち、当該外部接続用パッド102上に於いて、凸状外部接続端子103A、103Bは、半導体素子100の縁部の延びる方向に対して直角方向に並んで配設されている。

【0029】

尚、ここでは、当該半導体素子100にあって、シリコン半導体基板101内に形成された能動素子及び/或いは受動素子、並びに当該一方の主面上に形成された多層配線層及び/或いは再配線層を図示することを省略している。

【0030】

前記外部接続用パッド102は、アルミニューム(Al)、銅(Cu)、及びこれらの合金(例えば、Al95%−Cu5%合金等)等をもって形成されており、また凸状外部接続端子103は、前述の従来技術と同様、所謂ボールボンディング法によって金(Au)ボールが圧接固着・接続されて台座部が形成され、更に当該台座部上に突出する部位からなる凸状の外部接続端子が一体に形成されている。金線の突出部分の頂部は必要に応じて平坦化処理がなされる。

【0031】

なお、外部接続端子パッド102の露出表面(最上層)には、電解めっき法又は蒸着法等により金(Au)層を形成しておくことが望ましい。

【0032】

かかる半導体素子100の凸状外部接続端子103A、103Bと、これに対応する前記支持基板11上の導電層12Aは、はんだ或いは導電性接着剤等からなる接続部材14によって共通に被覆され、機械的・電気的に接続されている。並設された2個の凸状外部接続端子103A、103Bは、広い接触面積をもって、導電層12Aに接続・固着されている。

【0033】

即ち、当該半導体素子100は、支持基板11の一方の主面上にフリップチップ(フェイスダウン)方式をもって搭載・固着されている。

【0034】

そして、当該半導体素子100と支持基板11の一方の主面との間には、エポキシ系樹脂を主体とするアンダーフィル材15が充填されている。

【0035】

一方、前記支持基板11の他方の主面には、外部接続端子16の配設用或いは配線層を含む導電層12Bが選択的に配設されている。当該導電層12Bはソルダーレジスト層13Bにより選択的に被覆されており、当該ソルダーレジスト層13Bは外部接続端子16の配設領域を画定している。当該ソルダーレジスト層13Bにより画定された導電層12Bには、はんだを主体とする外部接続端子16が配設されている。

【0036】

尚、かかる支持基板11に於ける外部接続用端子部の配設構造は、ここに示す形態に特定されるものではない。支持基板11の一方の主面、即ち半導体素子100が搭載される主面に於いて、当該半導体素子100の周囲に外部接続用端子を配設することも可能であり、また外部接続用端子の導出構造もワイヤボンディング法、ボール・グリッド・アレイ(BGA)構造など適宜選択することができる。

【0037】

また、当該支持基板11は、前述の多層構造の配線基板に限られるものではなく、単一の絶縁基板の表裏両面に導電層が配設された所謂両面配線基板、或いは単一の絶縁基板の片面に導電層が配設された片面配線基板を適用することもできる。

【0038】

前記支持基板11の一方の主面に於いて、半導体素子100の凸状外部接続端子103A、103Bが接続される導電層12Aの平面形状を、図2(a)〜(c)に示す。ここでは、導電層12Aが3本(条)並んで配設された状態に於ける形態を示す。

【0039】

同図(a)に示される形態にあっては、ソルダーレジスト層13Aによって半導体素子100の凸状外部接続端子との接続領域200が規定される導電層12Aは、当該ソルダーレジスト層13A下に延在する領域と同一の幅を有している。接続領域200内にあって、円201は、半導体素子100の凸状外部接続端子103A、103Bが接続される部位を示す。

【0040】

また、同図(b)に示される形態にあっては、ソルダーレジスト層13Aによって半導体素子100の凸状外部接続端子との接続領域200が規定される導電層12Aは、当該ソルダーレジスト層13A下に延在する領域よりも幅広とされている。接続領域200内にあって、円201は、半導体素子100の凸状外部接続端子103A、103Bが接続される部位を示す。

【0041】

かかる形態によれば、前記(a)に示す形態に比して、接続領域200に収容可能な接続部材14の量を増加させることができ、凸状外部接続端子103A、103Bと、導電層12Aとの接続をより強固に行うことができる。

【0042】

一方、同図(c)に示される形態にあっては、ソルダーレジスト層13Aによって半導体素子101の凸状外部接続端子との接続領域200が規定される導電層12Aは、当該ソルダーレジスト層13A下に延在する領域よりも幅広とされ、且つ半導体素子100の凸状外部接続端子103A、103Bが接続される部位の間203にあってはその幅を狭く、ソルダーレジスト層13A下に延在する領域と同等の幅とされている。

【0043】

かかる形態によれば、前記(a)に示す形態に比して、接続領域200に収容可能な接続部材14の量を増加させることができ、且つ凸状外部接続端子103A、103Bが接続される部位間にあっては幅狭とされていることにより、接続部材14の量が過多にならないように所定の量に制御することが容易となる。

【0044】

これにより、凸状外部接続端子103A、103Bと導電層12Aとの接続を、より強固に行うことができ、且つ半導体素子100の外部接続用パッド102のパッドピッチが微細になった場合であっても、隣接する外部接続用パッド間での接続部材14のブリッジによる短絡の発生を抑制することができる。

【0045】

このように、図2(a)乃至(c)に示す構成にあっては、支持基板11上に配設された導電層12Aは、半導体素子101の凸状外部接続端子103が接続される接続領域200を表出し、当該接続領域200の周囲はソルダーレジスト層13Aにより被覆された構造を有する。

【0046】

前記支持基板11の一方の主面に於いて、半導体素子100の凸状外部接続端子103A、103Bが接続される導電層12Aを覆うソルダーレジスト13Aの被覆形状は、このような形状に限られるものではない。

【0047】

当該ソルダーレジスト13Aの被覆形状の変形例を、図3に示す。同図(a)乃至(c)に示される導電層12Aの形状は、前記図2(a)乃至(c)に示される導電層の形状に対応している。

【0048】

図3に示される例にあっては、隣接する導電層12Aは、接続領域201から離間した位置に於いて、ソルダーレジスト13Aにより共通に被覆されている。隣接する接続領域201間にはソルダーレジスト13Aは配設されておらず、支持基板11が表出している。

【0049】

この様なソルダーレジストの被覆形態は、導電層12Aの配設される間隔がより狭くされた場合に適用することができる。

【0050】

前記半導体素子100に於いて、一つの外部接続用パッド102上に並設された凸状外部接続端子103A、103Bの形態を図4に示す。同図(a)は当該凸状外部接続端子103A、103Bの配置の平面形状を示し、同図(b)は同図(a)のX−X断面を示す。

【0051】

同図に於いて、101はシリコン半導体基板、104は窒化シリコン(Si3N4)などからなる表面保護膜を示す。 尚、シリコン半導体基板101の主面に於ける他の導電層、絶縁層の表示は省略している。

【0052】

同図に於いて、凸状外部接続端子103A、103Bは、前述の如く、金(Au)ボールが圧接固着・接続されて台座部301及び当該台座部301上に突出する部位302からなり、一体に凸状に形成される。当該突出する部位302は、ボンディングツール(図示せず)の先端部の形状により前記金ボールの一部が整形されて生ずるものであって、必要に応じて平坦化処理がなされるが、ここでは当該平坦化処理を施していない。

【0053】

かかる形態に於いて、凸状外部接続端子103Aと103Bは、できるだけ近接して配置されることが望ましい。

【0054】

前記ボンディングツールの先端部の形状により制限を受けるものであるが、凸状外部接続端子103Aの台座部301Aと凸状外部接続端子103Bの台座部301Bとがより近接して配置されることにより両端子間の空間が減少し、これにより前記接続部材14の回り込みが容易になされ、両端子間に当該接続部材14の未充填領域(ボイド)を生じない。

【0055】

未充填領域を生じないことから、半導体素子100と支持基板11との間隙部にアンダーフィル材15を充填する際に、両端子間にアンダーフィル材15の未充填領域が生じることを抑制することができる。これにより、アンダーフィル材15内に於けるボイドの存在に起因する半導体装置の信頼性の低下を抑制することができる。

【0056】

本実施例に於ける半導体装置の製造工程を、図5に示す。

【0057】

同図(a)は、ボンディングステージ401上に載置・固定された支持基板101と、吸着用治具402に吸着保持された半導体素子100とを対向させた状態を示す。

【0058】

支持基板11の一方の主面に於ける導電層12Aには、予め例えば錫(Sn)を主体とするはんだ(半田)からなる接続部材14が選択的に被覆されている。

【0059】

当該接続部材14は、印刷法、メッキ法或いは蒸着・リフロー法などにより、被着・形成することができ、その厚さは5μm〜70μm程とされる。尚、導電層12Aは厚さ9μm〜25μm程の銅(Cu)から形成されるが、他の材料から適宜選択することができる。

【0060】

また、ソルダーレジスト層13Aは例えば5μm〜25μm程の厚さとされる。

【0061】

尚、支持基板11に於ける外部接続用端子部の構成は、前述の如く種々選択可能であることから、ここでは当該支持基板11の他方の主面に於ける導電層などの表示を省略する。

【0062】

一方、半導体素子100にあっては、シリコン半導体基板101の主面上に形成された多層配線層を含む絶縁層を介して配設された外部接続用端子パッド102上に、本発明思想に従って凸状外部接続端子103A、103Bが配設されている。

【0063】

外部接続用端子パッド102は、厚さ0.4μm〜1.5μm程のアルミニューム(Al)から形成されている。

【0064】

また、凸状外部接続端子103A、103Bは、外部接続用端子パッド102表面に所謂ボールボンディング法によって金(Au)ボールが圧接固着・接続されて、台座部(図4、301)が形成され、更に当該台座部上に突出する部位(図4、302)からなる凸状をもって一体に形成されている。

【0065】

当該台座部の直径は30μm〜60μm、厚さは5μm〜25μm程とされ、一方突出する部位は直径10μm〜50μm、その高さは10μm〜70μm程とされる。

【0066】

これらの寸法は、半導体素子に於ける設計ルールに基づき、端子パッドの面積、隣接する間隔或いは半導体装置として求められる高さなどから、適宜選択される。

【0067】

なお、外部接続用端子パッド102表面への凸状外部接続端子103A、103Bの形成は、上述したボールボンディング法の他、電解めっき法又は無電解めっき法により外部接続用端子パッド102表面に金(Au)、銅(Cu)、ニッケル(Ni)等の金属を析出させるめっき法を用いることで形成してもよい。

【0068】

また、外部接続用端子パッド102の露出表面(最上層)には、電解めっき法又は蒸着法等により金(Au)層を形成しておくことが望ましい。

【0069】

このように、導電層12Aと凸状外部接続端子103A、103Bとが位置合わせされ、対向された状態で、ボンディングステージ401を加熱・昇温して、前記接続部材14の融点以上の温度に加熱すると共に、前記吸着用治具402を降下させて、凸状外部接続端子103A、103Bを溶融状態にある接続部材14中に圧入する。

【0070】

この結果、当該接続部材14は、凸状外部接続端子103A、103Bを覆うと共に、外部接続用端子パッド102の露出表面にも接して、導電層12Aと外部接続用端子パッド102との間を結合する。この時、凸状外部接続端子103Aと103Bとの間の空間も、当該接続部材14により充填される。かかる状態を、同図(b)に示す。

【0071】

尚、ボンディングステージ401を加熱・昇温する代わりに、半導体素子100を、予め所定温度(例えば280℃〜300℃)に加熱された吸着用治具402に吸着・保持し、加熱・昇温された凸状外部接続端子103A、103Bを接続部材14に接触させることにより、当該接続部材14を昇温・溶融させてもよい。

【0072】

また、ボンディングステージ401を予め所定温度(例えば50℃〜100℃)に加熱して、支持基板11に対し予熱を印加しておくことにより、接続部材14をより短時間で昇温させることができる。

【0073】

このように、支持基板11上の導電層12Aに半導体素子100の凸状外部接続端子103A、103Bが接続・固着され、当該支持基板11に半導体素子100が搭載された後、当該支持基板11と半導体素子100との間に、エポキシ系樹脂を主体とするアンダーフィル材15が充填される。かかる状態を、同図(C)に示す。

【0074】

しかる後、支持基板11の前記一方の主面或いは他方の主面に、必要とする外部接続端子を形成する。

【実施例2】

【0075】

本発明の第2の実施例に於ける半導体装置を、図6及び図7に示す。

【0076】

図7は、図6に示される半導体素子150が支持基板11上に搭載された半導体装置構造を示し、図7に於ける半導体素子150は、図6のX−X'断面を示す。

【0077】

尚、前記第1の実施例に於ける構造と対応する部位には同一の符号を付している。

【0078】

図6及び図7を参照するに、当該第2の実施例に於ける半導体装置にあっては、DRAM(Dynamic Random Access Memory)等、複数個の外部接続用パッド152が半導体基板151の中央部に列状に並んで配設された構造を有する半導体素子150が、支持基板11にフリップチップ接続されている。

【0079】

本実施例に於ける半導体装置に於いては、前記第1の実施例に於ける半導体装置と同様に、外部接続用パッド152上に並設された凸状外部接続端子153A、153Bは、当該凸状外部接続端子153A、153Bを共通に被覆する接続部材14を介して、支持基板11の一方の主面上に配設された導電層12Aに固着されている。

【0080】

本実施例に於ける半導体装置にあっては、半導体素子150に於ける複数個の外部接続用パッド152が、半導体基板151の略中央に列状に配設されている。

【0081】

従って、当該半導体装置の製造工程に於いて、或いは当該半導体装置に於いて、半導体素子150の半導体基板151の略中央に配設された凸状外部接続端子153A、153Bと支持基板11上の導電層12Aとの間に於ける接続部材14に、半導体素子150と支持基板11との熱膨張係数の違いに基づく応力が集中して、当該接続部材14にクラックを生じ、凸状外部接続端子153A、153Bと導電層12Aとの電気的接続が破断されてしまう恐れがある。

【0082】

しかしながら、本実施例に於いても、1つの外部接続用パッド152に、2個の凸状外部接続端子153A、153Bが配設され、当該凸状外部接続端子153A、153Bは、当該凸状外部接続端子153A、153Bを共通に被覆する接続部材14を介して、支持基板11の一方の主面上に配設された導電層12Aに接続・固着されている。

【0083】

即ち、当該外部接続用パッド152上に於いて、凸状外部接続端子153A、153Bは、当該パッド配列の延びる方向に対して直角方向に並んで配設されている。

【0084】

従って、半導体素子150の凸状外部接続端子153A、153Bと支持基板11上の導電層12Aとの間に介在される接続部材14との接触面積が増加することから、半導体素子150と支持基板11との熱膨張係数の違いに基づく応力が、当該凸状外部接続端子153A、153Bと導電層12Aとの間に集中したとしても、当該応力はより広い範囲に分散される。

【0085】

従って、半導体素子150の凸状外部接続端子153A、153Bと支持基板11上の導電層12Aとの間に於ける接続部材14の全域に跨がってクラックを生ずる恐れは大きく低減する。このように、本実施例においても、半導体素子150と支持基板11との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0086】

尚、本実施例に於いても、導電層12Aの形状及び配設構造として、前記図2又は図3に示す構造を適用してよく、また凸状外部接続端子153A、153Bの配設形態も前記図4に示す形態を適用することができる。

【0087】

更に、支持基板11上に半導体素子150を実装する際の工程として、前記図5に示した工程を適用することができる。

【実施例3】

【0088】

本発明の第3の実施例に於ける半導体装置について、図8を参照して説明する。尚、前記第1の実施例に於ける構造と対応する部位には同一符号を付している。

【0089】

図8を参照するに、本発明の第3の実施例に於ける半導体装置は、前記第1の実施例に於ける半導体装置の半導体素子100、即ち支持基板11上にフリップチップ接続された半導体素子100(以下、本実施例においては「第1の半導体素子100」と称する)の背面上に、外部接続用パッド161が形成された面を上とした所謂フェイスアップ状態で、第2の半導体素子160が載置されてなる半導体素子積層構造を有する。

【0090】

当該第2の半導体素子160は、接着剤164を介して第1の半導体素子100の背面上に固着されている。接着剤164としては、エポキシ、ポリイミド等のフィルム状又はペースト状の樹脂接着剤を用いることができるが、これに限定されるものではない。

【0091】

そして、当該第2の半導体素子160の上面に配設された外部接続用パッド161と、前記支持基板11の第2半導体素子用導電層162(以下、本実施例においては、前記第1の実施例に於ける導電層12Aを第1半導体素子用導電層12Aと称する。)は、ボンディングワイヤ165により接続されている。

【0092】

また、第1の半導体素子100及び第2の半導体素子160は、支持基板11上に於いて、封止樹脂166によって樹脂封止されている。封止樹脂166としては、シリコン系樹脂、アクリル系樹脂或いはエポキシ系樹脂等を用いることができるが、これらに限定されない。

【0093】

このように、本実施例の半導体装置は、支持基板11上に実装された第1の半導体素子100の上に、第2の半導体素子160が載置・積層された構造を有する。

【0094】

当該半導体装置は、支持基板11上に第1の半導体素子100をフリップチップ実装し、次いで、当該第1の半導体素子100上に第2の半導体素子160を接着固定し、当該第2の半導体素子160の外部接続用パッド161と支持基板11上の第2半導体素子用導電層162とをワイヤボンディングする。

【0095】

次いで、前記支持基板11、第1の半導体素子100及び第2の半導体素子160を、封止樹脂166により樹脂封止し、しかる後支持基板11の他方の主面に外部接続端子16を形成する。

【0096】

この様に、本実施例に於いても、第1の半導体素子100の1つの外部接続用パッド102には2個の凸状外部接続端子103A、103Bが配設され、当該凸状外部接続端子103A、103Bは、当該凸状外部接続端子103A、103Bを共通に被覆する接続部材14を介して支持基板11の一方の主面上に配設された導電層12Aに接続・固着されている。

【0097】

従って、第1の半導体素子100の凸状外部接続端子103A、103Bと支持基板11上の導電層12Aとの間に介在される接続部材14との接触面積が増加する。

尚、外部接続用パッド102に於いて、凸状外部接続端子103A及び凸状外部接続端子103Bは、半導体素子100の縁部の延びる方向に対して直角方向に並んで配設されている。

【0098】

この為、前記製造工程中、印加される熱応力及び/或いは機械的応力等により、或いは第1の半導体素子100と支持基板11との熱膨張係数の相違によって、第1の半導体素子100の半導体基板101に配設された凸状外部接続端子103A、103Bと支持基板11上の導電層12Aとの間に設けられた接続部材14に応力が集中したとしても、当該応力はより広い範囲に分散される。

【0099】

よって、第1の半導体素子100の凸状外部接続端子103A、103Bと支持基板11上の導電層12Aとの間に於ける接続部材14の全域に跨がってクラックを生ずる恐れは大きく低減する。

【0100】

このように、本実施例に於いても、第1の半導体素子100と支持基板11との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0101】

尚、本実施例に於いても、導電層12Aの形状及び配設構造として、前記図2又は図3に示す構造を適用してよく、また凸状外部接続端子103A、103Bの配設形態も前記図4に示す形態を適用することができる。

【0102】

更に、支持基板11上に半導体素子100を実装する際の工程として、前記図5に示した工程を適用することができる。

【実施例4】

【0103】

本発明の第4の実施例に於ける半導体装置を、図9及び図10に示す。当該第4の実施例に於ける半導体装置の断面構造を図9に示し、図9に於いて破線で囲んだ部分を図10に拡大して示す。なお、本実施例の説明に於いて、前記第1乃至第3の実施例に於ける部位と対応する部位については同じ符号を付し、その詳細な説明は省略する。

【0104】

図9を参照するに、本実施例に於ける半導体装置にあっては、支持基板11の上に、配線基板600を介して半導体素子500が搭載されている。

【0105】

当該配線基板600は、支持基板11と半導体素子500とを接続する中継基板(ターミナルチップ)として機能する。

【0106】

前記支持基板11の一方の主面上には、銅(Cu)層からなる導電層112Aが選択的に配設されている。

【0107】

当該導電層112Aは、支持基板11と配線基板600とを接続するボンディングワイヤ265が接続される導電層及び配線層を含み、ボンディングワイヤ265が接続される領域を除いてソルダーレジスト層13Aにより選択的に被覆されている。即ち、当該ソルダーレジスト層13Aは、導電層112Aに於ける、配線基板600との接続領域を画定している。

【0108】

一方、前記配線基板600は、例えばガラスエポキシ、ガラスビスマレイミドトリアジン(BT:Bismaleimide−Triazine)或いはポリイミド等からなる有機絶縁性基板をもって構成され、接着剤164を介して支持基板11上に固着されている。

【0109】

当該配線基板600の上面、即ち半導体素子500が載置される面には、当該半導体素子500の外部接続用パッドに対応して、銅(Cu)から成る外部接続用パッド612Aが複数個配設され、当該外部接続用パッド612Aには、それぞれ一つの凸状外部接続端子603が配設されている。

【0110】

また、配線基板600の上面にあって、前記半導体素子500の周囲に位置して、銅(Cu)から成る外部接続用パッド612Bが複数個配設されている。当該外部接続用パッド612Bは、配線基板600の主面の四辺または対向する二辺の近傍に設けられる。

【0111】

前記外部接続用パッド612Aは、配線基板600の表面或いは内部に形成された配線層(図示せず)をもって、対応する外部接続用パッド612Bに接続されている。

【0112】

当該パッド612A、612Bの表面には、下層側からニッケル(Ni)/金(Au)、或いは下層側から銅(Cu)/ニッケル(Ni)/金(Au)からなるめっき層が形成されていることが好ましい。

【0113】

また、前記半導体素子500は、第1乃至第3の実施例における半導体素子100と同様、シリコン(Si)、或いはガリウム砒素(GaAs)等の半導体基板を用い、周知の半導体製造プロセスをもって形成されている。

【0114】

当該半導体素子500の主面には、複数個の外部接続用パッド502が設けられ、当該外部接続用パッド502上には、一つの凸状外部接続端子503が配設されている。

【0115】

当該半導体素子500は、前記配線基板600上に所謂フリップチップ方式をもって実装される。この時、当該半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503と、配線基板600の外部接続用パッド612A上に設けられた凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされる。当該凸状外部接続端子503、凸状外部接続端子603は、半導体素子500の縁部の延びる方向に対して直角方向に並んで配設されている。

【0116】

加えて、当該凸状外部接続端子503、凸状外部接続端子603は、前記平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向には重畳した(互いに入り込んだ)状態とされる。

【0117】

そして、当該凸状外部接続端子503と凸状外部接続端子603は、はんだ或いは導電性接着剤等からなる接続部材14により機械的・電気的に接続され、また半導体素子500と配線基板600との間にはエポキシ系樹脂を主体とするアンダーフィル材15が充填されて、半導体素子500は配線基板600に固着されている。

【0118】

そして、配線基板600に於ける外部接続用パッド612Bと、前記支持基板11の導電層112Aは、ボンディングワイヤ265により接続されている。

【0119】

更に、前記支持基板11、第1の半導体素子100は、支持基板11上にあって封止樹脂166により樹脂封止され、支持基板11の他方の主面には外部接続端子16が配設されている。

【0120】

この様な構造に於いて、前記配線基板600としては、セラミック、ガラス等の無機絶縁性基板、或いはシリコン(Si)、ガリウム砒素(GaAs)等の半導体基板を適用することができる。

【0121】

配線基板600として、半導体基板を適用した場合には、半導体素子の形成と同様のウエハプロセスを適用し、前記外部接続用パッド612を、アルミニューム(Al)、銅(Cu)、及びこれらの合金(例えば、Al95%−Cu5%合金等)等をもって形成することができる。

【0122】

また配線基板600を、当該配線基板600上に実装される半導体素子500と同じシリコン(Si)により形成することにより、両者の熱膨張係数を略同一にすることができ、半導体素子500の外部接続用パッド502と配線基板600の外部接続用パッド602との間に配設される接続部材14に於ける応力の集中を低減することができる。

【0123】

従って、半導体素子500と配線基板600との間の電気的・機械的接続を高い信頼性をもって実現することができる。

【0124】

ウエハプロセスの適用により、外部接続用パッド502及び外部接続用パッド612Bのピッチをより微細なものとすることができ、半導体装置の小型化及び高集積化を図ることができる。更に、半導体素子500の外部接続用パッド502の配設数を容易に増加させることができ、半導体装置の高機能化及び多ビット化に対応することができる。

【0125】

また、前記配線基板600として半導体基板を適用した場合には、当該配線基板600に半導体集積回路が形成されてもよい。

【0126】

当該配線基板600に半導体集積回路を形成することにより、複数個の半導体素子を3次元に実装してパッケージ化した所謂チップ・オン・チップ(COC:Chip−On−Chip)型の半導体装置を構成することができ、実装面積をより小とすることができる。

【0127】

更に、当該配線基板600には、必要に応じて多層配線構造が適用されてよく、またその表面或いは内層の配線部に、抵抗素子、容量素子或いはインダクタンス素子等の受動素子が搭載、或いは形成されてもよい。

【0128】

前述の如く、本実施例にあっては、半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503と、配線基板600の外部接続用パッド612A上に設けられた凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされ、且つ当該平面に垂直な方向には重畳した(互いに入り込んだ)状態とされて、接続部材14により機械的・電気的に固着・接続されている。

【0129】

かかる凸状外部接続端子503と凸状外部接続端子603との相互接続構造を、図10(A)に拡大して示す。

【0130】

外部接続用パッド502に於ける凸状外部接続端子503の配設箇所と外部接続用パッド612Bに於ける凸状外部接続端子603との配設箇所は、半導体素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされて、図9に於ける横方向即ち半導体素子500或いは配線基板600の幅方向に於いて、互いに異なる位置とされている。

【0131】

加えて、当該凸状外部接続端子503と凸状外部接続端子603は、当該平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向には、寸法Aに相当する高さ分重畳した(互いに入り込んだ)状態とされている。

【0132】

この様な接続・固着構造にあっては、凸状外部接続端子503と凸状外部接続端子603とが横方向に異なる位置に在り、且つその先端部は異なる平面に位置する。

【0133】

従って、熱的或いは機械的ストレスによって、凸状外部接続端子503の先端部と接続部材14との界面及び凸状外部接続端子603の先端部と接続部材14との界面にクラックが生じても、一方の凸状外部接続端子の先端部に於けるクラックが他方の凸状外部接続端子の先端部に於けるクラックに伝搬して連続することは生じない。

【0134】

従って、当該凸状外部接続端子503と凸状外部接続端子603の周囲を覆う接続部材14の全体にわたるクラックの発生、接続部材14の破断を招来せず、強固な固着・接続が維持される。

【0135】

即ち、本実施例に於ける凸状外部接続端子配設構造によれば、接続部材14において、応力が集中する部位、即ち、クラックが発生し得る部位は分散されるため、半導体素子500と配線基板600との間の電気的・機械的接続は高い信頼性をもって実現される。

【0136】

前述の如く、前記半導体基板11、配線基板600、及び半導体素子500は、封止樹脂166により樹脂封止される。

【0137】

従って、本実施例における半導体装置の製造工程中に印加される熱応力及び/或いは機械的応力等により、或いは半導体素子500、配線基板500、及び支持基板11との熱膨張係数の違いに基づき、接続部材14に応力が集中する恐れがある。

【0138】

しかしながら、本実施例に於ける半導体装置にあっては、半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503と、配線基板600の外部接続用パッド612A上に設けられた凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは配線基板600の表面と平行な平面に於いて位置が異ならしめられた状態とされ、且つ当該平面に垂直な方向には重畳した(互いに入り込んだ)状態とされて、接続部材14により機械的・電気的に固着・接続されている。

【0139】

かかる構成により、応力が集中してクラックが発生し得る部位が分散され、半導体素子500と配線基板600との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0140】

尚、外部接続用パッド502上に設けられた凸状外部接続端子503の先端部と、外部接続用パッド612B上に設けられた凸状外部接続端子603の先端部が、図10(b)に示すように、半導体素子500の厚さ方向(図10に於ける縦方向)において略一致、即ち同一平面上に位置すると、熱的或いは機械的ストレスによって、凸状外部接続端子503と接続部材14との界面及び凸状外部接続端子603の先端部と接続部材14との界面にクラックが生じた場合、一方の凸状外部接続端子の先端部に於けるクラックが他方の凸状外部接続端子の先端部に於けるクラックに容易に伝搬して連続し、当該接続部材14が最終的に破断してしまう可能性が大きい。

【0141】

本実施例の様に、半導体素子の電極パッドとこれに対応する支持基板上の電極パッドとの間を複数個の凸状外部接続端子を用いて接続する構成に於いて、前記図9、図10(a)に示される如く、当該半導体素子の電極パッドと支持基板上の電極パッドのそれぞれに凸状外部接続端子を配設し、且つ当該凸状外部接続端子の位置ならびに高さを設定する構成は、前記第1乃至第3実施例に於ける半導体素子の搭載構造に適用することができる。

【0142】

かかる半導体素子の電極パッドと支持基板上の電極パッドのそれぞれに凸状外部接続端子を配設し、且つ当該凸状外部接続端子の位置ならびに高さを設定する構成を、前記第1実施例に示される半導体装置に適用した例を図11に示す。

【0143】

図11を参照するに、支持基板11の導電層12Aには、凸状外部接続端子19が配設され、一方、半導体素子100の外部接続用パッド102には、凸状外部接続端子119が配設されている。

【0144】

即ち、半導体素子100の外部接続用パッド102上に形成された凸状外部接続端子19と、支持基板11の外部接続用パッド102上に形成された凸状外部接続端子119は、その先端部を対向することなく、即ち当該半導体層素子100の表面或いは支持基板11の表面と平行な平面に於いて位置が異ならしめられた状態とされ、且つ当該平面に垂直な方向には重畳した(互いに入り込んだ)状態とされて、接続部材14により機械的・電気的に固着・接続されている。

【0145】

そして、当該凸状外部接続端子19及び凸状外部接続端子119は、半導体素子100の縁部の延びる方向に対して直角方向に並んで配設されている。

【0146】

かかる構成によれば、接続部材14に於いて応力が集中する部位、即ち、クラックが発生し得る部位が分散されるため、半導体素子100と支持基板11との間の電気的・機械的接続は、高い信頼性をもって実現される。

【0147】

当該第4の実施例における半導体装置の、製造工程の要部について、図12を用いて説明する。

【0148】

同図(a)は、ボンディングステージ401上に載置・固定された配線基板600と、吸着用治具402に吸着保持された半導体素子500とを対向させた状態を示す。

【0149】

半導体素子500の外部接続用パッド502上には凸状外部接続端子503が、また、配線基板600の外部接続用パッド612B上には凸状外部接続端子603が形成されている。

【0150】

外部接続用パッド502及び612Bの周囲は、窒化シリコン(Si3N4)などからなる表面保護膜104により被覆されている。

【0151】

図示されるように、半導体素子500の外部接続用パッド502上に形成された凸状外部接続端子503と、配線基板600の外部接続用パッド602上に形成された凸状外部接続端子603は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは支持基板600の表面と平行な平面に於いて位置が異ならしめられて配置される。

【0152】

尚、かかる対向状態とする前に、半導体素子500の凸状外部接続端子503或いは配線基板600の凸状外部接続端子603の少なくとも一方に、予め接続部材14を被着形成しておく。

【0153】

図示される例では、当該接続部材14が半導体素子500の外部接続用パッド502上に設けられた凸状外部接続端子503の先端に被覆形成されているが、勿論配線基板600の外部接続用パッド612B上に設けられた凸状外部接続端子603の先端に被着形成してもよい。また凸状外部接続端子503及び凸状外部接続端子603の双方に被着形成してもよい。

【0154】

凸状外部接続端子503と凸状外部接続端子603の双方に被着形成することにより、外部接続用パッド502と外部接続用パッド612Bとの間に接続部材14を均一に配設することができる。

【0155】

接続部材14が銀ペースト等の導電性樹脂から成る場合には、当該接続部材14を凸状外部接続端子503及び凸状外部接続端子603の双方に被着することにより、より均一に配設することができる。

【0156】

このように、半導体素子500と配線基板600とを対向させた状態において、ボンディングステージ401を前記接続部材14の融点以上の温度(例えば280℃〜300℃)に加熱すると共に、吸着用治具402を降下させて、溶融した接続部材14中に凸状外部接続端子503及び603を圧入する。

【0157】

尚、この時吸着用治具402も所定温度(例えば80℃〜200℃)に加熱してもよい。

【0158】

この結果、接続部材14は、凸状外部接続端子503又は603を覆うと共に、外部接続用端子パッド502及び612Aの露出表面にも接して、外部接続用端子パッド502及び612A間を結合する。この時、凸状外部接続端子503及び603間の空間も、当該接続部材14により充填される。

【0159】

また、この時、凸状外部接続端子503と凸状外部接続端子603は、当該平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向に、前記図10(a)に示す寸法Aに相当する高さ分重畳した(互いに入り込んだ)状態とされている。かかる状態を、同図(b)に示す。

【0160】

この様に、外部接続用端子パッド502と凸状外部接続端子603とが、また外部接続用端子パッド612Aと凸状外部接続端子503とが、それぞれ接続部材14を介して接続・固着され、当該配線基板600上に半導体素子500が搭載された後、当該配線基板600と半導体素子500との間に、エポキシ系樹脂を主体とするアンダーフィル材15が充填される。かかる状態を、同図(C)に示す。

【0161】

次いで、前記配線基板600を支持基板11上に搭載し、配線基板600上の端子パッド612Bと支持基板11上の導電層112Aとをボンディングワイヤ265により接続する。

【0162】

次いで、支持基板11、配線基板600及び半導体素子500を封止樹脂166により樹脂封止する。

【0163】

しかる後、支持基板11の他方の主面に外部接続端子16を配設して、前記図9に示す半導体装置を形成する。

【実施例5】

【0164】

本発明の第5の実施例に於ける半導体装置を、図13及び図14に示す。

【0165】

当該第5の実施例に於ける半導体装置の断面構造を図13に示し、当該図13に於いて破線で囲んだ部分を拡大して図14に示す。

【0166】

なお、本実施例の説明に於いて、前記第1乃至第4の実施例に於ける部位と対応する部位については同じ符号を付し、その詳細な説明を省略する。

【0167】

図13及び図14を参照するに、本実施例における半導体装置にあっては、半導体素子500の外部接続用パッド502には、そのほぼ中央部に、1つの凸状外部接続端子503が配設されている。

【0168】

一方、配線基板600の外部接続用パッド612B上には、2つの凸状外部接続端子603−1及び603−2が、所定の間隔B(図14参照)をもって離間して配設されている。

【0169】

当該2つの凸状外部接続端子603−1と603−2の相互の間隔Bは、前記半導体素子500の外部接続用パッド502に設けられた凸状外部接続端子503の幅C(図14参照)よりも僅かに大きくされている。

【0170】

この様な凸状外部接続端子の配設構成によって、半導体素子500が配線基板600上にフリップチップ接続・固着される際、半導体素子500の外部接続用パッド502上の凸状外部接続端子503は、その先端部を配線基板600の外部接続用パッド612B上の2つの凸状外部接続端子603−1或いは603−2に対向することなく、当該凸状外部接続端子603−1と603−2との間に受容されている。

【0171】

そして、当該凸状外部接続端子603−1、凸状外部接続端子502及び凸状外部接続端子603−2は、半導体素子500の縁部の延びる方向に対して直角方向に並んで配設されている。

【0172】

また、この時、凸状外部接続端子503と凸状外部接続端子603−1、603−2は、半導体素子500或いは配線基板600の平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向に、寸法A(図14参照)に相当する高さ分重畳した(互いに入り込んだ)状態とされている。

【0173】

この様な接続・固着構造によれば、凸状外部接続端子503に対し、その両側に凸状外部接続端子603−1、603−2が位置することにより、前記実施例に示す構造に比して接続部材14との接触面積が増大し、配線基板600に対する半導体素子500の接続・固着強度を高めることができる。

【0174】

また、この様な接続・固着構造によれば、凸状外部接続端子503と凸状外部接続端子603−1、603−2とが横方向に異なる位置に在り、且つその先端部も異なる平面にあることから、熱的或いは機械的ストレスによって、凸状外部接続端子503の先端部と接続部材14との界面及び凸状外部接続端子603−1或いは603−2の先端部と接続部材14との界面にクラックが生じても、一つの凸状外部接続端子の先端部に於けるクラックが他の凸状外部接続端子の先端部に於けるクラックに伝搬して連続する可能性は極めて低い。即ち、横方向に異なる位置に在り、且つその先端部が互いに異なる平面にある3個の凸状外部接続端子先端部に於けるクラックが全て連続する確率は極めて低い。

【0175】

従って、凸状外部接続端子503と凸状外部接続端子603の周囲を覆う接続部材14の全体にわたるクラックの発生、接続部材14の破断を招来せず、強固な固着・接続が維持される。

【0176】

尚、図13及び図14に示す本実施例にあっては、半導体素子500の外部接続用パッド502に1つの凸状外部接続端子503を設け、配線基板600の外部接続用パッド612Bには2つの凸状外部接続端子603−1及び603−2を設けているが、勿論かかる構成に限定されるものではない。

【0177】

半導体素子500の外部接続用パッド502に複数個の凸状外部接続端子503を設け、配線基板600の外部接続用パッド612Bに一つの凸状外部接続端子603を設けることとしてもよく、また、半導体素子500の外部接続用パッド502並びに配線基板600の外部接続用パッド612A のそれぞれに複数個の凸状外部接続端子を設けてもよい。

【0178】

何れの構成にあっても、半導体素子500の凸状外部接続端子503と配線基板600の凸状外部接続端子603は、相互に横方向に異なる位置に在り、且つその先端部も異なる平面にあることが必要とされる。

【0179】

当該第5の実施例に於ける半導体装置の、製造工程の要部について、図15を用いて説明する。

【0180】

同図(a)は、ボンディングステージ401上に載置・固定された配線基板600と、吸着用治具402に吸着保持された半導体素子500とを対向させた状態を示す。

【0181】

半導体素子500の外部接続用パッド502上には1つの凸状外部接続端子503が、一方配線基板600の外部接続用パッド612B上には2つの凸状外部接続端子603−1及び603−2が間隔Bを有して離間して形成されている。

【0182】

そして、外部接続用パッド502及び612Bの周囲は、窒化シリコン(Si3N4)などからなる表面保護膜104により被覆されている。

【0183】

図示されるように、半導体素子500の外部接続用パッド502上に形成された凸状外部接続端子503と、配線基板600の外部接続用パッド602上に形成された凸状外部接続端子603−1及び603−2は、互いにその先端部を対向することなく、即ち当該半導体層素子500の表面或いは支持基板600の表面と平行な平面に於いて位置が異ならしめられて配置され、配線基板600の凸状外部接続端子603−1と603−2との間に、半導体素子500の凸状外部接続端子503が位置している。

【0184】

尚、かかる対向状態とする前に、半導体素子500の凸状外部接続端子503或いは配線基板600の凸状外部接続端子603の少なくとも一方に、予め接続部材14を被着形成しておく。図(a)に示す例にあっては、半導体素子500の凸状外部接続端子503に接続部材14を被着形成している。

【0185】

この様に、半導体素子500と配線基板600とを対向させた状態において、ボンディングステージ401を前記接続部材14の融点以上の温度(例えば280℃〜300℃)に加熱すると共に、吸着用治具402を降下させて、溶融した接続部材14中に凸状外部接続端子503及び603を圧入する。

【0186】

この時、吸着用治具402を所定温度(例えば80℃〜200℃)に加熱してもよい。

【0187】

この結果、接続部材14は、凸状外部接続端子503、603−1及び603−2を覆うと共に、外部接続用端子パッド502及び612Aの露出表面にも接して、外部接続用端子パッド502及び612A間を結合する。凸状外部接続端子503と凸状外部接続端子603−1、603−2間の空間も、当該接続部材14により充填される。

【0188】

この時、凸状外部接続端子503と凸状外部接続端子603は、当該平面に垂直な方向、即ち半導体素子500或いは配線基板600の厚さ方向に、前記図10(a)に示す寸法Aに相当する高さ分重畳した(互いに入り込んだ)状態とされている。かかる状態を、同図(b)に示す。

【0189】

この様に、外部接続用端子パッド502と凸状外部接続端子603とが、また外部接続用端子パッド612Aと凸状外部接続端子503とが接続部材14を介して接続・固着され、当該配線基板600上に半導体素子500が搭載された後、当該配線基板600と半導体素子500との間に、エポキシ系樹脂を主体とするアンダーフィル材15が充填される。かかる状態を、同図(C)に示す。

【0190】

次いで、前記配線基板600を、支持基板11上に搭載し、配線基板600上の端子パッド612Bと支持基板11上の導電層112Aとをボンディングワイヤ265により接続する。

【0191】

次いで、支持基板11、配線基板600及び半導体素子500を封止樹脂166により樹脂封止する。

【0192】

しかる後、支持基板11の他方の主面に外部接続端子16を配設して、図13に示す半導体装置を形成する。

【0193】

以上、本発明の実施の形態について詳述したが、本発明は特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形及び変更が可能である。

【0194】

一つに、前記半導体素子の外部接続用パッド上に設けられる凸状外部接続端子は、金、銅、ニッケル又はこれらの合金等から形成され、例えば金属ワイヤを用いたボールボンディング法により形成されるスタッドバンプ、或いはめっき法により形成されるバンプを適用することができる。

【0195】

また、前記配線基板が、ガラスエポキシ、ガラスビスマレイミドトリアジン(BT:Bismaleimide−Triazine)、ポリイミド等の有機絶縁材料或いはセラミック、ガラス等の無機絶縁材料から成る場合には、外部接続用パッドを表面に下層側からニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層が形成された銅(Cu)から形成し、当該外部接続用パッドに対し、金(Au)、銅(Cu)及びこれらの合金等からなる金属ワイヤを用いてボールボンディング法により、凸状外部接続端子503を形成することができる。

【0196】

或いは、銅(Cu)等からなる外部接続用パッド上に、銀(Ag)等からなる凸状外部接続端子を印刷法、転写法、インクジェット法等で形成し、外部接続用パッド及び凸状外部接続端子全体に下層側からニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層を被覆形成してもよい。

【0197】

更には、銅(Cu)等からなる外部接続用パッドにエッチング処理を施し、局所的に凸状外部接続端子を形成し、下層側からニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層を被覆形成してもよい。

【0198】

或いは、銅(Cu)等からなる外部接続用パッド上に局所的に銅(Cu)めっきを施して凸状外部接続端子を形成し、下層よりニッケル(Ni)/金(Au)の2層めっき層、又は下層側から銅(Cu)/ニッケル(Ni)/金(Au)の3層めっき層を被覆形成してもよい。

【0199】

一方、配線基板が、シリコン(Si)、ガリウム砒素(GaAs)等の半導体基板から成る場合には、外部接続用パッドをアルミニューム(Al)、銅(Cu)、及びこれらの合金等から形成し、当該外部接続用パッド上に下層側よりニッケル(Ni)/金(Au)、チタン(Ti)/タングステン(W)/金(Au)、チタン(Ti)/パラジウム(Pd)/金(Au)、或いはチタン(Ti)/ニッケル(Ni)/パラジウム(Pd)/金(Au)等の金属被膜を形成し、当該金属被膜上に、金(Au)、銅(Cu)及びこれらの合金等から成る金属ワイヤを用いてボールボンディングすることにより、凸状外部接続端子を形成することができる。

【0200】

或いは、前記アルミニューム(Al)、銅(Cu)、及びこれらの合金等から成る外部接続用パッド上に、下層側よりチタン(Ti)/タングステン(W)、下層側からチタン(Ti)/タングステン(W)/金(Au)、下層側からチタン(Ti)/パラジウム(Pd)、下層側からチタン(Ti)/パラジウム(Pd)/金(Au)、或いは下層側からチタン(Ti)/ニッケル(Ni)/パラジウム(Pd)等の金属被膜を形成し、当該金属被膜上に電解めっき法により金(Au)、銅(Cu)等から成る凸状外部接続端子を形成してもよい。

【0201】

また、外部接続用パッドに於ける、少なくとも凸状外部接続端子が形成されていない箇所の表面(最上層)には、電解めっき法又は蒸着法等により金(Au)層を形成しておくことが望ましい。

【0202】

かかる金(Au)層を形成しておくことにより、接続部材として半田を用いる場合、当該半田が外部接続用パッドの表面(最上層)において濡れ広がることを確保することができる。

【0203】

また、凸状外部接続端子としてスタッドバンプを適用する場合、当該凸状外部接続端子を形成する箇所の表面(最上層)に、予め金(Au)層を形成しておくことにより、金(Au)線を用いたスタッドバンプを容易に形成することができる。

【0204】

なお、当該下地金(Au)層の形成にあっては、当該金(Au)層と凸状外部接続端子の表面(最上層)との間に、下層としてチタン(Ti)、タングステン(W)、パラジウム(Pd)、ニッケル(Ni)、又はこれらの合金等の金属層を形成することが望ましい。これらの金属層により、外部接続用パッドの腐食を防止することができ、また、層間密着力の向上等を図ることができる。

【0205】

具体的には、当該金(Au)層と凸状外部接続端子の表面(最上層)との間に、外部接続用パッド側からニッケル(Ni)、チタン(Ti)/タングステン(W)、チタン(Ti)/パラジウム(Pd)、或いはチタン(Ti)/ニッケル(Ni)/パラジウム(Pd)を設けることが望ましい。

【0206】

また、前記接続部材としては、錫(Sn)−銀(Ag)、錫(Sn)−銀(Ag)−銅(Cu)、又は錫(Sn)−銀(Sg)−インジウム(In)から成る半田、或いは銀(Ag)、銅(Cu)、銅合金等の金属粒子或いはこれら金属の金属被膜を形成した粒子等を含むエポキシ樹脂等の導電性樹脂を用いることができる。

【0207】

かかる接続部材は、外部接続用パッドの表面への選択的電解めっき法、又は他の基板上に塗布され均一な厚さとされた接続部材層に凸状外部接続端子の先端を接触させて当該先端に接続部材を付着させる転写法、或いはペースト状または微細粒子状の接続部材をマイクロノズルより噴出して凸状外部接続端子の先端に局所的に付着させる方法等により形成することができる。

【0208】

以上の説明に関し、更に以下の項を開示する。

(付記1) 半導体基板の一方の主面に外部接続用端子パッドを具備する半導体素子が、前記外部接続用端子パッド上に配設された凸状外部接続端子及び接続部材を介して、支持基板上の導電層に接続される半導体装置であって、

前記外部接続用端子パッドは複数個の凸状外部接続端子を具備し、前記接続部材は当該複数個の凸状外部接続端子を共通に被覆してなることを特徴とする半導体装置。

(付記2) 半導体基板、前記半導体基板の一方の主面に配設された外部接続用端子パッド、及び前記外部接続用端子パッド上に複数個配設された凸状外部接続端子を具備する半導体素子と、

絶縁性基板、前記絶縁基板の一方の主面に配設された導電層、及び前記絶縁基板の前記一方の主面上に配設されて前記導電層を選択的に被覆する絶縁層を具備する支持基板と、

前記絶縁層に被覆されない前記導電層に、前記複数個の凸状外部接続端子を共通に被覆して固着する接続部材と、を具備することを特徴とする半導体装置。

(付記3) 半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設されてなる半導体素子と、

前記外部接続用端子パッドに対応した複数個の導電層が配設され、当該導電層上に少なくとも一つの第2の凸状外部接続端子が配設されてなる支持基板と、を具備し、

前記第1の凸状外部接続端子が接続部材を介して前記導電層に接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

(付記4) 付記3記載の半導体装置であって、

前記外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記導電層における前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

(付記5) 付記4記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

(付記6) 付記1乃至5いずれか一項記載の半導体装置であって、

前記半導体素子は第1の半導体素子として機能し、

前記第1の半導体素子の上に第2の半導体素子が接着固定されていることを特徴とする半導体装置。

(付記7) 付記1乃至6いずれか一項記載の半導体装置であって、

前記複数個の外部接続端子パッドは、前記半導体基板の略中央において列を形成して配設されえていることを特徴とする半導体装置。

(付記8) 付記6及び7記載の半導体装置であって、

前記第1の半導体素子、前記第2の半導体素子及び前記支持基板は封止樹脂により封止されていることを特徴とする半導体装置。

(付記9) 支持基板と、

前記支持基板の上に実装された配線基板を介して前記支持基板に接続され、前記配線基板の上に実装された半導体素子と、を備えた半導体装置であって、

前記半導体素子の半導体基板の主面のうち、前記配線基板に面した側の面に複数個の半導体素子外部接続用端子パッドが配設され、当該半導体素子外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設され、

前記配線基板の主面のうち、前記半導体素子に面した側の面に複数個の配線基板外部接続用端子パッドが配設され、当該配線基板外部接続用端子パッド上に少なくとも一つの第2の凸状外部接続端子が配設され、

前記第1の凸状外部接続端子が接続部材を介して前記配線基板外部接続用端子パッドに接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記半導体素子外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

(付記10) 付記9記載の半導体装置であって、

前記半導体素子外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記配線基板外部接続用端子パッドにおける前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

(付記11) 付記10記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

(付記12) 付記9乃至11いずれか一項記載の半導体装置であって、

前記配線基板は、有機材料、セラミック、又はガラスから選択される材料から構成されていることを特徴とする半導体装置。

(付記13) 付記9乃至11いずれか一項記載の半導体装置であって、

前記配線基板は、シリコンから成ることを特徴とする半導体装置。

(付記14) 付記13記載の半導体装置であって、

前記配線基板に、半導体集積回路が形成されていることを特徴とする半導体装置。

(付記15) 付記9及び14記載の半導体装置であって、

前記半導体素子、前記配線基板及び前記支持基板は封止樹脂により封止されていることを特徴とする半導体装置。

【図面の簡単な説明】

【0209】

【図1】本発明の第1の実施例における半導体装置の構造を示す、断面図である。

【図2】本発明の第1の実施例における半導体装置に於いて、支持基板の主面に配設される導電層の形状を示す平面図である。

【図3】本発明の第1の実施例における半導体装置に於いて、支持基板の主面に配設される導電層の配設例の変形例を示す平面図である。

【図4】本発明の第1の実施例における半導体装置に於いて、半導体素子の凸状外部接続端子の構成を示す平面図及び断面図である。

【図5】本発明の第1の実施例における半導体装置の製造工程を示す断面図である。

【図6】本発明の第2の実施例における半導体装置に於いて、凸状外部接続端子が配設された半導体素子の主面を示す平面図である。

【図7】本発明の第2の実施例における半導体装置の構造を示す、断面図である。

【図8】本発明の第3の実施例における半導体装置の構造を示す、断面図である。

【図9】本発明の第4の実施例における半導体装置の構造を示す、断面図である。

【図10】図9において点線で囲んだ部分を説明するための図である。

【図11】本発明の第4の実施例の半導体素子の外部接続用パッドと配線基板の外部接続用パッドとの接続構造を、図1に示す半導体装置に適用した場合の、当該半導体装置の断面図である。

【図12】本発明の第4の実施例における半導体装置の製造工程を示す断面図である。

【図13】本発明の第5の実施例における半導体装置の構造を示す、断面図である。

【図14】図13において点線で囲んだ部分の拡大図である。

【図15】本発明の第5の実施例における半導体装置の製造工程を示す断面図である。

【符号の説明】

【0210】

11 支持基板

12 導電層

13 ソルダーレジスト

14 接続部材

15 アンダーフィル材

19、103、119、153、503、603 凸状外部接続端子

100、150、160、500 半導体素子

101、151、161、501 半導体基板

102、152、502、612B 外部接続用パッド

200 接続領域

301 台座部

302 突出する部位

401 ボンディングステージ

402 吸着用治具

600 配線基板

【特許請求の範囲】

【請求項1】

半導体基板の一方の主面に外部接続用端子パッドを具備する半導体素子が、前記外部接続用端子パッド上に配設された凸状外部接続端子及び接続部材を介して、支持基板上の導電層に接続される半導体装置であって、

前記外部接続用端子パッドは複数個の凸状外部接続端子を具備し、前記接続部材は当該複数個の凸状外部接続端子を共通に被覆してなることを特徴とする半導体装置。

【請求項2】

半導体基板、前記半導体基板の一方の主面に配設された外部接続用端子パッド、及び前記外部接続用端子パッド上に複数個配設された凸状外部接続端子を具備する半導体素子と、

絶縁性基板、前記絶縁基板の一方の主面に配設された導電層、及び前記絶縁基板の前記一方の主面上に配設されて前記導電層を選択的に被覆する絶縁層を具備する支持基板と、

前記絶縁層に被覆されない前記導電層に、前記複数個の凸状外部接続端子を共通に被覆して固着する接続部材と、を具備することを特徴とする半導体装置。

【請求項3】

半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設されてなる半導体素子と、

前記外部接続用端子パッドに対応した複数個の導電層が配設され、当該導電層上に少なくとも一つの第2の凸状外部接続端子が配設されてなる支持基板と、を具備し、

前記第1の凸状外部接続端子が接続部材を介して前記導電層に接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

【請求項4】

請求項3記載の半導体装置であって、

前記外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記導電層における前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

【請求項6】

請求項1乃至5いずれか一項記載の半導体装置であって、

前記半導体素子は第1の半導体素子として機能し、

前記第1の半導体素子の上に第2の半導体素子が接着固定されていることを特徴とする半導体装置。

【請求項7】

支持基板と、

前記支持基板の上に実装された配線基板を介して前記支持基板に接続され、前記配線基板の上に実装された半導体素子と、を備えた半導体装置であって、

前記半導体素子の半導体基板の主面のうち、前記配線基板に面した側の面に複数個の半導体素子外部接続用端子パッドが配設され、当該半導体素子外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設され、

前記配線基板の主面のうち、前記半導体素子に面した側の面に複数個の配線基板外部接続用端子パッドが配設され、当該配線基板外部接続用端子パッド上に少なくとも一つの第2の凸状外部接続端子が配設され、

前記第1の凸状外部接続端子が接続部材を介して前記配線基板外部接続用端子パッドに接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記半導体素子外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

【請求項8】

請求項7記載の半導体装置であって、

前記半導体素子外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記配線基板外部接続用端子パッドにおける前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

【請求項9】

請求項8記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

【請求項10】

請求項7乃至9いずれか一項記載の半導体装置であって、

前記配線基板は、シリコンから成ることを特徴とする半導体装置。

【請求項1】

半導体基板の一方の主面に外部接続用端子パッドを具備する半導体素子が、前記外部接続用端子パッド上に配設された凸状外部接続端子及び接続部材を介して、支持基板上の導電層に接続される半導体装置であって、

前記外部接続用端子パッドは複数個の凸状外部接続端子を具備し、前記接続部材は当該複数個の凸状外部接続端子を共通に被覆してなることを特徴とする半導体装置。

【請求項2】

半導体基板、前記半導体基板の一方の主面に配設された外部接続用端子パッド、及び前記外部接続用端子パッド上に複数個配設された凸状外部接続端子を具備する半導体素子と、

絶縁性基板、前記絶縁基板の一方の主面に配設された導電層、及び前記絶縁基板の前記一方の主面上に配設されて前記導電層を選択的に被覆する絶縁層を具備する支持基板と、

前記絶縁層に被覆されない前記導電層に、前記複数個の凸状外部接続端子を共通に被覆して固着する接続部材と、を具備することを特徴とする半導体装置。

【請求項3】

半導体基板の一方の主面に複数個の外部接続用端子パッドが配設され、当該外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設されてなる半導体素子と、

前記外部接続用端子パッドに対応した複数個の導電層が配設され、当該導電層上に少なくとも一つの第2の凸状外部接続端子が配設されてなる支持基板と、を具備し、

前記第1の凸状外部接続端子が接続部材を介して前記導電層に接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

【請求項4】

請求項3記載の半導体装置であって、

前記外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記導電層における前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

【請求項6】

請求項1乃至5いずれか一項記載の半導体装置であって、

前記半導体素子は第1の半導体素子として機能し、

前記第1の半導体素子の上に第2の半導体素子が接着固定されていることを特徴とする半導体装置。

【請求項7】

支持基板と、

前記支持基板の上に実装された配線基板を介して前記支持基板に接続され、前記配線基板の上に実装された半導体素子と、を備えた半導体装置であって、

前記半導体素子の半導体基板の主面のうち、前記配線基板に面した側の面に複数個の半導体素子外部接続用端子パッドが配設され、当該半導体素子外部接続用端子パッド上に少なくとも一つの第1の凸状外部接続端子が配設され、

前記配線基板の主面のうち、前記半導体素子に面した側の面に複数個の配線基板外部接続用端子パッドが配設され、当該配線基板外部接続用端子パッド上に少なくとも一つの第2の凸状外部接続端子が配設され、

前記第1の凸状外部接続端子が接続部材を介して前記配線基板外部接続用端子パッドに接続されるとともに、前記第2の凸状外部接続端子が当該接続部材を介して前記半導体素子外部接続用端子パッドに接続されてなることを特徴とする半導体装置。

【請求項8】

請求項7記載の半導体装置であって、

前記半導体素子外部接続用端子パッドにおける前記第1の凸状外部接続端子の配設箇所と、前記配線基板外部接続用端子パッドにおける前記第2の凸状外部接続端子の配設箇所とは、当該半導体装置の幅方向において位置が異なっており、

前記第1の凸状外部接続端子の先端面の位置と、前記第2の凸状外部接続端子の先端面の位置は、当該半導体装置の厚さ方向において相違している、ことを特徴とする半導体装置。

【請求項9】

請求項8記載の半導体装置であって、

前記第1の凸状外部接続端子又は前記第2の凸状外部接続端子の少なくとも一方は複数個配設されており、

隣り合う前記第1の凸状外部接続端子の間に前記第2の凸状外部接続端子が、又は隣り合う前記第2の凸状外部接続端子の間に前記前記第1の凸状外部接続端子が配設されていることを特徴とする半導体装置。

【請求項10】

請求項7乃至9いずれか一項記載の半導体装置であって、

前記配線基板は、シリコンから成ることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2007−43065(P2007−43065A)

【公開日】平成19年2月15日(2007.2.15)

【国際特許分類】

【出願番号】特願2006−61759(P2006−61759)

【出願日】平成18年3月7日(2006.3.7)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成19年2月15日(2007.2.15)

【国際特許分類】

【出願日】平成18年3月7日(2006.3.7)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]