半導体装置

【課題】封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることを可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10に形成された電極をなす複数の外部端子11と、パッケージ基材20に形成された複数の引出配線21とが接合され、複数の外部端子11及び複数の引出配線21が封止材により封止されたものである。半導体チップ10においては、複数の外部端子11からなる外部端子列12が、外部端子列12の延びる方向に対して交差する方向に複数配列しており、かつ、複数の外部端子列12において、複数の外部端子11のうち2以上がチップ辺10Eに対して交差する方向に同軸配列している。

【解決手段】半導体装置1は、半導体チップ10に形成された電極をなす複数の外部端子11と、パッケージ基材20に形成された複数の引出配線21とが接合され、複数の外部端子11及び複数の引出配線21が封止材により封止されたものである。半導体チップ10においては、複数の外部端子11からなる外部端子列12が、外部端子列12の延びる方向に対して交差する方向に複数配列しており、かつ、複数の外部端子列12において、複数の外部端子11のうち2以上がチップ辺10Eに対して交差する方向に同軸配列している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体チップに形成された電極をなす複数の外部端子と、パッケージ基材に形成された複数の引出配線とが接合され、複数の外部端子及び複数の引出配線が封止材により封止された半導体装置に関するものである。

【背景技術】

【0002】

半導体装置の一つとして、TAB(テープ・オートメイテッド・ボンディング)型半導体装置がある。

TAB型半導体装置では、半導体チップの電極となるパッド上の複数のバンプが、半導体チップのチップ辺に対して略平行方向に配列されており、最近では狭ピッチ化対応として2列以上の千鳥配列が増加している。通常、これらのバンプに接続されるフィルム基材のインナーリードは、バンプ上から半導体チップの外部に直線状に延在形成されている。

電子機器の小型化及び高機能化に伴って、これに搭載されるTAB型半導体装置も一層の小型化が必要となっている。そのためにはTAB型半導体装置内のインナーリードの狭ピッチ化(例えば、25μmピッチ→23μmピッチ→20μmピッチ)が進められている。

【0003】

特許文献1には、千鳥配置の複数のバンプを持つ半導体チップを用いたTAB型半導体装置において、封止樹脂(封止材)の流れを良くするための構造が提案されている。

図11に、特許文献1の図1に記載の半導体装置の要部平面図を示す。図12に、図11のXXII-XXII線断面図を示す。ここでは、特許文献1とは符号は変えてある。

【0004】

図示するTAB型半導体装置101は、半導体チップ110に形成された電極をなす複数のバンプ(外部端子)111とテープ状のフィルム基材(パッケージ基材)120に形成された複数のインナーリード(引出配線)121とを熱圧着で接合し、半導体チップ110とフィルム基材120との隙間に封止樹脂CPを注入し、これを硬化させて、製造されたものである。

図12には、封止樹脂CPの注入の様子が示されている。

【0005】

図11に示すように、半導体装置101の半導体チップ110においては、バンプ111が2列に千鳥配置されている。

図中、外側(チップ辺110E側)のバンプに符号111Aを付し、内側(チップの中央側)のバンプに符号111Bを付してある。

半導体チップ110の外側バンプ111Aには、フィルム基材120のインナーリード121Aが接合され、半導体チップ110の内側バンプ111Bには、フィルム基材120のインナーリード121Bが接合されている。

特許文献1では、外側バンプ111Aの内側から、互いに隣接する内側バンプ111B間を通る突起パターン130が設けられている(請求項1、図1、及び要約書等)。

【0006】

特許文献1には、上記構成により、半導体チップとフィルム基材とを接続し、その間に樹脂を注入する際に、突起パターンに伝わって封止樹脂が進行し、半導体チップの中央側の列のバンプ間の封止樹脂の流れが助長されるので、バンプ近辺のボイドの発生を防止することができることが記載されている(要約書等)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−221320号公報

【特許文献2】特開2001−284413号公報

【特許文献3】特開2006−19699号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1では、2列に千鳥配列された複数のバンプのうち、半導体チップのチップ辺側の列をなす複数の外側バンプの両側から半導体チップの内側方向への封止樹脂の流れだけを考慮しているため、半導体チップの中央側の列をなす複数の内側バンプの存在が樹脂注入を妨げとなる恐れがある。この様子を図13に模式的に示す。

特許文献1の突起パターンは、半導体チップのチップ辺側の列をなす複数の外側バンプの両側から半導体チップの内側方向への封止樹脂の流れを整流するだけで、半導体チップの中央側の列をなす複数の内側バンプに当たって流れが妨げられた封止樹脂の流れを良くすることはできない。

封止樹脂の流れの不良は、封止樹脂の充填不良(ボイド)を起こす場合がある。そのため、封止樹脂の注入速度を遅くする必要があり、生産性(歩留りと生産能力)を向上させることが困難となっている。また、外側バンプと内側バンプとの間隔を必要以上に広く取る必要があり、このことがチップサイズの増大及びチップコストの増加を招いている。

【0009】

特許文献2においても、封止樹脂の流れを良くするために、ベースフィルム(2)の半導体チップ(4)を搭載する搭載領域(2a)にパターン部材(20A)を設ける構成が提案されている(要約書)。特許文献2において、パターン部材(20A)はインナリード(8)の内側に形成され、半導体チップ(4)の周囲とパターン部材(20A)との間に封止樹脂(10)が充填される領域が画成されている。

特許文献2では、半導体チップの複数のバンプ(図2の符号4a)の配列については記載がない。したがって、半導体チップの複数のバンプを千鳥配置した場合、特許文献1と同様の課題を有する。

【0010】

特許文献3には、設計上の間隔の規格を遵守しながら、電極パッドを狭ピッチ化することを目的とし、電極パッドが多段に配列された半導体チップ(1)の外周に並んだ電極パッドの間を通って、内側の電極パッドに接続されたテープ配線基板(12)の配線(6)を2本以上まとめて半導体チップ(1)の外側へ引き出す構成が提案されている(要約書、図1)。

特許文献3では、最内周から2段目以降外周に配列された任意の電極パッド間にあらかじめ定められた所定の間隔を設け、最外周から2段目以降内側に配列された電極パッドと接続される配線のうちの隣接して配線される複数の配線を上記間隔に配設させている(請求項1)。

そのため、半導体チップのチップ辺に対して略垂直方向に見た場合、1個のバンプしかない箇所が多く存在し、バンプを高密度に配置することができない。

【課題を解決するための手段】

【0011】

本発明の半導体装置は、

半導体チップに形成された電極をなす複数の外部端子と、パッケージ基材に形成された複数の引出配線とが接合され、複数の前記外部端子及び複数の前記引出配線が封止材により封止された半導体装置であって、

前記半導体チップにおいては、複数の前記外部端子からなる外部端子列が、当該外部端子列の延びる方向に対して交差する方向に複数配列しており、かつ、前記複数の外部端子列において、複数の前記外部端子のうち2以上が前記外部端子列の延びる方向に対して交差する方向に同軸配列したものである。

【0012】

通常、外部端子は略矩形状である。

本明細書において、「同軸配列」とは、複数の外部端子列の延びる方向と交差する方向に並んだ互いに隣接する2つの外部端子の互いに対向する2つの辺のうち、一方の辺(2つの辺の長さに差がある場合は短い方)の半分以上が、他方の辺に対向している状態と定義する。

したがって、「同軸配列」において、上記条件を充たせば、外部端子列の延びる方向に対して交差する方向に並んだ互いに隣接する2つの外部端子の中心軸がずれていても構わない。

ただし、外部端子列の延びる方向に同軸配列した複数の外部端子は、中心軸を同軸として、同軸配列していることが好ましい。

【0013】

本発明の半導体装置においては、複数の外部端子列において、複数の外部端子のうち2以上が外部端子列の延びる方向に対して交差する方向に同軸配列しているので、半導体チップのサイズを大きくすることなく、特許文献3よりも半導体チップに外部端子を高密度に配置することができる。

本発明の半導体装置においては、複数の外部端子列において、複数の外部端子のうち2以上が外部端子列の延びる方向に対して交差する方向に同軸配列しているので、封止材の通り道が広く確保され、半導体装置への封止材の注入・浸透が容易である。そのため、封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができる。

【発明の効果】

【0014】

本発明によれば、半導体チップのサイズを大きくすることなく、半導体チップに外部端子を高密度に配置することができ、かつ、封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができる半導体装置を提供することができる。

【図面の簡単な説明】

【0015】

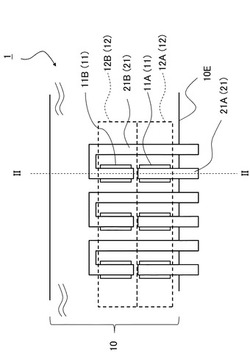

【図1】本発明に係る一実施形態の半導体装置の要部平面図である。

【図2】図1の半導体装置のII-II線断面図である。

【図3】図1の半導体装置において、封止樹脂の流れの様子を模式的に示す要部平面図である。

【図4】図1の半導体装置において、半導体チップのバンプ周辺の素子配置を示す要部平面図である。

【図5】設計変更例1を示す要部平面図である。

【図6】設計変更例2を示す要部平面図である。

【図7】設計変更例3を示す要部平面図である。

【図8】設計変更例4を示す要部平面図である。

【図9】設計変更例5を示す要部平面図である。

【図10】設計変更例6を示す要部平面図である。

【図11】特許文献1の半導体装置の要部平面図である。

【図12】図11の半導体装置のXXII-XXII線断面図である。

【図13】図11の半導体装置において、封止樹脂の流れの様子を模式的に示す要部平面図である。

【発明を実施するための形態】

【0016】

「一実施形態」

図面を参照して、本発明に係る一実施形態の半導体装置の構成について説明する。図1は本実施形態の半導体装置の要部平面図である。図2は図1の半導体装置のII-II線断面図である。図3は封止樹脂の流れの様子を模式的に示す要部平面図である。図4は半導体チップのバンプ周辺の素子配置を示す要部平面図である。

図面上は視認しやすくするため、各部材の縮尺や位置は適宜、実際のものとは異ならせて、簡略化してある。

【0017】

本実施形態の半導体装置1はTAB型半導体装置である。

本実施形態の半導体装置1は、半導体チップ10に形成された電極をなす複数のバンプ(外部端子)11とテープ状のフィルム基材(パッケージ基材)20に形成された複数のインナーリード(引出配線)21とを熱圧着で接合し、半導体チップ10とフィルム基材20との隙間に封止樹脂(封止材)CPを注入し、これを硬化させて、製造されたものである。

【0018】

フィルム基材20は可撓性を持ち、封止樹脂CPで封止された部分以外では折り曲げて、基板あるいは表示装置等に実装することが可能である。ここで、本実施形態の半導体装置が表示ドライバの場合、「表示装置」とは例えば、液晶(LCD)パネル、プラズマディスプレイ(PDP)パネル、エレクトロルミネッセンス(EL)パネル等の表示デバイスを指す。ただし、本実施形態の半導体装置が実装される装置は表示装置には限らない。

【0019】

図2には、封止樹脂CPの注入の様子が示されている。

半導体チップとパッケージ基材との境目に置かれた封止樹脂は、毛細管現象で半導体チップの下部に浸透していき、半導体チップ下のパッケージ基材との隙間を埋めることができる。半導体チップとパッケージ基材との隙間の間隔で所望の毛細管現象が効率的に起き、かつボイドの発生が無いように封止樹脂の粘度等が設計される。

【0020】

本実施形態の半導体装置1の半導体チップ10においては、半導体チップ10のチップ辺10Eに沿って配列した複数のバンプ(外部端子)からなるバンプ列(外部端子列)12が、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向に複数配列している。

本実施形態において、外側(チップ辺10E側)のバンプ列に符号12Aを付し、このバンプ列のバンプに符号11Aを付し、内側(チップの中央側)のバンプ列に符号12Bを付し、このバンプ列のバンプに符号11Bを付してある。

本実施形態ではさらに、上記2列のバンプ列12A、12Bにおいて、複数のバンプ11A、11Bが、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列している。

【0021】

本実施形態では、各バンプ11A、11Bは略矩形状であり、長軸方向がチップ辺10Eに対して略垂直方向、短軸方向がチップ辺10Eに対して略平行方向に配置されている。そして、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bが、チップ辺10Eに対して略垂直方向に同軸配列している。2個のバンプ11A、11Bは、中心軸を同軸として同軸配列している。

各バンプ11A、11Bは略矩形状のパッド11P上に形成されている(図4を参照)。

【0022】

半導体チップ10の外側バンプ11Aには、フィルム基材20上に形成されたインナーリード21Aが接合され、半導体チップ10の内側バンプ11Bには、フィルム基材20上に形成されたインナーリード21Bが接合されている。

本実施形態において、外側バンプ11Aに接続されたインナーリード21Aは半導体チップ10の外部から直線状に延びて、外側バンプ11Aに接続されている。内側バンプ11Bに接続されたインナーリード21Bは半導体チップ10の外部から、隣接する外側バンプ11A間及び隣接する内側バンプ11B間を通り、内側バンプ列12Bより内側で略J字状に屈曲して、内側バンプ11Bに接続されている。

【0023】

本実施形態の半導体装置1においては、2列のバンプ列12A、12Bにおいて、最も近接した2個のバンプ11A、11Bが、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列しているので、半導体チップ10のサイズを大きくすることなく、特許文献3よりも半導体チップ10にバンプ11を高密度に配置することができる。

本実施形態の半導体装置1においては、特許文献1に記載の2列の千鳥配置に対して、半導体チップ10のサイズを増加することなく、同等数のバンプ11を実装することができる。

【0024】

半導体装置1の製造においては、半導体チップ10上に配置された各バンプ11A、11Bとフィルム基材20上に形成されたインナーリード21A、21Bとを熱圧着により接合した後、図2に示すように、半導体チップ10とフィルム基材20との間に封止樹脂CPを流し込む。封止樹脂CPは、毛細管現象によって半導体チップ10とフィルム基材20との隙間に流れ込んでいく。

【0025】

図3は封止樹脂CPの流れの様子を模式的に示している。

図示するように、本実施形態では、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bがチップ辺10E(バンプ列12の延びる方向)に対して交差する方向(本実施形態では略垂直方向)に同軸配列しているので、外側バンプ11Bの間を流れてきた封止樹脂CPは、内側バンプ11Bに流れを邪魔されることなく直進して、半導体チップ10の内側まで到達する。この際、外側バンプ11Aと内側バンプ11Bと間には、封止樹脂CPの流れの一部が入っていく。

【0026】

本実施形態の半導体装置1においては、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bがチップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列しているので、封止樹脂CPの通り道が広く確保され、半導体装置1への封止樹脂CPの注入・浸透が容易である。そのため、封止樹脂CPの充填不良(ボイド)が抑制され、封止樹脂CPの注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができる。

【0027】

本実施形態においては、内側バンプ列12Bよりさらに内側でインナーリード21Bを屈曲させている。かかる構成では、インナーリード21Bの屈曲部分の厚みによって封止樹脂CPの流動が阻害される恐れもない。

【0028】

また、本実施形態においては、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bがバンプ列12の延びる方向に対して交差する方向に同軸配列している2つのバンプの組を、バンプ列12の延びる方向に複数かつ等間隔に配置している。そのため、それぞれの2つのバンプの組の間の封止樹脂CPが流動する部分の立体的形状を同一にすることができ、この部分の封止樹脂CPの流入時間を一定値に揃えることができる。これにより、バンプの横を通り抜けた封止樹脂CPのチップ下への流入が均一になり、全体の封止樹脂CPの流入効率が最大になるとともに、バンプの先のチップ下でのボイドの発生確率をさらに小さくすることができるようになる。

【0029】

図3等に示すように、本実施形態では、互いに隣接する外側バンプ11A間、及び互いに隣接する内側バンプ11B間にスペースが形成されている。このスペースは、インナーリード21Bの配設、及び同一面上に形成されているインナーリード21A、12B間の間隔を確保するために必要な部分であり、面積としては従来技術にもあったスペースである。本実施形態では、このスペースを略矩形状にして、半導体チップ10の面積を効率良く利用することを可能としている。

【0030】

図4は、本実施形態の半導体チップ10のバンプ11周辺の素子配置を示す要部平面図である。

本実施形態では、互いに隣接する外側バンプ11A間、及び互いに隣接する内側バンプ11B間のスペースに、面積の大きいESD保護回路Eを配置することができる。ESD保護回路Eには内部回路が接続される。

図中、符号W1はバンプ11のパッド11PとESD保護回路Eとを接続する配線を示し、符号W2はESD保護回路Eと内部回路とを接続する配線を示している。

本実施形態では、互いに隣接する外側バンプ11A間、及び互いに隣接する内側バンプ11B間のスペースに面積の大きいESD保護回路Eを配置することができるので、特許文献1に記載の千鳥配置よりさらに半導体チップ10のサイズを減少させることも可能である。

図4では、ESD保護回路Eをパッド11Pの下に配置していないが、プロセス上可能であれば、パッド11P下も利用してさらに大きなESD保護回路Eを形成することもできる。かかる構成では、さらにESD保護性能が高い半導体チップ10を実現することが可能である。

【0031】

以上説明したように、本実施形態によれば、半導体チップ10のサイズを大きくすることなく、半導体チップ10にバンプ11を高密度に配置することができ、かつ、封止樹脂CPの充填不良(ボイド)が抑制され、封止樹脂CPの注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができるTAB型半導体装置1を提供することができる。

【0032】

「設計変更」

上記実施形態の半導体装置では、半導体チップ10において、複数のバンプ11からなるバンプ列12がバンプ列12の延びる方向に対して交差する方向に複数配列しており、かつ、複数のバンプ列12において、複数のバンプ11のうち2以上が(バンプ列12の延びる方向)に対して交差する方向に同軸配列していればよく、バンプ11の配列パターン及びインナーリード21の配設パターンは適宜設計変更できる。

以下、図面を参照して、設計変更例について説明する。

【0033】

<設計変更例1>

半導体チップ10とフィルム基材20との隙間及び封止樹脂CPの流動性等の条件から、インナーリード21Bの屈曲部の厚みがそれ程問題にならない場合は、図5に示す半導体装置1Aのように、内側バンプ11Bの側方で、内側バンプ11Bに接続されるインナーリード21Bを屈曲させてもよい。

かかる構成では、内側バンプ11Bに接続されたインナーリード21Bが、内側バンプ11Bより半導体チップ10の内側にはみ出さないため、上記実施形態よりも半導体チップ10のサイズをより小さくすることが可能である。

【0034】

<設計変更例2>

半導体チップ10において、バンプ列12の列数は3以上でもよい。

図6に示す半導体装置1Bは、バンプ列12の列数を3列とした例である。

図6において、外側バンプ列に符号12Aを付し、このバンプ列のバンプに符号11Aを付し、中央バンプ列に符号12Bを付し、このバンプ列のバンプに符号11Bを付し、内側バンプ列に符号12Cを付し、このバンプ列のバンプに符号11Cを付してある。

かかる設計変更では、より広い面積の封止樹脂CPの流入経路が確保されるため、より封止樹脂CPの注入効率が良くなるなどの効果が得られる。

【0035】

<設計変更例3>

図7に示す半導体装置1Cは、図6に示した設計変更例と基本構成は同様であるが、3列のバンプ列12において、3個のバンプ11A〜11Cのうち、2個のバンプ11A、11Bのみが、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向(本例では略垂直方向)に同軸配列し、バンプ11Cは同軸配列していない例である。

この例では、内側バンプ11Cに接続されたインナーリード21Cは直線状に配設されている。

複数のバンプ列12において、複数のバンプ11がすべてチップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列していることが最も好ましいが、3列以上のバンプ配列においては、2列以上の複数のバンプ11が同軸配列していれば、その横に2本以上のインナーリード21を配線する間隔ができるため、封止樹脂CPの流入効率に関して、特許文献1に記載の千鳥配置に対する優位的な効果が得られる。

【0036】

<設計変更例4>

バンプ列12が3列以上になると、同バンプ列12をなす互いに隣接するバンプ11間に充分な隙間ができるため、バンプ11の配列パターンの設計自由度が増す。

図8に示す半導体装置1Dは、図7に示した設計変更例において、内側バンプ11Cに接続されたインナーリード21Cを途中で屈曲させて、インナーリード21Cを直線状に配設した図7に示した設計変更例よりも内側バンプ11Cを若干その他の列のバンプ11A、11Bに近付けた例である。これにより、封止樹脂CPの流入がバンプ11Cの両側に略均等に起きるため、条件によっては図7の設計変更例4よりも封止樹脂の流入効率が良くなる。

【0037】

<設計変更例5>

図9に示す半導体装置1Eは、図5に示した設計変更例において、2列のバンプ11A、11Bがチップ辺10E(バンプ列12の延びる方向)に対して斜め方向に同軸配列した例である。

かかる構成でも、上記実施形態と同様の効果が得られる。かかる設計変更では、半導体チップ10上のバンプ11の配置の設計自由度が増し、レイアウトを効率的に行うことが可能となる。また、バンプ11Aと11Bとの間への封止樹脂CPの流入方向が斜め一方向(図示例では、図示左下方から図示右上方向への斜め一方向)になるため、バンプ11間への封止樹脂CPの流入が、より速くかつより確実になり、バンプ11Aとバンプ11Bとの間におけるボイドの発生確率が減少するという効果も得られる。

さらに内側バンプ11Bに接続されたインナーリード21Bを図示のように封止樹脂CPの流れの一部をバンプ列12間の隙間に誘導するような形状にすることにより、上記効果をより確実なものにすることができる。

【0038】

<設計変更例6>

図10は、上記実施形態の図4に対応する図にインナーリードを加えた図である。

図10に示す半導体装置1Fにおいては、図6に示した設計変更例と同様、3列のバンプ列12A〜12Cを有しているが、各バンプ11A〜11C(及びこれらのパッド11P)は、短軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略垂直方向、長軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略平行方向に配置されている。そして、3列のバンプ列12A〜12Cにおいて、3列のバンプ11A〜11Cがチップ辺10E(バンプ列12の延びる方向)に対して略垂直方向に同軸配列している。

【0039】

本例においても、互いに隣接する外側バンプ11A間、互いに隣接する中央バンプ11B間、及び互いに隣接する内側バンプ11C間のスペースに、面積の大きいESD保護回路Eを配置することができる。ESD保護回路Eには内部回路が接続される。

図中の符号W1はバンプ11のパッド11PとESD保護回路Eとを接続する配線を示し、符号W2はESD保護回路Eと内部回路とを接続する配線を示している。

本例において、インナーリード21A〜21CはいずれもL字状に配設されており、いずれのインナーリード21A〜21Cも、無理なく配設することが可能である。

【0040】

本例のように、各バンプ11A〜11Cを、短軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略垂直方向、長軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略平行方向に配置することにより、バンプ列12の数が増加しても、半導体チップ10のサイズを大きくすることなく、半導体チップ10に数多くのバンプ11を搭載することが可能である。

【0041】

「その他の設計変更」

本発明は上記実施形態に限らず、本発明の趣旨を逸脱しない範囲内において適宜設計変更可能である。

【符号の説明】

【0042】

1、1A〜1F 半導体装置

10 半導体チップ

10E チップ辺

11、11A〜11C バンプ(外部端子)

12、12A〜12C バンプ列(外部端子列)

20 フィルム基材(パッケージ基材)

21、21A〜21C インナーリード(引出配線)

【技術分野】

【0001】

本発明は、半導体チップに形成された電極をなす複数の外部端子と、パッケージ基材に形成された複数の引出配線とが接合され、複数の外部端子及び複数の引出配線が封止材により封止された半導体装置に関するものである。

【背景技術】

【0002】

半導体装置の一つとして、TAB(テープ・オートメイテッド・ボンディング)型半導体装置がある。

TAB型半導体装置では、半導体チップの電極となるパッド上の複数のバンプが、半導体チップのチップ辺に対して略平行方向に配列されており、最近では狭ピッチ化対応として2列以上の千鳥配列が増加している。通常、これらのバンプに接続されるフィルム基材のインナーリードは、バンプ上から半導体チップの外部に直線状に延在形成されている。

電子機器の小型化及び高機能化に伴って、これに搭載されるTAB型半導体装置も一層の小型化が必要となっている。そのためにはTAB型半導体装置内のインナーリードの狭ピッチ化(例えば、25μmピッチ→23μmピッチ→20μmピッチ)が進められている。

【0003】

特許文献1には、千鳥配置の複数のバンプを持つ半導体チップを用いたTAB型半導体装置において、封止樹脂(封止材)の流れを良くするための構造が提案されている。

図11に、特許文献1の図1に記載の半導体装置の要部平面図を示す。図12に、図11のXXII-XXII線断面図を示す。ここでは、特許文献1とは符号は変えてある。

【0004】

図示するTAB型半導体装置101は、半導体チップ110に形成された電極をなす複数のバンプ(外部端子)111とテープ状のフィルム基材(パッケージ基材)120に形成された複数のインナーリード(引出配線)121とを熱圧着で接合し、半導体チップ110とフィルム基材120との隙間に封止樹脂CPを注入し、これを硬化させて、製造されたものである。

図12には、封止樹脂CPの注入の様子が示されている。

【0005】

図11に示すように、半導体装置101の半導体チップ110においては、バンプ111が2列に千鳥配置されている。

図中、外側(チップ辺110E側)のバンプに符号111Aを付し、内側(チップの中央側)のバンプに符号111Bを付してある。

半導体チップ110の外側バンプ111Aには、フィルム基材120のインナーリード121Aが接合され、半導体チップ110の内側バンプ111Bには、フィルム基材120のインナーリード121Bが接合されている。

特許文献1では、外側バンプ111Aの内側から、互いに隣接する内側バンプ111B間を通る突起パターン130が設けられている(請求項1、図1、及び要約書等)。

【0006】

特許文献1には、上記構成により、半導体チップとフィルム基材とを接続し、その間に樹脂を注入する際に、突起パターンに伝わって封止樹脂が進行し、半導体チップの中央側の列のバンプ間の封止樹脂の流れが助長されるので、バンプ近辺のボイドの発生を防止することができることが記載されている(要約書等)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−221320号公報

【特許文献2】特開2001−284413号公報

【特許文献3】特開2006−19699号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1では、2列に千鳥配列された複数のバンプのうち、半導体チップのチップ辺側の列をなす複数の外側バンプの両側から半導体チップの内側方向への封止樹脂の流れだけを考慮しているため、半導体チップの中央側の列をなす複数の内側バンプの存在が樹脂注入を妨げとなる恐れがある。この様子を図13に模式的に示す。

特許文献1の突起パターンは、半導体チップのチップ辺側の列をなす複数の外側バンプの両側から半導体チップの内側方向への封止樹脂の流れを整流するだけで、半導体チップの中央側の列をなす複数の内側バンプに当たって流れが妨げられた封止樹脂の流れを良くすることはできない。

封止樹脂の流れの不良は、封止樹脂の充填不良(ボイド)を起こす場合がある。そのため、封止樹脂の注入速度を遅くする必要があり、生産性(歩留りと生産能力)を向上させることが困難となっている。また、外側バンプと内側バンプとの間隔を必要以上に広く取る必要があり、このことがチップサイズの増大及びチップコストの増加を招いている。

【0009】

特許文献2においても、封止樹脂の流れを良くするために、ベースフィルム(2)の半導体チップ(4)を搭載する搭載領域(2a)にパターン部材(20A)を設ける構成が提案されている(要約書)。特許文献2において、パターン部材(20A)はインナリード(8)の内側に形成され、半導体チップ(4)の周囲とパターン部材(20A)との間に封止樹脂(10)が充填される領域が画成されている。

特許文献2では、半導体チップの複数のバンプ(図2の符号4a)の配列については記載がない。したがって、半導体チップの複数のバンプを千鳥配置した場合、特許文献1と同様の課題を有する。

【0010】

特許文献3には、設計上の間隔の規格を遵守しながら、電極パッドを狭ピッチ化することを目的とし、電極パッドが多段に配列された半導体チップ(1)の外周に並んだ電極パッドの間を通って、内側の電極パッドに接続されたテープ配線基板(12)の配線(6)を2本以上まとめて半導体チップ(1)の外側へ引き出す構成が提案されている(要約書、図1)。

特許文献3では、最内周から2段目以降外周に配列された任意の電極パッド間にあらかじめ定められた所定の間隔を設け、最外周から2段目以降内側に配列された電極パッドと接続される配線のうちの隣接して配線される複数の配線を上記間隔に配設させている(請求項1)。

そのため、半導体チップのチップ辺に対して略垂直方向に見た場合、1個のバンプしかない箇所が多く存在し、バンプを高密度に配置することができない。

【課題を解決するための手段】

【0011】

本発明の半導体装置は、

半導体チップに形成された電極をなす複数の外部端子と、パッケージ基材に形成された複数の引出配線とが接合され、複数の前記外部端子及び複数の前記引出配線が封止材により封止された半導体装置であって、

前記半導体チップにおいては、複数の前記外部端子からなる外部端子列が、当該外部端子列の延びる方向に対して交差する方向に複数配列しており、かつ、前記複数の外部端子列において、複数の前記外部端子のうち2以上が前記外部端子列の延びる方向に対して交差する方向に同軸配列したものである。

【0012】

通常、外部端子は略矩形状である。

本明細書において、「同軸配列」とは、複数の外部端子列の延びる方向と交差する方向に並んだ互いに隣接する2つの外部端子の互いに対向する2つの辺のうち、一方の辺(2つの辺の長さに差がある場合は短い方)の半分以上が、他方の辺に対向している状態と定義する。

したがって、「同軸配列」において、上記条件を充たせば、外部端子列の延びる方向に対して交差する方向に並んだ互いに隣接する2つの外部端子の中心軸がずれていても構わない。

ただし、外部端子列の延びる方向に同軸配列した複数の外部端子は、中心軸を同軸として、同軸配列していることが好ましい。

【0013】

本発明の半導体装置においては、複数の外部端子列において、複数の外部端子のうち2以上が外部端子列の延びる方向に対して交差する方向に同軸配列しているので、半導体チップのサイズを大きくすることなく、特許文献3よりも半導体チップに外部端子を高密度に配置することができる。

本発明の半導体装置においては、複数の外部端子列において、複数の外部端子のうち2以上が外部端子列の延びる方向に対して交差する方向に同軸配列しているので、封止材の通り道が広く確保され、半導体装置への封止材の注入・浸透が容易である。そのため、封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができる。

【発明の効果】

【0014】

本発明によれば、半導体チップのサイズを大きくすることなく、半導体チップに外部端子を高密度に配置することができ、かつ、封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができる半導体装置を提供することができる。

【図面の簡単な説明】

【0015】

【図1】本発明に係る一実施形態の半導体装置の要部平面図である。

【図2】図1の半導体装置のII-II線断面図である。

【図3】図1の半導体装置において、封止樹脂の流れの様子を模式的に示す要部平面図である。

【図4】図1の半導体装置において、半導体チップのバンプ周辺の素子配置を示す要部平面図である。

【図5】設計変更例1を示す要部平面図である。

【図6】設計変更例2を示す要部平面図である。

【図7】設計変更例3を示す要部平面図である。

【図8】設計変更例4を示す要部平面図である。

【図9】設計変更例5を示す要部平面図である。

【図10】設計変更例6を示す要部平面図である。

【図11】特許文献1の半導体装置の要部平面図である。

【図12】図11の半導体装置のXXII-XXII線断面図である。

【図13】図11の半導体装置において、封止樹脂の流れの様子を模式的に示す要部平面図である。

【発明を実施するための形態】

【0016】

「一実施形態」

図面を参照して、本発明に係る一実施形態の半導体装置の構成について説明する。図1は本実施形態の半導体装置の要部平面図である。図2は図1の半導体装置のII-II線断面図である。図3は封止樹脂の流れの様子を模式的に示す要部平面図である。図4は半導体チップのバンプ周辺の素子配置を示す要部平面図である。

図面上は視認しやすくするため、各部材の縮尺や位置は適宜、実際のものとは異ならせて、簡略化してある。

【0017】

本実施形態の半導体装置1はTAB型半導体装置である。

本実施形態の半導体装置1は、半導体チップ10に形成された電極をなす複数のバンプ(外部端子)11とテープ状のフィルム基材(パッケージ基材)20に形成された複数のインナーリード(引出配線)21とを熱圧着で接合し、半導体チップ10とフィルム基材20との隙間に封止樹脂(封止材)CPを注入し、これを硬化させて、製造されたものである。

【0018】

フィルム基材20は可撓性を持ち、封止樹脂CPで封止された部分以外では折り曲げて、基板あるいは表示装置等に実装することが可能である。ここで、本実施形態の半導体装置が表示ドライバの場合、「表示装置」とは例えば、液晶(LCD)パネル、プラズマディスプレイ(PDP)パネル、エレクトロルミネッセンス(EL)パネル等の表示デバイスを指す。ただし、本実施形態の半導体装置が実装される装置は表示装置には限らない。

【0019】

図2には、封止樹脂CPの注入の様子が示されている。

半導体チップとパッケージ基材との境目に置かれた封止樹脂は、毛細管現象で半導体チップの下部に浸透していき、半導体チップ下のパッケージ基材との隙間を埋めることができる。半導体チップとパッケージ基材との隙間の間隔で所望の毛細管現象が効率的に起き、かつボイドの発生が無いように封止樹脂の粘度等が設計される。

【0020】

本実施形態の半導体装置1の半導体チップ10においては、半導体チップ10のチップ辺10Eに沿って配列した複数のバンプ(外部端子)からなるバンプ列(外部端子列)12が、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向に複数配列している。

本実施形態において、外側(チップ辺10E側)のバンプ列に符号12Aを付し、このバンプ列のバンプに符号11Aを付し、内側(チップの中央側)のバンプ列に符号12Bを付し、このバンプ列のバンプに符号11Bを付してある。

本実施形態ではさらに、上記2列のバンプ列12A、12Bにおいて、複数のバンプ11A、11Bが、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列している。

【0021】

本実施形態では、各バンプ11A、11Bは略矩形状であり、長軸方向がチップ辺10Eに対して略垂直方向、短軸方向がチップ辺10Eに対して略平行方向に配置されている。そして、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bが、チップ辺10Eに対して略垂直方向に同軸配列している。2個のバンプ11A、11Bは、中心軸を同軸として同軸配列している。

各バンプ11A、11Bは略矩形状のパッド11P上に形成されている(図4を参照)。

【0022】

半導体チップ10の外側バンプ11Aには、フィルム基材20上に形成されたインナーリード21Aが接合され、半導体チップ10の内側バンプ11Bには、フィルム基材20上に形成されたインナーリード21Bが接合されている。

本実施形態において、外側バンプ11Aに接続されたインナーリード21Aは半導体チップ10の外部から直線状に延びて、外側バンプ11Aに接続されている。内側バンプ11Bに接続されたインナーリード21Bは半導体チップ10の外部から、隣接する外側バンプ11A間及び隣接する内側バンプ11B間を通り、内側バンプ列12Bより内側で略J字状に屈曲して、内側バンプ11Bに接続されている。

【0023】

本実施形態の半導体装置1においては、2列のバンプ列12A、12Bにおいて、最も近接した2個のバンプ11A、11Bが、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列しているので、半導体チップ10のサイズを大きくすることなく、特許文献3よりも半導体チップ10にバンプ11を高密度に配置することができる。

本実施形態の半導体装置1においては、特許文献1に記載の2列の千鳥配置に対して、半導体チップ10のサイズを増加することなく、同等数のバンプ11を実装することができる。

【0024】

半導体装置1の製造においては、半導体チップ10上に配置された各バンプ11A、11Bとフィルム基材20上に形成されたインナーリード21A、21Bとを熱圧着により接合した後、図2に示すように、半導体チップ10とフィルム基材20との間に封止樹脂CPを流し込む。封止樹脂CPは、毛細管現象によって半導体チップ10とフィルム基材20との隙間に流れ込んでいく。

【0025】

図3は封止樹脂CPの流れの様子を模式的に示している。

図示するように、本実施形態では、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bがチップ辺10E(バンプ列12の延びる方向)に対して交差する方向(本実施形態では略垂直方向)に同軸配列しているので、外側バンプ11Bの間を流れてきた封止樹脂CPは、内側バンプ11Bに流れを邪魔されることなく直進して、半導体チップ10の内側まで到達する。この際、外側バンプ11Aと内側バンプ11Bと間には、封止樹脂CPの流れの一部が入っていく。

【0026】

本実施形態の半導体装置1においては、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bがチップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列しているので、封止樹脂CPの通り道が広く確保され、半導体装置1への封止樹脂CPの注入・浸透が容易である。そのため、封止樹脂CPの充填不良(ボイド)が抑制され、封止樹脂CPの注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができる。

【0027】

本実施形態においては、内側バンプ列12Bよりさらに内側でインナーリード21Bを屈曲させている。かかる構成では、インナーリード21Bの屈曲部分の厚みによって封止樹脂CPの流動が阻害される恐れもない。

【0028】

また、本実施形態においては、2列のバンプ列12A、12Bにおいて、2個のバンプ11A、11Bがバンプ列12の延びる方向に対して交差する方向に同軸配列している2つのバンプの組を、バンプ列12の延びる方向に複数かつ等間隔に配置している。そのため、それぞれの2つのバンプの組の間の封止樹脂CPが流動する部分の立体的形状を同一にすることができ、この部分の封止樹脂CPの流入時間を一定値に揃えることができる。これにより、バンプの横を通り抜けた封止樹脂CPのチップ下への流入が均一になり、全体の封止樹脂CPの流入効率が最大になるとともに、バンプの先のチップ下でのボイドの発生確率をさらに小さくすることができるようになる。

【0029】

図3等に示すように、本実施形態では、互いに隣接する外側バンプ11A間、及び互いに隣接する内側バンプ11B間にスペースが形成されている。このスペースは、インナーリード21Bの配設、及び同一面上に形成されているインナーリード21A、12B間の間隔を確保するために必要な部分であり、面積としては従来技術にもあったスペースである。本実施形態では、このスペースを略矩形状にして、半導体チップ10の面積を効率良く利用することを可能としている。

【0030】

図4は、本実施形態の半導体チップ10のバンプ11周辺の素子配置を示す要部平面図である。

本実施形態では、互いに隣接する外側バンプ11A間、及び互いに隣接する内側バンプ11B間のスペースに、面積の大きいESD保護回路Eを配置することができる。ESD保護回路Eには内部回路が接続される。

図中、符号W1はバンプ11のパッド11PとESD保護回路Eとを接続する配線を示し、符号W2はESD保護回路Eと内部回路とを接続する配線を示している。

本実施形態では、互いに隣接する外側バンプ11A間、及び互いに隣接する内側バンプ11B間のスペースに面積の大きいESD保護回路Eを配置することができるので、特許文献1に記載の千鳥配置よりさらに半導体チップ10のサイズを減少させることも可能である。

図4では、ESD保護回路Eをパッド11Pの下に配置していないが、プロセス上可能であれば、パッド11P下も利用してさらに大きなESD保護回路Eを形成することもできる。かかる構成では、さらにESD保護性能が高い半導体チップ10を実現することが可能である。

【0031】

以上説明したように、本実施形態によれば、半導体チップ10のサイズを大きくすることなく、半導体チップ10にバンプ11を高密度に配置することができ、かつ、封止樹脂CPの充填不良(ボイド)が抑制され、封止樹脂CPの注入速度を速めることが可能であり、信頼性の向上及び生産性(歩留りと生産能力)の向上、及びこれらによる低コスト化を図ることができるTAB型半導体装置1を提供することができる。

【0032】

「設計変更」

上記実施形態の半導体装置では、半導体チップ10において、複数のバンプ11からなるバンプ列12がバンプ列12の延びる方向に対して交差する方向に複数配列しており、かつ、複数のバンプ列12において、複数のバンプ11のうち2以上が(バンプ列12の延びる方向)に対して交差する方向に同軸配列していればよく、バンプ11の配列パターン及びインナーリード21の配設パターンは適宜設計変更できる。

以下、図面を参照して、設計変更例について説明する。

【0033】

<設計変更例1>

半導体チップ10とフィルム基材20との隙間及び封止樹脂CPの流動性等の条件から、インナーリード21Bの屈曲部の厚みがそれ程問題にならない場合は、図5に示す半導体装置1Aのように、内側バンプ11Bの側方で、内側バンプ11Bに接続されるインナーリード21Bを屈曲させてもよい。

かかる構成では、内側バンプ11Bに接続されたインナーリード21Bが、内側バンプ11Bより半導体チップ10の内側にはみ出さないため、上記実施形態よりも半導体チップ10のサイズをより小さくすることが可能である。

【0034】

<設計変更例2>

半導体チップ10において、バンプ列12の列数は3以上でもよい。

図6に示す半導体装置1Bは、バンプ列12の列数を3列とした例である。

図6において、外側バンプ列に符号12Aを付し、このバンプ列のバンプに符号11Aを付し、中央バンプ列に符号12Bを付し、このバンプ列のバンプに符号11Bを付し、内側バンプ列に符号12Cを付し、このバンプ列のバンプに符号11Cを付してある。

かかる設計変更では、より広い面積の封止樹脂CPの流入経路が確保されるため、より封止樹脂CPの注入効率が良くなるなどの効果が得られる。

【0035】

<設計変更例3>

図7に示す半導体装置1Cは、図6に示した設計変更例と基本構成は同様であるが、3列のバンプ列12において、3個のバンプ11A〜11Cのうち、2個のバンプ11A、11Bのみが、チップ辺10E(バンプ列12の延びる方向)に対して交差する方向(本例では略垂直方向)に同軸配列し、バンプ11Cは同軸配列していない例である。

この例では、内側バンプ11Cに接続されたインナーリード21Cは直線状に配設されている。

複数のバンプ列12において、複数のバンプ11がすべてチップ辺10E(バンプ列12の延びる方向)に対して交差する方向に同軸配列していることが最も好ましいが、3列以上のバンプ配列においては、2列以上の複数のバンプ11が同軸配列していれば、その横に2本以上のインナーリード21を配線する間隔ができるため、封止樹脂CPの流入効率に関して、特許文献1に記載の千鳥配置に対する優位的な効果が得られる。

【0036】

<設計変更例4>

バンプ列12が3列以上になると、同バンプ列12をなす互いに隣接するバンプ11間に充分な隙間ができるため、バンプ11の配列パターンの設計自由度が増す。

図8に示す半導体装置1Dは、図7に示した設計変更例において、内側バンプ11Cに接続されたインナーリード21Cを途中で屈曲させて、インナーリード21Cを直線状に配設した図7に示した設計変更例よりも内側バンプ11Cを若干その他の列のバンプ11A、11Bに近付けた例である。これにより、封止樹脂CPの流入がバンプ11Cの両側に略均等に起きるため、条件によっては図7の設計変更例4よりも封止樹脂の流入効率が良くなる。

【0037】

<設計変更例5>

図9に示す半導体装置1Eは、図5に示した設計変更例において、2列のバンプ11A、11Bがチップ辺10E(バンプ列12の延びる方向)に対して斜め方向に同軸配列した例である。

かかる構成でも、上記実施形態と同様の効果が得られる。かかる設計変更では、半導体チップ10上のバンプ11の配置の設計自由度が増し、レイアウトを効率的に行うことが可能となる。また、バンプ11Aと11Bとの間への封止樹脂CPの流入方向が斜め一方向(図示例では、図示左下方から図示右上方向への斜め一方向)になるため、バンプ11間への封止樹脂CPの流入が、より速くかつより確実になり、バンプ11Aとバンプ11Bとの間におけるボイドの発生確率が減少するという効果も得られる。

さらに内側バンプ11Bに接続されたインナーリード21Bを図示のように封止樹脂CPの流れの一部をバンプ列12間の隙間に誘導するような形状にすることにより、上記効果をより確実なものにすることができる。

【0038】

<設計変更例6>

図10は、上記実施形態の図4に対応する図にインナーリードを加えた図である。

図10に示す半導体装置1Fにおいては、図6に示した設計変更例と同様、3列のバンプ列12A〜12Cを有しているが、各バンプ11A〜11C(及びこれらのパッド11P)は、短軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略垂直方向、長軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略平行方向に配置されている。そして、3列のバンプ列12A〜12Cにおいて、3列のバンプ11A〜11Cがチップ辺10E(バンプ列12の延びる方向)に対して略垂直方向に同軸配列している。

【0039】

本例においても、互いに隣接する外側バンプ11A間、互いに隣接する中央バンプ11B間、及び互いに隣接する内側バンプ11C間のスペースに、面積の大きいESD保護回路Eを配置することができる。ESD保護回路Eには内部回路が接続される。

図中の符号W1はバンプ11のパッド11PとESD保護回路Eとを接続する配線を示し、符号W2はESD保護回路Eと内部回路とを接続する配線を示している。

本例において、インナーリード21A〜21CはいずれもL字状に配設されており、いずれのインナーリード21A〜21Cも、無理なく配設することが可能である。

【0040】

本例のように、各バンプ11A〜11Cを、短軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略垂直方向、長軸方向がチップ辺10E(バンプ列12の延びる方向)に対して略平行方向に配置することにより、バンプ列12の数が増加しても、半導体チップ10のサイズを大きくすることなく、半導体チップ10に数多くのバンプ11を搭載することが可能である。

【0041】

「その他の設計変更」

本発明は上記実施形態に限らず、本発明の趣旨を逸脱しない範囲内において適宜設計変更可能である。

【符号の説明】

【0042】

1、1A〜1F 半導体装置

10 半導体チップ

10E チップ辺

11、11A〜11C バンプ(外部端子)

12、12A〜12C バンプ列(外部端子列)

20 フィルム基材(パッケージ基材)

21、21A〜21C インナーリード(引出配線)

【特許請求の範囲】

【請求項1】

半導体チップに形成された電極をなす複数の外部端子と、パッケージ基材に形成された複数の引出配線とが接合され、複数の前記外部端子及び複数の前記引出配線が封止材により封止された半導体装置であって、

前記半導体チップにおいては、複数の前記外部端子からなる外部端子列が、当該外部端子列の延びる方向に対して交差する方向に複数配列しており、かつ、前記複数の外部端子列において、複数の前記外部端子のうち2以上が前記外部端子列の延びる方向に対して交差する方向に同軸配列した半導体装置。

【請求項2】

前記外部端子列の延びる方向が前記半導体チップの辺の方向と一致することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記同軸配列した前記2つ以上の外部端子の組が隣接して2以上あることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記同軸配列した前記2つ以上の外部端子の組が、等間隔で隣接して3以上あることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

【請求項5】

前記パッケージ基材が可撓性を持つフィルム基材であることを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記パッケージ基材が、テープ状の前記フィルム基材であることを特徴とする請求項5に記載の半導体装置。

【請求項1】

半導体チップに形成された電極をなす複数の外部端子と、パッケージ基材に形成された複数の引出配線とが接合され、複数の前記外部端子及び複数の前記引出配線が封止材により封止された半導体装置であって、

前記半導体チップにおいては、複数の前記外部端子からなる外部端子列が、当該外部端子列の延びる方向に対して交差する方向に複数配列しており、かつ、前記複数の外部端子列において、複数の前記外部端子のうち2以上が前記外部端子列の延びる方向に対して交差する方向に同軸配列した半導体装置。

【請求項2】

前記外部端子列の延びる方向が前記半導体チップの辺の方向と一致することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記同軸配列した前記2つ以上の外部端子の組が隣接して2以上あることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記同軸配列した前記2つ以上の外部端子の組が、等間隔で隣接して3以上あることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

【請求項5】

前記パッケージ基材が可撓性を持つフィルム基材であることを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記パッケージ基材が、テープ状の前記フィルム基材であることを特徴とする請求項5に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−190999(P2012−190999A)

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願番号】特願2011−53098(P2011−53098)

【出願日】平成23年3月10日(2011.3.10)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願日】平成23年3月10日(2011.3.10)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]