半導体集積回路配置プログラム及び方法

【課題】ブロック配置を含むIC設計作業において、やり直し等を削減でき、設計の工数等を低減でき、設計効率を向上できる技術を提供する。

【解決手段】本ブロック配置方法及びプログラムでは、実配置処理の前の段階で、ブロック配置領域の大きさを見積もり、局所的配線混雑の発生を判定し、その結果に基づいてユーザによるブロックの最適な位置の決定を可能とする。S1でブロック間接続情報を抽出し、S2でブロックの回路ゲート物量情報を抽出する。S3,S4でユーザによりGUIの画面でブロックの位置を決定する。S5で配線の要求混雑度を評価して画面に表示する。S6でユーザにより配置の妥当性を判定し、OKであれば、S7で実現性の高いブロック配置情報が出力される。

【解決手段】本ブロック配置方法及びプログラムでは、実配置処理の前の段階で、ブロック配置領域の大きさを見積もり、局所的配線混雑の発生を判定し、その結果に基づいてユーザによるブロックの最適な位置の決定を可能とする。S1でブロック間接続情報を抽出し、S2でブロックの回路ゲート物量情報を抽出する。S3,S4でユーザによりGUIの画面でブロックの位置を決定する。S5で配線の要求混雑度を評価して画面に表示する。S6でユーザにより配置の妥当性を判定し、OKであれば、S7で実現性の高いブロック配置情報が出力される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路(IC)の設計及び配置方法、そのための情報処理装置及びコンピュータプログラムに関し、特に、論理的なブロック等(回路配置領域)の階層を含んで構成されるICにおけるブロック配置方法に関する。

【背景技術】

【0002】

従来技術のIC設計及び配置方法において、情報処理装置を用いてユーザ(設計者)によりICチップ領域に複数のブロックを配置する方法及び配置配線実装処理などに関して、以下のようである。従来、論理設計者は、ブロック間の論理機能を考慮し、ブロック配置図面を作成する。その図面をもとに、実装設計者は、ブロック配置情報を作成し、配置配線プログラムによる処理を実行する。

【0003】

図16は、従来技術のIC設計及びブロック配置方法の処理及びユーザ作業等のフローを示している。IC設計工程は、例えば、論理設計者による論理設計工程と実装設計者による実装設計工程とに分けられる。枠で囲まれた部分は、実装設計者による実装設計工程(関連する一部のみ)である。

【0004】

論理設計工程において、論理設計者は、VHDLやVerilog等のHDLツール(901)及びその処理を用いて論理ファイル(902)を作成する。論理ファイル(902)は、レジスタ転送レベル等でのデジタル回路の記述情報である。論理ファイル(902)を入力として、論理合成処理(903)及びそのツールにより、ゲートレベルネットリスト(906)や、合成結果レポート(907)等の情報データが出力される。ゲートレベルネットリスト(906)は、回路ゲートレベルにおける端子間の接続配線関係(ネット)のリスト情報である。合成結果レポート(907)は、回路ゲート物量情報などを含む。また、論理設計者は、論理ファイル(902)をもとに、ブロック間の論理機能を考慮して、ブロック配置図面(905)を作成する作業を行う。ブロック配置図面(905)は、手書き等により、ブロック配置(接続関係)がわかるように簡単に書き表した図面である。

【0005】

実装設計工程において、実装設計者は、論理設計者によって作成されたブロック配置図面(905)に基づき、ゲートレベルネットリスト(906)等を入力として、ブロック配置情報作成ツール(911)及びその処理を用いて、ブロック配置情報ファイル(913)を作成する。この際、実装設計者による配置可否判定(914)でOKであれば、ブロック配置情報ファイル(913)が得られる。

【0006】

そして、実装設計者は、ブロック配置情報ファイル(913)を用いて、配置配線プログラムによる処理(配置配線実装処理)(914)を実行する。当該処理を実配置処理などと略称する。当該処理には相応の時間を要し、大規模な回路ほど長時間となる。その処理の後、実装設計者による配線混雑度評価(915)でOKであれば、本ブロック配置及び実配置処理等の工程は終了であり、次のステップ(省略)へ進むことができる。

【0007】

また、ブロック配置方法に関し、特開2003−330986号公報(特許文献1)記載の技術では、ブロック位置を決定後、ブロック形状を決定し、配置配線プログラムによる処理(配置配線実装処理)を実行する。ここで実装設計者は、その処理結果におけるブロック内外配線混雑、及びタイミング制約違反を対策するために、ブロック形状を変更し、再度、配置配線実装処理を実行し、ブロック間配線混雑、ブロック内配線混雑、タイミング制約が解消されるまで繰り返す。

【特許文献1】特開2003−330986号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

前記従来技術のIC設計及びブロック配置方法において、以下のような問題がある。

【0009】

実装設計者がブロック配置情報ファイル(913)を作成する時、論理設計者によるブロック配置図面(905)上のブロック配置領域の大きさと、論理合成処理(903)後のブロック配置領域の大きさと、が異なることにより、同一にはブロック配置情報ファイル(913)が作成できない、という事態が発生することが多い。図16では、配置可否判定(912)でNGの場合である。この場合、解消のために、再度、論理設計者によるブロック配置図面作成(904)、ブロック配置の見直し、等が必要になる。即ち、設計作業のやり直しや後戻りが発生する。

【0010】

また、配置配線プログラムによる処理(914)の実行の結果、配線の局所的な混雑が発生する場合がある。図16では、実装設計者による配線混雑度評価(915)でNGの場合である。この場合、上記と同様に、解消のために、再度、ブロック配置図面作成(904)、ブロック配置の見直し、等が必要になる。

【0011】

上記のように、従来技術では、設計工程におけるブロック配置領域の大きさのズレや、局所的配線混雑の発生などにより、設計作業のやり直しや後戻り、ブロック配置見直し、再プログラム処理時間などが発生することによって、設計の工数、期間、及びコストの増加、並びに設計効率低下、といった問題がある。

【0012】

また、前記特許文献1の手法においても、ブロック間配線混雑、ブロック内配線混雑、タイミング制約が解消されるまで、ブロック位置及びブロック形状の見直しや、配置配線プログラムによる処理を繰り返す必要がある。よって上記同様に設計期間増加などの問題につながる。

【0013】

本発明は以上のような問題に鑑みてなされたものであり、その目的は、上記ブロック配置を含むIC設計作業において、やり直し等を削減でき、設計の工数、期間、コストを低減でき、設計効率を向上させることができる技術を提供することである。また特に、上記ブロック配置等の設計作業の効率を向上させることができるユーザインタフェースを提供することである。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。前記目的を達成するために、本発明は、ブロック等の階層を含んで構成されるICのチップ領域におけるブロック配置方法を含むIC設計及び配置方法、その処理作業を行うための情報処理装置、及びコンピュータプログラムに係わり、以下に示す構成を有することを特徴とする。

【0015】

本方法では、実装設計者が、配置配線プログラム処理(実配置処理)を実行する前の段階で、論理的(仮想的)にブロック配置(ブロック配置領域の大きさを含むブロック構成情報)の見積もり及び配線混雑の発生の予測・判定(配線物量及び配線要求混雑度の見積もり及び評価を含む)を行う。そして本方法では、その結果に基づきユーザの操作に従ってブロックの最適な配置を決定する処理(ブロック配置情報作成処理)を行う。本処理は前述した2つの問題に対処するための処理を含んでいる。

【0016】

具体的に、本方法では、論理合成処理結果の情報データ(ネットリスト等を含む)等に基づき、ブロック配置情報の作成段階で、配置対象ブロックに関して、(a)ブロック配置領域の大きさと、(b)配線物量と、を見積もる処理を行う。そして本方法では、それら(a),(b)の見積もりに基づき、(c)配線要求混雑度を見積もり及び評価する。このような情報を、GUI機能により、画面に設計情報と共に表示する。ユーザは、このような情報の参照、確認により、ブロック配置領域の大きさや、局所的配線混雑が発生しないかどうか等を予測しながら、実現性の高いブロック配置を決定することができる。

【0017】

本方法及び対応プログラムでは、以下のような処理工程及び処理機能を有する。

【0018】

(1)前記論理合成処理結果の情報データ(A)をもとに、ブロックの回路ゲート物量情報(B)と、ブロック間の接続情報(C)とを抽出する処理を行い、これにより、配置対象の複数のブロックにおけるブロック相互の関係(ブロック間接続関係)(D)を、GUIにより画面に表示する処理機能を有する。ブロック間接続情報(C)は、ネットリスト等をもとに、ブロック同士の接続関係を表した情報データである。例えば、上記複数ブロック間接続関係(D)の表示では、接続ブロック間を線で結んで表示し、ユーザ操作によりブロックが移動されると共に、接続関係を維持しながら表示内容を更新する。

【0019】

(2)前記回路ゲート物量情報(B)と、ブロック実装率情報(E)とに基づき、ブロック配置領域面積(F)(前記ブロック配置領域の大きさ)を見積もる処理を行う。そして、そのブロック配置領域面積(F)を維持しつつ、アスペクト比(縦横長さ比率)をユーザにより自由に変更可能として画面に表示する処理機能を有する。

【0020】

(3)また、前記ブロック間接続情報(C)を客観的に把握するために、ユーザ操作に応じて、画面に、ブロック間の接続ネット数(G)(ネットリスト等による)などに応じてブロック間の接続線の太さや色などを変えて表示する処理機能を有する。また、ユーザ操作に応じて、画面に、前記ブロック間の接続ネット数(G)を表示する処理機能を有する。また、ユーザ操作に応じてそれらの情報の表示/非表示を自由に切り替える処理機能を有する。

【0021】

(4)例えば予め配置位置が決められたブロック等について、ユーザ操作に応じて、画面で、座標などを指定して当該ブロックを配置することができ、且つその配置位置から誤って移動できないように固定することができ、また、当該固定されたブロックの色などを変えて表示することで他のブロックとの区別を容易にする処理機能を有する。

【0022】

(5)ユーザによりブロックの配置位置を一旦決めた時点で、ある一定領域内で配線可能な領域(配線使用可能率及び領域)に対して、どれだけの配線領域を必要としているかを予測した値(配線要求混雑度(H))を評価し、これに応じて、画面で、配線混雑箇所を強調して表示する処理機能を有する。特に、前記配線要求混雑度(H)の予測及び評価の処理については、領域の配線層ごとに、電源配線等の固定配線分を考慮して配線使用可能率を設定し、それに応じた配線混雑度評価を行う。また特に、配線混雑箇所の表示については、チップ領域等をメッシュ状など単位領域に分割し、その領域ごとの混雑度に応じて、色などを変えて表示する。

【0023】

(6)ある配置対象ブロックに対する接続関係のある全ブロックにおける配置座標で構成される領域の重心点の座標(I)(配線物量を考慮した重心)を表示する処理機能を有する。

【0024】

(7)チップ全面の配置可能領域を、前記ブロックとは別にリージョン等の階層によって分割し、その分割された領域(リージョン)ごとに、個別に、上記のようなブロック配置等の処理作業を並行して行うことができる処理機能を有する。また、その同時並行作業のために分割された領域(リージョン)ごとに個別に作成されたブロック配置情報を、チップ領域への実配置処理等のために1つの配置情報に併合する処理機能を有する。

【0025】

本IC配置方法は、例えば、複数のブロックを含んで構成される半導体集積回路のチップ領域におけるブロックの配置において、設計者の操作に応じてGUIで画面に設計情報を表示し、論理合成処理結果情報の入力に基づき、設計者によるブロックの配置を含む処理を行って、配置配線実装処理のための情報を出力する処理をコンピュータで実行するものであり、論理合成処理結果情報をもとに、ブロック間の接続情報、及びブロック内の回路ゲート物量情報を抽出する第1の処理工程、ブロック内の回路ゲート物量情報とブロック実装率情報とから、配置対象ブロック毎に、必要なブロック配置領域面積を含むブロック構成情報を見積もり、ブロック構成情報を含むブロック配置初期情報を作成する第2の処理工程、ブロック配置初期情報をもとに、設計者の操作に応じて、ブロック相互の関係を画面に表示し、チップ領域へのブロックの配置を決定しブロック配置情報を作成する第3の処理工程、ブロック配置情報における配置されたブロックについて、ブロック間の接続情報に基づくブロック間配線長の見積もり及びブロック内配線長の見積もりから、チップ領域内における配線領域の必要量を見積もり、これにより配線要求混雑度を評価し、この配線要求混雑度の状態を画面に表示する第4の処理工程、及び、ブロック配置情報を出力する第5の処理工程を有する。

【発明の効果】

【0026】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。本発明によれば、上記ブロック配置を含むIC設計作業において、やり直し等を削減でき、設計の工数、期間、コストを低減でき、設計効率を向上させることができる。また特に、上記ブロック配置等の設計作業の効率を向上させることができるユーザインタフェースを提供できる。

【発明を実施するための最良の形態】

【0027】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一部には原則として同一符号を付し、その繰り返しの説明は省略する。

【0028】

<システム>

図1において、本実施の形態のIC設計及びブロック配置方法及びプログラムを適用する情報処理システムの構成例を示している。本システムは、コンピュータネットワーク300上で接続される情報処理装置である、1つ以上のサーバコンピュータ100と、1つ以上のクライアントコンピュータ200と、を有して構成される、クライアントサーバシステムの形である。サーバコンピュータ100は、クライアントコンピュータ200からアクセスされ、プログラムや情報データなどを管理する。ユーザ(設計者)は、クライアントコンピュータ200を使用、操作して、サーバコンピュータ100の処理機能及び情報データをアクセスして利用する。本方法では、グラフィカルユーザインタフェース(GUI)機能を含む処理機能を実現するプログラムにより、クライアントコンピュータ200のディスプレイ画面に、設計に係わる情報(設計情報)を表示する。ユーザは、その画面を見て設計情報を編集することでIC設計作業を行う。

【0029】

なお、1台の情報処理装置にサーバコンピュータ100及びクライアントコンピュータ200の相当機能を備えて一人のユーザにより作業する形態なども勿論可能である。

【0030】

図2のように、サーバコンピュータ100は、制御装置110、主記憶装置120、補助記憶装置130、ネットワーク接続部140等を有する構成である。

【0031】

図3のように、クライアントコンピュータ200は、制御装置210、主記憶装置220、補助記憶装置230、ネットワーク接続部240、ディスプレイ250等の出力装置(他にプリンタ等)、キーボード260及びマウス270等の入力装置、等を有する構成である。

【0032】

本ブロック配置方法に対応するプログラム(ブロック配置プログラム10等)は、例えば、サーバコンピュータ100の補助記憶装置130に記憶されている。また、例えば、補助記憶装置130には、本プログラムによる処理機能に関わる各種の情報データも記憶され管理される。本プログラムは、例えば、一般的なIC設計ソフトウェアに対する追加的なプログラムとして実現可能である。

【0033】

本例では、補助記憶装置130(例えばHDD)には、ブロック配置プログラム10、論理ファイル11、ゲートレベルネットリスト12、ブロック構成情報13、回路ゲート物量情報14、ブロック実装率情報15、搭載領域情報16、接続情報17等が記憶される。

【0034】

また、クライアントコンピュータ200の補助記憶装置230(例えばHDD)等には、IC設計作業に応じて、設計情報20、ブロック配置情報21、ブロック間接続情報22などが格納される。設計情報20は、作業データであり、サーバコンピュータ100から読み出した情報、及びサーバコンピュータ100へ書き込む情報などを含む。

【0035】

サーバコンピュータ100側では、補助記憶装置130上のプログラム(ブロック配置プログラム10)は、主記憶装置120にロードされて制御装置110により実行される。また、クライアントコンピュータ200側では、制御装置210により、コンピュータネットワーク300を介して、サーバコンピュータ100側の処理機能(プログラム)及び情報データにアクセス及びデータ入出力する。それにより、クライアントコンピュータ200側で必要なプログラム及び情報データが、主記憶装置220にロードされて制御装置210により実行される。これらにより、ブロック配置処理を含むIC設計処理が実現される。

【0036】

本システムの利用において、ユーザは、クライアントコンピュータ200のキーボード260やマウス270等の操作によりコマンドを入力、選択することで、例えば、サーバコンピュータ100側の情報データを読み出す指示を実行する。指示はネットワーク接続部240及びコンピュータネットワーク300を介してサーバコンピュータ100へ送信される。これに応じて、サーバコンピュータ100側のプログラム(ブロック配置プログラム10)が実行され、指示に応じた結果の情報が、ネットワーク接続部140及びコンピュータネットワーク300を介してクライアントコンピュータ200側へ送信される。そして、ディスプレイ250等で結果が確認できる。

【0037】

<情報データ>

論理ファイル11は、ユーザによりHDLツール等で作成される。ゲートレベルネットリスト12及び回路ゲート物量情報14等は、論理合成処理結果として得られる。構成情報13は、チップ、ブロック等の階層を含む、基本的な構成を表す情報である。ブロック実装率情報15は、仕様などに応じて決まり、例えばユーザにより入力設定される。搭載領域情報16は、ブロックを搭載する領域の座標などの情報である。接続情報17は、ブロック内やブロック間の接続関係を表す情報である。ブロック配置情報21は、クライアント側で作成されたデータであり、ブロック(ブロック配置領域)の面積、配置位置座標、縦横長さなどの情報(ブロック構成情報)を持ち、ブロック間接続情報22などと関連付けられる。ブロック間接続情報22は、クライアント側の処理で抽出された、ブロック間の接続関係を表す情報であり、サーバ側の接続情報17と関連付けられる。クライアント側のデータは、サーバ側へのデータへ統合される。

【0038】

本処理機能(ユーザ設定機能)では、画面でのGUI表示などによって、ブロック実装率情報15などの他、設計に係わる各種の値をユーザ操作により指定(設定)が可能である。

【0039】

<ブロック配置方法>

本ブロック配置方法では、論理合成処理結果の情報データ等に基づき、ブロック配置情報21の作成段階で、配置対象ブロックに関して、(a)ブロック配置領域の大きさと、(b)配線物量と、を見積もる処理を行う。(a)ブロック配置領域の大きさは、配置対象ブロックの回路ゲート物量情報14などから見積もる。(b)配線物量は、配置対象ブロックに関連(接続関係)のあるブロックとの配線物量(接続配線物量)、及び配置対象ブロックの周辺ブロックを含めた配線物量(周辺配線物量)を見積もる。

【0040】

そして本方法では、それら(a),(b)の見積もりに基づき、(c)配線要求混雑度を見積もり及び評価する。このような情報を、GUI機能により、画面に設計情報20と共に表示する。ユーザは、このような情報の参照、確認により、ブロック配置領域の大きさや、局所的配線混雑が発生しないかどうか等を予測しながら、実現性の高いブロック配置(位置やサイズ等)を決定することができる。即ち、上記決定によるブロック配置情報の作成の後、それに対する配置配線プログラム処理(実配置処理)を実行すると、上記のように適切な見積もり等が実行済みであることによって、前述のやり直し等が発生しない可能性が高い。

【0041】

<フロー(概要)>

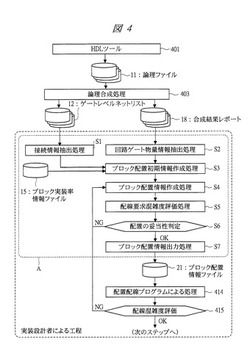

次に、図4において、本ブロック配置方法の処理、ユーザ作業等の工程、入出力情報等のフローを示している(Sは処理ステップを示す)。本IC設計工程は、論理設計者による論理設計工程と実装設計者による実装設計工程とに分けられる。枠で囲まれた部分は、実装設計者による実装設計工程(関連する一部のみ)である。そのうち更に、Aで示す部分は、図16のような従来技術とは異なる、本方法で特徴的な技術の部分を示す。まず以下に概略工程を示す。

【0042】

論理設計工程において、論理設計者は、VHDLやVerilog等のHDLツール(401)を用いて論理ファイル11を作成する。論理ファイル11を入力として、論理合成処理(論理合成ツール)(403)により、ゲートレベルネットリスト12や、合成結果レポート18等の情報データが出力される。

【0043】

実装設計工程において、実装設計者は、論理合成処理結果の情報データに基づき、ゲートレベルネットリスト12、合成結果レポート18等を入力として、ブロック配置を含む処理作業を行う。

【0044】

S1(接続情報抽出処理)では、ゲートレベルネットリスト12をもとに、ブロック内の回路ゲート同士(ブロック内)及びブロック同士(ブロック間)の接続関係を含む接続情報17(ブロック内接続情報及びブロック間接続情報)を抽出する。

【0045】

S2(回路ゲート物量情報抽出処理)では、合成結果レポート18をもとに、ブロック内の論理を構成する回路ゲートの物量情報(回路ゲート物量情報14)を抽出する。回路ゲート物量情報14をもとにブロック配置領域面積の大きさが見積もられる。

【0046】

S3(ブロック配置初期情報作成処理)では、S1で求めたブロック間接続情報(接続情報17)と、S2で求めたブロックの回路ゲート物量情報14と、ブロック実装率情報15(例えばユーザにより設定される)とから、ブロック配置初期情報(初期状態のブロック配置情報21)を作成する。ブロック配置初期情報は、ブロック配置領域面積(ブロック配置領域の大きさ)などの見積もりを含んでいる。

【0047】

ここで、ブロック実装率情報15とは、ブロック内の回路ゲートを敷き詰めて配置するための領域を1としたとき、回路ゲート同士を接続するための接続線を配線するために必要な領域、を加えたときの割合である。

【0048】

S4(ブロック配置情報作成処理)では、S1で抽出したブロック間接続情報(接続情報17)をもとに、実装設計者が、ブロック位置を決定する。処理としては、実装設計者の操作による編集作業に応じて、画面に情報を表示する。これにより、ブロック配置状態を表すブロック配置情報21が作成される。

【0049】

S5(配線要求混雑度評価処理)では、S4で決定したブロックの配置をもとに、配線の要求混雑度を評価する。ここで、配線の要求混雑度とは、配線物量(ブロック間配線物量及びブロック内配線物量)と、チップを構成する半導体の特性で定められている配線可能な物量と、の比率である。配線物量(ブロック間配線物量及びブロック内配線物量)は、ブロック間の接続数及びその距離から求めたブロック間配線長と、ブロック内の回路ゲートの配線を考慮したブロック内配線長と、から求められる。配線可能な物量は、複数存在する配線層の和で求められ、一般の論理に使用可能な物量は配線層ごとに異なる。

【0050】

S6(配線妥当性判定)では、実装設計者が、S5の評価結果をもとに、実現性のある(実現性の高い)ブロック配置であるかどうかの妥当性を判定する。NGと判定されればS4へ戻り、再度ブロック配置が検討される。OKと判定されれば、S7へ進む。

【0051】

S7(ブロック配置情報出力処理)では、ブロック配置情報ファイル21を出力する。出力されたブロック配置情報ファイル21は、従来技術に比べて実現性の高いブロック配置情報となっている。これにより、Aの部分の工程は終了し、その後は、例えば従来技術と同様の実配置処理などに続く。

【0052】

即ち、実装設計者は、ブロック配置情報ファイル21を用いて、配置配線プログラムによる処理(414)を実行する。その処理の後、実装設計者による配線混雑度評価(415)でOKであれば、ブロック配置及び実配置処理は終了であり、次のステップ(省略)へ進むことができる。

【0053】

<フロー(詳細)>

次に、以下、フロー詳細及び関連する画面表示例などを順に示す。

【0054】

前記S1,S2では、ユーザ(実装設計者)は、クライアントコンピュータ200の操作によりコマンドを入力することで、サーバコンピュータ100側にある、ブロックの回路ゲート物量情報14と、ブロック内及びブロック間の接続情報17と、を含む情報を抽出する指示を実行する。これに応じて、サーバコンピュータ100側のプログラム(ブロック配置プログラム10)が実行され、上記回路ゲート物量情報14と接続情報17とを含む結果の情報が、クライアントコンピュータ200のディスプレイ250等で確認できる。

【0055】

<構成情報>

図5は、設計対象のチップCの領域に搭載(配置)するブロック等に関する構成情報(構成情報13)の一部例を示す。チップC,リージョンR,ブロックBという階層構成の場合である。なお「ブロック」等の階層の名称は便宜的なものである。本例では、チップCの領域は、リージョンR1〜R5に分けられ(例えば図13)、更に、例えばリージョンR1の領域には、ブロックB1〜B8が搭載(配置)される。リージョンRは、チップCに含まれる論理(領域)の一部である。チップC領域内の複数のリージョンR、リージョンR内の複数のブロックB、といったように、2階層以上を持つ構成のICの設計を対象としている。

【0056】

また、本処理機能では、ブロック配置については、チップC領域に直接に全ブロックBを一括で配置する方法(リージョンR無し)と、チップC領域の全体の配置可能な領域を複数のリージョンRに分割し、そのリージョンR毎にブロックBを配置する方法と、の2つをユーザにより選択指定可能とする。

【0057】

<ブロック接続情報>

図6は、チップC(リージョンR1)に搭載(配置)するブロック(B1〜B8)に関するブロック接続図の一部例を示す。このブロック接続図は、ブロック同士の接続関係、論理の構成を視覚的にわかりやすいように図示したものである。S1の処理によって求められたブロック間接続情報(接続情報17)から、図6のようなブロック接続図を、必要に応じて作成して用いることができる(必須ではない)。

【0058】

図6のブロック接続図では、ブロック(B1〜B8)の接続関係は以下の通りである。なお矢印は信号配線入出力関係である。B1は、B3,B4と接続される(B1の出力は、B3,B4へ入力される)。B2は、B4,B5,B6と接続される。B3は、B4と相互接続される。B4は、B5と相互接続される。B3,B4,B5は、B7と接続される。B6は、B8と接続される。

【0059】

一方、ブロック間接続情報(接続情報17)は、上記のようなブロック接続図で示される内容を情報データとして構成したものである。例えば、データベースのレコードにおいて、B1の情報に対してB3,B4の情報が関連付けされる。

【0060】

実装設計者は、S1で求められた接続情報17(またはそれをもとに作成したブロック接続図)を参照することにより、ブロック間接続関係を知ることができる。そのため、従来技術のような論理設計者によるブロック配置図面作成(904)の作業を省略することができる。

【0061】

<ブロック配置初期情報>

図7は、前記S3で求めたブロック配置初期情報の例である。リージョンR1に含まれるブロックB1〜B8の大きさを抽出して配置した例を示している。本例は、チップCの右上にリージョンR1の領域がある場合である。各ブロックB1〜B8の配置領域の大きさ(面積)が抽出されている。初期段階(ユーザによる配置前)では、まだ、ブロックが配置情報(ブロック構成情報)を持たないため、適当な箇所に配置表示処理する。例えば、すべてのブロックを、領域の左下、中央など、一箇所にまとめられて配置表示されるようにする。また、ブロックが縦横長さ情報なども持たないため、例えば正方形で表示されるようにする。

【0062】

また例えば、チップ領域に直接にブロックを配置する場合、全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、チップ領域の外側に配置しておくようにしてもよい。また例えば、リージョン毎にブロックを配置する場合、全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、該当リージョンの内側に配置しておくようにしてもよい。

【0063】

また、チップ領域を分割したリージョン領域の名称を論理ファイル名称と同一とすることにより、例えば、リージョンR1の領域内にはブロックB1,ブロックB2,……,ブロックB8を配置する、というような指定をしなくても、ブロックB1〜B8はリージョンR1の領域内に配置するものと判断可能とする。

【0064】

図7はチップC領域の内側かつ該当リージョンR1の外側にブロックを配置した場合である。

【0065】

<ブロック配置情報>

前記S4では、接続情報17及びブロック配置初期情報をもとに、実装設計者が、ブロック配置位置を決定する。例えば、実装設計者は、マウス270操作により各ブロックをドラッグして好きな位置に移動する。これにより、例えば図8のようなブロック配置状態とする。この状態は、ブロック配置情報21に反映される。

【0066】

図8では、図7で示したチップCのリージョンR1に含まれるブロックB1〜B8におけるブロック配置初期情報をもとに、実装設計者が、ブロック間接続情報(接続情報17)を考慮して、リージョンR1内にブロックB1〜B8を配置した例を示す。ブロックB1〜B8の接続関係は前記図6の通りである。また例えば、リージョンやブロック等の名称を、適当な箇所、例えば矩形の内側または外側の一箇所に表示する。

【0067】

この時、図8のように、本プログラム処理により、接続関係のあるブロック同士を直線(接続線)で結ぶことによって、接続情報17(ブロック接続関係)をイメージとして画面に表示する。例えばブロック中心点同士が結ばれる。また、この接続情報17による接続線について、ブロック間の接続ネット数(ゲートレベルネットリスト12等からわかる)に応じて、太さを変えて表示する。これにより、ユーザは、ブロックの接続に関する論理的な結合度を知ることができ、対象とするブロック同士を近くに配置すべきか遠くに配置してもよいか等の判定が容易にできる。ユーザによりブロックが移動されても、接続線の表示が維持される。

【0068】

また、本処理機能では、ユーザが操作によりブロック配置位置を決定する際、図7のような初期のブロック矩形の状態のまま配置できるだけでなく、簡単な操作に応じて、当該ブロック矩形(ブロック配置領域)の面積を一定のまま、もしくは下回らない範囲で、アスペクト比(縦横長さ比率)を変化させることができる。例えばコントロールキー+wキーで横長に、コントロールキー+hキーで縦長に変更できる。これにより、ユーザは、ブロック同士の重なりを回避、解消して配置すること等ができる。

【0069】

また、本処理機能では、ブロック間の接続線などの表示については、表示/非表示をユーザにより適宜選択できる。また例えば、ユーザにより指定される配置対象ブロックについてのみ、それと接続関係のブロック間で表示するように指定することができる。あるいは、例えば、指定がなければ、すべてのブロックについて自動的に表示するようにすることができる。

【0070】

<配線要求混雑度>

前記S5では、S4で決定されたブロックの配置(ブロック配置情報21)から、配線の要求混雑度を評価する。本プログラム処理により、実配置処理(414)の前の段階(ブロック配置情報作成段階)で、配線要求混雑度の評価を行う。

【0071】

図9には、本プログラム処理により、混雑度(配線要求混雑度)を評価してその結果を画面に表示させた例を示す。配線要求混雑度は、ある一定領域内で配線可能な領域(配線使用可能率及び領域)に対して、どれだけの配線領域を必要としているかを予測・評価した値である。配線要求混雑度は、配置対象領域における配線使用可能率を考慮した値を設定して求めることができる。配線使用可能率は、配線層毎に設定された電源配線等の固定配線で使用不可能な比率を差し引いたものである。

【0072】

上記結果の表示方法には様々あるが、例えば、図9のように、チップC(リージョンR)領域全体を一定間隔で区切ったメッシュ状(格子状)の範囲(最小分割領域)を設け、この分割領域内を混雑度に応じて着色して表示する方法などを用いる。混雑度が高い領域を目立つように表示する。例えば、混雑度が、0〜30%では無色、30〜50%では緑色、50〜70%では黄色、70〜100%では桃色、100%以上では赤色、といったようにグラデーション表示する。これにより、ユーザは、領域におけるどの箇所が配線で混雑するか等を容易に判定することができる(S6の妥当性判定)。例えば混雑度が100%以上の箇所は事実上配線不可能と判定されるため、ブロック配置を変更する必要があることがわかる。

【0073】

また、上記メッシュ状の分割領域については、ユーザにより、X(横),Y(縦)方向で分割数や単位長などを指定することによって均等分割した単位とすることができる。

【0074】

また、分割領域ごとの配線要求混雑度については、例えば以下のように求める。分割領域の使用可能なチャネル(配線チャネル)の総数に対して、その領域内にあるブロック内配線及びその領域を通過するブロック間配線が使用する配線チャネルの使用予測数によって求める。

【0075】

また特に、ブロック内のチャネルの混雑度については、配置されたブロック内の回路ゲートで使用するピン(端子)の総数から、接続するブロック内のネットの総配線長を求め、求めた配線を引くために必要なブロック内のチャネル数を求める。

【0076】

また特に、ブロック内のチャネルの混雑度については、配置されたブロックの領域が、複数の分割領域にかかる場合、上記求めたブロック内の使用チャネル数を、複数の分割領域上の占有領域に応じて分割して配分してブロック内の使用チャネル数を求める。

【0077】

また特に、ブロック内のチャネルの混雑度については、配置された各ブロックから、接続関係のあるすべてのブロックを対象にして、その中からまず、接続関係のある2つのブロックにおいて、その2つのブロックを含む最外郭矩形内に入る分割領域の個数を、それぞれX,Y方向について2ブロック矩形内分割領域数として求め、次に、上記2ブロック間で、接続するネット本数を、上記求めたX,Y方向の分割領域数で割って、この2ブロックを含む最外郭矩形内に入る各分割領域のX,Y方向を通過する配線チャネル使用数を求め、同様に、他の接続の組み合わせとなる2ブロック間についても、それぞれ分割領域のX,Y方向を通過する配線チャネル使用数を求める。その後、チップ領域上で同一位置の分割領域についてそのX,Y方向を通過する配線チャネル使用数の総和を求める。これにより、分割領域毎のブロック間配線に必要なX,Y方向の配線チャネル数を表示する。

【0078】

また特に、本処理機能では、チップ領域の配線層毎に、それぞれの配線層で予め使用領域が決定されている電源配線を含む固定配線を除いた配線チャネル数を、その層の使用可能なチャネル総数として、ユーザにより指定可能とする。

【0079】

また特に、本処理機能では、配線要求混雑度の表示については、上記に基づき、ブロック内配線のみの混雑度、ブロック間配線のみの混雑度、ブロック内及びブロック間を合わせた混雑度などについての表示をユーザにより指定可能とする。

【0080】

<ブロック間接続ネット数>

図10では、前述した図8のようなブロック配置及び接続関係の表示において、更に、ブロック間接続ネット数を表示する例を示す。ブロック間接続ネット数は、ゲートレベルネットリスト12等からわかる。例えば、ブロックB3と関係があるのは、B1,B4,B7であり、それぞれ直線で結ばれて表示されている。そして、本処理により、ブロックB3に関して、各接続ブロックとの接続ネット数を、B1に対して24本、B4に対して128本、B7に対して36本といったように、詳細な数値を表示することができる。また、数値だけでなく接続線の色を変えて表示してもよい。ユーザの操作に応じて、当該数値のような接続情報17を、接続線の付近に表示させる。また、接続情報17の接続線の太さだけで判断できない場合に、例えばコントロールキー+aキーを繰り返し押すことで、より詳細な情報を表示/非表示させる。これらにより、ユーザは、接続関係のあるブロックのすべてを把握しながらブロック配置可能であり、ブロック位置決定の容易性を向上できる。

【0081】

<ブロック配置固定>

図11では、更に、任意のブロックの配置位置を固定することができるブロック配置固定機能の例を示す。例えばブロックB7の位置を固定(移動禁止設定)したい場合である。論理機能の特性や、周囲との接続関係等の理由から、ブロック位置が確定してしまう場合がある。このような場合、誤ってブロック位置を変更してしまわないように、本処理及びユーザ選択操作により、該当ブロックの位置を固定することができる。この方法としては、ユーザにより、搭載領域情報16(ブロック位置情報)として直接に当該ブロックの配置位置の座標を指定する方法や、GUI機能を持つ本プログラム処理上で当該位置を決定する方法などがある。また、図11のように、固定するブロックの色を変えて表示することで、移動可能なブロックとの区別を容易にする。ブロック固定の場合としては、論理設計時点で固定の場合、実装設計時点で固定の場合などがあり、いずれの場合でも本処理機能を使用できる。

【0082】

また特に、本処理機能により、配置対象リージョン以外のリージョン内に配置が必要な全ブロックを、移動禁止して固定して表示するようにする。

【0083】

また特に、本処理機能により、チップ領域上で予め配置位置が決められているブロックについて、チップ領域上の配置座標の指定に従って配置する処理を行う。また、座標指定により配置されるブロックを、移動禁止して固定して表示する。また、座標指定により配置され固定されるブロックについて、その上に他のブロックが重ならないように配置禁止を設定する処理を行う。

【0084】

<重心表示>

図12では、更に、あるブロックに対し接続関係のあるすべてのブロックの配置座標で構成される領域(最外郭矩形)におけるブロック配置の重心(配線物量を考慮した重心)の座標を表示する機能の例を示す。図12は、本処理により、例えばブロックB3に着目し、それと接続関係のあるブロックB1.B4,B7との配置座標及び接続情報から、ブロックB3を配置するにあたり最も効率の良い重心点を表示させた状態である。ブロックB3の接続範囲の最外郭矩形F(B3’)における中心から、ブロック間接続ネット数が多いブロックB4とB7側寄りに重心点G(B3’’)が表示される。ユーザは、この重心の表示を参照することで、当該ブロック付近に関しては、この重心点G(B3’’)にブロックB3の中心を配置することが最も効率の良い配置であると判断できる。これにより、ブロック配置決定が容易にできる。

【0085】

<並行設計作業>

次に、図13において、チップC領域全体における論理機能毎に分割されたリージョンR1〜R5をそれぞれブロック配置設計する場合の例を示す。リージョンR1〜R5には、それぞれ複数のブロックが含まれ、それぞれ個別に配置作業する必要がある。その際、一人のユーザ(実装設計者)がすべてを配置作業していたのでは、配置情報作成等の作業に要する期間が長くなってしまう。そこで、本処理例では、複数のリージョンR1〜R5の1つのリージョンに対して一人のユーザ(実装設計者)を割り当て、複数のユーザにより同時並行して配置情報作成等の作業を行う。これにより、チップC領域に関する全体の配置情報作成期間を短縮することができる。

【0086】

しかしながら、従来、この場合、分割された状態の配置情報では、チップC領域に対する実配置処理を実行することができない。このために、本実施の形態では、図14に示すように、それら複数の配置情報を併合する処理機能(配置情報併合機能)を設ける。例えば、各ユーザにより、リージョンごとの配置情報であるR1配置情報41〜R5配置情報45が並行的に作成される。それらを、本プログラム処理による配置情報併合機能に入力して1つに併合処理することで、チップC領域の配置情報(C配置情報)40が出力される。後は、C配置情報40に対して実配置処理(414)を実行することができる。

【0087】

図1の構成で言えば、サーバコンピュータ100に配置情報併合機能に対応したプログラムを設ける。各設計者が使用する複数のクライアントコンピュータ200でR1配置情報41〜R5配置情報45が個別に作成される。併合の際は、クライアントコンピュータ200から該当配置情報をサーバコンピュータ100へ送信し、サーバコンピュータ100の配置情報併合機能の処理によりC配置情報40へ併合する。

【0088】

これにより、分割・同時並行作業による配置情報作成期間の短縮が可能となる。併合処理を実現する方法としては様々あるが、例えば、元の配置情報と比較してブロック配置座標が変更されていれば情報を書き換えるといった処理を実行する。これにより、複数存在する配置情報ファイルから、配置移動後の情報だけを抽出して併合することが可能となる。

【0089】

例えば、ある設計者は、C配置情報40を参照することで、自分が担当するリージョンに対し隣接するリージョンにおけるブロックの配置の様子を知ることもできる。リージョン間に渡ってブロックを接続する必要がある部分についてはリージョンの端の領域に当該ブロックを配置すること等が可能である。

【0090】

また、本処理機能により、チップ領域を複数のリージョンに分割してブロックを配置する方法を用いる際、各リージョン内のブロック接続情報(ブロック接続関係)がリージョン間を渡る場合(あるブロックを隣接リージョン内のブロックと接続する場合)に、リージョン間ネットとして該当ブロックと該当リージョン間を直線で結び表示する。

【0091】

また、上記において、チップ領域上の任意の位置に配置されるブロックについては、その配置されるブロックを選定する処理が行われることで、その他のブロックと重ならない任意の位置に配置されるように処理を行う(チップ領域をリージョンに分割しても、分割されたリージョンの領域に依存せずに配置可能なブロックを選定する)。

【0092】

また、上記において、同一のリージョン内に配置するブロック同士の接続関係については、ブロック間ネットを表示し、他のリージョン内に配置したブロックとの接続情報については、リージョン間ネットを表示して、関係を視認できるように処理を行う。

【0093】

また、本処理機能では、複数のリージョンRに分割しそのリージョンR毎にブロックBを配置する方法においては、ユーザ指定により、リージョンRを構成するブロックBを、異なるリージョンRに配置することも可能とする。図15には、その例について示している。リージョンR1のブロックB8を、隣のリージョンR2の端に配置した場合である。

【0094】

以上のように、本実施の形態によれば、実配置処理の前の段階で適切なブロック配置の見積もり及び配線混雑評価を行うので、図面作成等の設計作業のやり直し・後戻り、配置見直し等を抑止でき、設計の工数、期間、コストの増加を抑制できる。また、ブロック配置作業を支援するGUI機能による各種処理機能の提供により、設計効率を向上することができる。

【0095】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0096】

本発明は、IC設計の情報処理システムに利用可能である。

【図面の簡単な説明】

【0097】

【図1】本発明の一実施の形態のブロック配置方法を適用する情報処理システムのブロック構成を示す図である。

【図2】本実施の形態の情報処理装置(サーバコンピュータ)のブロック構成を示す図である。

【図3】本実施の形態の情報処理装置(クライアントコンピュータ)のブロック構成を示す図である。

【図4】本発明の一実施の形態のブロック配置方法及びプログラムによる処理及びユーザ作業等のフローを示す図である。

【図5】本実施の形態におけるブロック構成情報の例を示す図である。

【図6】本実施の形態におけるブロック接続図の例を示す図である。

【図7】本実施の形態におけるブロック配置初期情報の例を示す図である。

【図8】本実施の形態におけるブロック配置後の表示例を示す図である。

【図9】本実施の形態における配線の要求混雑度の表示例を示す図である。

【図10】本実施の形態におけるブロック間接続ネット数の表示例を示す図である。

【図11】本実施の形態におけるブロック固定配置機能の表示例を示す図である。

【図12】本実施の形態におけるブロック配置の重心座標の表示例を示す図である。

【図13】本実施の形態における並行作業のためにチップ領域を複数のリージョンに分割した例を示す図である。

【図14】本実施の形態における並行作業で作成された複数の配置情報を併合する処理機能の構成を示す図である。

【図15】本実施の形態におけるリージョン間でブロックを配置する場合を示す図である。

【図16】従来技術のブロック配置方法による処理及びユーザ作業等のフローを示す図である。

【符号の説明】

【0098】

10…ブロック配置プログラム、11…論理ファイル、12…ゲートレベルネットリスト、13…構成情報、14…回路ゲート物量情報、15…ブロック実装率情報、16…搭載領域情報、17…接続情報、18…合成結果レポート、20…設計情報、21…ブロック配置情報(ブロック配置情報ファイル)、22…接続情報、40…チップ(C)配置情報、41〜45…リージョン(R)配置情報、100…サーバコンピュータ、110,210…制御装置、120,220…主記憶装置、130,230…補助記憶装置、140,240…ネットワーク接続部、200…クライアントコンピュータ、250…ディスプレイ、260…キーボード、270…マウス、300…コンピュータネットワーク、401…HDLツール、403…論理合成処理、414…配置配線プログラムによる処理、415…配線混雑度評価。

【技術分野】

【0001】

本発明は、半導体集積回路(IC)の設計及び配置方法、そのための情報処理装置及びコンピュータプログラムに関し、特に、論理的なブロック等(回路配置領域)の階層を含んで構成されるICにおけるブロック配置方法に関する。

【背景技術】

【0002】

従来技術のIC設計及び配置方法において、情報処理装置を用いてユーザ(設計者)によりICチップ領域に複数のブロックを配置する方法及び配置配線実装処理などに関して、以下のようである。従来、論理設計者は、ブロック間の論理機能を考慮し、ブロック配置図面を作成する。その図面をもとに、実装設計者は、ブロック配置情報を作成し、配置配線プログラムによる処理を実行する。

【0003】

図16は、従来技術のIC設計及びブロック配置方法の処理及びユーザ作業等のフローを示している。IC設計工程は、例えば、論理設計者による論理設計工程と実装設計者による実装設計工程とに分けられる。枠で囲まれた部分は、実装設計者による実装設計工程(関連する一部のみ)である。

【0004】

論理設計工程において、論理設計者は、VHDLやVerilog等のHDLツール(901)及びその処理を用いて論理ファイル(902)を作成する。論理ファイル(902)は、レジスタ転送レベル等でのデジタル回路の記述情報である。論理ファイル(902)を入力として、論理合成処理(903)及びそのツールにより、ゲートレベルネットリスト(906)や、合成結果レポート(907)等の情報データが出力される。ゲートレベルネットリスト(906)は、回路ゲートレベルにおける端子間の接続配線関係(ネット)のリスト情報である。合成結果レポート(907)は、回路ゲート物量情報などを含む。また、論理設計者は、論理ファイル(902)をもとに、ブロック間の論理機能を考慮して、ブロック配置図面(905)を作成する作業を行う。ブロック配置図面(905)は、手書き等により、ブロック配置(接続関係)がわかるように簡単に書き表した図面である。

【0005】

実装設計工程において、実装設計者は、論理設計者によって作成されたブロック配置図面(905)に基づき、ゲートレベルネットリスト(906)等を入力として、ブロック配置情報作成ツール(911)及びその処理を用いて、ブロック配置情報ファイル(913)を作成する。この際、実装設計者による配置可否判定(914)でOKであれば、ブロック配置情報ファイル(913)が得られる。

【0006】

そして、実装設計者は、ブロック配置情報ファイル(913)を用いて、配置配線プログラムによる処理(配置配線実装処理)(914)を実行する。当該処理を実配置処理などと略称する。当該処理には相応の時間を要し、大規模な回路ほど長時間となる。その処理の後、実装設計者による配線混雑度評価(915)でOKであれば、本ブロック配置及び実配置処理等の工程は終了であり、次のステップ(省略)へ進むことができる。

【0007】

また、ブロック配置方法に関し、特開2003−330986号公報(特許文献1)記載の技術では、ブロック位置を決定後、ブロック形状を決定し、配置配線プログラムによる処理(配置配線実装処理)を実行する。ここで実装設計者は、その処理結果におけるブロック内外配線混雑、及びタイミング制約違反を対策するために、ブロック形状を変更し、再度、配置配線実装処理を実行し、ブロック間配線混雑、ブロック内配線混雑、タイミング制約が解消されるまで繰り返す。

【特許文献1】特開2003−330986号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

前記従来技術のIC設計及びブロック配置方法において、以下のような問題がある。

【0009】

実装設計者がブロック配置情報ファイル(913)を作成する時、論理設計者によるブロック配置図面(905)上のブロック配置領域の大きさと、論理合成処理(903)後のブロック配置領域の大きさと、が異なることにより、同一にはブロック配置情報ファイル(913)が作成できない、という事態が発生することが多い。図16では、配置可否判定(912)でNGの場合である。この場合、解消のために、再度、論理設計者によるブロック配置図面作成(904)、ブロック配置の見直し、等が必要になる。即ち、設計作業のやり直しや後戻りが発生する。

【0010】

また、配置配線プログラムによる処理(914)の実行の結果、配線の局所的な混雑が発生する場合がある。図16では、実装設計者による配線混雑度評価(915)でNGの場合である。この場合、上記と同様に、解消のために、再度、ブロック配置図面作成(904)、ブロック配置の見直し、等が必要になる。

【0011】

上記のように、従来技術では、設計工程におけるブロック配置領域の大きさのズレや、局所的配線混雑の発生などにより、設計作業のやり直しや後戻り、ブロック配置見直し、再プログラム処理時間などが発生することによって、設計の工数、期間、及びコストの増加、並びに設計効率低下、といった問題がある。

【0012】

また、前記特許文献1の手法においても、ブロック間配線混雑、ブロック内配線混雑、タイミング制約が解消されるまで、ブロック位置及びブロック形状の見直しや、配置配線プログラムによる処理を繰り返す必要がある。よって上記同様に設計期間増加などの問題につながる。

【0013】

本発明は以上のような問題に鑑みてなされたものであり、その目的は、上記ブロック配置を含むIC設計作業において、やり直し等を削減でき、設計の工数、期間、コストを低減でき、設計効率を向上させることができる技術を提供することである。また特に、上記ブロック配置等の設計作業の効率を向上させることができるユーザインタフェースを提供することである。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。前記目的を達成するために、本発明は、ブロック等の階層を含んで構成されるICのチップ領域におけるブロック配置方法を含むIC設計及び配置方法、その処理作業を行うための情報処理装置、及びコンピュータプログラムに係わり、以下に示す構成を有することを特徴とする。

【0015】

本方法では、実装設計者が、配置配線プログラム処理(実配置処理)を実行する前の段階で、論理的(仮想的)にブロック配置(ブロック配置領域の大きさを含むブロック構成情報)の見積もり及び配線混雑の発生の予測・判定(配線物量及び配線要求混雑度の見積もり及び評価を含む)を行う。そして本方法では、その結果に基づきユーザの操作に従ってブロックの最適な配置を決定する処理(ブロック配置情報作成処理)を行う。本処理は前述した2つの問題に対処するための処理を含んでいる。

【0016】

具体的に、本方法では、論理合成処理結果の情報データ(ネットリスト等を含む)等に基づき、ブロック配置情報の作成段階で、配置対象ブロックに関して、(a)ブロック配置領域の大きさと、(b)配線物量と、を見積もる処理を行う。そして本方法では、それら(a),(b)の見積もりに基づき、(c)配線要求混雑度を見積もり及び評価する。このような情報を、GUI機能により、画面に設計情報と共に表示する。ユーザは、このような情報の参照、確認により、ブロック配置領域の大きさや、局所的配線混雑が発生しないかどうか等を予測しながら、実現性の高いブロック配置を決定することができる。

【0017】

本方法及び対応プログラムでは、以下のような処理工程及び処理機能を有する。

【0018】

(1)前記論理合成処理結果の情報データ(A)をもとに、ブロックの回路ゲート物量情報(B)と、ブロック間の接続情報(C)とを抽出する処理を行い、これにより、配置対象の複数のブロックにおけるブロック相互の関係(ブロック間接続関係)(D)を、GUIにより画面に表示する処理機能を有する。ブロック間接続情報(C)は、ネットリスト等をもとに、ブロック同士の接続関係を表した情報データである。例えば、上記複数ブロック間接続関係(D)の表示では、接続ブロック間を線で結んで表示し、ユーザ操作によりブロックが移動されると共に、接続関係を維持しながら表示内容を更新する。

【0019】

(2)前記回路ゲート物量情報(B)と、ブロック実装率情報(E)とに基づき、ブロック配置領域面積(F)(前記ブロック配置領域の大きさ)を見積もる処理を行う。そして、そのブロック配置領域面積(F)を維持しつつ、アスペクト比(縦横長さ比率)をユーザにより自由に変更可能として画面に表示する処理機能を有する。

【0020】

(3)また、前記ブロック間接続情報(C)を客観的に把握するために、ユーザ操作に応じて、画面に、ブロック間の接続ネット数(G)(ネットリスト等による)などに応じてブロック間の接続線の太さや色などを変えて表示する処理機能を有する。また、ユーザ操作に応じて、画面に、前記ブロック間の接続ネット数(G)を表示する処理機能を有する。また、ユーザ操作に応じてそれらの情報の表示/非表示を自由に切り替える処理機能を有する。

【0021】

(4)例えば予め配置位置が決められたブロック等について、ユーザ操作に応じて、画面で、座標などを指定して当該ブロックを配置することができ、且つその配置位置から誤って移動できないように固定することができ、また、当該固定されたブロックの色などを変えて表示することで他のブロックとの区別を容易にする処理機能を有する。

【0022】

(5)ユーザによりブロックの配置位置を一旦決めた時点で、ある一定領域内で配線可能な領域(配線使用可能率及び領域)に対して、どれだけの配線領域を必要としているかを予測した値(配線要求混雑度(H))を評価し、これに応じて、画面で、配線混雑箇所を強調して表示する処理機能を有する。特に、前記配線要求混雑度(H)の予測及び評価の処理については、領域の配線層ごとに、電源配線等の固定配線分を考慮して配線使用可能率を設定し、それに応じた配線混雑度評価を行う。また特に、配線混雑箇所の表示については、チップ領域等をメッシュ状など単位領域に分割し、その領域ごとの混雑度に応じて、色などを変えて表示する。

【0023】

(6)ある配置対象ブロックに対する接続関係のある全ブロックにおける配置座標で構成される領域の重心点の座標(I)(配線物量を考慮した重心)を表示する処理機能を有する。

【0024】

(7)チップ全面の配置可能領域を、前記ブロックとは別にリージョン等の階層によって分割し、その分割された領域(リージョン)ごとに、個別に、上記のようなブロック配置等の処理作業を並行して行うことができる処理機能を有する。また、その同時並行作業のために分割された領域(リージョン)ごとに個別に作成されたブロック配置情報を、チップ領域への実配置処理等のために1つの配置情報に併合する処理機能を有する。

【0025】

本IC配置方法は、例えば、複数のブロックを含んで構成される半導体集積回路のチップ領域におけるブロックの配置において、設計者の操作に応じてGUIで画面に設計情報を表示し、論理合成処理結果情報の入力に基づき、設計者によるブロックの配置を含む処理を行って、配置配線実装処理のための情報を出力する処理をコンピュータで実行するものであり、論理合成処理結果情報をもとに、ブロック間の接続情報、及びブロック内の回路ゲート物量情報を抽出する第1の処理工程、ブロック内の回路ゲート物量情報とブロック実装率情報とから、配置対象ブロック毎に、必要なブロック配置領域面積を含むブロック構成情報を見積もり、ブロック構成情報を含むブロック配置初期情報を作成する第2の処理工程、ブロック配置初期情報をもとに、設計者の操作に応じて、ブロック相互の関係を画面に表示し、チップ領域へのブロックの配置を決定しブロック配置情報を作成する第3の処理工程、ブロック配置情報における配置されたブロックについて、ブロック間の接続情報に基づくブロック間配線長の見積もり及びブロック内配線長の見積もりから、チップ領域内における配線領域の必要量を見積もり、これにより配線要求混雑度を評価し、この配線要求混雑度の状態を画面に表示する第4の処理工程、及び、ブロック配置情報を出力する第5の処理工程を有する。

【発明の効果】

【0026】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。本発明によれば、上記ブロック配置を含むIC設計作業において、やり直し等を削減でき、設計の工数、期間、コストを低減でき、設計効率を向上させることができる。また特に、上記ブロック配置等の設計作業の効率を向上させることができるユーザインタフェースを提供できる。

【発明を実施するための最良の形態】

【0027】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一部には原則として同一符号を付し、その繰り返しの説明は省略する。

【0028】

<システム>

図1において、本実施の形態のIC設計及びブロック配置方法及びプログラムを適用する情報処理システムの構成例を示している。本システムは、コンピュータネットワーク300上で接続される情報処理装置である、1つ以上のサーバコンピュータ100と、1つ以上のクライアントコンピュータ200と、を有して構成される、クライアントサーバシステムの形である。サーバコンピュータ100は、クライアントコンピュータ200からアクセスされ、プログラムや情報データなどを管理する。ユーザ(設計者)は、クライアントコンピュータ200を使用、操作して、サーバコンピュータ100の処理機能及び情報データをアクセスして利用する。本方法では、グラフィカルユーザインタフェース(GUI)機能を含む処理機能を実現するプログラムにより、クライアントコンピュータ200のディスプレイ画面に、設計に係わる情報(設計情報)を表示する。ユーザは、その画面を見て設計情報を編集することでIC設計作業を行う。

【0029】

なお、1台の情報処理装置にサーバコンピュータ100及びクライアントコンピュータ200の相当機能を備えて一人のユーザにより作業する形態なども勿論可能である。

【0030】

図2のように、サーバコンピュータ100は、制御装置110、主記憶装置120、補助記憶装置130、ネットワーク接続部140等を有する構成である。

【0031】

図3のように、クライアントコンピュータ200は、制御装置210、主記憶装置220、補助記憶装置230、ネットワーク接続部240、ディスプレイ250等の出力装置(他にプリンタ等)、キーボード260及びマウス270等の入力装置、等を有する構成である。

【0032】

本ブロック配置方法に対応するプログラム(ブロック配置プログラム10等)は、例えば、サーバコンピュータ100の補助記憶装置130に記憶されている。また、例えば、補助記憶装置130には、本プログラムによる処理機能に関わる各種の情報データも記憶され管理される。本プログラムは、例えば、一般的なIC設計ソフトウェアに対する追加的なプログラムとして実現可能である。

【0033】

本例では、補助記憶装置130(例えばHDD)には、ブロック配置プログラム10、論理ファイル11、ゲートレベルネットリスト12、ブロック構成情報13、回路ゲート物量情報14、ブロック実装率情報15、搭載領域情報16、接続情報17等が記憶される。

【0034】

また、クライアントコンピュータ200の補助記憶装置230(例えばHDD)等には、IC設計作業に応じて、設計情報20、ブロック配置情報21、ブロック間接続情報22などが格納される。設計情報20は、作業データであり、サーバコンピュータ100から読み出した情報、及びサーバコンピュータ100へ書き込む情報などを含む。

【0035】

サーバコンピュータ100側では、補助記憶装置130上のプログラム(ブロック配置プログラム10)は、主記憶装置120にロードされて制御装置110により実行される。また、クライアントコンピュータ200側では、制御装置210により、コンピュータネットワーク300を介して、サーバコンピュータ100側の処理機能(プログラム)及び情報データにアクセス及びデータ入出力する。それにより、クライアントコンピュータ200側で必要なプログラム及び情報データが、主記憶装置220にロードされて制御装置210により実行される。これらにより、ブロック配置処理を含むIC設計処理が実現される。

【0036】

本システムの利用において、ユーザは、クライアントコンピュータ200のキーボード260やマウス270等の操作によりコマンドを入力、選択することで、例えば、サーバコンピュータ100側の情報データを読み出す指示を実行する。指示はネットワーク接続部240及びコンピュータネットワーク300を介してサーバコンピュータ100へ送信される。これに応じて、サーバコンピュータ100側のプログラム(ブロック配置プログラム10)が実行され、指示に応じた結果の情報が、ネットワーク接続部140及びコンピュータネットワーク300を介してクライアントコンピュータ200側へ送信される。そして、ディスプレイ250等で結果が確認できる。

【0037】

<情報データ>

論理ファイル11は、ユーザによりHDLツール等で作成される。ゲートレベルネットリスト12及び回路ゲート物量情報14等は、論理合成処理結果として得られる。構成情報13は、チップ、ブロック等の階層を含む、基本的な構成を表す情報である。ブロック実装率情報15は、仕様などに応じて決まり、例えばユーザにより入力設定される。搭載領域情報16は、ブロックを搭載する領域の座標などの情報である。接続情報17は、ブロック内やブロック間の接続関係を表す情報である。ブロック配置情報21は、クライアント側で作成されたデータであり、ブロック(ブロック配置領域)の面積、配置位置座標、縦横長さなどの情報(ブロック構成情報)を持ち、ブロック間接続情報22などと関連付けられる。ブロック間接続情報22は、クライアント側の処理で抽出された、ブロック間の接続関係を表す情報であり、サーバ側の接続情報17と関連付けられる。クライアント側のデータは、サーバ側へのデータへ統合される。

【0038】

本処理機能(ユーザ設定機能)では、画面でのGUI表示などによって、ブロック実装率情報15などの他、設計に係わる各種の値をユーザ操作により指定(設定)が可能である。

【0039】

<ブロック配置方法>

本ブロック配置方法では、論理合成処理結果の情報データ等に基づき、ブロック配置情報21の作成段階で、配置対象ブロックに関して、(a)ブロック配置領域の大きさと、(b)配線物量と、を見積もる処理を行う。(a)ブロック配置領域の大きさは、配置対象ブロックの回路ゲート物量情報14などから見積もる。(b)配線物量は、配置対象ブロックに関連(接続関係)のあるブロックとの配線物量(接続配線物量)、及び配置対象ブロックの周辺ブロックを含めた配線物量(周辺配線物量)を見積もる。

【0040】

そして本方法では、それら(a),(b)の見積もりに基づき、(c)配線要求混雑度を見積もり及び評価する。このような情報を、GUI機能により、画面に設計情報20と共に表示する。ユーザは、このような情報の参照、確認により、ブロック配置領域の大きさや、局所的配線混雑が発生しないかどうか等を予測しながら、実現性の高いブロック配置(位置やサイズ等)を決定することができる。即ち、上記決定によるブロック配置情報の作成の後、それに対する配置配線プログラム処理(実配置処理)を実行すると、上記のように適切な見積もり等が実行済みであることによって、前述のやり直し等が発生しない可能性が高い。

【0041】

<フロー(概要)>

次に、図4において、本ブロック配置方法の処理、ユーザ作業等の工程、入出力情報等のフローを示している(Sは処理ステップを示す)。本IC設計工程は、論理設計者による論理設計工程と実装設計者による実装設計工程とに分けられる。枠で囲まれた部分は、実装設計者による実装設計工程(関連する一部のみ)である。そのうち更に、Aで示す部分は、図16のような従来技術とは異なる、本方法で特徴的な技術の部分を示す。まず以下に概略工程を示す。

【0042】

論理設計工程において、論理設計者は、VHDLやVerilog等のHDLツール(401)を用いて論理ファイル11を作成する。論理ファイル11を入力として、論理合成処理(論理合成ツール)(403)により、ゲートレベルネットリスト12や、合成結果レポート18等の情報データが出力される。

【0043】

実装設計工程において、実装設計者は、論理合成処理結果の情報データに基づき、ゲートレベルネットリスト12、合成結果レポート18等を入力として、ブロック配置を含む処理作業を行う。

【0044】

S1(接続情報抽出処理)では、ゲートレベルネットリスト12をもとに、ブロック内の回路ゲート同士(ブロック内)及びブロック同士(ブロック間)の接続関係を含む接続情報17(ブロック内接続情報及びブロック間接続情報)を抽出する。

【0045】

S2(回路ゲート物量情報抽出処理)では、合成結果レポート18をもとに、ブロック内の論理を構成する回路ゲートの物量情報(回路ゲート物量情報14)を抽出する。回路ゲート物量情報14をもとにブロック配置領域面積の大きさが見積もられる。

【0046】

S3(ブロック配置初期情報作成処理)では、S1で求めたブロック間接続情報(接続情報17)と、S2で求めたブロックの回路ゲート物量情報14と、ブロック実装率情報15(例えばユーザにより設定される)とから、ブロック配置初期情報(初期状態のブロック配置情報21)を作成する。ブロック配置初期情報は、ブロック配置領域面積(ブロック配置領域の大きさ)などの見積もりを含んでいる。

【0047】

ここで、ブロック実装率情報15とは、ブロック内の回路ゲートを敷き詰めて配置するための領域を1としたとき、回路ゲート同士を接続するための接続線を配線するために必要な領域、を加えたときの割合である。

【0048】

S4(ブロック配置情報作成処理)では、S1で抽出したブロック間接続情報(接続情報17)をもとに、実装設計者が、ブロック位置を決定する。処理としては、実装設計者の操作による編集作業に応じて、画面に情報を表示する。これにより、ブロック配置状態を表すブロック配置情報21が作成される。

【0049】

S5(配線要求混雑度評価処理)では、S4で決定したブロックの配置をもとに、配線の要求混雑度を評価する。ここで、配線の要求混雑度とは、配線物量(ブロック間配線物量及びブロック内配線物量)と、チップを構成する半導体の特性で定められている配線可能な物量と、の比率である。配線物量(ブロック間配線物量及びブロック内配線物量)は、ブロック間の接続数及びその距離から求めたブロック間配線長と、ブロック内の回路ゲートの配線を考慮したブロック内配線長と、から求められる。配線可能な物量は、複数存在する配線層の和で求められ、一般の論理に使用可能な物量は配線層ごとに異なる。

【0050】

S6(配線妥当性判定)では、実装設計者が、S5の評価結果をもとに、実現性のある(実現性の高い)ブロック配置であるかどうかの妥当性を判定する。NGと判定されればS4へ戻り、再度ブロック配置が検討される。OKと判定されれば、S7へ進む。

【0051】

S7(ブロック配置情報出力処理)では、ブロック配置情報ファイル21を出力する。出力されたブロック配置情報ファイル21は、従来技術に比べて実現性の高いブロック配置情報となっている。これにより、Aの部分の工程は終了し、その後は、例えば従来技術と同様の実配置処理などに続く。

【0052】

即ち、実装設計者は、ブロック配置情報ファイル21を用いて、配置配線プログラムによる処理(414)を実行する。その処理の後、実装設計者による配線混雑度評価(415)でOKであれば、ブロック配置及び実配置処理は終了であり、次のステップ(省略)へ進むことができる。

【0053】

<フロー(詳細)>

次に、以下、フロー詳細及び関連する画面表示例などを順に示す。

【0054】

前記S1,S2では、ユーザ(実装設計者)は、クライアントコンピュータ200の操作によりコマンドを入力することで、サーバコンピュータ100側にある、ブロックの回路ゲート物量情報14と、ブロック内及びブロック間の接続情報17と、を含む情報を抽出する指示を実行する。これに応じて、サーバコンピュータ100側のプログラム(ブロック配置プログラム10)が実行され、上記回路ゲート物量情報14と接続情報17とを含む結果の情報が、クライアントコンピュータ200のディスプレイ250等で確認できる。

【0055】

<構成情報>

図5は、設計対象のチップCの領域に搭載(配置)するブロック等に関する構成情報(構成情報13)の一部例を示す。チップC,リージョンR,ブロックBという階層構成の場合である。なお「ブロック」等の階層の名称は便宜的なものである。本例では、チップCの領域は、リージョンR1〜R5に分けられ(例えば図13)、更に、例えばリージョンR1の領域には、ブロックB1〜B8が搭載(配置)される。リージョンRは、チップCに含まれる論理(領域)の一部である。チップC領域内の複数のリージョンR、リージョンR内の複数のブロックB、といったように、2階層以上を持つ構成のICの設計を対象としている。

【0056】

また、本処理機能では、ブロック配置については、チップC領域に直接に全ブロックBを一括で配置する方法(リージョンR無し)と、チップC領域の全体の配置可能な領域を複数のリージョンRに分割し、そのリージョンR毎にブロックBを配置する方法と、の2つをユーザにより選択指定可能とする。

【0057】

<ブロック接続情報>

図6は、チップC(リージョンR1)に搭載(配置)するブロック(B1〜B8)に関するブロック接続図の一部例を示す。このブロック接続図は、ブロック同士の接続関係、論理の構成を視覚的にわかりやすいように図示したものである。S1の処理によって求められたブロック間接続情報(接続情報17)から、図6のようなブロック接続図を、必要に応じて作成して用いることができる(必須ではない)。

【0058】

図6のブロック接続図では、ブロック(B1〜B8)の接続関係は以下の通りである。なお矢印は信号配線入出力関係である。B1は、B3,B4と接続される(B1の出力は、B3,B4へ入力される)。B2は、B4,B5,B6と接続される。B3は、B4と相互接続される。B4は、B5と相互接続される。B3,B4,B5は、B7と接続される。B6は、B8と接続される。

【0059】

一方、ブロック間接続情報(接続情報17)は、上記のようなブロック接続図で示される内容を情報データとして構成したものである。例えば、データベースのレコードにおいて、B1の情報に対してB3,B4の情報が関連付けされる。

【0060】

実装設計者は、S1で求められた接続情報17(またはそれをもとに作成したブロック接続図)を参照することにより、ブロック間接続関係を知ることができる。そのため、従来技術のような論理設計者によるブロック配置図面作成(904)の作業を省略することができる。

【0061】

<ブロック配置初期情報>

図7は、前記S3で求めたブロック配置初期情報の例である。リージョンR1に含まれるブロックB1〜B8の大きさを抽出して配置した例を示している。本例は、チップCの右上にリージョンR1の領域がある場合である。各ブロックB1〜B8の配置領域の大きさ(面積)が抽出されている。初期段階(ユーザによる配置前)では、まだ、ブロックが配置情報(ブロック構成情報)を持たないため、適当な箇所に配置表示処理する。例えば、すべてのブロックを、領域の左下、中央など、一箇所にまとめられて配置表示されるようにする。また、ブロックが縦横長さ情報なども持たないため、例えば正方形で表示されるようにする。

【0062】

また例えば、チップ領域に直接にブロックを配置する場合、全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、チップ領域の外側に配置しておくようにしてもよい。また例えば、リージョン毎にブロックを配置する場合、全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、該当リージョンの内側に配置しておくようにしてもよい。

【0063】

また、チップ領域を分割したリージョン領域の名称を論理ファイル名称と同一とすることにより、例えば、リージョンR1の領域内にはブロックB1,ブロックB2,……,ブロックB8を配置する、というような指定をしなくても、ブロックB1〜B8はリージョンR1の領域内に配置するものと判断可能とする。

【0064】

図7はチップC領域の内側かつ該当リージョンR1の外側にブロックを配置した場合である。

【0065】

<ブロック配置情報>

前記S4では、接続情報17及びブロック配置初期情報をもとに、実装設計者が、ブロック配置位置を決定する。例えば、実装設計者は、マウス270操作により各ブロックをドラッグして好きな位置に移動する。これにより、例えば図8のようなブロック配置状態とする。この状態は、ブロック配置情報21に反映される。

【0066】

図8では、図7で示したチップCのリージョンR1に含まれるブロックB1〜B8におけるブロック配置初期情報をもとに、実装設計者が、ブロック間接続情報(接続情報17)を考慮して、リージョンR1内にブロックB1〜B8を配置した例を示す。ブロックB1〜B8の接続関係は前記図6の通りである。また例えば、リージョンやブロック等の名称を、適当な箇所、例えば矩形の内側または外側の一箇所に表示する。

【0067】

この時、図8のように、本プログラム処理により、接続関係のあるブロック同士を直線(接続線)で結ぶことによって、接続情報17(ブロック接続関係)をイメージとして画面に表示する。例えばブロック中心点同士が結ばれる。また、この接続情報17による接続線について、ブロック間の接続ネット数(ゲートレベルネットリスト12等からわかる)に応じて、太さを変えて表示する。これにより、ユーザは、ブロックの接続に関する論理的な結合度を知ることができ、対象とするブロック同士を近くに配置すべきか遠くに配置してもよいか等の判定が容易にできる。ユーザによりブロックが移動されても、接続線の表示が維持される。

【0068】

また、本処理機能では、ユーザが操作によりブロック配置位置を決定する際、図7のような初期のブロック矩形の状態のまま配置できるだけでなく、簡単な操作に応じて、当該ブロック矩形(ブロック配置領域)の面積を一定のまま、もしくは下回らない範囲で、アスペクト比(縦横長さ比率)を変化させることができる。例えばコントロールキー+wキーで横長に、コントロールキー+hキーで縦長に変更できる。これにより、ユーザは、ブロック同士の重なりを回避、解消して配置すること等ができる。

【0069】

また、本処理機能では、ブロック間の接続線などの表示については、表示/非表示をユーザにより適宜選択できる。また例えば、ユーザにより指定される配置対象ブロックについてのみ、それと接続関係のブロック間で表示するように指定することができる。あるいは、例えば、指定がなければ、すべてのブロックについて自動的に表示するようにすることができる。

【0070】

<配線要求混雑度>

前記S5では、S4で決定されたブロックの配置(ブロック配置情報21)から、配線の要求混雑度を評価する。本プログラム処理により、実配置処理(414)の前の段階(ブロック配置情報作成段階)で、配線要求混雑度の評価を行う。

【0071】

図9には、本プログラム処理により、混雑度(配線要求混雑度)を評価してその結果を画面に表示させた例を示す。配線要求混雑度は、ある一定領域内で配線可能な領域(配線使用可能率及び領域)に対して、どれだけの配線領域を必要としているかを予測・評価した値である。配線要求混雑度は、配置対象領域における配線使用可能率を考慮した値を設定して求めることができる。配線使用可能率は、配線層毎に設定された電源配線等の固定配線で使用不可能な比率を差し引いたものである。

【0072】

上記結果の表示方法には様々あるが、例えば、図9のように、チップC(リージョンR)領域全体を一定間隔で区切ったメッシュ状(格子状)の範囲(最小分割領域)を設け、この分割領域内を混雑度に応じて着色して表示する方法などを用いる。混雑度が高い領域を目立つように表示する。例えば、混雑度が、0〜30%では無色、30〜50%では緑色、50〜70%では黄色、70〜100%では桃色、100%以上では赤色、といったようにグラデーション表示する。これにより、ユーザは、領域におけるどの箇所が配線で混雑するか等を容易に判定することができる(S6の妥当性判定)。例えば混雑度が100%以上の箇所は事実上配線不可能と判定されるため、ブロック配置を変更する必要があることがわかる。

【0073】

また、上記メッシュ状の分割領域については、ユーザにより、X(横),Y(縦)方向で分割数や単位長などを指定することによって均等分割した単位とすることができる。

【0074】

また、分割領域ごとの配線要求混雑度については、例えば以下のように求める。分割領域の使用可能なチャネル(配線チャネル)の総数に対して、その領域内にあるブロック内配線及びその領域を通過するブロック間配線が使用する配線チャネルの使用予測数によって求める。

【0075】

また特に、ブロック内のチャネルの混雑度については、配置されたブロック内の回路ゲートで使用するピン(端子)の総数から、接続するブロック内のネットの総配線長を求め、求めた配線を引くために必要なブロック内のチャネル数を求める。

【0076】

また特に、ブロック内のチャネルの混雑度については、配置されたブロックの領域が、複数の分割領域にかかる場合、上記求めたブロック内の使用チャネル数を、複数の分割領域上の占有領域に応じて分割して配分してブロック内の使用チャネル数を求める。

【0077】

また特に、ブロック内のチャネルの混雑度については、配置された各ブロックから、接続関係のあるすべてのブロックを対象にして、その中からまず、接続関係のある2つのブロックにおいて、その2つのブロックを含む最外郭矩形内に入る分割領域の個数を、それぞれX,Y方向について2ブロック矩形内分割領域数として求め、次に、上記2ブロック間で、接続するネット本数を、上記求めたX,Y方向の分割領域数で割って、この2ブロックを含む最外郭矩形内に入る各分割領域のX,Y方向を通過する配線チャネル使用数を求め、同様に、他の接続の組み合わせとなる2ブロック間についても、それぞれ分割領域のX,Y方向を通過する配線チャネル使用数を求める。その後、チップ領域上で同一位置の分割領域についてそのX,Y方向を通過する配線チャネル使用数の総和を求める。これにより、分割領域毎のブロック間配線に必要なX,Y方向の配線チャネル数を表示する。

【0078】

また特に、本処理機能では、チップ領域の配線層毎に、それぞれの配線層で予め使用領域が決定されている電源配線を含む固定配線を除いた配線チャネル数を、その層の使用可能なチャネル総数として、ユーザにより指定可能とする。

【0079】

また特に、本処理機能では、配線要求混雑度の表示については、上記に基づき、ブロック内配線のみの混雑度、ブロック間配線のみの混雑度、ブロック内及びブロック間を合わせた混雑度などについての表示をユーザにより指定可能とする。

【0080】

<ブロック間接続ネット数>

図10では、前述した図8のようなブロック配置及び接続関係の表示において、更に、ブロック間接続ネット数を表示する例を示す。ブロック間接続ネット数は、ゲートレベルネットリスト12等からわかる。例えば、ブロックB3と関係があるのは、B1,B4,B7であり、それぞれ直線で結ばれて表示されている。そして、本処理により、ブロックB3に関して、各接続ブロックとの接続ネット数を、B1に対して24本、B4に対して128本、B7に対して36本といったように、詳細な数値を表示することができる。また、数値だけでなく接続線の色を変えて表示してもよい。ユーザの操作に応じて、当該数値のような接続情報17を、接続線の付近に表示させる。また、接続情報17の接続線の太さだけで判断できない場合に、例えばコントロールキー+aキーを繰り返し押すことで、より詳細な情報を表示/非表示させる。これらにより、ユーザは、接続関係のあるブロックのすべてを把握しながらブロック配置可能であり、ブロック位置決定の容易性を向上できる。

【0081】

<ブロック配置固定>

図11では、更に、任意のブロックの配置位置を固定することができるブロック配置固定機能の例を示す。例えばブロックB7の位置を固定(移動禁止設定)したい場合である。論理機能の特性や、周囲との接続関係等の理由から、ブロック位置が確定してしまう場合がある。このような場合、誤ってブロック位置を変更してしまわないように、本処理及びユーザ選択操作により、該当ブロックの位置を固定することができる。この方法としては、ユーザにより、搭載領域情報16(ブロック位置情報)として直接に当該ブロックの配置位置の座標を指定する方法や、GUI機能を持つ本プログラム処理上で当該位置を決定する方法などがある。また、図11のように、固定するブロックの色を変えて表示することで、移動可能なブロックとの区別を容易にする。ブロック固定の場合としては、論理設計時点で固定の場合、実装設計時点で固定の場合などがあり、いずれの場合でも本処理機能を使用できる。

【0082】

また特に、本処理機能により、配置対象リージョン以外のリージョン内に配置が必要な全ブロックを、移動禁止して固定して表示するようにする。

【0083】

また特に、本処理機能により、チップ領域上で予め配置位置が決められているブロックについて、チップ領域上の配置座標の指定に従って配置する処理を行う。また、座標指定により配置されるブロックを、移動禁止して固定して表示する。また、座標指定により配置され固定されるブロックについて、その上に他のブロックが重ならないように配置禁止を設定する処理を行う。

【0084】

<重心表示>

図12では、更に、あるブロックに対し接続関係のあるすべてのブロックの配置座標で構成される領域(最外郭矩形)におけるブロック配置の重心(配線物量を考慮した重心)の座標を表示する機能の例を示す。図12は、本処理により、例えばブロックB3に着目し、それと接続関係のあるブロックB1.B4,B7との配置座標及び接続情報から、ブロックB3を配置するにあたり最も効率の良い重心点を表示させた状態である。ブロックB3の接続範囲の最外郭矩形F(B3’)における中心から、ブロック間接続ネット数が多いブロックB4とB7側寄りに重心点G(B3’’)が表示される。ユーザは、この重心の表示を参照することで、当該ブロック付近に関しては、この重心点G(B3’’)にブロックB3の中心を配置することが最も効率の良い配置であると判断できる。これにより、ブロック配置決定が容易にできる。

【0085】

<並行設計作業>

次に、図13において、チップC領域全体における論理機能毎に分割されたリージョンR1〜R5をそれぞれブロック配置設計する場合の例を示す。リージョンR1〜R5には、それぞれ複数のブロックが含まれ、それぞれ個別に配置作業する必要がある。その際、一人のユーザ(実装設計者)がすべてを配置作業していたのでは、配置情報作成等の作業に要する期間が長くなってしまう。そこで、本処理例では、複数のリージョンR1〜R5の1つのリージョンに対して一人のユーザ(実装設計者)を割り当て、複数のユーザにより同時並行して配置情報作成等の作業を行う。これにより、チップC領域に関する全体の配置情報作成期間を短縮することができる。

【0086】

しかしながら、従来、この場合、分割された状態の配置情報では、チップC領域に対する実配置処理を実行することができない。このために、本実施の形態では、図14に示すように、それら複数の配置情報を併合する処理機能(配置情報併合機能)を設ける。例えば、各ユーザにより、リージョンごとの配置情報であるR1配置情報41〜R5配置情報45が並行的に作成される。それらを、本プログラム処理による配置情報併合機能に入力して1つに併合処理することで、チップC領域の配置情報(C配置情報)40が出力される。後は、C配置情報40に対して実配置処理(414)を実行することができる。

【0087】

図1の構成で言えば、サーバコンピュータ100に配置情報併合機能に対応したプログラムを設ける。各設計者が使用する複数のクライアントコンピュータ200でR1配置情報41〜R5配置情報45が個別に作成される。併合の際は、クライアントコンピュータ200から該当配置情報をサーバコンピュータ100へ送信し、サーバコンピュータ100の配置情報併合機能の処理によりC配置情報40へ併合する。

【0088】

これにより、分割・同時並行作業による配置情報作成期間の短縮が可能となる。併合処理を実現する方法としては様々あるが、例えば、元の配置情報と比較してブロック配置座標が変更されていれば情報を書き換えるといった処理を実行する。これにより、複数存在する配置情報ファイルから、配置移動後の情報だけを抽出して併合することが可能となる。

【0089】

例えば、ある設計者は、C配置情報40を参照することで、自分が担当するリージョンに対し隣接するリージョンにおけるブロックの配置の様子を知ることもできる。リージョン間に渡ってブロックを接続する必要がある部分についてはリージョンの端の領域に当該ブロックを配置すること等が可能である。

【0090】

また、本処理機能により、チップ領域を複数のリージョンに分割してブロックを配置する方法を用いる際、各リージョン内のブロック接続情報(ブロック接続関係)がリージョン間を渡る場合(あるブロックを隣接リージョン内のブロックと接続する場合)に、リージョン間ネットとして該当ブロックと該当リージョン間を直線で結び表示する。

【0091】

また、上記において、チップ領域上の任意の位置に配置されるブロックについては、その配置されるブロックを選定する処理が行われることで、その他のブロックと重ならない任意の位置に配置されるように処理を行う(チップ領域をリージョンに分割しても、分割されたリージョンの領域に依存せずに配置可能なブロックを選定する)。

【0092】

また、上記において、同一のリージョン内に配置するブロック同士の接続関係については、ブロック間ネットを表示し、他のリージョン内に配置したブロックとの接続情報については、リージョン間ネットを表示して、関係を視認できるように処理を行う。

【0093】

また、本処理機能では、複数のリージョンRに分割しそのリージョンR毎にブロックBを配置する方法においては、ユーザ指定により、リージョンRを構成するブロックBを、異なるリージョンRに配置することも可能とする。図15には、その例について示している。リージョンR1のブロックB8を、隣のリージョンR2の端に配置した場合である。

【0094】

以上のように、本実施の形態によれば、実配置処理の前の段階で適切なブロック配置の見積もり及び配線混雑評価を行うので、図面作成等の設計作業のやり直し・後戻り、配置見直し等を抑止でき、設計の工数、期間、コストの増加を抑制できる。また、ブロック配置作業を支援するGUI機能による各種処理機能の提供により、設計効率を向上することができる。

【0095】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0096】

本発明は、IC設計の情報処理システムに利用可能である。

【図面の簡単な説明】

【0097】

【図1】本発明の一実施の形態のブロック配置方法を適用する情報処理システムのブロック構成を示す図である。

【図2】本実施の形態の情報処理装置(サーバコンピュータ)のブロック構成を示す図である。

【図3】本実施の形態の情報処理装置(クライアントコンピュータ)のブロック構成を示す図である。

【図4】本発明の一実施の形態のブロック配置方法及びプログラムによる処理及びユーザ作業等のフローを示す図である。

【図5】本実施の形態におけるブロック構成情報の例を示す図である。

【図6】本実施の形態におけるブロック接続図の例を示す図である。

【図7】本実施の形態におけるブロック配置初期情報の例を示す図である。

【図8】本実施の形態におけるブロック配置後の表示例を示す図である。

【図9】本実施の形態における配線の要求混雑度の表示例を示す図である。

【図10】本実施の形態におけるブロック間接続ネット数の表示例を示す図である。

【図11】本実施の形態におけるブロック固定配置機能の表示例を示す図である。

【図12】本実施の形態におけるブロック配置の重心座標の表示例を示す図である。

【図13】本実施の形態における並行作業のためにチップ領域を複数のリージョンに分割した例を示す図である。

【図14】本実施の形態における並行作業で作成された複数の配置情報を併合する処理機能の構成を示す図である。

【図15】本実施の形態におけるリージョン間でブロックを配置する場合を示す図である。

【図16】従来技術のブロック配置方法による処理及びユーザ作業等のフローを示す図である。

【符号の説明】

【0098】

10…ブロック配置プログラム、11…論理ファイル、12…ゲートレベルネットリスト、13…構成情報、14…回路ゲート物量情報、15…ブロック実装率情報、16…搭載領域情報、17…接続情報、18…合成結果レポート、20…設計情報、21…ブロック配置情報(ブロック配置情報ファイル)、22…接続情報、40…チップ(C)配置情報、41〜45…リージョン(R)配置情報、100…サーバコンピュータ、110,210…制御装置、120,220…主記憶装置、130,230…補助記憶装置、140,240…ネットワーク接続部、200…クライアントコンピュータ、250…ディスプレイ、260…キーボード、270…マウス、300…コンピュータネットワーク、401…HDLツール、403…論理合成処理、414…配置配線プログラムによる処理、415…配線混雑度評価。

【特許請求の範囲】

【請求項1】

半導体集積回路配置プログラムであって、

複数のブロックを含んで構成される半導体集積回路のチップ領域における前記ブロックの配置において、設計者の操作に応じてグラフィカルユーザインタフェースで画面に設計情報を表示し、論理合成処理結果情報の入力に基づき、設計者による前記ブロックの配置を含む処理を行って、配置配線実装処理のための情報を出力する処理をコンピュータに実行させるものであり、

前記論理合成処理結果情報をもとに、ブロック間の接続情報、及びブロック内の回路ゲート物量情報を抽出する第1の処理、

前記ブロック内の回路ゲート物量情報と、ブロック実装率情報とから、配置対象ブロック毎に、必要なブロック配置領域面積とブロック内の配線長とを含む構成を見積もり、当該構成を含むブロック配置初期情報を作成する第2の処理、

前記ブロック配置初期情報と前記ブロック間の接続情報とをもとに、設計者の操作に応じて、前記ブロックの相互の関係を画面に表示し、前記チップ領域への前記ブロックの配置を決定しブロック配置情報を作成する第3の処理、

前記ブロック配置情報における前記配置されたブロックについて、前記ブロック間の接続情報に基づく前記ブロック間の配線長の見積もりと前記ブロック内の配線長の見積もりとから、前記チップ領域内における配線領域の必要量を見積もり、これにより配線要求混雑度を評価して画面に表示する第4の処理、及び、

前記ブロック配置情報を出力する第5の処理、を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項2】

半導体集積回路配置方法であって、

複数のブロックを含んで構成される半導体集積回路のチップ領域における前記ブロックの配置において、設計者の操作に応じてグラフィカルユーザインタフェースで画面に設計情報を表示し、論理合成処理結果情報の入力に基づき、設計者による前記ブロックの配置を含む処理を行って、配置配線実装処理のための情報を出力する処理をコンピュータで実行するものであり、

前記論理合成処理結果情報をもとに、ブロック間の接続情報、及びブロック内の回路ゲート物量情報を抽出する第1の処理工程、

前記ブロック内の回路ゲート物量情報と、ブロック実装率情報とから、配置対象ブロック毎に、必要なブロック配置領域面積とブロック内の配線長とを含む構成を見積もり、当該構成を含むブロック配置初期情報を作成する第2の処理工程、

前記ブロック配置初期情報と前記ブロック間の接続情報とをもとに、設計者の操作に応じて、前記ブロックの相互の関係を画面に表示し、前記チップ領域への前記ブロックの配置を決定しブロック配置情報を作成する第3の処理工程、

前記ブロック配置情報における前記配置されたブロックについて、前記ブロック間の接続情報に基づく前記ブロック間の配線長の見積もりと前記ブロック内の配線長の見積もりとから、前記チップ領域内における配線領域の必要量を見積もり、これにより配線要求混雑度を評価して画面に表示する第4の処理工程、及び、

前記ブロック配置情報を出力する第5の処理工程、を有すること、を特徴とする半導体集積回路配置方法。

【請求項3】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第2の処理では、前記ブロック配置領域面積として、ブロック矩形面積を求め、前記第3の処理では、前記ブロック矩形面積を一定維持または下回らない範囲で、当該ブロック矩形の横と縦の長さの比率を、設計者の操作に応じて変更して表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項4】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第3の処理では、前記ブロック間の接続関係に加えて前記ブロック間の接続数を設計者の操作に応じて画面に表示し、この際、配置対象ブロックと接続関係にあるブロックを接続線で結び、当該接続線の太さまたは色を、前記ブロック間の接続関係及び前記接続数に応じて変えて描画する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項5】

請求項4記載の半導体集積回路配置プログラムにおいて、

指定される配置対象ブロックと接続関係にあるブロックについてのみ、前記接続線及び接続数を表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項6】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第3の処理では、設計者の操作に応じて画面に、配置対象ブロックと接続関係にあるすべてのブロックを接続線で結び、これらのブロックの最外郭矩形のうちで、ブロック間の接続数を考慮して、前記配置対象ブロックの配置の重心を求めて表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項7】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第4の処理では、前記ブロックの配置対象の領域全体を所定の分割領域で表示し、当該分割領域ごとに、必要な配線物量を見積もることで前記配線要求混雑度を求め、当該混雑度に応じて色を変えて描画する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項8】

請求項7記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置対象の領域全体を均等なメッシュ状の領域に分割し、各々の分割領域ごとの配線要求混雑度を、分割領域の使用可能な配線チャネルの総数に対してその領域内にあるブロック内配線及びその領域を通過するブロック間配線が使用する配線チャネルの使用予測数によって求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項9】

請求項7記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置対象の領域全体を、設計者により任意に指定された値によって、均等なメッシュ状の領域に分割する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項10】

請求項8記載の半導体集積回路配置プログラムにおいて、

前記ブロック内の配線チャネルの混雑度について、配置されたブロック内の回路ゲートで使用するピンの総数から、接続するブロック内のネットの総配線長を求め、求めた配線を引くために必要なブロック内の配線チャネル数を求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項11】

請求項8記載の半導体集積回路配置プログラムにおいて、

前記ブロック内の配線チャネルの混雑度について、配置されたブロックの領域が、複数の分割領域にかかる場合、前記求めたブロック内の使用配線チャネル数を、複数の分割領域上の占有領域に応じて分割して配分してブロック内の使用配線チャネル数を求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項12】

請求項8記載の半導体集積回路配置プログラムにおいて、

前記ブロック内の配線チャネルの混雑度について、配置された各ブロックから、接続関係のあるすべてのブロックを対象にして、その中から、それぞれ接続関係のある2つのブロックの組み合わせにおいて、当該2つのブロックを含む最外郭矩形内に入る前記分割領域の個数をそれぞれX,Y方向について2ブロック矩形内分割領域数として求め、当該2ブロック間で、接続本数を前記求めたX,Y方向の分割領域数で割って当該2ブロックを含む最外郭矩形内に入る各分割領域のX,Y方向を通過する配線チャネル使用数を求め、前記チップ領域上で同一位置の分割領域についてそのX,Y方向を通過する配線チャネル使用数の総和を求め、これにより、前記分割領域毎のブロック間配線に必要なX,Y方向の配線チャネル数を求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項13】

請求項7記載の半導体集積回路配置プログラムにおいて、

前記チップ領域の配線層毎に、それぞれの配線層で予め使用領域が決定されている電源配線を含む固定配線を除いた配線チャネル数を、その層の使用可能な配線チャネル総数として、設計者により指定可能とする処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項14】

請求項7記載の半導体集積回路配置プログラムにおいて、

ブロック内配線のみの混雑度、ブロック間配線のみの混雑度、ブロック内及びブロック間を合わせた混雑度についての表示を、設計者により指定可能とする処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項15】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置について、前記チップ領域に直接に前記ブロックを配置する方法と、前記チップ領域を複数のリージョンに分割し、そのリージョン毎に前記ブロックを配置する方法と、を設計者により指定可能とする処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項16】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置について、前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、各リージョン内のブロック接続情報によるブロック接続関係がリージョン間を渡る場合、リージョン間接続情報として該当ブロックと該当リージョン間を直線で結び表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項17】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第2の処理では、前記チップ領域に直接にブロックを配置する場合、その初期値として、配置が必要な全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、前記チップ領域の外側に配置しておく処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項18】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第2の処理では、前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、その初期値として、配置が必要な全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、該当リージョンの内側に配置しておく処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項19】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第3の処理では、配置が必要な全ブロックのうち、指定されたブロックを、移動禁止して固定して表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項20】

請求項19記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、前記第3の処理では、配置対象のリージョン以外のリージョン内に配置が必要な全ブロックを、移動禁止して固定して表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項21】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域で予め配置位置が決められているブロックについて、前記チップ領域上の配置座標の指定に従って配置する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項22】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、それぞれのリージョンに設計者を割り当てて複数の設計者により同時並行での配置作業を行わせ、それぞれのリージョンの配置情報を、チップ領域の配置情報に併合する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項23】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、前記チップ領域の任意の位置に配置されるブロックについては、その配置されるブロックが設計者によりその他のブロックと重ならない任意の位置に配置されるように選定される処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項24】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、前記第3の処理では、設計者による操作に応じて、あるリージョンを構成するブロックを、そのリージョンとは異なるリージョンに配置する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項1】

半導体集積回路配置プログラムであって、

複数のブロックを含んで構成される半導体集積回路のチップ領域における前記ブロックの配置において、設計者の操作に応じてグラフィカルユーザインタフェースで画面に設計情報を表示し、論理合成処理結果情報の入力に基づき、設計者による前記ブロックの配置を含む処理を行って、配置配線実装処理のための情報を出力する処理をコンピュータに実行させるものであり、

前記論理合成処理結果情報をもとに、ブロック間の接続情報、及びブロック内の回路ゲート物量情報を抽出する第1の処理、

前記ブロック内の回路ゲート物量情報と、ブロック実装率情報とから、配置対象ブロック毎に、必要なブロック配置領域面積とブロック内の配線長とを含む構成を見積もり、当該構成を含むブロック配置初期情報を作成する第2の処理、

前記ブロック配置初期情報と前記ブロック間の接続情報とをもとに、設計者の操作に応じて、前記ブロックの相互の関係を画面に表示し、前記チップ領域への前記ブロックの配置を決定しブロック配置情報を作成する第3の処理、

前記ブロック配置情報における前記配置されたブロックについて、前記ブロック間の接続情報に基づく前記ブロック間の配線長の見積もりと前記ブロック内の配線長の見積もりとから、前記チップ領域内における配線領域の必要量を見積もり、これにより配線要求混雑度を評価して画面に表示する第4の処理、及び、

前記ブロック配置情報を出力する第5の処理、を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項2】

半導体集積回路配置方法であって、

複数のブロックを含んで構成される半導体集積回路のチップ領域における前記ブロックの配置において、設計者の操作に応じてグラフィカルユーザインタフェースで画面に設計情報を表示し、論理合成処理結果情報の入力に基づき、設計者による前記ブロックの配置を含む処理を行って、配置配線実装処理のための情報を出力する処理をコンピュータで実行するものであり、

前記論理合成処理結果情報をもとに、ブロック間の接続情報、及びブロック内の回路ゲート物量情報を抽出する第1の処理工程、

前記ブロック内の回路ゲート物量情報と、ブロック実装率情報とから、配置対象ブロック毎に、必要なブロック配置領域面積とブロック内の配線長とを含む構成を見積もり、当該構成を含むブロック配置初期情報を作成する第2の処理工程、

前記ブロック配置初期情報と前記ブロック間の接続情報とをもとに、設計者の操作に応じて、前記ブロックの相互の関係を画面に表示し、前記チップ領域への前記ブロックの配置を決定しブロック配置情報を作成する第3の処理工程、

前記ブロック配置情報における前記配置されたブロックについて、前記ブロック間の接続情報に基づく前記ブロック間の配線長の見積もりと前記ブロック内の配線長の見積もりとから、前記チップ領域内における配線領域の必要量を見積もり、これにより配線要求混雑度を評価して画面に表示する第4の処理工程、及び、

前記ブロック配置情報を出力する第5の処理工程、を有すること、を特徴とする半導体集積回路配置方法。

【請求項3】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第2の処理では、前記ブロック配置領域面積として、ブロック矩形面積を求め、前記第3の処理では、前記ブロック矩形面積を一定維持または下回らない範囲で、当該ブロック矩形の横と縦の長さの比率を、設計者の操作に応じて変更して表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項4】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第3の処理では、前記ブロック間の接続関係に加えて前記ブロック間の接続数を設計者の操作に応じて画面に表示し、この際、配置対象ブロックと接続関係にあるブロックを接続線で結び、当該接続線の太さまたは色を、前記ブロック間の接続関係及び前記接続数に応じて変えて描画する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項5】

請求項4記載の半導体集積回路配置プログラムにおいて、

指定される配置対象ブロックと接続関係にあるブロックについてのみ、前記接続線及び接続数を表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項6】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第3の処理では、設計者の操作に応じて画面に、配置対象ブロックと接続関係にあるすべてのブロックを接続線で結び、これらのブロックの最外郭矩形のうちで、ブロック間の接続数を考慮して、前記配置対象ブロックの配置の重心を求めて表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項7】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第4の処理では、前記ブロックの配置対象の領域全体を所定の分割領域で表示し、当該分割領域ごとに、必要な配線物量を見積もることで前記配線要求混雑度を求め、当該混雑度に応じて色を変えて描画する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項8】

請求項7記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置対象の領域全体を均等なメッシュ状の領域に分割し、各々の分割領域ごとの配線要求混雑度を、分割領域の使用可能な配線チャネルの総数に対してその領域内にあるブロック内配線及びその領域を通過するブロック間配線が使用する配線チャネルの使用予測数によって求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項9】

請求項7記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置対象の領域全体を、設計者により任意に指定された値によって、均等なメッシュ状の領域に分割する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項10】

請求項8記載の半導体集積回路配置プログラムにおいて、

前記ブロック内の配線チャネルの混雑度について、配置されたブロック内の回路ゲートで使用するピンの総数から、接続するブロック内のネットの総配線長を求め、求めた配線を引くために必要なブロック内の配線チャネル数を求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項11】

請求項8記載の半導体集積回路配置プログラムにおいて、

前記ブロック内の配線チャネルの混雑度について、配置されたブロックの領域が、複数の分割領域にかかる場合、前記求めたブロック内の使用配線チャネル数を、複数の分割領域上の占有領域に応じて分割して配分してブロック内の使用配線チャネル数を求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項12】

請求項8記載の半導体集積回路配置プログラムにおいて、

前記ブロック内の配線チャネルの混雑度について、配置された各ブロックから、接続関係のあるすべてのブロックを対象にして、その中から、それぞれ接続関係のある2つのブロックの組み合わせにおいて、当該2つのブロックを含む最外郭矩形内に入る前記分割領域の個数をそれぞれX,Y方向について2ブロック矩形内分割領域数として求め、当該2ブロック間で、接続本数を前記求めたX,Y方向の分割領域数で割って当該2ブロックを含む最外郭矩形内に入る各分割領域のX,Y方向を通過する配線チャネル使用数を求め、前記チップ領域上で同一位置の分割領域についてそのX,Y方向を通過する配線チャネル使用数の総和を求め、これにより、前記分割領域毎のブロック間配線に必要なX,Y方向の配線チャネル数を求める処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項13】

請求項7記載の半導体集積回路配置プログラムにおいて、

前記チップ領域の配線層毎に、それぞれの配線層で予め使用領域が決定されている電源配線を含む固定配線を除いた配線チャネル数を、その層の使用可能な配線チャネル総数として、設計者により指定可能とする処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項14】

請求項7記載の半導体集積回路配置プログラムにおいて、

ブロック内配線のみの混雑度、ブロック間配線のみの混雑度、ブロック内及びブロック間を合わせた混雑度についての表示を、設計者により指定可能とする処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項15】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置について、前記チップ領域に直接に前記ブロックを配置する方法と、前記チップ領域を複数のリージョンに分割し、そのリージョン毎に前記ブロックを配置する方法と、を設計者により指定可能とする処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項16】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記ブロックの配置について、前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、各リージョン内のブロック接続情報によるブロック接続関係がリージョン間を渡る場合、リージョン間接続情報として該当ブロックと該当リージョン間を直線で結び表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項17】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第2の処理では、前記チップ領域に直接にブロックを配置する場合、その初期値として、配置が必要な全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、前記チップ領域の外側に配置しておく処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項18】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第2の処理では、前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、その初期値として、配置が必要な全ブロックについて、必要なブロック配置領域面積を確保したブロック矩形を、該当リージョンの内側に配置しておく処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項19】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記第3の処理では、配置が必要な全ブロックのうち、指定されたブロックを、移動禁止して固定して表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項20】

請求項19記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、前記第3の処理では、配置対象のリージョン以外のリージョン内に配置が必要な全ブロックを、移動禁止して固定して表示する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項21】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域で予め配置位置が決められているブロックについて、前記チップ領域上の配置座標の指定に従って配置する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項22】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、それぞれのリージョンに設計者を割り当てて複数の設計者により同時並行での配置作業を行わせ、それぞれのリージョンの配置情報を、チップ領域の配置情報に併合する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項23】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、前記チップ領域の任意の位置に配置されるブロックについては、その配置されるブロックが設計者によりその他のブロックと重ならない任意の位置に配置されるように選定される処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【請求項24】

請求項1記載の半導体集積回路配置プログラムにおいて、

前記チップ領域を複数のリージョンに分割しそのリージョン毎に前記ブロックを配置する場合、前記第3の処理では、設計者による操作に応じて、あるリージョンを構成するブロックを、そのリージョンとは異なるリージョンに配置する処理を実行させること、を特徴とする半導体集積回路配置プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2009−238129(P2009−238129A)

【公開日】平成21年10月15日(2009.10.15)

【国際特許分類】

【出願番号】特願2008−86357(P2008−86357)

【出願日】平成20年3月28日(2008.3.28)

【出願人】(000233295)日立情報通信エンジニアリング株式会社 (195)

【Fターム(参考)】

【公開日】平成21年10月15日(2009.10.15)

【国際特許分類】

【出願日】平成20年3月28日(2008.3.28)

【出願人】(000233295)日立情報通信エンジニアリング株式会社 (195)

【Fターム(参考)】

[ Back to top ]