可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は可変容量素子に関し、特に並列に接続されるコンデンサの個数を切り替えて容量値を切り替える可変容量素子に関する。

【背景技術】

【0002】

半導体装置では、搭載される回路において容量素子を用いる。しかし、半導体装置では、半導体チップを製造した後に容量素子の容量値を可変することは困難である。そのため、半導体チップ製造後に容量素子の容量値を変更するために可変容量素子が用いられる。可変容量素子は、例えば、制御信号により容量値を切り替え、又は、変更することができきる素子である。この可変容量素子の例が特許文献1、2に開示されている。

【0003】

まず、特許文献1に開示されている可変容量素子と等価な可変容量素子100の回路図を図17に示す。図17に示すように、可変容量素子100は、コンデンサC1、C2、容量選択スイッチ101を有する。また、可変容量素子100は、出力端子COUTを有している。出力端子COUTは、可変容量素子100の一方の端子となる。また、可変容量素子100は、他方の端子に接地電圧VSSが供給されているものとする。

【0004】

そして、コンデンサC1は接地電圧VSSが供給される接地端子と出力端子COUTとの間に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、容量選択スイッチ101と直列に接続される。コンデンサC2の一方の端子は、接地端子に接続され、他方の端子は容量選択スイッチ101の一方の端子と接続される。ここで、以下の説明では、容量選択スイッチ101とコンデンサを接続するノードをND1と称す。容量選択スイッチ101の他方の端子は、出力端子COUTに接続される。容量選択スイッチ101は、トランスファスイッチを構成する。容量選択スイッチ101は、NMOSトランジスタN101、PMOSトランジスタP101、インバータINV101を有する。NMOSトランジスタN101のソースとPMOSトランジスタP101のソースは互いに接続される。また、NMOSトランジスタN101のドレインとPMOSトランジスタのドレインは互いに接続される。そして、NMOSトランジスタN101のゲートには、容量切替信号CSELが入力される。また、PMOSトランジスタP101のゲートには、インバータINV101を介して容量切替信号CSELが入力される。容量選択スイッチ101は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)の場合は導通状態となり、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)の場合は遮断状態となる。

【0005】

可変容量素子100は、容量選択スイッチ101が導通状態のときは、コンデンサC1、C2の合成容量(2つのコンデンサの容量値の合計値)を容量値とする。一方、可変容量素子100は、容量選択スイッチ101が遮断状態のときは、コンデンサC1の容量値のみを容量値とする。

【0006】

また、特許文献2に記載の可変容量素子と等価な可変容量素子200の回路図を図18に示す。図18に示すように、可変容量素子200は、コンデンサC1、C2、スイッチ回路(例えば、NMOSトランジスタN201)を有する。また、可変容量素子200は、出力端子COUTを有している。出力端子COUTは、可変容量素子200の一方の端子となる。また、可変容量素子200は、他方の端子に接地電圧VSSが供給されているものとする。

【0007】

そして、コンデンサC1は接地電圧VSSが供給される接地端子と出力端子COUTとの間に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、NMOSトランジスタN201と直列に接続される。NMOSトランジスタのソースは、接地端子に接続され、ドレインはコンデンサC2の一方の端子と接続される。ここで、以下の説明では、NMOSトランジスタN201のドレインとコンデンサとを接続するノードをND2と称す。コンデンサC2の他方の端子は、出力端子COUTに接続される。また、NMOSトランジスタN201のゲートには、容量切替信号CSELが入力される。NMOSトランジスタN201は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)の場合は導通状態となり、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)の場合は遮断状態となる。

【0008】

可変容量素子200は、NMOSトランジスタN201が導通状態のときは、コンデンサC1、C2の合成容量(2つのコンデンサの容量値の合計値)を容量値とする。一方、可変容量素子200は、NMOSトランジスタN201が遮断状態のときは、コンデンサC1の容量値のみを容量値とする。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許公報5,594,388号明細書

【特許文献2】特開2008−252774号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、可変容量素子100及び可変容量素子200には、容量値の精度が低い問題がある。可変容量素子100では、ノードND1の電圧と出力端子COUTの電圧とに電圧差がある場合、容量選択スイッチ101を介してリーク電流Ileakが流れる。また、可変容量素子200においても、ノードND2の電圧と接地電圧VSSとに電圧差がある場合、NMOSトランジスタN201を介してリーク電流Ileakが流れる。このリーク電流Ileakは、スイッチ回路が遮断状態のときに流れる。スイッチ回路が遮断状態である場合において、コンデンサC1への充放電が行われ場合、この充放電電流にリーク電流Ileakの影響が及ぶ。そして、このリーク電流Ileakは、コンデンサC1の容量値にずれが生じた場合と等価な容量値のずれの原因となる。また、リーク電流Ileakが一定の値に収束するまでの期間は、容量値が変動する問題がある。

【0011】

また、可変容量素子100では、出力端子COUTとコンデンサC2との間に容量選択スイッチ101がある。この容量選択スイッチ101は、トランジスタにより構成される。一般的に、トランジスタは、ゲート・ソース間及びゲート・ドレイン間に寄生容量を有する。この寄生容量は、出力端子COUTの電圧とノードND1の電圧との電圧差によって容量値が変動する。つまり、可変容量素子100は、容量選択スイッチ101の寄生容量の影響により、容量値ずれ及び容量値変動が生じる問題がある。

【課題を解決するための手段】

【0012】

本発明にかかる可変容量素子の一態様は、第1の電源端子と出力端子との間に接続される第1の容量素子と、容量切替信号に応じて導通状態が切り替えられる容量選択スイッチと、前記第1の容量素子と並列に接続され、かつ、前記容量選択スイッチと直列に接続される第2の容量素子と、前記容量選択スイッチが遮断状態とされる状態において、前記出力端子をリセット電圧にリセットする電荷リセット信号に応じて、前記第2の容量素子と前記容量選択スイッチとを接続する容量切替ノードの電圧と前記出力端子の電圧とを実質的に同じ電圧に設定する誤差補正回路と、を有する。

【0013】

本発明にかかる可変容量素子は、第1の容量素子への充放電が行われる前に、第1の容量素子に蓄積される電荷量をリセット電圧によりリセットする。このとき、本発明にかかる可変容量素子は、第2の容量素子と容量選択スイッチとを接続する容量切替ノードの電圧と出力端子の電圧とを実質的に同じ電圧に設定する。これにより、本発明にかかる可変容量素子は、第2の容量素子が非選択の状態において、第1の容量素子に充放電を行う場合に、容量選択スイッチに流れるリーク電流Ileakの影響を無くし、第1の容量素子の容量値ずれを防ぐことができる。

【発明の効果】

【0014】

本発明にかかる可変容量素子によれば、可変容量素子の容量値の精度を向上させることができる。

【図面の簡単な説明】

【0015】

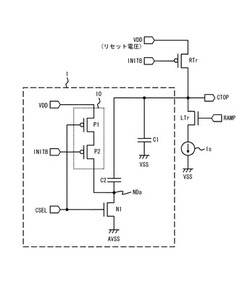

【図1】実施の形態1にかかる可変容量素子の回路図である。

【図2】図1に示す可変容量素子及びその充放電回路の動作を示すタイミングチャートである。

【図3】実施の形態1にかかる可変容量素子と従来の可変容量素子との容量切替後の特性を比較するグラフである。

【図4】実施の形態2にかかる可変容量素子の回路図である。

【図5】図4に示す可変容量素子及びその充放電回路の動作を示すタイミングチャートである。

【図6】実施の形態2にかかる可変容量素子と従来の可変容量素子との容量切替後の特性を比較するグラフである。

【図7】本発明にかかる可変容量素子を利用する発振回路の回路例を示すブロック図である。

【図8】図7に示す発振回路の差動増幅器の回路例を示す回路図である。

【図9】図7に示す発振回路のランプアンドホールド回路の動作を示すタイミングチャートである。

【図10】図7に示す発振回路の差動増幅器の動作を示すタイミングチャートである。

【図11】図7に示す発振回路の動作を示すタイミングチャートである。

【図12】本発明にかかる可変容量素子を利用するパルス幅変調回路の回路図である。

【図13】図12に示すパルス幅変調回路の動作を示すタイミングチャートである。

【図14】本発明にかかる可変容量素子を利用する遅延回路の回路図である。

【図15】図14に示す遅延回路で用いられる可変容量素子の回路図である。

【図16】図14に示す遅延回路の動作を示すタイミングチャートである。

【図17】特許文献1に記載の可変容量素子と等価な可変容量素子の回路図である。

【図18】特許文献2に記載の可変容量素子と等価な可変容量素子の回路図である。

【発明を実施するための形態】

【0016】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。図1に実施の形態1にかかる可変容量素子1の回路図を示す。なお、図1では、可変容量素子1に対して充放電を行う充放電回路を可変容量素子1の周辺回路として示した。図1に示す例では、リセットトランジスタRTrと、充放電制御トランジスタLTrと、電流源Isとが周辺回路である。なお、以下の説明では、符号Isは、電流源と電流源が出力する電流のいずれをも示すものとする。

【0017】

図1に示すように、可変容量素子1は、第1の容量素子(例えば、コンデンサC1)、第2の容量素子(例えば、コンデンサC2)、容量選択スイッチ(例えば、NMOSトランジスタN1)、誤差補正回路10を有する。

【0018】

コンデンサC1は、第1の電源端子(例えば、接地電圧VSSを供給する接地端子)と出力端子CTOPとの間に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、NMOSトランジスタN1と直列に接続される。NMOSトランジスタN1は、容量切替信号CSELに応じて導通状態が切り替えられる。NMOSトランジスタN1は、ソースが接地端子に接続され、ドレインがコンデンサC2に接続され、ゲートに容量切替信号CSELが入力される。なお、コンデンサC2は、第1の端子が出力端子CTOPに接続され、第2の端子がNMOSトランジスタN1のドレインに接続される。ここで、以下の説明では、コンデンサC1とNMSOトランジスタN1とを接続するノードを容量切替ノードNDaと称す。

【0019】

誤差補正回路10は、NMOSトランジスタN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する。誤差補正回路10は、PMOSトランジスタP1、P2を有する。PMOSトランジスタP1は、ソースに電源電圧VDDが供給され、ゲートに容量切替信号CSELが入力される。また、PMOSトランジスタP1のドレインは、PMOSトランジスタP2のソースと接続される。PMOSトランジスタP2は、ゲートに電荷リセット信号INITBが入力され、ドレインが容量切替ノードNDaに接続される。

【0020】

続いて、周辺回路について説明する。図1では、周辺回路として、リセットトランジスタRTrと、充放電制御トランジスタLTrと、電流源Isとを有する。リセットトランジスタRTrは、PMOSトランジスタにより形成される。リセットトランジスタRTrは、ソースに電源電圧VDD(例えば、リセット電圧)が供給され、ゲートに電荷リセット信号INITBが入力され、ドレインが出力端子CTOPに接続される。リセットトランジスタRTrは、電荷リセット信号INITBがイネーブル状態(例えば、ロウレベル)の場合に出力端子CTOPにリセット電圧を与える。また、リセットトランジスタRTrは、電荷リセット信号INITBがディスイネーブル状態(例えば、ハイレベル)の場合は、出力端子CTOPへのリセット電圧の供給を停止する。

【0021】

充放電制御トランジスタLTrは、NMOSトランジスタにより形成される。充放電制御トランジスタLTrは、ドレインが出力端子CTOPに接続され、ゲートにランプ制御信号RAMPが入力される。充放電制御トランジスタLTrのソースは、電流源Isの一方の端子に接続される。電流源Isは、電流Isを出力端子CTOPから引き込む。電流源Isは、他方の端子が接地端子に接続される。ここで、充放電制御トランジスタLTrは、ランプ制御信号RAMPがイネーブル状態(例えば、ハイレベル)の場合、導通状態となり電流源Isと出力端子CTOPとを接続する。充放電制御トランジスタLTrは、ランプ制御信号RAMPがディスイネーブル状態(例えば、ロウレベル)の場合、遮断状態となり電流源Isと出力端子CTOPとの接続状態を遮断状態とする。

【0022】

なお、本実施の形態における電荷リセット信号INITBとランプ制御信号RAMPは、図示しない制御回路が出力するものとする。

【0023】

続いて、可変容量素子1の動作について説明する。図2に図1に示した可変容量素子1の動作を示すタイミングチャートを示す。なお、図2に示す例では、電荷リセット信号INITBとランプ制御信号RAMPは同相信号を用いる。可変容量素子1は、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)である期間においてコンデンサC2と接地端子とを切り離す。つまり、可変容量素子1は、容量切替信号CSELがディスイネーブル状態の期間においては、コンデンサC2を非選択とする(又は無効化する)。そのため、可変容量素子1の容量値はコンデンサC1の容量値のみにより決まる。また、可変容量素子1は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)である期間においてコンデンサC2と接地端子とを接続する。つまり、可変容量素子1は、容量切替信号CSELがイネーブル状態の期間においては、コンデンサC2を選択する(又は有効化する)。そのため、可変容量素子1の容量値はコンデンサC1とコンデンサC2の容量値を足した値となる。

【0024】

そこで、まず、容量切替信号CSELがディスイネーブル状態となる期間の可変容量素子1の動作について説明する。可変容量素子1の制御においては、リセット期間Tinitとランプ期間Trampとがある。リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。そして、リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。また、電流源Isは出力端子CTOPと切り離される。また、誤差補正回路10のPMOSトランジスタP1、P2が共にオン状態となる。そのため、容量切替ノードNDaには、リセット電圧(例えば、電源電圧VDD)が与えられる。つまり、リセット期間Tinitにおいて、コンデンサC2の両端電圧は導電位となり、コンデンサC2に蓄積される電荷はほぼゼロとなる。

【0025】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1から電流Isを引き抜く。また、誤差補正回路10のPMOSトランジスタP2がオフ状態となる。そのため、容量切替ノードNDaは、フローティング状態となり、電流Isによる出力端子CTOPの電圧低下に伴い電圧が低下する。つまり、ランプ期間Trampでは、コンデンサC2への充放電はなく、コンデンサC1の容量値と電流Isのみにより出力端子CTOPの電圧低下の傾きが決定される。

【0026】

続いて、容量切替信号CSELがイネーブル状態となる期間の可変容量素子1の動作について説明する。この期間においても、可変容量素子1は、リセット期間Tinitとランプ期間Trampとを経て制御される。この期間においては、容量切替信号CSELがイネーブル状態であるため、容量切替ノードNDaには、接地電圧VSSが供給される。また、誤差補正回路10のPMOSトランジスタP1が容量切替信号CSELに応じてオフ状態となる。そのため、容量切替ノードNDaにはリセット期間Tinitとランプ期間Trampのいずれの期間においてもリセット電圧(例えば、電源電圧VDD)は供給されない。

【0027】

そして、リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。これにより、コンデンサC1、C2のいずれにもリセット電圧に応じた電荷が蓄積される。また、電流源Isは出力端子CTOPと切り離される。

【0028】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1、C2から電流Isを引き抜く。そのため、出力端子CTOPの電圧は、電流IsとコンデンサC1、C2の合成容量とに基づく傾きを持って低下する。従って、電流Isが一定である場合にコンデンサC2が有効になると、コンデンサC2が無効である期間よりも出力端子CTOPの電圧低下の傾きが緩やかになる。

【0029】

ここで、可変容量素子1と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化について説明する。そこで、図3に可変容量素子1と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化を示すグラフを示す。

【0030】

図3に示す例では、出力端子CTOPの電圧をリセット電圧(例えば、電源電圧VDD)で一定とした。また、図3に示すグラフの原点は、コンデンサC2が非選択状態に切り替わった時点である。図3に示すように、本実施の形態にかかる可変容量素子1においては、出力端子CTOPにリセット電圧が与えられる場合、容量切替ノードNDaにはリセット電圧が与えられる。そのため、コンデンサC2の両端の電圧差はほぼ0Vとなる。一方、図17に示す可変容量素子100では、コンデンサC2の出力端子側の端子に容量選択スイッチ101を介してリーク電流Ileakが流入するため、徐々にコンデンサC2の両端電圧が大きくなる。また、図18に示す可変容量素子200では、コンデンサC2の接地端子側端子からNMOSトランジスタN201を介してリーク電流Ileakが流れるため、コンデンサC2の両端電圧が徐々に大きくなる。このように、図17、図18に示した可変容量素子では、コンデンサC2が非選択状態となった後にコンデンサC2の両端電圧が収束するまでに時間tcが必要になる。つまり、図17、図18に示した可変容量素子では、この時間tcが経過するまでの期間は、容量値がリーク電流の影響により変動することになる。一方、本実施の形態にかかる可変容量素子1は、コンデンサC2が非選択となった後にコンデンサC2の両端の電圧差が変動しないため、図17、図18に示す可変容量素子のようにリーク電流Ileakによる容量値の変動は生じない。

【0031】

上記説明より、実施の形態1にかかる可変容量素子1では、スイッチ回路(NMOSトランジスタN1)の導通状態を切り替えることで、容量値を切り替える。このとき、可変容量素子1では、コンデンサC2を無効化する場合に、コンデンサC2の接地側端子をフローティング状態とする。そして、コンデンサC1に蓄積される電荷をリセット電圧によりリセットする期間に、コンデンサC2の接地側端子にリセット電圧とする。これにより、可変容量素子1では、コンデンサC1が放電される前の期間にコンデンサC2に蓄積される電荷をほぼゼロとする。そして、コンデンサC2の接地側端子を再度フローティング状態とした後にコンデンサC1からの放電を行う。これにより、可変容量素子1では、コンデンサC2が非選択状態である期間に、コンデンサC1からの放電を行う場合においても、コンデンサC2にリーク電流等が流れることを防止し、容量値の精度を高めることができる。

【0032】

実施の形態2

実施の形態2では、可変容量素子1のコンデンサC2と容量選択スイッチとを入れ替えた構成について説明する。そこで、実施の形態2にかかる可変容量素子2の回路図を図4に示す。図4に示す例では、実施の形態1と同様に可変容量素子2に充放電を行う周辺回路も含めた。また、実施の形態2の説明において実施の形態1において説明した構成要素と同じものについては実施の形態1と同じ符号を付して説明を省略する。

【0033】

図4に示すように、可変容量素子2は、コンデンサC2の第1の端子が容量選択スイッチ20の第2の端子に接続され、第2の端子が接地端子に接続される。容量選択スイッチ20は、第1の端子が出力端子に接続される。ここで、実施の形態2では、容量選択スイッチ20とコンデンサC2とを接続するノードを容量切替ノードNDbと称す。そして、誤差補正回路10は、電荷リセット信号INITBに基づきリセット電圧(例えば、電源電圧)容量切替ノードNDbに与える。

【0034】

また、実施の形態2では、容量選択スイッチ20としてトランスファスイッチを用いる。容量選択スイッチ20としてトランスファスイッチを用いることで、容量切替ノードNDbの電圧が上昇した場合においてもコンデンサC2と出力端子との導通状態を確保することが可能になる。

【0035】

トランスファスイッチは、PMOSトランジスタP3、NMOSトランジスタN2、インバータINV1を有する。PMOSトランジスタP3のソースとNMOSトランジスタN2のソースは互いに接続され、容量選択スイッチ20の第2の端子を構成する。また、PMOSトランジスタP3のドレインとNMOSトランジスタN2のドレインは互いに接続され、容量選択スイッチ20の第1の端子を構成する。NMOSトランジスタN2のゲートには容量切替信号CSELが入力される。また、PMOSトランジスタP3にはインバータINV1を介して容量切替信号CSELが与えられる。つまり、PMOSトランジスタP3とNMOSトランジスタのゲートには互いに反転した論理レベルを有する容量切替信号CSELが与えられる。

【0036】

続いて、可変容量素子2の動作について説明する。図5に可変容量素子2の動作を示すタイミングチャートを示す。なお、図5に示す例では、電荷リセット信号INITBとランプ制御信号RAMPは同相信号を用いる。可変容量素子2は、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)である期間においてコンデンサC2と出力端子CTOPとを切り離す。つまり、可変容量素子2は、容量切替信号CSELがディスイネーブル状態の期間においては、コンデンサC2を非選択とする(又は無効化する)。そのため、可変容量素子2の容量値はコンデンサC1の容量値のみにより決まる。また、可変容量素子2は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)である期間においてコンデンサC2と出力端子CTOPとを接続する。つまり、可変容量素子2は、容量切替信号CSELがイネーブル状態の期間においては、コンデンサC2を選択する(又は有効化する)。そのため、可変容量素子2の容量値はコンデンサC1とコンデンサC2の容量値を足した値となる。

【0037】

そこで、まず、容量切替信号CSELがディスイネーブル状態となる期間の可変容量素子2の動作について説明する。可変容量素子2の制御においては、リセット期間Tinitとランプ期間Trampとがある。リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。そして、リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。また、電流源Isは出力端子CTOPと切り離される。また、誤差補正回路10のPMOSトランジスタP1、P2が共にオン状態となる。そのため、容量切替ノードNDbには、リセット電圧(例えば、電源電圧VDD)が与えられる。つまり、リセット期間Tinitにおいて、容量選択スイッチ20の両端電圧は導電位となる。

【0038】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1から電流Isを引き抜く。また、誤差補正回路10のPMOSトランジスタP2がオフ状態となる。このとき、容量切替信号CSELがディスイネーブル状態であるため、容量選択スイッチ20がオフしている。そして、リセット期間Tinitにおいて、コンデンサC2にはリセット電圧に対応する電荷が蓄積されている。従って、誤差補正回路10が容量切替ノードNDbへのリセット電圧の供給を停止しても、容量選択スイッチ20が遮断状態であるため、容量切替ノードNDbの電圧はリセット電圧で維持される。つまり、ランプ期間Trampでは、コンデンサC2への充放電はなく、コンデンサC1の容量値と電流Isのみにより出力端子CTOPの電圧低下の傾きが決定される。

【0039】

続いて、容量切替信号CSELがイネーブル状態となる期間の可変容量素子1の動作について説明する。この期間においても、可変容量素子2は、リセット期間Tinitとランプ期間Trampとを経て制御される。この期間においては、容量切替信号CSELがイネーブル状態であるため、容量選択スイッチ20が導通状態となりコンデンサC2は出力端子CTOPと接続される。つまり、容量切替ノードNDbは、出力端子CTOPに接続される。また、誤差補正回路10のPMOSトランジスタP1が容量切替信号CSELに応じてオフ状態となる。そのため、容量切替ノードNDbにはリセット期間Tinitとランプ期間Trampのいずれの期間においてもリセット電圧(例えば、電源電圧VDD)は供給されない。

【0040】

そして、リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。これにより、コンデンサC1、C2のいずれにもリセット電圧に応じた電荷が蓄積される。また、電流源Isは出力端子CTOPと切り離される。

【0041】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1、C2から電流Isを引き抜く。そのため、出力端子CTOPの電圧は、電流IsとコンデンサC1、C2の合成容量とに基づく傾きを持って低下する。従って、電流Isが一定である場合にコンデンサC2が有効になると、コンデンサC2が無効である期間よりも出力端子CTOPの電圧低下の傾きが緩やかになる。

【0042】

ここで、可変容量素子2と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化について説明する。そこで、図6に可変容量素子2と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化を示すグラフを示す。

【0043】

図6に示す例では、出力端子CTOPの電圧をリセット電圧(例えば、電源電圧VDD)で一定とした。また、図6に示すグラフの原点は、コンデンサC2が非選択状態に切り替わった時点である。図6に示すように、本実施の形態にかかる可変容量素子2においては、出力端子CTOPにリセット電圧が与えられる場合、容量切替ノードNDbにはリセット電圧が与えられる。そのため、コンデンサC2の両端の電圧差はリセット電圧と男簿同じ値となる。一方、図17に示す可変容量素子100では、コンデンサC2の出力端子側の端子に容量選択スイッチ101を介してリーク電流Ileakが流入するため、徐々にコンデンサC2の両端電圧が大きくなる。また、図18に示す可変容量素子200では、コンデンサC2の接地端子側端子からNMOSトランジスタN201を介してリーク電流Ileakが流れるため、コンデンサC2の両端電圧が徐々に大きくなる。このように、図17、図18に示した可変容量素子では、コンデンサC2が非選択状態となった後にコンデンサC2の両端電圧が収束するまでに時間tcが必要になる。つまり、図17、図18に示した可変容量素子では、この時間tcが経過するまでの期間は、容量値がリーク電流の影響により変動することになる。一方、本実施の形態にかかる可変容量素子2は、コンデンサC2が非選択となった後にコンデンサC2の両端の電圧差が変動しない。このとき、可変容量素子2では、容量選択スイッチ20を介してリーク電流が流れる恐れがあるが、その場合であっても、容量切替ノードNDbはリセット期間Tinitにおいてリセット電圧とされるため、図17、図18に示す可変容量素子のようにリーク電流Ileakが時間と共に変化することがなく一定の電流量となるため、リーク電流Ileakよる容量値が時間と共に変動することがない。

【0044】

上記説明より、実施の形態2にかかる可変容量素子2は、容量選択スイッチ20の導通状態を切り替えることで、容量値を切り替える。このとき、可変容量素子2では、コンデンサC2を無効化する場合に、容量選択スイッチ20のコンデンサC2側の端子をリセット期間Tinitにおいてリセット電圧とする。これにより、可変容量素子2では、コンデンサC1が放電される前の期間に容量選択スイッチ20の両端の電圧差をほぼ0Vとする。そして、容量選択スイッチ20のコンデンサC2側の端子へのリセット電圧の供給を停止した後にコンデンサC1からの放電を行う。これにより、可変容量素子2では、コンデンサC2が非選択状態である期間に、コンデンサC1からの放電を行う場合においても、容量選択スイッチ20に流れるリーク電流を一定にして容量値の精度を高めることができる。

【0045】

実施の形態3

上記実施の形態において説明したよう、本発明にかかる可変容量素子は容量値を高精度に設定しながら、容量値の切替を可能にする。そこで、この可変容量素子を利用した機能回路について説明する。機能回路の一例として、実施の形態3では発振回路について説明する。ここで説明する発振回路は、抵抗により決定される電流量とコンデンサの容量値とにより決定される時定数に基づき発信信号の発振周波数を決定するRC発振回路である。そして、発振回路中の周波数検出回路において本発明にかかる可変容量素子を用いる。

【0046】

図7に実施の形態3にかかる発振回路3のブロック図を示す。図7に示すように発振回路3は、周波数検出回路30、差動増幅器40、電圧制御発振器50、制御回路60、フィルタコンデンサCpumpを有する。

【0047】

周波数検出回路30は、制御回路60が出力するタイミング制御信号に基づき発振信号(以下、出力信号Foutと称す)の周期の長さに応じて電圧レベルが変化する周波数検出電圧Vcapを生成する。なお、タイミング制御信号には、電荷リセット信号INITB、ランプ制御信号RAMP、ホールド制御信号HOLDを含み、周波数検出回路30は、これらの信号に応じて周波数検出電圧Vcapを生成する。

【0048】

図1に示すように、周波数検出回路30は、ランプアンドホールド回路31、NMOSトランジスタN3、N4、周波数設定抵抗R、周波数設定コンデンサCvを有する。周波数設定抵抗Rは、一端が電源端子VDDに接続され、他端がNMOSトランジスタN3のドレインに接続される。NMOSトランジスタN3は、ゲートとドレインが共通接続される。また、NMOSトランジスタN3のソースは接地端子に接続される。NMOSトランジスタN4は、ゲートがNMOSトランジスタN3のゲートと共通接続され、ソースが接地端子に接続される。また、NMOSトランジスタN4のドレインは、ランプアンドホールド回路31に接続される。つまり、NMOSトランジスタN3により生成されるダイオード電圧と電源電圧の差電圧を周波数設定抵抗Rの抵抗値により充放電電流の電流値が設定され、当該充放電電流は、NMOSトランジスタN3、N4により構成されるカレントミラー回路を介してランプアンドホールド回路31に与えられる。

【0049】

ランプアンドホールド回路31は、タイミング制御信号に基づき周波数設定コンデンサCvへの充放電電流の供給と周波数設定コンデンサCvに蓄積される電荷のリセットとを行う。ランプアンドホールド回路31は、NMOSトランジスタN5、N6、PMOトランジスタP4を有する。NMOSトランジスタN5、N6は、差動対を構成する。つまり、NMOSトランジスタN5、N6は、ソースが共通接続される。そして、NMOSトランジスタN5、N6のソース(共通接続点)には、NMOSトランジスタN4のドレインから出力される充放電電流が供給される。NMOSトランジスタN5のゲートには、ランプ制御信号RAMPが入力され、NMOSトランジスタN6のゲートにはホールド制御信号HOLDが入力される。NMOSトランジスタN5のドレインは、PMOSトランジスタP4のドレインと接続され、ランプアンドホールド回路31の出力端子となる。NMOSトランジスタN6のドレインは、電源端子VDDに接続される。PMOSトランジスタP4のゲートには、電荷リセット信号INITBが入力される。PMOSトランジスタP4のソースは、電源端子VDDに接続される。

【0050】

周波数設定コンデンサCvは、ランプアンドホールド回路31の出力端子と接地端子との間に接続される。この周波数設定コンデンサCvは、実施の形態1において説明した可変容量素子1である。そのため、周波数設定コンデンサCvには、容量値の切り替えを指示する容量切替信号CSELが入力される。そして、周波数設定コンデンサCvは、蓄積される電荷量に応じて周波数検出電圧Vcapを生成する。なお、周波数検出電圧Vcapは、ランプアンドホールド回路31の出力端子側のノードに生成されるものである。

【0051】

ランプアンドホールド回路31は、電荷リセット信号INITBがイネーブル状態(例えば、ロウレベル)となると、PMOSトランジスタP4をオンする。そして、ランプアンドホールド回路31は、周波数設定コンデンサCvに電源電圧に相当する電荷を蓄積することで、周波数設定コンデンサCvに蓄積される電荷のリセットを行う。また、ランプアンドホールド回路31は、電荷リセット信号INITBをディスイネーブル状態(例えば、ハイレベル)かつランプ制御信号RAMPがイネーブル状態(例えば、ハイレベル)となると、PMOSトランジスタP4をオフし、かつ、NMOSトランジスタN5をオンする。これにより、ランプアンドホールド回路31は、充放電電流によって周波数設定コンデンサCvから電荷の引き抜きを行う。また、ランプアンドホールド回路31は、ランプ制御信号RAMPをディスイネーブル状態(例えば、ロウレベル)、かつ、ホールド制御信号HOLDをイネーブル状態(例えば、ハイレベル)となると、NMOSトランジスタN5をオフし、かつ、NMOSトランジスタN6をオンする。これにより、ランプアンドホールド回路31は、周波数設定コンデンサCvからの放電を停止し、周波数設定コンデンサCvに蓄積された電荷により生じた周波数検出電圧Vcapを維持する。

【0052】

差動増幅器40は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流Icpを連続的に可変してフィルタコンデンサに出力する。より具体的には、差動増幅器40は、増幅部41とスイッチ回路42を有する。そして、増幅部41の反転入力端子には周波数検出電圧Vcapが入力され、非反転入力端子に基準電圧Vresが入力される。増幅部41は、例えば、トランスコンダクタンス増幅器であって、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じた電流値を有する発振周波数設定電流Icpを出力する。なお、本実施の形態では、基準電圧Vresとして、周波数設定抵抗Rが接続されるNMOSトランジスタN3のゲート電圧を用いる。

【0053】

スイッチ回路42は、増幅部41の出力端子とフィルタコンデンサCpumpとの間に設けられ、タイミング制御信号に含まれるポンプ制御信号PULSEに応じて導通状態が切り替えられる。より具体的には、スイッチ回路42は、ポンプ制御信号PULSEがイネーブル状態(例えば、ハイレベル)のときに導通状態となり、ディスイネーブル状態(例えば、ロウレベル)のときに遮断状態となる。

【0054】

ここで、差動増幅器40の回路について詳細な説明を行う。差動増幅器40の詳細な回路図を図8に示す。図8に示すように、差動増幅器40は、増幅部41、スイッチ回路42を有する。

【0055】

差動増幅器40は、フォールデッドカスコードアンプを構成する。より具体的には、差動増幅器40は、NMOSトランジスタN7〜N13、PMOSトランジスタP5〜P8を有する。NMOSトランジスタN7は、ソースが接地端子に接続され、ゲートに定電圧Vbn1が入力される。NMOSトランジスタN8、N9は、差動対を構成し、NMOSトランジスタN7が出力する動作電流に基づき動作する。NMOSトランジスタN8のゲートには基準電圧Vresが入力され、NMOSトランジスタN9のゲートには周波数検出電圧Vcapが入力される。そして、NMOSトランジスタN8のドレインはPMOSトランジスタP5のドレインに接続され、NMOSトランジスタN9のドレインはPMOSトランジスタP6のドレインに接続される。

【0056】

PMOSトランジスタP5のソース及びPMOSトランジスタP6のソースは電源端子VDDに接続される。また、PMOSトランジスタP5のゲートとPMOSトランジスタP6のゲートには定電圧Vbp1が入力される。PMOSトランジスタP7のソースはPMOSトランジスタP5のドレインに接続され、PMOSトランジスタP8のソースは、PMOSトランジスタP6のドレインに接続される。PMOSトランジスタP7のゲートとPMOSトランジスタP8のゲートには定電圧Vbp2が入力される。そして、PMOSトランジスタP8のドレインは、発振周波数設定電流Icpの流出側出力端子となる。

【0057】

NMOSトランジスタN10のソース及びNMOSトランジスタN11のソースは接地端子に接続される。また、NMOSトランジスタN10のゲートとNMOSトランジスタN11のゲートは共通接続される。NMOSトランジスタN12のソースはNMOSトランジスタN10のドレインと接続され、NMOSトランジスタN13のソースはNMOSトランジスタN11のドレインと接続される。NMOSトランジスタN12のゲートとNMOSトランジスタN13のゲートには定電圧Vbn2が入力される。NMOSトランジスタN12のドレインは、PMOSトランジスタP7のドレインと接続されると共にNMOSトランジスタN10、N11のゲートと接続される。そして、NMOSトランジスタN13のドレインは、発振周波数設定電流Icpの流入側出力端子となる。

【0058】

スイッチ回路42は、第1のスイッチ回路43と第2のスイッチ回路44を有する。第1のスイッチ回路43は、増幅部41の出力端子とフィルタコンデンサCpumpとの導通状態をポンプ制御信号PULSEに応じて切り替える。第1のスイッチ回路43は、PMOSトランジスタP9、NMOSトランジスタN14を有する。PMOSトランジスタP9の一方の端子とNMOSトランジスタN14の一方の端子は、フィルタコンデンサCpump及び電圧制御発振器50が接続されるノードに接続される。また、PMOSトランジスタP9の他方の端子は、PMOSトランジスタP8のドレイン(例えば、流出側出力端子)に接続される。一方、NMOSトランジスタN14の他方の端子は、NMOSトランジスタN13のドレイン(例えば、流入側出力端子)に接続される。そして、PMOSトランジスタP9のゲートには、後述するインバータ46で反転されたポンプ制御信号PULSEが入力される。NMOSトランジスタN14のゲートには、ポンプ制御信号PULSEが入力される。

【0059】

第2のスイッチ回路44は、第1のスイッチ回路43が遮断状態である期間に発振周波数制御電圧Vcpを増幅部41の出力端子に与え、増幅部41の出力端子から入出力される電流を打ち消す電流Icp0を出力する。第2のスイッチ回路44は、PMOSトランジスタP10、NMOSトランジスタN15、バッファ回路45、インバータ46を有する。PMOSトランジスタP10の一方の端子とNMOSトランジスタN15の一方の端子は、バッファ回路45の出力端子に接続される。また、PMOSトランジスタP10の他方の端子は、PMOSトランジスタP8のドレイン(例えば、流出側出力端子)に接続される。一方、NMOSトランジスタN15の他方の端子は、NMOSトランジスタN13のドレイン(例えば、流入側出力端子)に接続される。そして、PMOSトランジスタP10のゲートには、ポンプ制御信号PULSEが入力される。NMOSトランジスタN15のゲートには、インバータ46で反転されたポンプ制御信号PULSEが入力される。バッファ回路45は、正転入力端子にフィルタコンデンサCpumpが入力され、反転入力端子がバッファ回路45の出力と接続される。

【0060】

ここで、差動増幅器40は、ポンプ制御信号PULSEがイネーブル状態(例えば、ハイレベル)の場合、第1のスイッチ回路43が導通状態となり、フィルタコンデンサCpumpに発振周波数設定電流Icpを出力する。また、ポンプ制御信号PULSEがイネーブル状態の場合、第2のスイッチ回路44は、増幅部41の出力端子への電流Icp0の伝達を遮断する。

【0061】

一方、差動増幅器40は、ポンプ制御信号PULSEがディスイネーブル状態(例えば、ロウレベル)の場合、第1のスイッチ回路43が遮断状態となり、第2のスイッチ回路が電流Icp0を増幅部41の出力端子に与える。これにより、差動増幅器40の出力端子はフィルタコンデンサCpump側からはハイインピーダンス状態となる。このとき、差動増幅器40では、NMOSトランジスタN13のドレインと接地端子との間に寄生容量Conが形成され、PMOSトランジスタP8のドレインと電源端子VDDとの間に寄生容量Copが形成される。寄生容量Con、Copにより、第1のスイッチ回路43が遮断状態から導通状態となった場合、発振周波数制御電圧Vcpに電圧変動Vcp0が生じる。この電圧変動Vcp0は、PMOSトランジスタN8のドレインの電圧をVoutp、NMOSトランジスタN13のドレインの電圧をVoutnとすると、(1)式で表される。

Vcp0=((Voutp−Vcp)Cop−

(Voutn−Vcp)Con)/Cpump・・・(1)

【0062】

(1)式より、Vcp=Voutn=Voutpであれば、電圧変動Vcp0は生じないことがわかる。そこで、差動増幅器40では、第2のスイッチ回路44が第1のスイッチ回路43が遮断状態の期間にバッファ回路45により増幅部41が出力する電流を吸収し、かつ、増幅部41の出力端子に発振周波数制御電圧Vcpを与える。これにより、差動増幅器40では、第1のスイッチ回路43が遮断状態においてVcp=Voutn=Voutpとの条件を満たし、電圧変動Vcp0を抑制する。なお、このような電圧変動をチャージシェアと称す。本発明にかかる発振回路3では、発振周波数制御電圧Vcpの電圧レベルにより出力信号Foutの発振周波数が決定されるため、発振周波数制御電圧Vcpの電圧変動を抑制することで出力信号Foutのジッタが低減される。

【0063】

フィルタコンデンサCpumpは、発振周波数設定電流Icpに基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成する。フィルタコンデンサCpumpは、差動増幅器40の出力端子と電圧制御発振器50の入力端子とを接続するノードに一端が接続され、他端が接地端子に接続される。つまり、フィルタコンデンサCpumpは、差動増幅器40が出力する発振周波数設定電流Icpに応じて発振周波数制御電圧Vcpを生成し、発振周波数制御電圧Vcpを電圧制御発振器50に与える。

【0064】

電圧制御発振器50は、発振周波数制御電圧Vcpの電圧レベルに応じて出力信号Foutの発振周波数を制御する。

【0065】

制御回路60は、出力信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する。このタイミング制御信号には、電荷リセット信号INITB、ランプ制御信号RAMP、ホールド制御信号HOLD、ポンプ制御信号PULSEが含まれる。制御回路60は、出力信号Foutを分周した分周信号を生成し、当該分周信号のクロック数をカウントしたカウント値に基づき上記制御信号の論理レベルを切り替える。タイミング制御信号の論理レベルの切り替えタイミングの詳細は、後述する。

【0066】

続いて、図9に周波数検出回路30と制御回路60の動作を示すタイミングチャートを示す。そして、図9を参照して制御回路60がタイミング制御信号の論理レベルの切り替えタイミング及び周波数検出回路30の動作について説明する。

【0067】

図9に示すように、制御回路60は、出力信号Foutを分周して分周信号FDを生成する。図9に示す例では、分周信号FDは、出力信号Foutを2分周して生成する。また、制御回路60は、分周信号FDのクロック数をカウントしてカウント値COUNTを生成する。図9に示す例では、カウント値COUNTは2ビットの値であって0から3の値となる。そして、制御回路60は、カウント値COUNTの値に応じてタイミング制御信号の論理レベルを切り替える。

【0068】

具体的には、カウント値が0であった場合、制御回路60は、電荷リセット信号INITBをロウレベル(イネーブル状態)とし、ランプ制御信号RAMPをロウレベル(ディスイネーブル状態)とし、ホールド制御信号HOLDをハイレベル(イネーブル状態)とし、ポンプ制御信号PULSEをロウレベル(ディスイネーブル状態)とする。カウント値が0である期間を以下ではリセット期間Tinitと称す。

【0069】

カウント値が1であった場合、制御回路60は、電荷リセット信号INITBをハイレベル(ディスイネーブル状態)とし、ランプ制御信号RAMPをハイレベル(イネーブル状態)とし、ホールド制御信号HOLDをロウレベル(ディスイネーブル状態)とし、ポンプ制御信号PULSEをロウレベル(ディスイネーブル状態)とする。カウント値が1である期間を以下ではランプ期間Trampと称す。

【0070】

カウント値が2であった場合、制御回路60は、電荷リセット信号INITBをハイレベル(ディスイネーブル状態)とし、ランプ制御信号RAMPをロウレベル(ディスイネーブル状態)とし、ホールド制御信号HOLDをハイレベル(イネーブル状態)とし、ポンプ制御信号PULSEをロウレベル(ディスイネーブル状態)とする。カウント値が2である期間を以下ではホールド期間Tholdと称す。

【0071】

カウント値が3であった場合、制御回路60は、電荷リセット信号INITBをハイレベル(ディスイネーブル状態)とし、ランプ制御信号RAMPをロウレベル(ディスイネーブル状態)とし、ホールド制御信号HOLDをハイレベル(イネーブル状態)とし、ポンプ制御信号PULSEをハイレベル(イネーブル状態)とする。カウント値が3である期間を以下ではポンプ期間Tpumpと称す。

【0072】

続いて、周波数検出回路30の動作について説明する。周波数検出回路30は、リセット期間Tinitにおいて、電荷リセット信号INITBに基づきPMOSトランジスタP4を導通させることで周波数設定コンデンサCvに蓄積されている電荷を電源電圧に応じた電荷量にリセットする。これにより、周波数検出電圧Vcapは電源電圧とほぼ等しい電圧となる。このとき、NMOSトランジスタN5はランプ制御信号RAMPに応じてオフし、NMOSトランジスタN6はホールド制御信号HOLDに応じてオンする。

【0073】

そして、ランプ期間Trampにおいて、周波数検出回路30は、電荷リセット信号INITBに応じてPMOSトランジスタP4をオフし、ランプ制御信号RAMPに応じてNMOSトランジスタN5をオンし、ホールド制御信号HOLDに応じてNMOSトランジスタN6をオフする。つまり、周波数検出回路30は、ランプ期間Trampにおいて、充放電電流に基づき周波数設定コンデンサCvから電荷の引き抜きを行う。これにより、周波数検出電圧Vcapの電圧レベルは徐々に低下する。周波数検出電圧Vcapが低下する傾きは充放電電流の大きさ及び周波数設定コンデンサCvの容量値により決定される。また、ランプ期間Trampでは、周波数検出電圧Vcapの電圧レベルが低下するが、電圧低下速度は一定である。そのため、ランプ期間Trampにおける周波数検出電圧Vcapの電圧低下量dVcapは、ランプ期間Trampの長さ(出力信号Foutの発振周波数)によって決まる。

【0074】

そして、ホールド期間Tholdにおいて、周波数検出回路30は、電荷リセット信号INITBに応じてPMOSトランジスタP4をオフし、ランプ制御信号RAMPに応じてNMOSトランジスタN5をオフし、ホールド制御信号HOLDに応じてNMOSトランジスタN6をオンする。つまり、周波数検出回路30は、ホールド期間Tholdにおいて、周波数設定コンデンサCvが接続されるノードをハイインピーダンス状態とし、周波数設定コンデンサCvにより生成される周波数検出電圧Vcapの電圧レベルを維持する。

【0075】

そして、ポンプ期間Tpumpにおいては、差動増幅器40によるフィルタコンデンサCpumpへの発振周波数設定電流Icpの供給が行われる。このとき、周波数検出回路30に与えられる電荷リセット信号INITB、ランプ制御信号RAMP、ホールド制御信号HOLDはホールド期間Tholdとポンプ期間Tpumpとで同じである。そのため、ポンプ期間Tpumpにおいて周波数検出回路30により周波数検出電圧Vcapの電圧レベルが変動することはない。

【0076】

続いて、差動増幅器40の動作について説明する。図10に差動増幅器40の動作を示すタイミングチャートを示す。図10に示す例では、タイミングT0からT2の期間が図9で示した1組のリセット期間Tinit、ランプ期間Tramp、ホールド期間Thold、ポンプ期間Tpumpに相当する。そして、タイミングT1からT2の期間が図9で示したポンプ期間に相当する。

【0077】

差動増幅器40は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて電流Icpを出力する。しかし、タイミングT0からT1の期間では、ポンプ制御信号PULSEがディスイネーブル状態(ロウレベル)であるため、第1のスイッチ回路43が遮断状態となり、周波数検出電圧Vcapは一定に保たれる。一方、増幅部41は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて電流を出力する。しかし、この電流は、第2のスイッチ回路44がこの電流を打ち消す電流Icp0を出力し、増幅部41の出力電圧をVcpとする。

【0078】

そして、タイミングT1においてポンプ制御信号PULSEがイネーブル状態(例えば、ハイレベル)となると、第1のスイッチ回路43が導通状態となり、第2のスイッチ回路44が遮断状態となる。これにより、差動増幅器40は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて電流IcpをフィルタコンデンサCpumpに出力し、発振周波数制御電圧Vcpが変動する。図10に示す例では、発振周波数設定電流Icpが正の極性(フィルタコンデンサCpumpに充電を行う方向)で出力されるため、周波数検出電圧Vcapは、タイミングT1からT2で上昇する。

【0079】

続いて、実施の形態3にかかる発振回路3の全体の動作について説明する。実施の形態1にかかる発振回路3の動作を示すタイミングチャートを図11に示す。図11に示すタイミングチャートでは、周波数検出電圧Vcap、発振周波数制御電圧Vcp及び出力信号Foutの変動のみを示した。また、図11では、時間軸(横軸)の原点において発振回路3の動作が開始されるものとする。

【0080】

図11に示すように、発振回路3は、期間TM1からTM7の期間毎に発振周波数制御電圧Vcpを上昇させる。期間TM1からTM7の各期間には、図9に示すリセット期間Tinit、ランプ期間Tramp、ホールド期間Thold、ポンプ期間Tpumpが一組含まれる。また、出力信号Foutの周波数が期間毎に上昇するため、期間TM1から期間TM7は、徐々に短くなる。これはタイミング制御信号が出力信号Foutの周期に基づき生成されるためである。なお、図11に示す期間TM11からTM17がポンプ期間Tpumpに対応する期間となる。

【0081】

そして、期間TM7が経過した後は、周波数検出電圧Vcapの低レベル側電圧が基準電圧Vresとほぼ同じになる。これにより、発振回路3では、差動増幅器40が出力する発振周波数設定電流Icpがほぼ0となる。そのため、周波数検出電圧Vcapの低レベル側電圧が基準電圧Vresとほぼ同じになった後はその状態が維持される。また、周波数検出電圧Vcapが一定の電圧に保たれるため、出力信号Foutの発振周波数も一定に保たれる。つまり、発振回路3では、出力信号Foutの発振周波数が目標値に達した後は出力信号Foutにジッタは生じない。

【0082】

上記説明より、実施の形態3にかかる発振回路3では、フィルタコンデンサCpumpは、発振周波数設定電流Icpに応じて発振周波数制御電圧Vcpを生成する。このとき、発振回路3では、差動増幅器40が周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて連続的に値が変化する発振周波数設定電流Icpを出力する。つまり、周波数検出電圧Vcapと基準電圧Vresとの電圧差があれば発振周波数設定電流Icpは、当該電圧差に応じた大きさを有し、周波数検出電圧Vcapと基準電圧Vresとの電圧差がなければ発振周波数設定電流Icpは、実質的に0となる。これにより、発振回路3では、出力信号Foutの周波数が目標値と一致する状態(例えば、周波数検出電圧Vcapが基準電圧Vresと一致した状態)では、ポンプ制御信号PULSEがイネーブル状態となっても発振周波数制御電圧Vcpに変動が生じない。これにより、発振回路3では、出力信号Foutの発振周波数が目標値と一致した後に、発振周波数制御電圧Vcpの電圧値が変動することがなく、発振周波数制御電圧Vcpの電圧値に応じて電圧制御発振器50が決定する出力信号Foutの発振周波数もずれることがない。つまり、発振回路3では、出力信号Foutのジッタを低減することができる。

【0083】

このように、発振回路3では、発振周波数制御電圧Vcpが差動増幅器40により高精度に生成される。そのため、周波数設定コンデンサCvの容量値と充放電される電流値とにより決定される時定数のずれが出力信号Foutの周波数ずれ又はジッタに大きく影響する。このような用途において、本発明にかかる可変容量素子を用いることで、発振回路3の出力信号Foutの発振周波数の精度を高めることができる。また、発振回路3では、周波数設定コンデンサCvの容量値を容量切替信号CSELにより切り替えることができる。これにより、発振回路3の汎用性を高めることができる。

【0084】

また、実施の形態3にかかる発振回路3では、差動増幅器40がスイッチ回路42を有する。このスイッチ回路42は、差動増幅器40の入力信号の差電圧増幅結果を反映する期間(例えば、ポンプ期間Tpump)以外は遮断状態に制御される。発振回路3では、リセット期間Tinit、ランプ期間Trampにおいて周波数検出電圧Vcapが出力信号Foutを反映した電圧とずれた電圧値となる。しかし、スイッチ回路42がポンプ期間以外は遮断状態に制御されるため、リセット期間Tinit及びランプ期間Trampにおける周波数検出電圧Vcapのずれが発振周波数に反映されることを防ぐことができる。これにより、発振回路3では、いずれの期間においても発振周波数を安定化させることができる。

【0085】

また、実施の形態3にかかる発振回路3では、スイッチ回路42が第1のスイッチ回路43及び第2のスイッチ回路44を有する。そして、第1のスイッチ回路43が遮断状態の期間においても増幅部41の出力端子に第2のスイッチ回路44を動作させる。第2のスイッチ回路44は、周波数検出電圧Vcapと基準電圧Vresとの電圧差が生じるリセット期間Tinit及びランプ期間Trampにおいても、増幅部41が出力する電流を吸収し、増幅部41の出力端子を発振周波数制御電圧Vcpに維持する。これにより、第1のスイッチ回路43が遮断状態から導通状態に切り替わったタイミングで生じるチャージシェアに起因する発振周波数制御電圧Vcpの電位変動を抑制することができる。つまり、実施の形態3にかかる発振回路3では、スイッチ回路42を設けたことに起因するジッタを抑制することができる。

【0086】

実施の形態3にかかる発振回路3では、基準電圧VresとしてNMOSトランジスタN3のダイオード電圧を用い、充放電電流の電流値を電源電圧と当該ダイオード電圧との差電圧を周波数設定抵抗Rで割って決定する。ダイオード電圧が低くなると、充放電電流の電流値が大きくなり、ランプ期間Trampにおける周波数検出電圧Vcapの傾きが大きくなる。充放電電流の電流値Iresは、周波数設定抵抗R、基準電圧Vres、電源電圧VDDとすると(2)式で表される。

Ires=(VDD−Vres)/R・・・(2)

ホールド期間Tholdにおける周波数検出電圧をVcap(HOLD)とすると、Vcap(HOLD)は、充放電電流の電流値をIres、周波数設定コンデンサCの容量値をC、ランプ期間の長さをTrampとすると(3)式で表される。

Vcap(HOLD)=VDD−(Ires・Tramp)/C・・・(3)

ここで、実施の形態1にかかる発振回路3ではVcap(HOLD)=Vresとなるようにフィードバックループにより、周波数が補正される。そこで、(2)式、(3)式からランプ期間Tramp及び出力信号Foutの周波数を求めると(4)式となる。なお、(4)式においてNは、制御回路60内の分周回数である。

Fout=N/Tramp=N/RC・・・(4)

つまり、実施の形態1にかかる発振回路3では、電源電圧、NMOSのトランジスタN3のダイオード電圧が相殺され周波数設定抵抗R、周波数設定コンデンサC、分周回数Nのみの関数となる。

【0087】

実施の形態4

可変容量素子1、2は、時定数回路の時定数を高精度に設定する用途に利用可能である。そこで、時定数回路を有する回路例として、実施の形態4では、可変容量素子1、2を有するパルス幅変調回路について説明する。そこで、実施の形態4にかかるパルス幅変調回路4の回路図を図12に示す。図12に示すようにパルス幅変調回路4は、インバータ70、71、可変容量素子Cv1を有する。パルス幅変調回路4においては、可変容量素子Cvとインバータ70により時定数回路を構成する。この可変容量素子Cv1は、実施の形態1、2において説明した可変容量素子1、2である。そのため、可変容量素子Cv1には、容量切替信号CSELが入力される。また、可変容量素子Cv1には、電荷リセット信号INITBとして入力信号Vinが入力される。

【0088】

インバータ70は、PMOSトランジスタP11、NMOSトランジスタN16、電流源Is1を有する。PMOSトランジスタP11は、ソースに電源電圧VDDが供給され、ゲートに入力信号Vinが入力され、ドレインがNMOSトランジスタN16のドレインに接続される。NMOSトランジスタN16は、ソースが電流源Is1の第1の端子に接続され、ゲートに入力信号Vinが入力され、ドレインがPMOSトランジスタP11のドレインに接続される。PMOSトランジスタP11のドレインとNMOSトランジスタN16のドレインとが接続されるノードは、インバータ70の出力端子となる。そして、インバータ70は、出力端子から中間出力信号Vd1を出力する。電流源Is1は、NMOSトランジスタN16のソースと接地端子との間に接続される。

【0089】

インバータ71は、PMOSトランジスタP12、NMOSトランジスタN17を有する。PMOSトランジスタP12は、ソースに電源電圧VDDが供給され、ゲートに第1の中間出力信号Vd1が入力され、ドレインがNMOSトランジスタN17のドレインに接続される。NMOSトランジスタN17は、ソースに接地電圧VSSが供給され、ゲートに第1の中間出力信号Vd1が入力され、ドレインがPMOSトランジスタP12のドレインに接続される。PMOSトランジスタP12のドレインとNMOSトランジスタN17のドレインとが接続されるノードは、インバータ71の出力端子となる。なお、インバータ71から出力される信号がパルス幅変調回路4の出力信号Voutとなる。

【0090】

続いて、パルス幅変調回路4の動作について説明する。そこで、パルス幅変調回路4の動作を示すタイミングチャートを図13に示す。なお、以下の説明では、可変容量素子Cv1として可変容量素子1を用いる。

【0091】

パルス幅変調回路4は、容量切替信号CSELの論理レベルによって、出力信号Voutのパルス幅を変更する。より具体的には、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)の場合、可変容量素子Cv1の容量値は、コンデンサC1のみによって設定される。一方、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)の場合、可変容量素子Cv1の容量値は、コンデンサC1、C2の容量値の合計値となる。

【0092】

そこで、まず、容量切替信号CSELがディスイネーブル状態の期間の動作について説明する。図13に示すように、パルス幅変調回路4は、入力信号Vinがロウレベル(例えば、接地電圧VSS)の期間に中間出力信号Vd1をハイレベル(例えば、電源電圧VDD)とする。これにより、可変容量素子Cv1のコンデンサC1には、電源電圧VDDに対応した電荷が蓄積される。一方、入力信号Vinがロウレベルとなることで可変容量素子Cv1の誤差補正回路10は容量切替ノードNDaに電源電圧VDDを与え、コンデンサC2に蓄積されている電荷をほぼゼロにする。また、中間出力信号Vd1がハイレベルの期間は、出力信号Voutはロウレベルとなる。

【0093】

そして、入力信号Vinがロウレベルからハイレベルに切り替わると、NMOSトランジスタN16が導通状態となり、電流源Is1がコンデンサC1から電荷を引き抜く。そして、この電荷引き抜き動作により中間出力信号Vd1の電圧レベルが徐々に低下する。そして、中間出力信号Vd1の電圧レベルがインバータ71の閾値電圧Vthを下回ると出力信号Voutがハイレベルに切り替わる。このとき、中間出力信号Vd1は、可変容量素子Cv1により立ち下がりが立ち上がりよりも緩やかになる。そのため、出力信号Voutは、立ち上がりが入力信号Vinの立ち上がりよりも時間dly1だけ遅延する。

【0094】

続いて、容量切替信号CSELがイネーブル状態の期間の動作について説明する。容量切替信号CSELがイネーブル状態の期間では、可変容量素子Cv1の容量値が容量切替信号CSELがディスイネーブル状態の期間よりも大きくなる。そのため、容量切替信号CSELがイネーブル状態の期間における中間出力信号Vd1の立ち下がり速度は、容量切替信号CSELがディスイネーブル状態の期間よりも遅くなる。そして、この期間における出力信号Voutの立ち上がりは、入力信号Vinの立ち上がりから時間dly2だけ遅延する。なお、この時間dly2は、時間dly1よりも大きい。

【0095】

上記説明より、パルス幅変調回路4は、可変容量素子Cv1の容量値の大きさによって、出力信号Voutの立ち上がりを入力信号Vinの立ち上がりよりも遅くする。これにより、パルス幅変調回路4は、出力信号Voutのパルス幅を入力信号Vinのパルス幅異なる幅に設定することができる。また、パルス幅変調回路4は、可変容量素子Cv1の容量値を切り替えることで出力信号Voutのパルス幅を変更することができる。このようなパルス幅変調回路4では、可変容量素子Cv1の容量値の精度がパルス幅の値に影響を及ぼす。そのため、パルス幅の精度を向上させるためには、容量値の精度を向上させる必要がある。従って、本発明にかかる可変容量素子1、2は、このような用途において有効である。

【0096】

実施の形態5

時定数回路を有する回路例として、実施の形態5では、可変容量素子1、2を利用する遅延回路について説明する。そこで、実施の形態5にかかる遅延回路5の回路図を図14に示す。図14に示すように遅延回路5は、インバータ70〜73、可変容量素子Cv1、Cv2を有する。遅延回路5においては、インバータ70と可変容量素子Cv1により第1の時定数回路を構成し、インバータ72と可変容量素子Cv2により第2の時定数回路を構成する。なお、インバータ70、71、可変容量素子Cv1は、実施の形態4にかかるパルス幅変調回路4のものと同じであるためここでは説明を省略する。また、以下の説明では、実施の形態4における中間出力信号Vd1を第1の中間出力信号Vd1と称し、出力信号Voutを第2の中間出力信号Vd2と称す。

【0097】

インバータ72は、PMOSトランジスタP13、NMOSトランジスタN18、電流源Is2を有する。PMOSトランジスタP13は、ソースに電流源Is2が接続され、ゲートに第2の中間出力信号Vd2が入力され、ドレインがNMOSトランジスタN18のドレインに接続される。NMOSトランジスタN18は、ソースに接地電圧VSSが供給され、ゲートに第2の中間出力信号Vd2が入力され、ドレインがPMOSトランジスタP13のドレインに接続される。PMOSトランジスタP13のドレインとNMOSトランジスタN18のドレインとが接続されるノードは、インバータ72の出力端子となる。そして、インバータ72は、出力端子から第3の中間出力信号Vd3を出力する。電流源Is2は、PMOSトランジスタN13のソースと電源端子との間に接続される。

【0098】

インバータ73は、PMOSトランジスタP14、NMOSトランジスタN19を有する。PMOSトランジスタP14は、ソースに電源電圧VDDが供給され、ゲートに第3の中間出力信号Vd3が入力され、ドレインがNMOSトランジスタN17のドレインに接続される。NMOSトランジスタN17は、ソースに接地電圧VSSが供給され、ゲートに第3の中間出力信号Vd3が入力され、ドレインがPMOSトランジスタP14のドレインに接続される。PMOSトランジスタP14のドレインとNMOSトランジスタN19のドレインとが接続されるノードは、インバータ73の出力端子となる。なお、インバータ73から出力される信号が遅延回路5の出力信号Voutとなる。

【0099】

可変容量素子Cv2は、インバータ72の出力端子と接地端子との間に設けられる。この可変容量素子Cv2は、リセット電圧として接地電圧VSSが与えられる。そのため、回路構成が可変容量素子1とは異なる。そこで、可変容量素子Cv2の回路図を図15に示す。

【0100】

図15に示すように、可変容量素子Cv2は、第1の容量素子(例えば、コンデンサC1)、第2の容量素子(例えば、コンデンサC2)、容量選択スイッチ(例えば、NMOSトランジスタN20)誤差補正回路11を有する。

【0101】

コンデンサC1は、第1の電源端子(例えば、接地電圧VSSを供給する接地端子)と出力端子CTOPとの間に接続される。ここで、出力端子CTOPは、本実施の形態では、インバータ72の出力端子に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、NMOSトランジスタN20と直列に接続される。NMOSトランジスタN20は、容量切替信号CSELに応じて導通状態が切り替えられる。NMOSトランジスタN20は、ソースが接地端子に接続され、ドレインがコンデンサC2に接続され、ゲートに容量切替信号CSELが入力される。なお、コンデンサC2は、第1の端子が出力端子CTOPに接続され、第2の端子がNMOSトランジスタN20のドレインに接続される。ここで、以下の説明では、コンデンサC2とNMSOトランジスタN20とを接続するノードを容量切替ノードNDcと称す。

【0102】

誤差補正回路11は、NMOSトランジスタN20が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITB(本実施の形態では、第2の中間出力信号Vd2)に応じて、容量切替ノードNDcの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する。誤差補正回路11は、NMOSトランジスタN21、N22、インバータINV2を有する。NMOSトランジスタN22は、ソースに電源電圧VDDが供給され、ゲートにインバータINV2を介して容量切替信号CSELの反転信号が入力される。また、NMOSトランジスタN22のドレインは、NMOSトランジスタN21のソースと接続される。NMOSトランジスタN21は、ゲートに電荷リセット信号INITBが入力され、ドレインが容量切替ノードNDcに接続される。

【0103】

可変容量素子Cv2は、コンデンサC2が非選択の状態において、コンデンサC1の電荷をリセットする期間に、コンデンサC2の両端電圧をほぼ0Vとし、コンデンサC2の電荷をリセットする。つまり、基本的な動作は、可変容量素子1と同じである。

【0104】

続いて、遅延回路5の動作について説明する。遅延回路5の動作を示すタイミングチャートを図16に示す。図16に示すタイミングチャートの説明では、容量切替信号CSELをディスイネーブル状態(例えば、ロウレベル)で固定するものとする。

【0105】

図16に示すように、遅延回路5では、インバータ70と可変容量素子Cv1により、第1の中間出力信号Vd1の立ち下がりを遅延させる。これにより、遅延回路5は、第2の中間出力信号Vd2の立ち上がりエッジを入力信号Vinの立ち上がりエッジを遅延させる。また、遅延回路5は、インバータ72と可変容量素子Cv2により第3の中間出力信号Vd3の立ち上がりを遅延させる。これにより、遅延回路5は、出力信号Voutの立ち下がりエッジを第2の中間出力信号Vd2の立ち下がりエッジを遅延させる。つまり、遅延回路5は、可変容量素子Cv1、Cv2の容量値に応じて出力信号Voutを入力信号Vinから遅延させることができる。

【0106】

上記説明より、遅延回路5において、容量値の精度が高い本発明にかかる可変容量素子Cv1、Cv2を用いることで、遅延時間の設定精度を向上させることができる。

【0107】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0108】

1、2、Cv、Cv1、Cv2 可変容量素子

可変容量素子

3 発振回路

4 パルス幅変調回路

5 遅延回路

10、11 誤差補正回路

20 容量選択スイッチ

30 周波数検出回路

31 ランプアンドホールド回路

40 差動増幅器

41 増幅部

42 スイッチ回路

43 第1のスイッチ回路

44 第2のスイッチ回路

45 バッファ回路

46 インバータ回路

50 発振器

60 制御回路

C1 コンデンサ

C2 コンデンサ

CTOP 出力端子

CSEL 容量切替信号

Cpump フィルタコンデンサ

INITB 電荷リセット信号

RAMP ランプ制御信号

HOLD ホールド制御回路

PULSE ポンプ制御信号

Tinit リセット期間

Tramp ランプ期間

Thold ホールド期間

Tpump ポンプ期間

VSS 接地電圧

VDD 電源電圧

Is 電流源

R 周波数設定抵抗

RTr リセットトランジスタ

LTr 充放電制御トランジスタ

N1〜N20 NMOSトランジスタ

P1〜P19 PMOSトランジスタ

【技術分野】

【0001】

本発明は可変容量素子に関し、特に並列に接続されるコンデンサの個数を切り替えて容量値を切り替える可変容量素子に関する。

【背景技術】

【0002】

半導体装置では、搭載される回路において容量素子を用いる。しかし、半導体装置では、半導体チップを製造した後に容量素子の容量値を可変することは困難である。そのため、半導体チップ製造後に容量素子の容量値を変更するために可変容量素子が用いられる。可変容量素子は、例えば、制御信号により容量値を切り替え、又は、変更することができきる素子である。この可変容量素子の例が特許文献1、2に開示されている。

【0003】

まず、特許文献1に開示されている可変容量素子と等価な可変容量素子100の回路図を図17に示す。図17に示すように、可変容量素子100は、コンデンサC1、C2、容量選択スイッチ101を有する。また、可変容量素子100は、出力端子COUTを有している。出力端子COUTは、可変容量素子100の一方の端子となる。また、可変容量素子100は、他方の端子に接地電圧VSSが供給されているものとする。

【0004】

そして、コンデンサC1は接地電圧VSSが供給される接地端子と出力端子COUTとの間に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、容量選択スイッチ101と直列に接続される。コンデンサC2の一方の端子は、接地端子に接続され、他方の端子は容量選択スイッチ101の一方の端子と接続される。ここで、以下の説明では、容量選択スイッチ101とコンデンサを接続するノードをND1と称す。容量選択スイッチ101の他方の端子は、出力端子COUTに接続される。容量選択スイッチ101は、トランスファスイッチを構成する。容量選択スイッチ101は、NMOSトランジスタN101、PMOSトランジスタP101、インバータINV101を有する。NMOSトランジスタN101のソースとPMOSトランジスタP101のソースは互いに接続される。また、NMOSトランジスタN101のドレインとPMOSトランジスタのドレインは互いに接続される。そして、NMOSトランジスタN101のゲートには、容量切替信号CSELが入力される。また、PMOSトランジスタP101のゲートには、インバータINV101を介して容量切替信号CSELが入力される。容量選択スイッチ101は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)の場合は導通状態となり、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)の場合は遮断状態となる。

【0005】

可変容量素子100は、容量選択スイッチ101が導通状態のときは、コンデンサC1、C2の合成容量(2つのコンデンサの容量値の合計値)を容量値とする。一方、可変容量素子100は、容量選択スイッチ101が遮断状態のときは、コンデンサC1の容量値のみを容量値とする。

【0006】

また、特許文献2に記載の可変容量素子と等価な可変容量素子200の回路図を図18に示す。図18に示すように、可変容量素子200は、コンデンサC1、C2、スイッチ回路(例えば、NMOSトランジスタN201)を有する。また、可変容量素子200は、出力端子COUTを有している。出力端子COUTは、可変容量素子200の一方の端子となる。また、可変容量素子200は、他方の端子に接地電圧VSSが供給されているものとする。

【0007】

そして、コンデンサC1は接地電圧VSSが供給される接地端子と出力端子COUTとの間に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、NMOSトランジスタN201と直列に接続される。NMOSトランジスタのソースは、接地端子に接続され、ドレインはコンデンサC2の一方の端子と接続される。ここで、以下の説明では、NMOSトランジスタN201のドレインとコンデンサとを接続するノードをND2と称す。コンデンサC2の他方の端子は、出力端子COUTに接続される。また、NMOSトランジスタN201のゲートには、容量切替信号CSELが入力される。NMOSトランジスタN201は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)の場合は導通状態となり、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)の場合は遮断状態となる。

【0008】

可変容量素子200は、NMOSトランジスタN201が導通状態のときは、コンデンサC1、C2の合成容量(2つのコンデンサの容量値の合計値)を容量値とする。一方、可変容量素子200は、NMOSトランジスタN201が遮断状態のときは、コンデンサC1の容量値のみを容量値とする。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許公報5,594,388号明細書

【特許文献2】特開2008−252774号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、可変容量素子100及び可変容量素子200には、容量値の精度が低い問題がある。可変容量素子100では、ノードND1の電圧と出力端子COUTの電圧とに電圧差がある場合、容量選択スイッチ101を介してリーク電流Ileakが流れる。また、可変容量素子200においても、ノードND2の電圧と接地電圧VSSとに電圧差がある場合、NMOSトランジスタN201を介してリーク電流Ileakが流れる。このリーク電流Ileakは、スイッチ回路が遮断状態のときに流れる。スイッチ回路が遮断状態である場合において、コンデンサC1への充放電が行われ場合、この充放電電流にリーク電流Ileakの影響が及ぶ。そして、このリーク電流Ileakは、コンデンサC1の容量値にずれが生じた場合と等価な容量値のずれの原因となる。また、リーク電流Ileakが一定の値に収束するまでの期間は、容量値が変動する問題がある。

【0011】

また、可変容量素子100では、出力端子COUTとコンデンサC2との間に容量選択スイッチ101がある。この容量選択スイッチ101は、トランジスタにより構成される。一般的に、トランジスタは、ゲート・ソース間及びゲート・ドレイン間に寄生容量を有する。この寄生容量は、出力端子COUTの電圧とノードND1の電圧との電圧差によって容量値が変動する。つまり、可変容量素子100は、容量選択スイッチ101の寄生容量の影響により、容量値ずれ及び容量値変動が生じる問題がある。

【課題を解決するための手段】

【0012】

本発明にかかる可変容量素子の一態様は、第1の電源端子と出力端子との間に接続される第1の容量素子と、容量切替信号に応じて導通状態が切り替えられる容量選択スイッチと、前記第1の容量素子と並列に接続され、かつ、前記容量選択スイッチと直列に接続される第2の容量素子と、前記容量選択スイッチが遮断状態とされる状態において、前記出力端子をリセット電圧にリセットする電荷リセット信号に応じて、前記第2の容量素子と前記容量選択スイッチとを接続する容量切替ノードの電圧と前記出力端子の電圧とを実質的に同じ電圧に設定する誤差補正回路と、を有する。

【0013】

本発明にかかる可変容量素子は、第1の容量素子への充放電が行われる前に、第1の容量素子に蓄積される電荷量をリセット電圧によりリセットする。このとき、本発明にかかる可変容量素子は、第2の容量素子と容量選択スイッチとを接続する容量切替ノードの電圧と出力端子の電圧とを実質的に同じ電圧に設定する。これにより、本発明にかかる可変容量素子は、第2の容量素子が非選択の状態において、第1の容量素子に充放電を行う場合に、容量選択スイッチに流れるリーク電流Ileakの影響を無くし、第1の容量素子の容量値ずれを防ぐことができる。

【発明の効果】

【0014】

本発明にかかる可変容量素子によれば、可変容量素子の容量値の精度を向上させることができる。

【図面の簡単な説明】

【0015】

【図1】実施の形態1にかかる可変容量素子の回路図である。

【図2】図1に示す可変容量素子及びその充放電回路の動作を示すタイミングチャートである。

【図3】実施の形態1にかかる可変容量素子と従来の可変容量素子との容量切替後の特性を比較するグラフである。

【図4】実施の形態2にかかる可変容量素子の回路図である。

【図5】図4に示す可変容量素子及びその充放電回路の動作を示すタイミングチャートである。

【図6】実施の形態2にかかる可変容量素子と従来の可変容量素子との容量切替後の特性を比較するグラフである。

【図7】本発明にかかる可変容量素子を利用する発振回路の回路例を示すブロック図である。

【図8】図7に示す発振回路の差動増幅器の回路例を示す回路図である。

【図9】図7に示す発振回路のランプアンドホールド回路の動作を示すタイミングチャートである。

【図10】図7に示す発振回路の差動増幅器の動作を示すタイミングチャートである。

【図11】図7に示す発振回路の動作を示すタイミングチャートである。

【図12】本発明にかかる可変容量素子を利用するパルス幅変調回路の回路図である。

【図13】図12に示すパルス幅変調回路の動作を示すタイミングチャートである。

【図14】本発明にかかる可変容量素子を利用する遅延回路の回路図である。

【図15】図14に示す遅延回路で用いられる可変容量素子の回路図である。

【図16】図14に示す遅延回路の動作を示すタイミングチャートである。

【図17】特許文献1に記載の可変容量素子と等価な可変容量素子の回路図である。

【図18】特許文献2に記載の可変容量素子と等価な可変容量素子の回路図である。

【発明を実施するための形態】

【0016】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。図1に実施の形態1にかかる可変容量素子1の回路図を示す。なお、図1では、可変容量素子1に対して充放電を行う充放電回路を可変容量素子1の周辺回路として示した。図1に示す例では、リセットトランジスタRTrと、充放電制御トランジスタLTrと、電流源Isとが周辺回路である。なお、以下の説明では、符号Isは、電流源と電流源が出力する電流のいずれをも示すものとする。

【0017】

図1に示すように、可変容量素子1は、第1の容量素子(例えば、コンデンサC1)、第2の容量素子(例えば、コンデンサC2)、容量選択スイッチ(例えば、NMOSトランジスタN1)、誤差補正回路10を有する。

【0018】

コンデンサC1は、第1の電源端子(例えば、接地電圧VSSを供給する接地端子)と出力端子CTOPとの間に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、NMOSトランジスタN1と直列に接続される。NMOSトランジスタN1は、容量切替信号CSELに応じて導通状態が切り替えられる。NMOSトランジスタN1は、ソースが接地端子に接続され、ドレインがコンデンサC2に接続され、ゲートに容量切替信号CSELが入力される。なお、コンデンサC2は、第1の端子が出力端子CTOPに接続され、第2の端子がNMOSトランジスタN1のドレインに接続される。ここで、以下の説明では、コンデンサC1とNMSOトランジスタN1とを接続するノードを容量切替ノードNDaと称す。

【0019】

誤差補正回路10は、NMOSトランジスタN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する。誤差補正回路10は、PMOSトランジスタP1、P2を有する。PMOSトランジスタP1は、ソースに電源電圧VDDが供給され、ゲートに容量切替信号CSELが入力される。また、PMOSトランジスタP1のドレインは、PMOSトランジスタP2のソースと接続される。PMOSトランジスタP2は、ゲートに電荷リセット信号INITBが入力され、ドレインが容量切替ノードNDaに接続される。

【0020】

続いて、周辺回路について説明する。図1では、周辺回路として、リセットトランジスタRTrと、充放電制御トランジスタLTrと、電流源Isとを有する。リセットトランジスタRTrは、PMOSトランジスタにより形成される。リセットトランジスタRTrは、ソースに電源電圧VDD(例えば、リセット電圧)が供給され、ゲートに電荷リセット信号INITBが入力され、ドレインが出力端子CTOPに接続される。リセットトランジスタRTrは、電荷リセット信号INITBがイネーブル状態(例えば、ロウレベル)の場合に出力端子CTOPにリセット電圧を与える。また、リセットトランジスタRTrは、電荷リセット信号INITBがディスイネーブル状態(例えば、ハイレベル)の場合は、出力端子CTOPへのリセット電圧の供給を停止する。

【0021】

充放電制御トランジスタLTrは、NMOSトランジスタにより形成される。充放電制御トランジスタLTrは、ドレインが出力端子CTOPに接続され、ゲートにランプ制御信号RAMPが入力される。充放電制御トランジスタLTrのソースは、電流源Isの一方の端子に接続される。電流源Isは、電流Isを出力端子CTOPから引き込む。電流源Isは、他方の端子が接地端子に接続される。ここで、充放電制御トランジスタLTrは、ランプ制御信号RAMPがイネーブル状態(例えば、ハイレベル)の場合、導通状態となり電流源Isと出力端子CTOPとを接続する。充放電制御トランジスタLTrは、ランプ制御信号RAMPがディスイネーブル状態(例えば、ロウレベル)の場合、遮断状態となり電流源Isと出力端子CTOPとの接続状態を遮断状態とする。

【0022】

なお、本実施の形態における電荷リセット信号INITBとランプ制御信号RAMPは、図示しない制御回路が出力するものとする。

【0023】

続いて、可変容量素子1の動作について説明する。図2に図1に示した可変容量素子1の動作を示すタイミングチャートを示す。なお、図2に示す例では、電荷リセット信号INITBとランプ制御信号RAMPは同相信号を用いる。可変容量素子1は、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)である期間においてコンデンサC2と接地端子とを切り離す。つまり、可変容量素子1は、容量切替信号CSELがディスイネーブル状態の期間においては、コンデンサC2を非選択とする(又は無効化する)。そのため、可変容量素子1の容量値はコンデンサC1の容量値のみにより決まる。また、可変容量素子1は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)である期間においてコンデンサC2と接地端子とを接続する。つまり、可変容量素子1は、容量切替信号CSELがイネーブル状態の期間においては、コンデンサC2を選択する(又は有効化する)。そのため、可変容量素子1の容量値はコンデンサC1とコンデンサC2の容量値を足した値となる。

【0024】

そこで、まず、容量切替信号CSELがディスイネーブル状態となる期間の可変容量素子1の動作について説明する。可変容量素子1の制御においては、リセット期間Tinitとランプ期間Trampとがある。リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。そして、リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。また、電流源Isは出力端子CTOPと切り離される。また、誤差補正回路10のPMOSトランジスタP1、P2が共にオン状態となる。そのため、容量切替ノードNDaには、リセット電圧(例えば、電源電圧VDD)が与えられる。つまり、リセット期間Tinitにおいて、コンデンサC2の両端電圧は導電位となり、コンデンサC2に蓄積される電荷はほぼゼロとなる。

【0025】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1から電流Isを引き抜く。また、誤差補正回路10のPMOSトランジスタP2がオフ状態となる。そのため、容量切替ノードNDaは、フローティング状態となり、電流Isによる出力端子CTOPの電圧低下に伴い電圧が低下する。つまり、ランプ期間Trampでは、コンデンサC2への充放電はなく、コンデンサC1の容量値と電流Isのみにより出力端子CTOPの電圧低下の傾きが決定される。

【0026】

続いて、容量切替信号CSELがイネーブル状態となる期間の可変容量素子1の動作について説明する。この期間においても、可変容量素子1は、リセット期間Tinitとランプ期間Trampとを経て制御される。この期間においては、容量切替信号CSELがイネーブル状態であるため、容量切替ノードNDaには、接地電圧VSSが供給される。また、誤差補正回路10のPMOSトランジスタP1が容量切替信号CSELに応じてオフ状態となる。そのため、容量切替ノードNDaにはリセット期間Tinitとランプ期間Trampのいずれの期間においてもリセット電圧(例えば、電源電圧VDD)は供給されない。

【0027】

そして、リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。これにより、コンデンサC1、C2のいずれにもリセット電圧に応じた電荷が蓄積される。また、電流源Isは出力端子CTOPと切り離される。

【0028】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1、C2から電流Isを引き抜く。そのため、出力端子CTOPの電圧は、電流IsとコンデンサC1、C2の合成容量とに基づく傾きを持って低下する。従って、電流Isが一定である場合にコンデンサC2が有効になると、コンデンサC2が無効である期間よりも出力端子CTOPの電圧低下の傾きが緩やかになる。

【0029】

ここで、可変容量素子1と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化について説明する。そこで、図3に可変容量素子1と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化を示すグラフを示す。

【0030】

図3に示す例では、出力端子CTOPの電圧をリセット電圧(例えば、電源電圧VDD)で一定とした。また、図3に示すグラフの原点は、コンデンサC2が非選択状態に切り替わった時点である。図3に示すように、本実施の形態にかかる可変容量素子1においては、出力端子CTOPにリセット電圧が与えられる場合、容量切替ノードNDaにはリセット電圧が与えられる。そのため、コンデンサC2の両端の電圧差はほぼ0Vとなる。一方、図17に示す可変容量素子100では、コンデンサC2の出力端子側の端子に容量選択スイッチ101を介してリーク電流Ileakが流入するため、徐々にコンデンサC2の両端電圧が大きくなる。また、図18に示す可変容量素子200では、コンデンサC2の接地端子側端子からNMOSトランジスタN201を介してリーク電流Ileakが流れるため、コンデンサC2の両端電圧が徐々に大きくなる。このように、図17、図18に示した可変容量素子では、コンデンサC2が非選択状態となった後にコンデンサC2の両端電圧が収束するまでに時間tcが必要になる。つまり、図17、図18に示した可変容量素子では、この時間tcが経過するまでの期間は、容量値がリーク電流の影響により変動することになる。一方、本実施の形態にかかる可変容量素子1は、コンデンサC2が非選択となった後にコンデンサC2の両端の電圧差が変動しないため、図17、図18に示す可変容量素子のようにリーク電流Ileakによる容量値の変動は生じない。

【0031】

上記説明より、実施の形態1にかかる可変容量素子1では、スイッチ回路(NMOSトランジスタN1)の導通状態を切り替えることで、容量値を切り替える。このとき、可変容量素子1では、コンデンサC2を無効化する場合に、コンデンサC2の接地側端子をフローティング状態とする。そして、コンデンサC1に蓄積される電荷をリセット電圧によりリセットする期間に、コンデンサC2の接地側端子にリセット電圧とする。これにより、可変容量素子1では、コンデンサC1が放電される前の期間にコンデンサC2に蓄積される電荷をほぼゼロとする。そして、コンデンサC2の接地側端子を再度フローティング状態とした後にコンデンサC1からの放電を行う。これにより、可変容量素子1では、コンデンサC2が非選択状態である期間に、コンデンサC1からの放電を行う場合においても、コンデンサC2にリーク電流等が流れることを防止し、容量値の精度を高めることができる。

【0032】

実施の形態2

実施の形態2では、可変容量素子1のコンデンサC2と容量選択スイッチとを入れ替えた構成について説明する。そこで、実施の形態2にかかる可変容量素子2の回路図を図4に示す。図4に示す例では、実施の形態1と同様に可変容量素子2に充放電を行う周辺回路も含めた。また、実施の形態2の説明において実施の形態1において説明した構成要素と同じものについては実施の形態1と同じ符号を付して説明を省略する。

【0033】

図4に示すように、可変容量素子2は、コンデンサC2の第1の端子が容量選択スイッチ20の第2の端子に接続され、第2の端子が接地端子に接続される。容量選択スイッチ20は、第1の端子が出力端子に接続される。ここで、実施の形態2では、容量選択スイッチ20とコンデンサC2とを接続するノードを容量切替ノードNDbと称す。そして、誤差補正回路10は、電荷リセット信号INITBに基づきリセット電圧(例えば、電源電圧)容量切替ノードNDbに与える。

【0034】

また、実施の形態2では、容量選択スイッチ20としてトランスファスイッチを用いる。容量選択スイッチ20としてトランスファスイッチを用いることで、容量切替ノードNDbの電圧が上昇した場合においてもコンデンサC2と出力端子との導通状態を確保することが可能になる。

【0035】

トランスファスイッチは、PMOSトランジスタP3、NMOSトランジスタN2、インバータINV1を有する。PMOSトランジスタP3のソースとNMOSトランジスタN2のソースは互いに接続され、容量選択スイッチ20の第2の端子を構成する。また、PMOSトランジスタP3のドレインとNMOSトランジスタN2のドレインは互いに接続され、容量選択スイッチ20の第1の端子を構成する。NMOSトランジスタN2のゲートには容量切替信号CSELが入力される。また、PMOSトランジスタP3にはインバータINV1を介して容量切替信号CSELが与えられる。つまり、PMOSトランジスタP3とNMOSトランジスタのゲートには互いに反転した論理レベルを有する容量切替信号CSELが与えられる。

【0036】

続いて、可変容量素子2の動作について説明する。図5に可変容量素子2の動作を示すタイミングチャートを示す。なお、図5に示す例では、電荷リセット信号INITBとランプ制御信号RAMPは同相信号を用いる。可変容量素子2は、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)である期間においてコンデンサC2と出力端子CTOPとを切り離す。つまり、可変容量素子2は、容量切替信号CSELがディスイネーブル状態の期間においては、コンデンサC2を非選択とする(又は無効化する)。そのため、可変容量素子2の容量値はコンデンサC1の容量値のみにより決まる。また、可変容量素子2は、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)である期間においてコンデンサC2と出力端子CTOPとを接続する。つまり、可変容量素子2は、容量切替信号CSELがイネーブル状態の期間においては、コンデンサC2を選択する(又は有効化する)。そのため、可変容量素子2の容量値はコンデンサC1とコンデンサC2の容量値を足した値となる。

【0037】

そこで、まず、容量切替信号CSELがディスイネーブル状態となる期間の可変容量素子2の動作について説明する。可変容量素子2の制御においては、リセット期間Tinitとランプ期間Trampとがある。リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。そして、リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。また、電流源Isは出力端子CTOPと切り離される。また、誤差補正回路10のPMOSトランジスタP1、P2が共にオン状態となる。そのため、容量切替ノードNDbには、リセット電圧(例えば、電源電圧VDD)が与えられる。つまり、リセット期間Tinitにおいて、容量選択スイッチ20の両端電圧は導電位となる。

【0038】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1から電流Isを引き抜く。また、誤差補正回路10のPMOSトランジスタP2がオフ状態となる。このとき、容量切替信号CSELがディスイネーブル状態であるため、容量選択スイッチ20がオフしている。そして、リセット期間Tinitにおいて、コンデンサC2にはリセット電圧に対応する電荷が蓄積されている。従って、誤差補正回路10が容量切替ノードNDbへのリセット電圧の供給を停止しても、容量選択スイッチ20が遮断状態であるため、容量切替ノードNDbの電圧はリセット電圧で維持される。つまり、ランプ期間Trampでは、コンデンサC2への充放電はなく、コンデンサC1の容量値と電流Isのみにより出力端子CTOPの電圧低下の傾きが決定される。

【0039】

続いて、容量切替信号CSELがイネーブル状態となる期間の可変容量素子1の動作について説明する。この期間においても、可変容量素子2は、リセット期間Tinitとランプ期間Trampとを経て制御される。この期間においては、容量切替信号CSELがイネーブル状態であるため、容量選択スイッチ20が導通状態となりコンデンサC2は出力端子CTOPと接続される。つまり、容量切替ノードNDbは、出力端子CTOPに接続される。また、誤差補正回路10のPMOSトランジスタP1が容量切替信号CSELに応じてオフ状態となる。そのため、容量切替ノードNDbにはリセット期間Tinitとランプ期間Trampのいずれの期間においてもリセット電圧(例えば、電源電圧VDD)は供給されない。

【0040】

そして、リセット期間Tinitにおいては、電荷リセット信号INITBがイネーブル状態かつランプ制御信号RAMPがディスイネーブル状態となる。リセット期間Tinitでは、リセットトランジスタRTrが出力端子CTOPにリセット電圧(例えば、電源電圧VDD)を与える。これにより、コンデンサC1、C2のいずれにもリセット電圧に応じた電荷が蓄積される。また、電流源Isは出力端子CTOPと切り離される。

【0041】

続いて、ランプ期間Trampにおいては、電荷リセット信号INITBがディスイネーブル状態かつランプ制御信号RAMPがイネーブル状態となる。そして、ランプ期間Trampでは、リセットトランジスタRTrが遮断状態となり出力端子CTOPへのリセット電圧の供給を停止する。また、電流源Isは出力端子CTOPと接続され、コンデンサC1、C2から電流Isを引き抜く。そのため、出力端子CTOPの電圧は、電流IsとコンデンサC1、C2の合成容量とに基づく傾きを持って低下する。従って、電流Isが一定である場合にコンデンサC2が有効になると、コンデンサC2が無効である期間よりも出力端子CTOPの電圧低下の傾きが緩やかになる。

【0042】

ここで、可変容量素子2と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化について説明する。そこで、図6に可変容量素子2と図17、18に示す可変容量素子においてコンデンサC2を非選択とした場合のコンデンサC2の両端の電圧差の変化を示すグラフを示す。

【0043】

図6に示す例では、出力端子CTOPの電圧をリセット電圧(例えば、電源電圧VDD)で一定とした。また、図6に示すグラフの原点は、コンデンサC2が非選択状態に切り替わった時点である。図6に示すように、本実施の形態にかかる可変容量素子2においては、出力端子CTOPにリセット電圧が与えられる場合、容量切替ノードNDbにはリセット電圧が与えられる。そのため、コンデンサC2の両端の電圧差はリセット電圧と男簿同じ値となる。一方、図17に示す可変容量素子100では、コンデンサC2の出力端子側の端子に容量選択スイッチ101を介してリーク電流Ileakが流入するため、徐々にコンデンサC2の両端電圧が大きくなる。また、図18に示す可変容量素子200では、コンデンサC2の接地端子側端子からNMOSトランジスタN201を介してリーク電流Ileakが流れるため、コンデンサC2の両端電圧が徐々に大きくなる。このように、図17、図18に示した可変容量素子では、コンデンサC2が非選択状態となった後にコンデンサC2の両端電圧が収束するまでに時間tcが必要になる。つまり、図17、図18に示した可変容量素子では、この時間tcが経過するまでの期間は、容量値がリーク電流の影響により変動することになる。一方、本実施の形態にかかる可変容量素子2は、コンデンサC2が非選択となった後にコンデンサC2の両端の電圧差が変動しない。このとき、可変容量素子2では、容量選択スイッチ20を介してリーク電流が流れる恐れがあるが、その場合であっても、容量切替ノードNDbはリセット期間Tinitにおいてリセット電圧とされるため、図17、図18に示す可変容量素子のようにリーク電流Ileakが時間と共に変化することがなく一定の電流量となるため、リーク電流Ileakよる容量値が時間と共に変動することがない。

【0044】

上記説明より、実施の形態2にかかる可変容量素子2は、容量選択スイッチ20の導通状態を切り替えることで、容量値を切り替える。このとき、可変容量素子2では、コンデンサC2を無効化する場合に、容量選択スイッチ20のコンデンサC2側の端子をリセット期間Tinitにおいてリセット電圧とする。これにより、可変容量素子2では、コンデンサC1が放電される前の期間に容量選択スイッチ20の両端の電圧差をほぼ0Vとする。そして、容量選択スイッチ20のコンデンサC2側の端子へのリセット電圧の供給を停止した後にコンデンサC1からの放電を行う。これにより、可変容量素子2では、コンデンサC2が非選択状態である期間に、コンデンサC1からの放電を行う場合においても、容量選択スイッチ20に流れるリーク電流を一定にして容量値の精度を高めることができる。

【0045】

実施の形態3

上記実施の形態において説明したよう、本発明にかかる可変容量素子は容量値を高精度に設定しながら、容量値の切替を可能にする。そこで、この可変容量素子を利用した機能回路について説明する。機能回路の一例として、実施の形態3では発振回路について説明する。ここで説明する発振回路は、抵抗により決定される電流量とコンデンサの容量値とにより決定される時定数に基づき発信信号の発振周波数を決定するRC発振回路である。そして、発振回路中の周波数検出回路において本発明にかかる可変容量素子を用いる。

【0046】

図7に実施の形態3にかかる発振回路3のブロック図を示す。図7に示すように発振回路3は、周波数検出回路30、差動増幅器40、電圧制御発振器50、制御回路60、フィルタコンデンサCpumpを有する。

【0047】

周波数検出回路30は、制御回路60が出力するタイミング制御信号に基づき発振信号(以下、出力信号Foutと称す)の周期の長さに応じて電圧レベルが変化する周波数検出電圧Vcapを生成する。なお、タイミング制御信号には、電荷リセット信号INITB、ランプ制御信号RAMP、ホールド制御信号HOLDを含み、周波数検出回路30は、これらの信号に応じて周波数検出電圧Vcapを生成する。

【0048】

図1に示すように、周波数検出回路30は、ランプアンドホールド回路31、NMOSトランジスタN3、N4、周波数設定抵抗R、周波数設定コンデンサCvを有する。周波数設定抵抗Rは、一端が電源端子VDDに接続され、他端がNMOSトランジスタN3のドレインに接続される。NMOSトランジスタN3は、ゲートとドレインが共通接続される。また、NMOSトランジスタN3のソースは接地端子に接続される。NMOSトランジスタN4は、ゲートがNMOSトランジスタN3のゲートと共通接続され、ソースが接地端子に接続される。また、NMOSトランジスタN4のドレインは、ランプアンドホールド回路31に接続される。つまり、NMOSトランジスタN3により生成されるダイオード電圧と電源電圧の差電圧を周波数設定抵抗Rの抵抗値により充放電電流の電流値が設定され、当該充放電電流は、NMOSトランジスタN3、N4により構成されるカレントミラー回路を介してランプアンドホールド回路31に与えられる。

【0049】

ランプアンドホールド回路31は、タイミング制御信号に基づき周波数設定コンデンサCvへの充放電電流の供給と周波数設定コンデンサCvに蓄積される電荷のリセットとを行う。ランプアンドホールド回路31は、NMOSトランジスタN5、N6、PMOトランジスタP4を有する。NMOSトランジスタN5、N6は、差動対を構成する。つまり、NMOSトランジスタN5、N6は、ソースが共通接続される。そして、NMOSトランジスタN5、N6のソース(共通接続点)には、NMOSトランジスタN4のドレインから出力される充放電電流が供給される。NMOSトランジスタN5のゲートには、ランプ制御信号RAMPが入力され、NMOSトランジスタN6のゲートにはホールド制御信号HOLDが入力される。NMOSトランジスタN5のドレインは、PMOSトランジスタP4のドレインと接続され、ランプアンドホールド回路31の出力端子となる。NMOSトランジスタN6のドレインは、電源端子VDDに接続される。PMOSトランジスタP4のゲートには、電荷リセット信号INITBが入力される。PMOSトランジスタP4のソースは、電源端子VDDに接続される。

【0050】

周波数設定コンデンサCvは、ランプアンドホールド回路31の出力端子と接地端子との間に接続される。この周波数設定コンデンサCvは、実施の形態1において説明した可変容量素子1である。そのため、周波数設定コンデンサCvには、容量値の切り替えを指示する容量切替信号CSELが入力される。そして、周波数設定コンデンサCvは、蓄積される電荷量に応じて周波数検出電圧Vcapを生成する。なお、周波数検出電圧Vcapは、ランプアンドホールド回路31の出力端子側のノードに生成されるものである。

【0051】

ランプアンドホールド回路31は、電荷リセット信号INITBがイネーブル状態(例えば、ロウレベル)となると、PMOSトランジスタP4をオンする。そして、ランプアンドホールド回路31は、周波数設定コンデンサCvに電源電圧に相当する電荷を蓄積することで、周波数設定コンデンサCvに蓄積される電荷のリセットを行う。また、ランプアンドホールド回路31は、電荷リセット信号INITBをディスイネーブル状態(例えば、ハイレベル)かつランプ制御信号RAMPがイネーブル状態(例えば、ハイレベル)となると、PMOSトランジスタP4をオフし、かつ、NMOSトランジスタN5をオンする。これにより、ランプアンドホールド回路31は、充放電電流によって周波数設定コンデンサCvから電荷の引き抜きを行う。また、ランプアンドホールド回路31は、ランプ制御信号RAMPをディスイネーブル状態(例えば、ロウレベル)、かつ、ホールド制御信号HOLDをイネーブル状態(例えば、ハイレベル)となると、NMOSトランジスタN5をオフし、かつ、NMOSトランジスタN6をオンする。これにより、ランプアンドホールド回路31は、周波数設定コンデンサCvからの放電を停止し、周波数設定コンデンサCvに蓄積された電荷により生じた周波数検出電圧Vcapを維持する。

【0052】

差動増幅器40は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流Icpを連続的に可変してフィルタコンデンサに出力する。より具体的には、差動増幅器40は、増幅部41とスイッチ回路42を有する。そして、増幅部41の反転入力端子には周波数検出電圧Vcapが入力され、非反転入力端子に基準電圧Vresが入力される。増幅部41は、例えば、トランスコンダクタンス増幅器であって、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じた電流値を有する発振周波数設定電流Icpを出力する。なお、本実施の形態では、基準電圧Vresとして、周波数設定抵抗Rが接続されるNMOSトランジスタN3のゲート電圧を用いる。

【0053】

スイッチ回路42は、増幅部41の出力端子とフィルタコンデンサCpumpとの間に設けられ、タイミング制御信号に含まれるポンプ制御信号PULSEに応じて導通状態が切り替えられる。より具体的には、スイッチ回路42は、ポンプ制御信号PULSEがイネーブル状態(例えば、ハイレベル)のときに導通状態となり、ディスイネーブル状態(例えば、ロウレベル)のときに遮断状態となる。

【0054】

ここで、差動増幅器40の回路について詳細な説明を行う。差動増幅器40の詳細な回路図を図8に示す。図8に示すように、差動増幅器40は、増幅部41、スイッチ回路42を有する。

【0055】

差動増幅器40は、フォールデッドカスコードアンプを構成する。より具体的には、差動増幅器40は、NMOSトランジスタN7〜N13、PMOSトランジスタP5〜P8を有する。NMOSトランジスタN7は、ソースが接地端子に接続され、ゲートに定電圧Vbn1が入力される。NMOSトランジスタN8、N9は、差動対を構成し、NMOSトランジスタN7が出力する動作電流に基づき動作する。NMOSトランジスタN8のゲートには基準電圧Vresが入力され、NMOSトランジスタN9のゲートには周波数検出電圧Vcapが入力される。そして、NMOSトランジスタN8のドレインはPMOSトランジスタP5のドレインに接続され、NMOSトランジスタN9のドレインはPMOSトランジスタP6のドレインに接続される。

【0056】

PMOSトランジスタP5のソース及びPMOSトランジスタP6のソースは電源端子VDDに接続される。また、PMOSトランジスタP5のゲートとPMOSトランジスタP6のゲートには定電圧Vbp1が入力される。PMOSトランジスタP7のソースはPMOSトランジスタP5のドレインに接続され、PMOSトランジスタP8のソースは、PMOSトランジスタP6のドレインに接続される。PMOSトランジスタP7のゲートとPMOSトランジスタP8のゲートには定電圧Vbp2が入力される。そして、PMOSトランジスタP8のドレインは、発振周波数設定電流Icpの流出側出力端子となる。

【0057】

NMOSトランジスタN10のソース及びNMOSトランジスタN11のソースは接地端子に接続される。また、NMOSトランジスタN10のゲートとNMOSトランジスタN11のゲートは共通接続される。NMOSトランジスタN12のソースはNMOSトランジスタN10のドレインと接続され、NMOSトランジスタN13のソースはNMOSトランジスタN11のドレインと接続される。NMOSトランジスタN12のゲートとNMOSトランジスタN13のゲートには定電圧Vbn2が入力される。NMOSトランジスタN12のドレインは、PMOSトランジスタP7のドレインと接続されると共にNMOSトランジスタN10、N11のゲートと接続される。そして、NMOSトランジスタN13のドレインは、発振周波数設定電流Icpの流入側出力端子となる。

【0058】

スイッチ回路42は、第1のスイッチ回路43と第2のスイッチ回路44を有する。第1のスイッチ回路43は、増幅部41の出力端子とフィルタコンデンサCpumpとの導通状態をポンプ制御信号PULSEに応じて切り替える。第1のスイッチ回路43は、PMOSトランジスタP9、NMOSトランジスタN14を有する。PMOSトランジスタP9の一方の端子とNMOSトランジスタN14の一方の端子は、フィルタコンデンサCpump及び電圧制御発振器50が接続されるノードに接続される。また、PMOSトランジスタP9の他方の端子は、PMOSトランジスタP8のドレイン(例えば、流出側出力端子)に接続される。一方、NMOSトランジスタN14の他方の端子は、NMOSトランジスタN13のドレイン(例えば、流入側出力端子)に接続される。そして、PMOSトランジスタP9のゲートには、後述するインバータ46で反転されたポンプ制御信号PULSEが入力される。NMOSトランジスタN14のゲートには、ポンプ制御信号PULSEが入力される。

【0059】

第2のスイッチ回路44は、第1のスイッチ回路43が遮断状態である期間に発振周波数制御電圧Vcpを増幅部41の出力端子に与え、増幅部41の出力端子から入出力される電流を打ち消す電流Icp0を出力する。第2のスイッチ回路44は、PMOSトランジスタP10、NMOSトランジスタN15、バッファ回路45、インバータ46を有する。PMOSトランジスタP10の一方の端子とNMOSトランジスタN15の一方の端子は、バッファ回路45の出力端子に接続される。また、PMOSトランジスタP10の他方の端子は、PMOSトランジスタP8のドレイン(例えば、流出側出力端子)に接続される。一方、NMOSトランジスタN15の他方の端子は、NMOSトランジスタN13のドレイン(例えば、流入側出力端子)に接続される。そして、PMOSトランジスタP10のゲートには、ポンプ制御信号PULSEが入力される。NMOSトランジスタN15のゲートには、インバータ46で反転されたポンプ制御信号PULSEが入力される。バッファ回路45は、正転入力端子にフィルタコンデンサCpumpが入力され、反転入力端子がバッファ回路45の出力と接続される。

【0060】

ここで、差動増幅器40は、ポンプ制御信号PULSEがイネーブル状態(例えば、ハイレベル)の場合、第1のスイッチ回路43が導通状態となり、フィルタコンデンサCpumpに発振周波数設定電流Icpを出力する。また、ポンプ制御信号PULSEがイネーブル状態の場合、第2のスイッチ回路44は、増幅部41の出力端子への電流Icp0の伝達を遮断する。

【0061】

一方、差動増幅器40は、ポンプ制御信号PULSEがディスイネーブル状態(例えば、ロウレベル)の場合、第1のスイッチ回路43が遮断状態となり、第2のスイッチ回路が電流Icp0を増幅部41の出力端子に与える。これにより、差動増幅器40の出力端子はフィルタコンデンサCpump側からはハイインピーダンス状態となる。このとき、差動増幅器40では、NMOSトランジスタN13のドレインと接地端子との間に寄生容量Conが形成され、PMOSトランジスタP8のドレインと電源端子VDDとの間に寄生容量Copが形成される。寄生容量Con、Copにより、第1のスイッチ回路43が遮断状態から導通状態となった場合、発振周波数制御電圧Vcpに電圧変動Vcp0が生じる。この電圧変動Vcp0は、PMOSトランジスタN8のドレインの電圧をVoutp、NMOSトランジスタN13のドレインの電圧をVoutnとすると、(1)式で表される。

Vcp0=((Voutp−Vcp)Cop−

(Voutn−Vcp)Con)/Cpump・・・(1)

【0062】

(1)式より、Vcp=Voutn=Voutpであれば、電圧変動Vcp0は生じないことがわかる。そこで、差動増幅器40では、第2のスイッチ回路44が第1のスイッチ回路43が遮断状態の期間にバッファ回路45により増幅部41が出力する電流を吸収し、かつ、増幅部41の出力端子に発振周波数制御電圧Vcpを与える。これにより、差動増幅器40では、第1のスイッチ回路43が遮断状態においてVcp=Voutn=Voutpとの条件を満たし、電圧変動Vcp0を抑制する。なお、このような電圧変動をチャージシェアと称す。本発明にかかる発振回路3では、発振周波数制御電圧Vcpの電圧レベルにより出力信号Foutの発振周波数が決定されるため、発振周波数制御電圧Vcpの電圧変動を抑制することで出力信号Foutのジッタが低減される。

【0063】

フィルタコンデンサCpumpは、発振周波数設定電流Icpに基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成する。フィルタコンデンサCpumpは、差動増幅器40の出力端子と電圧制御発振器50の入力端子とを接続するノードに一端が接続され、他端が接地端子に接続される。つまり、フィルタコンデンサCpumpは、差動増幅器40が出力する発振周波数設定電流Icpに応じて発振周波数制御電圧Vcpを生成し、発振周波数制御電圧Vcpを電圧制御発振器50に与える。

【0064】

電圧制御発振器50は、発振周波数制御電圧Vcpの電圧レベルに応じて出力信号Foutの発振周波数を制御する。

【0065】

制御回路60は、出力信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する。このタイミング制御信号には、電荷リセット信号INITB、ランプ制御信号RAMP、ホールド制御信号HOLD、ポンプ制御信号PULSEが含まれる。制御回路60は、出力信号Foutを分周した分周信号を生成し、当該分周信号のクロック数をカウントしたカウント値に基づき上記制御信号の論理レベルを切り替える。タイミング制御信号の論理レベルの切り替えタイミングの詳細は、後述する。

【0066】

続いて、図9に周波数検出回路30と制御回路60の動作を示すタイミングチャートを示す。そして、図9を参照して制御回路60がタイミング制御信号の論理レベルの切り替えタイミング及び周波数検出回路30の動作について説明する。

【0067】

図9に示すように、制御回路60は、出力信号Foutを分周して分周信号FDを生成する。図9に示す例では、分周信号FDは、出力信号Foutを2分周して生成する。また、制御回路60は、分周信号FDのクロック数をカウントしてカウント値COUNTを生成する。図9に示す例では、カウント値COUNTは2ビットの値であって0から3の値となる。そして、制御回路60は、カウント値COUNTの値に応じてタイミング制御信号の論理レベルを切り替える。

【0068】

具体的には、カウント値が0であった場合、制御回路60は、電荷リセット信号INITBをロウレベル(イネーブル状態)とし、ランプ制御信号RAMPをロウレベル(ディスイネーブル状態)とし、ホールド制御信号HOLDをハイレベル(イネーブル状態)とし、ポンプ制御信号PULSEをロウレベル(ディスイネーブル状態)とする。カウント値が0である期間を以下ではリセット期間Tinitと称す。

【0069】

カウント値が1であった場合、制御回路60は、電荷リセット信号INITBをハイレベル(ディスイネーブル状態)とし、ランプ制御信号RAMPをハイレベル(イネーブル状態)とし、ホールド制御信号HOLDをロウレベル(ディスイネーブル状態)とし、ポンプ制御信号PULSEをロウレベル(ディスイネーブル状態)とする。カウント値が1である期間を以下ではランプ期間Trampと称す。

【0070】

カウント値が2であった場合、制御回路60は、電荷リセット信号INITBをハイレベル(ディスイネーブル状態)とし、ランプ制御信号RAMPをロウレベル(ディスイネーブル状態)とし、ホールド制御信号HOLDをハイレベル(イネーブル状態)とし、ポンプ制御信号PULSEをロウレベル(ディスイネーブル状態)とする。カウント値が2である期間を以下ではホールド期間Tholdと称す。

【0071】

カウント値が3であった場合、制御回路60は、電荷リセット信号INITBをハイレベル(ディスイネーブル状態)とし、ランプ制御信号RAMPをロウレベル(ディスイネーブル状態)とし、ホールド制御信号HOLDをハイレベル(イネーブル状態)とし、ポンプ制御信号PULSEをハイレベル(イネーブル状態)とする。カウント値が3である期間を以下ではポンプ期間Tpumpと称す。

【0072】

続いて、周波数検出回路30の動作について説明する。周波数検出回路30は、リセット期間Tinitにおいて、電荷リセット信号INITBに基づきPMOSトランジスタP4を導通させることで周波数設定コンデンサCvに蓄積されている電荷を電源電圧に応じた電荷量にリセットする。これにより、周波数検出電圧Vcapは電源電圧とほぼ等しい電圧となる。このとき、NMOSトランジスタN5はランプ制御信号RAMPに応じてオフし、NMOSトランジスタN6はホールド制御信号HOLDに応じてオンする。

【0073】

そして、ランプ期間Trampにおいて、周波数検出回路30は、電荷リセット信号INITBに応じてPMOSトランジスタP4をオフし、ランプ制御信号RAMPに応じてNMOSトランジスタN5をオンし、ホールド制御信号HOLDに応じてNMOSトランジスタN6をオフする。つまり、周波数検出回路30は、ランプ期間Trampにおいて、充放電電流に基づき周波数設定コンデンサCvから電荷の引き抜きを行う。これにより、周波数検出電圧Vcapの電圧レベルは徐々に低下する。周波数検出電圧Vcapが低下する傾きは充放電電流の大きさ及び周波数設定コンデンサCvの容量値により決定される。また、ランプ期間Trampでは、周波数検出電圧Vcapの電圧レベルが低下するが、電圧低下速度は一定である。そのため、ランプ期間Trampにおける周波数検出電圧Vcapの電圧低下量dVcapは、ランプ期間Trampの長さ(出力信号Foutの発振周波数)によって決まる。

【0074】

そして、ホールド期間Tholdにおいて、周波数検出回路30は、電荷リセット信号INITBに応じてPMOSトランジスタP4をオフし、ランプ制御信号RAMPに応じてNMOSトランジスタN5をオフし、ホールド制御信号HOLDに応じてNMOSトランジスタN6をオンする。つまり、周波数検出回路30は、ホールド期間Tholdにおいて、周波数設定コンデンサCvが接続されるノードをハイインピーダンス状態とし、周波数設定コンデンサCvにより生成される周波数検出電圧Vcapの電圧レベルを維持する。

【0075】

そして、ポンプ期間Tpumpにおいては、差動増幅器40によるフィルタコンデンサCpumpへの発振周波数設定電流Icpの供給が行われる。このとき、周波数検出回路30に与えられる電荷リセット信号INITB、ランプ制御信号RAMP、ホールド制御信号HOLDはホールド期間Tholdとポンプ期間Tpumpとで同じである。そのため、ポンプ期間Tpumpにおいて周波数検出回路30により周波数検出電圧Vcapの電圧レベルが変動することはない。

【0076】

続いて、差動増幅器40の動作について説明する。図10に差動増幅器40の動作を示すタイミングチャートを示す。図10に示す例では、タイミングT0からT2の期間が図9で示した1組のリセット期間Tinit、ランプ期間Tramp、ホールド期間Thold、ポンプ期間Tpumpに相当する。そして、タイミングT1からT2の期間が図9で示したポンプ期間に相当する。

【0077】

差動増幅器40は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて電流Icpを出力する。しかし、タイミングT0からT1の期間では、ポンプ制御信号PULSEがディスイネーブル状態(ロウレベル)であるため、第1のスイッチ回路43が遮断状態となり、周波数検出電圧Vcapは一定に保たれる。一方、増幅部41は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて電流を出力する。しかし、この電流は、第2のスイッチ回路44がこの電流を打ち消す電流Icp0を出力し、増幅部41の出力電圧をVcpとする。

【0078】

そして、タイミングT1においてポンプ制御信号PULSEがイネーブル状態(例えば、ハイレベル)となると、第1のスイッチ回路43が導通状態となり、第2のスイッチ回路44が遮断状態となる。これにより、差動増幅器40は、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて電流IcpをフィルタコンデンサCpumpに出力し、発振周波数制御電圧Vcpが変動する。図10に示す例では、発振周波数設定電流Icpが正の極性(フィルタコンデンサCpumpに充電を行う方向)で出力されるため、周波数検出電圧Vcapは、タイミングT1からT2で上昇する。

【0079】

続いて、実施の形態3にかかる発振回路3の全体の動作について説明する。実施の形態1にかかる発振回路3の動作を示すタイミングチャートを図11に示す。図11に示すタイミングチャートでは、周波数検出電圧Vcap、発振周波数制御電圧Vcp及び出力信号Foutの変動のみを示した。また、図11では、時間軸(横軸)の原点において発振回路3の動作が開始されるものとする。

【0080】

図11に示すように、発振回路3は、期間TM1からTM7の期間毎に発振周波数制御電圧Vcpを上昇させる。期間TM1からTM7の各期間には、図9に示すリセット期間Tinit、ランプ期間Tramp、ホールド期間Thold、ポンプ期間Tpumpが一組含まれる。また、出力信号Foutの周波数が期間毎に上昇するため、期間TM1から期間TM7は、徐々に短くなる。これはタイミング制御信号が出力信号Foutの周期に基づき生成されるためである。なお、図11に示す期間TM11からTM17がポンプ期間Tpumpに対応する期間となる。

【0081】

そして、期間TM7が経過した後は、周波数検出電圧Vcapの低レベル側電圧が基準電圧Vresとほぼ同じになる。これにより、発振回路3では、差動増幅器40が出力する発振周波数設定電流Icpがほぼ0となる。そのため、周波数検出電圧Vcapの低レベル側電圧が基準電圧Vresとほぼ同じになった後はその状態が維持される。また、周波数検出電圧Vcapが一定の電圧に保たれるため、出力信号Foutの発振周波数も一定に保たれる。つまり、発振回路3では、出力信号Foutの発振周波数が目標値に達した後は出力信号Foutにジッタは生じない。

【0082】

上記説明より、実施の形態3にかかる発振回路3では、フィルタコンデンサCpumpは、発振周波数設定電流Icpに応じて発振周波数制御電圧Vcpを生成する。このとき、発振回路3では、差動増幅器40が周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて連続的に値が変化する発振周波数設定電流Icpを出力する。つまり、周波数検出電圧Vcapと基準電圧Vresとの電圧差があれば発振周波数設定電流Icpは、当該電圧差に応じた大きさを有し、周波数検出電圧Vcapと基準電圧Vresとの電圧差がなければ発振周波数設定電流Icpは、実質的に0となる。これにより、発振回路3では、出力信号Foutの周波数が目標値と一致する状態(例えば、周波数検出電圧Vcapが基準電圧Vresと一致した状態)では、ポンプ制御信号PULSEがイネーブル状態となっても発振周波数制御電圧Vcpに変動が生じない。これにより、発振回路3では、出力信号Foutの発振周波数が目標値と一致した後に、発振周波数制御電圧Vcpの電圧値が変動することがなく、発振周波数制御電圧Vcpの電圧値に応じて電圧制御発振器50が決定する出力信号Foutの発振周波数もずれることがない。つまり、発振回路3では、出力信号Foutのジッタを低減することができる。

【0083】

このように、発振回路3では、発振周波数制御電圧Vcpが差動増幅器40により高精度に生成される。そのため、周波数設定コンデンサCvの容量値と充放電される電流値とにより決定される時定数のずれが出力信号Foutの周波数ずれ又はジッタに大きく影響する。このような用途において、本発明にかかる可変容量素子を用いることで、発振回路3の出力信号Foutの発振周波数の精度を高めることができる。また、発振回路3では、周波数設定コンデンサCvの容量値を容量切替信号CSELにより切り替えることができる。これにより、発振回路3の汎用性を高めることができる。

【0084】

また、実施の形態3にかかる発振回路3では、差動増幅器40がスイッチ回路42を有する。このスイッチ回路42は、差動増幅器40の入力信号の差電圧増幅結果を反映する期間(例えば、ポンプ期間Tpump)以外は遮断状態に制御される。発振回路3では、リセット期間Tinit、ランプ期間Trampにおいて周波数検出電圧Vcapが出力信号Foutを反映した電圧とずれた電圧値となる。しかし、スイッチ回路42がポンプ期間以外は遮断状態に制御されるため、リセット期間Tinit及びランプ期間Trampにおける周波数検出電圧Vcapのずれが発振周波数に反映されることを防ぐことができる。これにより、発振回路3では、いずれの期間においても発振周波数を安定化させることができる。

【0085】

また、実施の形態3にかかる発振回路3では、スイッチ回路42が第1のスイッチ回路43及び第2のスイッチ回路44を有する。そして、第1のスイッチ回路43が遮断状態の期間においても増幅部41の出力端子に第2のスイッチ回路44を動作させる。第2のスイッチ回路44は、周波数検出電圧Vcapと基準電圧Vresとの電圧差が生じるリセット期間Tinit及びランプ期間Trampにおいても、増幅部41が出力する電流を吸収し、増幅部41の出力端子を発振周波数制御電圧Vcpに維持する。これにより、第1のスイッチ回路43が遮断状態から導通状態に切り替わったタイミングで生じるチャージシェアに起因する発振周波数制御電圧Vcpの電位変動を抑制することができる。つまり、実施の形態3にかかる発振回路3では、スイッチ回路42を設けたことに起因するジッタを抑制することができる。

【0086】

実施の形態3にかかる発振回路3では、基準電圧VresとしてNMOSトランジスタN3のダイオード電圧を用い、充放電電流の電流値を電源電圧と当該ダイオード電圧との差電圧を周波数設定抵抗Rで割って決定する。ダイオード電圧が低くなると、充放電電流の電流値が大きくなり、ランプ期間Trampにおける周波数検出電圧Vcapの傾きが大きくなる。充放電電流の電流値Iresは、周波数設定抵抗R、基準電圧Vres、電源電圧VDDとすると(2)式で表される。

Ires=(VDD−Vres)/R・・・(2)

ホールド期間Tholdにおける周波数検出電圧をVcap(HOLD)とすると、Vcap(HOLD)は、充放電電流の電流値をIres、周波数設定コンデンサCの容量値をC、ランプ期間の長さをTrampとすると(3)式で表される。

Vcap(HOLD)=VDD−(Ires・Tramp)/C・・・(3)

ここで、実施の形態1にかかる発振回路3ではVcap(HOLD)=Vresとなるようにフィードバックループにより、周波数が補正される。そこで、(2)式、(3)式からランプ期間Tramp及び出力信号Foutの周波数を求めると(4)式となる。なお、(4)式においてNは、制御回路60内の分周回数である。

Fout=N/Tramp=N/RC・・・(4)

つまり、実施の形態1にかかる発振回路3では、電源電圧、NMOSのトランジスタN3のダイオード電圧が相殺され周波数設定抵抗R、周波数設定コンデンサC、分周回数Nのみの関数となる。

【0087】

実施の形態4

可変容量素子1、2は、時定数回路の時定数を高精度に設定する用途に利用可能である。そこで、時定数回路を有する回路例として、実施の形態4では、可変容量素子1、2を有するパルス幅変調回路について説明する。そこで、実施の形態4にかかるパルス幅変調回路4の回路図を図12に示す。図12に示すようにパルス幅変調回路4は、インバータ70、71、可変容量素子Cv1を有する。パルス幅変調回路4においては、可変容量素子Cvとインバータ70により時定数回路を構成する。この可変容量素子Cv1は、実施の形態1、2において説明した可変容量素子1、2である。そのため、可変容量素子Cv1には、容量切替信号CSELが入力される。また、可変容量素子Cv1には、電荷リセット信号INITBとして入力信号Vinが入力される。

【0088】

インバータ70は、PMOSトランジスタP11、NMOSトランジスタN16、電流源Is1を有する。PMOSトランジスタP11は、ソースに電源電圧VDDが供給され、ゲートに入力信号Vinが入力され、ドレインがNMOSトランジスタN16のドレインに接続される。NMOSトランジスタN16は、ソースが電流源Is1の第1の端子に接続され、ゲートに入力信号Vinが入力され、ドレインがPMOSトランジスタP11のドレインに接続される。PMOSトランジスタP11のドレインとNMOSトランジスタN16のドレインとが接続されるノードは、インバータ70の出力端子となる。そして、インバータ70は、出力端子から中間出力信号Vd1を出力する。電流源Is1は、NMOSトランジスタN16のソースと接地端子との間に接続される。

【0089】

インバータ71は、PMOSトランジスタP12、NMOSトランジスタN17を有する。PMOSトランジスタP12は、ソースに電源電圧VDDが供給され、ゲートに第1の中間出力信号Vd1が入力され、ドレインがNMOSトランジスタN17のドレインに接続される。NMOSトランジスタN17は、ソースに接地電圧VSSが供給され、ゲートに第1の中間出力信号Vd1が入力され、ドレインがPMOSトランジスタP12のドレインに接続される。PMOSトランジスタP12のドレインとNMOSトランジスタN17のドレインとが接続されるノードは、インバータ71の出力端子となる。なお、インバータ71から出力される信号がパルス幅変調回路4の出力信号Voutとなる。

【0090】

続いて、パルス幅変調回路4の動作について説明する。そこで、パルス幅変調回路4の動作を示すタイミングチャートを図13に示す。なお、以下の説明では、可変容量素子Cv1として可変容量素子1を用いる。

【0091】

パルス幅変調回路4は、容量切替信号CSELの論理レベルによって、出力信号Voutのパルス幅を変更する。より具体的には、容量切替信号CSELがディスイネーブル状態(例えば、ロウレベル)の場合、可変容量素子Cv1の容量値は、コンデンサC1のみによって設定される。一方、容量切替信号CSELがイネーブル状態(例えば、ハイレベル)の場合、可変容量素子Cv1の容量値は、コンデンサC1、C2の容量値の合計値となる。

【0092】

そこで、まず、容量切替信号CSELがディスイネーブル状態の期間の動作について説明する。図13に示すように、パルス幅変調回路4は、入力信号Vinがロウレベル(例えば、接地電圧VSS)の期間に中間出力信号Vd1をハイレベル(例えば、電源電圧VDD)とする。これにより、可変容量素子Cv1のコンデンサC1には、電源電圧VDDに対応した電荷が蓄積される。一方、入力信号Vinがロウレベルとなることで可変容量素子Cv1の誤差補正回路10は容量切替ノードNDaに電源電圧VDDを与え、コンデンサC2に蓄積されている電荷をほぼゼロにする。また、中間出力信号Vd1がハイレベルの期間は、出力信号Voutはロウレベルとなる。

【0093】

そして、入力信号Vinがロウレベルからハイレベルに切り替わると、NMOSトランジスタN16が導通状態となり、電流源Is1がコンデンサC1から電荷を引き抜く。そして、この電荷引き抜き動作により中間出力信号Vd1の電圧レベルが徐々に低下する。そして、中間出力信号Vd1の電圧レベルがインバータ71の閾値電圧Vthを下回ると出力信号Voutがハイレベルに切り替わる。このとき、中間出力信号Vd1は、可変容量素子Cv1により立ち下がりが立ち上がりよりも緩やかになる。そのため、出力信号Voutは、立ち上がりが入力信号Vinの立ち上がりよりも時間dly1だけ遅延する。

【0094】

続いて、容量切替信号CSELがイネーブル状態の期間の動作について説明する。容量切替信号CSELがイネーブル状態の期間では、可変容量素子Cv1の容量値が容量切替信号CSELがディスイネーブル状態の期間よりも大きくなる。そのため、容量切替信号CSELがイネーブル状態の期間における中間出力信号Vd1の立ち下がり速度は、容量切替信号CSELがディスイネーブル状態の期間よりも遅くなる。そして、この期間における出力信号Voutの立ち上がりは、入力信号Vinの立ち上がりから時間dly2だけ遅延する。なお、この時間dly2は、時間dly1よりも大きい。

【0095】

上記説明より、パルス幅変調回路4は、可変容量素子Cv1の容量値の大きさによって、出力信号Voutの立ち上がりを入力信号Vinの立ち上がりよりも遅くする。これにより、パルス幅変調回路4は、出力信号Voutのパルス幅を入力信号Vinのパルス幅異なる幅に設定することができる。また、パルス幅変調回路4は、可変容量素子Cv1の容量値を切り替えることで出力信号Voutのパルス幅を変更することができる。このようなパルス幅変調回路4では、可変容量素子Cv1の容量値の精度がパルス幅の値に影響を及ぼす。そのため、パルス幅の精度を向上させるためには、容量値の精度を向上させる必要がある。従って、本発明にかかる可変容量素子1、2は、このような用途において有効である。

【0096】

実施の形態5

時定数回路を有する回路例として、実施の形態5では、可変容量素子1、2を利用する遅延回路について説明する。そこで、実施の形態5にかかる遅延回路5の回路図を図14に示す。図14に示すように遅延回路5は、インバータ70〜73、可変容量素子Cv1、Cv2を有する。遅延回路5においては、インバータ70と可変容量素子Cv1により第1の時定数回路を構成し、インバータ72と可変容量素子Cv2により第2の時定数回路を構成する。なお、インバータ70、71、可変容量素子Cv1は、実施の形態4にかかるパルス幅変調回路4のものと同じであるためここでは説明を省略する。また、以下の説明では、実施の形態4における中間出力信号Vd1を第1の中間出力信号Vd1と称し、出力信号Voutを第2の中間出力信号Vd2と称す。

【0097】

インバータ72は、PMOSトランジスタP13、NMOSトランジスタN18、電流源Is2を有する。PMOSトランジスタP13は、ソースに電流源Is2が接続され、ゲートに第2の中間出力信号Vd2が入力され、ドレインがNMOSトランジスタN18のドレインに接続される。NMOSトランジスタN18は、ソースに接地電圧VSSが供給され、ゲートに第2の中間出力信号Vd2が入力され、ドレインがPMOSトランジスタP13のドレインに接続される。PMOSトランジスタP13のドレインとNMOSトランジスタN18のドレインとが接続されるノードは、インバータ72の出力端子となる。そして、インバータ72は、出力端子から第3の中間出力信号Vd3を出力する。電流源Is2は、PMOSトランジスタN13のソースと電源端子との間に接続される。

【0098】

インバータ73は、PMOSトランジスタP14、NMOSトランジスタN19を有する。PMOSトランジスタP14は、ソースに電源電圧VDDが供給され、ゲートに第3の中間出力信号Vd3が入力され、ドレインがNMOSトランジスタN17のドレインに接続される。NMOSトランジスタN17は、ソースに接地電圧VSSが供給され、ゲートに第3の中間出力信号Vd3が入力され、ドレインがPMOSトランジスタP14のドレインに接続される。PMOSトランジスタP14のドレインとNMOSトランジスタN19のドレインとが接続されるノードは、インバータ73の出力端子となる。なお、インバータ73から出力される信号が遅延回路5の出力信号Voutとなる。

【0099】

可変容量素子Cv2は、インバータ72の出力端子と接地端子との間に設けられる。この可変容量素子Cv2は、リセット電圧として接地電圧VSSが与えられる。そのため、回路構成が可変容量素子1とは異なる。そこで、可変容量素子Cv2の回路図を図15に示す。

【0100】

図15に示すように、可変容量素子Cv2は、第1の容量素子(例えば、コンデンサC1)、第2の容量素子(例えば、コンデンサC2)、容量選択スイッチ(例えば、NMOSトランジスタN20)誤差補正回路11を有する。

【0101】

コンデンサC1は、第1の電源端子(例えば、接地電圧VSSを供給する接地端子)と出力端子CTOPとの間に接続される。ここで、出力端子CTOPは、本実施の形態では、インバータ72の出力端子に接続される。コンデンサC2は、コンデンサC1と並列に接続され、かつ、NMOSトランジスタN20と直列に接続される。NMOSトランジスタN20は、容量切替信号CSELに応じて導通状態が切り替えられる。NMOSトランジスタN20は、ソースが接地端子に接続され、ドレインがコンデンサC2に接続され、ゲートに容量切替信号CSELが入力される。なお、コンデンサC2は、第1の端子が出力端子CTOPに接続され、第2の端子がNMOSトランジスタN20のドレインに接続される。ここで、以下の説明では、コンデンサC2とNMSOトランジスタN20とを接続するノードを容量切替ノードNDcと称す。

【0102】

誤差補正回路11は、NMOSトランジスタN20が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITB(本実施の形態では、第2の中間出力信号Vd2)に応じて、容量切替ノードNDcの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する。誤差補正回路11は、NMOSトランジスタN21、N22、インバータINV2を有する。NMOSトランジスタN22は、ソースに電源電圧VDDが供給され、ゲートにインバータINV2を介して容量切替信号CSELの反転信号が入力される。また、NMOSトランジスタN22のドレインは、NMOSトランジスタN21のソースと接続される。NMOSトランジスタN21は、ゲートに電荷リセット信号INITBが入力され、ドレインが容量切替ノードNDcに接続される。

【0103】

可変容量素子Cv2は、コンデンサC2が非選択の状態において、コンデンサC1の電荷をリセットする期間に、コンデンサC2の両端電圧をほぼ0Vとし、コンデンサC2の電荷をリセットする。つまり、基本的な動作は、可変容量素子1と同じである。

【0104】

続いて、遅延回路5の動作について説明する。遅延回路5の動作を示すタイミングチャートを図16に示す。図16に示すタイミングチャートの説明では、容量切替信号CSELをディスイネーブル状態(例えば、ロウレベル)で固定するものとする。

【0105】

図16に示すように、遅延回路5では、インバータ70と可変容量素子Cv1により、第1の中間出力信号Vd1の立ち下がりを遅延させる。これにより、遅延回路5は、第2の中間出力信号Vd2の立ち上がりエッジを入力信号Vinの立ち上がりエッジを遅延させる。また、遅延回路5は、インバータ72と可変容量素子Cv2により第3の中間出力信号Vd3の立ち上がりを遅延させる。これにより、遅延回路5は、出力信号Voutの立ち下がりエッジを第2の中間出力信号Vd2の立ち下がりエッジを遅延させる。つまり、遅延回路5は、可変容量素子Cv1、Cv2の容量値に応じて出力信号Voutを入力信号Vinから遅延させることができる。

【0106】

上記説明より、遅延回路5において、容量値の精度が高い本発明にかかる可変容量素子Cv1、Cv2を用いることで、遅延時間の設定精度を向上させることができる。

【0107】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0108】

1、2、Cv、Cv1、Cv2 可変容量素子

可変容量素子

3 発振回路

4 パルス幅変調回路

5 遅延回路

10、11 誤差補正回路

20 容量選択スイッチ

30 周波数検出回路

31 ランプアンドホールド回路

40 差動増幅器

41 増幅部

42 スイッチ回路

43 第1のスイッチ回路

44 第2のスイッチ回路

45 バッファ回路

46 インバータ回路

50 発振器

60 制御回路

C1 コンデンサ

C2 コンデンサ

CTOP 出力端子

CSEL 容量切替信号

Cpump フィルタコンデンサ

INITB 電荷リセット信号

RAMP ランプ制御信号

HOLD ホールド制御回路

PULSE ポンプ制御信号

Tinit リセット期間

Tramp ランプ期間

Thold ホールド期間

Tpump ポンプ期間

VSS 接地電圧

VDD 電源電圧

Is 電流源

R 周波数設定抵抗

RTr リセットトランジスタ

LTr 充放電制御トランジスタ

N1〜N20 NMOSトランジスタ

P1〜P19 PMOSトランジスタ

【特許請求の範囲】

【請求項1】

第1の電源端子と出力端子との間に接続される第1の容量素子と、

容量切替信号に応じて導通状態が切り替えられる容量選択スイッチと、

前記第1の容量素子と並列に接続され、かつ、前記容量選択スイッチと直列に接続される第2の容量素子と、

前記容量選択スイッチが遮断状態とされる状態において、前記出力端子をリセット電圧にリセットする電荷リセット信号に応じて、前記第2の容量素子と前記容量選択スイッチとを接続する容量切替ノードの電圧と前記出力端子の電圧とを実質的に同じ電圧に設定する誤差補正回路と、

を有する可変容量素子。

【請求項2】

前記誤差補正回路は、

前記電荷リセット信号に応じて第2の電源端子から供給されるリセット電圧を前記容量切替ノードに印加する第1のスイッチ回路と、

前記第1のスイッチ回路と直列に接続され、導通状態が前記容量選択スイッチと排他的に制御され前記第1のスイッチ回路の有効状態と無効状態とを切り替える第2のスイッチ回路と、

を有する請求項1に記載の可変容量素子。

【請求項3】

前記第2の容量素子は、第1の端子が前記出力端子に接続され、第2の端子が前記容量切替ノードに接続され、

前記容量選択スイッチは、第1の端子が前記容量切替ノードに接続され、第2の端子が前記第1の電源端子に接続される請求項1又は2に記載の可変容量素子。

【請求項4】

前記第2の容量素子は、第1の端子が前記容量切替ノードに接続され、第2の端子が前記第1の電源端子に接続され、

前記容量選択スイッチは、第1の端子が前記出力端子に接続され、第2の端子が前記容量切替ノードに接続される請求項1又は2に記載の可変容量素子。

【請求項5】

前記出力端子と第2の電源端子との間に接続され、前記電荷リセット信号に応じて前記出力端子に前記第2の電源端子から供給される前記リセット電圧を与えるリセット回路を有する請求項1乃至4のいずれか1項に記載の可変容量素子。

【請求項6】

イネーブル状態が前記電荷リセット信号と排他的に制御される充放電制御信号に応じて前記第1の容量素子に充電又は放電を行う電流源を有する請求項1乃至6のいずれか1項に記載の可変容量素子。

【請求項7】

前記可変容量素子は、抵抗により設定される定電流と容量素子の容量値とにより発振周波数が設定される発振回路における前記容量素子として用いられる請求項1乃至6のいずれか1項に記載の可変容量素子。

【請求項8】

前記発振回路は、

発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧を生成するフィルタコンデンサと、

前記発振周波数制御電圧に応じて出力する発振信号の周波数を変動させる発振器と、

前記発振信号の周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路と、

前記可変容量素子を有し、前記タイミング制御信号に基づき前記発振信号の周期の長さと前記可変容量素子への充放電電流量とに応じて電圧レベルが変化する周波数検出電圧を生成する周波数検出回路と、

前記周波数検出電圧と基準電圧との電圧差に応じて前記発振周波数設定電流を連続的に可変して前記フィルタコンデンサに出力する差動増幅器と、を有する請求項7に記載の可変容量素子。

【請求項9】

前記可変容量素子は、入力信号に対する出力信号の遅延時間を設定する時定数回路に用いられる請求項1乃至6のいずれか1項に記載の可変容量素子。

【請求項1】

第1の電源端子と出力端子との間に接続される第1の容量素子と、

容量切替信号に応じて導通状態が切り替えられる容量選択スイッチと、

前記第1の容量素子と並列に接続され、かつ、前記容量選択スイッチと直列に接続される第2の容量素子と、

前記容量選択スイッチが遮断状態とされる状態において、前記出力端子をリセット電圧にリセットする電荷リセット信号に応じて、前記第2の容量素子と前記容量選択スイッチとを接続する容量切替ノードの電圧と前記出力端子の電圧とを実質的に同じ電圧に設定する誤差補正回路と、

を有する可変容量素子。

【請求項2】

前記誤差補正回路は、

前記電荷リセット信号に応じて第2の電源端子から供給されるリセット電圧を前記容量切替ノードに印加する第1のスイッチ回路と、

前記第1のスイッチ回路と直列に接続され、導通状態が前記容量選択スイッチと排他的に制御され前記第1のスイッチ回路の有効状態と無効状態とを切り替える第2のスイッチ回路と、

を有する請求項1に記載の可変容量素子。

【請求項3】

前記第2の容量素子は、第1の端子が前記出力端子に接続され、第2の端子が前記容量切替ノードに接続され、

前記容量選択スイッチは、第1の端子が前記容量切替ノードに接続され、第2の端子が前記第1の電源端子に接続される請求項1又は2に記載の可変容量素子。

【請求項4】

前記第2の容量素子は、第1の端子が前記容量切替ノードに接続され、第2の端子が前記第1の電源端子に接続され、

前記容量選択スイッチは、第1の端子が前記出力端子に接続され、第2の端子が前記容量切替ノードに接続される請求項1又は2に記載の可変容量素子。

【請求項5】

前記出力端子と第2の電源端子との間に接続され、前記電荷リセット信号に応じて前記出力端子に前記第2の電源端子から供給される前記リセット電圧を与えるリセット回路を有する請求項1乃至4のいずれか1項に記載の可変容量素子。

【請求項6】

イネーブル状態が前記電荷リセット信号と排他的に制御される充放電制御信号に応じて前記第1の容量素子に充電又は放電を行う電流源を有する請求項1乃至6のいずれか1項に記載の可変容量素子。

【請求項7】

前記可変容量素子は、抵抗により設定される定電流と容量素子の容量値とにより発振周波数が設定される発振回路における前記容量素子として用いられる請求項1乃至6のいずれか1項に記載の可変容量素子。

【請求項8】

前記発振回路は、

発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧を生成するフィルタコンデンサと、

前記発振周波数制御電圧に応じて出力する発振信号の周波数を変動させる発振器と、

前記発振信号の周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路と、

前記可変容量素子を有し、前記タイミング制御信号に基づき前記発振信号の周期の長さと前記可変容量素子への充放電電流量とに応じて電圧レベルが変化する周波数検出電圧を生成する周波数検出回路と、

前記周波数検出電圧と基準電圧との電圧差に応じて前記発振周波数設定電流を連続的に可変して前記フィルタコンデンサに出力する差動増幅器と、を有する請求項7に記載の可変容量素子。

【請求項9】

前記可変容量素子は、入力信号に対する出力信号の遅延時間を設定する時定数回路に用いられる請求項1乃至6のいずれか1項に記載の可変容量素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−9929(P2012−9929A)

【公開日】平成24年1月12日(2012.1.12)

【国際特許分類】

【出願番号】特願2010−141487(P2010−141487)

【出願日】平成22年6月22日(2010.6.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年1月12日(2012.1.12)

【国際特許分類】

【出願日】平成22年6月22日(2010.6.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]