周辺機器に対するアクセスを制御する方法およびデバイス

プロセッサによるこのプロセッサの周辺機器に対するアクセスを制御する方法において、制御割り込みと呼ばれる、プロセッサの割り込みをトリガするステップ(E34)と、このトリガ後に、プロセッサから、周辺機器に対するアクセス認証コード(Code−AA)を取得するステップ(E37)と、アクセス認証コード(Code−AA)を予め定められた基準値(Code−UMCA)と比較するステップ(E38)と、前記比較ステップ(E30)の結果によって、周辺機器に対するアクセス信号を有効化するための電子信号を発生させるステップ(E50)とを含む方法。

【発明の詳細な説明】

【発明の分野】

【0001】

本発明は電子デバイスのセキュリティの分野に関連し、さらに正確には、電子デバイスの保全性への不正操作および攻撃に対して、これらのデバイスを保護する分野に関連する。

【発明の背景】

【0002】

2つの主なタイプの攻撃が知られており、すなわち、一方は、ソフトウェアタイプの攻撃で、他方は、ハードウェア構成要素の追加または置換を含む攻撃である。

【0003】

ソフトウェア攻撃に対処するため、いわゆる高レベルツール、すなわち、オペレーティングシステムの層の上で作動するツール(アンチウィルス、ファイヤーウォール等)が知られている。

【0004】

これらのツールは強力であるが、残念ながら、これらのツールがメモリにロードされる前に、これらのツールが活動停止され、または、バイパスされるおそれがあるという深刻な弱点を有している。

【0005】

トラステッドコンピューティンググループ(TCG)という名称のコンソーシアムは、低レベルソフトウェアの層を保護するツールおよび方法を提供することによって、ならびに、物理的周辺機器を識別することでも、この欠点を克服することを意図している。

【0006】

TCGは、パーソナルコンピュータのBIOS(基本入出力システム)の信頼性を、BIOSがロードされる前にチェックする方法を特に提案している。

【0007】

そこで、そのような方法は、CRTMトラストコード(信頼性測定のコアルート)を使用し、このCRTMコードは、コンピュータがスイッチオンされるときに、BIOS署名を計算するために実行される。

【0008】

したがって、このCRTMトラストコードは、システム中の何らかのソフトウェアセキュリティシーケンスの基礎を構成し、したがって、それ自身も攻撃に対して保護されていなければならない。

【0009】

このCRTMコードを保護するため、従来では、システムのマザーボード上にインストールされたフラッシュ型メモリの特定のセクタ中でコードを実行するための準備が行われる。

【0010】

2003年7月17日発行のIBM文書、US2003/0135727に説明されているように、そのようなソリューションの欠点は、例えば目的をアップグレードするために、このCRTMトラストコードを修正することは、マザーボード上へ物理的な介入をすることなく、不可能なことである。

【0011】

IBM文書は、マザーボードアドオンカード(機能拡張用カード)中で、トラストコード(CRTM)を実行することを含む、この問題に対する第1のソリューションを提案しており、この機能拡張用カードは、それ自身のBIOSを有する。アップグレードは、単にこの機能拡張用カードの物理的置換によって実効化することができる。

【0012】

このソリューションは、TCGによって発展された仕様のフレームワーク内では許容可能であるが、ユーザまたは第三者による第2のタイプの攻撃、いわゆるハードウェア攻撃(ゲームコンソール、特にGSMデバイスのIMEIコードおよびSIMロック)に対して、ブートローダーおよびBIOSの保護を拡張することが望ましいときには、このソリューションは、全く許容できないことを理解すべきである。

【0013】

システムセキュリティ機能のすべてを活動停止させるために必要とされることは、この機能拡張用カードを除去することだけであるので、したがって、このソリューションは、この拡張された保護のケースに対して重大な欠点をもたらす。

【0014】

TGCコンソーシアムは、使用される周辺機器を制御することによる、コンピュータ(PC)のハードウェア保全性の問題も述べている。より正確には、コンソーシアムは、例えばハードディスクのような周辺機器が2回のブートシーケンスの間に置換された場合にアラームを発生させるために、コンピュータの周辺機器の名称およびロケーションを登録する、TPMモジュールの使用を規定する。これは、周辺機器の同一性をチェックすることを含む。

【0015】

同様の方法で、ゲームコンソールの文脈で、文書WO43716(3DO)は、(コンソールの)プロセッサによって、カセットの非合法コピーを撲滅するために、周辺機器(ゲームカセット)を認証する方法を説明している。

【0016】

3DO文書は、カセット内に秘密鍵を組み込むことを提案しており、秘密鍵はこの鍵をまた保持しているコンソールにより確認される。正当に認証されたカセットの海賊版カセットによる置換を防ぐため、3DOは、ゲーム中に、カセットとコンソールとの間でセキュリティデータを交換するメカニズムの使用をさらに提案している。コンソールは、したがって、コンソールが常に同一のカセットと対話していることをチェックする。

【0017】

残念なことに、このソリューションは、秘密鍵と秘密セキュリティアルゴリズムを備える専用プログラムとが、周辺機器(カセット)中に組み込まれ、隠されることを要求する。この制約は、このタイプの技術開発におけるブレーキとなる。

【発明の目的と概要】

【0018】

本発明は、前述の欠点を克服することを可能にする。

【0019】

そこで、出願人は、同一性メカニズムにも、認証メカニズムにも基づいていない、非常に異なるアプローチを選択した。

【0020】

より正確には、第1の観点にしたがうと、本発明はプロセッサによるこのプロセッサの周辺機器に対するアクセスを制御するハードウェアユニットに関連し、このハードウェアユニットは、

制御割り込みと呼ばれる、プロセッサの割り込みをトリガする手段と、

割り込みのトリガに続いて、プロセッサから、周辺機器に対するアクセスを認証するコードを取得する手段と、

このアクセス認証コードを予め定められた基準値と比較する手段と、

前記比較の結果によって、周辺機器に対するアクセスのための電気信号を有効化する電気信号を発生させるように設計されている、いわゆる有効化手段とを具備する。

【0021】

よって、本発明にしたがったメカニズムは、バス分離のために、周辺機器の先頭に配置されたハードウェアユニットにより監視されるアクセス認証コードのプロセッサによる発行に基づいている。

【0022】

非常に有利な方法では、アクセス制御ハードウェアユニットが、プロセッサに向けられた割り込みの形態で、このコードを取得するためにプロセッサに対する明示的な要求をした後に、アクセス認証コードがアクセス制御ハードウェアユニットによって受け取られる。したがって、ハードウェアユニットはアクセス認証コードがプロセッサによってハードウェアユニットに供給されたことを確実に知る。

【0023】

この特徴は、制御割り込みルーチンによって構成されるトラストの構成要素から、アクセス認証コードが確かに受信されることを確実にするので、この特徴は、周辺機器に対するアクセスの非常に効果的な制御を達成することを可能にする。

【0024】

言い換えると、本発明は、周辺機器に対する単一のアクセスポイントを構成し、アクセス制御ハードウェアユニットと協調して、および、アクセス制御ハードウェアユニット経由で、周辺機器にアクセスするための電子信号を監視する、ソフトウェア構成要素(コンピュータプログラム)の使用に基づいている。

【0025】

好ましくは、このソフトウェア構成要素は、プロセッサのセキュリティ保護され、制御された領域に配置される。

【0026】

したがって、本発明は、ハードウェア手段によって、この周辺機器にアクセスする電気信号を最も低いレベルにおいて有効化することにより、プロセッサの周辺機器に対するアクセスを制御可能にしている。周辺機器は、スクリーン、キーボード、メモリ、通信インターフェイス制御装置、メモリ管理ユニット(MMU)、または、メモリ保護ユニット(MPU)から特に選択することができる。

【0027】

本発明が、スタートアップコード(ブートローダー)を持つフラッシュメモリに対する書き込みアクセスを制御するのに使用されるとき、本発明は、物理的な介入がなくてもこのスタートアップコードが更新されることを可能にし、同時に不正操作に対してコードを保護する。

【0028】

以後の本明細書において、用語「周辺機器」は、任意のタイプの電子的構成要素(スクリーン、キーボード、メモリ、通信インターフェイス、スマートカードインターフェイス、MMU、MPU等)に関して使用され、それらは、個別の構成要素であってもよく、もしくは、現場プログラム可能ゲートアレイまたは特定用途向け集積回路中に「統合されて」いてもよい。

【0029】

同様に、表現「アクセス電気信号」は、周辺機器を選択するためブートされる必要のある(チップ選択(CS)タイプ信号)、または、周辺機器に書き込むためブートされる必要のある(WRITE−ENABLE(WE)タイプ信号)のような、何らかの電気信号に関して使用されるだろう。

【0030】

同様に、用語「割り込み」は、非同期で、または、同期で、ソフトウェアの実行を一時停止するように設計された、何らかの手段に関して使用される。

【0031】

システムのセキュリティをかなり強化するため、制御割り込みは、マスク不可能割り込みであり、このことは、前述の一時停止をマスクすることが不可能であることを意味する。

【0032】

選ばれたアーキテクチャによって、この目的に対して、特に、

INTELx86系列のアーキテクチャに対するNMI信号、

MOTOROLA68K系列のアーキテクチャに対するIPL(7)レベル、

MC68Kアーキテクチャ中の/BERR信号に関係するアドレスまたはデータエラーサイクル、

ARM7TDMIアーキテクチャ中のABORT例外、

といった異なるタイプの信号が、使用されてもよいことを、当業者は理解するだろう。

【0033】

本発明にしたがうと、ハードウェアユニットの既知の予め定められた基準値と適合している前記周辺機器のアクセス認証コードの、アクセスを制御するハードウェアユニットに対する提示でのみ、このように保護された周辺機器はアクセスすることができる。

【0034】

したがって、本発明は、例えば、オペレータとの加入の商業約定を記憶するため、GSM準拠の移動電話機に含まれるメモリ(SIMロック)のような、いわゆるセキュリティ保護されたメモリを特に保護することを可能にする。

【0035】

これらのSIMロックルールの不正な置換は、このメモリに対するアクセスを制御しているハードウェアユニットに対する有効化アクセス認証コードの提示においてのみ可能となる。

【0036】

本発明は、BIOSまたはデバイスのオペレーティングシステムを遠隔でアップグレードするためにも使用できる。したがって、ポータブル電話機は、顧客がアップグレードセンターを訪問することなく、GSMワイヤレスリンク経由で直接、容易にアップグレード可能になるだろう。

【0037】

したがって、本発明は、PCのBIOSの何らかの不正な修正を防止するのに使用することができ、これらによって、BIOSがより高いレベルのセキュリティメカニズムを含むときは特に、かなりPCのセキュリティを強化する。

【0038】

ハードウェアユニットの制御は、トリガコードを取得する手段をさらに含み、制御割り込みをトリガする手段は、一度トリガコードが取得されると、割り込みをトリガするように設計されていることが好ましい。

【0039】

このトリガコードは、例えば、周辺機器への何らかのアクセスの前にプロセッサによって送出することができる。したがって、完全に閉鎖されたループメカニズムがプロセッサとハードウェアユニットとの間に配置され、このことはアクセス制御ハードウェアユニットが、アクセス信号を有効化する前に、プロセッサからアクセス認証コードを計画的に要求することを意味する。

【0040】

アクセス制御ハードウェアユニットは、このトリガコードを予め定められた基準値と比較する手段を含み、前記トリガ手段は、前記比較の結果の関数として、制御割り込みをトリガするように設計されていることが好ましい。

【0041】

したがって、間違ったトリガコードの提示の場合に、下記に説明するように、他のプロセスを代替として置くことができる。

【0042】

したがって、代替の実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、前記アクセス認証コードまたは前記トリガコードが予め定められた基準値と異なるとき、アラーム割り込みと呼ばれる、プロセッサ割り込みをトリガする手段を含む。このアラーム割り込みは、好ましくはマスク不可能割り込みである。

【0043】

第1の代替の実施形態では、予め定められた基準値は定数である。

【0044】

したがって、制御割り込みルーチンは、定数を制御ハードウェアユニットに対して単に送出することにより、周辺機器に対するアクセスを認証することができる。

【0045】

第2の代替の実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、予め定められた法則にしたがって、前述の基準値を発生させる手段を具備する。

【0046】

有効なアクセス認証コードをアクセス制御ハードウェアユニットに提示するためには、海賊版も予め定められた法則を知っている必要があるように、この特徴は周辺機器に対するアクセスの制御を強化する働きをすると好都合である。

【0047】

この第2の代替の実施形態の好ましいモードでは、予め定められた基準値は、ハードウェアユニットがスイッチオンされるとき、初期化されるカウンタであり、予め定められた法則は、アクセス認証コードが得られるたびにこのカウンタを増分することを含む。

【0048】

この予め定められた法則は、有限状態制御装置に関係するカウンタによって特に実施することができ、(コ)プロセッサのより費用のかかる使用を避け、ハードウェアユニットの全体の製造コストを限定する。

【0049】

他の有利な特徴にしたがうと、周辺機器に対するアクセスを制御するハードウェアユニットの有効化手段は、論理結合手段を備え、論理結合手段は、

周辺機器に対するアクセスを要求する電気信号を受信し、

有効化信号を受信し、

アクセス要求電気信号の状態と、有効化信号の状態と、真理値表で表される論理との関数として、アクセス電気信号を有効化するように設計されている。

【0050】

この特徴にしたがうと、周辺機器に対するアクセスは、したがって、2つの条件が満たされるときに有効化され、すなわち、一方では、例えばプロセッサのような第3の構成要素による、周辺機器に対するアクセスのための要求の提示、他方では、前述の比較の結果が、制御ハードウェアユニットによる有効アクセス認証コードの取得を表すときである。

【0051】

アクセス信号は、アクセス要求信号と有効化信号との間の「論理和」結合から結果として生じることが好ましい。この実施形態は、特に実効化するのが容易である。

【0052】

好ましい実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、アクセス要求電気信号の状態を読み出す手段と、この状態と、アクセス有効化電気信号の状態との関数として、好ましくはマスク不可能である、アラーム割り込みをトリガする手段とを含む。

【0053】

この特徴は、アクセス認証コードがアクセス制御ハードウェアユニットに提示されることなく、アクセス要求電気信号の状態が周辺機器に対するアクセスのための要求を表すとき、このアラーム割り込みをトリガできるようにすると好都合である。

【0054】

好ましい実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、有効化信号を抑止する手段を含み、この抑止は、好ましくは周辺機器に対する1回以上のアクセスの後に実効化される。

【0055】

この特徴は、有効化信号の抑止が定期的に、周辺機器に対する各アクセスよりもさらに前に、実行されなければならないように、周辺機器に対するアクセスの制御を強化可能であると好都合である。

【0056】

他の実施形態では、有効化信号の抑止は、アクセス有効化電気信号の発生から、または、アクセスコードの取得から計算された予め定められた遅延の後、実効化される。

【0057】

この特徴は、この遅延の間に制御することなく周辺機器に対するアクセスを認証することを可能にし、このことはシステムの全体のパフォーマンスを改善すると好都合である。この特徴は、スクリーンのケースでのように、周辺機器と交換されるデータ量が大きいときに特に役立つ。

【0058】

相補的に、本発明は、プロセッサによるこのプロセッサの周辺機器に対するアクセスを制御する方法に関連する。この方法は、

好ましくはマスク不可能な、制御割り込みと呼ばれるプロセッサの割り込みをトリガするステップと、

前記トリガ後に、周辺機器に対するアクセスを認証するコードをプロセッサから取得するステップと、

アクセス認証コードを予め定められた基準値と比較するステップと、

前記比較ステップの結果の関数として、周辺機器アクセス信号を有効化する電気信号を発生させるステップとを含む。

【0059】

このアクセス制御方法に特有な利点と特徴は、制御ハードウェアユニットに関して上で説明したものと同一であるため、それらはここで再度述べない。この方法は、本質的に、アクセス認証コードを(定数または法則にしたがって発生された)予め定められた基準値と比較することにより、周辺機器アクセス電気信号をこの比較の関数として有効化することにより、トラストの構成要素から必然的に受け取られた、1以上のアクセス認証コードの有効性をチェックすることを含む。

【0060】

他の観点にしたがうと、本発明は、上で簡単に説明したようにアクセス制御ハードウェアユニットを含むプロセッサに関連する。このプロセッサは、

アクセス認証コードを取得するよう設計されている制御割り込みルーチンを実行する手段と、

アクセス制御ハードウェアユニットにアクセス認証コードを送出する手段と

をまた含む。

【0061】

本発明のこの好ましい実施形態では、上で説明したアクセス制御ハードウェアユニットは、プロセッサ内に組み込まれ、このプロセッサは、所定の周辺機器に対するアクセスを認証するコードを制御ハードウェアユニットに送出する手段を含む。

【0062】

本発明のこの好ましい実施形態は、アクセス制御ハードウェアユニットを物理的にバイパスすること、または言い換えると、分路することを不可能にするという点で、周辺機器に対するアクセス制御をかなり強化する。

【0063】

本発明にしたがったプロセッサは、それに対するアクセスがそのように保護されている周辺機器を含むことが好ましい。

【0064】

この周辺機器は、特にメモリ管理ユニットとすることができる。

【0065】

したがって、本発明は、メモリ管理ユニット(MMU)に対するアクセスを保護することができる。これは、同一のプロセッサ上に、2つの完全に封印されたシステム環境を作ることを可能にする。これらの2つの環境の間の制御されたデータ交換のための空間がさらに提供される場合、当業者は、ある機能(オペレーティングシステム、または、支払、認証、著作権保護およびコピー保護アプリケーションのような機密アプリケーション)がより開放的であり、したがって、より攻撃を受けやすいアプリケーション(インターネットブラウザ、ゲーム、ビデオ、eメール等)から切り離されるデバイスを構築することは簡単なことであると理解するだろう。

【0066】

本発明にしたがったプロセッサに含まれる周辺機器は、プロセッサブートメモリのための書き込み制御装置とすることもできる。

【0067】

したがって、この好ましい実施形態は、プロセッサブートメモリのセキュリティを確実にし、この保護は、このメモリ中に含まれるデータの不正な修正を不可能にし、それがより高いレベルのセキュリティプロシジャーコールを取り扱うことが多いという点で、これはセキュリティが非常に重大である領域である。

【0068】

相補的に、本発明は、周辺機器に対するアクセスを管理する方法に関連する。この管理方法は、好ましくはマスク不可能な制御割り込みに関係するルーチンを実行するステップを含む。この制御ルーチンは、上で簡単に説明したように、アクセス制御ハードウェアユニットにアクセス認証コードを送出するステップを含む。

【0069】

第1の代替の実施形態では、アクセス制御コードは保護されたメモリから読み出される定数である。

【0070】

第2の代替の実施形態では、アクセス管理方法は、予め定められた法則にしたがって、アクセス認証コードを発生させるステップをさらに含む。

【0071】

当業者は、この第1の代替の実施形態では、周辺機器に対する無許可のアクセスが、保護メモリからの定数の読み出しとマスク不可能制御割り込みルーチンのトリガとの間の時間間隔の間に、悪意のある割り込みによって実効化される可能性を排除して、すべての割り込みをマスクすることが好ましいことを容易に理解するだろう。

【0072】

このアクセス管理方法に特有な利点と特徴は、本発明にしたがったプロセッサに関して上で簡単に説明したものと同一であるため、それらはここで再度述べない。この方法は、本質的に、トラストの構成要素(すなわち、制御割込みルーチンを実行するプロセッサ)から、アクセス認証コードを提供することを含み、これらのコードは、周辺機器に対するアクセスを認証または拒否するために、制御ハードウェアユニットによって予め定められた(定数または法則にしたがって発生された)基準値と比較される。

【0073】

本発明は、周辺機器にアクセスするための命令と、上で簡単に説明したように、このアクセス命令の実行の前に、この周辺機器に対するアクセスを制御するハードウェアユニットにトリガコードを送出する命令とを含むコンピュータプログラムも開示している。

【0074】

このコンピュータプログラムは、アクセス認証コードの発生のための予め定められた法則にしたがって、トリガコードを発生させる手段をさらに含むことが好ましい。

【0075】

このコンピュータプログラムは、プロセッサのセキュリティ保護され、制御された領域に配置されている周辺機器に対する単一のアクセスポイントを構成することが好ましい。このプログラムは、ハードウェアユニットと共同して、この周辺機器にアクセスするための電気信号を制御する。

【0076】

本発明は、アクセス制御方法、アクセス管理方法、および/または、上で簡単に説明したようなコンピュータプログラムを実行するように設計されているプロセッサも開示する。

【0077】

本発明の他の観点および利点は、下記に説明する特定の実施形態を読むことにより、さらに明らかになるだろう。この説明は、限定的でなく、単に例示的なものとして提供され、添付の図面を参照して行われる。

【実施形態の詳細な説明】

【0078】

ここで説明する本発明の実施形態は、より詳細には、プロセッサに含まれるブートメモリに対するアクセスの保護に関連する。

【0079】

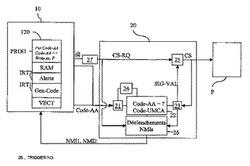

図1は、好ましい実施形態中の本発明にしたがったプロセッサ110を示す。

【0080】

プロセッサ110は、ブートメモリ120(ブートROM)と保護された揮発性メモリ(RAM)とを含む。このブートメモリ120は、割り込みベクトルテーブルVECTと、2つの割り込みルーチン、それぞれ制御IRT1およびアラームIRT2と、コンピュータプログラムPROGとを含む。

【0081】

このコンピュータプログラムPROGは、プロセッサに内蔵されている周辺機器Pに対する制御プログラムであり、そのようなプログラムは、通常「ドライバ」として呼ばれる。

【0082】

ここで説明する好ましい実施形態では、プロセッサに内蔵されている周辺機器Pは、前述のブートメモリ120に対する書き込み制御装置である。

【0083】

プロセッサ110は、本発明にしたがうと、周辺機器Pに対するアクセスを制御するハードウェアユニット20を含む。

【0084】

アクセス制御ハードウェアユニット20は、周辺機器Pに対するアクセスのため、トリガコードCode−DDと、認証コードCode−AAとを取得する手段を含む。

【0085】

ここで説明する実施形態では、トリガコードCode−DDとアクセス認証コードCode−AAとは、同一のレジスタ21から取得される。

【0086】

ここで説明する好ましい実施形態では、

アクセス認証コードCode−AAは、制御割り込みルーチンIRT1によってレジスタ21に書き込まれ、トリガコードCode−DDは、周辺機器PのドライバPROGによってレジスタ21に書き込まれる。

【0087】

よって、本発明にしたがうと、周辺機器Pに対してアクセスするための各命令(WRITE、READ等)の前に、コンピュータプログラムPROGは、ハードウェアユニット20のレジスタ21に、トリガコードCode−DDを書き込む。

【0088】

ここで説明する実施形態では、トリガコードCode−DDとアクセス認証コードCode−AAとは、予め定められた増分法則にしたがって計算される、同一変数の2つの連続する値である。

【0089】

この変数は、プロセッサの揮発性RAMメモリの保護されたエリア中に記憶される。このメモリは、コンピュータプログラムPROGと制御割り込みルーチンIRT1とにのみアクセス可能である。

【0090】

アクセス制御ハードウェアユニット20は、認証コードCode−AAまたはトリガコードCode−DDがレジスタ21に書き込まれるとき、予め定められた法則にしたがって、基準値Code−UMCAを発生させるように設計されている手段24も含む。

【0091】

ここで説明する好ましい実施形態では、この法則は、Code−UMCAカウンタを増分することを含み、カウンタは、プロセッサ110がスイッチオンされるとき、初期化される。

【0092】

アクセス制御ハードウェアユニット20は、レジスタ21から取得されたアクセス認証コードCode−AA(およびトリガコードCode−DD)を、この値を発生させる手段24によって計算された、予め定められた基準値Code−UMCAと比較する手段22も含む。

【0093】

ここで説明した好ましい実施形態では、これらの比較手段22は、ワイヤード論理により構成される。

【0094】

場合により、トリガコードCode−DDが基準値Code−UMCAの現在の値と等しいとわかったとき、これらの比較手段22は、割り込みトリガユニット26に第1の信号を送出するように設計されている。これは、図4aに関して下記に説明する。

【0095】

この第1の信号を受け取ると、割り込みトリガ手段26は、割り込み信号を発生させる。ここで説明する例では、この割り込み信号は、マスク不可能割り込み信号NMI1である。

【0096】

このマスク不可能割り込み信号NMI1を受け取ると、プロセッサは、割り込みベクトルテーブルVECTを用いて、制御割り込みルーチンIRT1を実行する。

【0097】

この制御割り込みルーチンIRT1は、予め定められた法則にしたがって、アクセス認証コードCode−AAの新たな値を計算し、この新たな値を保護メモリに記憶し、この新たなCode−AA値をアクセス制御ハードウェアユニット20のレジスタ21に書き込むように設計されている、計算関数発生コードを実行する。

【0098】

この予め定められた法則は、基準値Code−UMCAを発生させる手段24によって実行される法則と同じである。したがって、ここで説明する好ましい実施形態では、この法則は増分法則であり、アクセス認証コードCode−AAは、トリガコードCode−DDプラス1の値に等しい。

【0099】

アクセス認証コードCode−AAを取得する手段21が、制御割り込みルーチンIRT1から、この認証コードCode−AAを受け取るとき、基準値Code−UMCAを発生させる手段24は、予め定められた増分法則にしたがって、新たな基準値を発生させる。

【0100】

これらの2つの新たな値は、上で説明した比較手段22によって比較される。

【0101】

本発明にしたがうと、比較手段22は、アクセス制御ハードウェアユニット20のフリップフロップ23中に、これらの2つの新たな値の比較の結果を表す値を設定するように設計されている。

【0102】

ここで説明する実施形態では、新たなアクセス認証コードCode−AAと、新たな予め定められた基準値Code−UMCAとが等しいとき、ワイヤード論理22は、フリップフロップ23中に値1を設定することを仮定する。

【0103】

したがって、ここで説明する好ましい実施形態では、ドライバPROGと制御割り込みルーチンIRT1とから連続して受け取られる、トリガコードCode−DDと認証コードCode−AAとが、コードを受け取るときに手段24によって発生された、2つの予め定められた基準値Code−UMCAと等しいとき、フリップフロップ23の内容は、1に設定される。

【0104】

この好ましい実施形態にしたがうと、フリップフロップ23が1に設定されるとき、フリップフロップ23は、アクセス制御ハードウェアユニット20の論理結合手段25に送出するための有効化電気信号SIG_VALを発生させる。

【0105】

したがって、この好ましい実施形態では、上記の2つの条件が満たされるとき、有効化信号SIG_VALが発生される。

【0106】

トリガコードCode−DDをアクセス制御ハードウェアユニット20に送出する前に、ドライバPROGは、予め定められた法則にしたがって新たな値を発生させ、すなわち、ここで説明する実施形態中でそれを増分させ、この新たな値を保護された揮発性RAMメモリ中に記憶させる。

【0107】

周辺機器Pのドライバは、周辺機器Pに対してアクセスする命令を実行する。

【0108】

当業者に知られている方法で、アドレスデコーダ27の出力において、この命令は周辺機器Pに送出するための、チップ選択(CS)タイプのアクセス電気信号を発生させる。

【0109】

本発明にしたがうと、このアクセス信号は、周辺機器Pに直接送出されず、前述の論理結合手段25の入力に引き渡される。

【0110】

以下の本明細書において、この信号は、アクセス要求電気信号CS−RQとして呼ばれる。

【0111】

論理結合手段25は、それらの入力において、一方では、周辺機器Pに対するアクセスを要求する電気信号CS−RQを受け取り、他方では、有効化信号SIG_VALを受け取る。論理結合手段25は、知られている方法で、周辺機器Pへの送信に対するチップ選択(CS)タイプのアクセス信号を発生させるよう設計されている真理値表も含む。

【0112】

言い換えると、本発明の目的のため、真理値表25は、周辺機器Pに対してアクセスするための電気信号の有効化を促進する。

【0113】

ここで説明する好ましい実施形態では、論理結合手段25の出力におけるアクセス信号CSは、フリップフロップ23の入力に引き渡される。

【0114】

この実施形態では、周辺機器Pに対するアクセスが行われるとき、すなわち、アクセス信号CSの状態がハイのとき、フリップフロップ23の値は、0に再設定される。

【0115】

これは、この同一フリップフロップ23の出力において、有効化信号SIG_VALを抑止する効果を有し、したがって、周辺機器Pへの何らかのアクセスを非有効化する効果を有する。

【0116】

他の実施形態では、有効化信号SIG_VALは、例えば、周辺機器Pに対するアクセスのたびにというよりは、むしろ5回のアクセスごとのような、循環方式で抑止される。

【0117】

他の好ましい実施形態では、アクセス信号CSは、フリップフロップ23にフィードバックされない。フリップフロップ23は、この同一信号の発生から、または、トリガコードCode−DDの取得から計算された予め定められた遅延の後、有効化信号SIG_VALを自動的に抑止するよう設計されている。

【0118】

ここで説明する好ましい実施形態では、レジスタ21から取得されたコードが、このコードを受け取るときに発生された予め定められた基準値Code−UMCAと異なっていることを、比較手段22が比較によって検出するとき、比較手段22は、割り込みトリガユニット26に第2の信号を送出するように設計されている。

【0119】

この第2の信号を受け取ると、割り込みトリガ手段26は、ブートメモリ120に第2の割り込み信号を送出する。ここで説明する実施形態では、これはマスク不可能割り込み信号NMI2である。

【0120】

したがって、敵対的プログラムが、レジスタ21にランダムコードを書き込む場合、比較手段22は、マスク不可能割り込みNMI2をトリガするだろう。

【0121】

この第2の割り込み信号を受け取ると、プロセッサは、周辺機器Pへの不正アクセスの取り扱いに対する、アラーム割り込みルーチンIRT2を実行する。

【0122】

図2は、本発明の他の実施形態にしたがった、他のプロセッサ210を図解する。

【0123】

このプロセッサ210と上に図1に関して説明したプロセッサ110との間の唯一の違いは、プロセッサ210が、外付の周辺機器Pに対するアクセスを制御するのに使用される点である。

【0124】

他の特徴のすべてが同一であるため、ここでさらに図2の説明はしない。

【0125】

図3は、プロセッサ10に対する外付の構成要素の形態で、アクセス制御ハードウェアユニット20を図解する。

【0126】

本発明のこの実施形態では、アクセス制御ハードウェアユニット20と協調しているプロセッサ10は、図1のプロセッサ110に関して上で説明したブートメモリ120と同一のブートメモリ120を含む。

【0127】

この図3のアクセス制御ハードウェアユニット20は、図1に関して上で説明したアクセス制御ハードウェアユニット20と同じであり、下記では詳細に述べない。

【0128】

図4aは、有限状態制御装置の形態で、本発明の好ましい実施形態にしたがったアクセス制御方法の主要ステップを図解する。

【0129】

この図では、「楕円」は状態を表し、矢印は遷移を表し、四角形は遷移の実行のために必要かつ十分な条件を表している。

【0130】

以下の本明細書において、用語「ステップ」または「状態」は、コンピュータプログラムの当業者に知られているように、相互交換可能に使用されるだろう。

【0131】

この制御装置は、第1の初期化状態E10を含み、予め定められた基準値Code−UMCAが、例えば0のような初期値で初期化されるとき、E10を終了し(遷移E15)、揮発性RAMメモリにCode−UMCAが記憶される。

【0132】

待機状態E20に入る。

【0133】

この待機状態E20中で、アクセス制御ハードウェアユニットが、トリガコードCode−DDを受け取るとき(遷移E25)、状態E30に入り、状態E30では、このトリガコードCode−DDは、予め定められた基準値Code−UMCAと比較される。

【0134】

しかしながら、この待機状態E20中で、周辺機器Pにおいて、アクセス要求電気信号CS−RQが検出されるとき(遷移E22)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。

【0135】

マスク不可能アラーム割り込みNMI2をトリガするこの状態E100は自動的に終了し、アラーム管理状態E110に入る。

【0136】

好ましい実施形態では、アラーム管理状態E110は、端末コードを実行させる(RESET状態の発生)。他の実施形態では、応用によって、さまざまな反応が予想できる。これらの実施形態は、本発明の目的ではないため、ここで詳細に述べない。

【0137】

一度このアラーム管理プロシジャーが完了すると、アラームはキャンセルすることができ、上で説明した待機状態E20を再開することができる。

【0138】

トリガコードCode−DDが予め定められた基準値Code−UMCAと異なることが決定されるとき(遷移E85)、比較状態E30から、状態E100に入り、状態E100では、上で説明したマスク不可能アラーム割り込みNMI2がトリガされる。

【0139】

しかしながら、トリガコードCode−DDの値が予め定められた基準値Code−UMCAと等しいことが決定されるとき(遷移E31)、比較状態E30から、状態E32に入り、状態E32では、予め定められた増分法則にしたがって、新たな予め定められた基準値Code−UMCAが発生される。

【0140】

新たな基準値Code−UMCAが発生されるこの状態E32は、マスク不可能制御割り込みNMI1がトリガされる状態E34によって後続される。

【0141】

一度このマスク不可能制御割り込みNMI1がトリガされると、待機状態E36に入り、待機状態E36では、アクセス認証コードCode−AAを待機する。

【0142】

アクセス認証コードCode−AAを待機するこの状態E36中で、アクセス要求電気信号CS−RQが検出される場合(遷移E90)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。

【0143】

しかしながら、待機状態E36中で、アクセス認証コードCode−AAが取得されるとき(遷移E37)、状態E38に入り、状態E38では、このアクセス認証コードCode−AAは、新たな現在の基準値Code−UMCAと比較される。

【0144】

この比較状態E38の間に、アクセス認証コードCode−AAが基準値Code−UMCAと異なることが決定された場合(遷移E95)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。

【0145】

しかしながら、これらの2つの値が等しい場合(遷移E39)、比較状態E38を終了し、状態E40に入り、状態E40では、新たな基準値Code−UMCAが発生される。

【0146】

この発生状態E40は自動的に終了して、状態E50に入り、状態E50では、周辺機器Pに対するアクセス信号を有効化するために電気信号SIG_VALが発生される。

【0147】

有効化電気信号SIG_VALが発生されるこの状態E50は自動的に終了し、周辺機器Pに対するアクセスが実際に発生するまで、待機状態E60に入る。

【0148】

この待機状態E60中に、アクセスが実際に発生したことが検出されるとき(遷移E65)、状態E70に入り、状態E70では、有効化信号SIG_VALが抑止される。

【0149】

この抑止状態E70は自動的に終了し、上で説明した待機状態E20が再開する。

【0150】

他の実施形態では、待機状態E60中で、レジスタ21からのコードの取得が検出されるとき(遷移E67)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。このアクセス認証コードは、当然に悪意のある第三者により、アクセス制御ハードウェアユニットに送られたものである。この実施形態は、アクセスの有効化の後(状態E60)、周辺機器への不正なアクセスを検出することにより、システムのセキュリティを強化するように働く。

【0151】

図4bは、本発明の第2の実施形態にしたがった、アクセス制御方法の状態図を示す。

【0152】

本発明のこの実施形態は、トリガコードCode−DDを受け取るステップE25を含まないという意味で、単純化されている。もちろんこのトリガコードCode−DDを取り扱う任意のステップ(E30、E31、E32、E85)は削除される。

【0153】

ステップE25は、トリガステップE26により置き換えられ、ステップE26は、当業者によって知られている割り込みを発生させることができる何らかの手段により実行される。

【0154】

トリガステップE26は、ステップE34により自動的に後続され、E34では、図4aに関して説明したマスク不可能制御割り込みNMI1が発生される。

【0155】

この実施形態では、認証コードCode−AAは定数であり、基準値Code−UMCAを発生させるステップE40は削除される。

【0156】

制御割り込みルーチンIRT1が、保護されたメモリ中のコンピュータプログラムPROGにより記憶された値をレジスタ21にもたらす。

【0157】

図5は、本発明の好ましい実施形態にしたがったプロセッサによって実施される、マスク不可能制御割り込みルーチンIRT1の主要ステップE500からE520を図解する。

【0158】

アクセス制御ハードウェアユニット20がマスク不可能制御割り込みNMI1を発生させるとき、このルーチンが起動される。

【0159】

ここで説明するルーチンIRT1は、第1のステップE500を含み、E500の間に、同一名称のアクセス認証コードを含む、変数Code−AAの内容が変数VA中に記憶される。

【0160】

図4aに関して説明した実施形態では、アクセス認証コードCode−AAを読み出すステップE500は、ステップE510によって後続され、E510の間に、新たなアクセス認証コードCode−AAが、上で説明した予め定められた法則にしたがって発生される。この同一のステップの間、このアクセス認証コードCode−AAの新たな値は、保護されたメモリ中に記憶される。

【0161】

新たなアクセス認証コードCode−AAを発生および記憶させるステップE510は、アクセス制御ハードウェアユニット20に変数VAの内容を送出するステップE520によって後続される。

【0162】

ここで説明した好ましい実施形態では、この送出ステップは、変数VAの内容をレジスタ21に書き込むことを含む。

【0163】

図4bに関して説明した実施形態では、アクセス認証コードCode−AAの読み出しステップE500は、このステップE520により後続される。

【0164】

場合により、アクセス認証コードを送出するステップE520は、当業者に知られたタイプIRETの命令により後続され、タイプIRETの命令は、一方では割り込みNMI1のソースをキャンセルし、前記割り込みから戻ることに関係する。

【0165】

本発明にしたがったアクセス管理方法は、アクセス制御ハードウェアユニット20を起源とするマスク不可能割り込みNMI2に応答する、アラーム割り込みルーチンIRT2をオプション的に含む。

【0166】

このマスク不可能アラーム割り込みは、本質的に、アラートを発生させること、および/または、適切なルールにしたがって、認証されないアクセスを取り扱うことを含む。

【0167】

図6は、本発明の図4aの実施形態にしたがった、セキュリティ保護された周辺機器Pに対してアクセスするための命令を含む、コンピュータプログラムPROGの主要ステップE600からE630を図解する。

【0168】

このコンピュータプログラムは、図5に関して上で説明した、アクセス認証コードを読み出すステップE500とアクセス認証コードを発生および記憶させるステップE510と、それぞれ同一または類似である2つのステップE600とE610とを含む。

【0169】

したがって、これら2つのステップの間、コンピュータプログラムP[sic]は、変数VA中に現在のトリガコードCode−DDの内容を記憶し、予め定められた法則(増分法則)にしたがって、新たなトリガコードCode−DDを発生させ、割り込みルーチンIRT1と共有されているセキュリティ保護されたメモリに、この新たな値を記憶させる。

【0170】

周辺機器Pに対してアクセスする各ステップE630の前に、コンピュータプログラムPROGは、ステップE620を含み、E620の間に、変数VAの内容は、アクセス制御ハードウェアユニット20に送出され、ここで説明する実施形態では、これは、レジスタ21にこの変数の内容を書き込むことを含む。

【0171】

アクセス制御ハードウェアユニット20にアクセス認証コードVAを送出するこのステップE620は、周辺機器Pに対してアクセスするステップE630により後続される。

【0172】

図4b中の実施形態にしたがった本発明の実施形態では、コンピュータプログラムPROGは、プロセッサの保護されたメモリに定数値を記憶させるステップE610’を含み、周辺機器に対してアクセスするステップE630の前に、第1のマスク不可能制御割り込みIRT1をトリガするステップE620’を含む。

【0173】

アクセスの後、前記定数の何らかの異なる値がプロセッサの保護されたメモリ中に記憶される。

【0174】

このステップは、制御割り込みルーチンIRT1によっても実行することができる。

【図面の簡単な説明】

【0175】

【図1】図1は、本発明の第1の実施形態にしたがったプロセッサを図解する。

【図2】図2は、本発明の第2の実施形態にしたがったプロセッサを図解する。

【図3】図3は、本発明の好ましい実施形態にしたがったアクセス制御ハードウェアユニットを図解する。

【図4a】図4aは、本発明にしたがったアクセス制御方法の主要なステップを、制御チャートの形態で図解する。

【図4b】図4bは、本発明にしたがったアクセス制御方法の主要なステップを、制御チャートの形態で図解する。

【図5】図5は、本発明の好ましい実施形態にしたがった制御割り込みルーチンの主要ステップを、ブロック図の形態で図解する。

【図6】図6は、本発明にしたがった保護された周辺機器にアクセスするプログラムの主要ステップを、ブロック図の形態で図解する。

【発明の分野】

【0001】

本発明は電子デバイスのセキュリティの分野に関連し、さらに正確には、電子デバイスの保全性への不正操作および攻撃に対して、これらのデバイスを保護する分野に関連する。

【発明の背景】

【0002】

2つの主なタイプの攻撃が知られており、すなわち、一方は、ソフトウェアタイプの攻撃で、他方は、ハードウェア構成要素の追加または置換を含む攻撃である。

【0003】

ソフトウェア攻撃に対処するため、いわゆる高レベルツール、すなわち、オペレーティングシステムの層の上で作動するツール(アンチウィルス、ファイヤーウォール等)が知られている。

【0004】

これらのツールは強力であるが、残念ながら、これらのツールがメモリにロードされる前に、これらのツールが活動停止され、または、バイパスされるおそれがあるという深刻な弱点を有している。

【0005】

トラステッドコンピューティンググループ(TCG)という名称のコンソーシアムは、低レベルソフトウェアの層を保護するツールおよび方法を提供することによって、ならびに、物理的周辺機器を識別することでも、この欠点を克服することを意図している。

【0006】

TCGは、パーソナルコンピュータのBIOS(基本入出力システム)の信頼性を、BIOSがロードされる前にチェックする方法を特に提案している。

【0007】

そこで、そのような方法は、CRTMトラストコード(信頼性測定のコアルート)を使用し、このCRTMコードは、コンピュータがスイッチオンされるときに、BIOS署名を計算するために実行される。

【0008】

したがって、このCRTMトラストコードは、システム中の何らかのソフトウェアセキュリティシーケンスの基礎を構成し、したがって、それ自身も攻撃に対して保護されていなければならない。

【0009】

このCRTMコードを保護するため、従来では、システムのマザーボード上にインストールされたフラッシュ型メモリの特定のセクタ中でコードを実行するための準備が行われる。

【0010】

2003年7月17日発行のIBM文書、US2003/0135727に説明されているように、そのようなソリューションの欠点は、例えば目的をアップグレードするために、このCRTMトラストコードを修正することは、マザーボード上へ物理的な介入をすることなく、不可能なことである。

【0011】

IBM文書は、マザーボードアドオンカード(機能拡張用カード)中で、トラストコード(CRTM)を実行することを含む、この問題に対する第1のソリューションを提案しており、この機能拡張用カードは、それ自身のBIOSを有する。アップグレードは、単にこの機能拡張用カードの物理的置換によって実効化することができる。

【0012】

このソリューションは、TCGによって発展された仕様のフレームワーク内では許容可能であるが、ユーザまたは第三者による第2のタイプの攻撃、いわゆるハードウェア攻撃(ゲームコンソール、特にGSMデバイスのIMEIコードおよびSIMロック)に対して、ブートローダーおよびBIOSの保護を拡張することが望ましいときには、このソリューションは、全く許容できないことを理解すべきである。

【0013】

システムセキュリティ機能のすべてを活動停止させるために必要とされることは、この機能拡張用カードを除去することだけであるので、したがって、このソリューションは、この拡張された保護のケースに対して重大な欠点をもたらす。

【0014】

TGCコンソーシアムは、使用される周辺機器を制御することによる、コンピュータ(PC)のハードウェア保全性の問題も述べている。より正確には、コンソーシアムは、例えばハードディスクのような周辺機器が2回のブートシーケンスの間に置換された場合にアラームを発生させるために、コンピュータの周辺機器の名称およびロケーションを登録する、TPMモジュールの使用を規定する。これは、周辺機器の同一性をチェックすることを含む。

【0015】

同様の方法で、ゲームコンソールの文脈で、文書WO43716(3DO)は、(コンソールの)プロセッサによって、カセットの非合法コピーを撲滅するために、周辺機器(ゲームカセット)を認証する方法を説明している。

【0016】

3DO文書は、カセット内に秘密鍵を組み込むことを提案しており、秘密鍵はこの鍵をまた保持しているコンソールにより確認される。正当に認証されたカセットの海賊版カセットによる置換を防ぐため、3DOは、ゲーム中に、カセットとコンソールとの間でセキュリティデータを交換するメカニズムの使用をさらに提案している。コンソールは、したがって、コンソールが常に同一のカセットと対話していることをチェックする。

【0017】

残念なことに、このソリューションは、秘密鍵と秘密セキュリティアルゴリズムを備える専用プログラムとが、周辺機器(カセット)中に組み込まれ、隠されることを要求する。この制約は、このタイプの技術開発におけるブレーキとなる。

【発明の目的と概要】

【0018】

本発明は、前述の欠点を克服することを可能にする。

【0019】

そこで、出願人は、同一性メカニズムにも、認証メカニズムにも基づいていない、非常に異なるアプローチを選択した。

【0020】

より正確には、第1の観点にしたがうと、本発明はプロセッサによるこのプロセッサの周辺機器に対するアクセスを制御するハードウェアユニットに関連し、このハードウェアユニットは、

制御割り込みと呼ばれる、プロセッサの割り込みをトリガする手段と、

割り込みのトリガに続いて、プロセッサから、周辺機器に対するアクセスを認証するコードを取得する手段と、

このアクセス認証コードを予め定められた基準値と比較する手段と、

前記比較の結果によって、周辺機器に対するアクセスのための電気信号を有効化する電気信号を発生させるように設計されている、いわゆる有効化手段とを具備する。

【0021】

よって、本発明にしたがったメカニズムは、バス分離のために、周辺機器の先頭に配置されたハードウェアユニットにより監視されるアクセス認証コードのプロセッサによる発行に基づいている。

【0022】

非常に有利な方法では、アクセス制御ハードウェアユニットが、プロセッサに向けられた割り込みの形態で、このコードを取得するためにプロセッサに対する明示的な要求をした後に、アクセス認証コードがアクセス制御ハードウェアユニットによって受け取られる。したがって、ハードウェアユニットはアクセス認証コードがプロセッサによってハードウェアユニットに供給されたことを確実に知る。

【0023】

この特徴は、制御割り込みルーチンによって構成されるトラストの構成要素から、アクセス認証コードが確かに受信されることを確実にするので、この特徴は、周辺機器に対するアクセスの非常に効果的な制御を達成することを可能にする。

【0024】

言い換えると、本発明は、周辺機器に対する単一のアクセスポイントを構成し、アクセス制御ハードウェアユニットと協調して、および、アクセス制御ハードウェアユニット経由で、周辺機器にアクセスするための電子信号を監視する、ソフトウェア構成要素(コンピュータプログラム)の使用に基づいている。

【0025】

好ましくは、このソフトウェア構成要素は、プロセッサのセキュリティ保護され、制御された領域に配置される。

【0026】

したがって、本発明は、ハードウェア手段によって、この周辺機器にアクセスする電気信号を最も低いレベルにおいて有効化することにより、プロセッサの周辺機器に対するアクセスを制御可能にしている。周辺機器は、スクリーン、キーボード、メモリ、通信インターフェイス制御装置、メモリ管理ユニット(MMU)、または、メモリ保護ユニット(MPU)から特に選択することができる。

【0027】

本発明が、スタートアップコード(ブートローダー)を持つフラッシュメモリに対する書き込みアクセスを制御するのに使用されるとき、本発明は、物理的な介入がなくてもこのスタートアップコードが更新されることを可能にし、同時に不正操作に対してコードを保護する。

【0028】

以後の本明細書において、用語「周辺機器」は、任意のタイプの電子的構成要素(スクリーン、キーボード、メモリ、通信インターフェイス、スマートカードインターフェイス、MMU、MPU等)に関して使用され、それらは、個別の構成要素であってもよく、もしくは、現場プログラム可能ゲートアレイまたは特定用途向け集積回路中に「統合されて」いてもよい。

【0029】

同様に、表現「アクセス電気信号」は、周辺機器を選択するためブートされる必要のある(チップ選択(CS)タイプ信号)、または、周辺機器に書き込むためブートされる必要のある(WRITE−ENABLE(WE)タイプ信号)のような、何らかの電気信号に関して使用されるだろう。

【0030】

同様に、用語「割り込み」は、非同期で、または、同期で、ソフトウェアの実行を一時停止するように設計された、何らかの手段に関して使用される。

【0031】

システムのセキュリティをかなり強化するため、制御割り込みは、マスク不可能割り込みであり、このことは、前述の一時停止をマスクすることが不可能であることを意味する。

【0032】

選ばれたアーキテクチャによって、この目的に対して、特に、

INTELx86系列のアーキテクチャに対するNMI信号、

MOTOROLA68K系列のアーキテクチャに対するIPL(7)レベル、

MC68Kアーキテクチャ中の/BERR信号に関係するアドレスまたはデータエラーサイクル、

ARM7TDMIアーキテクチャ中のABORT例外、

といった異なるタイプの信号が、使用されてもよいことを、当業者は理解するだろう。

【0033】

本発明にしたがうと、ハードウェアユニットの既知の予め定められた基準値と適合している前記周辺機器のアクセス認証コードの、アクセスを制御するハードウェアユニットに対する提示でのみ、このように保護された周辺機器はアクセスすることができる。

【0034】

したがって、本発明は、例えば、オペレータとの加入の商業約定を記憶するため、GSM準拠の移動電話機に含まれるメモリ(SIMロック)のような、いわゆるセキュリティ保護されたメモリを特に保護することを可能にする。

【0035】

これらのSIMロックルールの不正な置換は、このメモリに対するアクセスを制御しているハードウェアユニットに対する有効化アクセス認証コードの提示においてのみ可能となる。

【0036】

本発明は、BIOSまたはデバイスのオペレーティングシステムを遠隔でアップグレードするためにも使用できる。したがって、ポータブル電話機は、顧客がアップグレードセンターを訪問することなく、GSMワイヤレスリンク経由で直接、容易にアップグレード可能になるだろう。

【0037】

したがって、本発明は、PCのBIOSの何らかの不正な修正を防止するのに使用することができ、これらによって、BIOSがより高いレベルのセキュリティメカニズムを含むときは特に、かなりPCのセキュリティを強化する。

【0038】

ハードウェアユニットの制御は、トリガコードを取得する手段をさらに含み、制御割り込みをトリガする手段は、一度トリガコードが取得されると、割り込みをトリガするように設計されていることが好ましい。

【0039】

このトリガコードは、例えば、周辺機器への何らかのアクセスの前にプロセッサによって送出することができる。したがって、完全に閉鎖されたループメカニズムがプロセッサとハードウェアユニットとの間に配置され、このことはアクセス制御ハードウェアユニットが、アクセス信号を有効化する前に、プロセッサからアクセス認証コードを計画的に要求することを意味する。

【0040】

アクセス制御ハードウェアユニットは、このトリガコードを予め定められた基準値と比較する手段を含み、前記トリガ手段は、前記比較の結果の関数として、制御割り込みをトリガするように設計されていることが好ましい。

【0041】

したがって、間違ったトリガコードの提示の場合に、下記に説明するように、他のプロセスを代替として置くことができる。

【0042】

したがって、代替の実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、前記アクセス認証コードまたは前記トリガコードが予め定められた基準値と異なるとき、アラーム割り込みと呼ばれる、プロセッサ割り込みをトリガする手段を含む。このアラーム割り込みは、好ましくはマスク不可能割り込みである。

【0043】

第1の代替の実施形態では、予め定められた基準値は定数である。

【0044】

したがって、制御割り込みルーチンは、定数を制御ハードウェアユニットに対して単に送出することにより、周辺機器に対するアクセスを認証することができる。

【0045】

第2の代替の実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、予め定められた法則にしたがって、前述の基準値を発生させる手段を具備する。

【0046】

有効なアクセス認証コードをアクセス制御ハードウェアユニットに提示するためには、海賊版も予め定められた法則を知っている必要があるように、この特徴は周辺機器に対するアクセスの制御を強化する働きをすると好都合である。

【0047】

この第2の代替の実施形態の好ましいモードでは、予め定められた基準値は、ハードウェアユニットがスイッチオンされるとき、初期化されるカウンタであり、予め定められた法則は、アクセス認証コードが得られるたびにこのカウンタを増分することを含む。

【0048】

この予め定められた法則は、有限状態制御装置に関係するカウンタによって特に実施することができ、(コ)プロセッサのより費用のかかる使用を避け、ハードウェアユニットの全体の製造コストを限定する。

【0049】

他の有利な特徴にしたがうと、周辺機器に対するアクセスを制御するハードウェアユニットの有効化手段は、論理結合手段を備え、論理結合手段は、

周辺機器に対するアクセスを要求する電気信号を受信し、

有効化信号を受信し、

アクセス要求電気信号の状態と、有効化信号の状態と、真理値表で表される論理との関数として、アクセス電気信号を有効化するように設計されている。

【0050】

この特徴にしたがうと、周辺機器に対するアクセスは、したがって、2つの条件が満たされるときに有効化され、すなわち、一方では、例えばプロセッサのような第3の構成要素による、周辺機器に対するアクセスのための要求の提示、他方では、前述の比較の結果が、制御ハードウェアユニットによる有効アクセス認証コードの取得を表すときである。

【0051】

アクセス信号は、アクセス要求信号と有効化信号との間の「論理和」結合から結果として生じることが好ましい。この実施形態は、特に実効化するのが容易である。

【0052】

好ましい実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、アクセス要求電気信号の状態を読み出す手段と、この状態と、アクセス有効化電気信号の状態との関数として、好ましくはマスク不可能である、アラーム割り込みをトリガする手段とを含む。

【0053】

この特徴は、アクセス認証コードがアクセス制御ハードウェアユニットに提示されることなく、アクセス要求電気信号の状態が周辺機器に対するアクセスのための要求を表すとき、このアラーム割り込みをトリガできるようにすると好都合である。

【0054】

好ましい実施形態では、本発明にしたがったアクセス制御ハードウェアユニットは、有効化信号を抑止する手段を含み、この抑止は、好ましくは周辺機器に対する1回以上のアクセスの後に実効化される。

【0055】

この特徴は、有効化信号の抑止が定期的に、周辺機器に対する各アクセスよりもさらに前に、実行されなければならないように、周辺機器に対するアクセスの制御を強化可能であると好都合である。

【0056】

他の実施形態では、有効化信号の抑止は、アクセス有効化電気信号の発生から、または、アクセスコードの取得から計算された予め定められた遅延の後、実効化される。

【0057】

この特徴は、この遅延の間に制御することなく周辺機器に対するアクセスを認証することを可能にし、このことはシステムの全体のパフォーマンスを改善すると好都合である。この特徴は、スクリーンのケースでのように、周辺機器と交換されるデータ量が大きいときに特に役立つ。

【0058】

相補的に、本発明は、プロセッサによるこのプロセッサの周辺機器に対するアクセスを制御する方法に関連する。この方法は、

好ましくはマスク不可能な、制御割り込みと呼ばれるプロセッサの割り込みをトリガするステップと、

前記トリガ後に、周辺機器に対するアクセスを認証するコードをプロセッサから取得するステップと、

アクセス認証コードを予め定められた基準値と比較するステップと、

前記比較ステップの結果の関数として、周辺機器アクセス信号を有効化する電気信号を発生させるステップとを含む。

【0059】

このアクセス制御方法に特有な利点と特徴は、制御ハードウェアユニットに関して上で説明したものと同一であるため、それらはここで再度述べない。この方法は、本質的に、アクセス認証コードを(定数または法則にしたがって発生された)予め定められた基準値と比較することにより、周辺機器アクセス電気信号をこの比較の関数として有効化することにより、トラストの構成要素から必然的に受け取られた、1以上のアクセス認証コードの有効性をチェックすることを含む。

【0060】

他の観点にしたがうと、本発明は、上で簡単に説明したようにアクセス制御ハードウェアユニットを含むプロセッサに関連する。このプロセッサは、

アクセス認証コードを取得するよう設計されている制御割り込みルーチンを実行する手段と、

アクセス制御ハードウェアユニットにアクセス認証コードを送出する手段と

をまた含む。

【0061】

本発明のこの好ましい実施形態では、上で説明したアクセス制御ハードウェアユニットは、プロセッサ内に組み込まれ、このプロセッサは、所定の周辺機器に対するアクセスを認証するコードを制御ハードウェアユニットに送出する手段を含む。

【0062】

本発明のこの好ましい実施形態は、アクセス制御ハードウェアユニットを物理的にバイパスすること、または言い換えると、分路することを不可能にするという点で、周辺機器に対するアクセス制御をかなり強化する。

【0063】

本発明にしたがったプロセッサは、それに対するアクセスがそのように保護されている周辺機器を含むことが好ましい。

【0064】

この周辺機器は、特にメモリ管理ユニットとすることができる。

【0065】

したがって、本発明は、メモリ管理ユニット(MMU)に対するアクセスを保護することができる。これは、同一のプロセッサ上に、2つの完全に封印されたシステム環境を作ることを可能にする。これらの2つの環境の間の制御されたデータ交換のための空間がさらに提供される場合、当業者は、ある機能(オペレーティングシステム、または、支払、認証、著作権保護およびコピー保護アプリケーションのような機密アプリケーション)がより開放的であり、したがって、より攻撃を受けやすいアプリケーション(インターネットブラウザ、ゲーム、ビデオ、eメール等)から切り離されるデバイスを構築することは簡単なことであると理解するだろう。

【0066】

本発明にしたがったプロセッサに含まれる周辺機器は、プロセッサブートメモリのための書き込み制御装置とすることもできる。

【0067】

したがって、この好ましい実施形態は、プロセッサブートメモリのセキュリティを確実にし、この保護は、このメモリ中に含まれるデータの不正な修正を不可能にし、それがより高いレベルのセキュリティプロシジャーコールを取り扱うことが多いという点で、これはセキュリティが非常に重大である領域である。

【0068】

相補的に、本発明は、周辺機器に対するアクセスを管理する方法に関連する。この管理方法は、好ましくはマスク不可能な制御割り込みに関係するルーチンを実行するステップを含む。この制御ルーチンは、上で簡単に説明したように、アクセス制御ハードウェアユニットにアクセス認証コードを送出するステップを含む。

【0069】

第1の代替の実施形態では、アクセス制御コードは保護されたメモリから読み出される定数である。

【0070】

第2の代替の実施形態では、アクセス管理方法は、予め定められた法則にしたがって、アクセス認証コードを発生させるステップをさらに含む。

【0071】

当業者は、この第1の代替の実施形態では、周辺機器に対する無許可のアクセスが、保護メモリからの定数の読み出しとマスク不可能制御割り込みルーチンのトリガとの間の時間間隔の間に、悪意のある割り込みによって実効化される可能性を排除して、すべての割り込みをマスクすることが好ましいことを容易に理解するだろう。

【0072】

このアクセス管理方法に特有な利点と特徴は、本発明にしたがったプロセッサに関して上で簡単に説明したものと同一であるため、それらはここで再度述べない。この方法は、本質的に、トラストの構成要素(すなわち、制御割込みルーチンを実行するプロセッサ)から、アクセス認証コードを提供することを含み、これらのコードは、周辺機器に対するアクセスを認証または拒否するために、制御ハードウェアユニットによって予め定められた(定数または法則にしたがって発生された)基準値と比較される。

【0073】

本発明は、周辺機器にアクセスするための命令と、上で簡単に説明したように、このアクセス命令の実行の前に、この周辺機器に対するアクセスを制御するハードウェアユニットにトリガコードを送出する命令とを含むコンピュータプログラムも開示している。

【0074】

このコンピュータプログラムは、アクセス認証コードの発生のための予め定められた法則にしたがって、トリガコードを発生させる手段をさらに含むことが好ましい。

【0075】

このコンピュータプログラムは、プロセッサのセキュリティ保護され、制御された領域に配置されている周辺機器に対する単一のアクセスポイントを構成することが好ましい。このプログラムは、ハードウェアユニットと共同して、この周辺機器にアクセスするための電気信号を制御する。

【0076】

本発明は、アクセス制御方法、アクセス管理方法、および/または、上で簡単に説明したようなコンピュータプログラムを実行するように設計されているプロセッサも開示する。

【0077】

本発明の他の観点および利点は、下記に説明する特定の実施形態を読むことにより、さらに明らかになるだろう。この説明は、限定的でなく、単に例示的なものとして提供され、添付の図面を参照して行われる。

【実施形態の詳細な説明】

【0078】

ここで説明する本発明の実施形態は、より詳細には、プロセッサに含まれるブートメモリに対するアクセスの保護に関連する。

【0079】

図1は、好ましい実施形態中の本発明にしたがったプロセッサ110を示す。

【0080】

プロセッサ110は、ブートメモリ120(ブートROM)と保護された揮発性メモリ(RAM)とを含む。このブートメモリ120は、割り込みベクトルテーブルVECTと、2つの割り込みルーチン、それぞれ制御IRT1およびアラームIRT2と、コンピュータプログラムPROGとを含む。

【0081】

このコンピュータプログラムPROGは、プロセッサに内蔵されている周辺機器Pに対する制御プログラムであり、そのようなプログラムは、通常「ドライバ」として呼ばれる。

【0082】

ここで説明する好ましい実施形態では、プロセッサに内蔵されている周辺機器Pは、前述のブートメモリ120に対する書き込み制御装置である。

【0083】

プロセッサ110は、本発明にしたがうと、周辺機器Pに対するアクセスを制御するハードウェアユニット20を含む。

【0084】

アクセス制御ハードウェアユニット20は、周辺機器Pに対するアクセスのため、トリガコードCode−DDと、認証コードCode−AAとを取得する手段を含む。

【0085】

ここで説明する実施形態では、トリガコードCode−DDとアクセス認証コードCode−AAとは、同一のレジスタ21から取得される。

【0086】

ここで説明する好ましい実施形態では、

アクセス認証コードCode−AAは、制御割り込みルーチンIRT1によってレジスタ21に書き込まれ、トリガコードCode−DDは、周辺機器PのドライバPROGによってレジスタ21に書き込まれる。

【0087】

よって、本発明にしたがうと、周辺機器Pに対してアクセスするための各命令(WRITE、READ等)の前に、コンピュータプログラムPROGは、ハードウェアユニット20のレジスタ21に、トリガコードCode−DDを書き込む。

【0088】

ここで説明する実施形態では、トリガコードCode−DDとアクセス認証コードCode−AAとは、予め定められた増分法則にしたがって計算される、同一変数の2つの連続する値である。

【0089】

この変数は、プロセッサの揮発性RAMメモリの保護されたエリア中に記憶される。このメモリは、コンピュータプログラムPROGと制御割り込みルーチンIRT1とにのみアクセス可能である。

【0090】

アクセス制御ハードウェアユニット20は、認証コードCode−AAまたはトリガコードCode−DDがレジスタ21に書き込まれるとき、予め定められた法則にしたがって、基準値Code−UMCAを発生させるように設計されている手段24も含む。

【0091】

ここで説明する好ましい実施形態では、この法則は、Code−UMCAカウンタを増分することを含み、カウンタは、プロセッサ110がスイッチオンされるとき、初期化される。

【0092】

アクセス制御ハードウェアユニット20は、レジスタ21から取得されたアクセス認証コードCode−AA(およびトリガコードCode−DD)を、この値を発生させる手段24によって計算された、予め定められた基準値Code−UMCAと比較する手段22も含む。

【0093】

ここで説明した好ましい実施形態では、これらの比較手段22は、ワイヤード論理により構成される。

【0094】

場合により、トリガコードCode−DDが基準値Code−UMCAの現在の値と等しいとわかったとき、これらの比較手段22は、割り込みトリガユニット26に第1の信号を送出するように設計されている。これは、図4aに関して下記に説明する。

【0095】

この第1の信号を受け取ると、割り込みトリガ手段26は、割り込み信号を発生させる。ここで説明する例では、この割り込み信号は、マスク不可能割り込み信号NMI1である。

【0096】

このマスク不可能割り込み信号NMI1を受け取ると、プロセッサは、割り込みベクトルテーブルVECTを用いて、制御割り込みルーチンIRT1を実行する。

【0097】

この制御割り込みルーチンIRT1は、予め定められた法則にしたがって、アクセス認証コードCode−AAの新たな値を計算し、この新たな値を保護メモリに記憶し、この新たなCode−AA値をアクセス制御ハードウェアユニット20のレジスタ21に書き込むように設計されている、計算関数発生コードを実行する。

【0098】

この予め定められた法則は、基準値Code−UMCAを発生させる手段24によって実行される法則と同じである。したがって、ここで説明する好ましい実施形態では、この法則は増分法則であり、アクセス認証コードCode−AAは、トリガコードCode−DDプラス1の値に等しい。

【0099】

アクセス認証コードCode−AAを取得する手段21が、制御割り込みルーチンIRT1から、この認証コードCode−AAを受け取るとき、基準値Code−UMCAを発生させる手段24は、予め定められた増分法則にしたがって、新たな基準値を発生させる。

【0100】

これらの2つの新たな値は、上で説明した比較手段22によって比較される。

【0101】

本発明にしたがうと、比較手段22は、アクセス制御ハードウェアユニット20のフリップフロップ23中に、これらの2つの新たな値の比較の結果を表す値を設定するように設計されている。

【0102】

ここで説明する実施形態では、新たなアクセス認証コードCode−AAと、新たな予め定められた基準値Code−UMCAとが等しいとき、ワイヤード論理22は、フリップフロップ23中に値1を設定することを仮定する。

【0103】

したがって、ここで説明する好ましい実施形態では、ドライバPROGと制御割り込みルーチンIRT1とから連続して受け取られる、トリガコードCode−DDと認証コードCode−AAとが、コードを受け取るときに手段24によって発生された、2つの予め定められた基準値Code−UMCAと等しいとき、フリップフロップ23の内容は、1に設定される。

【0104】

この好ましい実施形態にしたがうと、フリップフロップ23が1に設定されるとき、フリップフロップ23は、アクセス制御ハードウェアユニット20の論理結合手段25に送出するための有効化電気信号SIG_VALを発生させる。

【0105】

したがって、この好ましい実施形態では、上記の2つの条件が満たされるとき、有効化信号SIG_VALが発生される。

【0106】

トリガコードCode−DDをアクセス制御ハードウェアユニット20に送出する前に、ドライバPROGは、予め定められた法則にしたがって新たな値を発生させ、すなわち、ここで説明する実施形態中でそれを増分させ、この新たな値を保護された揮発性RAMメモリ中に記憶させる。

【0107】

周辺機器Pのドライバは、周辺機器Pに対してアクセスする命令を実行する。

【0108】

当業者に知られている方法で、アドレスデコーダ27の出力において、この命令は周辺機器Pに送出するための、チップ選択(CS)タイプのアクセス電気信号を発生させる。

【0109】

本発明にしたがうと、このアクセス信号は、周辺機器Pに直接送出されず、前述の論理結合手段25の入力に引き渡される。

【0110】

以下の本明細書において、この信号は、アクセス要求電気信号CS−RQとして呼ばれる。

【0111】

論理結合手段25は、それらの入力において、一方では、周辺機器Pに対するアクセスを要求する電気信号CS−RQを受け取り、他方では、有効化信号SIG_VALを受け取る。論理結合手段25は、知られている方法で、周辺機器Pへの送信に対するチップ選択(CS)タイプのアクセス信号を発生させるよう設計されている真理値表も含む。

【0112】

言い換えると、本発明の目的のため、真理値表25は、周辺機器Pに対してアクセスするための電気信号の有効化を促進する。

【0113】

ここで説明する好ましい実施形態では、論理結合手段25の出力におけるアクセス信号CSは、フリップフロップ23の入力に引き渡される。

【0114】

この実施形態では、周辺機器Pに対するアクセスが行われるとき、すなわち、アクセス信号CSの状態がハイのとき、フリップフロップ23の値は、0に再設定される。

【0115】

これは、この同一フリップフロップ23の出力において、有効化信号SIG_VALを抑止する効果を有し、したがって、周辺機器Pへの何らかのアクセスを非有効化する効果を有する。

【0116】

他の実施形態では、有効化信号SIG_VALは、例えば、周辺機器Pに対するアクセスのたびにというよりは、むしろ5回のアクセスごとのような、循環方式で抑止される。

【0117】

他の好ましい実施形態では、アクセス信号CSは、フリップフロップ23にフィードバックされない。フリップフロップ23は、この同一信号の発生から、または、トリガコードCode−DDの取得から計算された予め定められた遅延の後、有効化信号SIG_VALを自動的に抑止するよう設計されている。

【0118】

ここで説明する好ましい実施形態では、レジスタ21から取得されたコードが、このコードを受け取るときに発生された予め定められた基準値Code−UMCAと異なっていることを、比較手段22が比較によって検出するとき、比較手段22は、割り込みトリガユニット26に第2の信号を送出するように設計されている。

【0119】

この第2の信号を受け取ると、割り込みトリガ手段26は、ブートメモリ120に第2の割り込み信号を送出する。ここで説明する実施形態では、これはマスク不可能割り込み信号NMI2である。

【0120】

したがって、敵対的プログラムが、レジスタ21にランダムコードを書き込む場合、比較手段22は、マスク不可能割り込みNMI2をトリガするだろう。

【0121】

この第2の割り込み信号を受け取ると、プロセッサは、周辺機器Pへの不正アクセスの取り扱いに対する、アラーム割り込みルーチンIRT2を実行する。

【0122】

図2は、本発明の他の実施形態にしたがった、他のプロセッサ210を図解する。

【0123】

このプロセッサ210と上に図1に関して説明したプロセッサ110との間の唯一の違いは、プロセッサ210が、外付の周辺機器Pに対するアクセスを制御するのに使用される点である。

【0124】

他の特徴のすべてが同一であるため、ここでさらに図2の説明はしない。

【0125】

図3は、プロセッサ10に対する外付の構成要素の形態で、アクセス制御ハードウェアユニット20を図解する。

【0126】

本発明のこの実施形態では、アクセス制御ハードウェアユニット20と協調しているプロセッサ10は、図1のプロセッサ110に関して上で説明したブートメモリ120と同一のブートメモリ120を含む。

【0127】

この図3のアクセス制御ハードウェアユニット20は、図1に関して上で説明したアクセス制御ハードウェアユニット20と同じであり、下記では詳細に述べない。

【0128】

図4aは、有限状態制御装置の形態で、本発明の好ましい実施形態にしたがったアクセス制御方法の主要ステップを図解する。

【0129】

この図では、「楕円」は状態を表し、矢印は遷移を表し、四角形は遷移の実行のために必要かつ十分な条件を表している。

【0130】

以下の本明細書において、用語「ステップ」または「状態」は、コンピュータプログラムの当業者に知られているように、相互交換可能に使用されるだろう。

【0131】

この制御装置は、第1の初期化状態E10を含み、予め定められた基準値Code−UMCAが、例えば0のような初期値で初期化されるとき、E10を終了し(遷移E15)、揮発性RAMメモリにCode−UMCAが記憶される。

【0132】

待機状態E20に入る。

【0133】

この待機状態E20中で、アクセス制御ハードウェアユニットが、トリガコードCode−DDを受け取るとき(遷移E25)、状態E30に入り、状態E30では、このトリガコードCode−DDは、予め定められた基準値Code−UMCAと比較される。

【0134】

しかしながら、この待機状態E20中で、周辺機器Pにおいて、アクセス要求電気信号CS−RQが検出されるとき(遷移E22)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。

【0135】

マスク不可能アラーム割り込みNMI2をトリガするこの状態E100は自動的に終了し、アラーム管理状態E110に入る。

【0136】

好ましい実施形態では、アラーム管理状態E110は、端末コードを実行させる(RESET状態の発生)。他の実施形態では、応用によって、さまざまな反応が予想できる。これらの実施形態は、本発明の目的ではないため、ここで詳細に述べない。

【0137】

一度このアラーム管理プロシジャーが完了すると、アラームはキャンセルすることができ、上で説明した待機状態E20を再開することができる。

【0138】

トリガコードCode−DDが予め定められた基準値Code−UMCAと異なることが決定されるとき(遷移E85)、比較状態E30から、状態E100に入り、状態E100では、上で説明したマスク不可能アラーム割り込みNMI2がトリガされる。

【0139】

しかしながら、トリガコードCode−DDの値が予め定められた基準値Code−UMCAと等しいことが決定されるとき(遷移E31)、比較状態E30から、状態E32に入り、状態E32では、予め定められた増分法則にしたがって、新たな予め定められた基準値Code−UMCAが発生される。

【0140】

新たな基準値Code−UMCAが発生されるこの状態E32は、マスク不可能制御割り込みNMI1がトリガされる状態E34によって後続される。

【0141】

一度このマスク不可能制御割り込みNMI1がトリガされると、待機状態E36に入り、待機状態E36では、アクセス認証コードCode−AAを待機する。

【0142】

アクセス認証コードCode−AAを待機するこの状態E36中で、アクセス要求電気信号CS−RQが検出される場合(遷移E90)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。

【0143】

しかしながら、待機状態E36中で、アクセス認証コードCode−AAが取得されるとき(遷移E37)、状態E38に入り、状態E38では、このアクセス認証コードCode−AAは、新たな現在の基準値Code−UMCAと比較される。

【0144】

この比較状態E38の間に、アクセス認証コードCode−AAが基準値Code−UMCAと異なることが決定された場合(遷移E95)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。

【0145】

しかしながら、これらの2つの値が等しい場合(遷移E39)、比較状態E38を終了し、状態E40に入り、状態E40では、新たな基準値Code−UMCAが発生される。

【0146】

この発生状態E40は自動的に終了して、状態E50に入り、状態E50では、周辺機器Pに対するアクセス信号を有効化するために電気信号SIG_VALが発生される。

【0147】

有効化電気信号SIG_VALが発生されるこの状態E50は自動的に終了し、周辺機器Pに対するアクセスが実際に発生するまで、待機状態E60に入る。

【0148】

この待機状態E60中に、アクセスが実際に発生したことが検出されるとき(遷移E65)、状態E70に入り、状態E70では、有効化信号SIG_VALが抑止される。

【0149】

この抑止状態E70は自動的に終了し、上で説明した待機状態E20が再開する。

【0150】

他の実施形態では、待機状態E60中で、レジスタ21からのコードの取得が検出されるとき(遷移E67)、状態E100に入り、状態E100では、マスク不可能アラーム割り込みNMI2がトリガされる。このアクセス認証コードは、当然に悪意のある第三者により、アクセス制御ハードウェアユニットに送られたものである。この実施形態は、アクセスの有効化の後(状態E60)、周辺機器への不正なアクセスを検出することにより、システムのセキュリティを強化するように働く。

【0151】

図4bは、本発明の第2の実施形態にしたがった、アクセス制御方法の状態図を示す。

【0152】

本発明のこの実施形態は、トリガコードCode−DDを受け取るステップE25を含まないという意味で、単純化されている。もちろんこのトリガコードCode−DDを取り扱う任意のステップ(E30、E31、E32、E85)は削除される。

【0153】

ステップE25は、トリガステップE26により置き換えられ、ステップE26は、当業者によって知られている割り込みを発生させることができる何らかの手段により実行される。

【0154】

トリガステップE26は、ステップE34により自動的に後続され、E34では、図4aに関して説明したマスク不可能制御割り込みNMI1が発生される。

【0155】

この実施形態では、認証コードCode−AAは定数であり、基準値Code−UMCAを発生させるステップE40は削除される。

【0156】

制御割り込みルーチンIRT1が、保護されたメモリ中のコンピュータプログラムPROGにより記憶された値をレジスタ21にもたらす。

【0157】

図5は、本発明の好ましい実施形態にしたがったプロセッサによって実施される、マスク不可能制御割り込みルーチンIRT1の主要ステップE500からE520を図解する。

【0158】

アクセス制御ハードウェアユニット20がマスク不可能制御割り込みNMI1を発生させるとき、このルーチンが起動される。

【0159】

ここで説明するルーチンIRT1は、第1のステップE500を含み、E500の間に、同一名称のアクセス認証コードを含む、変数Code−AAの内容が変数VA中に記憶される。

【0160】

図4aに関して説明した実施形態では、アクセス認証コードCode−AAを読み出すステップE500は、ステップE510によって後続され、E510の間に、新たなアクセス認証コードCode−AAが、上で説明した予め定められた法則にしたがって発生される。この同一のステップの間、このアクセス認証コードCode−AAの新たな値は、保護されたメモリ中に記憶される。

【0161】

新たなアクセス認証コードCode−AAを発生および記憶させるステップE510は、アクセス制御ハードウェアユニット20に変数VAの内容を送出するステップE520によって後続される。

【0162】

ここで説明した好ましい実施形態では、この送出ステップは、変数VAの内容をレジスタ21に書き込むことを含む。

【0163】

図4bに関して説明した実施形態では、アクセス認証コードCode−AAの読み出しステップE500は、このステップE520により後続される。

【0164】

場合により、アクセス認証コードを送出するステップE520は、当業者に知られたタイプIRETの命令により後続され、タイプIRETの命令は、一方では割り込みNMI1のソースをキャンセルし、前記割り込みから戻ることに関係する。

【0165】

本発明にしたがったアクセス管理方法は、アクセス制御ハードウェアユニット20を起源とするマスク不可能割り込みNMI2に応答する、アラーム割り込みルーチンIRT2をオプション的に含む。

【0166】

このマスク不可能アラーム割り込みは、本質的に、アラートを発生させること、および/または、適切なルールにしたがって、認証されないアクセスを取り扱うことを含む。

【0167】

図6は、本発明の図4aの実施形態にしたがった、セキュリティ保護された周辺機器Pに対してアクセスするための命令を含む、コンピュータプログラムPROGの主要ステップE600からE630を図解する。

【0168】

このコンピュータプログラムは、図5に関して上で説明した、アクセス認証コードを読み出すステップE500とアクセス認証コードを発生および記憶させるステップE510と、それぞれ同一または類似である2つのステップE600とE610とを含む。

【0169】

したがって、これら2つのステップの間、コンピュータプログラムP[sic]は、変数VA中に現在のトリガコードCode−DDの内容を記憶し、予め定められた法則(増分法則)にしたがって、新たなトリガコードCode−DDを発生させ、割り込みルーチンIRT1と共有されているセキュリティ保護されたメモリに、この新たな値を記憶させる。

【0170】

周辺機器Pに対してアクセスする各ステップE630の前に、コンピュータプログラムPROGは、ステップE620を含み、E620の間に、変数VAの内容は、アクセス制御ハードウェアユニット20に送出され、ここで説明する実施形態では、これは、レジスタ21にこの変数の内容を書き込むことを含む。

【0171】

アクセス制御ハードウェアユニット20にアクセス認証コードVAを送出するこのステップE620は、周辺機器Pに対してアクセスするステップE630により後続される。

【0172】

図4b中の実施形態にしたがった本発明の実施形態では、コンピュータプログラムPROGは、プロセッサの保護されたメモリに定数値を記憶させるステップE610’を含み、周辺機器に対してアクセスするステップE630の前に、第1のマスク不可能制御割り込みIRT1をトリガするステップE620’を含む。

【0173】

アクセスの後、前記定数の何らかの異なる値がプロセッサの保護されたメモリ中に記憶される。

【0174】

このステップは、制御割り込みルーチンIRT1によっても実行することができる。

【図面の簡単な説明】

【0175】

【図1】図1は、本発明の第1の実施形態にしたがったプロセッサを図解する。

【図2】図2は、本発明の第2の実施形態にしたがったプロセッサを図解する。

【図3】図3は、本発明の好ましい実施形態にしたがったアクセス制御ハードウェアユニットを図解する。

【図4a】図4aは、本発明にしたがったアクセス制御方法の主要なステップを、制御チャートの形態で図解する。

【図4b】図4bは、本発明にしたがったアクセス制御方法の主要なステップを、制御チャートの形態で図解する。

【図5】図5は、本発明の好ましい実施形態にしたがった制御割り込みルーチンの主要ステップを、ブロック図の形態で図解する。

【図6】図6は、本発明にしたがった保護された周辺機器にアクセスするプログラムの主要ステップを、ブロック図の形態で図解する。

【特許請求の範囲】

【請求項1】

プロセッサ(10、110、120)による、このプロセッサの周辺機器(P)に対するアクセスを制御するハードウェアユニット(20)において、

前記ハードウェアユニット(20)は、

制御割り込みと呼ばれる、前記プロセッサの割り込みをトリガする手段(26)と、

前記トリガ後に、前記周辺機器(P)に対するアクセス認証コード(Code−AA)を前記プロセッサから取得する手段(21)と、

前記アクセス認証コード(Code−AA)を予め定められた基準値(Code−UMCA)と比較する手段(22)と、

前記比較の結果によって、前記周辺機器(P)に対するアクセス電気信号(CS、WE、PWR)を有効化するための電気信号(SIG_VAL)を発生させるように設計されている、いわゆる有効化手段(22、23、25)と

を具備するハードウェアユニット。

【請求項2】

前記制御割り込みは、マスク不可能割り込み(NMI1)であることを特徴とする、請求項1記載のアクセス制御ハードウェアユニット。

【請求項3】

前記アクセス制御ハードウェアユニットは、トリガコード(Code−DD)を取得する手段(21)をさらに具備することと、前記制御割り込み(NMI1)をトリガする手段(26)は、前記トリガコード(Code−DD)の取得に続いて、前記割り込みをトリガするように設計されていることとを特徴とする、請求項1または2記載のアクセス制御ハードウェアユニット。

【請求項4】

前記アクセス制御ハードウェアユニットは、前記トリガコード(Code−DD)を前記予め定められた基準値(Code−UMCA)と比較する手段(22)をさらに具備することと、前記トリガ手段(26)は、前記比較の結果によって、前記制御割り込み(NMI1)をトリガするように設計されていることとを特徴とする、請求項3記載のアクセス制御ハードウェアユニット。

【請求項5】

前記アクセス制御ハードウェアユニットは、前記アクセス認証コード(Code−AA)または前記トリガコード(Code−DD)が、前記予め定められた基準値(Code−UMCA)と異なっているとき、アラーム割り込みと呼ばれる、前記プロセッサの割り込みをトリガする手段(26)を具備することを特徴とする、請求項1ないし4のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項6】

前記アラーム割り込みは、マスク不可能割り込み(NMI2)であることを特徴とする、請求項5記載のアクセス制御ハードウェアユニット。

【請求項7】

前記予め定められた基準値(Code−UMCA)は、定数であることを特徴とする、請求項1ないし6のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項8】

前記アクセス制御ハードウェアユニットは、予め定められた法則にしたがって、前記基準値(Code−UMCA)を発生させる手段(24)を具備することを特徴とする、請求項1ないし6のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項9】

前記予め定められた基準値(Code−UMCA)は、前記ハードウェアユニットがスイッチオンされるとき(UMCA)、初期化されるカウンタであることと、前記予め定められた法則にしたがって、前記カウンタは、前記アクセス認証コード(Code−AA)が取得されるたびに増分されることとを特徴とする、請求項8記載のアクセス制御ハードウェアユニット。

【請求項10】

前記有効化手段(22、23、25)は、論理結合手段(25)を備え、前記論理結合手段(25)は、

前記周辺機器(P)に対するアクセスを要求する電気信号(CS−RQ、WE−RQ)を受信し、

前記有効化信号(SIG_VAL)を受信し、

前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)と、前記有効化信号の状態(VAL_0、VAL_1)と、真理値表で表される論理(25)との関数として、前記アクセス電気信号(CS、WE)を有効化する

ように設計されていることを特徴とする、請求項1ないし9のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項11】

前記アクセス制御ハードウェアユニットは、前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)を読み出す手段(26)と、アラーム割り込み(NMI2)と呼ばれ、好ましくはマスク不可能である、前記プロセッサの割り込みを、この状態(RQ_0、RQ_1)と、前記アクセス有効化電気信号(SIG_VAL)の状態(VAL_0、VAL_1)との関数として、トリガする手段(26)とを具備することを特徴とする、請求項10記載のアクセス制御ハードウェアユニット。

【請求項12】

前記アクセス制御ハードウェアユニットは、前記有効化信号(SIG_VAL)を抑止する手段(23)を具備することを特徴とする、請求項1ないし11のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項13】

前記抑止手段(23)は、前記周辺機器(P)に対する少なくとも1回のアクセスに続いて、前記有効化信号(SIG_VAL)を抑止するように設計されていることを特徴とする、請求項12記載のアクセス制御ハードウェアユニット。

【請求項14】

前記抑止手段(23)は、前記アクセス有効化電気信号(SIG_VAL)の発生から、または、前記アクセスコード(Code−AA)の取得から計算された予め定められた遅延の後、前記有効化信号(SIG_VAL)を抑止するように設計されていることを特徴とする、請求項12または13記載のアクセス制御ハードウェアユニット。

【請求項15】

プロセッサ(110)において、

請求項1ないし14のいずれか1項記載のアクセス制御ハードウェアユニット(20)と、

前記アクセス認証コード(Code−AA)を取得するように設計されている制御割り込みルーチン(IRT1)を実行する手段(VECT)と、

前記アクセス制御ハードウェアユニット(20)に前記アクセス認証コード(Code−AA)を送出する手段(IRT1)と

を備えることを特徴とするプロセッサ。

【請求項16】

前記制御割り込みルーチンは、保護されたメモリから前記アクセスコード(Code−AA)を読み出す手段を含むことを特徴とする、請求項15記載のプロセッサ。

【請求項17】

前記プロセッサは、前記アクセス制御ハードウェアユニット(20)にトリガコード(Code−DD)を送出する手段をさらに備えることを特徴とする、請求項15または16記載のプロセッサ。

【請求項18】

前記制御割り込みルーチン(IRT1)は、予め定められた法則にしたがって、前記アクセスコード(Code−AA)を発生させるように設計されていることを特徴とする、請求項15ないし17のいずれか1項記載のプロセッサ。

【請求項19】

前記アクセスコード(Code−AA)はカウンタであること、および、前記予め定められた法則は、前記プロセッサ(110)がスイッチオンされるときに、前記カウンタ(Code−AA)を初期化することと、前記コードが前記ハードウェアユニット(20)に送出されるたびに、前記カウンタを増分することとを含むことを特徴とする、請求項18記載のプロセッサ。

【請求項20】

前記プロセッサは、アラートを発生させるように、および/または、前記周辺機器(P)の使用を抑止するように設計されているアラーム割り込みルーチン(IRT2)を実行する手段(VECT)をさらに備えることを特徴とする、請求項15ないし19のいずれか1項記載のプロセッサ。

【請求項21】

前記プロセッサは、前記周辺機器(P)を備え、前記周辺機器(P)は、前記プロセッサのブートメモリ(120)に対する書き込み制御装置およびメモリ管理ユニット(MMU)から選択されることが特に可能であることを特徴とする、請求項15ないし20のいずれか1項記載のプロセッサ。

【請求項22】

プロセッサ(10、110、120)による、このプロセッサの周辺機器(P)に対するアクセスを制御する方法において、

制御割り込みと呼ばれる、前記プロセッサの割り込みをトリガするステップ(E34)と、

前記トリガ後に、前記周辺機器(P)に対するアクセス認証コード(Code−AA)を前記プロセッサから取得するステップ(E37)と、

前記アクセス認証コード(Code−AA)を予め定められた基準値(Code−UMCA)と比較するステップ(E38)と、

前記比較ステップ(E30)の結果によって、前記周辺機器(P)に対するアクセス信号(CS、WS、PWR)を有効化するための電気信号(SIG_VAL)を発生させるステップ(E50)と

を含むことを特徴とする方法。

【請求項23】

前記制御割り込みは、マスク不可能割り込み(NMI1)であることを特徴とする、請求項22記載のアクセス制御方法。

【請求項24】

前記トリガステップ(E34)は、トリガコード(Code−DD)を取得するステップ(E25)の後に実行されることを特徴とする、請求項22または23記載のアクセス制御方法。

【請求項25】

前記アクセス制御方法は、前記トリガコード(Code−DD)を前記予め定められた基準値(Code−UMCA)と比較するステップ(E30)をさらに含むことと、前記トリガステップ(E34)は、前記比較ステップ(E30)の結果によって、実行されることとを特徴とする、請求項24記載のアクセス制御方法。

【請求項26】

前記アクセス制御方法は、前記アクセス認証コード(Code−AA)または前記トリガコード(Code−DD)が、前記予め定められた基準値(Code−UMCA)と異なっているとき、アラーム割り込みと呼ばれる、前記プロセッサの割り込みをトリガするステップ(E100)を含むことを特徴とする、請求項22ないし25のいずれか1項記載のアクセス制御方法。

【請求項27】

前記アラーム割り込みは、マスク不可能割り込み(NMI2)であることを特徴とする、請求項26記載のアクセス制御方法。

【請求項28】

前記予め定められた基準値(Code−UMCA)は、定数であることを特徴とする、請求項22ないし27のいずれか1項記載のアクセス制御方法。

【請求項29】

前記アクセス制御方法は、予め定められた法則にしたがって、前記予め定められた基準値(Code−UMCA)を発生させるステップ(E40)をさらに含むことを特徴とする、請求項22ないし27のいずれか1項記載のアクセス制御方法。

【請求項30】

前記予め定められた基準値(Code−UMCA)はカウンタであり、前記アクセス制御方法は、前記カウンタを初期化するステップ(E10)をさらに含み、前記カウンタは前記発生ステップ(E40)の間に増分されることを特徴とする、請求項29記載のアクセス制御方法。

【請求項31】

前記アクセス制御方法において、

前記有効化信号を発生させるステップ(E50)の間に、

前記周辺機器(P)に対するアクセスを要求する電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)を読み出し、

前記有効化電気信号(SIG_VAL)の状態(VAL_0、VAL_1)を読み出し、

前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_1)と、前記有効化信号(SIG_VAL)の状態(VAL_1)と、論理ルールとの関数として、前記アクセス電気信号(CS、WE)を有効化する

ことを特徴とする、請求項22ないし30のいずれか1項記載のアクセス制御方法。

【請求項32】

前記アクセス制御方法は、前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)を読み出すステップ(E20、E36)と、アラーム割り込みと呼ばれ、好ましくはマスク不可能(NMI2)である、前記プロセッサのマスク可能割り込みを、前記状態(RQ_0、RQ_1)と、前記アクセス有効化電気信号(SIG_VAL)の状態(VAL_0、VAL_1)との関数として、トリガするステップ(E100)とを含むことを特徴とする、請求項31記載のアクセス制御方法。

【請求項33】

前記アクセス制御方法は、前記有効化信号(SIG_VAL)を抑止するステップ(E70)を含むことを特徴とする、請求項22ないし32のいずれか1項記載のアクセス制御方法。

【請求項34】

前記抑止ステップ(E70)は、少なくとも1回の前記周辺機器(P)に対してアクセスするステップ(E65)に続いて実行されることを特徴とする、請求項33記載のアクセス制御方法。

【請求項35】

前記抑止ステップは、前記有効化電気信号(SIG_VAL)を発生させるステップ(E50)から、または、前記トリガコード(Code−DD)を取得するステップ(E25)から計算された予め定められた遅延の後、実行されることを特徴とする、請求項33または34記載のアクセス制御方法。

【請求項36】

周辺機器(P)に対するアクセスを管理する方法において、

好ましくはマスク不可能(NMI1)である、制御割り込みに関係するルーチン(IRT1)を実行するステップを含み、前記制御ルーチンは、請求項1ないし14のいずれか1項記載のアクセス制御ハードウェアユニット(20)に、アクセス認証コード(Code−AA)を送出するステップ(E520)を含むことを特徴とする、周辺機器(P)に対するアクセスを管理する方法。

【請求項37】

前記アクセスを管理する方法は、前記送出に関して、前記アクセスコード(Code−AA)を保護されたメモリから読み出すステップを含むことを特徴とする、請求項36記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項38】

前記アクセスを管理する方法は、前記送出に関して、予め定められた法則にしたがって、前記周辺機器(P)に対するアクセスコード(Code−AA)を発生させるステップ(E510)を含むことを特徴とする、請求項36記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項39】

前記アクセス認証コード(Code−AA)はカウンタであり、前記アクセスを管理する方法は、前記カウンタ(Code−AA)を初期化するステップをさらに含むことと、前記発生ステップ(E510)は、前記ハードウェアユニット(20)に対するこのコード(Code−AA)の各送出(S100)の前に、前記カウンタ(Code−AA)を増分することを含むこととを特徴とする、請求項38記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項40】

前記アクセスを管理する方法は、アラーム割り込みルーチン(IRT2)を実行するステップをさらに含み、前記アラームルーチンは、アラートを発生させるステップ、および/または、前記周辺機器の使用を抑止するステップを含むことを特徴とする、請求項36ないし39のいずれか1項記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項41】

周辺機器(P)にアクセスするための命令(E630)を含むコンピュータプログラムにおいて、

前記アクセス命令の実行前に、請求項1ないし14のいずれか1項記載の、前記周辺機器(P)のアクセス制御ハードウェアユニット(20)に対してトリガコード(Code−DD)を送出する命令(E620)を含むことを特徴とする、コンピュータプログラム。

【請求項42】

前記コンピュータプログラムは、前記予め定められた法則にしたがって、前記トリガコード(Code−DD)を発生させる手段をさらに含むことを特徴とする、請求項41記載のコンピュータプログラム。

【請求項43】

前記プロセッサにおいて、

請求項22ないし35のいずれか1項記載のアクセス制御方法、および/または、請求項36ないし40のいずれか1項記載のアクセスを管理する方法、および/または、請求項41または42記載のコンピュータプログラムを実行するように設計されている、プロセッサ。

【請求項44】

請求項1ないし14のいずれか1項記載のアクセス制御ハードウェアユニット(20)の使用において、

スクリーン、キーボード、メモリ、通信インターフェイス制御装置、メモリ管理ユニット(MMU)、または、メモリ保護ユニット(MPU)から、特に選択することができる周辺機器(P)に対するアクセス信号を有効化する、アクセス制御ハードウェアユニット(20)の使用。

【請求項1】

プロセッサ(10、110、120)による、このプロセッサの周辺機器(P)に対するアクセスを制御するハードウェアユニット(20)において、

前記ハードウェアユニット(20)は、

制御割り込みと呼ばれる、前記プロセッサの割り込みをトリガする手段(26)と、

前記トリガ後に、前記周辺機器(P)に対するアクセス認証コード(Code−AA)を前記プロセッサから取得する手段(21)と、

前記アクセス認証コード(Code−AA)を予め定められた基準値(Code−UMCA)と比較する手段(22)と、

前記比較の結果によって、前記周辺機器(P)に対するアクセス電気信号(CS、WE、PWR)を有効化するための電気信号(SIG_VAL)を発生させるように設計されている、いわゆる有効化手段(22、23、25)と

を具備するハードウェアユニット。

【請求項2】

前記制御割り込みは、マスク不可能割り込み(NMI1)であることを特徴とする、請求項1記載のアクセス制御ハードウェアユニット。

【請求項3】

前記アクセス制御ハードウェアユニットは、トリガコード(Code−DD)を取得する手段(21)をさらに具備することと、前記制御割り込み(NMI1)をトリガする手段(26)は、前記トリガコード(Code−DD)の取得に続いて、前記割り込みをトリガするように設計されていることとを特徴とする、請求項1または2記載のアクセス制御ハードウェアユニット。

【請求項4】

前記アクセス制御ハードウェアユニットは、前記トリガコード(Code−DD)を前記予め定められた基準値(Code−UMCA)と比較する手段(22)をさらに具備することと、前記トリガ手段(26)は、前記比較の結果によって、前記制御割り込み(NMI1)をトリガするように設計されていることとを特徴とする、請求項3記載のアクセス制御ハードウェアユニット。

【請求項5】

前記アクセス制御ハードウェアユニットは、前記アクセス認証コード(Code−AA)または前記トリガコード(Code−DD)が、前記予め定められた基準値(Code−UMCA)と異なっているとき、アラーム割り込みと呼ばれる、前記プロセッサの割り込みをトリガする手段(26)を具備することを特徴とする、請求項1ないし4のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項6】

前記アラーム割り込みは、マスク不可能割り込み(NMI2)であることを特徴とする、請求項5記載のアクセス制御ハードウェアユニット。

【請求項7】

前記予め定められた基準値(Code−UMCA)は、定数であることを特徴とする、請求項1ないし6のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項8】

前記アクセス制御ハードウェアユニットは、予め定められた法則にしたがって、前記基準値(Code−UMCA)を発生させる手段(24)を具備することを特徴とする、請求項1ないし6のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項9】

前記予め定められた基準値(Code−UMCA)は、前記ハードウェアユニットがスイッチオンされるとき(UMCA)、初期化されるカウンタであることと、前記予め定められた法則にしたがって、前記カウンタは、前記アクセス認証コード(Code−AA)が取得されるたびに増分されることとを特徴とする、請求項8記載のアクセス制御ハードウェアユニット。

【請求項10】

前記有効化手段(22、23、25)は、論理結合手段(25)を備え、前記論理結合手段(25)は、

前記周辺機器(P)に対するアクセスを要求する電気信号(CS−RQ、WE−RQ)を受信し、

前記有効化信号(SIG_VAL)を受信し、

前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)と、前記有効化信号の状態(VAL_0、VAL_1)と、真理値表で表される論理(25)との関数として、前記アクセス電気信号(CS、WE)を有効化する

ように設計されていることを特徴とする、請求項1ないし9のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項11】

前記アクセス制御ハードウェアユニットは、前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)を読み出す手段(26)と、アラーム割り込み(NMI2)と呼ばれ、好ましくはマスク不可能である、前記プロセッサの割り込みを、この状態(RQ_0、RQ_1)と、前記アクセス有効化電気信号(SIG_VAL)の状態(VAL_0、VAL_1)との関数として、トリガする手段(26)とを具備することを特徴とする、請求項10記載のアクセス制御ハードウェアユニット。

【請求項12】

前記アクセス制御ハードウェアユニットは、前記有効化信号(SIG_VAL)を抑止する手段(23)を具備することを特徴とする、請求項1ないし11のいずれか1項記載のアクセス制御ハードウェアユニット。

【請求項13】

前記抑止手段(23)は、前記周辺機器(P)に対する少なくとも1回のアクセスに続いて、前記有効化信号(SIG_VAL)を抑止するように設計されていることを特徴とする、請求項12記載のアクセス制御ハードウェアユニット。

【請求項14】

前記抑止手段(23)は、前記アクセス有効化電気信号(SIG_VAL)の発生から、または、前記アクセスコード(Code−AA)の取得から計算された予め定められた遅延の後、前記有効化信号(SIG_VAL)を抑止するように設計されていることを特徴とする、請求項12または13記載のアクセス制御ハードウェアユニット。

【請求項15】

プロセッサ(110)において、

請求項1ないし14のいずれか1項記載のアクセス制御ハードウェアユニット(20)と、

前記アクセス認証コード(Code−AA)を取得するように設計されている制御割り込みルーチン(IRT1)を実行する手段(VECT)と、

前記アクセス制御ハードウェアユニット(20)に前記アクセス認証コード(Code−AA)を送出する手段(IRT1)と

を備えることを特徴とするプロセッサ。

【請求項16】

前記制御割り込みルーチンは、保護されたメモリから前記アクセスコード(Code−AA)を読み出す手段を含むことを特徴とする、請求項15記載のプロセッサ。

【請求項17】

前記プロセッサは、前記アクセス制御ハードウェアユニット(20)にトリガコード(Code−DD)を送出する手段をさらに備えることを特徴とする、請求項15または16記載のプロセッサ。

【請求項18】

前記制御割り込みルーチン(IRT1)は、予め定められた法則にしたがって、前記アクセスコード(Code−AA)を発生させるように設計されていることを特徴とする、請求項15ないし17のいずれか1項記載のプロセッサ。

【請求項19】

前記アクセスコード(Code−AA)はカウンタであること、および、前記予め定められた法則は、前記プロセッサ(110)がスイッチオンされるときに、前記カウンタ(Code−AA)を初期化することと、前記コードが前記ハードウェアユニット(20)に送出されるたびに、前記カウンタを増分することとを含むことを特徴とする、請求項18記載のプロセッサ。

【請求項20】

前記プロセッサは、アラートを発生させるように、および/または、前記周辺機器(P)の使用を抑止するように設計されているアラーム割り込みルーチン(IRT2)を実行する手段(VECT)をさらに備えることを特徴とする、請求項15ないし19のいずれか1項記載のプロセッサ。

【請求項21】

前記プロセッサは、前記周辺機器(P)を備え、前記周辺機器(P)は、前記プロセッサのブートメモリ(120)に対する書き込み制御装置およびメモリ管理ユニット(MMU)から選択されることが特に可能であることを特徴とする、請求項15ないし20のいずれか1項記載のプロセッサ。

【請求項22】

プロセッサ(10、110、120)による、このプロセッサの周辺機器(P)に対するアクセスを制御する方法において、

制御割り込みと呼ばれる、前記プロセッサの割り込みをトリガするステップ(E34)と、

前記トリガ後に、前記周辺機器(P)に対するアクセス認証コード(Code−AA)を前記プロセッサから取得するステップ(E37)と、

前記アクセス認証コード(Code−AA)を予め定められた基準値(Code−UMCA)と比較するステップ(E38)と、

前記比較ステップ(E30)の結果によって、前記周辺機器(P)に対するアクセス信号(CS、WS、PWR)を有効化するための電気信号(SIG_VAL)を発生させるステップ(E50)と

を含むことを特徴とする方法。

【請求項23】

前記制御割り込みは、マスク不可能割り込み(NMI1)であることを特徴とする、請求項22記載のアクセス制御方法。

【請求項24】

前記トリガステップ(E34)は、トリガコード(Code−DD)を取得するステップ(E25)の後に実行されることを特徴とする、請求項22または23記載のアクセス制御方法。

【請求項25】

前記アクセス制御方法は、前記トリガコード(Code−DD)を前記予め定められた基準値(Code−UMCA)と比較するステップ(E30)をさらに含むことと、前記トリガステップ(E34)は、前記比較ステップ(E30)の結果によって、実行されることとを特徴とする、請求項24記載のアクセス制御方法。

【請求項26】

前記アクセス制御方法は、前記アクセス認証コード(Code−AA)または前記トリガコード(Code−DD)が、前記予め定められた基準値(Code−UMCA)と異なっているとき、アラーム割り込みと呼ばれる、前記プロセッサの割り込みをトリガするステップ(E100)を含むことを特徴とする、請求項22ないし25のいずれか1項記載のアクセス制御方法。

【請求項27】

前記アラーム割り込みは、マスク不可能割り込み(NMI2)であることを特徴とする、請求項26記載のアクセス制御方法。

【請求項28】

前記予め定められた基準値(Code−UMCA)は、定数であることを特徴とする、請求項22ないし27のいずれか1項記載のアクセス制御方法。

【請求項29】

前記アクセス制御方法は、予め定められた法則にしたがって、前記予め定められた基準値(Code−UMCA)を発生させるステップ(E40)をさらに含むことを特徴とする、請求項22ないし27のいずれか1項記載のアクセス制御方法。

【請求項30】

前記予め定められた基準値(Code−UMCA)はカウンタであり、前記アクセス制御方法は、前記カウンタを初期化するステップ(E10)をさらに含み、前記カウンタは前記発生ステップ(E40)の間に増分されることを特徴とする、請求項29記載のアクセス制御方法。

【請求項31】

前記アクセス制御方法において、

前記有効化信号を発生させるステップ(E50)の間に、

前記周辺機器(P)に対するアクセスを要求する電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)を読み出し、

前記有効化電気信号(SIG_VAL)の状態(VAL_0、VAL_1)を読み出し、

前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_1)と、前記有効化信号(SIG_VAL)の状態(VAL_1)と、論理ルールとの関数として、前記アクセス電気信号(CS、WE)を有効化する

ことを特徴とする、請求項22ないし30のいずれか1項記載のアクセス制御方法。

【請求項32】

前記アクセス制御方法は、前記アクセス要求電気信号(CS−RQ、WE−RQ)の状態(RQ_0、RQ_1)を読み出すステップ(E20、E36)と、アラーム割り込みと呼ばれ、好ましくはマスク不可能(NMI2)である、前記プロセッサのマスク可能割り込みを、前記状態(RQ_0、RQ_1)と、前記アクセス有効化電気信号(SIG_VAL)の状態(VAL_0、VAL_1)との関数として、トリガするステップ(E100)とを含むことを特徴とする、請求項31記載のアクセス制御方法。

【請求項33】

前記アクセス制御方法は、前記有効化信号(SIG_VAL)を抑止するステップ(E70)を含むことを特徴とする、請求項22ないし32のいずれか1項記載のアクセス制御方法。

【請求項34】

前記抑止ステップ(E70)は、少なくとも1回の前記周辺機器(P)に対してアクセスするステップ(E65)に続いて実行されることを特徴とする、請求項33記載のアクセス制御方法。

【請求項35】

前記抑止ステップは、前記有効化電気信号(SIG_VAL)を発生させるステップ(E50)から、または、前記トリガコード(Code−DD)を取得するステップ(E25)から計算された予め定められた遅延の後、実行されることを特徴とする、請求項33または34記載のアクセス制御方法。

【請求項36】

周辺機器(P)に対するアクセスを管理する方法において、

好ましくはマスク不可能(NMI1)である、制御割り込みに関係するルーチン(IRT1)を実行するステップを含み、前記制御ルーチンは、請求項1ないし14のいずれか1項記載のアクセス制御ハードウェアユニット(20)に、アクセス認証コード(Code−AA)を送出するステップ(E520)を含むことを特徴とする、周辺機器(P)に対するアクセスを管理する方法。

【請求項37】

前記アクセスを管理する方法は、前記送出に関して、前記アクセスコード(Code−AA)を保護されたメモリから読み出すステップを含むことを特徴とする、請求項36記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項38】

前記アクセスを管理する方法は、前記送出に関して、予め定められた法則にしたがって、前記周辺機器(P)に対するアクセスコード(Code−AA)を発生させるステップ(E510)を含むことを特徴とする、請求項36記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項39】

前記アクセス認証コード(Code−AA)はカウンタであり、前記アクセスを管理する方法は、前記カウンタ(Code−AA)を初期化するステップをさらに含むことと、前記発生ステップ(E510)は、前記ハードウェアユニット(20)に対するこのコード(Code−AA)の各送出(S100)の前に、前記カウンタ(Code−AA)を増分することを含むこととを特徴とする、請求項38記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項40】

前記アクセスを管理する方法は、アラーム割り込みルーチン(IRT2)を実行するステップをさらに含み、前記アラームルーチンは、アラートを発生させるステップ、および/または、前記周辺機器の使用を抑止するステップを含むことを特徴とする、請求項36ないし39のいずれか1項記載の周辺機器(P)に対するアクセスを管理する方法。

【請求項41】

周辺機器(P)にアクセスするための命令(E630)を含むコンピュータプログラムにおいて、

前記アクセス命令の実行前に、請求項1ないし14のいずれか1項記載の、前記周辺機器(P)のアクセス制御ハードウェアユニット(20)に対してトリガコード(Code−DD)を送出する命令(E620)を含むことを特徴とする、コンピュータプログラム。

【請求項42】

前記コンピュータプログラムは、前記予め定められた法則にしたがって、前記トリガコード(Code−DD)を発生させる手段をさらに含むことを特徴とする、請求項41記載のコンピュータプログラム。

【請求項43】

前記プロセッサにおいて、

請求項22ないし35のいずれか1項記載のアクセス制御方法、および/または、請求項36ないし40のいずれか1項記載のアクセスを管理する方法、および/または、請求項41または42記載のコンピュータプログラムを実行するように設計されている、プロセッサ。

【請求項44】

請求項1ないし14のいずれか1項記載のアクセス制御ハードウェアユニット(20)の使用において、

スクリーン、キーボード、メモリ、通信インターフェイス制御装置、メモリ管理ユニット(MMU)、または、メモリ保護ユニット(MPU)から、特に選択することができる周辺機器(P)に対するアクセス信号を有効化する、アクセス制御ハードウェアユニット(20)の使用。

【図1】

【図2】

【図3】

【図4a】

【図4b】

【図5】

【図6】

【図2】

【図3】

【図4a】

【図4b】

【図5】

【図6】

【公表番号】特表2007−529803(P2007−529803A)

【公表日】平成19年10月25日(2007.10.25)

【国際特許分類】

【出願番号】特願2007−503380(P2007−503380)

【出願日】平成17年3月17日(2005.3.17)

【国際出願番号】PCT/FR2005/000648

【国際公開番号】WO2005/101160

【国際公開日】平成17年10月27日(2005.10.27)

【出願人】(506315583)セキュア・マシーンズ・エス.エー. (1)

【Fターム(参考)】

【公表日】平成19年10月25日(2007.10.25)

【国際特許分類】

【出願日】平成17年3月17日(2005.3.17)

【国際出願番号】PCT/FR2005/000648

【国際公開番号】WO2005/101160

【国際公開日】平成17年10月27日(2005.10.27)

【出願人】(506315583)セキュア・マシーンズ・エス.エー. (1)

【Fターム(参考)】

[ Back to top ]