固体撮像装置

【課題】多重サンプリングを適用した場合においても、小信号レベルでのRTSノイズの増大を抑制する。

【解決手段】画素PCとカラムADC回路3とマルチランプ波発生回路6とが設けられている。画素PCは、光電変換された信号を出力する。カラムADC回路3は、画素PCから出力された信号に応じて変化する信号レベルと基準電圧VREFとの比較結果に基づいて、画素PCの信号成分をCDSにて検出する。マルチランプ波発生回路6は、信号レベルと基準電圧との比較時にランプ波RW1の平均レベルを段階的に変化させながら、各段階L1〜L4において複数のランプ波RW1を生成し、信号レベルの小さい方に対応した段階L1〜L4から各段階L1〜L4ごとに複数のランプ波RWを基準電圧VREFとしてカラムADC回路3に順次出力する。

【解決手段】画素PCとカラムADC回路3とマルチランプ波発生回路6とが設けられている。画素PCは、光電変換された信号を出力する。カラムADC回路3は、画素PCから出力された信号に応じて変化する信号レベルと基準電圧VREFとの比較結果に基づいて、画素PCの信号成分をCDSにて検出する。マルチランプ波発生回路6は、信号レベルと基準電圧との比較時にランプ波RW1の平均レベルを段階的に変化させながら、各段階L1〜L4において複数のランプ波RW1を生成し、信号レベルの小さい方に対応した段階L1〜L4から各段階L1〜L4ごとに複数のランプ波RWを基準電圧VREFとしてカラムADC回路3に順次出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は固体撮像装置に関する。

【背景技術】

【0002】

固体撮像装置では、多重サンプリングによりランダムノイズを低減する方法が提案されている。

【0003】

しかしながら、多重サンプリングをCDS(相関2重サンプリング)に単純に適用すると、CDS間隔が長くなるため、RTSノイズや1/fノイズが増大し、特に、小信号レベルでノイズ低減効果が少ない。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】映情学技報 情報センシング 2006年7月 VOL,30,NO.38 P73−78

【非特許文献2】ISSCC2010 ”ISSCC Digest of Technical Papers, pp.396−398, Feb. 2010.

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、多重サンプリングを適用した場合においても、小信号レベルでのRTSノイズの増大を抑制することが可能な固体撮像装置を提供することである。

【課題を解決するための手段】

【0006】

実施形態の固体撮像装置によれば、画素とカラムADC回路と基準電圧発生回路とが設けられている。画素は、光電変換された信号を出力する。カラムADC回路は、前記画素から出力された信号に応じて変化する信号レベルと基準電圧との比較結果に基づいて、前記画素の信号成分をCDSにて検出する。基準電圧発生回路は、前記信号レベルと前記基準電圧との比較時にランプ波の平均レベルを段階的に変化させながら、各段階において複数のランプ波を生成し、前記信号レベルの小さい方に対応した段階から各段階ごとに複数のランプ波を前記基準電圧として前記カラムADC回路に順次出力する。

【図面の簡単な説明】

【0007】

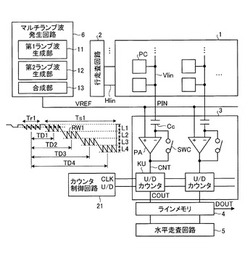

【図1】図1は、本発明の第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図2】図2は、図1の固体撮像装置の画素PCの構成例を示す回路図である。

【図3】図3は、図1の固体撮像装置の各部の波形を示すタイミングチャートである。

【図4】図4は、本発明の第2実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図5】図5は、図4の固体撮像装置の各部の波形を示すタイミングチャートである。

【図6】図6は、本発明の第3実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図7】図7は、図6の基準電圧発生回路6bにて生成される基準電圧VREFの波形の一部を拡大して示す図である。

【図8】図8は、本発明の第4実施形態に係る固体撮像装置の基準電圧VREFの波形の一部を拡大して示す図である。

【図9】図9は、本発明の第5実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図10】図10は、本発明の第6実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図11】図11は、図10の固体撮像装置の各部の波形を示すタイミングチャートである。

【図12】図12は、マルチランプ波発生回路の概略構成を示すブロック図である。

【発明を実施するための形態】

【0008】

以下、本発明の実施形態に係る固体撮像装置について図面を参照しながら説明する。

【0009】

(第1実施形態)

図1は、本発明の第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図1において、この固体撮像装置には、光電変換した電荷を蓄積する画素PCがロウ方向およびカラム方向にマトリックス状に配置された画素アレイ部1、読み出し対象となる画素PCを垂直方向に走査する行走査回路2、各画素PCの信号成分をCDSにて検出するカラムADC回路3、カラムADC回路3にて検出された信号成分を水平画素分だけ記憶するラインメモリ4、記憶したラインメモリ4から信号を読み出すための水平方向に走査する水平走査回路5、各画素PCから出力された信号に応じて変化する信号レベルと比較される基準電圧VREFを発生するマルチランプ波発生回路6およびカウンタ制御を行うカウンタ制御回路21が設けられている。

【0010】

ここで、画素アレイ部1において、ロウ方向には画素PCの読み出し制御を行う水平制御線Hlinが設けられ、カラム方向には画素PCから読み出された信号を伝送する垂直信号線Vlinが設けられている。

【0011】

また、カラムADC回路3には、各画素PCから出力された信号の基準レベルを保持するコンデンサCc、画素PCからの読み出し信号と基準電圧VREFとを比較するコンパレータPA、コンパレータPAの反転入力端子と出力端子を短絡するスイッチSWCおよびコンパレータPAの比較結果に基づいてアップカウウントおよびダウンカウントを行うことでCDSの基準レベルと信号レベルとの差分を算出するアップダウンカウンタKUがカラムごとに設けられている。

【0012】

また、マルチランプ波発生回路6は、各画素PCから出力された信号に応じて変化する信号レベルと基準電圧VREFとの比較時にランプ波RW1の平均レベルを段階的に変化させながら、各段階L1〜L4において複数のランプ波RW1を生成し、信号レベルの小さい方に対応した段階L1から各段階L1〜L4ごとに複数のランプ波RW1を基準電圧VREFとしてカラムADC回路3に順次出力することができる。

【0013】

ここで、マルチランプ波発生回路6には、小振幅のランプ波RW1を生成する第1のランプ波生成部11、大振幅の階段波を生成する第2のランプ波生成部12と同一時刻に生成した第1のランプ波と第2のランプ波を合成する合成部13が設けられている。なお、図1の実施形態では、階段状に発生した第2のランプ波により、カラムADC回路3にて検出される信号の検出レンジが4段階L1〜L4に分割される例を示した。

【0014】

カラムADC回路3の検出レンジとしては、例えば、カラムADC回路3の最小信号入力レベルから最大信号入力レベルまでに対応させることができる。例えば、カラムADC回路3の検出レンジが1024デジタル値まであるとすると、段階L1は0〜255デジタル値、段階L2は256〜511デジタル値、段階L3は512〜767デジタル値、段階L4は768〜1023デジタル値までの範囲に設定することができる。

【0015】

また、カラムADC回路3の検出レンジを分割する場合、必ずしも等分割する必要はなく、例えば、信号レベルが小さい時のCDS間隔TD1を小さくするために、段階L1の分割レンジを段階L2〜L4の分割レンジよりも小さくするようにしてもよい。

【0016】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3に伝送される。

【0017】

一方、画素PCから出力される基準レベル信号の検出期間Tr1では、マルチランプ波発生回路6の第1のランプ波生成部11にて複数のランプ波RW1が生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts1では、マルチランプ波発生回路6の第2のランプ生成部12にて各段階L1〜L4ごとに複数のランプ波RW1が生成され、コンパレータPAの非反転入力端子に順次入力される。

【0018】

そして、カラムADC回路3において、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0019】

ここで、アップダウンカウンタKUでは、多重サンプリングのために各画素PCからの基準レベル信号が基準電圧VREFのレベルとそれぞれ一致するまでダウンカウント動作が繰り返し行われる。同様に今度は各画素PCからの信号レベルが基準電圧VREFのレベルとそれぞれ一致するまでアップカウント動作が繰り返し行われる。その結果CDSにて検出される信号成分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0020】

なお、各画素PCから読み出された信号の信号レベルが段階L1にある場合は平均的なCDS間隔はTD1、各画素PCから読み出された信号の信号レベルが段階L2にある場合は平均的なCDS間隔はTD2、各画素PCから読み出された信号の信号レベルが段階L3にある場合は平均的なCDS間隔はTD3、各画素PCから読み出された信号の信号レベルが段階L4にある場合は平均的なCDS間隔はTD4になる。

【0021】

このため、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD1を、各画素PCから読み出された信号の信号レベルが大きい時のCDS間隔TD4よりも短くすることができ、多重サンプリングによりランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大を抑制することが可能となる。

【0022】

なお、図1の例では、ランプ波RW1の平均レベルをN=4段階L1〜L4に変化させる方法について説明したが、N(Nは2以上の整数)ならば何段階でもよい。また、図1の例では、多重サンプリングの回数Mを各段階L1〜L4ごとに4回とする方法について説明したが、M(Mは2以上の整数)ならば何回でもよい。また、多重サンプリングの回数を各段階L1〜L4ごとに異ならせるようにしてもよく、特に、信号レベルの大きい方に対応した段階における多重サンプリングの回数を信号レベルの小さい方に対応した段階における多重サンプリングの回より少なくするようにしてもよい。この多重サンプリングの回数の少ない分だけ大きい方の信号レベルを増幅する増幅回路を設けるようにしてもよい。

【0023】

また、上述した実施形態では、画素PCから読み出された信号をカラムADC回路3に直接入力する方法について説明したが、画素アレイ部1とカラムADC回路3との間にカラム増幅回路を設け、画素PCから読み出された信号をカラムごとに増幅してからカラムADC回路3に入力するようにしてもよい。

【0024】

図2は、図1の固体撮像装置の画素PCの構成例を示す回路図である。

図2(a)において、画素PCnには、フォトダイオードPD、行選択トランジスタTa、増幅トランジスタTb、リセットトランジスタTcおよび読み出しトランジスタTdがそれぞれ設けられている。また、増幅トランジスタTbとリセットトランジスタTcと読み出しトランジスタTdとの接続点には検出ノードとしてフローティングディフュージョンFDが形成されている。

【0025】

そして、読み出しトランジスタTdのソースは、フォトダイオードPDに接続され、読み出しトランジスタTdのゲートには、読み出し信号READnが入力される。また、リセットトランジスタTcのソースは、読み出しトランジスタTdのドレインに接続され、リセットトランジスタTcのゲートには、リセット信号RESETnが入力され、リセットトランジスタTcのドレインは、電源電位VDDに接続されている。また、行選択トランジスタTaのゲートには、行選択信号ADRESnが入力され、行選択トランジスタTaのドレインは、電源電位VDDに接続されている。また、増幅トランジスタTbのソースは、垂直信号線Vlinに接続され、増幅トランジスタTbのゲートは、読み出しトランジスタTdのドレインに接続され、増幅トランジスタTbのドレインは、行選択トランジスタTaのソースに接続されている。また、電流源Gは垂直信号線Vlinに接続されている。

【0026】

なお、図1の水平制御線Hlinは、読み出し信号READn、リセット信号RESETnおよび行選択信号ADRESnをロウごとに画素PCに伝送することができる。

【0027】

また、図2(b)において、画素PCn´では図2(a)の画素PCnから行選択トランジスタTaが省略されている。なお、この画素PCn´では、電源電位VDDとグランド電位を切り替えできるように構成されている。

【0028】

そして、非選択行では、リセットトランジスタTcを介してフローティングディフュージョンFDの電位をグランド電位に設定し、増幅トランジスタTbがオフされる。一方、選択行では、リセットトランジスタTcを介してフローティングディフュージョンFDの電位を電源電位VDDに設定し、増幅トランジスタTbがオンされる。

【0029】

また、図2(c)において、画素PCn´´では、読み出しトランジスタTd1およびフォトダイオードPD1が画素PCnに追加され、1個の増幅トランジスタTbがフォトダイオードPDの2画素で共用されている。

【0030】

また、図2(d)において、画素PCn´´´では、読み出しトランジスタTd1〜Td3およびフォトダイオードPD1〜PD3が画素PCnに追加され、1個の増幅トランジスタTbがフォトダイオードPDの4画素で共用されている。

【0031】

図3は、図1の固体撮像装置の各部の波形を示すタイミングチャートである。なお、以下の説明では、画素PCとして図2(a)の画素PCnを用いた場合を例にとる。

図3において、行選択信号ADRESnがロウレベルの場合、行選択トランジスタTaがオフ状態となりソースフォロワ動作しないため、垂直信号線Vlinに信号は出力されない。この時、読み出し信号READnとリセット信号RESETnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに排出される。そして、リセットトランジスタTcを介して電源VDDに排出される。

【0032】

フォトダイオードPDに蓄積されていた電荷が電源VDDに排出された後、読み出し信号READnがロウレベルになると、フォトダイオードPDでは、有効な信号電荷の蓄積が開始される。

【0033】

次に、行選択信号ADRESnがハイレベルになると、画素PCの行選択トランジスタTaがオンし、増幅トランジスタTbのドレインに電源電位VDDが印加されることで、増幅トランジスタTbと定電流トランジスタ(定電流源G)とでソースフォロアが構成される。

【0034】

そして、行選択トランジスタTaがオンの状態でリセット信号RESETnがハイレベルになると、リセットトランジスタTcがオンし、フローティングディフュージョンFDにリーク電流などで発生した余分な電荷がリセットされる。そして、フローティングディフュージョンFDの基準レベルに応じた電圧が増幅トランジスタTbのゲートにかかる。ここで、増幅トランジスタTbと定電流トランジスタ(定電流源G)とでソースフォロアが構成されているので、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、基準レベルの出力電圧VPINとして垂直信号線Vlinに出力される。

【0035】

ここで、画素PCから読み出された信号の基準レベルが出力されている時にスイッチSWCがオンされることで、コンパレータPAの反転入力端子の入力電圧が出力電圧でクランプされ、動作点が設定される。

【0036】

そして、スイッチSWCがオフされた後、基準レベル検出期間Tr1において基準レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW1が繰り返し与えられ、基準レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0037】

そして、基準レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW1ごとに基準レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて繰り返しダウンカウントされることで、多重サンプリングされた基準レベルの出力電圧PINがデジタル値COUTに変換され、アップダウンカウンタKUに保持される。例えば、基準レベルが4回だけ多重サンプリングされるものとすると、1回の基準レベルのサンプリングに対応したダウンカウントを4回だけ繰り返すことで、4回分の基準レベルのダウンカウント値を積算することができる。

【0038】

次に、画素PCnの行選択トランジスタTaがオンの状態で読み出し信号READnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに転送され、フローティングディフュージョンFDの信号レベルに応じた電圧が増幅トランジスタTbのゲートにかかる。ここで、増幅トランジスタTbと電流源Gとでソースフォロアが構成されているので、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、信号レベルの出力電圧PINとして垂直信号線Vlinに出力される。

【0039】

そして、信号レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW1が各段階L1〜L4ごとに繰り返し与えられ、信号レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0040】

そして、信号レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW1ごとに信号レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて今度は繰り返しアップカウントされることで、多重サンプリングされた信号レベルの出力電圧PINと基準レベルの出力電圧PINとの差分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。例えば、信号レベルが4回だけ多重サンプリングされるものとすると、1回の信号レベルのサンプリングに対応したアップカウントを4回だけ繰り返すことで、4回分の信号レベルのアップカウント値を積算することができる。そして、このラインメモリ4に保持されたデジタル値COUTが出力データDOUTとして出力される。

【0041】

これにより、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD1を、各画素PCから読み出された信号の信号レベルが大きい時のCDS間隔TD4よりも小さくすることができ、多重サンプリングによるランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大を抑制することが可能となる。

【0042】

(第2実施形態)

図4は、本発明の第2実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図4において、この固体撮像装置には、図1のカラムADC回路3およびマルチランプ波発生回路6の代わりにカラムADC回路3aおよびマルチランプ波発生回路6aが設けられている。

【0043】

マルチランプ波発生回路6aには、図1の第1のランプ波生成部11の代わりに第1のランプ波生成部11aが設けられている。この第1のランプ波生成部11aは、複数のランプ波RW2を生成することができる。ここで、ランプ波RW2には上り傾斜と下り傾斜とが設けられている。

【0044】

カラムADC回路3aには、図1のアップダウンカウンタKUの代わりにアップダウンカウンタKUaがカラムごとに設けられている。このアップダウンカウンタKUaは、ランプ波RW2の上り傾斜と下り傾斜の双方で、基準レベルをサンプリングするカウント動作を行ったり、信号レベルをサンプリングするカウント動作を行ったりすることができる。

【0045】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3aに伝送される。

【0046】

一方、基準レベル検出期間Tr2では、マルチランプ波発生回路6aの第1のランプ波生成部11aにて複数のランプ波RW2が生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts2では、マルチランプ波発生回路6aの第2のランプ生成部12にて各段階L1〜L4ごとに複数のランプ波RW2が生成され、コンパレータPAの非反転入力端子に順次入力される。

【0047】

そして、カラムADC回路3aにおいて、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0048】

ここで、アップダウンカウンタKUaでは、各画素PCの信号から多重サンプリングされた基準レベルが基準電圧VREFのレベルと上り傾斜側と下り傾斜側でそれぞれ一致するまでダウンカウント動作が繰り返し行われた後、今度は各画素PCの信号から多重サンプリングされた信号レベルが基準電圧VREFのレベルと上り傾斜側と下り傾斜側でそれぞれ一致するまでアップカウント動作が繰り返し行われることで、CDSにて検出される信号成分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0049】

ここで、基準電圧VREFの上り傾斜と下り傾斜の双方を利用してサンプリングを行わせることで、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD21を図1の方法よりも小さくすることができ、多重サンプリングによるランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大をより一層抑制することが可能となる。

【0050】

図5は、図4の固体撮像装置の各部の波形を示すタイミングチャートである。

図5において、行選択トランジスタTaがオンの状態でリセット信号RESETnがハイレベルになると、リセットトランジスタTcがオンし、フローティングディフュージョンFDの基準レベルに応じた電圧が増幅トランジスタTbのゲートにかかると、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、基準レベルの出力電圧VPINとして垂直信号線Vlinに出力される。

【0051】

ここで、画素PCから読み出された信号の基準レベルが出力されている時にスイッチSWCがオンされることで、コンパレータPAの反転入力端子の入力電圧が出力電圧でクランプされ、動作点が設定される。

【0052】

そして、スイッチSWCがオフされた後、基準レベル検出期間Tr2において基準レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW2が繰り返し与えられ、基準レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0053】

そして、基準電圧VREFのレベルが基準レベルの出力電圧PINより大きくなると、カウント動作が停止し、基準電圧VREFのレベルが基準レベルの出力電圧PINより小さくなるとアップダウンカウンタKUaにて繰り返しダウンカウントされることで、多重サンプリングされた基準レベルの出力電圧PINがデジタル値COUTに変換され、アップダウンカウンタKUaに保持される。

【0054】

次に、画素PCnの行選択トランジスタTaがオンの状態で読み出し信号READnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに転送される。このため、フローティングディフュージョンFDの信号レベルに応じた電圧が増幅トランジスタTbのゲートにかかり、信号レベルの出力電圧PINとして垂直信号線Vlinに出力される。

【0055】

そして、信号レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW2が各段階L1〜L4ごとに繰り返し与えられ、信号レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0056】

そして、基準電圧VREFのレベルが信号レベルの出力電圧PINより大きくなると、カウント動作が停止し、基準電圧VREFのレベルが基準レベルの出力電圧PINより小さくなるとアップダウンカウンタKUaにて今度は繰り返しアップカウントされることで、多重サンプリングされた信号レベルの出力電圧PINと基準レベルの出力電圧PINとの差分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0057】

これにより、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD21を短くすることができ、多重サンプリングによるランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大を抑制することが可能となる。なお、5回の多重サンプリングでは、ランダムノイズを1/√5=1/2.23に低減できる。

【0058】

(第3実施形態)

図6は、本発明の第3実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図6において、この固体撮像装置には、図1のマルチランプ波発生回路6の代わりにマルチランプ波発生回路6bが設けられている。

【0059】

マルチランプ波発生回路6bには、図1のマルチランプ波発生回路6の第1のランプ波生成部11の代わりに第1のランプ波生成部11bおよびスイープ起点制御部14が設けられている。

【0060】

第1のランプ波生成部11bは、カラムADC回路3のAD変換の分解能がその限界よりも荒くなるようにランプ波RW3の傾斜を設定することができる。スイープ起点制御部14は、各段階L1〜L4内において各ランプ波RW3のスイープの起点を異ならせることができる。

【0061】

なお、第1のランプ波生成部11bにて設定されたAD変換の分解能よりも細かくなるように各段階L1〜L4のランプ波RW3のスイープの起点を異ならせることが好ましい。

【0062】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3に伝送される。

【0063】

一方、基準レベル検出期間Tr3では、マルチランプ波発生回路6bにおいて、各段階L1〜L4のスイープの起点が異なるように複数のランプ波RW3が生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts3では、マルチランプ波発生回路6bの第1のランプ波生成部11bもしくは第2のランプ生成部12bにおいて、各段階L1〜L4内のスイープの起点が異なるように各段階L1〜L4ごとに複数のランプ波RW3が生成され、コンパレータPAの非反転入力端子に順次入力される。

【0064】

そして、カラムADC回路3において、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0065】

ここで、カラムADC回路3のAD変換の分解能がその限界よりも荒くなるようにランプ波RW3の傾斜を設定することにより、ランプ波RW3の傾斜を大きく(STEP回数を少なく)することができ、カラムADC回路3のAD変換処理を高速化することができる。

【0066】

また、各段階L1〜L4のランプ波RW3のスイープの起点を異ならせることにより、同一の信号レベルに対して各ランプ波RW3におけるサンプリング位置を異ならせることができる。このため、カラムADC回路3のAD変換の分解能がその限界よりも荒くなるようにランプ波RW3の傾斜が設定されている場合においても、信号レベルの検出時の分解能の低下を抑制することができる。

【0067】

図7は、図6のマルチランプ波発生回路6bにて生成される基準電圧VREFの波形の一部を拡大して示す図である。

図7において、例えば、段階L1は0〜255デジタル値までの範囲に設定され、段階L1のランプ波RW3として4個のランプ波RW3−1、RW3−2、RW3−3、RW3−4が発生されるものとする。

【0068】

また、各ランプ波RW3−1、RW3−2、RW3−3、RW3−4の1ステップ分は4デジタル値分に設定され、カラムADC回路3のAD変換の分解能の1/4に対応しているものする。この場合、各ランプ波RW3−1、RW3−2、RW3−3、RW3−4の傾斜は4倍になり、カラムADC回路3のAD変換の速度は4倍になる。

【0069】

また、ランプ波RW3−1のスイープの起点は0デジタル値に設定され、ランプ波RW3−1のスイープ範囲は0〜252デジタル値までの範囲に設定されている。ランプ波RW3−2のスイープの起点は1デジタル値に設定され、ランプ波RW3−2のスイープ範囲は1〜253デジタル値までの範囲に設定されている。ランプ波RW3−3のスイープの起点は2デジタル値に設定され、ランプ波RW3−3のスイープ範囲は2〜254デジタル値までの範囲に設定されている。ランプ波RW3−4のスイープの起点は3デジタル値に設定され、ランプ波RW3−4のスイープ範囲は4〜255デジタル値までの範囲に設定されている。

【0070】

そして、例えば、信号レベルの出力電圧PINが11〜12デジタル値の間にあるものとする。この場合、ランプ波RW3−1、RW3−2、RW3−3、RW3−4にて検出される信号レベルは8〜12デジタル値の間にある。

【0071】

ここで、ランプ波RW3−2は、ランプ波RW3−1に対して1デジタル値分だけスイープの起点がずれているので、もしも信号レベルが8〜9デジタル値の間にあるならば、ランプ波RW3−2にて検出される信号レベルは4〜8デジタル値の間になければならないが、実際は8〜12デジタル値の間にあるので、信号レベルは8〜9デジタル値の間にないことが判る。

【0072】

また、ランプ波RW3−3は、ランプ波RW3−1に対して2デジタル値分だけスイープの起点がずれているので、もしも信号レベルが9〜10デジタル値の間にあるならば、ランプ波RW3−3にて検出される信号レベルは4〜8デジタル値の間になければならないが、実際は8〜12デジタル値の間にあるので、信号レベルは9〜10デジタル値の間にないことが判る。

【0073】

また、ランプ波RW3−4は、ランプ波RW3−1に対して3デジタル値分だけスイープの起点がずれているので、もしも信号レベルが10〜11デジタル値の間にあるならば、ランプ波RW3−4にて検出される信号レベルは4〜8デジタル値の間になければならないが、実際は8〜12デジタル値の間にあるので、信号レベルは10〜11デジタル値の間にないことが判る。

【0074】

結局、ランプ波RW3−1、RW3−2、RW3−3、RW3−4にて検出される信号レベルは8〜12デジタル値の間であるにもかかわらず、8〜11デジタル値の間にないことが判るので、11〜12デジタル値の間にあることが判る。

【0075】

これにより、ランプ波RW3の傾斜を大きくした場合においても、信号レベルの分解能が低下するのを抑制することができ、画質の低下を抑制しつつ、カラムADC回路3のAD変換処理を高速化することができる。

【0076】

(第4実施形態)

図8は、本発明の第4実施形態に係る固体撮像装置の基準電圧VREFの波形の一部を拡大して示す図である。

図8において、図4のランプ波RW2の上り傾斜側と下り傾斜を利用してサンプリングを行う場合においても、ランプ波RW2よりも傾きが急なランプ波RW2´を生成し、ランプ波RW2´のスイープの起点を異ならせることにより、信号レベルの分解能が低下するのを抑制しつつ、カラムADC回路3aのAD変換処理を高速化することができる。

【0077】

(第5実施形態)

図9は、本発明の第5実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図9において、この固体撮像装置には、図1のカラムADC回路3およびラインメモリ4の代わりにカラムADC回路3b、ラインメモリ4a、4bおよび減算器7が設けられている。

【0078】

ここで、カラムADC回路3には、図1のアップダウンカウンタKUの代わりにカウンタKUbが設けられている。

【0079】

そして、カウンタKUbでは、各画素PCの信号から多重サンプリングされた基準レベルが基準電圧VREFのレベルとそれぞれ一致するまでアップカウント動作が繰り返し行われることで、各画素PCの信号の基準レベルがデジタル値COUTに変換され、水平画素分だけラインメモリ4aに保持される。

【0080】

また、カウンタKUbでは、各画素PCの信号から多重サンプリングされた信号レベルが基準電圧VREFのレベルとそれぞれ一致するまでアップカウント動作が繰り返し行われることで、各画素PCの信号の信号レベルがデジタル値COUTに変換され、水平画素分だけラインメモリ4bに保持される。

【0081】

そして、減算器7において、多重サンプリングされた信号レベルのデジタル値COUTと多重サンプリングされた基準レベルのデジタル値COUTとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0082】

ここで、ラインメモリ4の代わりにラインメモリ4a、4bを設けることにより、図1のアップダウンカウンタKUの代わりにカウンタKUbを設けた場合においても、CDS処理を実現することができる。

【0083】

(第6実施形態)

図10は、本発明の第6実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図10において、この固体撮像装置には、図1のマルチランプ波発生回路6の代わりにマルチランプ波発生回路6cが設けられている。マルチランプ波発生回路6cには、マルチランプ波発生回路6にランプ波間隔制御部15が追加されている。

【0084】

ランプ波間隔制御部15は、CDSにおける基準レベルの最後のサンプリング時刻から信号レベルの最初のサンプリング時刻までの時間間隔TD41と一致するように、基準レベルのサンプリングに用いられるランプ波RW4の間隔を調整することができる。

【0085】

また、ランプ波間隔制御部15は、CDSにおける基準レベルの最後のサンプリング時刻から信号レベルの最初のサンプリング時刻までの時間間隔TD41と一致するように、少なくとも信号レベルの小さい方に対応した段階L1での基準レベルのサンプリングに用いられるランプ波RW4の間隔を調整することができる。

【0086】

また、ランプ波間隔制御部15は、CDSにおける基準レベルの最後のサンプリング時刻から信号レベルの最初のサンプリング時刻までの時間間隔TD41の1/2の時間間隔TD42と一致するように、信号レベルの大きい方に対応した段階L2〜L4での基準レベルのサンプリングに用いられるランプ波RW5の間隔を調整することができる。

【0087】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3aに伝送される。

【0088】

一方、基準レベル検出期間Tr4において、複数のランプ波RW4が時間間隔TD41で生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts4において、段階L1では複数のランプ波RW4が時間間隔TD41で生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts4において、段階L2〜L4では複数のランプ波RW5が時間間隔TD42で生成され、コンパレータPAの非反転入力端子に順次入力される。

【0089】

そして、カラムADC回路3において、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0090】

ここで、基準レベルおよび段階L1の信号レベルのサンプリングに用いられるランプ波RW4の時間間隔をTD41に設定することにより、基準レベルおよび段階L1の信号レベルのRTSノイズを多重サンプリングにて効果的に低減させることができる。

【0091】

また、段階L2〜L4の信号レベルのサンプリングに用いられるランプ波RW5の時間間隔をTD42に設定することにより、信号処理にかかる時間の増大を抑制しつつ、段階L2〜L4の信号レベルのRTSノイズを多重サンプリングにて効果的に低減させることができる。

【0092】

なお、図10の例では、基準レベルおよび段階L1の信号レベルのサンプリングに用いられるランプ波RW4の時間間隔をTD41に設定し、段階L2〜L4の信号レベルのサンプリングに用いられるランプ波RW5の時間間隔をTD42に設定する方法について説明したが、段階L2〜L4の信号レベルのサンプリングに用いられるランプ波RW5の時間間隔もTD41に設定するようにしてもよい。

【0093】

図11は、図10の固体撮像装置の各部の波形を示すタイミングチャートである。

図11において、行選択トランジスタTaがオンの状態でリセット信号RESETnがハイレベルになると、リセットトランジスタTcがオンし、フローティングディフュージョンFDの基準レベルに応じた電圧が増幅トランジスタTbのゲートにかかると、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、基準レベルの出力電圧VPINとして垂直信号線Vlinに出力される。

【0094】

ここで、画素PCから読み出された信号の基準レベルが出力されている時にスイッチSWCがオンされることで、コンパレータPAの反転入力端子の入力電圧が出力電圧でクランプされ、動作点が設定される。

【0095】

そして、スイッチSWCがオフされた後、基準レベル検出期間Tr4において基準レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW4が繰り返し与えられ、基準レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0096】

そして、基準レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW4ごとに基準レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて繰り返しダウンカウントされることで、多重サンプリングされた基準レベルの出力電圧PINがデジタル値COUTに変換され、アップダウンカウンタKUに保持される。

【0097】

次に、画素PCnの行選択トランジスタTaがオンの状態で読み出し信号READnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに転送される。このため、フローティングディフュージョンFDの信号レベルに応じた電圧が増幅トランジスタTbのゲートにかかり、信号レベルの出力電圧PINとして垂直信号線Vlinに出力される。

【0098】

そして、信号レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW4が段階L1で繰り返し与えられた後、ランプ波RW5が段階L2〜L4ごとに繰り返し与えられ、信号レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0099】

そして、信号レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW4、RW5ごとに信号レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて今度は繰り返しアップカウントされることで、多重サンプリングされた信号レベルの出力電圧PINと基準レベルの出力電圧PINとの差分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0100】

これにより、多重サンプリングによるランダムノイズを低下させつつ、基準レベルおよび信号レベルのRTSノイズを多重サンプリングにて効果的に低減させることができる。RTSノイズの低減できる周波数は、少なくともCDS間隔TD41とその2倍さらに4倍のTD43で発生する3種類の揺らぎを効果的に低減させることができる。

【0101】

また、上述した実施形態では、デジタルCDS処理として信号の基準レベル信号と信号レベルの差を演算する回路にアップダウンカウンタと基準レベル信号と信号レベルを別々のラインメモリに保持し、読み出した出力信号の差分を演算する回路を用いた。他にも、基準レベル信号をアップカウンタでカウントし、カウント値を反転させる制御信号により値を反転させ、その後、信号レベルをアップカウントすることで2の補数を使ったカウンタ型の演算処理回路を設けるようにしてもよい。

【0102】

また、第1のランプ生成部でのランプ発生回数を第2のランプ生成部のランプ発生部で信号レベルが大きい時に第1のランプ波生成部で発生するランプ波の発生回数を削減することで、AD変換時間を短くすることで動作速度を早くすることができる。

さらに、前記第1のランプ波生成部で発生するランプ波の発生回数を削減したデジタル信号を増幅する増幅回路をさらに設けることで、光電変換特性を線形化することができる。

【0103】

図12にマルチランプ波発生回路の実施例を示す。

マルチランプ波発生回路は、オペアンプ31を使ったランプ波発生を実施している。

オペアンプ31の反転入力端子には、定電流源回路Iramp1を入力している。オペアンプ31の出力は、スイッチSWramp1を介して負入力端子に接続している。さらに、オペアンプ31の出力は、コンデンサCramp1を介して反転入力端子に接続している。スイッチSWramp1は、ランプ波間隔制御回路41の出力パルスPrampで第1のランプ波の周期Tra1を制御している。第1のランプ波の傾きは、定電流源回路Iramp1の電流量とコンデンサCramp1の容量で変化させることができる。よって、第1のランプ波の振幅は、第1ランプ波制御回路42により定電流源回路Iramp1の電流量を制御することで変化させることができる。

【0104】

オペアンプ31の正入力端子には、所定の電圧例えば1.5Vを発生させ入力する。この電圧は、定電流源回路Iramp2と抵抗R1と抵抗R2で発生したバイアス電圧を印加している。オペアンプ31の出力VREFは、この入力電圧と同じ電圧1.5Vが出力される。この時、スイッチSWramp1をONにすると、負入力電圧も1.5Vにセットされる。スイッチSWramp1をOFFにすると定電流源回路Iramp1で発生させた電流がコンデンサCramp1へ流れ込む。オペアンプ31の正と負の入力端子は、同じ電圧を維持するため、出力電圧が変化する。定電流源回路Iramp1が定電流で電流を流し込むため、出力は傾きが一定の第1のランプ波を発生する。

【0105】

時刻t4では、第2ランプ波制御回路43で抵抗R1の値を大きく変化させる。すると、Vramp2のバイアス電圧が変化する。同様に第2ランプ波制御回路43で抵抗R1の値をさらに大きく変化させることで、階段状の第2のランプ波Vramp2を生成することができる。さらに、スイープ起点制御回路44で、抵抗R2の値を小さく変化させることで、時刻t1,t2,t3のように、階段状に小さく変化させることができる。オペアンプ31の出力では、このVRamp2とVRamp1を合成したランプ波VREFを生成することができる。

【0106】

第2ランプ波制御回路43、さらにスイープ起点制御回路44は、ランプ波間隔制御回路41に同期した制御を実施している。

【符号の説明】

【0107】

PC、PCn、PCn´、PCn´´、PCn´´´、 画素、Ta 行選択トランジスタ、Tb 増幅トランジスタ、Tc リセットトランジスタ、Td、Td1〜Td3 読み出しトランジスタ、PD フォトダイオード、FD フローティングディフュージョン、G 電流源、Vlin 垂直信号線、Hlin 水平制御線、1 画素アレイ部、2 行走査回路、3、3a、3b カラムADC回路、4、4a、4b ラインメモリ、5 水平走査回路、6、6a〜6c マルチランプ波発生回路、7 減算器、PA コンパレータ、Cc コンデンサ、SWC スイッチ、KU、KUa アップダウンカウンタ、KUb カウンタ、11、11a、11b 第1のランプ波生成部、12 第2のランプ波生成部、13 合成部、14 スイープ起点制御部、15 ランプ波間隔制御部、21 カウンタ制御回路

【技術分野】

【0001】

本発明の実施形態は固体撮像装置に関する。

【背景技術】

【0002】

固体撮像装置では、多重サンプリングによりランダムノイズを低減する方法が提案されている。

【0003】

しかしながら、多重サンプリングをCDS(相関2重サンプリング)に単純に適用すると、CDS間隔が長くなるため、RTSノイズや1/fノイズが増大し、特に、小信号レベルでノイズ低減効果が少ない。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】映情学技報 情報センシング 2006年7月 VOL,30,NO.38 P73−78

【非特許文献2】ISSCC2010 ”ISSCC Digest of Technical Papers, pp.396−398, Feb. 2010.

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、多重サンプリングを適用した場合においても、小信号レベルでのRTSノイズの増大を抑制することが可能な固体撮像装置を提供することである。

【課題を解決するための手段】

【0006】

実施形態の固体撮像装置によれば、画素とカラムADC回路と基準電圧発生回路とが設けられている。画素は、光電変換された信号を出力する。カラムADC回路は、前記画素から出力された信号に応じて変化する信号レベルと基準電圧との比較結果に基づいて、前記画素の信号成分をCDSにて検出する。基準電圧発生回路は、前記信号レベルと前記基準電圧との比較時にランプ波の平均レベルを段階的に変化させながら、各段階において複数のランプ波を生成し、前記信号レベルの小さい方に対応した段階から各段階ごとに複数のランプ波を前記基準電圧として前記カラムADC回路に順次出力する。

【図面の簡単な説明】

【0007】

【図1】図1は、本発明の第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図2】図2は、図1の固体撮像装置の画素PCの構成例を示す回路図である。

【図3】図3は、図1の固体撮像装置の各部の波形を示すタイミングチャートである。

【図4】図4は、本発明の第2実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図5】図5は、図4の固体撮像装置の各部の波形を示すタイミングチャートである。

【図6】図6は、本発明の第3実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図7】図7は、図6の基準電圧発生回路6bにて生成される基準電圧VREFの波形の一部を拡大して示す図である。

【図8】図8は、本発明の第4実施形態に係る固体撮像装置の基準電圧VREFの波形の一部を拡大して示す図である。

【図9】図9は、本発明の第5実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図10】図10は、本発明の第6実施形態に係る固体撮像装置の概略構成を示すブロック図である。

【図11】図11は、図10の固体撮像装置の各部の波形を示すタイミングチャートである。

【図12】図12は、マルチランプ波発生回路の概略構成を示すブロック図である。

【発明を実施するための形態】

【0008】

以下、本発明の実施形態に係る固体撮像装置について図面を参照しながら説明する。

【0009】

(第1実施形態)

図1は、本発明の第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図1において、この固体撮像装置には、光電変換した電荷を蓄積する画素PCがロウ方向およびカラム方向にマトリックス状に配置された画素アレイ部1、読み出し対象となる画素PCを垂直方向に走査する行走査回路2、各画素PCの信号成分をCDSにて検出するカラムADC回路3、カラムADC回路3にて検出された信号成分を水平画素分だけ記憶するラインメモリ4、記憶したラインメモリ4から信号を読み出すための水平方向に走査する水平走査回路5、各画素PCから出力された信号に応じて変化する信号レベルと比較される基準電圧VREFを発生するマルチランプ波発生回路6およびカウンタ制御を行うカウンタ制御回路21が設けられている。

【0010】

ここで、画素アレイ部1において、ロウ方向には画素PCの読み出し制御を行う水平制御線Hlinが設けられ、カラム方向には画素PCから読み出された信号を伝送する垂直信号線Vlinが設けられている。

【0011】

また、カラムADC回路3には、各画素PCから出力された信号の基準レベルを保持するコンデンサCc、画素PCからの読み出し信号と基準電圧VREFとを比較するコンパレータPA、コンパレータPAの反転入力端子と出力端子を短絡するスイッチSWCおよびコンパレータPAの比較結果に基づいてアップカウウントおよびダウンカウントを行うことでCDSの基準レベルと信号レベルとの差分を算出するアップダウンカウンタKUがカラムごとに設けられている。

【0012】

また、マルチランプ波発生回路6は、各画素PCから出力された信号に応じて変化する信号レベルと基準電圧VREFとの比較時にランプ波RW1の平均レベルを段階的に変化させながら、各段階L1〜L4において複数のランプ波RW1を生成し、信号レベルの小さい方に対応した段階L1から各段階L1〜L4ごとに複数のランプ波RW1を基準電圧VREFとしてカラムADC回路3に順次出力することができる。

【0013】

ここで、マルチランプ波発生回路6には、小振幅のランプ波RW1を生成する第1のランプ波生成部11、大振幅の階段波を生成する第2のランプ波生成部12と同一時刻に生成した第1のランプ波と第2のランプ波を合成する合成部13が設けられている。なお、図1の実施形態では、階段状に発生した第2のランプ波により、カラムADC回路3にて検出される信号の検出レンジが4段階L1〜L4に分割される例を示した。

【0014】

カラムADC回路3の検出レンジとしては、例えば、カラムADC回路3の最小信号入力レベルから最大信号入力レベルまでに対応させることができる。例えば、カラムADC回路3の検出レンジが1024デジタル値まであるとすると、段階L1は0〜255デジタル値、段階L2は256〜511デジタル値、段階L3は512〜767デジタル値、段階L4は768〜1023デジタル値までの範囲に設定することができる。

【0015】

また、カラムADC回路3の検出レンジを分割する場合、必ずしも等分割する必要はなく、例えば、信号レベルが小さい時のCDS間隔TD1を小さくするために、段階L1の分割レンジを段階L2〜L4の分割レンジよりも小さくするようにしてもよい。

【0016】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3に伝送される。

【0017】

一方、画素PCから出力される基準レベル信号の検出期間Tr1では、マルチランプ波発生回路6の第1のランプ波生成部11にて複数のランプ波RW1が生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts1では、マルチランプ波発生回路6の第2のランプ生成部12にて各段階L1〜L4ごとに複数のランプ波RW1が生成され、コンパレータPAの非反転入力端子に順次入力される。

【0018】

そして、カラムADC回路3において、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0019】

ここで、アップダウンカウンタKUでは、多重サンプリングのために各画素PCからの基準レベル信号が基準電圧VREFのレベルとそれぞれ一致するまでダウンカウント動作が繰り返し行われる。同様に今度は各画素PCからの信号レベルが基準電圧VREFのレベルとそれぞれ一致するまでアップカウント動作が繰り返し行われる。その結果CDSにて検出される信号成分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0020】

なお、各画素PCから読み出された信号の信号レベルが段階L1にある場合は平均的なCDS間隔はTD1、各画素PCから読み出された信号の信号レベルが段階L2にある場合は平均的なCDS間隔はTD2、各画素PCから読み出された信号の信号レベルが段階L3にある場合は平均的なCDS間隔はTD3、各画素PCから読み出された信号の信号レベルが段階L4にある場合は平均的なCDS間隔はTD4になる。

【0021】

このため、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD1を、各画素PCから読み出された信号の信号レベルが大きい時のCDS間隔TD4よりも短くすることができ、多重サンプリングによりランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大を抑制することが可能となる。

【0022】

なお、図1の例では、ランプ波RW1の平均レベルをN=4段階L1〜L4に変化させる方法について説明したが、N(Nは2以上の整数)ならば何段階でもよい。また、図1の例では、多重サンプリングの回数Mを各段階L1〜L4ごとに4回とする方法について説明したが、M(Mは2以上の整数)ならば何回でもよい。また、多重サンプリングの回数を各段階L1〜L4ごとに異ならせるようにしてもよく、特に、信号レベルの大きい方に対応した段階における多重サンプリングの回数を信号レベルの小さい方に対応した段階における多重サンプリングの回より少なくするようにしてもよい。この多重サンプリングの回数の少ない分だけ大きい方の信号レベルを増幅する増幅回路を設けるようにしてもよい。

【0023】

また、上述した実施形態では、画素PCから読み出された信号をカラムADC回路3に直接入力する方法について説明したが、画素アレイ部1とカラムADC回路3との間にカラム増幅回路を設け、画素PCから読み出された信号をカラムごとに増幅してからカラムADC回路3に入力するようにしてもよい。

【0024】

図2は、図1の固体撮像装置の画素PCの構成例を示す回路図である。

図2(a)において、画素PCnには、フォトダイオードPD、行選択トランジスタTa、増幅トランジスタTb、リセットトランジスタTcおよび読み出しトランジスタTdがそれぞれ設けられている。また、増幅トランジスタTbとリセットトランジスタTcと読み出しトランジスタTdとの接続点には検出ノードとしてフローティングディフュージョンFDが形成されている。

【0025】

そして、読み出しトランジスタTdのソースは、フォトダイオードPDに接続され、読み出しトランジスタTdのゲートには、読み出し信号READnが入力される。また、リセットトランジスタTcのソースは、読み出しトランジスタTdのドレインに接続され、リセットトランジスタTcのゲートには、リセット信号RESETnが入力され、リセットトランジスタTcのドレインは、電源電位VDDに接続されている。また、行選択トランジスタTaのゲートには、行選択信号ADRESnが入力され、行選択トランジスタTaのドレインは、電源電位VDDに接続されている。また、増幅トランジスタTbのソースは、垂直信号線Vlinに接続され、増幅トランジスタTbのゲートは、読み出しトランジスタTdのドレインに接続され、増幅トランジスタTbのドレインは、行選択トランジスタTaのソースに接続されている。また、電流源Gは垂直信号線Vlinに接続されている。

【0026】

なお、図1の水平制御線Hlinは、読み出し信号READn、リセット信号RESETnおよび行選択信号ADRESnをロウごとに画素PCに伝送することができる。

【0027】

また、図2(b)において、画素PCn´では図2(a)の画素PCnから行選択トランジスタTaが省略されている。なお、この画素PCn´では、電源電位VDDとグランド電位を切り替えできるように構成されている。

【0028】

そして、非選択行では、リセットトランジスタTcを介してフローティングディフュージョンFDの電位をグランド電位に設定し、増幅トランジスタTbがオフされる。一方、選択行では、リセットトランジスタTcを介してフローティングディフュージョンFDの電位を電源電位VDDに設定し、増幅トランジスタTbがオンされる。

【0029】

また、図2(c)において、画素PCn´´では、読み出しトランジスタTd1およびフォトダイオードPD1が画素PCnに追加され、1個の増幅トランジスタTbがフォトダイオードPDの2画素で共用されている。

【0030】

また、図2(d)において、画素PCn´´´では、読み出しトランジスタTd1〜Td3およびフォトダイオードPD1〜PD3が画素PCnに追加され、1個の増幅トランジスタTbがフォトダイオードPDの4画素で共用されている。

【0031】

図3は、図1の固体撮像装置の各部の波形を示すタイミングチャートである。なお、以下の説明では、画素PCとして図2(a)の画素PCnを用いた場合を例にとる。

図3において、行選択信号ADRESnがロウレベルの場合、行選択トランジスタTaがオフ状態となりソースフォロワ動作しないため、垂直信号線Vlinに信号は出力されない。この時、読み出し信号READnとリセット信号RESETnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに排出される。そして、リセットトランジスタTcを介して電源VDDに排出される。

【0032】

フォトダイオードPDに蓄積されていた電荷が電源VDDに排出された後、読み出し信号READnがロウレベルになると、フォトダイオードPDでは、有効な信号電荷の蓄積が開始される。

【0033】

次に、行選択信号ADRESnがハイレベルになると、画素PCの行選択トランジスタTaがオンし、増幅トランジスタTbのドレインに電源電位VDDが印加されることで、増幅トランジスタTbと定電流トランジスタ(定電流源G)とでソースフォロアが構成される。

【0034】

そして、行選択トランジスタTaがオンの状態でリセット信号RESETnがハイレベルになると、リセットトランジスタTcがオンし、フローティングディフュージョンFDにリーク電流などで発生した余分な電荷がリセットされる。そして、フローティングディフュージョンFDの基準レベルに応じた電圧が増幅トランジスタTbのゲートにかかる。ここで、増幅トランジスタTbと定電流トランジスタ(定電流源G)とでソースフォロアが構成されているので、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、基準レベルの出力電圧VPINとして垂直信号線Vlinに出力される。

【0035】

ここで、画素PCから読み出された信号の基準レベルが出力されている時にスイッチSWCがオンされることで、コンパレータPAの反転入力端子の入力電圧が出力電圧でクランプされ、動作点が設定される。

【0036】

そして、スイッチSWCがオフされた後、基準レベル検出期間Tr1において基準レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW1が繰り返し与えられ、基準レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0037】

そして、基準レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW1ごとに基準レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて繰り返しダウンカウントされることで、多重サンプリングされた基準レベルの出力電圧PINがデジタル値COUTに変換され、アップダウンカウンタKUに保持される。例えば、基準レベルが4回だけ多重サンプリングされるものとすると、1回の基準レベルのサンプリングに対応したダウンカウントを4回だけ繰り返すことで、4回分の基準レベルのダウンカウント値を積算することができる。

【0038】

次に、画素PCnの行選択トランジスタTaがオンの状態で読み出し信号READnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに転送され、フローティングディフュージョンFDの信号レベルに応じた電圧が増幅トランジスタTbのゲートにかかる。ここで、増幅トランジスタTbと電流源Gとでソースフォロアが構成されているので、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、信号レベルの出力電圧PINとして垂直信号線Vlinに出力される。

【0039】

そして、信号レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW1が各段階L1〜L4ごとに繰り返し与えられ、信号レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0040】

そして、信号レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW1ごとに信号レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて今度は繰り返しアップカウントされることで、多重サンプリングされた信号レベルの出力電圧PINと基準レベルの出力電圧PINとの差分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。例えば、信号レベルが4回だけ多重サンプリングされるものとすると、1回の信号レベルのサンプリングに対応したアップカウントを4回だけ繰り返すことで、4回分の信号レベルのアップカウント値を積算することができる。そして、このラインメモリ4に保持されたデジタル値COUTが出力データDOUTとして出力される。

【0041】

これにより、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD1を、各画素PCから読み出された信号の信号レベルが大きい時のCDS間隔TD4よりも小さくすることができ、多重サンプリングによるランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大を抑制することが可能となる。

【0042】

(第2実施形態)

図4は、本発明の第2実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図4において、この固体撮像装置には、図1のカラムADC回路3およびマルチランプ波発生回路6の代わりにカラムADC回路3aおよびマルチランプ波発生回路6aが設けられている。

【0043】

マルチランプ波発生回路6aには、図1の第1のランプ波生成部11の代わりに第1のランプ波生成部11aが設けられている。この第1のランプ波生成部11aは、複数のランプ波RW2を生成することができる。ここで、ランプ波RW2には上り傾斜と下り傾斜とが設けられている。

【0044】

カラムADC回路3aには、図1のアップダウンカウンタKUの代わりにアップダウンカウンタKUaがカラムごとに設けられている。このアップダウンカウンタKUaは、ランプ波RW2の上り傾斜と下り傾斜の双方で、基準レベルをサンプリングするカウント動作を行ったり、信号レベルをサンプリングするカウント動作を行ったりすることができる。

【0045】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3aに伝送される。

【0046】

一方、基準レベル検出期間Tr2では、マルチランプ波発生回路6aの第1のランプ波生成部11aにて複数のランプ波RW2が生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts2では、マルチランプ波発生回路6aの第2のランプ生成部12にて各段階L1〜L4ごとに複数のランプ波RW2が生成され、コンパレータPAの非反転入力端子に順次入力される。

【0047】

そして、カラムADC回路3aにおいて、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0048】

ここで、アップダウンカウンタKUaでは、各画素PCの信号から多重サンプリングされた基準レベルが基準電圧VREFのレベルと上り傾斜側と下り傾斜側でそれぞれ一致するまでダウンカウント動作が繰り返し行われた後、今度は各画素PCの信号から多重サンプリングされた信号レベルが基準電圧VREFのレベルと上り傾斜側と下り傾斜側でそれぞれ一致するまでアップカウント動作が繰り返し行われることで、CDSにて検出される信号成分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0049】

ここで、基準電圧VREFの上り傾斜と下り傾斜の双方を利用してサンプリングを行わせることで、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD21を図1の方法よりも小さくすることができ、多重サンプリングによるランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大をより一層抑制することが可能となる。

【0050】

図5は、図4の固体撮像装置の各部の波形を示すタイミングチャートである。

図5において、行選択トランジスタTaがオンの状態でリセット信号RESETnがハイレベルになると、リセットトランジスタTcがオンし、フローティングディフュージョンFDの基準レベルに応じた電圧が増幅トランジスタTbのゲートにかかると、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、基準レベルの出力電圧VPINとして垂直信号線Vlinに出力される。

【0051】

ここで、画素PCから読み出された信号の基準レベルが出力されている時にスイッチSWCがオンされることで、コンパレータPAの反転入力端子の入力電圧が出力電圧でクランプされ、動作点が設定される。

【0052】

そして、スイッチSWCがオフされた後、基準レベル検出期間Tr2において基準レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW2が繰り返し与えられ、基準レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0053】

そして、基準電圧VREFのレベルが基準レベルの出力電圧PINより大きくなると、カウント動作が停止し、基準電圧VREFのレベルが基準レベルの出力電圧PINより小さくなるとアップダウンカウンタKUaにて繰り返しダウンカウントされることで、多重サンプリングされた基準レベルの出力電圧PINがデジタル値COUTに変換され、アップダウンカウンタKUaに保持される。

【0054】

次に、画素PCnの行選択トランジスタTaがオンの状態で読み出し信号READnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに転送される。このため、フローティングディフュージョンFDの信号レベルに応じた電圧が増幅トランジスタTbのゲートにかかり、信号レベルの出力電圧PINとして垂直信号線Vlinに出力される。

【0055】

そして、信号レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW2が各段階L1〜L4ごとに繰り返し与えられ、信号レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0056】

そして、基準電圧VREFのレベルが信号レベルの出力電圧PINより大きくなると、カウント動作が停止し、基準電圧VREFのレベルが基準レベルの出力電圧PINより小さくなるとアップダウンカウンタKUaにて今度は繰り返しアップカウントされることで、多重サンプリングされた信号レベルの出力電圧PINと基準レベルの出力電圧PINとの差分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0057】

これにより、各画素PCから読み出された信号の信号レベルが小さい時のCDS間隔TD21を短くすることができ、多重サンプリングによるランダムノイズを低下させつつ、小信号レベルでのRTSノイズや1/fノイズの増大を抑制することが可能となる。なお、5回の多重サンプリングでは、ランダムノイズを1/√5=1/2.23に低減できる。

【0058】

(第3実施形態)

図6は、本発明の第3実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図6において、この固体撮像装置には、図1のマルチランプ波発生回路6の代わりにマルチランプ波発生回路6bが設けられている。

【0059】

マルチランプ波発生回路6bには、図1のマルチランプ波発生回路6の第1のランプ波生成部11の代わりに第1のランプ波生成部11bおよびスイープ起点制御部14が設けられている。

【0060】

第1のランプ波生成部11bは、カラムADC回路3のAD変換の分解能がその限界よりも荒くなるようにランプ波RW3の傾斜を設定することができる。スイープ起点制御部14は、各段階L1〜L4内において各ランプ波RW3のスイープの起点を異ならせることができる。

【0061】

なお、第1のランプ波生成部11bにて設定されたAD変換の分解能よりも細かくなるように各段階L1〜L4のランプ波RW3のスイープの起点を異ならせることが好ましい。

【0062】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3に伝送される。

【0063】

一方、基準レベル検出期間Tr3では、マルチランプ波発生回路6bにおいて、各段階L1〜L4のスイープの起点が異なるように複数のランプ波RW3が生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts3では、マルチランプ波発生回路6bの第1のランプ波生成部11bもしくは第2のランプ生成部12bにおいて、各段階L1〜L4内のスイープの起点が異なるように各段階L1〜L4ごとに複数のランプ波RW3が生成され、コンパレータPAの非反転入力端子に順次入力される。

【0064】

そして、カラムADC回路3において、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0065】

ここで、カラムADC回路3のAD変換の分解能がその限界よりも荒くなるようにランプ波RW3の傾斜を設定することにより、ランプ波RW3の傾斜を大きく(STEP回数を少なく)することができ、カラムADC回路3のAD変換処理を高速化することができる。

【0066】

また、各段階L1〜L4のランプ波RW3のスイープの起点を異ならせることにより、同一の信号レベルに対して各ランプ波RW3におけるサンプリング位置を異ならせることができる。このため、カラムADC回路3のAD変換の分解能がその限界よりも荒くなるようにランプ波RW3の傾斜が設定されている場合においても、信号レベルの検出時の分解能の低下を抑制することができる。

【0067】

図7は、図6のマルチランプ波発生回路6bにて生成される基準電圧VREFの波形の一部を拡大して示す図である。

図7において、例えば、段階L1は0〜255デジタル値までの範囲に設定され、段階L1のランプ波RW3として4個のランプ波RW3−1、RW3−2、RW3−3、RW3−4が発生されるものとする。

【0068】

また、各ランプ波RW3−1、RW3−2、RW3−3、RW3−4の1ステップ分は4デジタル値分に設定され、カラムADC回路3のAD変換の分解能の1/4に対応しているものする。この場合、各ランプ波RW3−1、RW3−2、RW3−3、RW3−4の傾斜は4倍になり、カラムADC回路3のAD変換の速度は4倍になる。

【0069】

また、ランプ波RW3−1のスイープの起点は0デジタル値に設定され、ランプ波RW3−1のスイープ範囲は0〜252デジタル値までの範囲に設定されている。ランプ波RW3−2のスイープの起点は1デジタル値に設定され、ランプ波RW3−2のスイープ範囲は1〜253デジタル値までの範囲に設定されている。ランプ波RW3−3のスイープの起点は2デジタル値に設定され、ランプ波RW3−3のスイープ範囲は2〜254デジタル値までの範囲に設定されている。ランプ波RW3−4のスイープの起点は3デジタル値に設定され、ランプ波RW3−4のスイープ範囲は4〜255デジタル値までの範囲に設定されている。

【0070】

そして、例えば、信号レベルの出力電圧PINが11〜12デジタル値の間にあるものとする。この場合、ランプ波RW3−1、RW3−2、RW3−3、RW3−4にて検出される信号レベルは8〜12デジタル値の間にある。

【0071】

ここで、ランプ波RW3−2は、ランプ波RW3−1に対して1デジタル値分だけスイープの起点がずれているので、もしも信号レベルが8〜9デジタル値の間にあるならば、ランプ波RW3−2にて検出される信号レベルは4〜8デジタル値の間になければならないが、実際は8〜12デジタル値の間にあるので、信号レベルは8〜9デジタル値の間にないことが判る。

【0072】

また、ランプ波RW3−3は、ランプ波RW3−1に対して2デジタル値分だけスイープの起点がずれているので、もしも信号レベルが9〜10デジタル値の間にあるならば、ランプ波RW3−3にて検出される信号レベルは4〜8デジタル値の間になければならないが、実際は8〜12デジタル値の間にあるので、信号レベルは9〜10デジタル値の間にないことが判る。

【0073】

また、ランプ波RW3−4は、ランプ波RW3−1に対して3デジタル値分だけスイープの起点がずれているので、もしも信号レベルが10〜11デジタル値の間にあるならば、ランプ波RW3−4にて検出される信号レベルは4〜8デジタル値の間になければならないが、実際は8〜12デジタル値の間にあるので、信号レベルは10〜11デジタル値の間にないことが判る。

【0074】

結局、ランプ波RW3−1、RW3−2、RW3−3、RW3−4にて検出される信号レベルは8〜12デジタル値の間であるにもかかわらず、8〜11デジタル値の間にないことが判るので、11〜12デジタル値の間にあることが判る。

【0075】

これにより、ランプ波RW3の傾斜を大きくした場合においても、信号レベルの分解能が低下するのを抑制することができ、画質の低下を抑制しつつ、カラムADC回路3のAD変換処理を高速化することができる。

【0076】

(第4実施形態)

図8は、本発明の第4実施形態に係る固体撮像装置の基準電圧VREFの波形の一部を拡大して示す図である。

図8において、図4のランプ波RW2の上り傾斜側と下り傾斜を利用してサンプリングを行う場合においても、ランプ波RW2よりも傾きが急なランプ波RW2´を生成し、ランプ波RW2´のスイープの起点を異ならせることにより、信号レベルの分解能が低下するのを抑制しつつ、カラムADC回路3aのAD変換処理を高速化することができる。

【0077】

(第5実施形態)

図9は、本発明の第5実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図9において、この固体撮像装置には、図1のカラムADC回路3およびラインメモリ4の代わりにカラムADC回路3b、ラインメモリ4a、4bおよび減算器7が設けられている。

【0078】

ここで、カラムADC回路3には、図1のアップダウンカウンタKUの代わりにカウンタKUbが設けられている。

【0079】

そして、カウンタKUbでは、各画素PCの信号から多重サンプリングされた基準レベルが基準電圧VREFのレベルとそれぞれ一致するまでアップカウント動作が繰り返し行われることで、各画素PCの信号の基準レベルがデジタル値COUTに変換され、水平画素分だけラインメモリ4aに保持される。

【0080】

また、カウンタKUbでは、各画素PCの信号から多重サンプリングされた信号レベルが基準電圧VREFのレベルとそれぞれ一致するまでアップカウント動作が繰り返し行われることで、各画素PCの信号の信号レベルがデジタル値COUTに変換され、水平画素分だけラインメモリ4bに保持される。

【0081】

そして、減算器7において、多重サンプリングされた信号レベルのデジタル値COUTと多重サンプリングされた基準レベルのデジタル値COUTとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0082】

ここで、ラインメモリ4の代わりにラインメモリ4a、4bを設けることにより、図1のアップダウンカウンタKUの代わりにカウンタKUbを設けた場合においても、CDS処理を実現することができる。

【0083】

(第6実施形態)

図10は、本発明の第6実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図10において、この固体撮像装置には、図1のマルチランプ波発生回路6の代わりにマルチランプ波発生回路6cが設けられている。マルチランプ波発生回路6cには、マルチランプ波発生回路6にランプ波間隔制御部15が追加されている。

【0084】

ランプ波間隔制御部15は、CDSにおける基準レベルの最後のサンプリング時刻から信号レベルの最初のサンプリング時刻までの時間間隔TD41と一致するように、基準レベルのサンプリングに用いられるランプ波RW4の間隔を調整することができる。

【0085】

また、ランプ波間隔制御部15は、CDSにおける基準レベルの最後のサンプリング時刻から信号レベルの最初のサンプリング時刻までの時間間隔TD41と一致するように、少なくとも信号レベルの小さい方に対応した段階L1での基準レベルのサンプリングに用いられるランプ波RW4の間隔を調整することができる。

【0086】

また、ランプ波間隔制御部15は、CDSにおける基準レベルの最後のサンプリング時刻から信号レベルの最初のサンプリング時刻までの時間間隔TD41の1/2の時間間隔TD42と一致するように、信号レベルの大きい方に対応した段階L2〜L4での基準レベルのサンプリングに用いられるランプ波RW5の間隔を調整することができる。

【0087】

そして、行走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向の画素PCが選択され、その画素PCから読み出された信号は垂直信号線Vlinを介してカラムADC回路3aに伝送される。

【0088】

一方、基準レベル検出期間Tr4において、複数のランプ波RW4が時間間隔TD41で生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts4において、段階L1では複数のランプ波RW4が時間間隔TD41で生成され、コンパレータPAの非反転入力端子に順次入力される。また、信号レベル検出期間Ts4において、段階L2〜L4では複数のランプ波RW5が時間間隔TD42で生成され、コンパレータPAの非反転入力端子に順次入力される。

【0089】

そして、カラムADC回路3において、各画素PCの信号から基準レベルが多重サンプリングされるとともに、各画素PCの信号から信号レベルに応じた段階L1〜L4において信号レベルが多重サンプリングされる。そして、多重サンプリングされた信号レベルと多重サンプリングされた基準レベルとの差分がとられることで各画素PCの信号成分がCDSにて検出される。

【0090】

ここで、基準レベルおよび段階L1の信号レベルのサンプリングに用いられるランプ波RW4の時間間隔をTD41に設定することにより、基準レベルおよび段階L1の信号レベルのRTSノイズを多重サンプリングにて効果的に低減させることができる。

【0091】

また、段階L2〜L4の信号レベルのサンプリングに用いられるランプ波RW5の時間間隔をTD42に設定することにより、信号処理にかかる時間の増大を抑制しつつ、段階L2〜L4の信号レベルのRTSノイズを多重サンプリングにて効果的に低減させることができる。

【0092】

なお、図10の例では、基準レベルおよび段階L1の信号レベルのサンプリングに用いられるランプ波RW4の時間間隔をTD41に設定し、段階L2〜L4の信号レベルのサンプリングに用いられるランプ波RW5の時間間隔をTD42に設定する方法について説明したが、段階L2〜L4の信号レベルのサンプリングに用いられるランプ波RW5の時間間隔もTD41に設定するようにしてもよい。

【0093】

図11は、図10の固体撮像装置の各部の波形を示すタイミングチャートである。

図11において、行選択トランジスタTaがオンの状態でリセット信号RESETnがハイレベルになると、リセットトランジスタTcがオンし、フローティングディフュージョンFDの基準レベルに応じた電圧が増幅トランジスタTbのゲートにかかると、増幅トランジスタTbのゲートに印加された電圧に垂直信号線Vlinの電圧が追従し、基準レベルの出力電圧VPINとして垂直信号線Vlinに出力される。

【0094】

ここで、画素PCから読み出された信号の基準レベルが出力されている時にスイッチSWCがオンされることで、コンパレータPAの反転入力端子の入力電圧が出力電圧でクランプされ、動作点が設定される。

【0095】

そして、スイッチSWCがオフされた後、基準レベル検出期間Tr4において基準レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW4が繰り返し与えられ、基準レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0096】

そして、基準レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW4ごとに基準レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて繰り返しダウンカウントされることで、多重サンプリングされた基準レベルの出力電圧PINがデジタル値COUTに変換され、アップダウンカウンタKUに保持される。

【0097】

次に、画素PCnの行選択トランジスタTaがオンの状態で読み出し信号READnがハイレベルになると、読み出しトランジスタTdがオンし、フォトダイオードPDに蓄積されていた電荷がフローティングディフュージョンFDに転送される。このため、フローティングディフュージョンFDの信号レベルに応じた電圧が増幅トランジスタTbのゲートにかかり、信号レベルの出力電圧PINとして垂直信号線Vlinに出力される。

【0098】

そして、信号レベルの出力電圧PINがコンデンサCcを介してコンパレータPAに入力された状態で、基準電圧VREFとしてランプ波RW4が段階L1で繰り返し与えられた後、ランプ波RW5が段階L2〜L4ごとに繰り返し与えられ、信号レベルの出力電圧PINと基準電圧VREFとが繰り返し比較される。

【0099】

そして、信号レベルの出力電圧PINが基準電圧VREFのレベルより小さい場合は、コンパレータPAの出力電圧CNTがハイレベルとなり、各ランプ波RW4、RW5ごとに信号レベルの出力電圧PINが基準電圧VREFのレベルと一致するとCNTがロウレベルとなり、このハイ期間の長さをアップダウンカウンタKUにて今度は繰り返しアップカウントされることで、多重サンプリングされた信号レベルの出力電圧PINと基準レベルの出力電圧PINとの差分がデジタル値COUTに変換され、水平画素分だけラインメモリ4に保持される。

【0100】

これにより、多重サンプリングによるランダムノイズを低下させつつ、基準レベルおよび信号レベルのRTSノイズを多重サンプリングにて効果的に低減させることができる。RTSノイズの低減できる周波数は、少なくともCDS間隔TD41とその2倍さらに4倍のTD43で発生する3種類の揺らぎを効果的に低減させることができる。

【0101】

また、上述した実施形態では、デジタルCDS処理として信号の基準レベル信号と信号レベルの差を演算する回路にアップダウンカウンタと基準レベル信号と信号レベルを別々のラインメモリに保持し、読み出した出力信号の差分を演算する回路を用いた。他にも、基準レベル信号をアップカウンタでカウントし、カウント値を反転させる制御信号により値を反転させ、その後、信号レベルをアップカウントすることで2の補数を使ったカウンタ型の演算処理回路を設けるようにしてもよい。

【0102】

また、第1のランプ生成部でのランプ発生回数を第2のランプ生成部のランプ発生部で信号レベルが大きい時に第1のランプ波生成部で発生するランプ波の発生回数を削減することで、AD変換時間を短くすることで動作速度を早くすることができる。

さらに、前記第1のランプ波生成部で発生するランプ波の発生回数を削減したデジタル信号を増幅する増幅回路をさらに設けることで、光電変換特性を線形化することができる。

【0103】

図12にマルチランプ波発生回路の実施例を示す。

マルチランプ波発生回路は、オペアンプ31を使ったランプ波発生を実施している。

オペアンプ31の反転入力端子には、定電流源回路Iramp1を入力している。オペアンプ31の出力は、スイッチSWramp1を介して負入力端子に接続している。さらに、オペアンプ31の出力は、コンデンサCramp1を介して反転入力端子に接続している。スイッチSWramp1は、ランプ波間隔制御回路41の出力パルスPrampで第1のランプ波の周期Tra1を制御している。第1のランプ波の傾きは、定電流源回路Iramp1の電流量とコンデンサCramp1の容量で変化させることができる。よって、第1のランプ波の振幅は、第1ランプ波制御回路42により定電流源回路Iramp1の電流量を制御することで変化させることができる。

【0104】

オペアンプ31の正入力端子には、所定の電圧例えば1.5Vを発生させ入力する。この電圧は、定電流源回路Iramp2と抵抗R1と抵抗R2で発生したバイアス電圧を印加している。オペアンプ31の出力VREFは、この入力電圧と同じ電圧1.5Vが出力される。この時、スイッチSWramp1をONにすると、負入力電圧も1.5Vにセットされる。スイッチSWramp1をOFFにすると定電流源回路Iramp1で発生させた電流がコンデンサCramp1へ流れ込む。オペアンプ31の正と負の入力端子は、同じ電圧を維持するため、出力電圧が変化する。定電流源回路Iramp1が定電流で電流を流し込むため、出力は傾きが一定の第1のランプ波を発生する。

【0105】

時刻t4では、第2ランプ波制御回路43で抵抗R1の値を大きく変化させる。すると、Vramp2のバイアス電圧が変化する。同様に第2ランプ波制御回路43で抵抗R1の値をさらに大きく変化させることで、階段状の第2のランプ波Vramp2を生成することができる。さらに、スイープ起点制御回路44で、抵抗R2の値を小さく変化させることで、時刻t1,t2,t3のように、階段状に小さく変化させることができる。オペアンプ31の出力では、このVRamp2とVRamp1を合成したランプ波VREFを生成することができる。

【0106】

第2ランプ波制御回路43、さらにスイープ起点制御回路44は、ランプ波間隔制御回路41に同期した制御を実施している。

【符号の説明】

【0107】

PC、PCn、PCn´、PCn´´、PCn´´´、 画素、Ta 行選択トランジスタ、Tb 増幅トランジスタ、Tc リセットトランジスタ、Td、Td1〜Td3 読み出しトランジスタ、PD フォトダイオード、FD フローティングディフュージョン、G 電流源、Vlin 垂直信号線、Hlin 水平制御線、1 画素アレイ部、2 行走査回路、3、3a、3b カラムADC回路、4、4a、4b ラインメモリ、5 水平走査回路、6、6a〜6c マルチランプ波発生回路、7 減算器、PA コンパレータ、Cc コンデンサ、SWC スイッチ、KU、KUa アップダウンカウンタ、KUb カウンタ、11、11a、11b 第1のランプ波生成部、12 第2のランプ波生成部、13 合成部、14 スイープ起点制御部、15 ランプ波間隔制御部、21 カウンタ制御回路

【特許請求の範囲】

【請求項1】

光電変換された信号を出力する画素と、

前記画素から出力された信号レベルと基準電圧となるランプ波との比較結果に基づいて、前記画素のアナログ信号をデジタル信号に変換する画素エリアの端部に配置したADC回路と、

前記ランプ波は、振幅のことなる複数のランプ波を生成し合成するマルチランプ波発生回路とを備えることを特徴とする固体撮像装置。

【請求項2】

前記マルチランプ波発生回路は、

小振幅のランプ波を生成する第1のランプ波生成部と、

第1のランプ波の振幅より大きな振幅を階段状に生成する第2のランプ波生成部と

を備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項3】

前記マルチランプ波発生回路は、

前記第1のランプ波の傾きを制御するための第1のランプ波制御部と、

前記第2のランプ波の階段の振幅幅を制御するための第2のランプ波制御部と

を備えることを特徴とする請求項2に記載の固体撮像装置。

【請求項4】

前記マルチランプ波発生回路は、

前記第2のランプ波の各階段の1レベル期間に、前記第1のランプ波を複数回生成する前記第1のランプ波制御部と前記第1のランプ波と前記第2のランプ波を合成する合成回路を備えることを特徴とする請求項3に記載の固体撮像装置。

【請求項5】

前記マルチランプ波発生回路は、

前記合成回路で合成したランプ波で複数回発生させた第1ランプ波の各スイープ起点のレベルを制御するスイープ起点制御部をさらに備えることを特徴とする請求項4に記載の固体撮像装置。

【請求項6】

前記第2のランプ波生成部は、

前記画素からの出力信号の増加方向と同一方向に、ランプ波の階段が順次増加するように前記第2のランプ波制御部をさらに備えることを特徴とする請求項3に記載の固体撮像装置。

【請求項7】

前記第1のランプ波生成部は、

ランプ波は上り傾斜と下り傾斜とが同一の傾きとなるように制御する、第1のランプ波制御部を備えたことを特徴とする請求項3に記載の固体撮像装置。

【請求項8】

前記マルチランプ波発生回路は、単位ランプ波で取り込む前記基準レベルの取り込み時刻と、前記信号レベルの取り込み時刻間の最小間隔と同等の期間で、前記基準レベルを複数回取り込むための複数のランプ波を発生させるためのランプ波間隔調整部をさらに備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項9】

前記マルチランプ波発生回路は、単位ランプ波で取り込む前記基準レベルの取り込み時刻と、前記信号レベルの取り込み時刻間の最小間隔と同等の期間で、少なくとも前記階段ランプ波の最小信号レベルで複数回取り込むための複数のランプ波を発生させるためのランプ波間隔調整部をさらに備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項10】

前記マルチランプ波発生回路は、

前記第2のランプ波の階段レベルが大きいレベルにおいて、前記第1のランプ波生成部で生成する生成する回数を削減する前記第1ランプ波制御部をさらに備えることを

を特徴とする請求項3に記載の固体撮像装置。

【請求項11】

前記第2のランプ波の各ステップに発生する第1のランプ波の発生回数に反して、デジタルデータを増幅する増幅回路の増幅率を制御する増幅率制御部をさらに備えることを特徴とする請求項10に記載の固体撮像装置。

【請求項12】

前記ADC回路は、

アナログ信号をデジタル信号に変換するコンパレータ回路と、

コンパレータ出力が変化するまでの長さをカウントするカウンタ回路を備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項13】

前記ADC回路は、

前記画素から出力される信号がない基準レベルを取り込みと、光電変換した信号レベルを取り込む前記カウンタ回路を制御するカウンタ制御部をさらに備えることを特徴とする請求項12に記載の固体撮像装置。

【請求項14】

前記ADC回路は、

前記基準レベルを保存する第1のラインメモリと、

前記信号レベルを保存する第2のラインメモリと

を備えることを特徴とする請求項12または13のいずれか1項に記載の固体撮像装置。

【請求項1】

光電変換された信号を出力する画素と、

前記画素から出力された信号レベルと基準電圧となるランプ波との比較結果に基づいて、前記画素のアナログ信号をデジタル信号に変換する画素エリアの端部に配置したADC回路と、

前記ランプ波は、振幅のことなる複数のランプ波を生成し合成するマルチランプ波発生回路とを備えることを特徴とする固体撮像装置。

【請求項2】

前記マルチランプ波発生回路は、

小振幅のランプ波を生成する第1のランプ波生成部と、

第1のランプ波の振幅より大きな振幅を階段状に生成する第2のランプ波生成部と

を備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項3】

前記マルチランプ波発生回路は、

前記第1のランプ波の傾きを制御するための第1のランプ波制御部と、

前記第2のランプ波の階段の振幅幅を制御するための第2のランプ波制御部と

を備えることを特徴とする請求項2に記載の固体撮像装置。

【請求項4】

前記マルチランプ波発生回路は、

前記第2のランプ波の各階段の1レベル期間に、前記第1のランプ波を複数回生成する前記第1のランプ波制御部と前記第1のランプ波と前記第2のランプ波を合成する合成回路を備えることを特徴とする請求項3に記載の固体撮像装置。

【請求項5】

前記マルチランプ波発生回路は、

前記合成回路で合成したランプ波で複数回発生させた第1ランプ波の各スイープ起点のレベルを制御するスイープ起点制御部をさらに備えることを特徴とする請求項4に記載の固体撮像装置。

【請求項6】

前記第2のランプ波生成部は、

前記画素からの出力信号の増加方向と同一方向に、ランプ波の階段が順次増加するように前記第2のランプ波制御部をさらに備えることを特徴とする請求項3に記載の固体撮像装置。

【請求項7】

前記第1のランプ波生成部は、

ランプ波は上り傾斜と下り傾斜とが同一の傾きとなるように制御する、第1のランプ波制御部を備えたことを特徴とする請求項3に記載の固体撮像装置。

【請求項8】

前記マルチランプ波発生回路は、単位ランプ波で取り込む前記基準レベルの取り込み時刻と、前記信号レベルの取り込み時刻間の最小間隔と同等の期間で、前記基準レベルを複数回取り込むための複数のランプ波を発生させるためのランプ波間隔調整部をさらに備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項9】

前記マルチランプ波発生回路は、単位ランプ波で取り込む前記基準レベルの取り込み時刻と、前記信号レベルの取り込み時刻間の最小間隔と同等の期間で、少なくとも前記階段ランプ波の最小信号レベルで複数回取り込むための複数のランプ波を発生させるためのランプ波間隔調整部をさらに備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項10】

前記マルチランプ波発生回路は、

前記第2のランプ波の階段レベルが大きいレベルにおいて、前記第1のランプ波生成部で生成する生成する回数を削減する前記第1ランプ波制御部をさらに備えることを

を特徴とする請求項3に記載の固体撮像装置。

【請求項11】

前記第2のランプ波の各ステップに発生する第1のランプ波の発生回数に反して、デジタルデータを増幅する増幅回路の増幅率を制御する増幅率制御部をさらに備えることを特徴とする請求項10に記載の固体撮像装置。

【請求項12】

前記ADC回路は、

アナログ信号をデジタル信号に変換するコンパレータ回路と、

コンパレータ出力が変化するまでの長さをカウントするカウンタ回路を備えることを特徴とする請求項1に記載の固体撮像装置。

【請求項13】

前記ADC回路は、

前記画素から出力される信号がない基準レベルを取り込みと、光電変換した信号レベルを取り込む前記カウンタ回路を制御するカウンタ制御部をさらに備えることを特徴とする請求項12に記載の固体撮像装置。

【請求項14】

前記ADC回路は、

前記基準レベルを保存する第1のラインメモリと、

前記信号レベルを保存する第2のラインメモリと

を備えることを特徴とする請求項12または13のいずれか1項に記載の固体撮像装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−19410(P2012−19410A)

【公開日】平成24年1月26日(2012.1.26)

【国際特許分類】

【出願番号】特願2010−156075(P2010−156075)

【出願日】平成22年7月8日(2010.7.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年1月26日(2012.1.26)

【国際特許分類】

【出願日】平成22年7月8日(2010.7.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]