増幅回路

【課題】 アクティブフィードバック回路のピーキング強度を外部から調整することができる増幅回路を得る。

【解決手段】 第1の差動増幅回路と、第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、第2の差動増幅回路の出力信号をフィードバックして第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、アクティブフィードバック回路は、コレクタ又はドレインがそれぞれ第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、一端が第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有する。

【解決手段】 第1の差動増幅回路と、第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、第2の差動増幅回路の出力信号をフィードバックして第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、アクティブフィードバック回路は、コレクタ又はドレインがそれぞれ第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、一端が第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ通信分野に属するものであり、波形整形を行うアクティブフィードバック回路(イコライザ回路)を有する増幅回路に関するものである。

【背景技術】

【0002】

データ通信装置のデータ受信ブロックに設けられた増幅回路において、波形整形を行うためにアクティブフィードバック回路(イコライザ回路)を有するものが提案されている(例えば、非特許文献1参照)。

【0003】

【非特許文献1】Sherif Galal and Behzad Razavi, IEEE Journal of Solid circuits, vol. 38, No. 12, December 2003, Fig. 5

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来の増幅回路では、アクティブフィードバック回路のピーキング値、ピーキング戻り値、ピーキング幅といったピーキング強度を外部から調整することはできなかった。従って、設計後にピーキング強度を各種の伝送線路の劣化特性に適合させることはできなかった。

【0005】

本発明は、上述のような課題を解決するためになされたもので、その目的は、アクティブフィードバック回路のピーキング強度を外部から調整することができる増幅回路を得るものである。

【課題を解決するための手段】

【0006】

本発明に係る増幅回路は、第1の差動増幅回路と、第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、第2の差動増幅回路の出力信号をフィードバックして第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、アクティブフィードバック回路は、コレクタ又はドレインがそれぞれ第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、一端が第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有する。本発明のその他の特徴は以下に明らかにする。

【発明の効果】

【0007】

本発明により、アクティブフィードバック回路のピーキング強度を外部から調整することができる。これにより、設計後にピーキング強度を各種の伝送線路の劣化特性に適合させることができる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

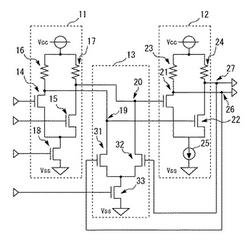

図1は、本発明の実施の形態1に係る増幅回路を示す回路図である。この増幅回路には、第1の差動増幅回路11と、第1の差動増幅回路11の出力信号を増幅する第2の差動増幅回路12と、第2の差動増幅回路12の出力信号をフィードバックして第1の差動増幅回路11の出力信号を波形整形するアクティブフィードバック回路13が設けられている。

【0009】

まず、第1の差動増幅回路11には、トランジスタ14,15と、抵抗16,17と電流源18が設けられている。このトランジスタ14,15として、バイポーラトランジスタとMOSトランジスタの何れを用いてもよい。そして、トランジスタ14,15は、コレクタ又はドレインがそれぞれ抵抗16,17を介して高電位側電源Vccに接続され、かつ、それぞれ2つの出力ノード19,20に接続され、ベース又はゲートがそれぞれ2つの入力ノードに接続され、エミッタ又はソースが共通接続されている。また、電流源18は、一端がトランジスタ14,15のエミッタ又はソースに接続され、他端が低電位側電源Vssに接続されている。そして、電流源18はトランジスタで構成され、そのゲートバイアス値を調整することで電流値を外部から調整することができる。

【0010】

次に、第2の差動増幅回路12には、トランジスタ21,22と、抵抗23,24と電流源25が設けられている。このトランジスタ21,22として、バイポーラトランジスタとMOSトランジスタの何れを用いてもよい。そして、トランジスタ21,22は、コレクタ又はドレインがそれぞれ抵抗23,24を介して高電位側電源Vccに接続され、かつ、それぞれ2つの出力ノード26,27に接続され、ベース又はゲートがそれぞれ第1の差動増幅回路11の2つの出力ノード20,19に接続され、エミッタ又はソースが共通接続されている。また、電流源25は、一端がトランジスタ21,22のエミッタ又はソースに接続され、他端が低電位側電源Vssに接続されている。

【0011】

そして、アクティブフィードバック回路13には、トランジスタ31,32と電流源33が設けられている。このトランジスタ31,32は、コレクタ又はドレインがそれぞれ第1の差動増幅回路11の2つの出力ノード19,20に接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノード26,27に接続され、エミッタ又はソースが共通接続されている。また、電流源33は、一端がトランジスタ31,32のエミッタ又はソースに接続され、他端が低電位側電源Vssに接続されている。そして、電流源33はトランジスタにより構成され、そのゲートバイアス値を調整することで、電流値を外部から調整することができる。

【0012】

以上の構成を有する増幅回路は、第1の差動増幅回路11の出力信号にアクティブフィードバック回路13の出力信号を合成することで、第1の差動増幅回路11の出力信号を波形整形する。このように、第1の差動増幅回路11の出力ノードに直接フィードバックをかけることにより、出力信号のピーキング強度の調整範囲が大きくなり、希望のピーキング波形にすることができる。

【0013】

ここで、アクティブフィードバック回路13に入力されるのは第2の差動増幅回路12の出力信号であるため、アクティブフィードバック回路13の出力信号は、第1の差動増幅回路11の出力信号に比べて、第2の差動増幅回路12とアクティブフィードバック回路13のスイッチング遅延量分だけ遅れている。

【0014】

これにより、図2に示すように、第1の差動増幅回路の出力信号(a)とアクティブフィードバック回路の出力信号(b)を合成した信号(c)は、ピーキングを持った波形となる。

【0015】

ここで、第1の差動増幅回路11とアクティブフィードバック回路13は抵抗16,17を共有しているため、第1の差動増幅回路11の電流源18の電流値とアクティブフィードバック回路13の電流源33の電流値がそれぞれの出力信号の振幅を決める。従って、第1の差動増幅回路11の電流源18とアクティブフィードバック回路13の電流源の何れか一方又は両方について、電流値を調整することにより、第1の差動増幅回路11の出力信号のピーキング値及びピーキング戻り値を調整することができる。

【0016】

具体的には、第1の差動増幅回路11の電流源18の電流値を一定にして、アクティブフィードバック回路13の電流源33の電流値を小さくすれば、第1の差動増幅回路11の出力信号のピーキング値とピーキング戻り値は小さくすることができる。ただし、ピーキング値と定常振幅の差は小さくなる。

【0017】

一方、第1の差動増幅回路の電流源の電流値を一定にして、アクティブフィードバック回路の電流源の電流値を大きくすれば、第1の差動増幅回路のピーキング値とピーキング戻り値を大きくすることができる。ただし、ピーキング値と定常振幅の差は大きくなる。

【0018】

また、逆に、アクティブフィードバック回路13の電流源33の電流値を一定にして第1の差動増幅回路11の電流源18の電流値を変更しても同様の効果を奏する。そして、両方の電流源の電流値を変更しても同様の効果を奏する。

【0019】

実施の形態2.

図3は、本発明の実施の形態2に係る増幅回路を示す回路図である。図1と同様の構成要素には同じ番号を付し、説明を省略する。

【0020】

実施の形態2に係る増幅回路では、実施の形態1の構成に加えて、抵抗41,42及び容量43,44が設けられている。この抵抗41,42は、一端が第2の差動増幅回路12の出力ノード26,27にそれぞれ接続され、他端がトランジスタ31,32のベース又はゲートに接続されている。即ち、抵抗41,42は、第2の差動増幅回路12の出力ノード26,27からトランジスタ31,32のベース又はゲートに至るアクティブフィードバック経路に設けられている。

【0021】

また、容量43,44は、一端がトランジスタ31,32のベース又はゲート、即ちアクティブフィードバック経路にそれぞれ接続され、他端が低電位側電源Vssに接続されている。そして、容量43,44は、その容量値を外部から調整することができる。

【0022】

ここで、アクティブフィードバック回路13の出力信号は、第1の差動増幅回路11の出力信号に比べて遅延している。この遅延量は、第2の差動増幅回路12とアクティブフィードバック回路13のスイッチング遅延量と、抵抗41,42及び容量43,44のCR時定数により決まる。

【0023】

従って、容量43,44の容量値を調整することにより、遅延量を調整することができる。これにより、遅延量と対応する第1の差動増幅回路11の出力信号のピーキング幅を調整することができる。

【0024】

このような容量値を調整することができる容量43,44としては、PMOS基板バラクタ、NMOS基板バラクタ及びMIM容量の何れかを用いることができる。

【0025】

図4は、PMOS基板バラクタを示す断面図である。図示のように、N型基板51中にP型ウェル52が形成され、その上にゲート絶縁膜53及びゲート電極54が形成されている。また、P型ウェル52中にソース領域55及びドレイン領域56が形成され、その上にそれぞれソース電極57及びドレイン電極58が形成されている。そして、ゲート電極54をアクティブフィードバック経路に接続し、ボディ電圧を外部から調整できるようにする。このように、バラクタとしてアキュムレーション型MOS容量を用いる。このPMOS基板バラクタの特性を図5に示す。

【0026】

このPMOS基板バラクタを用いた場合、ボディ電圧を下げれば、バラクタ容量が減少し、CR時定数が小さくなり、フィードバック信号の遅延量は小さくなるため、第1の差動増幅回路の出力信号のピーキング幅を狭めることができる。逆に、ボディ電圧を上げれば、ピーキング幅を広げることができる。

【0027】

一方、図6は、NMOS基板バラクタを示す断面図である。図示のように、P型基板61中にN型ウェル62が形成され、その上にゲート絶縁膜63及びゲート電極64が形成されている。また、N型ウェル62中にソース領域65及びドレイン領域66が形成され、その上にそれぞれソース電極67及びドレイン電極68が形成されている。そして、ゲート電極64をアクティブフィードバック経路に接続し、ボディ電圧を外部から調整できるようにする。このNMOS基板バラクタの特性を図7に示す。

【0028】

このNMOS基板バラクタを用いた場合、PMOS基板を用いた場合とは極性が反対になるが、同様の効果を奏する。

【0029】

また、MIM容量を用いた場合、同様の効果を奏するだけでなく、MOS容量を用いた場合よりも容量値が正確になるので、より設計値に近いピーキング強度にすることができる。

【図面の簡単な説明】

【0030】

【図1】本発明の実施の形態1に係る増幅回路を示す回路図である。

【図2】第1の差動増幅回路の出力信号(a)と、第2の差動増幅回路の出力信号(b)と、第1の差動増幅回路の出力信号とアクティブフィードバック回路の出力信号を合成した信号(c)を示す波形図である。

【図3】本発明の実施の形態2に係る増幅回路を示す回路図である。

【図4】PMOS基板バラクタを示す断面図である。

【図5】PMOS基板バラクタのボディ電圧と容量値の関係図である。

【図6】NMOS基板バラクタを示す断面図である。

【図7】NMOS基板バラクタのボディ電圧と容量値の関係図である。

【符号の説明】

【0031】

11 第1の差動増幅回路

12 第2の差動増幅回路

13 アクティブフィードバック回路

14,15,21,22,31,32 トランジスタ

16,17,23,24,41,42 抵抗

18,25,33 電流源

19,20,26,27 出力ノード

43,44 容量

【技術分野】

【0001】

本発明は、データ通信分野に属するものであり、波形整形を行うアクティブフィードバック回路(イコライザ回路)を有する増幅回路に関するものである。

【背景技術】

【0002】

データ通信装置のデータ受信ブロックに設けられた増幅回路において、波形整形を行うためにアクティブフィードバック回路(イコライザ回路)を有するものが提案されている(例えば、非特許文献1参照)。

【0003】

【非特許文献1】Sherif Galal and Behzad Razavi, IEEE Journal of Solid circuits, vol. 38, No. 12, December 2003, Fig. 5

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来の増幅回路では、アクティブフィードバック回路のピーキング値、ピーキング戻り値、ピーキング幅といったピーキング強度を外部から調整することはできなかった。従って、設計後にピーキング強度を各種の伝送線路の劣化特性に適合させることはできなかった。

【0005】

本発明は、上述のような課題を解決するためになされたもので、その目的は、アクティブフィードバック回路のピーキング強度を外部から調整することができる増幅回路を得るものである。

【課題を解決するための手段】

【0006】

本発明に係る増幅回路は、第1の差動増幅回路と、第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、第2の差動増幅回路の出力信号をフィードバックして第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、アクティブフィードバック回路は、コレクタ又はドレインがそれぞれ第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、一端が第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有する。本発明のその他の特徴は以下に明らかにする。

【発明の効果】

【0007】

本発明により、アクティブフィードバック回路のピーキング強度を外部から調整することができる。これにより、設計後にピーキング強度を各種の伝送線路の劣化特性に適合させることができる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

図1は、本発明の実施の形態1に係る増幅回路を示す回路図である。この増幅回路には、第1の差動増幅回路11と、第1の差動増幅回路11の出力信号を増幅する第2の差動増幅回路12と、第2の差動増幅回路12の出力信号をフィードバックして第1の差動増幅回路11の出力信号を波形整形するアクティブフィードバック回路13が設けられている。

【0009】

まず、第1の差動増幅回路11には、トランジスタ14,15と、抵抗16,17と電流源18が設けられている。このトランジスタ14,15として、バイポーラトランジスタとMOSトランジスタの何れを用いてもよい。そして、トランジスタ14,15は、コレクタ又はドレインがそれぞれ抵抗16,17を介して高電位側電源Vccに接続され、かつ、それぞれ2つの出力ノード19,20に接続され、ベース又はゲートがそれぞれ2つの入力ノードに接続され、エミッタ又はソースが共通接続されている。また、電流源18は、一端がトランジスタ14,15のエミッタ又はソースに接続され、他端が低電位側電源Vssに接続されている。そして、電流源18はトランジスタで構成され、そのゲートバイアス値を調整することで電流値を外部から調整することができる。

【0010】

次に、第2の差動増幅回路12には、トランジスタ21,22と、抵抗23,24と電流源25が設けられている。このトランジスタ21,22として、バイポーラトランジスタとMOSトランジスタの何れを用いてもよい。そして、トランジスタ21,22は、コレクタ又はドレインがそれぞれ抵抗23,24を介して高電位側電源Vccに接続され、かつ、それぞれ2つの出力ノード26,27に接続され、ベース又はゲートがそれぞれ第1の差動増幅回路11の2つの出力ノード20,19に接続され、エミッタ又はソースが共通接続されている。また、電流源25は、一端がトランジスタ21,22のエミッタ又はソースに接続され、他端が低電位側電源Vssに接続されている。

【0011】

そして、アクティブフィードバック回路13には、トランジスタ31,32と電流源33が設けられている。このトランジスタ31,32は、コレクタ又はドレインがそれぞれ第1の差動増幅回路11の2つの出力ノード19,20に接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノード26,27に接続され、エミッタ又はソースが共通接続されている。また、電流源33は、一端がトランジスタ31,32のエミッタ又はソースに接続され、他端が低電位側電源Vssに接続されている。そして、電流源33はトランジスタにより構成され、そのゲートバイアス値を調整することで、電流値を外部から調整することができる。

【0012】

以上の構成を有する増幅回路は、第1の差動増幅回路11の出力信号にアクティブフィードバック回路13の出力信号を合成することで、第1の差動増幅回路11の出力信号を波形整形する。このように、第1の差動増幅回路11の出力ノードに直接フィードバックをかけることにより、出力信号のピーキング強度の調整範囲が大きくなり、希望のピーキング波形にすることができる。

【0013】

ここで、アクティブフィードバック回路13に入力されるのは第2の差動増幅回路12の出力信号であるため、アクティブフィードバック回路13の出力信号は、第1の差動増幅回路11の出力信号に比べて、第2の差動増幅回路12とアクティブフィードバック回路13のスイッチング遅延量分だけ遅れている。

【0014】

これにより、図2に示すように、第1の差動増幅回路の出力信号(a)とアクティブフィードバック回路の出力信号(b)を合成した信号(c)は、ピーキングを持った波形となる。

【0015】

ここで、第1の差動増幅回路11とアクティブフィードバック回路13は抵抗16,17を共有しているため、第1の差動増幅回路11の電流源18の電流値とアクティブフィードバック回路13の電流源33の電流値がそれぞれの出力信号の振幅を決める。従って、第1の差動増幅回路11の電流源18とアクティブフィードバック回路13の電流源の何れか一方又は両方について、電流値を調整することにより、第1の差動増幅回路11の出力信号のピーキング値及びピーキング戻り値を調整することができる。

【0016】

具体的には、第1の差動増幅回路11の電流源18の電流値を一定にして、アクティブフィードバック回路13の電流源33の電流値を小さくすれば、第1の差動増幅回路11の出力信号のピーキング値とピーキング戻り値は小さくすることができる。ただし、ピーキング値と定常振幅の差は小さくなる。

【0017】

一方、第1の差動増幅回路の電流源の電流値を一定にして、アクティブフィードバック回路の電流源の電流値を大きくすれば、第1の差動増幅回路のピーキング値とピーキング戻り値を大きくすることができる。ただし、ピーキング値と定常振幅の差は大きくなる。

【0018】

また、逆に、アクティブフィードバック回路13の電流源33の電流値を一定にして第1の差動増幅回路11の電流源18の電流値を変更しても同様の効果を奏する。そして、両方の電流源の電流値を変更しても同様の効果を奏する。

【0019】

実施の形態2.

図3は、本発明の実施の形態2に係る増幅回路を示す回路図である。図1と同様の構成要素には同じ番号を付し、説明を省略する。

【0020】

実施の形態2に係る増幅回路では、実施の形態1の構成に加えて、抵抗41,42及び容量43,44が設けられている。この抵抗41,42は、一端が第2の差動増幅回路12の出力ノード26,27にそれぞれ接続され、他端がトランジスタ31,32のベース又はゲートに接続されている。即ち、抵抗41,42は、第2の差動増幅回路12の出力ノード26,27からトランジスタ31,32のベース又はゲートに至るアクティブフィードバック経路に設けられている。

【0021】

また、容量43,44は、一端がトランジスタ31,32のベース又はゲート、即ちアクティブフィードバック経路にそれぞれ接続され、他端が低電位側電源Vssに接続されている。そして、容量43,44は、その容量値を外部から調整することができる。

【0022】

ここで、アクティブフィードバック回路13の出力信号は、第1の差動増幅回路11の出力信号に比べて遅延している。この遅延量は、第2の差動増幅回路12とアクティブフィードバック回路13のスイッチング遅延量と、抵抗41,42及び容量43,44のCR時定数により決まる。

【0023】

従って、容量43,44の容量値を調整することにより、遅延量を調整することができる。これにより、遅延量と対応する第1の差動増幅回路11の出力信号のピーキング幅を調整することができる。

【0024】

このような容量値を調整することができる容量43,44としては、PMOS基板バラクタ、NMOS基板バラクタ及びMIM容量の何れかを用いることができる。

【0025】

図4は、PMOS基板バラクタを示す断面図である。図示のように、N型基板51中にP型ウェル52が形成され、その上にゲート絶縁膜53及びゲート電極54が形成されている。また、P型ウェル52中にソース領域55及びドレイン領域56が形成され、その上にそれぞれソース電極57及びドレイン電極58が形成されている。そして、ゲート電極54をアクティブフィードバック経路に接続し、ボディ電圧を外部から調整できるようにする。このように、バラクタとしてアキュムレーション型MOS容量を用いる。このPMOS基板バラクタの特性を図5に示す。

【0026】

このPMOS基板バラクタを用いた場合、ボディ電圧を下げれば、バラクタ容量が減少し、CR時定数が小さくなり、フィードバック信号の遅延量は小さくなるため、第1の差動増幅回路の出力信号のピーキング幅を狭めることができる。逆に、ボディ電圧を上げれば、ピーキング幅を広げることができる。

【0027】

一方、図6は、NMOS基板バラクタを示す断面図である。図示のように、P型基板61中にN型ウェル62が形成され、その上にゲート絶縁膜63及びゲート電極64が形成されている。また、N型ウェル62中にソース領域65及びドレイン領域66が形成され、その上にそれぞれソース電極67及びドレイン電極68が形成されている。そして、ゲート電極64をアクティブフィードバック経路に接続し、ボディ電圧を外部から調整できるようにする。このNMOS基板バラクタの特性を図7に示す。

【0028】

このNMOS基板バラクタを用いた場合、PMOS基板を用いた場合とは極性が反対になるが、同様の効果を奏する。

【0029】

また、MIM容量を用いた場合、同様の効果を奏するだけでなく、MOS容量を用いた場合よりも容量値が正確になるので、より設計値に近いピーキング強度にすることができる。

【図面の簡単な説明】

【0030】

【図1】本発明の実施の形態1に係る増幅回路を示す回路図である。

【図2】第1の差動増幅回路の出力信号(a)と、第2の差動増幅回路の出力信号(b)と、第1の差動増幅回路の出力信号とアクティブフィードバック回路の出力信号を合成した信号(c)を示す波形図である。

【図3】本発明の実施の形態2に係る増幅回路を示す回路図である。

【図4】PMOS基板バラクタを示す断面図である。

【図5】PMOS基板バラクタのボディ電圧と容量値の関係図である。

【図6】NMOS基板バラクタを示す断面図である。

【図7】NMOS基板バラクタのボディ電圧と容量値の関係図である。

【符号の説明】

【0031】

11 第1の差動増幅回路

12 第2の差動増幅回路

13 アクティブフィードバック回路

14,15,21,22,31,32 トランジスタ

16,17,23,24,41,42 抵抗

18,25,33 電流源

19,20,26,27 出力ノード

43,44 容量

【特許請求の範囲】

【請求項1】

第1の差動増幅回路と、

前記第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、

前記第2の差動増幅回路の出力信号をフィードバックして前記第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、

前記アクティブフィードバック回路は、

コレクタ又はドレインがそれぞれ前記第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ前記第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、

一端が前記第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有することを特徴とする増幅回路。

【請求項2】

前記第1の差動増幅回路は、

コレクタ又はドレインがそれぞれ第1及び第2の抵抗を介して高電位側電源に接続され、かつ、それぞれ2つの出力ノードに接続され、ベース又はゲートがそれぞれ2つの入力ノードに接続され、エミッタ又はソースが共通接続された第3及び第4のトランジスタと、

一端が前記第3及び第4のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第2の電流源とを有することを特徴とする請求項1記載の増幅回路。

【請求項3】

第1の差動増幅回路と、

前記第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、

前記第2の差動増幅回路の出力信号をフィードバックして前記第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、

前記第1の差動増幅回路は、

コレクタ又はドレインがそれぞれ第1及び第2の抵抗を介して高電位側電源に接続され、かつ、それぞれ2つの出力ノードに接続され、ベース又はゲートがそれぞれ2つの入力ノードに接続され、エミッタ又はソースが共通接続された第3及び第4のトランジスタと、

一端が前記第3及び第4のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第2の電流源とを有することを特徴とする増幅回路。

【請求項4】

第1の差動増幅回路と、

前記第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、

前記第2の差動増幅回路の出力信号をフィードバックして前記第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、

前記アクティブフィードバック回路は、

コレクタ又はドレインがそれぞれ前記第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ前記第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、

一端が前記第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された第1の電流源と、

一端が前記第1及び第2のトランジスタのベース又はゲートにそれぞれ接続され、他端が低電位側電源に接続された、容量値を外部から調整することができる第1及び第2の容量とを有することを特徴とする増幅回路。

【請求項5】

前記第1及び第2の容量は、PMOS基板バラクタ、NMOS基板バラクタ及びMIM容量の何れかであることを特徴とする請求項4に記載の増幅回路。

【請求項1】

第1の差動増幅回路と、

前記第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、

前記第2の差動増幅回路の出力信号をフィードバックして前記第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、

前記アクティブフィードバック回路は、

コレクタ又はドレインがそれぞれ前記第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ前記第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、

一端が前記第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有することを特徴とする増幅回路。

【請求項2】

前記第1の差動増幅回路は、

コレクタ又はドレインがそれぞれ第1及び第2の抵抗を介して高電位側電源に接続され、かつ、それぞれ2つの出力ノードに接続され、ベース又はゲートがそれぞれ2つの入力ノードに接続され、エミッタ又はソースが共通接続された第3及び第4のトランジスタと、

一端が前記第3及び第4のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第2の電流源とを有することを特徴とする請求項1記載の増幅回路。

【請求項3】

第1の差動増幅回路と、

前記第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、

前記第2の差動増幅回路の出力信号をフィードバックして前記第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、

前記第1の差動増幅回路は、

コレクタ又はドレインがそれぞれ第1及び第2の抵抗を介して高電位側電源に接続され、かつ、それぞれ2つの出力ノードに接続され、ベース又はゲートがそれぞれ2つの入力ノードに接続され、エミッタ又はソースが共通接続された第3及び第4のトランジスタと、

一端が前記第3及び第4のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第2の電流源とを有することを特徴とする増幅回路。

【請求項4】

第1の差動増幅回路と、

前記第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、

前記第2の差動増幅回路の出力信号をフィードバックして前記第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、

前記アクティブフィードバック回路は、

コレクタ又はドレインがそれぞれ前記第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ前記第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、

一端が前記第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された第1の電流源と、

一端が前記第1及び第2のトランジスタのベース又はゲートにそれぞれ接続され、他端が低電位側電源に接続された、容量値を外部から調整することができる第1及び第2の容量とを有することを特徴とする増幅回路。

【請求項5】

前記第1及び第2の容量は、PMOS基板バラクタ、NMOS基板バラクタ及びMIM容量の何れかであることを特徴とする請求項4に記載の増幅回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2006−86682(P2006−86682A)

【公開日】平成18年3月30日(2006.3.30)

【国際特許分類】

【出願番号】特願2004−267838(P2004−267838)

【出願日】平成16年9月15日(2004.9.15)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成18年3月30日(2006.3.30)

【国際特許分類】

【出願日】平成16年9月15日(2004.9.15)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]