差動増幅回路

【課題】差動増幅回路のオフセット電圧を小さくする。

【解決手段】本発明の差動増幅回路は、差動入力信号を受け取るNMOSトランジスタ対を備えるN型入力段2と、N型入力段2に接続された出力段4と、前記差動入力信号を受け取るPMOSトランジスタ対を備えるP型入力段3と、P型入力段3に接続された出力段5と、出力端子OUTとを備えている。出力段5は、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、PMOSトランジスタをNMOSトランジスタに置き換え、接地端子を電源端子に置き換え、電源端子を接地端子に置き換えた構成を有している。出力端子OUTは、出力段4の出力と出力段5の出力に共通に接続されている。

【解決手段】本発明の差動増幅回路は、差動入力信号を受け取るNMOSトランジスタ対を備えるN型入力段2と、N型入力段2に接続された出力段4と、前記差動入力信号を受け取るPMOSトランジスタ対を備えるP型入力段3と、P型入力段3に接続された出力段5と、出力端子OUTとを備えている。出力段5は、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、PMOSトランジスタをNMOSトランジスタに置き換え、接地端子を電源端子に置き換え、電源端子を接地端子に置き換えた構成を有している。出力端子OUTは、出力段4の出力と出力段5の出力に共通に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、差動増幅回路に関し、特に、導電型が異なるトランジスタで構成された2つ

の入力段を備える差動増幅回路に関する。

【背景技術】

【0002】

近年は、LSI加工技術の進歩により、例えばCMOSFET(Complementary Metal Oxide Semiconductor Field Effect Transistor)を回路構成要素とするLSIにおいてはMOSFETの実現寸法がますます微細化されており、それに伴いMOSFETへ印加可能な電圧も低下しつつある。一方、携帯可能な各種電子機器に対する性能要求や需要の高まり、またそれらを構成するLSI以外の電池や周辺部品等の進歩、さらには性能要求とも関連するが機器の動作電力の省電力化等への社会的要請等により、これらの機器の電源電圧の低減化の要求が高まっている。

【0003】

電源電圧が低減化されるに従って、電子機器を構成する電子回路の動作や設計はより困難になっている。一つの問題は、NMOSトランジスタ、PMOSトランジスタの何れについても、通常、CMOS構成のLSIで多用されるエンハンスメント型と呼ばれる特性を持つFETにおいては入力電圧として有効な電圧範囲に限度があることである。つまり、エンハンスメント型FETにおいては出力電流をオフ状態に保つ(これをノーマリーオフと呼ぶ。)ために有効な入力電圧として対応出来ない閾値電圧が存在する。具体的には、NMOSトランジスタでは閾値電圧以上の入力電圧にしか対応できず、PMOS型MOSFETでは電源電圧から閾値電圧を減じた電圧以下の入力電圧にしか対応できない。ところが、電源電圧が低減するとそれらに対する閾値電圧の割合が増加する、即ち有効な入力電圧として対応できない電圧範囲の割合が増加することになる。または、回路中の信号の電圧が閾値電圧以下となり、回路の一部が動作しない場合が発生することになる。

【0004】

こうした問題に対処するための一つの有効なアプローチは、NMOSトランジスタで構成された入力段とPMOSトランジスタで構成された入力段の両方を差動増幅回路に設けることである。図1は、このような差動増幅回路の典型的な構成を示す回路図である。図1の構成は、例えば、Behzad Razavi, "Design of Analog CMOS Integrated

Circuits", McGraw-Hill, 2002, p.326に開示されている。

【0005】

図1の差動増幅回路100は、N型入力段101と、P型入力段102と、出力段103とを備えている。N型入力段101は、NMOSトランジスタM11〜M13を備えており、P型入力段102は、PMOSトランジスタM14〜M16を備えている。NMOSトランジスタM12とPMOSトランジスタM14とは、差動入力信号の一方の信号(非反転入力信号)を受け取る非反転入力端子IPに接続されており、NMOSトランジスタM13とPMOSトランジスタM15とは、差動入力信号の他方の信号(反転入力信号)を受け取る反転入力端子IMに接続されている。即ち、N型入力段101のNMOSトランジスタM12、M13は、差動入力信号を受け取るNMOSトランジスタ対を構成しており、P型入力段102のPMOSトランジスタM14、M15は、差動入力信号を受け取るPMOSトランジスタ対を構成している。

【0006】

出力段103は、NMOSトランジスタM17〜M1Aと、PMOSトランジスタM1B〜M1Eとを備えている。出力段103のノードN11、N12は、それぞれ、P型入力段102のPMOSトランジスタM14、M15のドレインに接続されており、出力段103のノードN14、N15は、それぞれ、N型入力段101のNMOSトランジスタM12、M13に接続されている。出力段103は、N型入力段101及びP型入力段102に入力された差動入力信号に対応する出力信号を出力端子OUTから出力する。

【0007】

差動増幅回路100に含まれるNMOSトランジスタ、PMOSトランジスタとしては、(ノーマリーオフである)エンハンスメント型のトランジスタが使用され得る。

【0008】

図1の差動増幅回路100では、NMOSトランジスタM12、M13で構成されたN型入力段101が、NMOSトランジスタの閾値電圧以上の入力電圧に対応可能であり、一方、PMOSトランジスタM14、M15で構成されたP型入力段102は、電源電圧からPMOSトランジスタの閾値電圧を減じた電圧以下の入力電圧に対応可能である。従って、図1の差動増幅回路100では、接地から電源電圧の間の全範囲の入力電圧に対応することができる。

【非特許文献1】Behzad Razavi, "Design of Analog CMOSIntegrated Circuits", McGraw-Hill, 2002, p.326

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、図1の差動増幅回路100は、オフセット電圧がゼロにならないという問題がある。以下、この問題について詳細に議論する。以下の議論においては、特に断りの無い限り、全てのMOSトランジスタが飽和領域で動作しているものとする。以下の議論では、動作の概要が説明されることが重要であり、また、この目的のために、全てのMOSトランジスタが飽和領域で動作していると仮定しても、実際の差動増幅回路100の動作と本質的な相違はない。

【0010】

一般に、MOSトランジスタのドレイン電流IDは、式(1)で表される:

【数1】

ここで、μは、チャネルにおけるキャリア移動度であり、Coxは、単位面積当たりのゲート容量であり、Wはゲート幅であり、Lはゲート長であり、VGSは、ゲート−ソース間電圧であり、Vthは閾値電圧であり、VDSはドレイン−ソース間電圧であり、VAはアーリー電圧である。

【0011】

回路の分析と理解を容易にするために、以下の説明では、全てのNMOSトランジスタ及びPMOSトランジスタの利得係数β(=μCox・W/L)、閾値電圧Vth、及びアーリー電圧VAは、同一であると仮定する。更に、下記の表記を用いる:

Ix:MOSトランジスタMxのドレイン電流(x=11〜1E)

VGSx:MOSトランジスタMxのゲート−ソース間電圧

VDSx:MOSトランジスタMxのドレイン−ソース間電圧

VNy:ノードNyの電位(y=13)

VIP:非反転入力信号の電圧(非反転入力端子IPの電位)

VIM:反転入力信号の電圧(反転入力端子IMの電位)

VO:出力電圧(出力端子OUTの電位)

【0012】

図1の差動増幅回路100において、オフセット電圧がゼロであるということは、VIP=VIMの場合に、次式(2)が成立することである:

VO=VDD/2 ・・・(2)

ここで、VDDは、電源電圧である。

【0013】

出力端子OUTから差動増幅回路100の内部を見込んだ出力抵抗をRoutと標記すると、式(1)から出力電圧VOは、次式(3)の通りになる:

【数2】

【0014】

式(3)においては、差動増幅回路100の各トランジスタの特性が理想的な場合であっても、第1項がゼロにならない。即ち、仮にP型入力段102のPMOSトランジスタM14、M15の特性が全く同一で、N型入力段101のNMOSトランジスタM12、M13の特性が全く同一で、PMOSトランジスタとNMOSトランジスタの閾値電圧が等しくても、式(2)は恒等式として成立しない。式(2)が成立するのはVth17=VOの特別な場合のみである。即ち、図1の回路では常にオフセット電圧はゼロとは言えない。各トランジスタの特性が理想的でない場合には(例えば、各入力段のトランジスタの特性が異なる場合には)、オフセット電圧が更にゼロから離れてしまう。

【課題を解決するための手段】

【0015】

発明者の検討によれば、オフセット電圧がゼロにならない原因の一つは、差動増幅回路100の回路構成、特に、MOSトランジスタM17〜M1Eで構成される出力段103の回路構成が、トランジスタの極性(NチャネルとPチャネル)の違いに対して対称でないからである。発明者の検討によれば、回路構成の非対称性を解消すれば、オフセット電圧を小さくすることができ、理想的には零にすることができる。

【0016】

より具体的には、本発明は、以下に述べられる手段を採用する。その手段を構成する技術的事項の記述には、[特許請求の範囲]の記載と[発明を実施するための最良の形態]の記載との対応関係を明らかにするために、[発明を実施するための最良の形態]で使用される番号・符号が付記されている。但し、付記された番号・符号は、[特許請求の範囲]に記載されている発明の技術的範囲を限定的に解釈するために用いてはならない。

【0017】

本発明の差動増幅回路は、差動入力信号を受け取る第1導電型のトランジスタ対を備える第1入力段(2、12)と、前記第1入力段(2、12)に接続された第1出力段(4、14)と、前記差動入力信号を受け取る、前記第1導電型と異なる第2導電型のトランジスタ対を備える第2入力段(3、13)と、前記第2入力段(3、13)に接続された第2出力段(5、15)と、出力端子(OUT)とを備えている。前記第2出力段(5、15)は、前記第1出力段(4、14)に含まれる前記第1導電型のトランジスタを前記第2導電型のトランジスタに置き換え、前記第1出力段(4、14)に含まれる前記第2導電型のトランジスタを前記第1導電型のトランジスタに置き換え、前記第1出力段(4、14)に含まれる接地端子を電源端子に置き換え、前記第1出力段(4、14)に含まれる電源端子を接地端子に置き換えた構成を有している。前記出力端子(OUT)は、前記第1出力段(4、14)の出力と前記第2出力段(5、15)の出力に共通に接続されている。

【発明の効果】

【0018】

本発明によれば、差動増幅回路のオフセット電圧を小さくする、理想的には零にすることができる。

【発明を実施するための最良の形態】

【0019】

(第1の実施形態)

図2は、本発明の第1の実施形態の差動増幅回路1の構成を示す回路図である。差動増幅回路1は、N型入力段2と、P型入力段3と、出力段4、5を備えている。

【0020】

N型入力段2は、NMOSトランジスタM21〜M23を備えている。NMOSトランジスタM22、23は、ソースが共通に接続された差動トランジスタ対として機能する。即ち、NMOSトランジスタM22のゲートは、差動入力信号の一方(非反転入力信号)が入力される非反転入力端子IPに接続され、NMOSトランジスタM23のゲートは、差動入力信号の他方(反転入力信号)が入力される反転入力端子IMに接続されている。NMOSトランジスタM22、M23のソースは、NMOSトランジスタM21のドレインに接続されている。NMOSトランジスタM21は、そのゲートにバイアス電圧V21が供給されており、NMOSトランジスタM22、M23からなる差動トランジスタ対に定電流を供給する定電流源として機能する。バイアス電圧V21は、NMOSトランジスタM21の閾値電圧より多少高い電圧であり、NMOSトランジスタM21に充分なドレイン電流が流れるように設定される。

【0021】

P型入力段3は、PMOSトランジスタM2C〜M2Eを備えている。PMOSトランジスタM2C、M2Dは、ソースが共通に接続された差動トランジスタ対として機能する。即ち、PMOSトランジスタM2Cのゲートは、非反転入力信号が入力される非反転入力端子IPに接続され、PMOSトランジスタM2Dのゲートは、反転入力信号が入力される反転入力端子IMに接続されている。PMOSトランジスタM2C、M2Dのソースは、PMOSトランジスタM2Eのドレインに接続されている。PMOSトランジスタM2Eは、そのゲートにバイアス電圧V25が供給されており、PMOSトランジスタM22、M23からなる差動トランジスタ対に定電流を供給する定電流源として機能する。バイアス電圧V25は、電源電圧VDDからPMOSトランジスタM2Eの閾値電圧を減じた電圧より多少低い電圧であり、PMOSトランジスタM2Eに充分なドレイン電流が流れるように設定される。

【0022】

N型入力段2には、NMOSトランジスタM24〜M27とPMOSトランジスタM28〜M2Bからなる出力段4が接続されている。出力段4は、折り返しカスコード型カレントミラーとして構成されており、N型入力段2のNMOSトランジスタM22、M23に流れるドレイン電流I22、I23に対応する出力信号をノードN29に生成する。

【0023】

同様に、P型入力段3には、NMOSトランジスタM2F〜M2IとPMOSトランジスタM2J〜M2Mからなる出力段5が接続されている。出力段5も、折り返しカスコード型カレントミラーとして構成されており、P型入力段3のPMOSトランジスタM2C、M2Dに流れるドレイン電流I2C、I2Dに対応する出力信号をノードN2Bに生成する。

【0024】

出力段4、5のそれぞれには3つのバイアス電圧が供給される。詳細には、出力段4には、バイアス電圧V22、V23、V24が供給され、出力段5には、バイアス電圧V22、V23、V26が供給される。バイアス電圧V22、V23は、出力段4、5の両方に供給されることに留意されたい。

【0025】

バイアス電圧V22は、(接地電位GNDを基準電位として)NMOSトランジスタM26、M27、M2H、M2Iの閾値電圧より多少高い所定の電圧であり、NMOSトランジスタM26、M27、M2H、M2Iに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V22は、下記式で表される電圧である:

V22=VTHN1+VDS_satN1+α1

ここで、VTHN1は、NMOSトランジスタM26、M27、M2H、M2Iの閾値電圧であり、VDS_satN1は、NMOSトランジスタM24、M25、M2F、M2Gのドレイン−ソース間飽和電圧であり、α1>0である。バイアス電圧V22は、NMOSトランジスタM26、M27、M2H、M2Iのゲートに供給される。

【0026】

一方、バイアス電圧V23は、電源電圧VDDからPMOSトランジスタM28、M29、M2J、M2Kの閾値電圧を減じた電圧よりも多少低い所定の電圧であり、PMOSトランジスタM28、M29、M2J、M2Kに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V23は、下記式で表される電圧である:

V23=VDD−(VTHP1+VDS_satP1+α2)

ここで、VTHP1は、PMOSトランジスタM28、M29、M2J、M2Kの閾値電圧であり、VDS_satP1は、PMOSトランジスタM2A、M2B、M2L、M2Mのドレイン−ソース間飽和電圧であり、α2>0である。

【0027】

また、バイアス電圧V24は、電源電圧VDDからPMOSトランジスタM2A、M2Bの閾値電圧を減じた電圧より多少低い所定の電圧であり、PMOSトランジスタM2A、M2Bに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V24は、下記式で表される電圧である:

V24=VDD−(VTHP2+α3)

ここで、VTHP2は、PMOSトランジスタM2A、M2Bの閾値電圧であり、α3>0である。

【0028】

最後に、バイアス電圧V26は、NMOSトランジスタM2F、M2Gの閾値電圧よりも多少高い所定の電圧であり、NMOSトランジスタM2F、M2Gに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V26は、下記式で表される電圧である:

V26=VTHN2+α4

ここで、VTHN2は、NMOSトランジスタM2F、M2Gの閾値電圧であり、α4>0である。

【0029】

差動増幅回路1の出力端子OUTは、出力段4の出力として機能するノードN29と、出力段5の出力として機能するノードN2Bとに共通に接続されている。出力端子OUTからは、入力端子IP、IMに入力される差動入力信号に対応する出力信号が出力される。

【0030】

図2の差動増幅回路1に含まれるMOSトランジスタとしては、いずれも、(ノーマリーオフである)エンハンスメント型のトランジスタが使用可能である。

【0031】

本実施形態の差動増幅回路1の構成において重要な点は、その回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称であることである。即ち、本実施形態の差動増幅回路1では、出力段5が、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、出力段4に含まれるPMOSトランジスタをNMOSトランジスタに置き換え、出力段4に含まれるNMOSトランジスタに接続される接地端子を電源端子に置き換え、出力段4に含まれるPMOSトランジスタに接続される電源端子を接地端子に置き換えた構成を有している。加えて、NMOSトランジスタの閾値電圧より高い所定のバイアス電圧が供給される出力段4のNMOSトランジスタに対応する出力段5のPMOSトランジスタには、電源電圧VDDからPMOSトランジスタの閾値電圧を減じた電圧より低い所定のバイアス電圧が供給される。更に、電源電圧VDDからPMOSトランジスタの閾値電圧を減じた電圧より低い所定のバイアス電圧が供給される出力段4のPMOSトランジスタに対応する出力段5のNMOSトランジスタには、NMOSトランジスタの閾値電圧より高い所定のバイアス電圧が供給される。

【0032】

出力段4、5の間の対応関係をより具体的に説明すると、出力段5は、出力段4のNMOSトランジスタM24〜M27をこの順にPMOSトランジスタM2L、M2M、M2J、M2Kに置き換え、PMOSトランジスタM28〜M2Bをこの順にNMOSトランジスタM2H、M2I、M2F、M2Gに置き換え、NMOSトランジスタM24、M25に接続されている接地端子を電源端子に置き換え、PMOSトランジスタM2A、M2Bに接続されている電源端子を接地端子に置き換えた構成を有している。

【0033】

加えて、出力段4のバイアス電圧V22が供給されるNMOSトランジスタM26、M27に対応する出力段5のPMOSトランジスタM2J、M2Kには、バイアス電圧V23が供給されている。

【0034】

また、出力段4のバイアス電圧V23が供給されるPMOSトランジスタM28、M29に対応する出力段5のNMOSトランジスタM2H、M2Iには、バイアス電圧V22が供給されている。更に、出力段4のバイアス電圧V24が供給されるPMOSトランジスタM2A、M2Bに対応する出力段5のNMOSトランジスタM2F、M2Gには、バイアス電圧V26が供給されている。

【0035】

このような構成によれば、出力段4、5の回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称になり、従って、オフセット電圧が小さくなる。原理的には、図2の差動増幅回路1の構成によれば、オフセット電圧はゼロにまで低減できる。以下では、第1の実施形態の差動増幅回路1においてオフセット電圧が小さくなること、原理的にはゼロになることを説明する。

【0036】

背景技術における議論と同様に、以下の議論においては、特に断りの無い限り、全てのMOSトランジスタが飽和領域で動作しているものとする。以下の議論では、動作の概要が説明されることが重要であり、また、この目的のために、全てのMOSトランジスタが飽和領域で動作していると仮定しても、実際の差動増幅回路1の動作と本質的な相違はない。

【0037】

回路の分析と理解を容易にするために、以下の説明では、全てのNMOSトランジスタ及びPMOSトランジスタの利得係数β(=μCox・W/L)、閾値電圧Vth、及びアーリー電圧VAは、同一であると仮定する。更に、下記の表記を用いる:

Ix:MOSトランジスタMxのドレイン電流(x=21〜2M)

VGSx:MOSトランジスタMxのゲート−ソース間電圧

VDSx:MOSトランジスタMxのドレイン−ソース間電圧

VNy:ノードNyの電位(y=21、26)

VIP:非反転入力信号の電圧(非反転入力端子IPの電位)

VIM:反転入力信号の電圧(反転入力端子IMの電位)

VO:出力電圧(出力端子OUTの電位)

【0038】

出力端子OUTから差動増幅回路1の内部をみた出力抵抗をRoutと表記すると、出力電圧VOは、次式(4)の通りになる:

【数3】

【0039】

ここで、VIP=VIM、即ち、

I22=I23=I2C=I2D ・・・(5)

が成立する場合、式(4)から下記式(6)が成立する:

【数4】

式(6)において

VO=VDD/2 ・・・(7)

であれば、式(6)の第1項が零になるので、やはり式(6)が成立し、矛盾しない。従って、式(7)が成立する、即ち、オフセット電圧が零になる。

【0040】

(第2の実施形態)

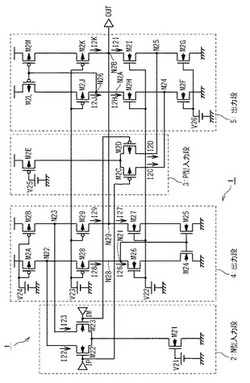

図3は、本発明の第2の実施形態の差動増幅回路11の構成を示す回路図である。差動増幅回路11は、N型入力段12と、P型入力段13と、出力段14、15と、バイアス回路16とを備えている。第1の実施形態に係る図2では、バイアス電圧V22〜V26が電圧源から供給されているとして図示されているが、第2の実施形態では、バイアス電圧V31〜V34を供給するバイアス回路16の構成が具体的に提示されている。

【0041】

詳細には、N型入力段12は、NMOSトランジスタM33〜M35を備えている。NMOSトランジスタM34、35は、ソースが共通に接続された差動トランジスタ対として機能する。即ち、NMOSトランジスタM34のゲートは、非反転入力信号が入力される非反転入力端子IPに接続され、NMOSトランジスタM35のゲートは、反転入力信号が入力される反転入力端子IMに接続されている。NMOSトランジスタM34、35のソースは、NMOSトランジスタM33のドレインに接続されている。NMOSトランジスタM33は、そのゲートにバイアス電圧V31が供給されており、NMOSトランジスタM34、35からなる差動トランジスタ対に定電流を供給する定電流源として機能する。

【0042】

P型入力段13は、PMOSトランジスタM3C〜M3Eを備えている。PMOSトランジスタM3C、M3Eは、ソースが共通に接続された差動トランジスタ対として機能する。即ち、PMOSトランジスタM3Cのゲートは、非反転入力信号が入力される非反転入力端子IPに接続され、PMOSトランジスタM3Dのゲートは、反転入力信号が入力される反転入力端子IMに接続されている。PMOSトランジスタM3C、M3Dのソースは、PMOSトランジスタM3Eのドレインに接続されている。PMOSトランジスタM3Eは、そのゲートにバイアス電圧V34が供給されており、PMOSトランジスタM3C、M3Dからなる差動トランジスタ対に定電流を供給する定電流源として機能する。

【0043】

N型入力段12には、NMOSトランジスタM36、M37とPMOSトランジスタM38〜M3Bからなる出力段14が接続されている。出力段14は、折り返しカスコード型カレントミラーとして構成されており、N型入力段12のNMOSトランジスタM34、M35に流れるドレイン電流I34、I35に対応する出力信号をノードN38に生成する。出力段14には、2つのバイアス電圧V31、V33が供給される。バイアス電圧V31は、NMOSトランジスタM36、M37のゲートに供給され、バイアス電圧V33は、PMOSトランジスタM38、M39のゲートに供給される。

【0044】

同様に、P型入力段13には、NMOSトランジスタM3F〜M3IとPMOSトランジスタM3J、M3Kからなる出力段15が接続されている。出力段15も折り返しカスコード型カレントミラーとして構成されており、P型入力段13のPMOSトランジスタM3C、M3Dに流れるドレイン電流I3C、I3Dに対応する出力信号をノードN3Aに生成する。出力段15には、2つのバイアス電圧V32、V34が供給される。

【0045】

N型入力段12、P型入力段13、出力段14、15に供給されるバイアス電圧V31〜V34は、下記のように設定された電圧である。まず、バイアス電圧V31は、NMOSトランジスタM33、M36、M37の閾値電圧よりも多少高い所定の電圧であり、NMOSトランジスタM33、M36、M37に充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V31は、下記式で表される電圧である:

V31=VTHN3+α5

ここで、VTHN3は、NMOSトランジスタM33、M36、M37の閾値電圧であり、α5>0である。バイアス電圧V31は、NMOSトランジスタM33、M36、M37のゲートに供給される。

【0046】

また、バイアス電圧V32は、NMOSトランジスタM3H、M3Iの閾値電圧よりも多少高い所定の電圧であり、NMOSトランジスタM3H、M3Iに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V32は、下記式で表される電圧である:

V32=VTHN4+VDS_satN2+α6

ここで、VTHN4は、NMOSトランジスタM3H、M3Iの閾値電圧であり、VDS_satN2は、NMOSトランジスタM3F、M3Gのドレイン−ソース間飽和電圧であり、α6>0である。バイアス電圧V32は、NMOSトランジスタM3H、M3Iのゲートに供給される。

【0047】

更に、バイアス電圧V33は、電源電圧VDDからPMOSトランジスタM38、M39の閾値電圧を減じた電圧より多少低い所定の電圧であり、PMOSトランジスタM38、M39に充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V33は、下記式で表される電圧である:

V33=VDD−(VTHP3+VDS_satP2+α7)

ここで、VTHN3は、PMOSトランジスタM38、M39の閾値電圧であり、VDS_satP2は、PMOSトランジスタM3A、M3Bのドレイン−ソース間飽和電圧であり、α7>0である。バイアス電圧V33は、PMOSトランジスタM38、M39のゲートに供給される。

【0048】

最後にバイアス電圧V34は、電源電圧VDDからPMOSトランジスタM3E、M3J、M3Kの閾値電圧を減じた電圧より多少低い所定の電圧であり、PMOSトランジスタM3E、M3J、M3Kに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V34は、下記式で表される電圧である:

V34=VDD−(VTHP4+α8)

ここで、VTHP4は、PMOSトランジスタM3E、M3J、M3Kの閾値電圧であり、α8>0である。バイアス電圧V34は、PMOSトランジスタM3E、M3J、M3Kのゲートに供給される。

【0049】

バイアス回路16は、上述のバイアス電圧V31〜V34を生成する。本実施形態では、バイアス回路16は、ダイオード接続されたNMOSトランジスタM31及びPMOSトランジスタM32と、NMOSトランジスタM31のドレインとPMOSトランジスタM32のドレインの間に直列に接続された抵抗素子R31〜R33とを備えている。バイアス電圧V31は、NMOSトランジスタM31のドレインに生成され、バイアス電圧V32は、抵抗素子R31、R32の接続ノードに生成される。更に、バイアス電圧V33は、抵抗素子R32、R33の接続ノードに生成され、バイアス電圧V34は、PMOSトランジスタM32のドレインに生成される。バイアスV31〜V34の間には、下記関係が成立する:

GND<V31<V32<V33<V34<VDD

【0050】

差動増幅回路11の出力端子OUTは、出力段14の出力として機能するノードN38と、出力段15の出力として機能するノードN3Aとに共通に接続されている。出力端子OUTからは、入力端子IP、IMに入力される差動入力信号に対応する出力信号が出力される。

【0051】

図3の差動増幅回路11に含まれるMOSトランジスタとしては、いずれも、(ノーマリーオフである)エンハンスメント型のトランジスタが使用可能である。

【0052】

第1の実施形態と同様に、第2の実施形態の差動増幅回路11についても、その回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称である。即ち、第2実施形態の差動増幅回路11では、出力段15が、出力段14に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、出力段14に含まれるPMOSトランジスタをNMOSトランジスタに置き換え、出力段14に含まれるNMOSトランジスタに接続される接地端子を電源端子に置き換え、出力段14に含まれるPMOSトランジスタに接続される電源端子を接地端子に置き換えた構成を有している。加えて、出力段14の、閾値電圧より多少高いバイアス電圧V31が供給されるNMOSトランジスタM36、M37に対応する出力段15のPMOSトランジスタM3J、M3Kには、電源電圧VDDから閾値電圧を減じた電圧より多少低いバイアス電圧V34が供給される。更に、出力段14の、電源電圧VDDから閾値電圧を減じた電圧より多少低いバイアス電圧V33が供給されるPMOSトランジスタM38、M39に対応する出力段15のNMOSトランジスタM3H、M3Iには、閾値電圧より多少高いバイアス電圧V32が供給される。

【0053】

このような構成によれば、出力段14、15の回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称になり、従って、オフセット電圧が小さくなる。原理的には、図3の差動増幅回路11の構成によれば、オフセット電圧はゼロにまで低減できる。以下では、第2の実施形態の差動増幅回路11においてオフセット電圧が小さくなること、原理的にはゼロになることを説明する。

【0054】

第1の実施形態における議論と同様に、以下の議論においては、特に断りの無い限り、全てのMOSトランジスタが飽和領域で動作しているものとされ、また、全てのNMOSトランジスタ及びPMOSトランジスタの利得係数β(=μCox・W/L)、閾値電圧Vth、及びアーリー電圧VAは、同一であると仮定される。また、以下の説明では、第1の実施形態と同様の表記が使用される。

【0055】

出力端子OUTから差動増幅回路11の内部をみた出力抵抗をRoutと表記すると、出力電圧VOは、次式(8)の通りになる:

【数5】

【0056】

ここで、VIP=VIM、即ち、

I34=I35=I3C=I3D ・・・(9)

が成立する場合、式(8)から下記式(10)が成立する:

【数6】

式(10)において

VO=VDD/2 ・・・(11)

であれば、式(10)の第1項が零になるので、やはり式(10)が成立し、矛盾しない。従って、式(11)が成立する、即ち、オフセット電圧が零になる。

【0057】

以上に説明されているように、本発明の各実施形態の差動増幅回路は、その回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称であるため、オフセット電圧を小さく、原理的には零にすることができる。

【0058】

なお、上記には本発明の様々な実施形態が記述されているが、本発明は、上記の各実施形態に限定して解釈してはならない。例えば、図2及び図3の差動増幅回路においては、同相帰還手段としてカスコード型カレントミラーが用いられているが、他の構成の同相帰還手段が使用されてもよい。

【0059】

加えて、本発明は、バイポーラトランジスタで構成された差動増幅回路にも適用可能であることに留意されたい。バイポーラトランジスタで構成された差動増幅回路においても、回路構成を、トランジスタの導電型(NPNとPNP)の違いに対して対称にすることにより、オフセット電圧を小さくする、理想的には零にすることができる。更に、本発明は、接合型FET等、MOSトランジスタと同等の動作を行うトランジスタで構成された差動増幅回路にも適用可能であることにも留意されたい。

【図面の簡単な説明】

【0060】

【図1】図1は、公知の差動増幅回路の構成を示す回路図である。

【図2】図2は、本発明の第1の実施形態の構成を示す回路図である。

【図3】図3は、本発明の第2の実施形態の構成を示す回路図である。

【符号の説明】

【0061】

1、11:差動増幅回路

2、12:N型入力段

3、13:P型入力段

4、5、14、15:出力段

16:バイアス回路

【技術分野】

【0001】

本発明は、差動増幅回路に関し、特に、導電型が異なるトランジスタで構成された2つ

の入力段を備える差動増幅回路に関する。

【背景技術】

【0002】

近年は、LSI加工技術の進歩により、例えばCMOSFET(Complementary Metal Oxide Semiconductor Field Effect Transistor)を回路構成要素とするLSIにおいてはMOSFETの実現寸法がますます微細化されており、それに伴いMOSFETへ印加可能な電圧も低下しつつある。一方、携帯可能な各種電子機器に対する性能要求や需要の高まり、またそれらを構成するLSI以外の電池や周辺部品等の進歩、さらには性能要求とも関連するが機器の動作電力の省電力化等への社会的要請等により、これらの機器の電源電圧の低減化の要求が高まっている。

【0003】

電源電圧が低減化されるに従って、電子機器を構成する電子回路の動作や設計はより困難になっている。一つの問題は、NMOSトランジスタ、PMOSトランジスタの何れについても、通常、CMOS構成のLSIで多用されるエンハンスメント型と呼ばれる特性を持つFETにおいては入力電圧として有効な電圧範囲に限度があることである。つまり、エンハンスメント型FETにおいては出力電流をオフ状態に保つ(これをノーマリーオフと呼ぶ。)ために有効な入力電圧として対応出来ない閾値電圧が存在する。具体的には、NMOSトランジスタでは閾値電圧以上の入力電圧にしか対応できず、PMOS型MOSFETでは電源電圧から閾値電圧を減じた電圧以下の入力電圧にしか対応できない。ところが、電源電圧が低減するとそれらに対する閾値電圧の割合が増加する、即ち有効な入力電圧として対応できない電圧範囲の割合が増加することになる。または、回路中の信号の電圧が閾値電圧以下となり、回路の一部が動作しない場合が発生することになる。

【0004】

こうした問題に対処するための一つの有効なアプローチは、NMOSトランジスタで構成された入力段とPMOSトランジスタで構成された入力段の両方を差動増幅回路に設けることである。図1は、このような差動増幅回路の典型的な構成を示す回路図である。図1の構成は、例えば、Behzad Razavi, "Design of Analog CMOS Integrated

Circuits", McGraw-Hill, 2002, p.326に開示されている。

【0005】

図1の差動増幅回路100は、N型入力段101と、P型入力段102と、出力段103とを備えている。N型入力段101は、NMOSトランジスタM11〜M13を備えており、P型入力段102は、PMOSトランジスタM14〜M16を備えている。NMOSトランジスタM12とPMOSトランジスタM14とは、差動入力信号の一方の信号(非反転入力信号)を受け取る非反転入力端子IPに接続されており、NMOSトランジスタM13とPMOSトランジスタM15とは、差動入力信号の他方の信号(反転入力信号)を受け取る反転入力端子IMに接続されている。即ち、N型入力段101のNMOSトランジスタM12、M13は、差動入力信号を受け取るNMOSトランジスタ対を構成しており、P型入力段102のPMOSトランジスタM14、M15は、差動入力信号を受け取るPMOSトランジスタ対を構成している。

【0006】

出力段103は、NMOSトランジスタM17〜M1Aと、PMOSトランジスタM1B〜M1Eとを備えている。出力段103のノードN11、N12は、それぞれ、P型入力段102のPMOSトランジスタM14、M15のドレインに接続されており、出力段103のノードN14、N15は、それぞれ、N型入力段101のNMOSトランジスタM12、M13に接続されている。出力段103は、N型入力段101及びP型入力段102に入力された差動入力信号に対応する出力信号を出力端子OUTから出力する。

【0007】

差動増幅回路100に含まれるNMOSトランジスタ、PMOSトランジスタとしては、(ノーマリーオフである)エンハンスメント型のトランジスタが使用され得る。

【0008】

図1の差動増幅回路100では、NMOSトランジスタM12、M13で構成されたN型入力段101が、NMOSトランジスタの閾値電圧以上の入力電圧に対応可能であり、一方、PMOSトランジスタM14、M15で構成されたP型入力段102は、電源電圧からPMOSトランジスタの閾値電圧を減じた電圧以下の入力電圧に対応可能である。従って、図1の差動増幅回路100では、接地から電源電圧の間の全範囲の入力電圧に対応することができる。

【非特許文献1】Behzad Razavi, "Design of Analog CMOSIntegrated Circuits", McGraw-Hill, 2002, p.326

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、図1の差動増幅回路100は、オフセット電圧がゼロにならないという問題がある。以下、この問題について詳細に議論する。以下の議論においては、特に断りの無い限り、全てのMOSトランジスタが飽和領域で動作しているものとする。以下の議論では、動作の概要が説明されることが重要であり、また、この目的のために、全てのMOSトランジスタが飽和領域で動作していると仮定しても、実際の差動増幅回路100の動作と本質的な相違はない。

【0010】

一般に、MOSトランジスタのドレイン電流IDは、式(1)で表される:

【数1】

ここで、μは、チャネルにおけるキャリア移動度であり、Coxは、単位面積当たりのゲート容量であり、Wはゲート幅であり、Lはゲート長であり、VGSは、ゲート−ソース間電圧であり、Vthは閾値電圧であり、VDSはドレイン−ソース間電圧であり、VAはアーリー電圧である。

【0011】

回路の分析と理解を容易にするために、以下の説明では、全てのNMOSトランジスタ及びPMOSトランジスタの利得係数β(=μCox・W/L)、閾値電圧Vth、及びアーリー電圧VAは、同一であると仮定する。更に、下記の表記を用いる:

Ix:MOSトランジスタMxのドレイン電流(x=11〜1E)

VGSx:MOSトランジスタMxのゲート−ソース間電圧

VDSx:MOSトランジスタMxのドレイン−ソース間電圧

VNy:ノードNyの電位(y=13)

VIP:非反転入力信号の電圧(非反転入力端子IPの電位)

VIM:反転入力信号の電圧(反転入力端子IMの電位)

VO:出力電圧(出力端子OUTの電位)

【0012】

図1の差動増幅回路100において、オフセット電圧がゼロであるということは、VIP=VIMの場合に、次式(2)が成立することである:

VO=VDD/2 ・・・(2)

ここで、VDDは、電源電圧である。

【0013】

出力端子OUTから差動増幅回路100の内部を見込んだ出力抵抗をRoutと標記すると、式(1)から出力電圧VOは、次式(3)の通りになる:

【数2】

【0014】

式(3)においては、差動増幅回路100の各トランジスタの特性が理想的な場合であっても、第1項がゼロにならない。即ち、仮にP型入力段102のPMOSトランジスタM14、M15の特性が全く同一で、N型入力段101のNMOSトランジスタM12、M13の特性が全く同一で、PMOSトランジスタとNMOSトランジスタの閾値電圧が等しくても、式(2)は恒等式として成立しない。式(2)が成立するのはVth17=VOの特別な場合のみである。即ち、図1の回路では常にオフセット電圧はゼロとは言えない。各トランジスタの特性が理想的でない場合には(例えば、各入力段のトランジスタの特性が異なる場合には)、オフセット電圧が更にゼロから離れてしまう。

【課題を解決するための手段】

【0015】

発明者の検討によれば、オフセット電圧がゼロにならない原因の一つは、差動増幅回路100の回路構成、特に、MOSトランジスタM17〜M1Eで構成される出力段103の回路構成が、トランジスタの極性(NチャネルとPチャネル)の違いに対して対称でないからである。発明者の検討によれば、回路構成の非対称性を解消すれば、オフセット電圧を小さくすることができ、理想的には零にすることができる。

【0016】

より具体的には、本発明は、以下に述べられる手段を採用する。その手段を構成する技術的事項の記述には、[特許請求の範囲]の記載と[発明を実施するための最良の形態]の記載との対応関係を明らかにするために、[発明を実施するための最良の形態]で使用される番号・符号が付記されている。但し、付記された番号・符号は、[特許請求の範囲]に記載されている発明の技術的範囲を限定的に解釈するために用いてはならない。

【0017】

本発明の差動増幅回路は、差動入力信号を受け取る第1導電型のトランジスタ対を備える第1入力段(2、12)と、前記第1入力段(2、12)に接続された第1出力段(4、14)と、前記差動入力信号を受け取る、前記第1導電型と異なる第2導電型のトランジスタ対を備える第2入力段(3、13)と、前記第2入力段(3、13)に接続された第2出力段(5、15)と、出力端子(OUT)とを備えている。前記第2出力段(5、15)は、前記第1出力段(4、14)に含まれる前記第1導電型のトランジスタを前記第2導電型のトランジスタに置き換え、前記第1出力段(4、14)に含まれる前記第2導電型のトランジスタを前記第1導電型のトランジスタに置き換え、前記第1出力段(4、14)に含まれる接地端子を電源端子に置き換え、前記第1出力段(4、14)に含まれる電源端子を接地端子に置き換えた構成を有している。前記出力端子(OUT)は、前記第1出力段(4、14)の出力と前記第2出力段(5、15)の出力に共通に接続されている。

【発明の効果】

【0018】

本発明によれば、差動増幅回路のオフセット電圧を小さくする、理想的には零にすることができる。

【発明を実施するための最良の形態】

【0019】

(第1の実施形態)

図2は、本発明の第1の実施形態の差動増幅回路1の構成を示す回路図である。差動増幅回路1は、N型入力段2と、P型入力段3と、出力段4、5を備えている。

【0020】

N型入力段2は、NMOSトランジスタM21〜M23を備えている。NMOSトランジスタM22、23は、ソースが共通に接続された差動トランジスタ対として機能する。即ち、NMOSトランジスタM22のゲートは、差動入力信号の一方(非反転入力信号)が入力される非反転入力端子IPに接続され、NMOSトランジスタM23のゲートは、差動入力信号の他方(反転入力信号)が入力される反転入力端子IMに接続されている。NMOSトランジスタM22、M23のソースは、NMOSトランジスタM21のドレインに接続されている。NMOSトランジスタM21は、そのゲートにバイアス電圧V21が供給されており、NMOSトランジスタM22、M23からなる差動トランジスタ対に定電流を供給する定電流源として機能する。バイアス電圧V21は、NMOSトランジスタM21の閾値電圧より多少高い電圧であり、NMOSトランジスタM21に充分なドレイン電流が流れるように設定される。

【0021】

P型入力段3は、PMOSトランジスタM2C〜M2Eを備えている。PMOSトランジスタM2C、M2Dは、ソースが共通に接続された差動トランジスタ対として機能する。即ち、PMOSトランジスタM2Cのゲートは、非反転入力信号が入力される非反転入力端子IPに接続され、PMOSトランジスタM2Dのゲートは、反転入力信号が入力される反転入力端子IMに接続されている。PMOSトランジスタM2C、M2Dのソースは、PMOSトランジスタM2Eのドレインに接続されている。PMOSトランジスタM2Eは、そのゲートにバイアス電圧V25が供給されており、PMOSトランジスタM22、M23からなる差動トランジスタ対に定電流を供給する定電流源として機能する。バイアス電圧V25は、電源電圧VDDからPMOSトランジスタM2Eの閾値電圧を減じた電圧より多少低い電圧であり、PMOSトランジスタM2Eに充分なドレイン電流が流れるように設定される。

【0022】

N型入力段2には、NMOSトランジスタM24〜M27とPMOSトランジスタM28〜M2Bからなる出力段4が接続されている。出力段4は、折り返しカスコード型カレントミラーとして構成されており、N型入力段2のNMOSトランジスタM22、M23に流れるドレイン電流I22、I23に対応する出力信号をノードN29に生成する。

【0023】

同様に、P型入力段3には、NMOSトランジスタM2F〜M2IとPMOSトランジスタM2J〜M2Mからなる出力段5が接続されている。出力段5も、折り返しカスコード型カレントミラーとして構成されており、P型入力段3のPMOSトランジスタM2C、M2Dに流れるドレイン電流I2C、I2Dに対応する出力信号をノードN2Bに生成する。

【0024】

出力段4、5のそれぞれには3つのバイアス電圧が供給される。詳細には、出力段4には、バイアス電圧V22、V23、V24が供給され、出力段5には、バイアス電圧V22、V23、V26が供給される。バイアス電圧V22、V23は、出力段4、5の両方に供給されることに留意されたい。

【0025】

バイアス電圧V22は、(接地電位GNDを基準電位として)NMOSトランジスタM26、M27、M2H、M2Iの閾値電圧より多少高い所定の電圧であり、NMOSトランジスタM26、M27、M2H、M2Iに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V22は、下記式で表される電圧である:

V22=VTHN1+VDS_satN1+α1

ここで、VTHN1は、NMOSトランジスタM26、M27、M2H、M2Iの閾値電圧であり、VDS_satN1は、NMOSトランジスタM24、M25、M2F、M2Gのドレイン−ソース間飽和電圧であり、α1>0である。バイアス電圧V22は、NMOSトランジスタM26、M27、M2H、M2Iのゲートに供給される。

【0026】

一方、バイアス電圧V23は、電源電圧VDDからPMOSトランジスタM28、M29、M2J、M2Kの閾値電圧を減じた電圧よりも多少低い所定の電圧であり、PMOSトランジスタM28、M29、M2J、M2Kに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V23は、下記式で表される電圧である:

V23=VDD−(VTHP1+VDS_satP1+α2)

ここで、VTHP1は、PMOSトランジスタM28、M29、M2J、M2Kの閾値電圧であり、VDS_satP1は、PMOSトランジスタM2A、M2B、M2L、M2Mのドレイン−ソース間飽和電圧であり、α2>0である。

【0027】

また、バイアス電圧V24は、電源電圧VDDからPMOSトランジスタM2A、M2Bの閾値電圧を減じた電圧より多少低い所定の電圧であり、PMOSトランジスタM2A、M2Bに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V24は、下記式で表される電圧である:

V24=VDD−(VTHP2+α3)

ここで、VTHP2は、PMOSトランジスタM2A、M2Bの閾値電圧であり、α3>0である。

【0028】

最後に、バイアス電圧V26は、NMOSトランジスタM2F、M2Gの閾値電圧よりも多少高い所定の電圧であり、NMOSトランジスタM2F、M2Gに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V26は、下記式で表される電圧である:

V26=VTHN2+α4

ここで、VTHN2は、NMOSトランジスタM2F、M2Gの閾値電圧であり、α4>0である。

【0029】

差動増幅回路1の出力端子OUTは、出力段4の出力として機能するノードN29と、出力段5の出力として機能するノードN2Bとに共通に接続されている。出力端子OUTからは、入力端子IP、IMに入力される差動入力信号に対応する出力信号が出力される。

【0030】

図2の差動増幅回路1に含まれるMOSトランジスタとしては、いずれも、(ノーマリーオフである)エンハンスメント型のトランジスタが使用可能である。

【0031】

本実施形態の差動増幅回路1の構成において重要な点は、その回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称であることである。即ち、本実施形態の差動増幅回路1では、出力段5が、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、出力段4に含まれるPMOSトランジスタをNMOSトランジスタに置き換え、出力段4に含まれるNMOSトランジスタに接続される接地端子を電源端子に置き換え、出力段4に含まれるPMOSトランジスタに接続される電源端子を接地端子に置き換えた構成を有している。加えて、NMOSトランジスタの閾値電圧より高い所定のバイアス電圧が供給される出力段4のNMOSトランジスタに対応する出力段5のPMOSトランジスタには、電源電圧VDDからPMOSトランジスタの閾値電圧を減じた電圧より低い所定のバイアス電圧が供給される。更に、電源電圧VDDからPMOSトランジスタの閾値電圧を減じた電圧より低い所定のバイアス電圧が供給される出力段4のPMOSトランジスタに対応する出力段5のNMOSトランジスタには、NMOSトランジスタの閾値電圧より高い所定のバイアス電圧が供給される。

【0032】

出力段4、5の間の対応関係をより具体的に説明すると、出力段5は、出力段4のNMOSトランジスタM24〜M27をこの順にPMOSトランジスタM2L、M2M、M2J、M2Kに置き換え、PMOSトランジスタM28〜M2Bをこの順にNMOSトランジスタM2H、M2I、M2F、M2Gに置き換え、NMOSトランジスタM24、M25に接続されている接地端子を電源端子に置き換え、PMOSトランジスタM2A、M2Bに接続されている電源端子を接地端子に置き換えた構成を有している。

【0033】

加えて、出力段4のバイアス電圧V22が供給されるNMOSトランジスタM26、M27に対応する出力段5のPMOSトランジスタM2J、M2Kには、バイアス電圧V23が供給されている。

【0034】

また、出力段4のバイアス電圧V23が供給されるPMOSトランジスタM28、M29に対応する出力段5のNMOSトランジスタM2H、M2Iには、バイアス電圧V22が供給されている。更に、出力段4のバイアス電圧V24が供給されるPMOSトランジスタM2A、M2Bに対応する出力段5のNMOSトランジスタM2F、M2Gには、バイアス電圧V26が供給されている。

【0035】

このような構成によれば、出力段4、5の回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称になり、従って、オフセット電圧が小さくなる。原理的には、図2の差動増幅回路1の構成によれば、オフセット電圧はゼロにまで低減できる。以下では、第1の実施形態の差動増幅回路1においてオフセット電圧が小さくなること、原理的にはゼロになることを説明する。

【0036】

背景技術における議論と同様に、以下の議論においては、特に断りの無い限り、全てのMOSトランジスタが飽和領域で動作しているものとする。以下の議論では、動作の概要が説明されることが重要であり、また、この目的のために、全てのMOSトランジスタが飽和領域で動作していると仮定しても、実際の差動増幅回路1の動作と本質的な相違はない。

【0037】

回路の分析と理解を容易にするために、以下の説明では、全てのNMOSトランジスタ及びPMOSトランジスタの利得係数β(=μCox・W/L)、閾値電圧Vth、及びアーリー電圧VAは、同一であると仮定する。更に、下記の表記を用いる:

Ix:MOSトランジスタMxのドレイン電流(x=21〜2M)

VGSx:MOSトランジスタMxのゲート−ソース間電圧

VDSx:MOSトランジスタMxのドレイン−ソース間電圧

VNy:ノードNyの電位(y=21、26)

VIP:非反転入力信号の電圧(非反転入力端子IPの電位)

VIM:反転入力信号の電圧(反転入力端子IMの電位)

VO:出力電圧(出力端子OUTの電位)

【0038】

出力端子OUTから差動増幅回路1の内部をみた出力抵抗をRoutと表記すると、出力電圧VOは、次式(4)の通りになる:

【数3】

【0039】

ここで、VIP=VIM、即ち、

I22=I23=I2C=I2D ・・・(5)

が成立する場合、式(4)から下記式(6)が成立する:

【数4】

式(6)において

VO=VDD/2 ・・・(7)

であれば、式(6)の第1項が零になるので、やはり式(6)が成立し、矛盾しない。従って、式(7)が成立する、即ち、オフセット電圧が零になる。

【0040】

(第2の実施形態)

図3は、本発明の第2の実施形態の差動増幅回路11の構成を示す回路図である。差動増幅回路11は、N型入力段12と、P型入力段13と、出力段14、15と、バイアス回路16とを備えている。第1の実施形態に係る図2では、バイアス電圧V22〜V26が電圧源から供給されているとして図示されているが、第2の実施形態では、バイアス電圧V31〜V34を供給するバイアス回路16の構成が具体的に提示されている。

【0041】

詳細には、N型入力段12は、NMOSトランジスタM33〜M35を備えている。NMOSトランジスタM34、35は、ソースが共通に接続された差動トランジスタ対として機能する。即ち、NMOSトランジスタM34のゲートは、非反転入力信号が入力される非反転入力端子IPに接続され、NMOSトランジスタM35のゲートは、反転入力信号が入力される反転入力端子IMに接続されている。NMOSトランジスタM34、35のソースは、NMOSトランジスタM33のドレインに接続されている。NMOSトランジスタM33は、そのゲートにバイアス電圧V31が供給されており、NMOSトランジスタM34、35からなる差動トランジスタ対に定電流を供給する定電流源として機能する。

【0042】

P型入力段13は、PMOSトランジスタM3C〜M3Eを備えている。PMOSトランジスタM3C、M3Eは、ソースが共通に接続された差動トランジスタ対として機能する。即ち、PMOSトランジスタM3Cのゲートは、非反転入力信号が入力される非反転入力端子IPに接続され、PMOSトランジスタM3Dのゲートは、反転入力信号が入力される反転入力端子IMに接続されている。PMOSトランジスタM3C、M3Dのソースは、PMOSトランジスタM3Eのドレインに接続されている。PMOSトランジスタM3Eは、そのゲートにバイアス電圧V34が供給されており、PMOSトランジスタM3C、M3Dからなる差動トランジスタ対に定電流を供給する定電流源として機能する。

【0043】

N型入力段12には、NMOSトランジスタM36、M37とPMOSトランジスタM38〜M3Bからなる出力段14が接続されている。出力段14は、折り返しカスコード型カレントミラーとして構成されており、N型入力段12のNMOSトランジスタM34、M35に流れるドレイン電流I34、I35に対応する出力信号をノードN38に生成する。出力段14には、2つのバイアス電圧V31、V33が供給される。バイアス電圧V31は、NMOSトランジスタM36、M37のゲートに供給され、バイアス電圧V33は、PMOSトランジスタM38、M39のゲートに供給される。

【0044】

同様に、P型入力段13には、NMOSトランジスタM3F〜M3IとPMOSトランジスタM3J、M3Kからなる出力段15が接続されている。出力段15も折り返しカスコード型カレントミラーとして構成されており、P型入力段13のPMOSトランジスタM3C、M3Dに流れるドレイン電流I3C、I3Dに対応する出力信号をノードN3Aに生成する。出力段15には、2つのバイアス電圧V32、V34が供給される。

【0045】

N型入力段12、P型入力段13、出力段14、15に供給されるバイアス電圧V31〜V34は、下記のように設定された電圧である。まず、バイアス電圧V31は、NMOSトランジスタM33、M36、M37の閾値電圧よりも多少高い所定の電圧であり、NMOSトランジスタM33、M36、M37に充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V31は、下記式で表される電圧である:

V31=VTHN3+α5

ここで、VTHN3は、NMOSトランジスタM33、M36、M37の閾値電圧であり、α5>0である。バイアス電圧V31は、NMOSトランジスタM33、M36、M37のゲートに供給される。

【0046】

また、バイアス電圧V32は、NMOSトランジスタM3H、M3Iの閾値電圧よりも多少高い所定の電圧であり、NMOSトランジスタM3H、M3Iに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V32は、下記式で表される電圧である:

V32=VTHN4+VDS_satN2+α6

ここで、VTHN4は、NMOSトランジスタM3H、M3Iの閾値電圧であり、VDS_satN2は、NMOSトランジスタM3F、M3Gのドレイン−ソース間飽和電圧であり、α6>0である。バイアス電圧V32は、NMOSトランジスタM3H、M3Iのゲートに供給される。

【0047】

更に、バイアス電圧V33は、電源電圧VDDからPMOSトランジスタM38、M39の閾値電圧を減じた電圧より多少低い所定の電圧であり、PMOSトランジスタM38、M39に充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V33は、下記式で表される電圧である:

V33=VDD−(VTHP3+VDS_satP2+α7)

ここで、VTHN3は、PMOSトランジスタM38、M39の閾値電圧であり、VDS_satP2は、PMOSトランジスタM3A、M3Bのドレイン−ソース間飽和電圧であり、α7>0である。バイアス電圧V33は、PMOSトランジスタM38、M39のゲートに供給される。

【0048】

最後にバイアス電圧V34は、電源電圧VDDからPMOSトランジスタM3E、M3J、M3Kの閾値電圧を減じた電圧より多少低い所定の電圧であり、PMOSトランジスタM3E、M3J、M3Kに充分なドレイン電流を流すことができるように決定される。詳細には、バイアス電圧V34は、下記式で表される電圧である:

V34=VDD−(VTHP4+α8)

ここで、VTHP4は、PMOSトランジスタM3E、M3J、M3Kの閾値電圧であり、α8>0である。バイアス電圧V34は、PMOSトランジスタM3E、M3J、M3Kのゲートに供給される。

【0049】

バイアス回路16は、上述のバイアス電圧V31〜V34を生成する。本実施形態では、バイアス回路16は、ダイオード接続されたNMOSトランジスタM31及びPMOSトランジスタM32と、NMOSトランジスタM31のドレインとPMOSトランジスタM32のドレインの間に直列に接続された抵抗素子R31〜R33とを備えている。バイアス電圧V31は、NMOSトランジスタM31のドレインに生成され、バイアス電圧V32は、抵抗素子R31、R32の接続ノードに生成される。更に、バイアス電圧V33は、抵抗素子R32、R33の接続ノードに生成され、バイアス電圧V34は、PMOSトランジスタM32のドレインに生成される。バイアスV31〜V34の間には、下記関係が成立する:

GND<V31<V32<V33<V34<VDD

【0050】

差動増幅回路11の出力端子OUTは、出力段14の出力として機能するノードN38と、出力段15の出力として機能するノードN3Aとに共通に接続されている。出力端子OUTからは、入力端子IP、IMに入力される差動入力信号に対応する出力信号が出力される。

【0051】

図3の差動増幅回路11に含まれるMOSトランジスタとしては、いずれも、(ノーマリーオフである)エンハンスメント型のトランジスタが使用可能である。

【0052】

第1の実施形態と同様に、第2の実施形態の差動増幅回路11についても、その回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称である。即ち、第2実施形態の差動増幅回路11では、出力段15が、出力段14に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、出力段14に含まれるPMOSトランジスタをNMOSトランジスタに置き換え、出力段14に含まれるNMOSトランジスタに接続される接地端子を電源端子に置き換え、出力段14に含まれるPMOSトランジスタに接続される電源端子を接地端子に置き換えた構成を有している。加えて、出力段14の、閾値電圧より多少高いバイアス電圧V31が供給されるNMOSトランジスタM36、M37に対応する出力段15のPMOSトランジスタM3J、M3Kには、電源電圧VDDから閾値電圧を減じた電圧より多少低いバイアス電圧V34が供給される。更に、出力段14の、電源電圧VDDから閾値電圧を減じた電圧より多少低いバイアス電圧V33が供給されるPMOSトランジスタM38、M39に対応する出力段15のNMOSトランジスタM3H、M3Iには、閾値電圧より多少高いバイアス電圧V32が供給される。

【0053】

このような構成によれば、出力段14、15の回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称になり、従って、オフセット電圧が小さくなる。原理的には、図3の差動増幅回路11の構成によれば、オフセット電圧はゼロにまで低減できる。以下では、第2の実施形態の差動増幅回路11においてオフセット電圧が小さくなること、原理的にはゼロになることを説明する。

【0054】

第1の実施形態における議論と同様に、以下の議論においては、特に断りの無い限り、全てのMOSトランジスタが飽和領域で動作しているものとされ、また、全てのNMOSトランジスタ及びPMOSトランジスタの利得係数β(=μCox・W/L)、閾値電圧Vth、及びアーリー電圧VAは、同一であると仮定される。また、以下の説明では、第1の実施形態と同様の表記が使用される。

【0055】

出力端子OUTから差動増幅回路11の内部をみた出力抵抗をRoutと表記すると、出力電圧VOは、次式(8)の通りになる:

【数5】

【0056】

ここで、VIP=VIM、即ち、

I34=I35=I3C=I3D ・・・(9)

が成立する場合、式(8)から下記式(10)が成立する:

【数6】

式(10)において

VO=VDD/2 ・・・(11)

であれば、式(10)の第1項が零になるので、やはり式(10)が成立し、矛盾しない。従って、式(11)が成立する、即ち、オフセット電圧が零になる。

【0057】

以上に説明されているように、本発明の各実施形態の差動増幅回路は、その回路構成がトランジスタの極性(NチャネルとPチャネル)の違いに対して対称であるため、オフセット電圧を小さく、原理的には零にすることができる。

【0058】

なお、上記には本発明の様々な実施形態が記述されているが、本発明は、上記の各実施形態に限定して解釈してはならない。例えば、図2及び図3の差動増幅回路においては、同相帰還手段としてカスコード型カレントミラーが用いられているが、他の構成の同相帰還手段が使用されてもよい。

【0059】

加えて、本発明は、バイポーラトランジスタで構成された差動増幅回路にも適用可能であることに留意されたい。バイポーラトランジスタで構成された差動増幅回路においても、回路構成を、トランジスタの導電型(NPNとPNP)の違いに対して対称にすることにより、オフセット電圧を小さくする、理想的には零にすることができる。更に、本発明は、接合型FET等、MOSトランジスタと同等の動作を行うトランジスタで構成された差動増幅回路にも適用可能であることにも留意されたい。

【図面の簡単な説明】

【0060】

【図1】図1は、公知の差動増幅回路の構成を示す回路図である。

【図2】図2は、本発明の第1の実施形態の構成を示す回路図である。

【図3】図3は、本発明の第2の実施形態の構成を示す回路図である。

【符号の説明】

【0061】

1、11:差動増幅回路

2、12:N型入力段

3、13:P型入力段

4、5、14、15:出力段

16:バイアス回路

【特許請求の範囲】

【請求項1】

差動入力信号を受け取る第1導電型のトランジスタ対を備える第1入力段と、

前記第1入力段に接続された第1出力段と、

前記差動入力信号を受け取る、前記第1導電型と異なる第2導電型のトランジスタ対を備える第2入力段と、

前記第2入力段に接続された第2出力段と、

出力端子

とを備え、

前記第2出力段は、前記第1出力段に含まれる前記第1導電型のトランジスタを前記第2導電型のトランジスタに置き換え、前記第1出力段に含まれる前記第2導電型のトランジスタを前記第1導電型のトランジスタに置き換え、前記第1出力段に含まれる接地端子を電源端子に置き換え、前記第1出力段に含まれる電源端子を接地端子に置き換えた構成を有し、

前記出力端子は、前記第1出力段の出力と前記第2出力段の出力に共通に接続された

差動増幅回路。

【請求項2】

請求項1に記載の差動増幅回路であって、

前記第1導電型はN型であり、

前記第2導電型はP型であり、

前記第1出力段に含まれるトランジスタのうち閾値電圧より高い所定のバイアス電圧が供給される前記第1導電型のトランジスタに対応する前記第2出力段の前記第2導電型のトランジスタには、電源電圧から閾値電圧を減じた電圧より低い所定のバイアス電圧が供給され、

前記第1出力段に含まれるトランジスタのうち電源電圧より概略閾値電圧だけ低いバイアス電圧が供給される前記第2導電型のトランジスタに対応する前記第2出力段の前記第1導電型のトランジスタには、閾値電圧より高い所定のバイアス電圧が供給される

差動増幅回路。

【請求項3】

請求項1又は2に記載の差動増幅回路であって、

前記第1入力段は、ソースが共通に接続された第1及び第2NMOSトランジスタを備え、

前記第2入力段は、ソースが共通に接続された第1及び第2PMOSトランジスタを備え、

前記第1NMOSトランジスタ及び前記第1PMOSトランジスタのゲートには、前記差動入力信号の一方が入力され、

前記第2NMOSトランジスタ及び前記第2PMOSトランジスタのゲートには、前記差動入力信号の他方が入力され、

前記第1出力段は、

第3〜第6NMOSトランジスタと、

第3〜第6PMOSトランジスタ

とを備え、

前記第3及び第4NMOSトランジスタは、接地されたソースと、共通に接続されたゲートとを有し、

前記第5NMOSトランジスタは、前記第3NMOSトランジスタのドレインに接続されたソースと、前記第3及び第4NMOSトランジスタのゲート及び第1ノードに接続されたドレインを有し、

前記第6NMOSトランジスタは、前記第4NMOSトランジスタのドレインに接続されたソースと、第2ノードに接続されたドレインを有し、

前記第5及び第6NMOSトランジスタのゲートには第1バイアス電圧が供給され、

前記第3PMOSトランジスタは、前記第1ノードに接続されたドレインと、前記第1NMOSトランジスタのドレインに接続されたソースを有し、

前記第4PMOSトランジスタは、前記第2ノードに接続されたドレインと、前記第2NMOSトランジスタのドレインに接続されたソースを有し、

前記第3及び第4PMOSトランジスタのゲートには第2バイアス電圧が供給され、

前記第5PMOSトランジスタは、前記第3PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第6PMOSトランジスタは、前記第4PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第5及び第6PMOSトランジスタのゲートには第3バイアス電圧が供給され、

前記第2出力段は、

第7〜第10PMOSトランジスタ

第7〜第10NMOSトランジスタ

とを備え、

前記第7及び第8PMOSトランジスタは、電源端子に接続されたソースと、共通に接続されたゲートとを有し、

前記第9PMOSトランジスタは、前記第7PMOSトランジスタのドレインに接続されたソースと、前記第7及び第8PMOSトランジスタのゲート及び第3ノードに接続されたドレインを有し、

前記第10PMOSトランジスタは、前記第8PMOSトランジスタのドレインに接続されたソースと、第4ノードに接続されたドレインを有し、

前記第9及び第10PMOSトランジスタのゲートには前記第2バイアス電圧が供給さ

れ、

前記第7NMOSトランジスタは、前記第3ノードに接続されたドレインと、前記第1PMOSトランジスタのドレインに接続されたソースを有し、

前記第8NMOSトランジスタは、前記第4ノードに接続されたドレインと、前記第2PMOSトランジスタのドレインに接続されたソースを有し、

前記第7及び第8NMOSトランジスタのゲートには前記第1バイアス電圧が供給され

、

前記第9NMOSトランジスタは、前記第7PMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第10NMOSトランジスタは、前記第8PMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第9及び第10PMOSトランジスタのゲートには第4バイアス電圧が供給され、

前記出力端子は、前記第1出力段の前記第2ノードと前記第2出力段の前記第4ノードとに接続される

差動増幅回路。

【請求項4】

請求項1又は2に記載の差動増幅回路であって、

前記第1入力段は、ソースが共通に接続された第1及び第2NMOSトランジスタを備え、

前記第2入力段は、ソースが共通に接続された第1及び第2PMOSトランジスタを備え、

前記第1NMOSトランジスタ及び前記第1PMOSトランジスタのゲートには、前記差動入力信号の一方が入力され、

前記第2NMOSトランジスタ及び前記第2PMOSトランジスタのゲートには、前記差動入力信号の他方が入力され、

前記第1出力段は、

第3及び第4NMOSトランジスタ

第3〜第6PMOSトランジスタと、

とを備え、

前記第3NMOSトランジスタは、接地されたソースと、第1ノードに接続されたドレインとを有し、

前記第4NMOSトランジスタは、接地されたソースと、第2ノードに接続されたドレインとを有し、

前記第3及び第4NMOSトランジスタのゲートには第1バイアス電圧が供給され、

前記第3PMOSトランジスタは、前記第1ノードに接続されたドレインと、前記第1NMOSトランジスタのドレインに接続されたソースを有し、

前記第4PMOSトランジスタは、前記第2ノードに接続されたドレインと、前記第2NMOSトランジスタのドレインに接続されたソースを有し、

前記第3及び第4PMOSトランジスタのゲートには第2バイアス電圧が供給され、

前記第5PMOSトランジスタは、前記第3PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第6PMOSトランジスタは、前記第4PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第5及び第6PMOSトランジスタのゲートは、前記第3PMOSトランジスタのドレインに共通に接続され、

前記第2出力段は、

第7及び第8PMOSトランジスタと、

第5〜第8NMOSトランジスタ

とを備え、

前記第7PMOSトランジスタは、電源端子に接続されたソースと、第3ノードに接続されたドレインとを有し、

前記第8PMOSトランジスタは、電源端子に接続されたソースと、第4ノードに接続されたドレインとを有し、

前記第7及び第8PMOSトランジスタのゲートには第3バイアス電圧が供給され、

前記第5NMOSトランジスタは、前記第3ノードに接続されたドレインと、前記第1PMOSトランジスタのドレインに接続されたソースを有し、

前記第6NMOSトランジスタは、前記第4ノードに接続されたドレインと、前記第2PMOSトランジスタのドレインに接続されたソースを有し、

前記第5及び第6NMOSトランジスタのゲートには第4バイアス電圧が供給され、

前記第7NMOSトランジスタは、前記第5NMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第8NMOSトランジスタは、前記第6NMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第7及び第8NMOSトランジスタのゲートは、前記第5NMOSトランジスタのドレインに共通に接続され、

前記出力端子は、前記第1出力段の前記第2ノードと前記第2出力段の前記第4ノードとに接続される

差動増幅回路。

【請求項5】

請求項4に記載の差動増幅回路であって、

前記第1バイアス電圧よりも前記第4バイアス電圧が高く、

前記第4バイアス電圧よりも前記第2バイアス電圧が高く、

前記第2バイアス電圧よりも前記第3バイアス電圧が高い

差動増幅回路。

【請求項1】

差動入力信号を受け取る第1導電型のトランジスタ対を備える第1入力段と、

前記第1入力段に接続された第1出力段と、

前記差動入力信号を受け取る、前記第1導電型と異なる第2導電型のトランジスタ対を備える第2入力段と、

前記第2入力段に接続された第2出力段と、

出力端子

とを備え、

前記第2出力段は、前記第1出力段に含まれる前記第1導電型のトランジスタを前記第2導電型のトランジスタに置き換え、前記第1出力段に含まれる前記第2導電型のトランジスタを前記第1導電型のトランジスタに置き換え、前記第1出力段に含まれる接地端子を電源端子に置き換え、前記第1出力段に含まれる電源端子を接地端子に置き換えた構成を有し、

前記出力端子は、前記第1出力段の出力と前記第2出力段の出力に共通に接続された

差動増幅回路。

【請求項2】

請求項1に記載の差動増幅回路であって、

前記第1導電型はN型であり、

前記第2導電型はP型であり、

前記第1出力段に含まれるトランジスタのうち閾値電圧より高い所定のバイアス電圧が供給される前記第1導電型のトランジスタに対応する前記第2出力段の前記第2導電型のトランジスタには、電源電圧から閾値電圧を減じた電圧より低い所定のバイアス電圧が供給され、

前記第1出力段に含まれるトランジスタのうち電源電圧より概略閾値電圧だけ低いバイアス電圧が供給される前記第2導電型のトランジスタに対応する前記第2出力段の前記第1導電型のトランジスタには、閾値電圧より高い所定のバイアス電圧が供給される

差動増幅回路。

【請求項3】

請求項1又は2に記載の差動増幅回路であって、

前記第1入力段は、ソースが共通に接続された第1及び第2NMOSトランジスタを備え、

前記第2入力段は、ソースが共通に接続された第1及び第2PMOSトランジスタを備え、

前記第1NMOSトランジスタ及び前記第1PMOSトランジスタのゲートには、前記差動入力信号の一方が入力され、

前記第2NMOSトランジスタ及び前記第2PMOSトランジスタのゲートには、前記差動入力信号の他方が入力され、

前記第1出力段は、

第3〜第6NMOSトランジスタと、

第3〜第6PMOSトランジスタ

とを備え、

前記第3及び第4NMOSトランジスタは、接地されたソースと、共通に接続されたゲートとを有し、

前記第5NMOSトランジスタは、前記第3NMOSトランジスタのドレインに接続されたソースと、前記第3及び第4NMOSトランジスタのゲート及び第1ノードに接続されたドレインを有し、

前記第6NMOSトランジスタは、前記第4NMOSトランジスタのドレインに接続されたソースと、第2ノードに接続されたドレインを有し、

前記第5及び第6NMOSトランジスタのゲートには第1バイアス電圧が供給され、

前記第3PMOSトランジスタは、前記第1ノードに接続されたドレインと、前記第1NMOSトランジスタのドレインに接続されたソースを有し、

前記第4PMOSトランジスタは、前記第2ノードに接続されたドレインと、前記第2NMOSトランジスタのドレインに接続されたソースを有し、

前記第3及び第4PMOSトランジスタのゲートには第2バイアス電圧が供給され、

前記第5PMOSトランジスタは、前記第3PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第6PMOSトランジスタは、前記第4PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第5及び第6PMOSトランジスタのゲートには第3バイアス電圧が供給され、

前記第2出力段は、

第7〜第10PMOSトランジスタ

第7〜第10NMOSトランジスタ

とを備え、

前記第7及び第8PMOSトランジスタは、電源端子に接続されたソースと、共通に接続されたゲートとを有し、

前記第9PMOSトランジスタは、前記第7PMOSトランジスタのドレインに接続されたソースと、前記第7及び第8PMOSトランジスタのゲート及び第3ノードに接続されたドレインを有し、

前記第10PMOSトランジスタは、前記第8PMOSトランジスタのドレインに接続されたソースと、第4ノードに接続されたドレインを有し、

前記第9及び第10PMOSトランジスタのゲートには前記第2バイアス電圧が供給さ

れ、

前記第7NMOSトランジスタは、前記第3ノードに接続されたドレインと、前記第1PMOSトランジスタのドレインに接続されたソースを有し、

前記第8NMOSトランジスタは、前記第4ノードに接続されたドレインと、前記第2PMOSトランジスタのドレインに接続されたソースを有し、

前記第7及び第8NMOSトランジスタのゲートには前記第1バイアス電圧が供給され

、

前記第9NMOSトランジスタは、前記第7PMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第10NMOSトランジスタは、前記第8PMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第9及び第10PMOSトランジスタのゲートには第4バイアス電圧が供給され、

前記出力端子は、前記第1出力段の前記第2ノードと前記第2出力段の前記第4ノードとに接続される

差動増幅回路。

【請求項4】

請求項1又は2に記載の差動増幅回路であって、

前記第1入力段は、ソースが共通に接続された第1及び第2NMOSトランジスタを備え、

前記第2入力段は、ソースが共通に接続された第1及び第2PMOSトランジスタを備え、

前記第1NMOSトランジスタ及び前記第1PMOSトランジスタのゲートには、前記差動入力信号の一方が入力され、

前記第2NMOSトランジスタ及び前記第2PMOSトランジスタのゲートには、前記差動入力信号の他方が入力され、

前記第1出力段は、

第3及び第4NMOSトランジスタ

第3〜第6PMOSトランジスタと、

とを備え、

前記第3NMOSトランジスタは、接地されたソースと、第1ノードに接続されたドレインとを有し、

前記第4NMOSトランジスタは、接地されたソースと、第2ノードに接続されたドレインとを有し、

前記第3及び第4NMOSトランジスタのゲートには第1バイアス電圧が供給され、

前記第3PMOSトランジスタは、前記第1ノードに接続されたドレインと、前記第1NMOSトランジスタのドレインに接続されたソースを有し、

前記第4PMOSトランジスタは、前記第2ノードに接続されたドレインと、前記第2NMOSトランジスタのドレインに接続されたソースを有し、

前記第3及び第4PMOSトランジスタのゲートには第2バイアス電圧が供給され、

前記第5PMOSトランジスタは、前記第3PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第6PMOSトランジスタは、前記第4PMOSトランジスタのソースに接続されたドレインと、電源端子に接続されたソースとを有し、

前記第5及び第6PMOSトランジスタのゲートは、前記第3PMOSトランジスタのドレインに共通に接続され、

前記第2出力段は、

第7及び第8PMOSトランジスタと、

第5〜第8NMOSトランジスタ

とを備え、

前記第7PMOSトランジスタは、電源端子に接続されたソースと、第3ノードに接続されたドレインとを有し、

前記第8PMOSトランジスタは、電源端子に接続されたソースと、第4ノードに接続されたドレインとを有し、

前記第7及び第8PMOSトランジスタのゲートには第3バイアス電圧が供給され、

前記第5NMOSトランジスタは、前記第3ノードに接続されたドレインと、前記第1PMOSトランジスタのドレインに接続されたソースを有し、

前記第6NMOSトランジスタは、前記第4ノードに接続されたドレインと、前記第2PMOSトランジスタのドレインに接続されたソースを有し、

前記第5及び第6NMOSトランジスタのゲートには第4バイアス電圧が供給され、

前記第7NMOSトランジスタは、前記第5NMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第8NMOSトランジスタは、前記第6NMOSトランジスタのソースに接続されたドレインと、接地されたソースとを有し、

前記第7及び第8NMOSトランジスタのゲートは、前記第5NMOSトランジスタのドレインに共通に接続され、

前記出力端子は、前記第1出力段の前記第2ノードと前記第2出力段の前記第4ノードとに接続される

差動増幅回路。

【請求項5】

請求項4に記載の差動増幅回路であって、

前記第1バイアス電圧よりも前記第4バイアス電圧が高く、

前記第4バイアス電圧よりも前記第2バイアス電圧が高く、

前記第2バイアス電圧よりも前記第3バイアス電圧が高い

差動増幅回路。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2009−171548(P2009−171548A)

【公開日】平成21年7月30日(2009.7.30)

【国際特許分類】

【出願番号】特願2008−285481(P2008−285481)

【出願日】平成20年11月6日(2008.11.6)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成21年7月30日(2009.7.30)

【国際特許分類】

【出願日】平成20年11月6日(2008.11.6)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]