新暗号規格(AES)向けの柔軟なアーキテクチャおよび命令

【課題】汎用プロセッサ用の柔軟なAES命令セットを提供する。

【解決手段】AES命令セットは、AES暗号化または復号化用に「1ラウンド」パスを行う命令を含み、さらに、鍵生成を行う命令を含む。128/192/256ビット鍵用の鍵生成の鍵サイズおよびラウンド数を示すのに直近を利用してよい。柔軟なAES命令セットは、暗黙のレジスタをトラッキングする必要がないので、パイプライン能力の最大限の発揮が可能である。

【解決手段】AES命令セットは、AES暗号化または復号化用に「1ラウンド」パスを行う命令を含み、さらに、鍵生成を行う命令を含む。128/192/256ビット鍵用の鍵生成の鍵サイズおよびラウンド数を示すのに直近を利用してよい。柔軟なAES命令セットは、暗黙のレジスタをトラッキングする必要がないので、パイプライン能力の最大限の発揮が可能である。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、暗号化アルゴリズムに係り、特に、新暗号規格(AES)アルゴリズムに係る。

【背景技術】

【0002】

暗号学はアルゴリズムに依存するツールであり、情報保護における要諦である。アルゴリズムは、複雑な数学的アルゴリズムであり、ビット列がその要諦である。暗号システムには、秘密鍵システムと公開鍵システムという2つの基本的な種類がある。秘密鍵システムは、2以上の当事者間で共有される単一の鍵(「秘密鍵」)を有する対称システムとも称される。単一の鍵は、情報の暗号化および復号化両方に用いられる。

【0003】

(米国)標準技術局(NIST)がFIPS(Federal Information Processing Standard)197として刊行した新暗号規格(AES)は秘密鍵システムである。AESは、情報の暗号化および復号化を行うことのできる対称ブロック暗号である。

【0004】

暗号化は、秘密鍵(暗号鍵)を用いて一連の変換を行うことで、「平文」と称される理解可能なデータを「暗号文」と称される理解不能な形式に変換する。暗号の変換は、(1)排他的論理和(XOR)演算を用いて、ラウンド鍵(暗号鍵から得られる値)を、状態(2次元のバイト列)に加算すること、(2)非線形バイト置換テーブル(S−Box)を用いて状態を処理すること、(3)状態の最後の3行を異なるオフセットで周期的にシフトすること、および(4)状態の全ての列を取り出して、そのデータを(互いに独立して)混合して、新たな列を作成すること、を含む。

【0005】

復号化(逆暗号化)は、暗号鍵を用いて一連の変化を行うことで、「暗号文」ブロックを、同じサイズの「平文」ブロックに変換する。逆暗号化における変換は、暗号化における変換の逆の処理である。

【0006】

AES規格では、128ビットのデータブロックの処理に、長さが128、192、および256ビットの暗号鍵を用いるラインデールアルゴリズムを指定する。異なる鍵の長さは、通常、AES−128、AES−192、およびAES−256と称される。

【0007】

AESアルゴリズムは、平文を暗号文に、または暗号文を平文に、10、12、または14個の連続したラウンドで変換し、ラウンド数は鍵の長さに依存している。

【図面の簡単な説明】

【0008】

請求されている主題の実施形態の特徴は、以下の詳細な記載を、図面を参照して読むことで明らかになるが、図面において同様の要素には同様の参照番号が付されている。

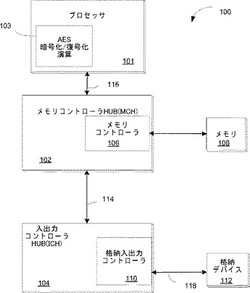

【図1】本発明の原理による、汎用プロセッサにおいてAES暗号化および復号化を行う柔軟なアーキテクチャおよび命令の一実施形態を含むシステムのブロック図である。

【図2】図1に示すプロセッサの一実施形態のブロック図である。

【図3】本発明の原理による、AES暗号化および復号化を行う図2に示す実行部の一実施形態を含むブロック図である。

【図4】図3の実行部によるAES暗号化ラウンド命令のフローを示すフローグラフである。

【図5】図3の実行部によるAES暗号化最終ラウンド命令のフローを示すフローグラフである。

【図6】図3の実行部によるAES復号化ラウンド命令のフローを示すフローグラフである。

【図7】図3の実行部によるAES復号化最終ラウンド命令のフローを示すフローグラフである。

【図8】ラウンド鍵を生成し暗号化および復号化を行うのに利用されうる直近のバイトを有するAESラウンド命令の一実施形態を示す。 以下の詳細な記載は、請求されている主題の例示的な実施形態を参照しながら述べるが、当業者には多くの代替例、変形例、および変更例が明らかである。故に、請求されている主題は広義に解釈されることが意図されており、添付請求項で定義が行われることが意図されている。

【発明を実施するための形態】

【0009】

新暗号規格(AES)アルゴリズムは、通常ソフトウェアまたは専用プロセッサで実行されるコンピューティング集約型のアルゴリズムである。故にこの暗号化は、通常、コンピュータに格納されている情報のサブセット(「トップシークレット」として機密扱いされうるような類の情報等)の暗号化に限って利用されている。しかし、コンピュータに格納されている情報を今まで以上に暗号化する必要がでてきている。例えば、携帯コンピュータに格納されている全ての情報が暗号化されれば、携帯コンピュータの盗難に際しても情報保護が可能となる。

【0010】

AESは、128、192、または256ビットのサイズの鍵を用いて、128ビットブロックに施されるブロック暗号である。鍵のサイズに応じて、演算列を多くのラウンド(10、12、または14)について繰り返す。

【0011】

各ラウンドにおける鍵の生成は、ラウンド鍵を格納する暗黙の128ビットレジスタを利用して、その都度(on the fly)(つまり各ラウンド直前に)行われてよい。しかし、暗黙のレジスタの利用により、前の命令結果に対する依存性から、x86レジスタベースのプロセッサの性能が低下する虞がある。

【0012】

例えば、アプリケーションによっては、フロー毎に異なる鍵を有しうるネットワークパケットを処理するためその都度鍵生成することが好都合なものもある。一方で、例えばディスクドライブのコンテンツを暗号化/復号化するのに用いられる単一の鍵に多くの性能が必要とされる類のアプリケーションもある。このように、鍵生成には柔軟性が求められる。本発明の一実施形態は、汎用プロセッサでAES暗号化および復号化を行う柔軟なアーキテクチャおよび命令を提供する。

【0013】

図1は、本発明の原理による、汎用プロセッサにおいてAES暗号化および復号化を行う柔軟なアーキテクチャおよび命令の一実施形態を含むシステム100のブロック図である。システム100は、プロセッサ101、メモリコントローラハブ(MCH)またはグラフィックメモリハブ(GMCH)102、および入出力(I/O)コントローラハブ(ICH)104を含む。MCH102は、プロセッサ101とメモリ108との間の通信を制御するメモリコントローラ106を含む。プロセッサ101とMCH102とは、システムバス116を介して通信する。

【0014】

プロセッサ101は、シングルコアIntel(登録商標)Pentium(登録商標) IV(登録商標)プロセッサ、シングルコアIntel Celeronプロセッサ、Intel(登録商標)XScaleプロセッサ、または、Intel(登録商標)Pentium(登録商標) D、Intel(登録商標)Xeon(登録商標)プロセッサ等のマルチコアプロセッサ、または、Intel(登録商標)Core(登録商標)Duoプロセッサ、または任意の他の種類のプロセッサ等の複数のプロセッサのいずれかであってよい。

【0015】

メモリ108は、ダイナミックRAM(DRAM)、スタティックRAM(SRAM)、シンクロナスDRAM(SDRAM)、ダブルデータレート2(DDR2)RAM、またはランバスDRAM(RDRAM)、または任意の他の種類のメモリであってよい。

【0016】

ICH104は、ディレクトメディアインタフェース(DMI)等の高速チップツーチップインターコネクト114を用いてMCH102に連結されてよい。DMIは、2ギガビット/秒の同時転送レートを2つの単方向レーンによりサポートする。

【0017】

ICH104は、ICH104に連結された少なくとも1つの格納デバイス112との通信を制御する格納I/Oコントローラ110を含みうる。格納デバイスは、例えば、ディスクドライブ、デジタルビデオディスク(DVD)ドライブ、コンパクトディスク(CD)ドライブ、RAID(Redundant Array of Independent Disks)、テープドライブまたは他の格納デバイスであってよい。ICH104は、格納プロトコルインターコネクト118を介して、SAS(Serial Attached Small Computer System Interface)またはSATA (Serial Advanced Technology Attachment)等のシリアル格納プロトコルを用いて格納デバイス112と通信しうる。

【0018】

プロセッサ101は、AES暗号化および復号化演算を行うAES機能103を含む。AES機能103は、メモリ108に格納されている、および/または、格納デバイス112に格納されている情報の暗号化または復号化に利用されうる。

【0019】

図2は、図1に示すプロセッサ101の一実施形態のブロック図である。プロセッサ101は、レベル1(L1)命令キャッシュ202から受信したプロセッサ命令を復号化するフェッチ復号化部206を含む。命令実行に利用されるデータはレジスタファイル208に格納されていてよい。一実施形態においては、レジスタファイル208は、複数の128ビットレジスタを含み、これらは、AES命令が利用するデータを格納する際、AES命令が利用する。

【0020】

一実施形態においては、レジスタファイルは、ストリーミング(シングルインストラクションマルチプルデータ(SIMD))エクステンション(SSE)インストラクションのセットを有するIntel Pentium(登録商標) MMXプロセッサに提供されている128ビットのMMXレジスタに類似した128ビットレジスタ群である。SIMDプロセッサでは、データが128ビットブロックで処理され、一度に1つの128ビットブロックがロードされる。

【0021】

フェッチ復号化部206は、L1命令キャッシュ202からマイクロインストラクションをフェッチして、該マイクロインストラクションを復号化して、マイクロコード読み取り専用メモリ(ROM)214に格納されうるマイクロ演算(μops)と称される簡単な演算に分割する。実行部210は、マイクロ演算をスケジューリングして実行する。示されている実施形態では、実行部210のAES機能103は、AES命令セット用のマイクロ演算を含む。リタイヤ部212は、実行された命令の結果を、レジスタまたはメモリに書き込む。AES命令が利用するラウンド鍵214は、L1データキャッシュ204に格納されており、実行部210にロードされて、マイクロ演算がAES命令セットのAES命令を実行するのに利用されてよい。ラウンド鍵214をデータキャッシュ204に格納することで、例えばシステム100に格納されている暗号化情報にアクセスすべくラウンド鍵を取得しようとする試みのようなサイドチャネル攻撃からラウンド鍵を守る。

【0022】

図3は、本発明の原理によりAES暗号化および復号化を行う図2に示す実行部210の一実施形態を示すブロック図である。図3を、図2との関連で説明する。

【0023】

フェッチ復号化部206がAES命令を復号した後、実行部210はAES命令を、マイクロコードROM214に格納されていてよいAES命令に関するマイクロ演算を行うことで実行する。

【0024】

本発明の一実施形態による柔軟なAES命令セットにより、プログラマーは、処理データ量、メモリ帯域幅および容量に対する性能のトレードオフを行うことができる。

【0025】

アプリケーションによっては、同じ鍵を使い続けるものもある。性能が非常に重要なアプリケーションでは、鍵の鍵スケジュールを1度予め計算して(つまり、ラウンド毎のラウンド鍵)、それをメモリに格納しておくという観点でのトレードオフが行われる。他の種類のアプリケーションには、鍵スケジュールを格納するのに利用されるメモリ量を最小限に抑え、且つ、マルチブロック演算では良好な性能を達成することを望むものもある。この種類のアプリケーションでは、鍵スケジュールを、処理前に多数のブロックについて予め演算しておくことが考えられる。暗号鍵または逆暗号鍵のみを格納して、他のものは適宜性能面の犠牲を鑑みながら生成することによって、メモリフットプリントがさらに低減されうる。

【0026】

x86−型プロセッサでは、AESラウンド鍵演算およびAESスケジューリング演算が利用可能な領域および実行ポート数により、AES命令の性能に制限が加わる。鍵拡張が全てのブロック暗号化で必要となるシステムにおいては、AESスケジューリング演算およびAESラウンド鍵演算を異なる実行ポートに実装することで、性能を向上させる可能性がある。しかし、x−86型プロセッサでは、異なる実行ポートおよびこれら異なるポート制御用の追加領域は提供不可能なことがある。

【0027】

一実施形態では、暗号化ラウンド、復号化ラウンド、暗号化復号化最終ラウンド最終ラウンドを行い、ラウンド暗号鍵またはラウンド復号鍵を算出するのに、それぞれ別個のAES命令を含むAES命令セットが提供される。一実施形態では、AES命令セットが6つのAES命令を含む。各AESラウンド命令は、固有演算コード(opcode)を有する。固定幅ラウンド鍵の一実施形態(例えば128ビット)におけるAES命令セットのAESラウンド命令を、以下の表1に示す。

【表1】

【0028】

AES命令セットは、4つのAESラウンド命令(暗号化、復号化、暗号化最終ラウンド、復号化最終ラウンド)、および2つのAESラウンド鍵命令(次のラウンド鍵および前のラウンド鍵)を含む。AES命令セットのAESラウンド命令は、最終ラウンド以外の全てのラウンドに利用される暗号化および復号化ラウンド演算を行うシングルラウンド演算を含む。例えば、表1のAESENCRYPTRoundのシングルラウンド命令では、入力データが128ビットレジスタ(xmmsrcdst)に格納され、ラウンド鍵が別の128ビットレジスタ(xmm)に格納される。この命令は、128ビットxmmsrcdstレジスタに格納されている入力データ(ソース)に対してAESラウンド演算を行い、128ビットxmmsrcdstレジスタに格納されている入力データを、ラウンド演算実行結果で上書きする。故に、xmmsrcdstは当初は入力データを、そして後には、AESラウンド演算結果を格納する。

【0029】

さらにAES命令セットは、最終復号化ラウンドのAES復号命令および最終暗号化ラウンドのAES暗号命令を含む。例えば、表1のAESENCRYPTLastRoundのシングルラウンド命令では、入力データが128ビットレジスタ(xmmsrcdst)に格納され、ラウンド鍵が別の128ビットレジスタ(xmm)に格納される。この命令は、xmmsrcdstレジスタに格納されている入力データ(ソース)に対してAESラウンド演算を行い、xmmsrcdstレジスタに格納されている入力データを、ラウンド演算実行結果で上書きする。故に、xmmsrcdstは当初は入力データを、そして後には、ラウンド演算結果を格納する。xmmレジスタは、ラウンド演算のラウンド鍵を格納する。

【0030】

別の実施形態では、ラウンドおよび最終ラウンド命令(例えば、AESENCRYPTRoundおよびAESENCRYPTLastRound)が、レジスタファイル304からではなくて、メモリ(m/128)から入力を受け取ってよい(例えば、AESラウンド命令は、AESENCRYPTRound xmmsrcdst m/128であってよい)。

【0031】

AES命令セットの他の2つのAES命令は、鍵のサイズ(つまり、128ビット、192ビット、または256ビット)に応じてAESラウンド用のラウンド鍵を生成する。これらAESラウンド鍵命令の一方は暗号化演算に利用されるラウンド鍵を生成し、他方は復号化演算に利用されるラウンド鍵を生成する。AESNextRoundKey AESPreviousRoundKey命令における直近のフィールドは、鍵のサイズを特定する{128、192、256}。

【0032】

また別の実施形態では、直近のフィールドの代わりに、異なる鍵のサイズが、各々が固有演算コードを有する別個の命令として実装されてよい。この実施形態では、AESラウンド鍵命令の数は、各ラウンド鍵演算(例えばAESNextRoundKey_128、AESNextRoundKey_192、およびAESNextRoundKey_256)について3つの別個の命令を含み、AESPreviousRoundKeyもまた、これらに類似した3つの命令のセットを含む。この実施形態では、命令セット内の命令の総数は、先に述べた実施形態の6つに比して、10となっている。

【0033】

レジスタファイル304は、AES命令セットのAES命令が利用しうる128ビットレジスタを複数有する。128ビットレジスタは、ソースオペランド、ラウンド鍵、およびAES命令の結果を格納しうる。第1ラウンドでは、AES命令は、暗号される128ビットの平文または復号される128ビットの暗号文であってよいソースオペランドを受信する。128ビット、192ビット、または256ビットの鍵の鍵スケジュールを生成する鍵は、レジスタファイル304内の複数の128ビットレジスタ308のいずれかに格納されていてよい。またラウンド鍵も、レジスタファイルの128ビットレジスタ308のいずれかに格納されてよい。全ての命令は、レジスタファイルのレジスタを利用し、さらに、後述するようにメモリから直接入力を得てよい。

【0034】

表1に示すAES命令セットの一実施形態を利用するソースコードの例を、以下の表2に示す。本例においては、多くのブロックに対して同じ鍵を利用する暗号化を行うアプリケーションで性能が最適化されている。このようなアプリケーションの1つに、ディスクに格納する前に全てのデータを暗号化する際に同じ鍵を利用するようなディスクのコンテンツを暗号化するのに単一の鍵を利用するものがある。本例では、AES−128暗号が行われる。

【0035】

鍵のサイズは、128ビット、192ビット、または256ビットであってよい。行われるラウンドの数(n)は、鍵のサイズに応じて1、10、12、または14で、各ラウンド鍵は固定サイズ(128ビット)であってよい。ラウンド値数が10、12、14の場合、AESマイクロ演算は、128ビット、192ビット、または256ビットの鍵サイズに対して標準的なAES暗号化および復号化を行ってよい。

【0036】

多くのブロックについて同じ鍵を利用する場合、各ラウンドのラウンド鍵(鍵スケジュール)は、予め計算されてメモリ(例えばレベル1データキャッシュ204)に格納されているので、各ブロックの暗号化/復号化演算の前に同じ鍵スケジュールを再度計算する必要がない。

【表2】

【0037】

10エレメントを有するアレイ(RK)を利用して、鍵の鍵スケジュールを格納する。AES−128暗号の入力鍵を、RK[0]に格納して、9ラウンド鍵RK[0]−RK[1]を、AES命令セットからAESNextRoundKey命令を読み出すことで予め計算する。AESNextRoundKey命令は、現在のラウンド鍵に基づいて次のラウンドを計算する。鍵スケジュールについて予め計算されたラウンド鍵は、レベル1データキャッシュ204のラウンド鍵214に格納されてよい。

【0038】

本例においては、そのラウンドのラウンド鍵である鍵スケジュールの該当部分(拡張鍵)が直接レジスタファイル304から入力されると、AESラウンドを行うループに入る前に、排他的論理和(XOR)演算を、状態と鍵とに対して行う。各ラウンド1から9においては、AES命令セットからAESENCRYPTRound命令を呼び出して、AESラウンド演算を1ラウンドについて行う。最終ラウンド(ラウンド10)については、AES命令セットからAESENCRYPTLastRound命令を呼び出して、この最終ラウンドにAESラウンド演算を行う。

【0039】

AES命令が暗号化または復号化する情報は、暗号または複号演算を開始する第1のAES命令が発行される前に、レジスタファイル304のソース/宛先レジスタ306へロードされる。ソースレジスタ306の情報の暗号化/復号化に利用される鍵は、レジスタファイル304の1以上の他のレジスタ308に格納されている。128ビット鍵の場合、鍵の全128ビットが、レジスタファイル304の他の128ビットレジスタのいずれかに格納される。128ビットより大きい鍵のサイズに対しては、最上位ビット(128ビットより大きい)を、128ビットレジスタのうち別のものに格納する。

【0040】

表2に示す例においては、レジスタファイル304のレジスタ308のいずれかにロードされる前に、鍵に基づいて各ラウンドのラウンド鍵が予め計算されて、レベル1データキャッシュ204に格納されていてよい。各ラウンドの鍵は、さらに、レジスタファイル304の1以上のレジスタに格納されていてもよく、または、レベル1データキャッシュ204のラウンド鍵214に格納されていてもよい。

【0041】

AESは、128ビットの固定ブロックサイズと、128、192、または256ビットの鍵サイズとを有し、4x4バイトアレイ(つまり16バイト(128ビット固定ブロックサイズ))で動作する(これを「状態」と称する)。AESアルゴリズムは、128ビットの平文ブロックを、128ビットの暗号文ブロックに変換(暗号化)する、または、128ビットの暗号文ブロックを、128ビットの平文ブロックに変換(復号化)し、これらは、10、12、または14の連続したラウンドで行われ、このラウンド数は鍵のサイズに応じている(128、192、または256ビット)。

【0042】

ラウンド毎の暗号化または復号化演算を行う前に、実行部210は、状態および鍵をレジスタファイル304から取得する。各暗号化/復号化ラウンド演算は、読み取り専用メモリ(ROM)214の鍵スケジューラ302に格納されているAES命令のマイクロ演算を利用して行われる。ここに示す実施形態では、状態(128ビットブロックの状態)は、レジスタ306に格納されており、鍵は、レジスタファイル304の他のレジスタ308の1以上に格納されている。AES命令の実行の結果生じる状態をレジスタファイル304のレジスタ306に格納する。状態は、次のAESラウンドまたはAES暗号化または復号化演算の最終結果が利用する中間ラウンドデータであってよい。

【0043】

ここで示す実施形態においては、鍵スケジューラ302は、AESラウンドで利用するラウンド鍵を生成する。鍵スケジューラ302は、マイクロコード演算として実装されてよく、FIPS PUB197で定義される128ビット、196ビット、および256ビット鍵のラウンド鍵を生成する一連の演算を行うマイクロコード演算を含みうる。

【0044】

別の実施形態では、鍵スケジューラは、実行部210のハードウェア状態マシン列として実装されてよい。また別の実施形態では、鍵スケジューラの幾らかの部分がマイクロコードROM214に格納されているマイクロコード演算として実装され、鍵スケジューラの残りの部分が実行部210のハードウェア状態マシン列として実装されてもよい。

【0045】

鍵スケジューラ302は、nバイトの鍵を、bバイトの拡張鍵(鍵スケジュール)に拡張してよく、この拡張鍵の最初のnバイトが元の鍵であってよい。例えば、128ビットの鍵においては、128ビットの鍵を176バイト(つまり、11x16バイト(128ビット))の拡張鍵に拡張して、この最初の16バイトが元の128ビットの鍵であり、ラウンド数は10である。192ビットの鍵の24バイトを、208バイト(13x16バイト)に拡張して、12個の「ラウンド鍵」を、12ラウンドそれぞれに対して1つずつ割り当てるよう提供し、256ビットの鍵の32バイトを、240バイト(15x16バイト)に拡張して、14個の「ラウンド鍵」を、14ラウンドそれぞれに対して1つずつ割り当てるよう提供する。

【0046】

演算コード(opcode)をAES命令で複号する際、1回のAESラウンドのAES命令のフローを制御するのに利用されるパラメータ数は、制御ロジック322に格納されている。パラメータは、演算の種類(暗号または復号)およびそれが最終ラウンドであるかの情報を含む。

【0047】

AESラウンドロジック324は、ブロック状態314、S−ボックス/逆S−ボックス316、行シフト316および逆列混合またはヌル混合(mix inverse, mix columns or null)(「列混合」と称される)320、およびラウンド鍵加算326という段階のマイクロ演算を含みうる。

【0048】

ブロック状態314では、AESラウンドロジック324への128ビットの入力(状態)に、ビットワイズXORを用いて、鍵(ラウンドに関連付けられた拡張鍵の128ビットの部分)を追加して、128ビットの中間値(状態)を生成する。

【0049】

S−ボックス/逆S−ボックス316では、この128ビットの中間値の各バイトを、これも置換ボックスまたは「S−ボックス」と称されるルックアップテーブルから格納・取得されうる別のバイト値で置換してよい。S−ボックスは、幾らかの数の入力ビットmを取り、それらを幾らかの数の出力ビットnに変換して、通常ルックアップテーブルとして実装する。固定ルックアップテーブルが通常利用される。この演算は、ガロア体(GF)(28)において逆関数を利用することで非線形性を生じる。例えば、nビットの出力は、mビットの入力の外側の2ビットを用いてルックアップテーブルで行を選択し、mビットの入力の内側のビットを用いて列を選択することで、見つけることができる。

【0050】

行シフト318ではS−ボックス/逆S−ボックス316の結果に、ビット線形変換を行い、サブバイト段階から受け取った4x4アレイ(128ビット(16バイト)状態)の各行のバイトを、周期的に左にシフトさせる。各バイトをシフトさせる位置の数は、4x4アレイの各行によって異なる。

【0051】

列混合320では、行シフト318の結果に、ビット線形変換を行い、4x4アレイ(状態)の各行を、バイナリガロア体(GF)(28)上の多項式として扱い、その後、c(x)=3x3+x2+x+2を固定多項式として、モジュロx4+1乗算する。最終AESラウンドは、他のAESラウンドと、列混合320が省かれている点で異なっている。

【0052】

列混合段階320の後、ラウンド鍵加算324では、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。

【0053】

例えば、以下のAES命令を発行して、AES復号の1ラウンドを行うことができる。

AESDECRYPTRound xmmsrcdst xmm

【0054】

本例では、128ビットAES暗号化ラウンド演算を、拡張鍵が{RK[1],RK[2],…RK[10]}として表される鍵を利用して行う。ラウンド鍵は、AESDECRYPTRound命令を発行する前に、AESPreviousRoundKey xmmsrc1,2 xmm dst(中間)命令を発行することで生成されうる。ラウンド鍵は、レベル1データキャッシュ204からブロック状態314へ直接ロードされてもよいし、または、先ずレジスタファイル304のレジスタ(xmm)に格納されていて、その後、レジスタからブロック状態314へロードされてもよい。

【0055】

異なる鍵を利用して各ブロックを暗号化/復号化する場合(例えば、データパケットを暗号化/復号化するネットワークインタフェースコントローラ(NIC)の場合)、ラウンド鍵は、以下の表3でAES−128暗号の疑似コードで示すように各ラウンドについて暗号化/復号化を行う前に、その都度計算されてよい。

【表3】

【0056】

本例においては、該ラウンドのラウンド鍵は、鍵スケジュール(拡張鍵)の10ラウンド各々(つまり、ラウンド1−9およびラウンド10(最終ラウンド))に対してラウンド鍵を利用して暗号化を行う前に生成される。

【0057】

シングルAESラウンド命令およびシングルAESラウンド鍵生成命令を含むAES命令セットにより、異なる数のラウンドおよび鍵スケジュールを有するAESの変形例を生成することができる、つまり、FIPS PUB197では定義されていないAESの変形例を生成することができる。故に、AES命令セットのシングルラウンドAES命令は、AES暗号化および復号化を行う際に柔軟性を提供する。

【0058】

AES命令セットが行うラウンド数は固定されていないので、適宜任意の数のラウンドを行うことができる。例えば、ラウンド数は、ハッシュまたはMAC攻撃またはAESへの攻撃に対する新たな規格が導入された場合、将来の暗号化/復号化規格をサポートするよう変更可能である。

【0059】

図4は、図3の実行部210によるAES暗号化ラウンド命令のフローを示すフローグラフである。

【0060】

ブロック400で、実行部210は、AES暗号化ラウンド命令を待つ。AES暗号化ラウンド命令がフェッチ復号化部206により既に復号化されている場合、処理はブロック402に進む。復号化されていない場合は、ブロック400に留まり、AES暗号化ラウンド命令を待つ。

【0061】

ブロック402で、フェッチ復号化部206による命令復号化中、暗号化が必要である旨を制御ロジック322に格納して、暗号化ラウンド実行に利用されるラウンド鍵および128ビットブロック状態(ソース)をレジスタファイル304から実行部210へロードする。処理はブロック404へ進む。

【0062】

ブロック404で、置換演算を128ビットブロック状態に対して、つまり、ブロック406または418の結果に対して、行う。128ビットブロック状態の各バイトを、これも置換ボックスまたは「S−ボックス」と称されるルックアップテーブルから格納・取得されうる別のバイト値で置換してよい。S−ボックスは、幾らかの数の入力ビットmを取り、それらを幾らかの数の出力ビットnに変換して、通常ルックアップテーブルとして実装する。結果を、128ビットブロック状態として格納する。処理はブロック406へ進む。

【0063】

ブロック406で、128ビットブロック状態(4x4アレイ)に、ビット線形変換を行い、4x4アレイの各行のバイトを、周期的に左にシフトさせる。各バイトをシフトさせる位置の数は、4x4アレイの各行によって異なる。処理はブロック408へ進む。

【0064】

ブロック408で、128ビットブロック状態(4x4アレイ)に、ビット線形変換を行い、4x4アレイ(状態)の各行を、GF(28)により多項式として扱い、その後、c(x)=3x3+x2+x+2を固定多項式として、モジュロx4+1乗算する。処理はブロック410へ進む。

【0065】

ブロック410で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック412へ進む。

【0066】

ブロック412で、そのラウンドの暗号化演算の結果(128ビットブロック状態)を、レジスタファイル304のソース/宛先レジスタ302に格納する。これでAES暗号化命令処理が完了する。

【0067】

以下の表4は、表3に示す疑似コードの実行後に、128ビットブロック入力に128ビット鍵を利用してAES−128暗号化を行った結果の一例を示す。

【表4】

【0068】

図5は、図3の実行部210によるAES暗号化最終ラウンド命令のフローを示すフローグラフである。

ブロック500で、実行は、AES暗号化最終ラウンド命令を待つ。もしもAES暗号化最終ラウンド命令がフェッチ復号化部206で既に復号化されている場合、処理はブロック502に進む。復号化されていない場合は、ブロック500に留まり、AESラウンド暗号化命令を待つ。

ブロック502で、ブロック404(図4)との関連で説明したS−ボックスルックアップに類似した方法で最終ラウンドにS−ボックスルックアップを行う。処理はブロック504へ進む。

ブロック504で、ブロック406(図4)で他のラウンドとの関連で説明したような方法で最終ラウンドに行シフト演算を行う。処理はブロック506へ進む。

ブロック506で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック508へ進む。

ブロック508で、暗号化最終ラウンド演算の結果を、レジスタファイル304のソース/宛先レジスタ306に格納する。これでAES命令の処理が完了する。

【0069】

図6は、図3の実行部210によるAES復号化ラウンド命令のフローを示すフローグラフである。

ブロック600で、実行は、AES復号化ラウンド命令を待つ。AES復号化ラウンド命令がフェッチ復号化部206により既に復号化されている場合、処理はブロック602に進む。復号化されていない場合は、ブロック600に留まり、AES復号化ラウンド命令を待つ。

ブロック602で、フェッチ復号化部206による命令復号化中、復号化ラウンドを行う必要がある旨を制御ロジック322に格納して、復号化ラウンド実行に利用されるラウンド鍵およびソース(128ビットブロック状態)をレジスタファイル304から実行部210へロードする。処理はブロック604へ進む。

ブロック604で行う処理は復号化である。AES規格に定義されている逆s−ボックスルックアップを行うことで、置換演算を128ビットブロック状態に対して行う。処理はブロック606へ進む。

ブロック606で、FIPS PUB197で定義されている逆行シフト演算を行う。処理はブロック608へ進む。

ブロック608で、FIPS PUB197で定義されている逆行シフト演算を行う。処理はブロック610へ進む。

ブロック610で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック612へ進む。

ブロック612で、そのラウンドの復号化演算の結果(128ビットブロック状態)を、レジスタファイル304のソース/宛先レジスタ302に格納する。これでAES復号化ラウンド命令処理が完了する。

【0070】

図7は、図3の実行部210によるAES復号化最終ラウンド命令のフローを示すフローグラフである。

ブロック700で、実行部210は、AES復号化最終ラウンド命令を待つ。もしもAES復号化最終ラウンド命令がフェッチ復号化部206で既に復号化されている場合、処理はブロック702に進む。復号化されていない場合は、ブロック700に留まり、AES復号化ラウンド命令を待つ。

ブロック702で、FIPS PUB197で定義されている逆s−ボックスルックアップを行うことで、最終ラウンドの128ビットブロック状態に置換演算を行う。処理はブロック704へ進む。

ブロック704で、FIPS PUB197で定義されているような方法で最終ラウンドに逆行シフト演算を行う。処理はブロック706へ進む。

ブロック706で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック708へ進む。

ブロック708で、復号化最終ラウンド演算の結果を、レジスタファイル304のソース/宛先レジスタ306に格納する。これでAES復号化最終ラウンド命令の処理が完了する。

【0071】

一実施形態では、図4−7のフローグラフのブロックを、実行部210のハードウェア状態マシン列として実装することができる。別の実施形態では、ブロックの幾らかの部分が読み取り専用メモリ(ROM)214に格納されうるマイクロプログラムとして実装することもできる。ブロックがハードウェア状態マシン列として実装されている実施形態のほうが性能は高いと考えられる。

【0072】

図8は、ラウンド鍵を生成し暗号化および復号化を行うのに利用されうる直近のバイトを有するAESラウンド命令の一実施形態を示す。表1に示すAES命令セットの代わりに単一のAESラウンド命令を提供することで、AES命令セットの機能を行う。単一のAES命令が行う特定の機能は、直近のバイト(key_select_modifier)内のビットに暗号化されている。直近のバイトにより、AESラウンド命令は、各命令が固有演算コードを有する複数の新たな命令を作成する代わりに、新たな特徴を追加するよう拡張される。

【0073】

AESラウンド命令は、記号として以下のように定義されうる。

dest:=aes_key_round(source2,source1),key_select_modifier

【0074】

aes_key_round命令はAES暗号または復号化演算を行うべく、ポート番号に基づいて特定の実行部210に発行される。示されている実施形態では、ポート番号4がAESラウンド命令に指定された実行ポートである。実行部210は、多くのパラレルポート(スーパー−スカラー)に分割される。しかし、全てのポートが等しいわけではない。ポートの中には、大きな整数のマルチプライアー、浮動小数点のマルチプライアーまたはデバイダ等の専用リソースを有するものがある。加算、減算、および排他的論理和等の、これらより簡単で一般的な命令は、多数のポートによりサポートされて最大の性能を発揮する。故に、各命令またはマイクロ演算では、発行制御ロジックがマイクロ演算/命令を発行するポートを決定する。本実施形態では、AES命令は常にポート番号4に対して発行される。しかし、他の実施形態では他のポート番号を利用することができる。

【0075】

図8を参照すると、destはラウンドNに対して128ビットの拡張鍵を格納し、ソース2はラウンドN−1に対して128ビットの拡張鍵を格納し、ソース1はラウンドN−2に対して128ビットの拡張鍵を格納する。key_select_modifierは、現在のラウンド数(N)、演算の方向(暗号化/復号化)、およびAES鍵のサイズを提供するのに利用される8ビットの直近の値である。AES−128では、ソース1は不要であるので無視される。実行部はAES部であり、フラグ(整数または浮動小数点)は利用されない。

【0076】

一実施形態では、直近の値の4つの最下位ビットのビット暗号化は、AES−128に対して1−10のラウンド数、AES−192に対して1−12のラウンド数、およびAES−256に対して2−14のラウンド数、といったラウンド数を示す。AES128および192では、ラウンド数0は無効である、というのも、最初のラウンドが無変更の入力鍵を利用するからである。AES−256では、ラウンド数0と1は無効である、というのも、最初の2つの128ビットラウンドが無変更の256ビット入力鍵を利用するからである。

【0077】

直近のバイトのビット4は演算の方向(暗号化または復号化)を示す(例えば一実施形態では0=暗号、および1=復号、また別の実施形態では1=暗号、および0=復号、というように)。直近のバイトのビット5および6は、AES鍵のサイズを示す。一実施形態では、AES鍵のサイズは以下の表5に示すように定義される。

【表5】

【0078】

別の実施形態では、値11を有するビット[6:5]も、128ビットの鍵のサイズのインジケータである。この実施形態では、ビット[6:5]の全ての値が有効であり、パースされうる。

【0079】

当業者であれば、本発明の実施形態に係る方法を、コンピュータ利用可能な媒体を含むコンピュータプログラムプロダクトに具現化することができることを想到しよう。例えば、コンピュータ利用可能な媒体は、コンピュータ可読プログラムコードが記憶されたコンパクトディスク読み取り専用メモリ(CD ROM)ディスクまたは従来のROMデバイス、またはコンピュータディスク等の読み取り専用メモリデバイスから形成されてよい。

【0080】

本発明の実施形態を特別に示し、実施形態を参照しながら記載してきたが、当業者であれば添付請求項が包括する本発明の実施形態の範囲を逸脱することなく、様々な変更を形態および詳細に対して加えることが可能であることを理解しよう。

【技術分野】

【0001】

本開示は、暗号化アルゴリズムに係り、特に、新暗号規格(AES)アルゴリズムに係る。

【背景技術】

【0002】

暗号学はアルゴリズムに依存するツールであり、情報保護における要諦である。アルゴリズムは、複雑な数学的アルゴリズムであり、ビット列がその要諦である。暗号システムには、秘密鍵システムと公開鍵システムという2つの基本的な種類がある。秘密鍵システムは、2以上の当事者間で共有される単一の鍵(「秘密鍵」)を有する対称システムとも称される。単一の鍵は、情報の暗号化および復号化両方に用いられる。

【0003】

(米国)標準技術局(NIST)がFIPS(Federal Information Processing Standard)197として刊行した新暗号規格(AES)は秘密鍵システムである。AESは、情報の暗号化および復号化を行うことのできる対称ブロック暗号である。

【0004】

暗号化は、秘密鍵(暗号鍵)を用いて一連の変換を行うことで、「平文」と称される理解可能なデータを「暗号文」と称される理解不能な形式に変換する。暗号の変換は、(1)排他的論理和(XOR)演算を用いて、ラウンド鍵(暗号鍵から得られる値)を、状態(2次元のバイト列)に加算すること、(2)非線形バイト置換テーブル(S−Box)を用いて状態を処理すること、(3)状態の最後の3行を異なるオフセットで周期的にシフトすること、および(4)状態の全ての列を取り出して、そのデータを(互いに独立して)混合して、新たな列を作成すること、を含む。

【0005】

復号化(逆暗号化)は、暗号鍵を用いて一連の変化を行うことで、「暗号文」ブロックを、同じサイズの「平文」ブロックに変換する。逆暗号化における変換は、暗号化における変換の逆の処理である。

【0006】

AES規格では、128ビットのデータブロックの処理に、長さが128、192、および256ビットの暗号鍵を用いるラインデールアルゴリズムを指定する。異なる鍵の長さは、通常、AES−128、AES−192、およびAES−256と称される。

【0007】

AESアルゴリズムは、平文を暗号文に、または暗号文を平文に、10、12、または14個の連続したラウンドで変換し、ラウンド数は鍵の長さに依存している。

【図面の簡単な説明】

【0008】

請求されている主題の実施形態の特徴は、以下の詳細な記載を、図面を参照して読むことで明らかになるが、図面において同様の要素には同様の参照番号が付されている。

【図1】本発明の原理による、汎用プロセッサにおいてAES暗号化および復号化を行う柔軟なアーキテクチャおよび命令の一実施形態を含むシステムのブロック図である。

【図2】図1に示すプロセッサの一実施形態のブロック図である。

【図3】本発明の原理による、AES暗号化および復号化を行う図2に示す実行部の一実施形態を含むブロック図である。

【図4】図3の実行部によるAES暗号化ラウンド命令のフローを示すフローグラフである。

【図5】図3の実行部によるAES暗号化最終ラウンド命令のフローを示すフローグラフである。

【図6】図3の実行部によるAES復号化ラウンド命令のフローを示すフローグラフである。

【図7】図3の実行部によるAES復号化最終ラウンド命令のフローを示すフローグラフである。

【図8】ラウンド鍵を生成し暗号化および復号化を行うのに利用されうる直近のバイトを有するAESラウンド命令の一実施形態を示す。 以下の詳細な記載は、請求されている主題の例示的な実施形態を参照しながら述べるが、当業者には多くの代替例、変形例、および変更例が明らかである。故に、請求されている主題は広義に解釈されることが意図されており、添付請求項で定義が行われることが意図されている。

【発明を実施するための形態】

【0009】

新暗号規格(AES)アルゴリズムは、通常ソフトウェアまたは専用プロセッサで実行されるコンピューティング集約型のアルゴリズムである。故にこの暗号化は、通常、コンピュータに格納されている情報のサブセット(「トップシークレット」として機密扱いされうるような類の情報等)の暗号化に限って利用されている。しかし、コンピュータに格納されている情報を今まで以上に暗号化する必要がでてきている。例えば、携帯コンピュータに格納されている全ての情報が暗号化されれば、携帯コンピュータの盗難に際しても情報保護が可能となる。

【0010】

AESは、128、192、または256ビットのサイズの鍵を用いて、128ビットブロックに施されるブロック暗号である。鍵のサイズに応じて、演算列を多くのラウンド(10、12、または14)について繰り返す。

【0011】

各ラウンドにおける鍵の生成は、ラウンド鍵を格納する暗黙の128ビットレジスタを利用して、その都度(on the fly)(つまり各ラウンド直前に)行われてよい。しかし、暗黙のレジスタの利用により、前の命令結果に対する依存性から、x86レジスタベースのプロセッサの性能が低下する虞がある。

【0012】

例えば、アプリケーションによっては、フロー毎に異なる鍵を有しうるネットワークパケットを処理するためその都度鍵生成することが好都合なものもある。一方で、例えばディスクドライブのコンテンツを暗号化/復号化するのに用いられる単一の鍵に多くの性能が必要とされる類のアプリケーションもある。このように、鍵生成には柔軟性が求められる。本発明の一実施形態は、汎用プロセッサでAES暗号化および復号化を行う柔軟なアーキテクチャおよび命令を提供する。

【0013】

図1は、本発明の原理による、汎用プロセッサにおいてAES暗号化および復号化を行う柔軟なアーキテクチャおよび命令の一実施形態を含むシステム100のブロック図である。システム100は、プロセッサ101、メモリコントローラハブ(MCH)またはグラフィックメモリハブ(GMCH)102、および入出力(I/O)コントローラハブ(ICH)104を含む。MCH102は、プロセッサ101とメモリ108との間の通信を制御するメモリコントローラ106を含む。プロセッサ101とMCH102とは、システムバス116を介して通信する。

【0014】

プロセッサ101は、シングルコアIntel(登録商標)Pentium(登録商標) IV(登録商標)プロセッサ、シングルコアIntel Celeronプロセッサ、Intel(登録商標)XScaleプロセッサ、または、Intel(登録商標)Pentium(登録商標) D、Intel(登録商標)Xeon(登録商標)プロセッサ等のマルチコアプロセッサ、または、Intel(登録商標)Core(登録商標)Duoプロセッサ、または任意の他の種類のプロセッサ等の複数のプロセッサのいずれかであってよい。

【0015】

メモリ108は、ダイナミックRAM(DRAM)、スタティックRAM(SRAM)、シンクロナスDRAM(SDRAM)、ダブルデータレート2(DDR2)RAM、またはランバスDRAM(RDRAM)、または任意の他の種類のメモリであってよい。

【0016】

ICH104は、ディレクトメディアインタフェース(DMI)等の高速チップツーチップインターコネクト114を用いてMCH102に連結されてよい。DMIは、2ギガビット/秒の同時転送レートを2つの単方向レーンによりサポートする。

【0017】

ICH104は、ICH104に連結された少なくとも1つの格納デバイス112との通信を制御する格納I/Oコントローラ110を含みうる。格納デバイスは、例えば、ディスクドライブ、デジタルビデオディスク(DVD)ドライブ、コンパクトディスク(CD)ドライブ、RAID(Redundant Array of Independent Disks)、テープドライブまたは他の格納デバイスであってよい。ICH104は、格納プロトコルインターコネクト118を介して、SAS(Serial Attached Small Computer System Interface)またはSATA (Serial Advanced Technology Attachment)等のシリアル格納プロトコルを用いて格納デバイス112と通信しうる。

【0018】

プロセッサ101は、AES暗号化および復号化演算を行うAES機能103を含む。AES機能103は、メモリ108に格納されている、および/または、格納デバイス112に格納されている情報の暗号化または復号化に利用されうる。

【0019】

図2は、図1に示すプロセッサ101の一実施形態のブロック図である。プロセッサ101は、レベル1(L1)命令キャッシュ202から受信したプロセッサ命令を復号化するフェッチ復号化部206を含む。命令実行に利用されるデータはレジスタファイル208に格納されていてよい。一実施形態においては、レジスタファイル208は、複数の128ビットレジスタを含み、これらは、AES命令が利用するデータを格納する際、AES命令が利用する。

【0020】

一実施形態においては、レジスタファイルは、ストリーミング(シングルインストラクションマルチプルデータ(SIMD))エクステンション(SSE)インストラクションのセットを有するIntel Pentium(登録商標) MMXプロセッサに提供されている128ビットのMMXレジスタに類似した128ビットレジスタ群である。SIMDプロセッサでは、データが128ビットブロックで処理され、一度に1つの128ビットブロックがロードされる。

【0021】

フェッチ復号化部206は、L1命令キャッシュ202からマイクロインストラクションをフェッチして、該マイクロインストラクションを復号化して、マイクロコード読み取り専用メモリ(ROM)214に格納されうるマイクロ演算(μops)と称される簡単な演算に分割する。実行部210は、マイクロ演算をスケジューリングして実行する。示されている実施形態では、実行部210のAES機能103は、AES命令セット用のマイクロ演算を含む。リタイヤ部212は、実行された命令の結果を、レジスタまたはメモリに書き込む。AES命令が利用するラウンド鍵214は、L1データキャッシュ204に格納されており、実行部210にロードされて、マイクロ演算がAES命令セットのAES命令を実行するのに利用されてよい。ラウンド鍵214をデータキャッシュ204に格納することで、例えばシステム100に格納されている暗号化情報にアクセスすべくラウンド鍵を取得しようとする試みのようなサイドチャネル攻撃からラウンド鍵を守る。

【0022】

図3は、本発明の原理によりAES暗号化および復号化を行う図2に示す実行部210の一実施形態を示すブロック図である。図3を、図2との関連で説明する。

【0023】

フェッチ復号化部206がAES命令を復号した後、実行部210はAES命令を、マイクロコードROM214に格納されていてよいAES命令に関するマイクロ演算を行うことで実行する。

【0024】

本発明の一実施形態による柔軟なAES命令セットにより、プログラマーは、処理データ量、メモリ帯域幅および容量に対する性能のトレードオフを行うことができる。

【0025】

アプリケーションによっては、同じ鍵を使い続けるものもある。性能が非常に重要なアプリケーションでは、鍵の鍵スケジュールを1度予め計算して(つまり、ラウンド毎のラウンド鍵)、それをメモリに格納しておくという観点でのトレードオフが行われる。他の種類のアプリケーションには、鍵スケジュールを格納するのに利用されるメモリ量を最小限に抑え、且つ、マルチブロック演算では良好な性能を達成することを望むものもある。この種類のアプリケーションでは、鍵スケジュールを、処理前に多数のブロックについて予め演算しておくことが考えられる。暗号鍵または逆暗号鍵のみを格納して、他のものは適宜性能面の犠牲を鑑みながら生成することによって、メモリフットプリントがさらに低減されうる。

【0026】

x86−型プロセッサでは、AESラウンド鍵演算およびAESスケジューリング演算が利用可能な領域および実行ポート数により、AES命令の性能に制限が加わる。鍵拡張が全てのブロック暗号化で必要となるシステムにおいては、AESスケジューリング演算およびAESラウンド鍵演算を異なる実行ポートに実装することで、性能を向上させる可能性がある。しかし、x−86型プロセッサでは、異なる実行ポートおよびこれら異なるポート制御用の追加領域は提供不可能なことがある。

【0027】

一実施形態では、暗号化ラウンド、復号化ラウンド、暗号化復号化最終ラウンド最終ラウンドを行い、ラウンド暗号鍵またはラウンド復号鍵を算出するのに、それぞれ別個のAES命令を含むAES命令セットが提供される。一実施形態では、AES命令セットが6つのAES命令を含む。各AESラウンド命令は、固有演算コード(opcode)を有する。固定幅ラウンド鍵の一実施形態(例えば128ビット)におけるAES命令セットのAESラウンド命令を、以下の表1に示す。

【表1】

【0028】

AES命令セットは、4つのAESラウンド命令(暗号化、復号化、暗号化最終ラウンド、復号化最終ラウンド)、および2つのAESラウンド鍵命令(次のラウンド鍵および前のラウンド鍵)を含む。AES命令セットのAESラウンド命令は、最終ラウンド以外の全てのラウンドに利用される暗号化および復号化ラウンド演算を行うシングルラウンド演算を含む。例えば、表1のAESENCRYPTRoundのシングルラウンド命令では、入力データが128ビットレジスタ(xmmsrcdst)に格納され、ラウンド鍵が別の128ビットレジスタ(xmm)に格納される。この命令は、128ビットxmmsrcdstレジスタに格納されている入力データ(ソース)に対してAESラウンド演算を行い、128ビットxmmsrcdstレジスタに格納されている入力データを、ラウンド演算実行結果で上書きする。故に、xmmsrcdstは当初は入力データを、そして後には、AESラウンド演算結果を格納する。

【0029】

さらにAES命令セットは、最終復号化ラウンドのAES復号命令および最終暗号化ラウンドのAES暗号命令を含む。例えば、表1のAESENCRYPTLastRoundのシングルラウンド命令では、入力データが128ビットレジスタ(xmmsrcdst)に格納され、ラウンド鍵が別の128ビットレジスタ(xmm)に格納される。この命令は、xmmsrcdstレジスタに格納されている入力データ(ソース)に対してAESラウンド演算を行い、xmmsrcdstレジスタに格納されている入力データを、ラウンド演算実行結果で上書きする。故に、xmmsrcdstは当初は入力データを、そして後には、ラウンド演算結果を格納する。xmmレジスタは、ラウンド演算のラウンド鍵を格納する。

【0030】

別の実施形態では、ラウンドおよび最終ラウンド命令(例えば、AESENCRYPTRoundおよびAESENCRYPTLastRound)が、レジスタファイル304からではなくて、メモリ(m/128)から入力を受け取ってよい(例えば、AESラウンド命令は、AESENCRYPTRound xmmsrcdst m/128であってよい)。

【0031】

AES命令セットの他の2つのAES命令は、鍵のサイズ(つまり、128ビット、192ビット、または256ビット)に応じてAESラウンド用のラウンド鍵を生成する。これらAESラウンド鍵命令の一方は暗号化演算に利用されるラウンド鍵を生成し、他方は復号化演算に利用されるラウンド鍵を生成する。AESNextRoundKey AESPreviousRoundKey命令における直近のフィールドは、鍵のサイズを特定する{128、192、256}。

【0032】

また別の実施形態では、直近のフィールドの代わりに、異なる鍵のサイズが、各々が固有演算コードを有する別個の命令として実装されてよい。この実施形態では、AESラウンド鍵命令の数は、各ラウンド鍵演算(例えばAESNextRoundKey_128、AESNextRoundKey_192、およびAESNextRoundKey_256)について3つの別個の命令を含み、AESPreviousRoundKeyもまた、これらに類似した3つの命令のセットを含む。この実施形態では、命令セット内の命令の総数は、先に述べた実施形態の6つに比して、10となっている。

【0033】

レジスタファイル304は、AES命令セットのAES命令が利用しうる128ビットレジスタを複数有する。128ビットレジスタは、ソースオペランド、ラウンド鍵、およびAES命令の結果を格納しうる。第1ラウンドでは、AES命令は、暗号される128ビットの平文または復号される128ビットの暗号文であってよいソースオペランドを受信する。128ビット、192ビット、または256ビットの鍵の鍵スケジュールを生成する鍵は、レジスタファイル304内の複数の128ビットレジスタ308のいずれかに格納されていてよい。またラウンド鍵も、レジスタファイルの128ビットレジスタ308のいずれかに格納されてよい。全ての命令は、レジスタファイルのレジスタを利用し、さらに、後述するようにメモリから直接入力を得てよい。

【0034】

表1に示すAES命令セットの一実施形態を利用するソースコードの例を、以下の表2に示す。本例においては、多くのブロックに対して同じ鍵を利用する暗号化を行うアプリケーションで性能が最適化されている。このようなアプリケーションの1つに、ディスクに格納する前に全てのデータを暗号化する際に同じ鍵を利用するようなディスクのコンテンツを暗号化するのに単一の鍵を利用するものがある。本例では、AES−128暗号が行われる。

【0035】

鍵のサイズは、128ビット、192ビット、または256ビットであってよい。行われるラウンドの数(n)は、鍵のサイズに応じて1、10、12、または14で、各ラウンド鍵は固定サイズ(128ビット)であってよい。ラウンド値数が10、12、14の場合、AESマイクロ演算は、128ビット、192ビット、または256ビットの鍵サイズに対して標準的なAES暗号化および復号化を行ってよい。

【0036】

多くのブロックについて同じ鍵を利用する場合、各ラウンドのラウンド鍵(鍵スケジュール)は、予め計算されてメモリ(例えばレベル1データキャッシュ204)に格納されているので、各ブロックの暗号化/復号化演算の前に同じ鍵スケジュールを再度計算する必要がない。

【表2】

【0037】

10エレメントを有するアレイ(RK)を利用して、鍵の鍵スケジュールを格納する。AES−128暗号の入力鍵を、RK[0]に格納して、9ラウンド鍵RK[0]−RK[1]を、AES命令セットからAESNextRoundKey命令を読み出すことで予め計算する。AESNextRoundKey命令は、現在のラウンド鍵に基づいて次のラウンドを計算する。鍵スケジュールについて予め計算されたラウンド鍵は、レベル1データキャッシュ204のラウンド鍵214に格納されてよい。

【0038】

本例においては、そのラウンドのラウンド鍵である鍵スケジュールの該当部分(拡張鍵)が直接レジスタファイル304から入力されると、AESラウンドを行うループに入る前に、排他的論理和(XOR)演算を、状態と鍵とに対して行う。各ラウンド1から9においては、AES命令セットからAESENCRYPTRound命令を呼び出して、AESラウンド演算を1ラウンドについて行う。最終ラウンド(ラウンド10)については、AES命令セットからAESENCRYPTLastRound命令を呼び出して、この最終ラウンドにAESラウンド演算を行う。

【0039】

AES命令が暗号化または復号化する情報は、暗号または複号演算を開始する第1のAES命令が発行される前に、レジスタファイル304のソース/宛先レジスタ306へロードされる。ソースレジスタ306の情報の暗号化/復号化に利用される鍵は、レジスタファイル304の1以上の他のレジスタ308に格納されている。128ビット鍵の場合、鍵の全128ビットが、レジスタファイル304の他の128ビットレジスタのいずれかに格納される。128ビットより大きい鍵のサイズに対しては、最上位ビット(128ビットより大きい)を、128ビットレジスタのうち別のものに格納する。

【0040】

表2に示す例においては、レジスタファイル304のレジスタ308のいずれかにロードされる前に、鍵に基づいて各ラウンドのラウンド鍵が予め計算されて、レベル1データキャッシュ204に格納されていてよい。各ラウンドの鍵は、さらに、レジスタファイル304の1以上のレジスタに格納されていてもよく、または、レベル1データキャッシュ204のラウンド鍵214に格納されていてもよい。

【0041】

AESは、128ビットの固定ブロックサイズと、128、192、または256ビットの鍵サイズとを有し、4x4バイトアレイ(つまり16バイト(128ビット固定ブロックサイズ))で動作する(これを「状態」と称する)。AESアルゴリズムは、128ビットの平文ブロックを、128ビットの暗号文ブロックに変換(暗号化)する、または、128ビットの暗号文ブロックを、128ビットの平文ブロックに変換(復号化)し、これらは、10、12、または14の連続したラウンドで行われ、このラウンド数は鍵のサイズに応じている(128、192、または256ビット)。

【0042】

ラウンド毎の暗号化または復号化演算を行う前に、実行部210は、状態および鍵をレジスタファイル304から取得する。各暗号化/復号化ラウンド演算は、読み取り専用メモリ(ROM)214の鍵スケジューラ302に格納されているAES命令のマイクロ演算を利用して行われる。ここに示す実施形態では、状態(128ビットブロックの状態)は、レジスタ306に格納されており、鍵は、レジスタファイル304の他のレジスタ308の1以上に格納されている。AES命令の実行の結果生じる状態をレジスタファイル304のレジスタ306に格納する。状態は、次のAESラウンドまたはAES暗号化または復号化演算の最終結果が利用する中間ラウンドデータであってよい。

【0043】

ここで示す実施形態においては、鍵スケジューラ302は、AESラウンドで利用するラウンド鍵を生成する。鍵スケジューラ302は、マイクロコード演算として実装されてよく、FIPS PUB197で定義される128ビット、196ビット、および256ビット鍵のラウンド鍵を生成する一連の演算を行うマイクロコード演算を含みうる。

【0044】

別の実施形態では、鍵スケジューラは、実行部210のハードウェア状態マシン列として実装されてよい。また別の実施形態では、鍵スケジューラの幾らかの部分がマイクロコードROM214に格納されているマイクロコード演算として実装され、鍵スケジューラの残りの部分が実行部210のハードウェア状態マシン列として実装されてもよい。

【0045】

鍵スケジューラ302は、nバイトの鍵を、bバイトの拡張鍵(鍵スケジュール)に拡張してよく、この拡張鍵の最初のnバイトが元の鍵であってよい。例えば、128ビットの鍵においては、128ビットの鍵を176バイト(つまり、11x16バイト(128ビット))の拡張鍵に拡張して、この最初の16バイトが元の128ビットの鍵であり、ラウンド数は10である。192ビットの鍵の24バイトを、208バイト(13x16バイト)に拡張して、12個の「ラウンド鍵」を、12ラウンドそれぞれに対して1つずつ割り当てるよう提供し、256ビットの鍵の32バイトを、240バイト(15x16バイト)に拡張して、14個の「ラウンド鍵」を、14ラウンドそれぞれに対して1つずつ割り当てるよう提供する。

【0046】

演算コード(opcode)をAES命令で複号する際、1回のAESラウンドのAES命令のフローを制御するのに利用されるパラメータ数は、制御ロジック322に格納されている。パラメータは、演算の種類(暗号または復号)およびそれが最終ラウンドであるかの情報を含む。

【0047】

AESラウンドロジック324は、ブロック状態314、S−ボックス/逆S−ボックス316、行シフト316および逆列混合またはヌル混合(mix inverse, mix columns or null)(「列混合」と称される)320、およびラウンド鍵加算326という段階のマイクロ演算を含みうる。

【0048】

ブロック状態314では、AESラウンドロジック324への128ビットの入力(状態)に、ビットワイズXORを用いて、鍵(ラウンドに関連付けられた拡張鍵の128ビットの部分)を追加して、128ビットの中間値(状態)を生成する。

【0049】

S−ボックス/逆S−ボックス316では、この128ビットの中間値の各バイトを、これも置換ボックスまたは「S−ボックス」と称されるルックアップテーブルから格納・取得されうる別のバイト値で置換してよい。S−ボックスは、幾らかの数の入力ビットmを取り、それらを幾らかの数の出力ビットnに変換して、通常ルックアップテーブルとして実装する。固定ルックアップテーブルが通常利用される。この演算は、ガロア体(GF)(28)において逆関数を利用することで非線形性を生じる。例えば、nビットの出力は、mビットの入力の外側の2ビットを用いてルックアップテーブルで行を選択し、mビットの入力の内側のビットを用いて列を選択することで、見つけることができる。

【0050】

行シフト318ではS−ボックス/逆S−ボックス316の結果に、ビット線形変換を行い、サブバイト段階から受け取った4x4アレイ(128ビット(16バイト)状態)の各行のバイトを、周期的に左にシフトさせる。各バイトをシフトさせる位置の数は、4x4アレイの各行によって異なる。

【0051】

列混合320では、行シフト318の結果に、ビット線形変換を行い、4x4アレイ(状態)の各行を、バイナリガロア体(GF)(28)上の多項式として扱い、その後、c(x)=3x3+x2+x+2を固定多項式として、モジュロx4+1乗算する。最終AESラウンドは、他のAESラウンドと、列混合320が省かれている点で異なっている。

【0052】

列混合段階320の後、ラウンド鍵加算324では、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。

【0053】

例えば、以下のAES命令を発行して、AES復号の1ラウンドを行うことができる。

AESDECRYPTRound xmmsrcdst xmm

【0054】

本例では、128ビットAES暗号化ラウンド演算を、拡張鍵が{RK[1],RK[2],…RK[10]}として表される鍵を利用して行う。ラウンド鍵は、AESDECRYPTRound命令を発行する前に、AESPreviousRoundKey xmmsrc1,2 xmm dst(中間)命令を発行することで生成されうる。ラウンド鍵は、レベル1データキャッシュ204からブロック状態314へ直接ロードされてもよいし、または、先ずレジスタファイル304のレジスタ(xmm)に格納されていて、その後、レジスタからブロック状態314へロードされてもよい。

【0055】

異なる鍵を利用して各ブロックを暗号化/復号化する場合(例えば、データパケットを暗号化/復号化するネットワークインタフェースコントローラ(NIC)の場合)、ラウンド鍵は、以下の表3でAES−128暗号の疑似コードで示すように各ラウンドについて暗号化/復号化を行う前に、その都度計算されてよい。

【表3】

【0056】

本例においては、該ラウンドのラウンド鍵は、鍵スケジュール(拡張鍵)の10ラウンド各々(つまり、ラウンド1−9およびラウンド10(最終ラウンド))に対してラウンド鍵を利用して暗号化を行う前に生成される。

【0057】

シングルAESラウンド命令およびシングルAESラウンド鍵生成命令を含むAES命令セットにより、異なる数のラウンドおよび鍵スケジュールを有するAESの変形例を生成することができる、つまり、FIPS PUB197では定義されていないAESの変形例を生成することができる。故に、AES命令セットのシングルラウンドAES命令は、AES暗号化および復号化を行う際に柔軟性を提供する。

【0058】

AES命令セットが行うラウンド数は固定されていないので、適宜任意の数のラウンドを行うことができる。例えば、ラウンド数は、ハッシュまたはMAC攻撃またはAESへの攻撃に対する新たな規格が導入された場合、将来の暗号化/復号化規格をサポートするよう変更可能である。

【0059】

図4は、図3の実行部210によるAES暗号化ラウンド命令のフローを示すフローグラフである。

【0060】

ブロック400で、実行部210は、AES暗号化ラウンド命令を待つ。AES暗号化ラウンド命令がフェッチ復号化部206により既に復号化されている場合、処理はブロック402に進む。復号化されていない場合は、ブロック400に留まり、AES暗号化ラウンド命令を待つ。

【0061】

ブロック402で、フェッチ復号化部206による命令復号化中、暗号化が必要である旨を制御ロジック322に格納して、暗号化ラウンド実行に利用されるラウンド鍵および128ビットブロック状態(ソース)をレジスタファイル304から実行部210へロードする。処理はブロック404へ進む。

【0062】

ブロック404で、置換演算を128ビットブロック状態に対して、つまり、ブロック406または418の結果に対して、行う。128ビットブロック状態の各バイトを、これも置換ボックスまたは「S−ボックス」と称されるルックアップテーブルから格納・取得されうる別のバイト値で置換してよい。S−ボックスは、幾らかの数の入力ビットmを取り、それらを幾らかの数の出力ビットnに変換して、通常ルックアップテーブルとして実装する。結果を、128ビットブロック状態として格納する。処理はブロック406へ進む。

【0063】

ブロック406で、128ビットブロック状態(4x4アレイ)に、ビット線形変換を行い、4x4アレイの各行のバイトを、周期的に左にシフトさせる。各バイトをシフトさせる位置の数は、4x4アレイの各行によって異なる。処理はブロック408へ進む。

【0064】

ブロック408で、128ビットブロック状態(4x4アレイ)に、ビット線形変換を行い、4x4アレイ(状態)の各行を、GF(28)により多項式として扱い、その後、c(x)=3x3+x2+x+2を固定多項式として、モジュロx4+1乗算する。処理はブロック410へ進む。

【0065】

ブロック410で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック412へ進む。

【0066】

ブロック412で、そのラウンドの暗号化演算の結果(128ビットブロック状態)を、レジスタファイル304のソース/宛先レジスタ302に格納する。これでAES暗号化命令処理が完了する。

【0067】

以下の表4は、表3に示す疑似コードの実行後に、128ビットブロック入力に128ビット鍵を利用してAES−128暗号化を行った結果の一例を示す。

【表4】

【0068】

図5は、図3の実行部210によるAES暗号化最終ラウンド命令のフローを示すフローグラフである。

ブロック500で、実行は、AES暗号化最終ラウンド命令を待つ。もしもAES暗号化最終ラウンド命令がフェッチ復号化部206で既に復号化されている場合、処理はブロック502に進む。復号化されていない場合は、ブロック500に留まり、AESラウンド暗号化命令を待つ。

ブロック502で、ブロック404(図4)との関連で説明したS−ボックスルックアップに類似した方法で最終ラウンドにS−ボックスルックアップを行う。処理はブロック504へ進む。

ブロック504で、ブロック406(図4)で他のラウンドとの関連で説明したような方法で最終ラウンドに行シフト演算を行う。処理はブロック506へ進む。

ブロック506で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック508へ進む。

ブロック508で、暗号化最終ラウンド演算の結果を、レジスタファイル304のソース/宛先レジスタ306に格納する。これでAES命令の処理が完了する。

【0069】

図6は、図3の実行部210によるAES復号化ラウンド命令のフローを示すフローグラフである。

ブロック600で、実行は、AES復号化ラウンド命令を待つ。AES復号化ラウンド命令がフェッチ復号化部206により既に復号化されている場合、処理はブロック602に進む。復号化されていない場合は、ブロック600に留まり、AES復号化ラウンド命令を待つ。

ブロック602で、フェッチ復号化部206による命令復号化中、復号化ラウンドを行う必要がある旨を制御ロジック322に格納して、復号化ラウンド実行に利用されるラウンド鍵およびソース(128ビットブロック状態)をレジスタファイル304から実行部210へロードする。処理はブロック604へ進む。

ブロック604で行う処理は復号化である。AES規格に定義されている逆s−ボックスルックアップを行うことで、置換演算を128ビットブロック状態に対して行う。処理はブロック606へ進む。

ブロック606で、FIPS PUB197で定義されている逆行シフト演算を行う。処理はブロック608へ進む。

ブロック608で、FIPS PUB197で定義されている逆行シフト演算を行う。処理はブロック610へ進む。

ブロック610で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック612へ進む。

ブロック612で、そのラウンドの復号化演算の結果(128ビットブロック状態)を、レジスタファイル304のソース/宛先レジスタ302に格納する。これでAES復号化ラウンド命令処理が完了する。

【0070】

図7は、図3の実行部210によるAES復号化最終ラウンド命令のフローを示すフローグラフである。

ブロック700で、実行部210は、AES復号化最終ラウンド命令を待つ。もしもAES復号化最終ラウンド命令がフェッチ復号化部206で既に復号化されている場合、処理はブロック702に進む。復号化されていない場合は、ブロック700に留まり、AES復号化ラウンド命令を待つ。

ブロック702で、FIPS PUB197で定義されている逆s−ボックスルックアップを行うことで、最終ラウンドの128ビットブロック状態に置換演算を行う。処理はブロック704へ進む。

ブロック704で、FIPS PUB197で定義されているような方法で最終ラウンドに逆行シフト演算を行う。処理はブロック706へ進む。

ブロック706で、拡張鍵からのラウンド鍵、およびそのAESラウンドの行シフト318または列混合320の結果の排他的論理和演算を行う。処理はブロック708へ進む。

ブロック708で、復号化最終ラウンド演算の結果を、レジスタファイル304のソース/宛先レジスタ306に格納する。これでAES復号化最終ラウンド命令の処理が完了する。

【0071】

一実施形態では、図4−7のフローグラフのブロックを、実行部210のハードウェア状態マシン列として実装することができる。別の実施形態では、ブロックの幾らかの部分が読み取り専用メモリ(ROM)214に格納されうるマイクロプログラムとして実装することもできる。ブロックがハードウェア状態マシン列として実装されている実施形態のほうが性能は高いと考えられる。

【0072】

図8は、ラウンド鍵を生成し暗号化および復号化を行うのに利用されうる直近のバイトを有するAESラウンド命令の一実施形態を示す。表1に示すAES命令セットの代わりに単一のAESラウンド命令を提供することで、AES命令セットの機能を行う。単一のAES命令が行う特定の機能は、直近のバイト(key_select_modifier)内のビットに暗号化されている。直近のバイトにより、AESラウンド命令は、各命令が固有演算コードを有する複数の新たな命令を作成する代わりに、新たな特徴を追加するよう拡張される。

【0073】

AESラウンド命令は、記号として以下のように定義されうる。

dest:=aes_key_round(source2,source1),key_select_modifier

【0074】

aes_key_round命令はAES暗号または復号化演算を行うべく、ポート番号に基づいて特定の実行部210に発行される。示されている実施形態では、ポート番号4がAESラウンド命令に指定された実行ポートである。実行部210は、多くのパラレルポート(スーパー−スカラー)に分割される。しかし、全てのポートが等しいわけではない。ポートの中には、大きな整数のマルチプライアー、浮動小数点のマルチプライアーまたはデバイダ等の専用リソースを有するものがある。加算、減算、および排他的論理和等の、これらより簡単で一般的な命令は、多数のポートによりサポートされて最大の性能を発揮する。故に、各命令またはマイクロ演算では、発行制御ロジックがマイクロ演算/命令を発行するポートを決定する。本実施形態では、AES命令は常にポート番号4に対して発行される。しかし、他の実施形態では他のポート番号を利用することができる。

【0075】

図8を参照すると、destはラウンドNに対して128ビットの拡張鍵を格納し、ソース2はラウンドN−1に対して128ビットの拡張鍵を格納し、ソース1はラウンドN−2に対して128ビットの拡張鍵を格納する。key_select_modifierは、現在のラウンド数(N)、演算の方向(暗号化/復号化)、およびAES鍵のサイズを提供するのに利用される8ビットの直近の値である。AES−128では、ソース1は不要であるので無視される。実行部はAES部であり、フラグ(整数または浮動小数点)は利用されない。

【0076】

一実施形態では、直近の値の4つの最下位ビットのビット暗号化は、AES−128に対して1−10のラウンド数、AES−192に対して1−12のラウンド数、およびAES−256に対して2−14のラウンド数、といったラウンド数を示す。AES128および192では、ラウンド数0は無効である、というのも、最初のラウンドが無変更の入力鍵を利用するからである。AES−256では、ラウンド数0と1は無効である、というのも、最初の2つの128ビットラウンドが無変更の256ビット入力鍵を利用するからである。

【0077】

直近のバイトのビット4は演算の方向(暗号化または復号化)を示す(例えば一実施形態では0=暗号、および1=復号、また別の実施形態では1=暗号、および0=復号、というように)。直近のバイトのビット5および6は、AES鍵のサイズを示す。一実施形態では、AES鍵のサイズは以下の表5に示すように定義される。

【表5】

【0078】

別の実施形態では、値11を有するビット[6:5]も、128ビットの鍵のサイズのインジケータである。この実施形態では、ビット[6:5]の全ての値が有効であり、パースされうる。

【0079】

当業者であれば、本発明の実施形態に係る方法を、コンピュータ利用可能な媒体を含むコンピュータプログラムプロダクトに具現化することができることを想到しよう。例えば、コンピュータ利用可能な媒体は、コンピュータ可読プログラムコードが記憶されたコンパクトディスク読み取り専用メモリ(CD ROM)ディスクまたは従来のROMデバイス、またはコンピュータディスク等の読み取り専用メモリデバイスから形成されてよい。

【0080】

本発明の実施形態を特別に示し、実施形態を参照しながら記載してきたが、当業者であれば添付請求項が包括する本発明の実施形態の範囲を逸脱することなく、様々な変更を形態および詳細に対して加えることが可能であることを理解しよう。

【特許請求の範囲】

【請求項1】

AES命令の一連の演算を行う実行部を備える装置であって、

前記一連の演算は、プラグラム可能な数のAESラウンドを行い、

前記演算は前記実行部に、

前記AESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードさせ、

各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成させ、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行わせて、次のAESラウンドの次の入力または前記AES命令の結果を提供させる、装置。

【請求項2】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記実行部は、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵をロードする、請求項1に記載の装置。

【請求項3】

前記一連のAESラウンド演算により、前記実行部は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成し、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行い、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う、請求項2に記載の装置。

【請求項4】

前記AESラウンドの数−1に対して前記一連のAESラウンド演算を行うことで、前記実行部は、

前記AESラウンドの前記入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成し、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行い、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行い、

前記置換演算の結果に、前記中間値の列同士を混合させるビット線形変換を行う、請求項1に記載の装置。

【請求項5】

最終ラウンドに前記一連のAESラウンド演算を行うことで、前記実行部は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成し、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行い、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う、請求項4に記載の装置。

【請求項6】

前記結果は暗号化された値である、請求項1に記載の装置。

【請求項7】

前記結果は復号化された値である、請求項1に記載の装置。

【請求項8】

第1のAESラウンドの鍵および入力がレジスタファイルに格納されている、請求項1に記載の装置。

【請求項9】

前記レジスタファイルは複数の128ビットレジスタを含む、請求項8に記載の装置。

【請求項10】

AES命令のプログラム可能なAESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードして、各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成する段階と、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行い、次のAESラウンドの次の入力または前記AES命令の結果を提供する段階と、を備える方法。

【請求項11】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵をロードする段階を備える、請求項10に記載の方法。

【請求項12】

前記一連のAESラウンド演算を行う段階は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成する段階と、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行う段階と、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う段階と、を有する、請求項11に記載の方法。

【請求項13】

前記ラウンドの数1に対して前記一連のAESラウンド演算を行う段階は、

前記AESラウンドの前記入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成する段階と、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行う段階と、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う段階と、

前記置換演算の結果に、前記中間値の列同士を混合させるビット線形変換を行う段階と、を有する、請求項10に記載の方法。

【請求項14】

最終AESラウンドに前記一連のAESラウンド演算を行う段階は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成する段階と、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行う段階と、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う段階と、を有する、請求項13に記載の方法。

【請求項15】

前記結果は暗号化された値である、請求項10に記載の方法。

【請求項16】

前記結果は復号化された値である、請求項10に記載の方法。

【請求項17】

第1のAESラウンドの鍵および入力がレジスタファイルに格納されている、請求項10に記載の方法。

【請求項18】

前記レジスタファイルは複数の128ビットレジスタを含む、請求項17に記載の方法。

【請求項19】

関連情報を有する機械アクセス可能な媒体を含む物品であって、前記情報はアクセスされると機械に、

AES命令のプログラム可能なAESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードさせ、各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成させ、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行わせて、次のAESラウンドの次の入力または前記AES命令の結果を提供させる、物品。

【請求項20】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵がロードされる、請求項19に記載の物品。

【請求項21】

データおよび命令を格納するダイナミックランダムアクセスメモリと、

前記メモリに連結されて前記命令を実行するプロセッサと、を備えるシステムであって、

前記プロセッサは、

AES命令の一連の演算を行う実行部を備え、

前記一連の演算は、プラグラム可能な数のAESラウンドを行い、

前記演算は前記実行部に、

前記AESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードさせ、

各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成させ、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行わせて、次のAESラウンドの次の入力または前記AES命令の結果を提供させる、システム。

【請求項22】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記実行部は、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵をロードする、請求項21に記載のシステム。

【請求項1】

AES命令の一連の演算を行う実行部を備える装置であって、

前記一連の演算は、プラグラム可能な数のAESラウンドを行い、

前記演算は前記実行部に、

前記AESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードさせ、

各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成させ、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行わせて、次のAESラウンドの次の入力または前記AES命令の結果を提供させる、装置。

【請求項2】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記実行部は、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵をロードする、請求項1に記載の装置。

【請求項3】

前記一連のAESラウンド演算により、前記実行部は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成し、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行い、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う、請求項2に記載の装置。

【請求項4】

前記AESラウンドの数−1に対して前記一連のAESラウンド演算を行うことで、前記実行部は、

前記AESラウンドの前記入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成し、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行い、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行い、

前記置換演算の結果に、前記中間値の列同士を混合させるビット線形変換を行う、請求項1に記載の装置。

【請求項5】

最終ラウンドに前記一連のAESラウンド演算を行うことで、前記実行部は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成し、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行い、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う、請求項4に記載の装置。

【請求項6】

前記結果は暗号化された値である、請求項1に記載の装置。

【請求項7】

前記結果は復号化された値である、請求項1に記載の装置。

【請求項8】

第1のAESラウンドの鍵および入力がレジスタファイルに格納されている、請求項1に記載の装置。

【請求項9】

前記レジスタファイルは複数の128ビットレジスタを含む、請求項8に記載の装置。

【請求項10】

AES命令のプログラム可能なAESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードして、各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成する段階と、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行い、次のAESラウンドの次の入力または前記AES命令の結果を提供する段階と、を備える方法。

【請求項11】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵をロードする段階を備える、請求項10に記載の方法。

【請求項12】

前記一連のAESラウンド演算を行う段階は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成する段階と、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行う段階と、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う段階と、を有する、請求項11に記載の方法。

【請求項13】

前記ラウンドの数1に対して前記一連のAESラウンド演算を行う段階は、

前記AESラウンドの前記入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成する段階と、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行う段階と、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う段階と、

前記置換演算の結果に、前記中間値の列同士を混合させるビット線形変換を行う段階と、を有する、請求項10に記載の方法。

【請求項14】

最終AESラウンドに前記一連のAESラウンド演算を行う段階は、

前記ラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して排他的論理和(XOR)演算を行って、中間値を生成する段階と、

ルックアップテーブルに格納されている値に基づいて、前記中間値の各バイトに対して置換演算を行う段階と、

前記置換演算の結果に、前記中間値の行をシフトさせるビット線形変換を行う段階と、を有する、請求項13に記載の方法。

【請求項15】

前記結果は暗号化された値である、請求項10に記載の方法。

【請求項16】

前記結果は復号化された値である、請求項10に記載の方法。

【請求項17】

第1のAESラウンドの鍵および入力がレジスタファイルに格納されている、請求項10に記載の方法。

【請求項18】

前記レジスタファイルは複数の128ビットレジスタを含む、請求項17に記載の方法。

【請求項19】

関連情報を有する機械アクセス可能な媒体を含む物品であって、前記情報はアクセスされると機械に、

AES命令のプログラム可能なAESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードさせ、各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成させ、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行わせて、次のAESラウンドの次の入力または前記AES命令の結果を提供させる、物品。

【請求項20】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵がロードされる、請求項19に記載の物品。

【請求項21】

データおよび命令を格納するダイナミックランダムアクセスメモリと、

前記メモリに連結されて前記命令を実行するプロセッサと、を備えるシステムであって、

前記プロセッサは、

AES命令の一連の演算を行う実行部を備え、

前記一連の演算は、プラグラム可能な数のAESラウンドを行い、

前記演算は前記実行部に、

前記AESラウンドの数が1より大きい場合、鍵を一時的鍵レジスタにロードさせ、

各AESラウンドを行う前に、前記鍵に基づいて前記AESラウンドのラウンド鍵を生成させ、

各AESラウンドにおいて、前記AESラウンドの入力および前記AESラウンドの前記ラウンド鍵に対して一連のAESラウンド演算を行わせて、次のAESラウンドの次の入力または前記AES命令の結果を提供させる、システム。

【請求項22】

前記AESラウンドの数が1に等しい場合、前記一連のAESラウンド演算を行う前に、前記実行部は、前記鍵に基づいて前記AESラウンドについて予め計算されたラウンド鍵をロードする、請求項21に記載のシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−57946(P2013−57946A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−226077(P2012−226077)

【出願日】平成24年10月11日(2012.10.11)

【分割の表示】特願2009−552935(P2009−552935)の分割

【原出願日】平成20年3月25日(2008.3.25)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2012−226077(P2012−226077)

【出願日】平成24年10月11日(2012.10.11)

【分割の表示】特願2009−552935(P2009−552935)の分割

【原出願日】平成20年3月25日(2008.3.25)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

[ Back to top ]