演算処理装置及び演算器同時実行制御方法

【課題】異なるプロセッサ間で同時に演算器が起動する電圧変動最悪パターンを改善すること。

【解決手段】本発明にかかる演算処理装置100は、同時に実行可能な複数の演算器を有する複数の処理回路120A〜120Nと、各処理回路で実行中の演算器の総数を集計する制御回路110と、を備え、複数の処理回路120A〜120Nのそれぞれは、制御回路110が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

【解決手段】本発明にかかる演算処理装置100は、同時に実行可能な複数の演算器を有する複数の処理回路120A〜120Nと、各処理回路で実行中の演算器の総数を集計する制御回路110と、を備え、複数の処理回路120A〜120Nのそれぞれは、制御回路110が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、演算処理装置及び演算器同時実行制御方法に関し、特に、複数の演算器を有する複数のプロセッサにおいて同時実行される演算器数を制御するための演算処理装置及び演算器同時実行制御方法に関する。

【背景技術】

【0002】

特許文献1には、低消費電力化と高速化が可能なマイクロプロセッサに関する技術が開示されている。特許文献1にかかるマイクロプロセッサは、各演算回路を操作する命令を先行検出する検出手段と、この検出手段により検出された命令に対応した演算回路を1つ以上演算実行に先立って活性化し、演算終了後に、活性化された演算回路を不活性化する手段とを有する。そして、当該マイクロプロセッサは、n個(n≧2)の命令を同時に読み出してデコードし、n個の演算回路を用いて同時に演算を実行する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平10−207859号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、特許文献1に代表される関連技術にかかるマイクロプロセッサを複数搭載した演算処理装置も開発されるようになった。このような演算処理装置では、その処理性能を高めるために、複数の演算器(加算器・乗算器など)を多数実装して、高速なギガヘルツ周波数でこれら演算器を同時に動作させるようにして処理を行っている。ギガヘルツ動作を可能にするためには、高速回路技術とともに回路に電源を供給する側の電源の耐ノイズ設計が重要になる。

【0005】

上述した演算処理装置では、電圧変動が発生すると回路のディレイ劣化や誤動作を発生させるため、高速化の妨げになってきている。LSI(Large Scale Integration)チップ内の電圧変動は、(1)回路動作による高周波ノイズと(2)電源抵抗による直流ドロップに大別される。特に(1)が支配的である。そこで、一般的な高周波ノイズの低減策にバイパスコンデンサ(パスコン)をLSIチップに搭載する方法がある。しかし、近年、1チップに複数のプロセッサを実装する傾向にあり、複数プロセッサが同時に起動する場合、電圧変動が大きくなる傾向にある。

【0006】

図8は、関連技術にかかる命令発行回路を複数搭載した演算処理装置900の一例を示す図である。演算処理装置900は、同等の構成を有するプロセッサ94A〜94Nを備える。プロセッサ94Aは、命令発行回路95Aと、複数の演算器である加算器6A、加算器7A、乗算器8A及び乗算器9Aと、汎用レジスタ10Aと、閾値レジスタ12Aとを備える。以降、同様に、プロセッサ94Nは、命令発行回路95Nと、複数の演算器である加算器6N、加算器7N、乗算器8N及び乗算器9Nと、汎用レジスタ10Nと、閾値レジスタ12Nとを備える。ここでは、代表してプロセッサ94Aの内部の構成及び動作について説明する。

【0007】

命令発行回路95Aは、加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれを起動させる場合、加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれに対して、実行指示103A、104A、105A及び106Aを発行する。加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれは、各実行命令に応じて独立して動作し、その処理結果を汎用レジスタ10Aに格納する。閾値レジスタ12Aには、プロセッサ94A内で同時実行可能な演算器の数の上限値が格納されている。命令発行回路95Aは、実行指示103A、104A、105A及び106Aを発行する際に、発行済みの実行指示の数と閾値レジスタ12Aに格納された上限値とを比較し、上限値を超える場合は実行指示の発行を抑制し、プロセッサ94A内で同時に動作させる演算器の数を制御する機構を持っている。

【0008】

しかしながら、演算処理装置900には、プロセッサ94A〜94Nの全体で動作可能な演算器数を制限する機構は持っていなかった。そのため、プロセッサごとに独立して制御をせざるを得ず、動作制限対処範囲が局所的になる。よって、プロセッサ単独では、動作制限を行うことができたとしても、演算処理装置900全体としては性能が落ちるケースも発生してしまうという問題点があった。例えば、あるプロセッサ内で同時に実行される演算器数が上限値未満であり、さらに演算器を同時に実行させる余裕があったとしても、特定のプロセッサ内で同時に実行される演算器数が上限値を超える可能性がある場合には、当該特定のプロセッサにおける演算器の追加の実行を抑制せざるを得ない。この場合、演算処理装置900の最大限の性能を発揮することができない。

【0009】

本発明は、上述した問題点を考慮してなされたものであり、異なるプロセッサ間で同時に演算器が起動する電圧変動最悪パターンを改善するための演算処理装置及び演算器同時実行制御方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の第1の態様にかかる演算処理装置は、

同時に実行可能な複数の演算器を有する複数の処理回路と、

各処理回路で実行中の演算器の総数を集計する制御回路と、を備え、

前記複数の処理回路のそれぞれは、前記制御回路が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

【0011】

本発明の第2の態様にかかる演算器同時実行制御方法は、

同時に実行可能な複数の演算器を有する複数の処理回路を制御する制御回路が、各処理回路で実行中の演算器の総数を集計し、

前記複数の処理回路のそれぞれが、前記集計された集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

【発明の効果】

【0012】

本発明により、異なるプロセッサ間で同時に演算器が起動する電圧変動最悪パターンを改善するための演算処理装置及び演算器同時実行制御方法を提供することができる。

【図面の簡単な説明】

【0013】

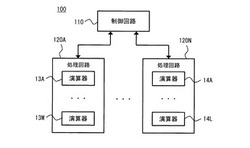

【図1】本発明の実施の形態1にかかる演算処理装置の構成を示すブロック図である。

【図2】本発明の実施の形態1にかかる演算器同時実行制御処理の流れを示すフローチャートである。

【図3】本発明の実施の形態2にかかる演算処理装置の構成を示すブロック図である。

【図4】本発明の実施の形態2にかかる演算器同時実行制御処理の例を示すタイムチャートである。

【図5】本発明の実施の形態3にかかる演算処理装置の構成を示すブロック図である。

【図6】本発明の実施の形態3にかかる汎用レジスタとデータ分散値レジスタとの関係を示す図である。

【図7】本発明の実施の形態3にかかる演算器同時実行制御処理の例を示すタイムチャートである。

【図8】関連技術にかかる演算処理装置の構成を示すブロック図である。

【発明を実施するための形態】

【0014】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。各図面において、同一要素には同一の符号が付されており、説明の明確化のため、必要に応じて重複説明は省略する。

【0015】

<発明の実施の形態1>

図1は、本発明の実施の形態1にかかる演算処理装置100の構成を示すブロック図である。演算処理装置100は、複数の演算器を有する複数の処理回路において同時実行される演算器数を制御するものである。演算処理装置100は、制御回路110と、処理回路120A〜120Nとを備える。尚、処理回路120A〜120Nは、複数個であればよい。処理回路120Aは、演算器13A〜13Mを有する。同様に、処理回路120Nは、演算器14A〜14Lを有する。処理回路120A〜120Nのそれぞれは、自己の有する複数の演算器を同時に実行することが可能である。尚、処理回路120A〜120Nにおける演算器の数は、複数個であればよい。

【0016】

図2は、本発明の実施の形態1にかかる演算器同時実行制御処理の流れを示すフローチャートである。まず、制御回路110は、各処理回路で実行中の演算器の総数を集計する(ステップS11)。次に、処理回路120A〜120Nのそれぞれは、制御回路110が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する(ステップS12)。

【0017】

このように、本発明の実施の形態1では、異なる処理装置間で同時に実行される演算器数を考慮して自己の演算器の実行可否を決定することができる。そのため、異なる処理装置間で同時に演算器が起動する電圧変動最悪パターンを改善することができる。

【0018】

<発明の実施の形態2>

図3は、本発明の実施の形態2にかかる演算処理装置200の構成を示すブロック図である。演算処理装置200は、制御回路1と、プロセッサ4A〜4Nとを備える。プロセッサ4A〜4Nは、複数の演算器を有し、これらの同時実行を行う。また、制御回路1は、プロセッサ4A〜4N内の複数の演算器の同時実行数を全体として制御する。

【0019】

制御回路1は、閾値レジスタ2と、比較報告回路3とを備える。閾値レジスタ2は、プロセッサ4A〜4N全てにおいて同時に実行可能な演算器の数の上限値を記憶する。

比較報告回路3は、プロセッサ4A〜4Nのそれぞれから実行指示同時発行数100A〜100Nを受け付ける。そして、比較報告回路3は、各プロセッサから通知された実行指示同時発行数100A〜100Nを集計してその総数を算出する。続いて、比較報告回路3は、当該総数と上限値との差分値(実行可能演算器残数)を各プロセッサへ通知する。ここで、実行指示同時発行数100A〜100Nは、各プロセッサ内で同時に実行中の演算器の数である同時実行演算器数である。また、実行可能演算器残数は、演算処理装置200内の全プロセッサで実行可能な演算器の残数である。または、実行可能演算器残数は、演算処理装置200内の全プロセッサで実行可能な演算器の余裕数と言い換えることもできる。

【0020】

プロセッサ4Aは、命令発行回路5A、加算器6A、加算器7A、乗算器8A、乗算器9A及び汎用レジスタ10Aを備える。汎用レジスタ10Aには、加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれによる演算結果が格納される。命令発行回路5Aは、プログラムに従い加算器6A、加算器7A、乗算器8A及び乗算器9Aについて実行の開始を指示するための実行指示103A、104A、105A及び106Aをそれぞれに対して発行する。特に、命令発行回路5Aは、同時に動作可能な加算及び乗算の演算があれば、該当する演算器に対して実行指示を行う。具体的には、加算器6Aの実行が可能なら汎用レジスタ10Aからオペランドデータを読み出して加算器6Aにデータを送付し同時に実行指示103Aを送付する。同様に、乗算器9Aの実行が可能なら汎用レジスタ10Aからオペランドデータを読み出して乗算器9Aにデータを送付し同時に実行指示106Aを送付する。

【0021】

また、命令発行回路5Aは、発行した実行指示の数を実行指示同時発行数として制御回路1へ通知する。そして、命令発行回路5Aは、制御回路1から実行可能演算器残数を受け付ける。そして、命令発行回路5Aは、演算器の起動を行う場合、実行可能演算器残数の値を見ながら起動の判断を行っている。他のプロセッサもプロセッサ4Aと同様の動作を行う。つまり、プロセッサ4A〜4Nのそれぞれは、実行可能演算器残数に応じて未実行の演算器を実行するか否かを決定する。そして、複数の処理回路のそれぞれは、実行すると決定した演算器の数が実行可能演算器残数を超える場合、当該超える分の演算器の実行の開始を保留する。これにより、演算処理装置200全体としての性能の最適化を図ることができる。

【0022】

尚、プロセッサ4Nは他のプロセッサの一例である。プロセッサ4Nは、例えば、命令発行回路5N、加算器6N、加算器7N、乗算器8N、乗算器9N及び汎用レジスタ10Nを備える。尚、プロセッサ4A〜4Nが備える演算器の種類及び数は、上述したものに限定されない。

【0023】

図4は、本発明の実施の形態2にかかる演算器同時実行制御処理の例を示すタイムチャートである。タイミングt1において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行する。同様に、命令発行回路5Aは、乗算器8Aを起動するために実行指示105Aを発行する。このとき、命令発行回路5Aは、タイミングt1の実行指示同時発行数100Aを"2"として比較報告回路3へ通知する。

【0024】

同様に、タイミングt1において、命令発行回路5Nは、加算器6Nを起動するために実行指示103Nを発行する。このとき、命令発行回路5Nは、タイミングt1の実行指示同時発行数100Nを"1"として比較報告回路3へ通知する。

【0025】

タイミングt1において、比較報告回路3は、全プロセッサからの実行指示同時発行数100A〜100Nを集計して"3"の値を算出する。そして、制御回路1は、閾値レジスタ2に格納された上限値"5"と上記集計結果"3"との比較を行い、その差分値"2"を算出する。その後、比較報告回路3は、差分値"2"を実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0026】

タイミングt2において、プロセッサ4Aは、再度、加算器6A及び乗算器8Aの起動を試みる。このとき、実行指示同時発行数100Aがタイミングt1と同数"2"となるため、そのまま実行指示103A及び実行指示105Aを発行し、実行指示同時発行数100A"2"を比較報告回路3へ通知する。また、プロセッサ4Nは、加算器6Nに加え、加算器7Nの起動を試みる。このとき、実行指示同時発行数100Nが直前のタイミングt1と比べて"1"大きい"2"となる。但し、タイミングt1で通知された実行可能演算器余裕数101Nが"2"であるため、命令発行回路5Nは、そのまま実行指示103N及び実行指示104Nを発行し、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0027】

タイミングt2において、比較報告回路3は、全プロセッサからの実行指示同時発行数100A〜100Nを集計して"4"の値を算出し、上限値"5"との差分値"1"を算出する。その後、比較報告回路3は、差分値"1"を実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0028】

タイミングt3において、プロセッサ4Aは、加算器6A及び乗算器8Aに加え、加算器7Aの起動を試みる。このとき、実行指示同時発行数100Aが直前のタイミングt2と比べて"1"大きい"3"となる。但し、タイミングt2で通知された実行可能演算器余裕数101Aが"1"であるため、命令発行回路5Aは、そのまま実行指示103A、104A及び105Aを発行し、実行指示同時発行数100A"3"を比較報告回路3へ通知する。また、プロセッサ4Nは、再度、加算器6N及び加算器7Nの起動を試みる。このとき、実行指示同時発行数100Nがタイミングt2と同数"2"となるため、そのまま実行指示103N及び104Nを発行し、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0029】

タイミングt3において、比較報告回路3は、全プロセッサからの実行指示同時発行数100A〜100Nを集計して"5"の値を算出し、上限値"5"との差分値"0"を算出する。その後、比較報告回路3は、差分値"0"を実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0030】

タイミングt4において、プロセッサ4Aは、再度、加算器6A、加算器7A及び乗算器8Aの起動を試みる。このとき、実行指示同時発行数100Aがタイミングt3と同数"3"となるため、そのまま実行指示103A、104A及び105Aを発行し、実行指示同時発行数100A"3"を比較報告回路3へ通知する。

【0031】

また、プロセッサ4Nは、加算器6N及び加算器7Nに加え、乗算器8Nの起動を試みる。このとき、実行指示同時発行数100Nが直前のタイミングt3と比べて"1"大きい"3"となってしまう。タイミングt3で通知された実行可能演算器余裕数101Nが"0"であるため、命令発行回路5Nは、直前に発行済みの実行指示103N及び104Nについては継続して発行しつつ、実行指示105Nについては発行を抑制する。つまり、未実行の演算器である乗算器8Nについての実行を保留し、乗算器8Nの起動を遅らせている。もし、このときに実行指示105Nまで発行してしまうと、全プロセッサの演算器の同時実行数の上限値"5"を超えてしまうためである。そして、命令発行回路5Nは、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0032】

タイミングt4において、比較報告回路3は、タイミングt3と同様に、差分値"0"を算出し、実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0033】

タイミングt5において、プロセッサ4Aは、タイミングt3及びt4と同様に動作する。そして、プロセッサ4Nは、加算器6N及び乗算器8Nの起動を試みる。このとき、加算器7Nが演算終了により起動不要となり、乗算器8Nの起動が可能となる。すなわち、実行指示同時発行数100Nがタイミングt4と同数"2"となるため、プロセッサ4Nは、実行指示103N及び105Nを発行し、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0034】

タイミングt5において、比較報告回路3は、タイミングt4と同様に、差分値"0"を算出し、実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0035】

以上説明したように本発明においては、以下に記載するような効果を奏する。それは、全プロセッサにおいて同時に実行可能な演算器の数の上限値を予め保持する閾値レジスタと複数のプロセッサ間における同時に動作させる演算器の動作状態を把握する機構を用意することで、把握した結果から演算器の起動をずらして動作させることが可能となり、同時に動作開始する演算器を減少させて電圧変動を低減できることである。

【0036】

また、制御回路1は、実行可能演算器残数を集中管理して各プロセッサに配布している。これにより、各プロセッサは、通知された実行可能演算器残数を基に自律的に未実行の演算器の実行可否を判定でき、処理の高速化を図ることができる。

【0037】

具体的には、制御回路1は、各プロセッサで動作させる演算器数を把握できる信号を各プロセッサから受け付けて集計することで、総数を把握する。そして、各プロセッサは、未実行の演算器を実行させると、全演算器の動作数が閾値を超えてしまう場合には、当該演算器の起動を遅らせる。そして、全演算器の動作数が閾値を下回った場合に、当該起動を遅らせた演算器を起動させる。これにより、電圧変動が急峻になることを防げる。

【0038】

さらに、制御回路1は、演算処理装置200全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部のプログラム等から受け付け、当該受け付けた演算器の数を上限値として閾値レジスタ2を更新することが望ましい。プログラムで指定される演算器の動作数に依存して電圧値が変わるが、閾値レジスタを電圧変動の最大許容値に設定することで大きく性能を落とさない処理が可能となる。

【0039】

また、複数のプロセッサのうち一のプロセッサは、未実行の演算器を実行すると決定した場合、その旨を他のプロセッサに対して通知するとさらに良い。これにより、他のプロセッサが当該通知により自己の未実行の演算器の実行を抑制することで、演算処理装置200全体の性能を維持することができる。

【0040】

さらに、複数のプロセッサのうち一のプロセッサは、未実行の演算器を実行すると決定した場合、差分値から当該実行すると決定された演算器の数を減じた値を新たな差分値として他の処理回路に対して通知するようにしてもよい。これにより、各プロセッサは、再度、比較報告回路3から実行可能演算器残数101A等の通知を待つことなく、自己の未実行の演算器の実行を抑制することができる。

【0041】

<発明の実施の形態3>

本発明の他の実施形態では、その基本的構成は上記の通りであるが、電圧変動の低減についてさらに工夫している。図5は、本発明の実施の形態3にかかる演算処理装置300の構成を示すブロック図である。演算処理装置300は、制御回路1と、プロセッサ4A〜4Nとを備える。尚、制御回路1は、実施の形態2の図3と同等であるため、詳細な説明を省略する。

【0042】

実施の形態3に係る命令発行回路5Aは、実施の形態2と比べて、閾値レジスタ12Aと、データ分散値レジスタ11Aをさらに備える。同様に、命令発行回路5Nは、閾値レジスタ12Nと、データ分散値レジスタ11Nをさらに備える。命令発行回路5A〜5Nのそれぞれは、各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して未実行の演算器を実行するか否かを決定する。尚、以下では、説明のため命令発行回路5Aについて記載するが、命令発行回路5A以外についても同様である。

【0043】

図6は、本発明の実施の形態3にかかる汎用レジスタ10Aとデータ分散値レジスタ11Aとの関係を示す図である。汎用レジスタ10Aには、1セット当たり32要素のデータを、8セット分(セット0〜7)格納されていることを示す。また、データ分散値レジスタ11Aには、セット内のデータにおけるデータのばらつき指標を示す値である分布値が各セットに対応して格納されていることを示す。

【0044】

図5に戻って説明する。プロセッサ4Aの加算器6A、加算器7A、乗算器8A及び乗算器9Aは、例えば、1回の演算で、汎用レジスタ10Aから32要素を2セット分読み出して演算を行うものとする。そして、各演算器は、32要素(1セット分)の演算を行った演算結果を汎用レジスタ10Aに書き込む。併せて、各演算器は、1セット単位に、分布値を算出して、汎用レジスタ10Aのセットに対応付けてデータ分散値レジスタ11Aに格納する。

【0045】

ここで、分布値は、データ1つ当たりどの程度ばらついているかを示す値である。分布値に統計学上の分散値を用いる場合には、以下の式(1)により算出することができる。

分散値V={Σ(Xi−Xn)2}/(n−1) ・・・(1)

ここで、nは、1セット当たりの要素数、Xnは平均値、Xiは、各要素の値、つまり、汎用レジスタ10Aに格納される演算結果を示す。

【0046】

閾値レジスタ12Aは、分散値の閾値を予め記憶する。そして、命令発行回路5Aは、プログラムに従いある演算器に対して実行指示を行う場合、直前に動作していた演算器の演算結果に対応する分散値をデータ分散値レジスタ11Aから読み出し、閾値レジスタ12Aに格納された閾値と比較する。このとき、実行可能演算器残数101Aが"0"であっても分散値が閾値以内である場合、命令発行回路5Aは、予定通り演算器へ実行指示を発行する。分散値が小さい場合には、電流変動が小さいと考えられるからである。または、実行可能演算器残数101Aが"1"以上であっても分散値が閾値以上である場合に、命令発行回路5Aは、演算器へ実行指示を保留しても構わない。例え、同時実行数が許容範囲だとしても、電流変動が大きい可能性があるためである。このように、実施の形態3では、データの変動分を考慮して実行指示を出すことで大きく性能を落とさない処理が可能となる。

【0047】

また、各演算器における分布値の算出時間を短縮化するために、以下の式(2)により算出される分布値を用いることもできる。

分布値V'={Σ(Xi−Xn)2} ・・・(2)

式(2)は、式(1)から要素数に応じた除算を省略したものである。つまり、分布値V'は、分散値Vの除算前の値であり、いわば演算結果から分散値を算出する過程で求まる値である。この場合、閾値レジスタ12Aには、各演算器における演算対象の要素数に応じた分布値の閾値を予め格納しておけばよい。分布値V'は、分散値Vと違い、合算する個数(最大32要素)によっても異なるためである。

【0048】

そのため、各演算器は、除算を省略して分布値を算出してデータ分散値レジスタ11Aに格納できる。その後、命令発行回路5Aは、演算器の演算対象の要素数に対応する閾値を閾値レジスタ12Aから読み出して、データ分散値レジスタ11Aから読み出した分布値との間で、同様に比較することができる。これにより、各演算器は、除算動作不要となり分布値V'の算出時間を短縮することができる。

【0049】

図7は、本発明の実施の形態3にかかる演算器同時実行制御処理の例を示すタイムチャートである。図7では、演算処理する要素数を"4"としている。尚、実際には、実行指示から結果が得られるまで数サイクルを必要とするが、ここでは、説明の便宜のため、演算結果とデータ分散値はそのタイミングで生成されると仮定したタイムチャートとしている。

【0050】

ここで、データ分散値(分布値)の生成について説明する。タイミングt1において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット0の演算結果を汎用レジスタ10Aに、セット0の分布値A1をデータ分散値レジスタ11Aに格納する。次に、タイミングt2において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット1の演算結果を汎用レジスタ10Aに、セット0及び1の分布値A2をデータ分散値レジスタ11Aに格納する。そして、タイミングt3において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット2の演算結果を汎用レジスタ10Aに、セット0〜2の分布値A3をデータ分散値レジスタ11Aに格納する。さらに、タイミングt4において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット3の演算結果を汎用レジスタ10Aに、セット0〜3の分布値A4をデータ分散値レジスタ11Aに格納する。また、乗算器8Aもタイミングt1〜t4において、セット0〜3の演算結果と、セット0〜3の分布値C1〜C4とをそれぞれ汎用レジスタ10A及びデータ分散値レジスタ11Aに格納する。このようにデータ分散値は、処理する要素を前タイミング結果に足しこみながら生成していく。

【0051】

一方、演算器を起動する制御について説明する。タイミングt2において、プロセッサ4Aは、加算器6Aと乗算器8Aが動作しているので、実行指示同時発行数100A"2"を比較報告回路3に通知する。同時に、プロセッサ4Nは、加算器6Nが動作しているので、実行指示同時発行数100N"1"を比較報告回路3に通知する。

【0052】

タイミングt5において、命令発行回路5Aは、直前のタイミングt4で比較報告回路3から通知された実行可能演算器残数101A"0"を参照して、演算器の起動を行う。その際に、命令発行回路5Aは、タイミングt4で演算が完了した加算器6Aの演算結果に対応する分布値A4及び乗算器8Aの演算結果に対応する分布値C4を、データ分散値レジスタ11Aから参照しつつ、乗算器9Aの起動判断を行う。ここでは、分布値"A4"と分布値"C4"の値が閾値より小さいものとする。この場合、命令発行回路5Aは、乗算器9Aが実行可能と判断し、タイミングt5で実行指示106Aを発行する。また、タイミングt5において仮に分布値"A4"と分布値"C4"の値のいずれかが閾値を上回っていた場合、実行可能演算器残数101Aに余裕があったとしても、命令発行回路5Aは、乗算器9Aの実行指示の発行を保留する。

【0053】

このように、本実施の形態3では、読み出すデータの分散値を参照しながら起動判断を行っているので、データの変動分を考慮して実行指示を出すことができ、演算処理装置300全体の性能を大きく落とさない処理が可能となる。

【0054】

<その他の発明の実施の形態>

尚、本発明の実施の形態2は、電圧変動に対応した処理装置において、同時に動作させる演算器の動作状態を把握し、把握した結果から演算器起動をずらして動作させることにより、同時に動作開始する演算器を減少させて電圧変動を低減させることを特徴としている。

【0055】

具体的には、設定値を可変にできる閾値レジスタを用意しておいて、動作させる演算器数を把握できる信号を各プロセッサで把握しながら全演算器の動作数が閾値を超えた場合、電圧変動が急峻にならないように閾値を超えた演算器の動作を遅らせるように動作させる。プログラムで指定される演算器の動作数に依存して電圧値が変わるが、閾値レジスタを電圧変動の最大許容値に設定することで大きく性能を落とさない処理が可能となる。

【0056】

そして、演算器動作数の他にデータに依存しても電圧変動値が変わるので、演算器で処理するデータのばらつき値として分散値を参照しながら動作させる演算器数を可変にできる処理装置も提供する。具体的には、汎用レジスタにデータを書き込む際に、統計学で使用されている分散値を回路で求めながら最後の算出結果を汎用レジスタ分散値レジスタに保持する。演算器を動作させる場合には、演算器の動作数に加えて汎用レジスタ分散値も参考にしながら電圧変動が急峻にならないように演算器の動作を遅らせるように動作させる。

【0057】

このように、本発明の実施の形態2では、設定値を可変にできる閾値レジスタを電圧変動の最大許容値に設定しながら演算器の動作状態を把握して処理を行うようにしているので、大きく性能を落とすことなく電圧変動に対応した動作が可能となる。

【0058】

言い換えると、本発明の実施の形態2にかかる演算処理装置200は、電圧変動対応処理装置と呼ぶことができる。そして、当該電圧変動対応処理装置は、設定値を可変に変更できる閾値レジスタを追加して、全プロセッサ内の演算器数をカウントする機構を用意する。全プロセッサの演算器数が閾値を超える場合は演算起動が追加される演算器に対して演算起動を遅らせることで、電圧変動を抑止することを特徴とする。

【0059】

また、本発明の実施の形態3は、演算器が処理する汎用レジスタ内データから分散値から求めて、レジスタに保存する機能を持つ。そして、演算処理を開始する場合、汎用レジスタからのデータ読み出しと同時にデータ分散値の読み出しも行う。ここで、大きなデータ分散差を示す内容では、演算器の電圧変動が大きくなる可能性があり、このデータ分散値を参考にして演算器の動作を制御する。そして、データ分散値が閾値を超える場合は、演算起動が追加される演算器に対して演算起動を遅らせることで、電圧変動を抑止することを特徴とする。

【0060】

さらに、本発明は上述した実施の形態のみに限定されるものではなく、既に述べた本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

【0061】

上記の実施形態の一部又は全部は、以下の付記のようにも記載され得るが、以下には限られない。

【0062】

(付記1) 同時に実行可能な複数の演算器を有する複数の処理回路と、

各処理回路で実行中の演算器の総数を集計する制御回路と、を備え、

前記複数の処理回路のそれぞれは、前記制御回路が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算処理装置。

【0063】

(付記2) 前記制御回路は、

前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値を記憶する閾値レジスタを有し、

前記複数の処理回路のそれぞれは、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路は、各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれは、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記1に記載の演算処理装置。

【0064】

(付記3) 前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする付記2に記載の演算処理装置。

【0065】

(付記4) 前記制御回路は、前記演算処理装置全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部から受け付け、当該受け付けた演算器の数を前記上限値として前記閾値レジスタを更新することを特徴とする付記2又は3に記載の演算処理装置。

【0066】

(付記5) 前記複数の処理回路のうち一の処理回路は、前記未実行の演算器を実行すると決定した場合、その旨を他の処理回路に対して通知することを特徴とする付記2乃至4のいずれか1項に記載の演算処理装置。

【0067】

(付記6) 前記複数の処理回路のそれぞれは、

各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記1乃至5のいずれか1項に記載の演算処理装置。

【0068】

(付記7) 前記複数の処理回路のそれぞれは、

各演算器における演算対象の要素数に応じた前記分布値の閾値を予め保持し、

前記演算結果から分散値を算出する過程で求まる値を前記分布値とし、

当該分布値と前記閾値とに基づいて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記6に記載の演算処理装置。

【0069】

(付記8) 同時に実行可能な複数の演算器を有する複数の処理回路を制御する制御回路が、各処理回路で実行中の演算器の総数を集計し、

前記複数の処理回路のそれぞれが、前記集計された集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算器同時実行制御方法。

【0070】

(付記9) 前記複数の処理回路のそれぞれが、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路が、

各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれが、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記8に記載の演算器同時実行制御方法。

【0071】

(付記10) 前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする付記9に記載の演算器同時実行制御方法。

【0072】

(付記11) 前記制御回路は、前記演算処理装置全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部から受け付け、当該受け付けた演算器の数を前記上限値として前記閾値レジスタを更新することを特徴とする付記9又は10に記載の演算器同時実行制御方法。

【0073】

(付記12) 前記複数の処理回路のうち一の処理回路は、前記未実行の演算器を実行すると決定した場合、その旨を他の処理回路に対して通知することを特徴とする付記9乃至11のいずれか1項に記載の演算器同時実行制御方法。

【0074】

(付記13) 前記複数の処理回路のそれぞれは、

各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記8乃至12のいずれか1項に記載の演算器同時実行制御方法。

【0075】

(付記14) 前記複数の処理回路のそれぞれは、

各演算器における演算対象の要素数に応じた前記分布値の閾値を予め保持し、

前記演算結果から分散値を算出する過程で求まる値を前記分布値とし、

当該分布値と前記閾値とに基づいて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記13に記載の演算器同時実行制御方法。

【符号の説明】

【0076】

100 演算処理装置

200 演算処理装置

300 演算処理装置

110 制御回路

120A 処理回路

120N 処理回路

13A 演算器

13M 演算器

14A 演算器

14L 演算器

1 制御回路

2 閾値レジスタ

3 比較報告回路

4A プロセッサ

5A 命令発行回路

6A 加算器

7A 加算器

8A 乗算器

9A 乗算器

10A 汎用レジスタ

11A データ分散値レジスタ

12A 閾値レジスタ

100A 実行指示同時発行数

101A 実行可能演算器残数

102A データ分散値

103A 実行指示

104A 実行指示

105A 実行指示

106A 実行指示

4N プロセッサ

5N 命令発行回路

6N 加算器

7N 加算器

8N 乗算器

9N 乗算器

10N 汎用レジスタ

11N データ分散値レジスタ

12N 閾値レジスタ

100N 実行指示同時発行数

101N 実行可能演算器余裕数

102N データ分散値

103N 実行指示

104N 実行指示

105N 実行指示

106N 実行指示

900 演算処理装置

94A プロセッサ

95A 命令発行回路

94N プロセッサ

95N 命令発行回路

t1 タイミング

t2 タイミング

t3 タイミング

t4 タイミング

t5 タイミング

t6 タイミング

t7 タイミング

t8 タイミング

t9 タイミング

【技術分野】

【0001】

本発明は、演算処理装置及び演算器同時実行制御方法に関し、特に、複数の演算器を有する複数のプロセッサにおいて同時実行される演算器数を制御するための演算処理装置及び演算器同時実行制御方法に関する。

【背景技術】

【0002】

特許文献1には、低消費電力化と高速化が可能なマイクロプロセッサに関する技術が開示されている。特許文献1にかかるマイクロプロセッサは、各演算回路を操作する命令を先行検出する検出手段と、この検出手段により検出された命令に対応した演算回路を1つ以上演算実行に先立って活性化し、演算終了後に、活性化された演算回路を不活性化する手段とを有する。そして、当該マイクロプロセッサは、n個(n≧2)の命令を同時に読み出してデコードし、n個の演算回路を用いて同時に演算を実行する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平10−207859号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、特許文献1に代表される関連技術にかかるマイクロプロセッサを複数搭載した演算処理装置も開発されるようになった。このような演算処理装置では、その処理性能を高めるために、複数の演算器(加算器・乗算器など)を多数実装して、高速なギガヘルツ周波数でこれら演算器を同時に動作させるようにして処理を行っている。ギガヘルツ動作を可能にするためには、高速回路技術とともに回路に電源を供給する側の電源の耐ノイズ設計が重要になる。

【0005】

上述した演算処理装置では、電圧変動が発生すると回路のディレイ劣化や誤動作を発生させるため、高速化の妨げになってきている。LSI(Large Scale Integration)チップ内の電圧変動は、(1)回路動作による高周波ノイズと(2)電源抵抗による直流ドロップに大別される。特に(1)が支配的である。そこで、一般的な高周波ノイズの低減策にバイパスコンデンサ(パスコン)をLSIチップに搭載する方法がある。しかし、近年、1チップに複数のプロセッサを実装する傾向にあり、複数プロセッサが同時に起動する場合、電圧変動が大きくなる傾向にある。

【0006】

図8は、関連技術にかかる命令発行回路を複数搭載した演算処理装置900の一例を示す図である。演算処理装置900は、同等の構成を有するプロセッサ94A〜94Nを備える。プロセッサ94Aは、命令発行回路95Aと、複数の演算器である加算器6A、加算器7A、乗算器8A及び乗算器9Aと、汎用レジスタ10Aと、閾値レジスタ12Aとを備える。以降、同様に、プロセッサ94Nは、命令発行回路95Nと、複数の演算器である加算器6N、加算器7N、乗算器8N及び乗算器9Nと、汎用レジスタ10Nと、閾値レジスタ12Nとを備える。ここでは、代表してプロセッサ94Aの内部の構成及び動作について説明する。

【0007】

命令発行回路95Aは、加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれを起動させる場合、加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれに対して、実行指示103A、104A、105A及び106Aを発行する。加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれは、各実行命令に応じて独立して動作し、その処理結果を汎用レジスタ10Aに格納する。閾値レジスタ12Aには、プロセッサ94A内で同時実行可能な演算器の数の上限値が格納されている。命令発行回路95Aは、実行指示103A、104A、105A及び106Aを発行する際に、発行済みの実行指示の数と閾値レジスタ12Aに格納された上限値とを比較し、上限値を超える場合は実行指示の発行を抑制し、プロセッサ94A内で同時に動作させる演算器の数を制御する機構を持っている。

【0008】

しかしながら、演算処理装置900には、プロセッサ94A〜94Nの全体で動作可能な演算器数を制限する機構は持っていなかった。そのため、プロセッサごとに独立して制御をせざるを得ず、動作制限対処範囲が局所的になる。よって、プロセッサ単独では、動作制限を行うことができたとしても、演算処理装置900全体としては性能が落ちるケースも発生してしまうという問題点があった。例えば、あるプロセッサ内で同時に実行される演算器数が上限値未満であり、さらに演算器を同時に実行させる余裕があったとしても、特定のプロセッサ内で同時に実行される演算器数が上限値を超える可能性がある場合には、当該特定のプロセッサにおける演算器の追加の実行を抑制せざるを得ない。この場合、演算処理装置900の最大限の性能を発揮することができない。

【0009】

本発明は、上述した問題点を考慮してなされたものであり、異なるプロセッサ間で同時に演算器が起動する電圧変動最悪パターンを改善するための演算処理装置及び演算器同時実行制御方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の第1の態様にかかる演算処理装置は、

同時に実行可能な複数の演算器を有する複数の処理回路と、

各処理回路で実行中の演算器の総数を集計する制御回路と、を備え、

前記複数の処理回路のそれぞれは、前記制御回路が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

【0011】

本発明の第2の態様にかかる演算器同時実行制御方法は、

同時に実行可能な複数の演算器を有する複数の処理回路を制御する制御回路が、各処理回路で実行中の演算器の総数を集計し、

前記複数の処理回路のそれぞれが、前記集計された集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

【発明の効果】

【0012】

本発明により、異なるプロセッサ間で同時に演算器が起動する電圧変動最悪パターンを改善するための演算処理装置及び演算器同時実行制御方法を提供することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施の形態1にかかる演算処理装置の構成を示すブロック図である。

【図2】本発明の実施の形態1にかかる演算器同時実行制御処理の流れを示すフローチャートである。

【図3】本発明の実施の形態2にかかる演算処理装置の構成を示すブロック図である。

【図4】本発明の実施の形態2にかかる演算器同時実行制御処理の例を示すタイムチャートである。

【図5】本発明の実施の形態3にかかる演算処理装置の構成を示すブロック図である。

【図6】本発明の実施の形態3にかかる汎用レジスタとデータ分散値レジスタとの関係を示す図である。

【図7】本発明の実施の形態3にかかる演算器同時実行制御処理の例を示すタイムチャートである。

【図8】関連技術にかかる演算処理装置の構成を示すブロック図である。

【発明を実施するための形態】

【0014】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。各図面において、同一要素には同一の符号が付されており、説明の明確化のため、必要に応じて重複説明は省略する。

【0015】

<発明の実施の形態1>

図1は、本発明の実施の形態1にかかる演算処理装置100の構成を示すブロック図である。演算処理装置100は、複数の演算器を有する複数の処理回路において同時実行される演算器数を制御するものである。演算処理装置100は、制御回路110と、処理回路120A〜120Nとを備える。尚、処理回路120A〜120Nは、複数個であればよい。処理回路120Aは、演算器13A〜13Mを有する。同様に、処理回路120Nは、演算器14A〜14Lを有する。処理回路120A〜120Nのそれぞれは、自己の有する複数の演算器を同時に実行することが可能である。尚、処理回路120A〜120Nにおける演算器の数は、複数個であればよい。

【0016】

図2は、本発明の実施の形態1にかかる演算器同時実行制御処理の流れを示すフローチャートである。まず、制御回路110は、各処理回路で実行中の演算器の総数を集計する(ステップS11)。次に、処理回路120A〜120Nのそれぞれは、制御回路110が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する(ステップS12)。

【0017】

このように、本発明の実施の形態1では、異なる処理装置間で同時に実行される演算器数を考慮して自己の演算器の実行可否を決定することができる。そのため、異なる処理装置間で同時に演算器が起動する電圧変動最悪パターンを改善することができる。

【0018】

<発明の実施の形態2>

図3は、本発明の実施の形態2にかかる演算処理装置200の構成を示すブロック図である。演算処理装置200は、制御回路1と、プロセッサ4A〜4Nとを備える。プロセッサ4A〜4Nは、複数の演算器を有し、これらの同時実行を行う。また、制御回路1は、プロセッサ4A〜4N内の複数の演算器の同時実行数を全体として制御する。

【0019】

制御回路1は、閾値レジスタ2と、比較報告回路3とを備える。閾値レジスタ2は、プロセッサ4A〜4N全てにおいて同時に実行可能な演算器の数の上限値を記憶する。

比較報告回路3は、プロセッサ4A〜4Nのそれぞれから実行指示同時発行数100A〜100Nを受け付ける。そして、比較報告回路3は、各プロセッサから通知された実行指示同時発行数100A〜100Nを集計してその総数を算出する。続いて、比較報告回路3は、当該総数と上限値との差分値(実行可能演算器残数)を各プロセッサへ通知する。ここで、実行指示同時発行数100A〜100Nは、各プロセッサ内で同時に実行中の演算器の数である同時実行演算器数である。また、実行可能演算器残数は、演算処理装置200内の全プロセッサで実行可能な演算器の残数である。または、実行可能演算器残数は、演算処理装置200内の全プロセッサで実行可能な演算器の余裕数と言い換えることもできる。

【0020】

プロセッサ4Aは、命令発行回路5A、加算器6A、加算器7A、乗算器8A、乗算器9A及び汎用レジスタ10Aを備える。汎用レジスタ10Aには、加算器6A、加算器7A、乗算器8A及び乗算器9Aのそれぞれによる演算結果が格納される。命令発行回路5Aは、プログラムに従い加算器6A、加算器7A、乗算器8A及び乗算器9Aについて実行の開始を指示するための実行指示103A、104A、105A及び106Aをそれぞれに対して発行する。特に、命令発行回路5Aは、同時に動作可能な加算及び乗算の演算があれば、該当する演算器に対して実行指示を行う。具体的には、加算器6Aの実行が可能なら汎用レジスタ10Aからオペランドデータを読み出して加算器6Aにデータを送付し同時に実行指示103Aを送付する。同様に、乗算器9Aの実行が可能なら汎用レジスタ10Aからオペランドデータを読み出して乗算器9Aにデータを送付し同時に実行指示106Aを送付する。

【0021】

また、命令発行回路5Aは、発行した実行指示の数を実行指示同時発行数として制御回路1へ通知する。そして、命令発行回路5Aは、制御回路1から実行可能演算器残数を受け付ける。そして、命令発行回路5Aは、演算器の起動を行う場合、実行可能演算器残数の値を見ながら起動の判断を行っている。他のプロセッサもプロセッサ4Aと同様の動作を行う。つまり、プロセッサ4A〜4Nのそれぞれは、実行可能演算器残数に応じて未実行の演算器を実行するか否かを決定する。そして、複数の処理回路のそれぞれは、実行すると決定した演算器の数が実行可能演算器残数を超える場合、当該超える分の演算器の実行の開始を保留する。これにより、演算処理装置200全体としての性能の最適化を図ることができる。

【0022】

尚、プロセッサ4Nは他のプロセッサの一例である。プロセッサ4Nは、例えば、命令発行回路5N、加算器6N、加算器7N、乗算器8N、乗算器9N及び汎用レジスタ10Nを備える。尚、プロセッサ4A〜4Nが備える演算器の種類及び数は、上述したものに限定されない。

【0023】

図4は、本発明の実施の形態2にかかる演算器同時実行制御処理の例を示すタイムチャートである。タイミングt1において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行する。同様に、命令発行回路5Aは、乗算器8Aを起動するために実行指示105Aを発行する。このとき、命令発行回路5Aは、タイミングt1の実行指示同時発行数100Aを"2"として比較報告回路3へ通知する。

【0024】

同様に、タイミングt1において、命令発行回路5Nは、加算器6Nを起動するために実行指示103Nを発行する。このとき、命令発行回路5Nは、タイミングt1の実行指示同時発行数100Nを"1"として比較報告回路3へ通知する。

【0025】

タイミングt1において、比較報告回路3は、全プロセッサからの実行指示同時発行数100A〜100Nを集計して"3"の値を算出する。そして、制御回路1は、閾値レジスタ2に格納された上限値"5"と上記集計結果"3"との比較を行い、その差分値"2"を算出する。その後、比較報告回路3は、差分値"2"を実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0026】

タイミングt2において、プロセッサ4Aは、再度、加算器6A及び乗算器8Aの起動を試みる。このとき、実行指示同時発行数100Aがタイミングt1と同数"2"となるため、そのまま実行指示103A及び実行指示105Aを発行し、実行指示同時発行数100A"2"を比較報告回路3へ通知する。また、プロセッサ4Nは、加算器6Nに加え、加算器7Nの起動を試みる。このとき、実行指示同時発行数100Nが直前のタイミングt1と比べて"1"大きい"2"となる。但し、タイミングt1で通知された実行可能演算器余裕数101Nが"2"であるため、命令発行回路5Nは、そのまま実行指示103N及び実行指示104Nを発行し、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0027】

タイミングt2において、比較報告回路3は、全プロセッサからの実行指示同時発行数100A〜100Nを集計して"4"の値を算出し、上限値"5"との差分値"1"を算出する。その後、比較報告回路3は、差分値"1"を実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0028】

タイミングt3において、プロセッサ4Aは、加算器6A及び乗算器8Aに加え、加算器7Aの起動を試みる。このとき、実行指示同時発行数100Aが直前のタイミングt2と比べて"1"大きい"3"となる。但し、タイミングt2で通知された実行可能演算器余裕数101Aが"1"であるため、命令発行回路5Aは、そのまま実行指示103A、104A及び105Aを発行し、実行指示同時発行数100A"3"を比較報告回路3へ通知する。また、プロセッサ4Nは、再度、加算器6N及び加算器7Nの起動を試みる。このとき、実行指示同時発行数100Nがタイミングt2と同数"2"となるため、そのまま実行指示103N及び104Nを発行し、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0029】

タイミングt3において、比較報告回路3は、全プロセッサからの実行指示同時発行数100A〜100Nを集計して"5"の値を算出し、上限値"5"との差分値"0"を算出する。その後、比較報告回路3は、差分値"0"を実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0030】

タイミングt4において、プロセッサ4Aは、再度、加算器6A、加算器7A及び乗算器8Aの起動を試みる。このとき、実行指示同時発行数100Aがタイミングt3と同数"3"となるため、そのまま実行指示103A、104A及び105Aを発行し、実行指示同時発行数100A"3"を比較報告回路3へ通知する。

【0031】

また、プロセッサ4Nは、加算器6N及び加算器7Nに加え、乗算器8Nの起動を試みる。このとき、実行指示同時発行数100Nが直前のタイミングt3と比べて"1"大きい"3"となってしまう。タイミングt3で通知された実行可能演算器余裕数101Nが"0"であるため、命令発行回路5Nは、直前に発行済みの実行指示103N及び104Nについては継続して発行しつつ、実行指示105Nについては発行を抑制する。つまり、未実行の演算器である乗算器8Nについての実行を保留し、乗算器8Nの起動を遅らせている。もし、このときに実行指示105Nまで発行してしまうと、全プロセッサの演算器の同時実行数の上限値"5"を超えてしまうためである。そして、命令発行回路5Nは、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0032】

タイミングt4において、比較報告回路3は、タイミングt3と同様に、差分値"0"を算出し、実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0033】

タイミングt5において、プロセッサ4Aは、タイミングt3及びt4と同様に動作する。そして、プロセッサ4Nは、加算器6N及び乗算器8Nの起動を試みる。このとき、加算器7Nが演算終了により起動不要となり、乗算器8Nの起動が可能となる。すなわち、実行指示同時発行数100Nがタイミングt4と同数"2"となるため、プロセッサ4Nは、実行指示103N及び105Nを発行し、実行指示同時発行数100N"2"を比較報告回路3へ通知する。

【0034】

タイミングt5において、比較報告回路3は、タイミングt4と同様に、差分値"0"を算出し、実行可能演算器残数101A〜101Nとして、プロセッサ4A〜4Nのそれぞれへ通知する。

【0035】

以上説明したように本発明においては、以下に記載するような効果を奏する。それは、全プロセッサにおいて同時に実行可能な演算器の数の上限値を予め保持する閾値レジスタと複数のプロセッサ間における同時に動作させる演算器の動作状態を把握する機構を用意することで、把握した結果から演算器の起動をずらして動作させることが可能となり、同時に動作開始する演算器を減少させて電圧変動を低減できることである。

【0036】

また、制御回路1は、実行可能演算器残数を集中管理して各プロセッサに配布している。これにより、各プロセッサは、通知された実行可能演算器残数を基に自律的に未実行の演算器の実行可否を判定でき、処理の高速化を図ることができる。

【0037】

具体的には、制御回路1は、各プロセッサで動作させる演算器数を把握できる信号を各プロセッサから受け付けて集計することで、総数を把握する。そして、各プロセッサは、未実行の演算器を実行させると、全演算器の動作数が閾値を超えてしまう場合には、当該演算器の起動を遅らせる。そして、全演算器の動作数が閾値を下回った場合に、当該起動を遅らせた演算器を起動させる。これにより、電圧変動が急峻になることを防げる。

【0038】

さらに、制御回路1は、演算処理装置200全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部のプログラム等から受け付け、当該受け付けた演算器の数を上限値として閾値レジスタ2を更新することが望ましい。プログラムで指定される演算器の動作数に依存して電圧値が変わるが、閾値レジスタを電圧変動の最大許容値に設定することで大きく性能を落とさない処理が可能となる。

【0039】

また、複数のプロセッサのうち一のプロセッサは、未実行の演算器を実行すると決定した場合、その旨を他のプロセッサに対して通知するとさらに良い。これにより、他のプロセッサが当該通知により自己の未実行の演算器の実行を抑制することで、演算処理装置200全体の性能を維持することができる。

【0040】

さらに、複数のプロセッサのうち一のプロセッサは、未実行の演算器を実行すると決定した場合、差分値から当該実行すると決定された演算器の数を減じた値を新たな差分値として他の処理回路に対して通知するようにしてもよい。これにより、各プロセッサは、再度、比較報告回路3から実行可能演算器残数101A等の通知を待つことなく、自己の未実行の演算器の実行を抑制することができる。

【0041】

<発明の実施の形態3>

本発明の他の実施形態では、その基本的構成は上記の通りであるが、電圧変動の低減についてさらに工夫している。図5は、本発明の実施の形態3にかかる演算処理装置300の構成を示すブロック図である。演算処理装置300は、制御回路1と、プロセッサ4A〜4Nとを備える。尚、制御回路1は、実施の形態2の図3と同等であるため、詳細な説明を省略する。

【0042】

実施の形態3に係る命令発行回路5Aは、実施の形態2と比べて、閾値レジスタ12Aと、データ分散値レジスタ11Aをさらに備える。同様に、命令発行回路5Nは、閾値レジスタ12Nと、データ分散値レジスタ11Nをさらに備える。命令発行回路5A〜5Nのそれぞれは、各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して未実行の演算器を実行するか否かを決定する。尚、以下では、説明のため命令発行回路5Aについて記載するが、命令発行回路5A以外についても同様である。

【0043】

図6は、本発明の実施の形態3にかかる汎用レジスタ10Aとデータ分散値レジスタ11Aとの関係を示す図である。汎用レジスタ10Aには、1セット当たり32要素のデータを、8セット分(セット0〜7)格納されていることを示す。また、データ分散値レジスタ11Aには、セット内のデータにおけるデータのばらつき指標を示す値である分布値が各セットに対応して格納されていることを示す。

【0044】

図5に戻って説明する。プロセッサ4Aの加算器6A、加算器7A、乗算器8A及び乗算器9Aは、例えば、1回の演算で、汎用レジスタ10Aから32要素を2セット分読み出して演算を行うものとする。そして、各演算器は、32要素(1セット分)の演算を行った演算結果を汎用レジスタ10Aに書き込む。併せて、各演算器は、1セット単位に、分布値を算出して、汎用レジスタ10Aのセットに対応付けてデータ分散値レジスタ11Aに格納する。

【0045】

ここで、分布値は、データ1つ当たりどの程度ばらついているかを示す値である。分布値に統計学上の分散値を用いる場合には、以下の式(1)により算出することができる。

分散値V={Σ(Xi−Xn)2}/(n−1) ・・・(1)

ここで、nは、1セット当たりの要素数、Xnは平均値、Xiは、各要素の値、つまり、汎用レジスタ10Aに格納される演算結果を示す。

【0046】

閾値レジスタ12Aは、分散値の閾値を予め記憶する。そして、命令発行回路5Aは、プログラムに従いある演算器に対して実行指示を行う場合、直前に動作していた演算器の演算結果に対応する分散値をデータ分散値レジスタ11Aから読み出し、閾値レジスタ12Aに格納された閾値と比較する。このとき、実行可能演算器残数101Aが"0"であっても分散値が閾値以内である場合、命令発行回路5Aは、予定通り演算器へ実行指示を発行する。分散値が小さい場合には、電流変動が小さいと考えられるからである。または、実行可能演算器残数101Aが"1"以上であっても分散値が閾値以上である場合に、命令発行回路5Aは、演算器へ実行指示を保留しても構わない。例え、同時実行数が許容範囲だとしても、電流変動が大きい可能性があるためである。このように、実施の形態3では、データの変動分を考慮して実行指示を出すことで大きく性能を落とさない処理が可能となる。

【0047】

また、各演算器における分布値の算出時間を短縮化するために、以下の式(2)により算出される分布値を用いることもできる。

分布値V'={Σ(Xi−Xn)2} ・・・(2)

式(2)は、式(1)から要素数に応じた除算を省略したものである。つまり、分布値V'は、分散値Vの除算前の値であり、いわば演算結果から分散値を算出する過程で求まる値である。この場合、閾値レジスタ12Aには、各演算器における演算対象の要素数に応じた分布値の閾値を予め格納しておけばよい。分布値V'は、分散値Vと違い、合算する個数(最大32要素)によっても異なるためである。

【0048】

そのため、各演算器は、除算を省略して分布値を算出してデータ分散値レジスタ11Aに格納できる。その後、命令発行回路5Aは、演算器の演算対象の要素数に対応する閾値を閾値レジスタ12Aから読み出して、データ分散値レジスタ11Aから読み出した分布値との間で、同様に比較することができる。これにより、各演算器は、除算動作不要となり分布値V'の算出時間を短縮することができる。

【0049】

図7は、本発明の実施の形態3にかかる演算器同時実行制御処理の例を示すタイムチャートである。図7では、演算処理する要素数を"4"としている。尚、実際には、実行指示から結果が得られるまで数サイクルを必要とするが、ここでは、説明の便宜のため、演算結果とデータ分散値はそのタイミングで生成されると仮定したタイムチャートとしている。

【0050】

ここで、データ分散値(分布値)の生成について説明する。タイミングt1において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット0の演算結果を汎用レジスタ10Aに、セット0の分布値A1をデータ分散値レジスタ11Aに格納する。次に、タイミングt2において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット1の演算結果を汎用レジスタ10Aに、セット0及び1の分布値A2をデータ分散値レジスタ11Aに格納する。そして、タイミングt3において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット2の演算結果を汎用レジスタ10Aに、セット0〜2の分布値A3をデータ分散値レジスタ11Aに格納する。さらに、タイミングt4において、命令発行回路5Aは、加算器6Aを起動するために実行指示103Aを発行し、加算器6Aは、セット3の演算結果を汎用レジスタ10Aに、セット0〜3の分布値A4をデータ分散値レジスタ11Aに格納する。また、乗算器8Aもタイミングt1〜t4において、セット0〜3の演算結果と、セット0〜3の分布値C1〜C4とをそれぞれ汎用レジスタ10A及びデータ分散値レジスタ11Aに格納する。このようにデータ分散値は、処理する要素を前タイミング結果に足しこみながら生成していく。

【0051】

一方、演算器を起動する制御について説明する。タイミングt2において、プロセッサ4Aは、加算器6Aと乗算器8Aが動作しているので、実行指示同時発行数100A"2"を比較報告回路3に通知する。同時に、プロセッサ4Nは、加算器6Nが動作しているので、実行指示同時発行数100N"1"を比較報告回路3に通知する。

【0052】

タイミングt5において、命令発行回路5Aは、直前のタイミングt4で比較報告回路3から通知された実行可能演算器残数101A"0"を参照して、演算器の起動を行う。その際に、命令発行回路5Aは、タイミングt4で演算が完了した加算器6Aの演算結果に対応する分布値A4及び乗算器8Aの演算結果に対応する分布値C4を、データ分散値レジスタ11Aから参照しつつ、乗算器9Aの起動判断を行う。ここでは、分布値"A4"と分布値"C4"の値が閾値より小さいものとする。この場合、命令発行回路5Aは、乗算器9Aが実行可能と判断し、タイミングt5で実行指示106Aを発行する。また、タイミングt5において仮に分布値"A4"と分布値"C4"の値のいずれかが閾値を上回っていた場合、実行可能演算器残数101Aに余裕があったとしても、命令発行回路5Aは、乗算器9Aの実行指示の発行を保留する。

【0053】

このように、本実施の形態3では、読み出すデータの分散値を参照しながら起動判断を行っているので、データの変動分を考慮して実行指示を出すことができ、演算処理装置300全体の性能を大きく落とさない処理が可能となる。

【0054】

<その他の発明の実施の形態>

尚、本発明の実施の形態2は、電圧変動に対応した処理装置において、同時に動作させる演算器の動作状態を把握し、把握した結果から演算器起動をずらして動作させることにより、同時に動作開始する演算器を減少させて電圧変動を低減させることを特徴としている。

【0055】

具体的には、設定値を可変にできる閾値レジスタを用意しておいて、動作させる演算器数を把握できる信号を各プロセッサで把握しながら全演算器の動作数が閾値を超えた場合、電圧変動が急峻にならないように閾値を超えた演算器の動作を遅らせるように動作させる。プログラムで指定される演算器の動作数に依存して電圧値が変わるが、閾値レジスタを電圧変動の最大許容値に設定することで大きく性能を落とさない処理が可能となる。

【0056】

そして、演算器動作数の他にデータに依存しても電圧変動値が変わるので、演算器で処理するデータのばらつき値として分散値を参照しながら動作させる演算器数を可変にできる処理装置も提供する。具体的には、汎用レジスタにデータを書き込む際に、統計学で使用されている分散値を回路で求めながら最後の算出結果を汎用レジスタ分散値レジスタに保持する。演算器を動作させる場合には、演算器の動作数に加えて汎用レジスタ分散値も参考にしながら電圧変動が急峻にならないように演算器の動作を遅らせるように動作させる。

【0057】

このように、本発明の実施の形態2では、設定値を可変にできる閾値レジスタを電圧変動の最大許容値に設定しながら演算器の動作状態を把握して処理を行うようにしているので、大きく性能を落とすことなく電圧変動に対応した動作が可能となる。

【0058】

言い換えると、本発明の実施の形態2にかかる演算処理装置200は、電圧変動対応処理装置と呼ぶことができる。そして、当該電圧変動対応処理装置は、設定値を可変に変更できる閾値レジスタを追加して、全プロセッサ内の演算器数をカウントする機構を用意する。全プロセッサの演算器数が閾値を超える場合は演算起動が追加される演算器に対して演算起動を遅らせることで、電圧変動を抑止することを特徴とする。

【0059】

また、本発明の実施の形態3は、演算器が処理する汎用レジスタ内データから分散値から求めて、レジスタに保存する機能を持つ。そして、演算処理を開始する場合、汎用レジスタからのデータ読み出しと同時にデータ分散値の読み出しも行う。ここで、大きなデータ分散差を示す内容では、演算器の電圧変動が大きくなる可能性があり、このデータ分散値を参考にして演算器の動作を制御する。そして、データ分散値が閾値を超える場合は、演算起動が追加される演算器に対して演算起動を遅らせることで、電圧変動を抑止することを特徴とする。

【0060】

さらに、本発明は上述した実施の形態のみに限定されるものではなく、既に述べた本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

【0061】

上記の実施形態の一部又は全部は、以下の付記のようにも記載され得るが、以下には限られない。

【0062】

(付記1) 同時に実行可能な複数の演算器を有する複数の処理回路と、

各処理回路で実行中の演算器の総数を集計する制御回路と、を備え、

前記複数の処理回路のそれぞれは、前記制御回路が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算処理装置。

【0063】

(付記2) 前記制御回路は、

前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値を記憶する閾値レジスタを有し、

前記複数の処理回路のそれぞれは、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路は、各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれは、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記1に記載の演算処理装置。

【0064】

(付記3) 前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする付記2に記載の演算処理装置。

【0065】

(付記4) 前記制御回路は、前記演算処理装置全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部から受け付け、当該受け付けた演算器の数を前記上限値として前記閾値レジスタを更新することを特徴とする付記2又は3に記載の演算処理装置。

【0066】

(付記5) 前記複数の処理回路のうち一の処理回路は、前記未実行の演算器を実行すると決定した場合、その旨を他の処理回路に対して通知することを特徴とする付記2乃至4のいずれか1項に記載の演算処理装置。

【0067】

(付記6) 前記複数の処理回路のそれぞれは、

各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記1乃至5のいずれか1項に記載の演算処理装置。

【0068】

(付記7) 前記複数の処理回路のそれぞれは、

各演算器における演算対象の要素数に応じた前記分布値の閾値を予め保持し、

前記演算結果から分散値を算出する過程で求まる値を前記分布値とし、

当該分布値と前記閾値とに基づいて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記6に記載の演算処理装置。

【0069】

(付記8) 同時に実行可能な複数の演算器を有する複数の処理回路を制御する制御回路が、各処理回路で実行中の演算器の総数を集計し、

前記複数の処理回路のそれぞれが、前記集計された集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算器同時実行制御方法。

【0070】

(付記9) 前記複数の処理回路のそれぞれが、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路が、

各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれが、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記8に記載の演算器同時実行制御方法。

【0071】

(付記10) 前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする付記9に記載の演算器同時実行制御方法。

【0072】

(付記11) 前記制御回路は、前記演算処理装置全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部から受け付け、当該受け付けた演算器の数を前記上限値として前記閾値レジスタを更新することを特徴とする付記9又は10に記載の演算器同時実行制御方法。

【0073】

(付記12) 前記複数の処理回路のうち一の処理回路は、前記未実行の演算器を実行すると決定した場合、その旨を他の処理回路に対して通知することを特徴とする付記9乃至11のいずれか1項に記載の演算器同時実行制御方法。

【0074】

(付記13) 前記複数の処理回路のそれぞれは、

各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記8乃至12のいずれか1項に記載の演算器同時実行制御方法。

【0075】

(付記14) 前記複数の処理回路のそれぞれは、

各演算器における演算対象の要素数に応じた前記分布値の閾値を予め保持し、

前記演算結果から分散値を算出する過程で求まる値を前記分布値とし、

当該分布値と前記閾値とに基づいて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする付記13に記載の演算器同時実行制御方法。

【符号の説明】

【0076】

100 演算処理装置

200 演算処理装置

300 演算処理装置

110 制御回路

120A 処理回路

120N 処理回路

13A 演算器

13M 演算器

14A 演算器

14L 演算器

1 制御回路

2 閾値レジスタ

3 比較報告回路

4A プロセッサ

5A 命令発行回路

6A 加算器

7A 加算器

8A 乗算器

9A 乗算器

10A 汎用レジスタ

11A データ分散値レジスタ

12A 閾値レジスタ

100A 実行指示同時発行数

101A 実行可能演算器残数

102A データ分散値

103A 実行指示

104A 実行指示

105A 実行指示

106A 実行指示

4N プロセッサ

5N 命令発行回路

6N 加算器

7N 加算器

8N 乗算器

9N 乗算器

10N 汎用レジスタ

11N データ分散値レジスタ

12N 閾値レジスタ

100N 実行指示同時発行数

101N 実行可能演算器余裕数

102N データ分散値

103N 実行指示

104N 実行指示

105N 実行指示

106N 実行指示

900 演算処理装置

94A プロセッサ

95A 命令発行回路

94N プロセッサ

95N 命令発行回路

t1 タイミング

t2 タイミング

t3 タイミング

t4 タイミング

t5 タイミング

t6 タイミング

t7 タイミング

t8 タイミング

t9 タイミング

【特許請求の範囲】

【請求項1】

同時に実行可能な複数の演算器を有する複数の処理回路と、

各処理回路で実行中の演算器の総数を集計する制御回路と、を備え、

前記複数の処理回路のそれぞれは、前記制御回路が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算処理装置。

【請求項2】

前記制御回路は、

前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値を記憶する閾値レジスタを有し、

前記複数の処理回路のそれぞれは、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路は、各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれは、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項1に記載の演算処理装置。

【請求項3】

前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする請求項2に記載の演算処理装置。

【請求項4】

前記制御回路は、前記演算処理装置全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部から受け付け、当該受け付けた演算器の数を前記上限値として前記閾値レジスタを更新することを特徴とする請求項2又は3に記載の演算処理装置。

【請求項5】

前記複数の処理回路のうち一の処理回路は、前記未実行の演算器を実行すると決定した場合、その旨を他の処理回路に対して通知することを特徴とする請求項2乃至4のいずれか1項に記載の演算処理装置。

【請求項6】

前記複数の処理回路のそれぞれは、

各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項1乃至5のいずれか1項に記載の演算処理装置。

【請求項7】

前記複数の処理回路のそれぞれは、

各演算器における演算対象の要素数に応じた前記分布値の閾値を予め保持し、

前記演算結果から分散値を算出する過程で求まる値を前記分布値とし、

当該分布値と前記閾値とに基づいて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項6に記載の演算処理装置。

【請求項8】

同時に実行可能な複数の演算器を有する複数の処理回路を制御する制御回路が、各処理回路で実行中の演算器の総数を集計し、

前記複数の処理回路のそれぞれが、前記集計された集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算器同時実行制御方法。

【請求項9】

前記複数の処理回路のそれぞれが、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路が、

各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれが、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項8に記載の演算器同時実行制御方法。

【請求項10】

前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする請求項9に記載の演算器同時実行制御方法。

【請求項1】

同時に実行可能な複数の演算器を有する複数の処理回路と、

各処理回路で実行中の演算器の総数を集計する制御回路と、を備え、

前記複数の処理回路のそれぞれは、前記制御回路が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算処理装置。

【請求項2】

前記制御回路は、

前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値を記憶する閾値レジスタを有し、

前記複数の処理回路のそれぞれは、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路は、各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれは、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項1に記載の演算処理装置。

【請求項3】

前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする請求項2に記載の演算処理装置。

【請求項4】

前記制御回路は、前記演算処理装置全体における電圧変動量の許容値に基づき定まる同時に実行可能な演算器の数を外部から受け付け、当該受け付けた演算器の数を前記上限値として前記閾値レジスタを更新することを特徴とする請求項2又は3に記載の演算処理装置。

【請求項5】

前記複数の処理回路のうち一の処理回路は、前記未実行の演算器を実行すると決定した場合、その旨を他の処理回路に対して通知することを特徴とする請求項2乃至4のいずれか1項に記載の演算処理装置。

【請求項6】

前記複数の処理回路のそれぞれは、

各演算器における演算結果のデータのばらつきを示す分布値をさらに考慮して前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項1乃至5のいずれか1項に記載の演算処理装置。

【請求項7】

前記複数の処理回路のそれぞれは、

各演算器における演算対象の要素数に応じた前記分布値の閾値を予め保持し、

前記演算結果から分散値を算出する過程で求まる値を前記分布値とし、

当該分布値と前記閾値とに基づいて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項6に記載の演算処理装置。

【請求項8】

同時に実行可能な複数の演算器を有する複数の処理回路を制御する制御回路が、各処理回路で実行中の演算器の総数を集計し、

前記複数の処理回路のそれぞれが、前記集計された集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する

演算器同時実行制御方法。

【請求項9】

前記複数の処理回路のそれぞれが、自己の処理回路内で同時に実行中の演算器の数である同時実行演算器数を前記制御回路へ通知し、

前記制御回路が、

各処理回路から通知された前記同時実行演算器数を集計して前記総数を算出し、

当該総数と前記複数の処理回路全てにおいて同時に実行可能な演算器の数の上限値との差分値を各処理回路へ通知し、

前記複数の処理回路のそれぞれが、前記差分値に応じて前記未実行の演算器を実行するか否かを決定する

ことを特徴とする請求項8に記載の演算器同時実行制御方法。

【請求項10】

前記複数の処理回路のそれぞれは、前記実行すると決定した演算器の数が前記差分値を超える場合、当該超える分の演算器の実行の開始を保留することを特徴とする請求項9に記載の演算器同時実行制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−69220(P2013−69220A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−208889(P2011−208889)

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]