画素値を抽出する方法および装置

【課題】順離散コサイン変換(DCT)を使用してMPEGかJPEGコード化に従ってコード化された画素の輝度および色光度を抽出するための方法および装置を提供する。

【解決手段】方法はMPEGコード化に使用される順DCTを数学的に分析するために理論上のワークを適用し、コード化された画像における画素値を、普通の画像コード化過程において順DCT変換を経て得られる1つ以上のDCT係数に直接関係付ける方程式の組を引き出す。これらの予め決定された方程式は、逆DCT変換を受ける必要はなくコード化された画素ブロックのDCT係数から直接画素値を非常に速くかつ計算上効率的な抽出を可能にするように使用される。発明は速くて効率的である方法でMPEGおよびJPEGコード化バージョンからオリジナル画像を抽出することが望ましいところでどんなアプリケーションにも役に立つことが期待される。

【解決手段】方法はMPEGコード化に使用される順DCTを数学的に分析するために理論上のワークを適用し、コード化された画像における画素値を、普通の画像コード化過程において順DCT変換を経て得られる1つ以上のDCT係数に直接関係付ける方程式の組を引き出す。これらの予め決定された方程式は、逆DCT変換を受ける必要はなくコード化された画素ブロックのDCT係数から直接画素値を非常に速くかつ計算上効率的な抽出を可能にするように使用される。発明は速くて効率的である方法でMPEGおよびJPEGコード化バージョンからオリジナル画像を抽出することが望ましいところでどんなアプリケーションにも役に立つことが期待される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は離散コサイン変換(DCT)係数から直接画素値を抽出する、特に逆DCT変換を引き受ける必要はなくてそのような値を抽出する方法、装置、およびコンピュータプログラムに関連する。

【背景技術】

【0002】

インターネットの増殖と電子商取引におけるマルチメディア情報技術の急速な展開と、そして様々なビジネスセクターに亘って、デジタル記憶装置のコストは想像を絶する速度で減少されている。テキストフォームだけでなく、ディジタル画像、デジタルビデオ、立体コンピュータグラフィックス、および他の多くのディジタルデータ形式のフォームに豊かなコンテンツ情報を記憶することが現在可能である。ワールドワイドウエブの到達の後に、インターネットアクセス可能な情報の宝庫がますます共通になるように、情報交換および創造が革命的変化の下にある。統制に関連する情報の全体のセクターの下での1つのインパクトは、効率、有効性、および丈夫さを有してマルチメディア情報のコンテンツを扱って、管理して、記憶するために新しい技術の展開の必要性である。この処理中に、何百万もの画像、ビデオクリップが取扱われ、調査され、索引をつけられ、検索されることができるが、それらの大部分が既に圧縮形式であることができる。現在使用されているすべての圧縮形式の中では、離散コサイン変換(DCT)が以下の理由で広く採用される:(a) 離散コサイン変換が最適のKarhunen-Loeve変換(KLT)に近い;(b)DCTは信号独立であり、KLTの短所を取除くことができる;そして(c)それは本当の係数を有し、速いアルゴリズムは実際に効率的である実施のために容易に利用可能である。したがって、DCTは画像/ビデオ圧縮規格(JPEG/MPEG、およびH261/H263)で広く使用される(J. Jiang “A parallel algorithm for 4×4 DCT” Journal of Parallel and Distributed Computing, Vol.57、1999、pp 257-269、ISDN: 0743-7315 and V.Bhaskaran and K.Konstanti, Image and Video Comptession Standards: Algorithms and Architectures, Kluwer Academic Publications,Boston, 1997参照)。この文脈の下では、圧縮領域または内部データ圧縮のコンテンツ記述における画像処理の研究の新たな波は、A.Abdel-Malek and J.E.Hershey “Feature cueing in the discrete cosine domain”, Journal of Electronic Imaging, Vol.3、pp. 71-80, Jan, 1994, B.Shen and Ishwar K.Sethi,“Direct feature extraction from compressed images”, SPIE: Vol.2670 Storage & Retrieval for Image and Video Databases IV, 1996,and R.Reeve, K.Kubik and W.Osberger,”Texture characterization of compressed aerial images using DCT coefficients“,Proc. Of SPIE: Storge and Retrival for Image and Video Databases V, Vol.3022、pp. 398-407,Feb, 1997に記述されるように、世界的な研究共同体で始められている。

【0003】

上記から明らかであるように、動きと静止画像のMPEGとJPEGコード化は技術において良く知られており、共通のエンコーダとデコーダ構造は図1で示される。MPEG(およびJPEG)画像をコード化するために、ソース画素画像は次に離散コサイン変換(DCT)を受けさせる8×8ブロックに最初に分割される。これは、頂部左隅にDC構成要素を有し、画素ブロックをとおして頂部左から外側へ分配された増大するより高次のAC構成要素を有する64のDCT係数をもたらす。これらの構成要素は次に、コードブックから2進コードを使用して量子化されてそれぞれそれらの実数DCT係数を表し、またその値が量子化閾値以下であるそれらの係数を廃棄し、次にジグザグパターン(図2で示されるように)に係数を取ることによって連続のデータワードに変換され、その結果ゼロに量子化された構成要素が効率的にラン-レングスコード化されることができ、伝送の前にエントロピーコード化により続けられる。この過程は画像の8×8画素ブロック毎に繰り返される。

【0004】

デコーダで画像をデコードするために、通常逆の過程が実行され、即ちエントロピーとラン-レングスは受信されたデータをデコードして、図2のジグザグパターンを逆にすることによってDCT係数を8×8ブロックに再構成し、逆DCT(IDCT)を実行して実際の画素値を得る。逆DCTステップは計算上徹底的であり、実行するのに時間とパワーを必要とする。通常、標準の完全な逆圧縮(IDCT)のために、計算コストは4096の掛け算と4032の足し算であるが、いくつかの実用的な実施では8×8画素ブロックあたり1024の掛け算と896の足し算だけであるかもしれない(さらなる比較のために我々の“結果”セクションの表を参照)。

【0005】

画像処理の領域は何年間も研究開発の焦点であった(増進、細分化、特徴抽出、パターン分類などのようなタスクで代表される)が、そのような開発は画素領域にすべて存在した。DCTベースのデータ圧縮が伝送効率と限られた記憶装置スペースの管理を大いに改良している間、圧縮された視覚データは、表示さらに処理または印刷される前に画素領域に戻って処理されなければならない。いくつかのしばしば採用される処理機能は、スケーリング、フィルタリング、回転、置換、特徴抽出、および分類を含んでいる。この終わりに、通常のアプローチは、そのような既存のアルゴリズムを適用することができる前にDCT領域から画素領域へデータを変換(逆圧縮)しなければならない。そのような処理は、すでに与えられたコンピュータの徹底形態から明らかであるように、画像処理と圧縮の全体の連鎖におけるオーバーヘッド計算コストと記憶装置コストの重要な増加に通じる。

【発明の概要】

【0006】

したがって、画像操作(探索、フィルタリング、表示など)が実行されなければならないときはいつもIDCT操作を使用して各画像を完全に逆圧縮する必要はなく、処理されるべき大規模画像メディアを許容するそれほど計算上徹底的でない手段が産業の中で強い必要性がある。

【0007】

本発明は、MPEGまたはJPEGをデコードするために逆離散コサイン変換を実行する必要性を取り除く方法、コンピュータプログラムおよび装置を提供することにより上記の問題を処理する。すなわち、図1で示される従来技術のデコーダに関して、発明は逆離散コサイン変換ブロック10を置き換えて、一組のパラメタを通して抽出された画素値を直接DCT係数に関係付ける一組の予め定義された、簡単な一次方程式の適用により、画素値がDCT係数から直接抽出されることを許容する方法、コンピュータプログラム、および装置を提供する。したがって、MPEGまたはJPEGのコード化された領域からソース画像を抽出するために、すべてのデコーダの必要な計算が入力DCT係数の与えられた組について予め設定された組の方程式の結果であり、したがって、それは、もはや付随のコンピュータの徹底計算を要する逆DCT変換を実行する必要はない。

【0008】

上記の観点において、本発明に従った第1の態様は、ソース画像における画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する方法が提供され、方法は、

それぞれ値が抽出されるべきである特定の画素に関連づけられる複数の予め計算されたパラメタを記憶し;

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算するステップを含む。

【0009】

1つ以上のDCT係数と共に予め計算されたパラメタを使用して画素値を計算する能力は、コンピュータの徹底計算が非常に減少することを意味する。採用される特定の実施に依存して、オリジナルの画像による画素の8×8ブロックについて、MPEGまたはJPEGコード化バージョンから最小8つの加算と4つの割算で画素値を抽出することが可能である。明らかに、これは以前に使用された完全な逆離散コサイン変換と比較して重要な減少である。

【0010】

その上、望ましくは、DCT係数の予め選択された部分集合は、画素値を計算するのに使用される。特定の実施例から明らかになるように、どんな特定の画素ブロックからのDCT係数の比較的小さい部分集合だけでも本発明の演算に必要とされる。一実施例では、最小4つの係数が必要であるが、他の実施例では多分9、または16の係数で使用される。どの実施例が選ばれても、使用されるDCT係数の数が完全な逆離散コサイン変換の実施の中で通常使用される64の係数より実質的に少ないことが認識されるであろう。これは非常に低い帯域幅ビデオ伝送を容易にするかもしれないので、重要な結果である。

【0011】

その上、予め計算されたパラメタは、複数の予め定義された関係に従ってDCT係数に抽出されるべき画素値を関係づける。関係は非常に簡単であって、その結果、さらにコンピュータの徹底計算を拒否する。

【0012】

望ましくは、計算するステップで使用されるDCT係数はゼロのインデックス値を持っている。さらに、望ましくは、計算するステップで使用されるDCT係数はDCT変換に関して最も高いエネルギーを表しているそれらである。これらの特徴は、画素値を見つけるのに使用される方程式の複雑さが減少して、最もすばらしいコンピュータのコスト節約ができる利点を提供する。

【0013】

その上、オリジナル画像におけるよりも入力画素ブロックあたり少ない数の画素を抽出することが可能であって、その結果、解像度が便利な方法で減少されることを許容する。これは抽出された画像が、パーソナルデジタルアシスタント(PDA)または移動電話に設けられるように、小さいスクリーンに表示のためであるなら役に立つかもしれない。

【0014】

また、別の態様から、本発明はソース画像における画素の値から得られる複数の離散コサイン変換係数を含む信号から画素値を抽出するコンピュータプログラムを提供し、コンピュータプログラムはコンピュータ上で実行されるとき第1の態様の方法にしたがってコンピュータに演算させる命令を含む。

【0015】

そのようなコンピュータプログラムは本発明の方法がコンピュータ上で実行されることを許容する利点に提供する。

【0016】

望ましくは、第2の態様に従ったコンピュータプログラムはコンピュータの読み込み可能な記憶媒体に記憶される。コンピュータの読み込み可能な記憶媒体は磁気的、光学的、磁気-光学的、固体の状態、または技術で知られているいかなる他のコンピュータの読み込み可能な記憶媒体であってもよい。

【0017】

第3の態様から、本発明はまたソース画像において画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する装置を提供し、装置は、

それぞれ値が抽出されるべきである特定の画素に関連づけられた複数の予め計算されたパラメタを記憶する記憶装置手段と、

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算する計算手段とを含む。

【0018】

発明の第3の態様はさらに第1の態様に関して以前に記述されたような同様の特徴と利点を提供する。

【0019】

本発明のさらなる特徴および利点は、同様な部分に同様な参照数字を付した添付図面を参照することにより、例示だけの方法で提示された実施例の以下の記述で明らかになるであろう。

【図面の簡単な説明】

【0020】

【図1】従来技術のMPEGエンコーダとデコーダを示すブロック図である。

【図2】8×8画素ブロックから発生するDCT係数がMPEGコード化の間ジグザグパターンでどのように読まれるかに関する図である。

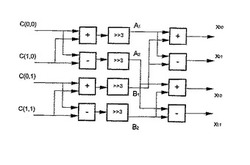

【図3】本発明の第1の実施例によるDCT係数から画素値を抽出するのに必要とした数学の演算を示すブロック図表示である。

【図4】本発明の第2の実施例ににおけるDCT係数から直接画素値を抽出するのに必要とした少なくともいくつかの数学の演算を示すブロック図である。

【図5】本発明の第3の実施例におけるDCT係数から画素値を抽出するのに必要とした数学の演算のいくつかを示すブロック図である。

【図6】本発明の実施例の1つで使用されるかもしれない値のマトリクスである。

【図7(a)】(a)と(b)は一緒に取られるとき、本発明の実施例の1つで使用される値の別のマトリクスである。

【図7(b)】(b)は一緒に取られるとき、本発明の実施例の1つで使用される値の別のマトリクスである。

【図8】本発明の実施例に従った装置のブロック図である。

【図9】本発明の実施例を実行するのに使用されるかもしれない代替の装置のブロック図である。

【図10】実施例にしたがって本発明の演算にかかわるステップを例証するフローチャートである。

【図11】(a)、(b)、および(c)はそれぞれ本発明の第1の実施例を使用して抽出されるフレームである。

【図12】(a)、(b)、および(c)はそれぞれ本発明の第2の実施例によって抽出されたフレームである。

【図13】(a)、(b)、および(c)はそれぞれ本発明の第3の実施例によると抽出される画像フレームである。

【図14】(a)、(b)、および(c)はそれぞれ従来技術の逆離散コサイン変換を使用して生成された画像フレームである。

【発明を実施するための形態】

【0021】

本発明はMPEGとJPEGデコーダに以前に必要とされた逆離散コサイン変換演算を置換する。これは、順DCT変換を分析することにより数学的に得られた一組の予め定義された方程式を使用して達成される。一組の方程式は各画素ブロックについてMPEGとJPEGコード化中に発生されるDCT係数の部分集合に対する画像の画素値に直接関係する。受信されたDCT係数の値を方程式に単に代入することにより、デコードされる画像の画素値は完全な逆離散コサイン変換を引き受ける必要なくMPEGとJPEGデコーダにより直接抽出することができる。したがって、本発明はそれが極めて簡単化されたMPEGデコーダ設計を許容するとき大きな潜在能力があり、それは以前の場合より少ないパワーと少ないコンピュータ的複雑さを必要とする。

【0022】

本発明で使用される方程式の組の由来の理論的基礎は、特定の実施例の記述に従って次に記述される。

【0023】

理論的基礎

DCTベースのMPEG圧縮アルゴリズムは、同じ画像内の近くの画素間の空間相関を有効に探究するために8×8の画像ブロックに働かせる。すでに記述され図1のエンコーダ側で示されたように、典型的な演算はブロックのDCT変換(DCT)と、制御可能なステップサイズ(sz)でのDCT係数の量子化(Q)と、ラン-レングスコーディングとエントロピーコーディングからなる可変長コーディング(VLC)を含む。

【0024】

したがって、MPEG圧縮ビットストリームが与えられると、本発明のビデオ抽出技術はDCT係数領域に入るためまず標準のエントロピーデコーディング(VLD)と再構成(Q*)を必要とする。それは次に逆DCT演算の代わりに一組の非常に簡単な演算を行い、減少された解像度で所望のビデオ画像を抽出する。これらの演算の理論的基礎を次に説明する。

【0025】

このような直接抽出アルゴリズムを設計するため、出発点は本来オリジナルMPEGデコーダで設計されたIDCT演算にあると思われる。しかしながら、本発明の抽出アルゴリズムが主として近似画素情報を抽出することを目的とするので、IDCTそれ自身での出発は困難であることを突き止め、期待された結果を達成することはできない。これはIDCTのための入力値がDCT係数それ自身であり、それらはすでに逆相関されているためである。結果として、どんな近似もひどい歪みを導入することができる。したがって、近くの画素が相関され、重要な冗長が一般に存在するので、任意の近似は望ましくは画素領域でなされるべきである。結果として、本発明のビデオ抽出の出発点は順DCT演算であることが選択された。その上、もちろん発明が所望なら異なったサイズの画素のブロックに容易に適用することができることが理解されるべきであるが、標準のMPEGデコーディング設計を活用するために、我々は議論を8×8画素に制限した。

【0026】

J. Jiang 'A parallel algorithm for 4×4DCT’ Journal of Parallel and Distributed Computing Vol.57、1999、pp257- 269、ISDN: 0743-7315で与えられるDCT定義によると、8×8画素x(i,j)、i,j=0,…,7の1つのブロックは、以下の方程式によってDCT領域C(u,v)、u,v=0,…,7に変換ことができる。

【数1】

【0027】

理論上この方程式はマトリクスフォームで表現することができる。

【0028】

[Cuv]=[A][xij]

ここに、[Cuv]はC00,C01,…C77の順番に配列された64DCT係数を含むベクトルであり、[xij]は8×8画素を含むベクトルである。オリジナル8×8画素の完全な解像度が使用されないか、DCT係数のすべてが結果として所望されないなら、スリムにしたバージョンは以下で表わせられる。

【数2】

【0029】

視覚上質とコンピュータの効率は使用されるDCT係数の選択と数に依存する。

【0030】

我々の設計の都合のために、方程式(1)を以下に再配列することができる。

【数3】

【0031】

三角関数の相互関係から、(2j+1)νπ/16の内側ζ(ν)により表されるすべての角は第1象限にマップされることができる。jがS = [0,7]の内側で変化するとき、角マッピングの詳細は以下のように働かされることができる:

S = S1U S2,ここにS1 = [0,3]およびS2 = [4,7]、我々は以下の式をもつ:

【数4】

【0032】

上記の過程をkについてS1およびS2それぞれに繰り返し、Sはさらに以下で表された4つの部分に分割されることができる:

S=S11 U S12 U S21 U S22 (4)

ここに、S11=[0,1], S12=[2,3], S21=[4,5]およびS22=[6,7]である。

【0033】

これは我々に以下を与える:

【数5】

【0034】

(2)に(5)を代入して、ζ(ν)は以下の形に再配列することができる:

【数6】

【0035】

ν∈[1,7]のとき、式(6)は以下のようになる。

【数7】

【0036】

上記から見られるように、全ての角の内側コサイン関数が第1象限に制限される。それ故、テイラー級数表現がx0=π/4で拡大cos(x)に適用されるとき、厳密な近似が維持されるであろう。そのような実行は我々に以下を与える:

【数8】

【0037】

1より高い次数を有するこれらの項が無視された後、式(11)は以下になる:

【数9】

【0038】

ζ(ν)がその必須の要素としてy/16を含む事実を考慮して、式(12)は対応して以下に配列されることができる:

【数10】

【0039】

ここに、式(7)-(10)から明らかなように、y∈[π,2π,3π,4π,5π,6π,7π]である。それ故, (13)を使用して式(7)- (10)を以下のように書き換えることができる。

【数11】

【0040】

最終的に我々は以下を得る。

【数12】

【0041】

第1の実施例−2×2ブロックでビデオ抽出

本発明の理論上の背景を記述したので、その第1の実施例がこれから記述され、それは8×8ブロック入力毎に2×2ブロックの画素を抽出する。

【0042】

圧縮されたビデオのコンテンツへの速いアクセスを提供して、それぞれのビデオフレームの低コスト抽出を可能にするために、8×8画素のブロックがその横方向と縦方向の両方に沿って2M:M∈[1,3] によりブロックサイズを分割してダウンサンプルされることができる。これはそれぞれ1画素、2×2画素、および4×4画素でブロックが抽出される3つの異なったサイズを我々に与えるだろう。事実上、1画素ブロックで、フレームがDC係数のみを有して抽出されることができ、その結果の値は内側ブロックのすべての画素の平均を表す。画素のブロックが再構成されるとき、これは本質的に他のすべてのAC係数を無視している。アプリケーションによって、そのように抽出されたビデオフレームの品質は、通常容認できないだろう。これは2つの選択だけを我々に残し、2×2画素か4×4画素でのブロックの抽出のいずれかである。2×2画素の抽出は、4つの方程式のグループを解くことを必要とし、4×4画素の抽出は、16の方程式のグループを解くことを必要とする。

【数13】

【0043】

これは重み付けされた足し算として各方程式(18-25)を見なすことによってすることができる。重さの値が方程式の間で異なるが、総合的な平均した画素はほとんど同じと見なすことができ、したがって、対応する4画素は1つの単一値によって平均されかつ表すことができる。さらに、最大のインデックス値がこの場合1であるので、我々は平均画素値を得るのに2つの方程式(18)と(19)のみを必要とし、それは以下の通り配置することができる:

【数14】

【0044】

この抽出が4つの方程式を必要とするだけであるので、4つの係数だけが必要である。しかしながら、抽出されたビデオ品質とコスト節約を最大にするために、以下の2つの条件が選択されたこれらのDCT係数のために満たされるべきである:

(i) 望ましくは、1つのインデックス値が方程式の内側で乗数の数を減少させるためにゼロであるべきである;

(ii) 係数は図2で示されたようにジグザグなルートに沿って最も高い可能なエネルギーを含むべきである。

【0045】

行および列の方向に沿ってそれぞれ方程式(26-27)を適用することによって、我々は以下の4つの数式を引き出すことができる:

【数15】

【0046】

これらの4つの方程式を解いて平均画素が以下の通り得られる:

【数16】

【数17】

【0047】

ブロック実施図が図3に示され、それはデコーダが第1の実施例にしたがって実行しなければならない数学の足し算と引き算を示す。それらは、通常使用される逆DCT変換を置換するために実行しなければならない第1の実施例に従ったデコーダの演算だけであり、演算が画素値Xabを得るために示されたDCT係数値に直接実行されることに注意を要する。MPEGの圧縮されたコードから2×2の平均された画素のブロックが8つの加算と4つの右シフト演算だけで抽出され得ることが明確である。方程式(32)で3つのDCT係数だけが使用されるならば、コンピューティングコストをさらに一層削減することができることに注意を要す。大規模な実験から、この変化はわずかな歪みを被るだけであり、それは多くの場合気付くのは難しい。しかし、今やコンピューティングコストは6つの加算と4つの右シフトまで削減される。したがって、発明の第1の実施例は、MPEGかJPEGデコーダの中にある図1で示される全体のIDCTブロック10を、図3で示される数学の演算を簡単に実行するハードウェアかソフトウェアの機能的な要素に取り替えることができることを提供する。

【0048】

その上、方程式の組が抽出されるべき画素の輝度値だけではなく色光度値にも等しく適用されるかもしれないことに注意すべきである。したがって、特定の画素についてそれぞれの輝度値と色光度値が、それぞれ適切な方程式の組を使用してそれぞれ関連しているDCT係数から直接抽出されるかもしれない。

【0049】

図3はそれらが発明の第1の実施例にしたがって実行される必要がある数学の演算と順序を例証するが、発明がハードウェアかソフトウェアのどちらかで実行されてもよいことが理解されるべきである。なお特に、図3の演算を実行することができるように専用集積回路を設計することを可能にするが、発明の実施例は等しく、EPROM、EEPROM、フィールドプログラマブルゲートアレイ(FPGA)、または同様のものなどのようなプログラマブル論理装置を通して実施されるかもしれないと我々は考える。その上、発明はまた、既存のコンピュータシステム上で実行するようにソフトウェアで容易に実施可能である。図8と9は本発明の実施例のいずれにも適用され得る可能な実施のそれぞれの例を示す。図10はさらに本発明の実施例のいずれによっても実行され得るステップを示す。図8、9、および10をこれから詳細に記述する。

【0050】

図8は本発明のハードウェア実施で必要である機能要素に示すブロック図を示す。本発明が従来技術のMPEGデコーダの逆DCT演算を取り替えることを意図し、このようなデコーダの中で動き補償と同様にラン-レングスおよびエントロピーデコード、および逆量子化のような他の演算が同じなままで残ることに注意を要す。したがって、本発明の中では、MPEGかJPEGデコーダの他の通常の要素が発明への入力として各画素ブロックについて実際のDCT係数を提供することができ、次に、発明は抽出された画素値を出力するであろうと我々は仮定する。

【0051】

したがって、図8で示されるように、発明の実施例のどれかに従った装置は入力としてDCT係数を受け、受けた係数はDCT選択器80へ供給される。DCT選択器80は、画素値を計算するために実際に必要であるそれらの係数を選択して、残りを捨てる。しかしながら、選択器へ供給されたDCT係数が第1の場所で事実上減少された組であることがあるかもしれず、その場合、なにも捨てられない。そのような場合において、減少された組が入力として供給されることが前もって知られているなら、選択器80なしですることが可能であるだろう。したがって、選択器80は発明の演算に不可欠ではない。

【0052】

DCT選択器80は選択されたDCT係数をDCT係数記憶装置82へ供給し、それらはその中に記憶される。DCT係数記憶装置82は画素値計算器84により制御されるように配置され、命令で要求されるとき画素値計算器へDCT係数を渡す。画素値計算器84はさらにパラメタおよび方程式記憶装置86を制御するように配置され、それは例えば、DCT係数値を出力されるべき画素値に直接関係づける第1の実施例における方程式の組(32)のような予定された方程式を記憶する。パラメタおよび方程式記憶装置86は画素値計算器からの命令で要求されるとき、画素値計算器へパラメタと方程式を渡す。

【0053】

画素値計算器84は、方程式記憶装置86に記憶されたパラメタおよび方程式を使用し、DCT係数記憶装置からそれに渡されたDCT係数値から直接画素値を計算するように作動する。そして、計算された画素値は一度計算されたなら画素値計算器84から出力される。

【0054】

図8が本発明のハードウェア実施に関連するように意図されるが、上述されたように、発明の実施例はコンピュータシステム上で実行するソフトウェアでも実施されることができ、コンピュータシステムに関する本発明の不可欠の要素は図9で示される。熟練した者には明らかであるように、図9はコンピュータシステムの作動について必要であるすべての要素を示してはおらず、本発明の実施例によって明確に必要とされるコンピュータシステムのそれらの要素を単に示すように意図される。

【0055】

図9に関して、本発明を実行するコンピュータシステムは数学的かつ論理演算を実行するために配置された中央処理装置90を含み、それは中央データバス94を通して他のシステム要素と通信する。入出力ポート92がデータバス94に接続して提供され、DCT係数の入力、および計算された画素値の出力を可能にする。ソリッドステートメモリ、ハードディスク、光ディスク、または同様のものであるかもしれない記憶媒体96が提供され、それは、制御プログラム98、DCT係数を記憶するための記憶領域97、DCT係数を画素値に直接関連付ける予め定義された方程式およびパラメタを記憶するための記憶領域95と同様に、コンピュータシステムを作動させるために必要とされる普通のオペレーティングシステム要素を記憶する。CPU90上で実行するとき、制御プログラム98は入力として受信されたDCT係数を使用して出力のために画素値を計算するため、CPUを適宜DCT記憶装置97と方程式およびパラメタ記憶装置95にアクセスさせる。

【0056】

図10は図8または9の代替実施のどちらかの演算を示すフローチャートであり、それは発明の実施例のいずれによっても使用されるかもしれない。

【0057】

まず最初に、ステップ10.1において、画素値が抽出されるべきであるDCT係数が受け取られる。これに続いて、ステップ10.2では、画素ブロックのため受け取られた一組のDCT係数が、実際に計算で使用されるそれらのDCT係数のみを含む減少された組であるか、それとも事実上64係数の完全なブロックであるかを見るためにチェックが成される。受け取られたDCT係数がその減少された組であることが決定されたなら、処理はステップ10.4へ進み、さもなく、受け取られたDCT係数が完全な組であるなら処理はステップ10.3に進む。

【0058】

ステップ10.3では、完全な組のDCT係数が受け取られて、部分集合だけが画素値を計算するのに必要であるので、計算に必要とされる係数が選択され、残りは廃棄される。次に処理はステップ10.4に進み、画素値を計算するために必要である係数がDCT係数記憶装置82、または97に記憶される。

【0059】

次に、ステップ10.5において、2つのカウンタa、およびbがゼロに初期化される。これらのカウンタaとbは、計算されるべき各画素値のための適切な方程式を検索するためにパラメタおよび方程式記憶装置86または95に索引をつけるのに使用される。

【0060】

カウンタの初期化に続いて、ステップ10.6ではパラメタおよび方程式記憶装置86または95がアクセスされ、画素x(a,b)のための適切な方程式が検索される。検索された方程式は特定の画素値の計算に必要とされるあるDCT係数を含み、これらの係数はステップ10.7においてDCT係数記憶装置82または97から読まれる。そして、検索された方程式により必要とされた適切なDCT係数と同様に、値が計算されている特定の画素のための方程式が検索され、ステップ10.8において、方程式と係数が画素x(a,b)の値を計算するために使用され、この値は次に記憶される。

【0061】

ステップ10.8に続いて、ステップ10.9では、カウンタaがその最大値a maxに達したかどうかをチェックするため評価がなされる。最大値a maxはDCT係数の入力ブロックとして抽出されるべきである画素ブロックのサイズに依存する。例えば、第1の実施例の場合では、2×2画素ブロックがDCT係数の各8×8ブロック毎に抽出され、したがってa maxは2に等しいだろう。しかしながら、各入力DCT係数ブロック毎に抽出される画素の数がより大きいところではa maxはより大きいサイズの画素ブロックの1つの次元に等しいだろう。

【0062】

aがa maxに等しくないとステップ10.9での評価が決定されるなら、ステップ10.10でカウンタaが増加されて、処理はステップ10.6に戻り、画素x(a,b)のための方程式が検索されて、処理が繰り返される。

【0063】

しかしながら、ステップ10.9でaがその最大値に達したと決定されるなら、処理はステップ10.11に進み、同様の評価がカウンタb、即ち、bがその最大値b maxに達したか否かについて成される。再び、カウンタaのように、カウンタbは与えられた入力DCT係数ブロックについて抽出されるべき画素ブロックの1次元を示して、最大値、例えば、第1の実施例において2、第2と第3の実施例において4の値を取ることができる。

【0064】

bがその最大値に達したことにステップ10.11の評価が戻るならば、それは抽出されるべき全ての画素値が計算された場合に違いなく、その場合に処理はステップ10.14へ進み、画素値はa×bブロックのサイズとして出力される。しかしながら、ステップ10.11の評価が否定であるなら、ステップ10.12においてbが増加されて、ステップ10.13でカウンタaの初期化がゼロへ戻ることにより続けられ、そのとき処理はステップ10.6へ戻る。そのような縮小のループ構成は技術に熟練した者にとってなじみ深いことであり、すべての画素x(a,b)がそれらの適切なそれぞれの方程式によって計算され、発明の実施例にしたがって計算された出力されるべき値の画素を含む出力画素ブロックを許容する。

【0065】

発明のさらなる実施例は今から説明される。さらなる実施例が図8、9、および10のこの組で既に説明されたのと実質的に同じ方法で作動し、DCT係数の入力ブロックあたりの抽出される画素の数(即ち、出力画素値を計算するのに使用される方程式の組に関して異なる)、または実際に計算に必要とされる特定のDCT係数およびその数のいずれかにおいてのみ異なることに注意すべきである。

【0066】

第2の実施例−4×4ブロックにおけるビデオ抽出

発明の第2実施例はこれから記述され、それは8×8入力ブロックから画素の4×4ブロックを抽出する。

【0067】

4×4画素の抽出において、最大のインデックス値が今3であるので、方程式(18-21)だけが必要である。平均演算により、

【数18】

【0068】

方程式(18-21)は同様に以下のように再配列することができる。

【数19】

【0069】

16の方程式のグループを得るために、我々は16のDCT係数C(u,v):(u,v)∈[0,3] を使用する必要がある。各係数について、それぞれ横および縦方向の両方に方程式(33- 36)の1つを単に適用することにより、対応する方程式を引き出すことができる。

【数20】

【0070】

または、効率のために非整数乗数を左手側に置き、方程式(37)は以下のように表現される。

【数21】

【0071】

同様な演算に続いて、すべての16のDCT係数を算定することができる。一次方程式の組を結果としてもたらすこれは以下のマトリクスの形に配置することができる:

【数22】

【0072】

ここに[CT]は式(39)に示される変換された16DCT係数を含むベクトルであり、

【数23】

【数24】

【0073】

その結果、4×4ブロックのビデオ抽出は3つの選択的な概型で実施されることができる。

【0074】

第1の概型は、4つの係数Cuv:(u,v)∈{(0,0),(0,1),(1,0),(2,0)}を考えるだけである。すべての画素は以下の方程式を通して抽出することができる:

【数25】

【0075】

上の方程式の中では、記法Cab > >xはDCT係数Cabの2進の表現をxビットだけ右シフトすることを意味し、その結果、x最下位ビットを有効に捨てる。意図された読者に理解されるように、このような演算は、実行されなければならない実際の算数の割算なしにDCT係数の値を2xにより分割することに近似する。

【0076】

第2の実施例のための不完全な3段実施ブロック図は図4で与えられ、それは上記方程式の組を実施するために必要ないくつかの数学の演算を示す。さらなる演算が上の方程式の組から必要であることは明らかである。第1の実施例と同様に、上の方程式の組がMPEGデコーダで実行されるべき逆DCTの必要性を取り替えて、したがって、発明の第2の実施例はまた、MPEGかJPEGデコーダの中で図1で示された全体のIDCTブロック10が、図4で部分的に示され、上の方程式によって完全に説明された数学の演算を単に実行するハードウェアかソフトウェアの機能的な要素により置換されることができる。この構成は2つの掛け算と28の加算のみを必要とすることが分かるが、抽出されたビデオフレーム品質は2×2ブロックにおける抽出のものよりもはるかに良く、そこでは使用される4分の1が異なっているが、4つの係数がまた使用される。本発明によって得られた結果に関する例は後でより詳細に議論する。

【0077】

第3の実施例

第3の実施例は第2の実施例に似ており、それはDCT係数入力の各8×8ブロックについて4×4ブロックに画素を抽出するが、それが9つの係数、Cuv:(u,v)∈[0,2]を考えるという点において第2の実施例と異なっている。以下の方程式によって16画素を抽出することができる:

【数26】

【0078】

不完全な実施ブロック図が図5で与えられ、それは構造が非常に簡単であることが分かるであろう。第2の実施例と同様に、図5で示されない演算は上記方程式の組から明らかである。第1と第2の実施例の両方と同様に、上の方程式の組がMPEGデコーダで実行されるべき逆DCTの必要性を取り替えて、したがって、発明の第3の実施例はまた、MPEGかJPEGデコーダの中で図1で示された全体のIDCTブロック10が、図5で部分的に示され、上の方程式によって完全に説明された数学の演算を単に実行するハードウェアかソフトウェアの機能的な要素により置換されることができる。第3の実施例のコストを計算する合計が5つの掛算と、42の加算と9の右シフトに達することが分かる。0.176xが(x > > 3)+(x > > 5)によって近似されるなら、計算コストは47の加算と19の右シフト、しかし掛算なしとなる。視覚検査から、これらの2つの実施にはどんなめぼしい差異もない。

【0079】

第4の実施例

第4の実施例は第3の実施例に密接に関連するが、16の係数のすべて、Cuv:(u,v)∈[0,3]を考慮する。しかしながら、すべての16の係数の包含は加算と掛算の数をほとんど倍にする。2つの方式間のほとんど目だたない視覚品質の違いは、計算量のそのような増加を正当化せず、したがって第4の実施例は好ましくない。

【0080】

以前に落とされた他の7つの係数を含むために、抽出方程式は以下の通り変更される:

【数27】

【0081】

前の実施例と同様に、上の方程式の組がMPEGデコーダで実行されるべき逆DCTの必要性を取り替えて、したがって、発明の第4の実施例はまた、MPEGかJPEGデコーダの中で図1で示された全体のIDCTブロック10が、上の方程式によって記述された数学の演算を単に実行するハードウェアかソフトウェアの機能的な要素により置換されることができる。3つの実数0.085、0.042、および0.18がそれぞれ1/16、1/32、および1/8により近似されるならば、上の方程式の実施コストは45の加算と17の右シフト演算である。しかしながら、以上のように、これらの余分な7つの係数の使用はその抽出されたフレームの品質になんらめぼしい改良も起こさないので、この方式はさらなる議論から除かれる。

【0082】

したがって、概要として本発明の実施例に従って、4つのビデオ抽出方式が提供され、その内3つの方式はそれぞれ4、9、および16 DCT係数を使用して4×4ブロックでビデオフレームを抽出し、1つの方式は4つのDCT係数を使用して2×2ブロックでビデオフレームを抽出する。4つの実施例が単なる例であり、より多いまたはより少ない数のDCT係数を使用して異なったサイズのブロックを生成する同様の方式が、ここに記述されたような本発明の数学の原則を適用することによって設計されることができ、かかる代替の方式は本発明の中に取り囲まれるように意図されることが理解されるべきである。

【0083】

結果

本発明の第1乃至第3の実施例により提供される結果は、図11、12、13、および14の各々で示される例示フレーム(a)、(b)、および(c) に関してこれから説明される。なお特に、図11は第1の実施例によって発生された3個のフレームを示し、図12は第2の実施例によって発生された同じ3個のフレームを示し、図13は第3の実施例にしたがって発生されたフレームを示す。比較のために、図14は従来技術の完全なIDCTを使用して抽出された同じフレームを示し、同じサイズで抽出されたフレームと比較のために288×352のオリジナルサイズから2だけダウンサンプルされている。

【0084】

上記のような画像を発生させるために、各実施例はインターネットからダウンロードされたオリジナルのMPEG-2デコーダのCソースコードに基づくMicrosoft(登録商標)Visual C+ +環境で実施された。したがってこの点で、特定の実施は以前に図9に関して説明されたソフトウェア実施に対応している。公平な比較を確実にするために、さらに各フレームは同じサイズに拡大され、この拡大は必要なサイズに達するまで横と縦方向の両方に沿って同じ画素を繰り返すことにより達成された。したがって、2×2画素ブロックがそれへのDCT係数入力の各8×8ブロックのために抽出されるところでは、抽出された画素をソース画像と同じサイズに拡大するために、各画素は縦4回および横4回繰り返され、16の同じ画素をもたらす。4×4ブロックが抽出されたところでは、各画素は各方向に2回だけ繰り返される必要がある。発明によって提供される画素を単に繰り返して拡大するこのモードは計算上分かり易く、非常に少ない間接費を支持し、その結果、発明の直接画素抽出の技術を使用して獲得されるコンピュータの効率の増加を危険にさらすことなく、拡大が実行されることを許容する。

【0085】

静止ビデオフレーム間の広範囲の再生と比較の後に、抽出されたビデオがその抽出されたサイズで再生されるならば、視覚認識によるビデオ画像の品質が64のDCT係数で逆圧縮された完全なIDCTのそれとほとんど同じであることを我々は観測した。拡大されたサイズの再生に関しては、わずかな歪みがいくつかのフレームに観察されたが、品質は許容できる。例えば、第1の実施例によって発生された図11から、解像度が他の例よりもかなり劣ることが分かるであろう。しかしながら、第3の実施例を使用して発生される図13からは、完全なIDCTを使用して発生されたフレームとほとんどどんな顕著な違いも起こらない。

【0086】

実験結果と視覚比較から、ビデオ抽出アルゴリズムのために以下のさらなる結論を下すことができる:

・第1と第3の実施例の2つのビデオ抽出アルゴリズムが、抽出されたサイズの再生で、即ち、第1の実施例に関してH/4×W/4、および第3の実施例に関してH/2×W/2でほぼ完全に逆圧縮ビデオ画像品質を達成する。

【0087】

・第2の実施例に関しては、抽出されたサイズの再生は完全に逆圧縮されたビデオフレームと比較して許容できる知覚の品質を持っており、第1の実施例のそれより良い品質を達成する。4分の1がC20対C11で異なっているが、両方の方式が4つのDCT係数を使用することに注意を要す。

【0088】

・2×2ブロックでのビデオ抽出、即ち第1の実施例はH/2×W/2の再生について許容できる知覚の品質を維持する。

【0089】

・4×4ブロックでのビデオ抽出、即ち第3の実施例は許容できる知覚の品質を有してフルサイズビデオフレーム再生を与えることができる。

【0090】

例証目的のために、研究された3つのビデオ抽出方式と文献で引用された他の速いIDCTコンピューティングアルゴリズムに関してコンピュータのコスト(しかし、複雑さでない)を表1にまとめた。

【表1】

【0091】

表において、参照[a],[b],および[c]はそれぞれ従来発行された論文:M. Vetterli,“Fast 2-D discrete cosine transform”,in Proc. ICASSP’85,Mar.1985; P. Duhamel and C. Guillemot,“Polynomial transform computation of 2-D DCT”,in Proc. ICASSP’90,pp.1515-1518, Apr. 1990;およびN.I.Cho and S.U.Lee,“Fast algorithm and implementation of 2-D discrete cosine transform”,IEEE Trans.Circuits Syst., vol.CAS-40, pp.259-266,Apr.1991,に関連し、それらは各々速い逆DCT演算に関する従来技術の例について説明する。

【0092】

表の結果は以下の通り批評される: 参照[a]乃至[c] での速いIDCT実施のための請求は、ソフトウェア実施と同様に理論上の試験によって慎重に確かめられる必要があることに特に注意を要す。速い速度は低い実施の複雑さを必ずしも意味するわけではない。速いIDCTコンピューティングの大多数はまだ高い計算量を被っている。即ち、速さが掛算と足し算の数によってのみ測定されるので、それらの係数または画素の再順序付け、多量の実数などを予め計算しかつ予め記憶することのような他の背景計算が無視された。その結果、大きいメモリ消費が必要とされることになった。そこで、これらの公開された速いIDCTコンピューティングアルゴリズムの大部分は価格を支払わないで速くすることはできない。対照的に、ここに発明された技術は、それらの実施の構造が非常に簡単であるので、DCTに関する少しも知識のない者でも容易について行くことができ、本当に低いコストを持つように容易に確かめることができる。どんな背景計算もなく、それらの係数または画素のなんら他の移動もなく、付加的メモリ消費もない。その上、第3の実施例のために必要とされるわずか5つの掛け算が10の右シフトに置換されることができる。これは、どんな掛算も全く必要でないことを意味する。しかも、知覚の品質は抽出されたサイズ表示において完全に逆圧縮されているものに拮抗しかつ非常に近い。我々はどんなに速いIDCTベースの速いコンピューティングもこれを達成することができたとは思わない。

【0093】

したがって、本発明は、逆DCTを受ける必要がなく、コード化されたMPEGかJPEG画像のDCT係数から直接抽出されるべき画素値を許容する方法と装置を提示する。発明のコンピュータの効率は従来技術の速いIDCTの技術に関して非常に高められ、発生されたDCT係数の部分集合だけを使用する能力は、MPEGとJPEGコード化画像およびビデオの今後の伝送に必要である帯域幅が非常に減少されるであろうことを意味する。発明は多くの潜在的な将来の応用があり、我々はDCT領域からの画像の速くて効率的な抽出を達成することが望ましいどんな将来の装置にも、発明により提供される技術の応用を考える。

【技術分野】

【0001】

本発明は離散コサイン変換(DCT)係数から直接画素値を抽出する、特に逆DCT変換を引き受ける必要はなくてそのような値を抽出する方法、装置、およびコンピュータプログラムに関連する。

【背景技術】

【0002】

インターネットの増殖と電子商取引におけるマルチメディア情報技術の急速な展開と、そして様々なビジネスセクターに亘って、デジタル記憶装置のコストは想像を絶する速度で減少されている。テキストフォームだけでなく、ディジタル画像、デジタルビデオ、立体コンピュータグラフィックス、および他の多くのディジタルデータ形式のフォームに豊かなコンテンツ情報を記憶することが現在可能である。ワールドワイドウエブの到達の後に、インターネットアクセス可能な情報の宝庫がますます共通になるように、情報交換および創造が革命的変化の下にある。統制に関連する情報の全体のセクターの下での1つのインパクトは、効率、有効性、および丈夫さを有してマルチメディア情報のコンテンツを扱って、管理して、記憶するために新しい技術の展開の必要性である。この処理中に、何百万もの画像、ビデオクリップが取扱われ、調査され、索引をつけられ、検索されることができるが、それらの大部分が既に圧縮形式であることができる。現在使用されているすべての圧縮形式の中では、離散コサイン変換(DCT)が以下の理由で広く採用される:(a) 離散コサイン変換が最適のKarhunen-Loeve変換(KLT)に近い;(b)DCTは信号独立であり、KLTの短所を取除くことができる;そして(c)それは本当の係数を有し、速いアルゴリズムは実際に効率的である実施のために容易に利用可能である。したがって、DCTは画像/ビデオ圧縮規格(JPEG/MPEG、およびH261/H263)で広く使用される(J. Jiang “A parallel algorithm for 4×4 DCT” Journal of Parallel and Distributed Computing, Vol.57、1999、pp 257-269、ISDN: 0743-7315 and V.Bhaskaran and K.Konstanti, Image and Video Comptession Standards: Algorithms and Architectures, Kluwer Academic Publications,Boston, 1997参照)。この文脈の下では、圧縮領域または内部データ圧縮のコンテンツ記述における画像処理の研究の新たな波は、A.Abdel-Malek and J.E.Hershey “Feature cueing in the discrete cosine domain”, Journal of Electronic Imaging, Vol.3、pp. 71-80, Jan, 1994, B.Shen and Ishwar K.Sethi,“Direct feature extraction from compressed images”, SPIE: Vol.2670 Storage & Retrieval for Image and Video Databases IV, 1996,and R.Reeve, K.Kubik and W.Osberger,”Texture characterization of compressed aerial images using DCT coefficients“,Proc. Of SPIE: Storge and Retrival for Image and Video Databases V, Vol.3022、pp. 398-407,Feb, 1997に記述されるように、世界的な研究共同体で始められている。

【0003】

上記から明らかであるように、動きと静止画像のMPEGとJPEGコード化は技術において良く知られており、共通のエンコーダとデコーダ構造は図1で示される。MPEG(およびJPEG)画像をコード化するために、ソース画素画像は次に離散コサイン変換(DCT)を受けさせる8×8ブロックに最初に分割される。これは、頂部左隅にDC構成要素を有し、画素ブロックをとおして頂部左から外側へ分配された増大するより高次のAC構成要素を有する64のDCT係数をもたらす。これらの構成要素は次に、コードブックから2進コードを使用して量子化されてそれぞれそれらの実数DCT係数を表し、またその値が量子化閾値以下であるそれらの係数を廃棄し、次にジグザグパターン(図2で示されるように)に係数を取ることによって連続のデータワードに変換され、その結果ゼロに量子化された構成要素が効率的にラン-レングスコード化されることができ、伝送の前にエントロピーコード化により続けられる。この過程は画像の8×8画素ブロック毎に繰り返される。

【0004】

デコーダで画像をデコードするために、通常逆の過程が実行され、即ちエントロピーとラン-レングスは受信されたデータをデコードして、図2のジグザグパターンを逆にすることによってDCT係数を8×8ブロックに再構成し、逆DCT(IDCT)を実行して実際の画素値を得る。逆DCTステップは計算上徹底的であり、実行するのに時間とパワーを必要とする。通常、標準の完全な逆圧縮(IDCT)のために、計算コストは4096の掛け算と4032の足し算であるが、いくつかの実用的な実施では8×8画素ブロックあたり1024の掛け算と896の足し算だけであるかもしれない(さらなる比較のために我々の“結果”セクションの表を参照)。

【0005】

画像処理の領域は何年間も研究開発の焦点であった(増進、細分化、特徴抽出、パターン分類などのようなタスクで代表される)が、そのような開発は画素領域にすべて存在した。DCTベースのデータ圧縮が伝送効率と限られた記憶装置スペースの管理を大いに改良している間、圧縮された視覚データは、表示さらに処理または印刷される前に画素領域に戻って処理されなければならない。いくつかのしばしば採用される処理機能は、スケーリング、フィルタリング、回転、置換、特徴抽出、および分類を含んでいる。この終わりに、通常のアプローチは、そのような既存のアルゴリズムを適用することができる前にDCT領域から画素領域へデータを変換(逆圧縮)しなければならない。そのような処理は、すでに与えられたコンピュータの徹底形態から明らかであるように、画像処理と圧縮の全体の連鎖におけるオーバーヘッド計算コストと記憶装置コストの重要な増加に通じる。

【発明の概要】

【0006】

したがって、画像操作(探索、フィルタリング、表示など)が実行されなければならないときはいつもIDCT操作を使用して各画像を完全に逆圧縮する必要はなく、処理されるべき大規模画像メディアを許容するそれほど計算上徹底的でない手段が産業の中で強い必要性がある。

【0007】

本発明は、MPEGまたはJPEGをデコードするために逆離散コサイン変換を実行する必要性を取り除く方法、コンピュータプログラムおよび装置を提供することにより上記の問題を処理する。すなわち、図1で示される従来技術のデコーダに関して、発明は逆離散コサイン変換ブロック10を置き換えて、一組のパラメタを通して抽出された画素値を直接DCT係数に関係付ける一組の予め定義された、簡単な一次方程式の適用により、画素値がDCT係数から直接抽出されることを許容する方法、コンピュータプログラム、および装置を提供する。したがって、MPEGまたはJPEGのコード化された領域からソース画像を抽出するために、すべてのデコーダの必要な計算が入力DCT係数の与えられた組について予め設定された組の方程式の結果であり、したがって、それは、もはや付随のコンピュータの徹底計算を要する逆DCT変換を実行する必要はない。

【0008】

上記の観点において、本発明に従った第1の態様は、ソース画像における画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する方法が提供され、方法は、

それぞれ値が抽出されるべきである特定の画素に関連づけられる複数の予め計算されたパラメタを記憶し;

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算するステップを含む。

【0009】

1つ以上のDCT係数と共に予め計算されたパラメタを使用して画素値を計算する能力は、コンピュータの徹底計算が非常に減少することを意味する。採用される特定の実施に依存して、オリジナルの画像による画素の8×8ブロックについて、MPEGまたはJPEGコード化バージョンから最小8つの加算と4つの割算で画素値を抽出することが可能である。明らかに、これは以前に使用された完全な逆離散コサイン変換と比較して重要な減少である。

【0010】

その上、望ましくは、DCT係数の予め選択された部分集合は、画素値を計算するのに使用される。特定の実施例から明らかになるように、どんな特定の画素ブロックからのDCT係数の比較的小さい部分集合だけでも本発明の演算に必要とされる。一実施例では、最小4つの係数が必要であるが、他の実施例では多分9、または16の係数で使用される。どの実施例が選ばれても、使用されるDCT係数の数が完全な逆離散コサイン変換の実施の中で通常使用される64の係数より実質的に少ないことが認識されるであろう。これは非常に低い帯域幅ビデオ伝送を容易にするかもしれないので、重要な結果である。

【0011】

その上、予め計算されたパラメタは、複数の予め定義された関係に従ってDCT係数に抽出されるべき画素値を関係づける。関係は非常に簡単であって、その結果、さらにコンピュータの徹底計算を拒否する。

【0012】

望ましくは、計算するステップで使用されるDCT係数はゼロのインデックス値を持っている。さらに、望ましくは、計算するステップで使用されるDCT係数はDCT変換に関して最も高いエネルギーを表しているそれらである。これらの特徴は、画素値を見つけるのに使用される方程式の複雑さが減少して、最もすばらしいコンピュータのコスト節約ができる利点を提供する。

【0013】

その上、オリジナル画像におけるよりも入力画素ブロックあたり少ない数の画素を抽出することが可能であって、その結果、解像度が便利な方法で減少されることを許容する。これは抽出された画像が、パーソナルデジタルアシスタント(PDA)または移動電話に設けられるように、小さいスクリーンに表示のためであるなら役に立つかもしれない。

【0014】

また、別の態様から、本発明はソース画像における画素の値から得られる複数の離散コサイン変換係数を含む信号から画素値を抽出するコンピュータプログラムを提供し、コンピュータプログラムはコンピュータ上で実行されるとき第1の態様の方法にしたがってコンピュータに演算させる命令を含む。

【0015】

そのようなコンピュータプログラムは本発明の方法がコンピュータ上で実行されることを許容する利点に提供する。

【0016】

望ましくは、第2の態様に従ったコンピュータプログラムはコンピュータの読み込み可能な記憶媒体に記憶される。コンピュータの読み込み可能な記憶媒体は磁気的、光学的、磁気-光学的、固体の状態、または技術で知られているいかなる他のコンピュータの読み込み可能な記憶媒体であってもよい。

【0017】

第3の態様から、本発明はまたソース画像において画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する装置を提供し、装置は、

それぞれ値が抽出されるべきである特定の画素に関連づけられた複数の予め計算されたパラメタを記憶する記憶装置手段と、

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算する計算手段とを含む。

【0018】

発明の第3の態様はさらに第1の態様に関して以前に記述されたような同様の特徴と利点を提供する。

【0019】

本発明のさらなる特徴および利点は、同様な部分に同様な参照数字を付した添付図面を参照することにより、例示だけの方法で提示された実施例の以下の記述で明らかになるであろう。

【図面の簡単な説明】

【0020】

【図1】従来技術のMPEGエンコーダとデコーダを示すブロック図である。

【図2】8×8画素ブロックから発生するDCT係数がMPEGコード化の間ジグザグパターンでどのように読まれるかに関する図である。

【図3】本発明の第1の実施例によるDCT係数から画素値を抽出するのに必要とした数学の演算を示すブロック図表示である。

【図4】本発明の第2の実施例ににおけるDCT係数から直接画素値を抽出するのに必要とした少なくともいくつかの数学の演算を示すブロック図である。

【図5】本発明の第3の実施例におけるDCT係数から画素値を抽出するのに必要とした数学の演算のいくつかを示すブロック図である。

【図6】本発明の実施例の1つで使用されるかもしれない値のマトリクスである。

【図7(a)】(a)と(b)は一緒に取られるとき、本発明の実施例の1つで使用される値の別のマトリクスである。

【図7(b)】(b)は一緒に取られるとき、本発明の実施例の1つで使用される値の別のマトリクスである。

【図8】本発明の実施例に従った装置のブロック図である。

【図9】本発明の実施例を実行するのに使用されるかもしれない代替の装置のブロック図である。

【図10】実施例にしたがって本発明の演算にかかわるステップを例証するフローチャートである。

【図11】(a)、(b)、および(c)はそれぞれ本発明の第1の実施例を使用して抽出されるフレームである。

【図12】(a)、(b)、および(c)はそれぞれ本発明の第2の実施例によって抽出されたフレームである。

【図13】(a)、(b)、および(c)はそれぞれ本発明の第3の実施例によると抽出される画像フレームである。

【図14】(a)、(b)、および(c)はそれぞれ従来技術の逆離散コサイン変換を使用して生成された画像フレームである。

【発明を実施するための形態】

【0021】

本発明はMPEGとJPEGデコーダに以前に必要とされた逆離散コサイン変換演算を置換する。これは、順DCT変換を分析することにより数学的に得られた一組の予め定義された方程式を使用して達成される。一組の方程式は各画素ブロックについてMPEGとJPEGコード化中に発生されるDCT係数の部分集合に対する画像の画素値に直接関係する。受信されたDCT係数の値を方程式に単に代入することにより、デコードされる画像の画素値は完全な逆離散コサイン変換を引き受ける必要なくMPEGとJPEGデコーダにより直接抽出することができる。したがって、本発明はそれが極めて簡単化されたMPEGデコーダ設計を許容するとき大きな潜在能力があり、それは以前の場合より少ないパワーと少ないコンピュータ的複雑さを必要とする。

【0022】

本発明で使用される方程式の組の由来の理論的基礎は、特定の実施例の記述に従って次に記述される。

【0023】

理論的基礎

DCTベースのMPEG圧縮アルゴリズムは、同じ画像内の近くの画素間の空間相関を有効に探究するために8×8の画像ブロックに働かせる。すでに記述され図1のエンコーダ側で示されたように、典型的な演算はブロックのDCT変換(DCT)と、制御可能なステップサイズ(sz)でのDCT係数の量子化(Q)と、ラン-レングスコーディングとエントロピーコーディングからなる可変長コーディング(VLC)を含む。

【0024】

したがって、MPEG圧縮ビットストリームが与えられると、本発明のビデオ抽出技術はDCT係数領域に入るためまず標準のエントロピーデコーディング(VLD)と再構成(Q*)を必要とする。それは次に逆DCT演算の代わりに一組の非常に簡単な演算を行い、減少された解像度で所望のビデオ画像を抽出する。これらの演算の理論的基礎を次に説明する。

【0025】

このような直接抽出アルゴリズムを設計するため、出発点は本来オリジナルMPEGデコーダで設計されたIDCT演算にあると思われる。しかしながら、本発明の抽出アルゴリズムが主として近似画素情報を抽出することを目的とするので、IDCTそれ自身での出発は困難であることを突き止め、期待された結果を達成することはできない。これはIDCTのための入力値がDCT係数それ自身であり、それらはすでに逆相関されているためである。結果として、どんな近似もひどい歪みを導入することができる。したがって、近くの画素が相関され、重要な冗長が一般に存在するので、任意の近似は望ましくは画素領域でなされるべきである。結果として、本発明のビデオ抽出の出発点は順DCT演算であることが選択された。その上、もちろん発明が所望なら異なったサイズの画素のブロックに容易に適用することができることが理解されるべきであるが、標準のMPEGデコーディング設計を活用するために、我々は議論を8×8画素に制限した。

【0026】

J. Jiang 'A parallel algorithm for 4×4DCT’ Journal of Parallel and Distributed Computing Vol.57、1999、pp257- 269、ISDN: 0743-7315で与えられるDCT定義によると、8×8画素x(i,j)、i,j=0,…,7の1つのブロックは、以下の方程式によってDCT領域C(u,v)、u,v=0,…,7に変換ことができる。

【数1】

【0027】

理論上この方程式はマトリクスフォームで表現することができる。

【0028】

[Cuv]=[A][xij]

ここに、[Cuv]はC00,C01,…C77の順番に配列された64DCT係数を含むベクトルであり、[xij]は8×8画素を含むベクトルである。オリジナル8×8画素の完全な解像度が使用されないか、DCT係数のすべてが結果として所望されないなら、スリムにしたバージョンは以下で表わせられる。

【数2】

【0029】

視覚上質とコンピュータの効率は使用されるDCT係数の選択と数に依存する。

【0030】

我々の設計の都合のために、方程式(1)を以下に再配列することができる。

【数3】

【0031】

三角関数の相互関係から、(2j+1)νπ/16の内側ζ(ν)により表されるすべての角は第1象限にマップされることができる。jがS = [0,7]の内側で変化するとき、角マッピングの詳細は以下のように働かされることができる:

S = S1U S2,ここにS1 = [0,3]およびS2 = [4,7]、我々は以下の式をもつ:

【数4】

【0032】

上記の過程をkについてS1およびS2それぞれに繰り返し、Sはさらに以下で表された4つの部分に分割されることができる:

S=S11 U S12 U S21 U S22 (4)

ここに、S11=[0,1], S12=[2,3], S21=[4,5]およびS22=[6,7]である。

【0033】

これは我々に以下を与える:

【数5】

【0034】

(2)に(5)を代入して、ζ(ν)は以下の形に再配列することができる:

【数6】

【0035】

ν∈[1,7]のとき、式(6)は以下のようになる。

【数7】

【0036】

上記から見られるように、全ての角の内側コサイン関数が第1象限に制限される。それ故、テイラー級数表現がx0=π/4で拡大cos(x)に適用されるとき、厳密な近似が維持されるであろう。そのような実行は我々に以下を与える:

【数8】

【0037】

1より高い次数を有するこれらの項が無視された後、式(11)は以下になる:

【数9】

【0038】

ζ(ν)がその必須の要素としてy/16を含む事実を考慮して、式(12)は対応して以下に配列されることができる:

【数10】

【0039】

ここに、式(7)-(10)から明らかなように、y∈[π,2π,3π,4π,5π,6π,7π]である。それ故, (13)を使用して式(7)- (10)を以下のように書き換えることができる。

【数11】

【0040】

最終的に我々は以下を得る。

【数12】

【0041】

第1の実施例−2×2ブロックでビデオ抽出

本発明の理論上の背景を記述したので、その第1の実施例がこれから記述され、それは8×8ブロック入力毎に2×2ブロックの画素を抽出する。

【0042】

圧縮されたビデオのコンテンツへの速いアクセスを提供して、それぞれのビデオフレームの低コスト抽出を可能にするために、8×8画素のブロックがその横方向と縦方向の両方に沿って2M:M∈[1,3] によりブロックサイズを分割してダウンサンプルされることができる。これはそれぞれ1画素、2×2画素、および4×4画素でブロックが抽出される3つの異なったサイズを我々に与えるだろう。事実上、1画素ブロックで、フレームがDC係数のみを有して抽出されることができ、その結果の値は内側ブロックのすべての画素の平均を表す。画素のブロックが再構成されるとき、これは本質的に他のすべてのAC係数を無視している。アプリケーションによって、そのように抽出されたビデオフレームの品質は、通常容認できないだろう。これは2つの選択だけを我々に残し、2×2画素か4×4画素でのブロックの抽出のいずれかである。2×2画素の抽出は、4つの方程式のグループを解くことを必要とし、4×4画素の抽出は、16の方程式のグループを解くことを必要とする。

【数13】

【0043】

これは重み付けされた足し算として各方程式(18-25)を見なすことによってすることができる。重さの値が方程式の間で異なるが、総合的な平均した画素はほとんど同じと見なすことができ、したがって、対応する4画素は1つの単一値によって平均されかつ表すことができる。さらに、最大のインデックス値がこの場合1であるので、我々は平均画素値を得るのに2つの方程式(18)と(19)のみを必要とし、それは以下の通り配置することができる:

【数14】

【0044】

この抽出が4つの方程式を必要とするだけであるので、4つの係数だけが必要である。しかしながら、抽出されたビデオ品質とコスト節約を最大にするために、以下の2つの条件が選択されたこれらのDCT係数のために満たされるべきである:

(i) 望ましくは、1つのインデックス値が方程式の内側で乗数の数を減少させるためにゼロであるべきである;

(ii) 係数は図2で示されたようにジグザグなルートに沿って最も高い可能なエネルギーを含むべきである。

【0045】

行および列の方向に沿ってそれぞれ方程式(26-27)を適用することによって、我々は以下の4つの数式を引き出すことができる:

【数15】

【0046】

これらの4つの方程式を解いて平均画素が以下の通り得られる:

【数16】

【数17】

【0047】

ブロック実施図が図3に示され、それはデコーダが第1の実施例にしたがって実行しなければならない数学の足し算と引き算を示す。それらは、通常使用される逆DCT変換を置換するために実行しなければならない第1の実施例に従ったデコーダの演算だけであり、演算が画素値Xabを得るために示されたDCT係数値に直接実行されることに注意を要する。MPEGの圧縮されたコードから2×2の平均された画素のブロックが8つの加算と4つの右シフト演算だけで抽出され得ることが明確である。方程式(32)で3つのDCT係数だけが使用されるならば、コンピューティングコストをさらに一層削減することができることに注意を要す。大規模な実験から、この変化はわずかな歪みを被るだけであり、それは多くの場合気付くのは難しい。しかし、今やコンピューティングコストは6つの加算と4つの右シフトまで削減される。したがって、発明の第1の実施例は、MPEGかJPEGデコーダの中にある図1で示される全体のIDCTブロック10を、図3で示される数学の演算を簡単に実行するハードウェアかソフトウェアの機能的な要素に取り替えることができることを提供する。

【0048】

その上、方程式の組が抽出されるべき画素の輝度値だけではなく色光度値にも等しく適用されるかもしれないことに注意すべきである。したがって、特定の画素についてそれぞれの輝度値と色光度値が、それぞれ適切な方程式の組を使用してそれぞれ関連しているDCT係数から直接抽出されるかもしれない。

【0049】

図3はそれらが発明の第1の実施例にしたがって実行される必要がある数学の演算と順序を例証するが、発明がハードウェアかソフトウェアのどちらかで実行されてもよいことが理解されるべきである。なお特に、図3の演算を実行することができるように専用集積回路を設計することを可能にするが、発明の実施例は等しく、EPROM、EEPROM、フィールドプログラマブルゲートアレイ(FPGA)、または同様のものなどのようなプログラマブル論理装置を通して実施されるかもしれないと我々は考える。その上、発明はまた、既存のコンピュータシステム上で実行するようにソフトウェアで容易に実施可能である。図8と9は本発明の実施例のいずれにも適用され得る可能な実施のそれぞれの例を示す。図10はさらに本発明の実施例のいずれによっても実行され得るステップを示す。図8、9、および10をこれから詳細に記述する。

【0050】

図8は本発明のハードウェア実施で必要である機能要素に示すブロック図を示す。本発明が従来技術のMPEGデコーダの逆DCT演算を取り替えることを意図し、このようなデコーダの中で動き補償と同様にラン-レングスおよびエントロピーデコード、および逆量子化のような他の演算が同じなままで残ることに注意を要す。したがって、本発明の中では、MPEGかJPEGデコーダの他の通常の要素が発明への入力として各画素ブロックについて実際のDCT係数を提供することができ、次に、発明は抽出された画素値を出力するであろうと我々は仮定する。

【0051】

したがって、図8で示されるように、発明の実施例のどれかに従った装置は入力としてDCT係数を受け、受けた係数はDCT選択器80へ供給される。DCT選択器80は、画素値を計算するために実際に必要であるそれらの係数を選択して、残りを捨てる。しかしながら、選択器へ供給されたDCT係数が第1の場所で事実上減少された組であることがあるかもしれず、その場合、なにも捨てられない。そのような場合において、減少された組が入力として供給されることが前もって知られているなら、選択器80なしですることが可能であるだろう。したがって、選択器80は発明の演算に不可欠ではない。

【0052】

DCT選択器80は選択されたDCT係数をDCT係数記憶装置82へ供給し、それらはその中に記憶される。DCT係数記憶装置82は画素値計算器84により制御されるように配置され、命令で要求されるとき画素値計算器へDCT係数を渡す。画素値計算器84はさらにパラメタおよび方程式記憶装置86を制御するように配置され、それは例えば、DCT係数値を出力されるべき画素値に直接関係づける第1の実施例における方程式の組(32)のような予定された方程式を記憶する。パラメタおよび方程式記憶装置86は画素値計算器からの命令で要求されるとき、画素値計算器へパラメタと方程式を渡す。

【0053】

画素値計算器84は、方程式記憶装置86に記憶されたパラメタおよび方程式を使用し、DCT係数記憶装置からそれに渡されたDCT係数値から直接画素値を計算するように作動する。そして、計算された画素値は一度計算されたなら画素値計算器84から出力される。

【0054】

図8が本発明のハードウェア実施に関連するように意図されるが、上述されたように、発明の実施例はコンピュータシステム上で実行するソフトウェアでも実施されることができ、コンピュータシステムに関する本発明の不可欠の要素は図9で示される。熟練した者には明らかであるように、図9はコンピュータシステムの作動について必要であるすべての要素を示してはおらず、本発明の実施例によって明確に必要とされるコンピュータシステムのそれらの要素を単に示すように意図される。

【0055】

図9に関して、本発明を実行するコンピュータシステムは数学的かつ論理演算を実行するために配置された中央処理装置90を含み、それは中央データバス94を通して他のシステム要素と通信する。入出力ポート92がデータバス94に接続して提供され、DCT係数の入力、および計算された画素値の出力を可能にする。ソリッドステートメモリ、ハードディスク、光ディスク、または同様のものであるかもしれない記憶媒体96が提供され、それは、制御プログラム98、DCT係数を記憶するための記憶領域97、DCT係数を画素値に直接関連付ける予め定義された方程式およびパラメタを記憶するための記憶領域95と同様に、コンピュータシステムを作動させるために必要とされる普通のオペレーティングシステム要素を記憶する。CPU90上で実行するとき、制御プログラム98は入力として受信されたDCT係数を使用して出力のために画素値を計算するため、CPUを適宜DCT記憶装置97と方程式およびパラメタ記憶装置95にアクセスさせる。

【0056】

図10は図8または9の代替実施のどちらかの演算を示すフローチャートであり、それは発明の実施例のいずれによっても使用されるかもしれない。

【0057】

まず最初に、ステップ10.1において、画素値が抽出されるべきであるDCT係数が受け取られる。これに続いて、ステップ10.2では、画素ブロックのため受け取られた一組のDCT係数が、実際に計算で使用されるそれらのDCT係数のみを含む減少された組であるか、それとも事実上64係数の完全なブロックであるかを見るためにチェックが成される。受け取られたDCT係数がその減少された組であることが決定されたなら、処理はステップ10.4へ進み、さもなく、受け取られたDCT係数が完全な組であるなら処理はステップ10.3に進む。

【0058】

ステップ10.3では、完全な組のDCT係数が受け取られて、部分集合だけが画素値を計算するのに必要であるので、計算に必要とされる係数が選択され、残りは廃棄される。次に処理はステップ10.4に進み、画素値を計算するために必要である係数がDCT係数記憶装置82、または97に記憶される。

【0059】

次に、ステップ10.5において、2つのカウンタa、およびbがゼロに初期化される。これらのカウンタaとbは、計算されるべき各画素値のための適切な方程式を検索するためにパラメタおよび方程式記憶装置86または95に索引をつけるのに使用される。

【0060】

カウンタの初期化に続いて、ステップ10.6ではパラメタおよび方程式記憶装置86または95がアクセスされ、画素x(a,b)のための適切な方程式が検索される。検索された方程式は特定の画素値の計算に必要とされるあるDCT係数を含み、これらの係数はステップ10.7においてDCT係数記憶装置82または97から読まれる。そして、検索された方程式により必要とされた適切なDCT係数と同様に、値が計算されている特定の画素のための方程式が検索され、ステップ10.8において、方程式と係数が画素x(a,b)の値を計算するために使用され、この値は次に記憶される。

【0061】

ステップ10.8に続いて、ステップ10.9では、カウンタaがその最大値a maxに達したかどうかをチェックするため評価がなされる。最大値a maxはDCT係数の入力ブロックとして抽出されるべきである画素ブロックのサイズに依存する。例えば、第1の実施例の場合では、2×2画素ブロックがDCT係数の各8×8ブロック毎に抽出され、したがってa maxは2に等しいだろう。しかしながら、各入力DCT係数ブロック毎に抽出される画素の数がより大きいところではa maxはより大きいサイズの画素ブロックの1つの次元に等しいだろう。

【0062】

aがa maxに等しくないとステップ10.9での評価が決定されるなら、ステップ10.10でカウンタaが増加されて、処理はステップ10.6に戻り、画素x(a,b)のための方程式が検索されて、処理が繰り返される。

【0063】

しかしながら、ステップ10.9でaがその最大値に達したと決定されるなら、処理はステップ10.11に進み、同様の評価がカウンタb、即ち、bがその最大値b maxに達したか否かについて成される。再び、カウンタaのように、カウンタbは与えられた入力DCT係数ブロックについて抽出されるべき画素ブロックの1次元を示して、最大値、例えば、第1の実施例において2、第2と第3の実施例において4の値を取ることができる。

【0064】

bがその最大値に達したことにステップ10.11の評価が戻るならば、それは抽出されるべき全ての画素値が計算された場合に違いなく、その場合に処理はステップ10.14へ進み、画素値はa×bブロックのサイズとして出力される。しかしながら、ステップ10.11の評価が否定であるなら、ステップ10.12においてbが増加されて、ステップ10.13でカウンタaの初期化がゼロへ戻ることにより続けられ、そのとき処理はステップ10.6へ戻る。そのような縮小のループ構成は技術に熟練した者にとってなじみ深いことであり、すべての画素x(a,b)がそれらの適切なそれぞれの方程式によって計算され、発明の実施例にしたがって計算された出力されるべき値の画素を含む出力画素ブロックを許容する。

【0065】

発明のさらなる実施例は今から説明される。さらなる実施例が図8、9、および10のこの組で既に説明されたのと実質的に同じ方法で作動し、DCT係数の入力ブロックあたりの抽出される画素の数(即ち、出力画素値を計算するのに使用される方程式の組に関して異なる)、または実際に計算に必要とされる特定のDCT係数およびその数のいずれかにおいてのみ異なることに注意すべきである。

【0066】

第2の実施例−4×4ブロックにおけるビデオ抽出

発明の第2実施例はこれから記述され、それは8×8入力ブロックから画素の4×4ブロックを抽出する。

【0067】

4×4画素の抽出において、最大のインデックス値が今3であるので、方程式(18-21)だけが必要である。平均演算により、

【数18】

【0068】

方程式(18-21)は同様に以下のように再配列することができる。

【数19】

【0069】

16の方程式のグループを得るために、我々は16のDCT係数C(u,v):(u,v)∈[0,3] を使用する必要がある。各係数について、それぞれ横および縦方向の両方に方程式(33- 36)の1つを単に適用することにより、対応する方程式を引き出すことができる。

【数20】

【0070】

または、効率のために非整数乗数を左手側に置き、方程式(37)は以下のように表現される。

【数21】

【0071】

同様な演算に続いて、すべての16のDCT係数を算定することができる。一次方程式の組を結果としてもたらすこれは以下のマトリクスの形に配置することができる:

【数22】

【0072】

ここに[CT]は式(39)に示される変換された16DCT係数を含むベクトルであり、

【数23】

【数24】

【0073】

その結果、4×4ブロックのビデオ抽出は3つの選択的な概型で実施されることができる。

【0074】

第1の概型は、4つの係数Cuv:(u,v)∈{(0,0),(0,1),(1,0),(2,0)}を考えるだけである。すべての画素は以下の方程式を通して抽出することができる:

【数25】

【0075】

上の方程式の中では、記法Cab > >xはDCT係数Cabの2進の表現をxビットだけ右シフトすることを意味し、その結果、x最下位ビットを有効に捨てる。意図された読者に理解されるように、このような演算は、実行されなければならない実際の算数の割算なしにDCT係数の値を2xにより分割することに近似する。

【0076】

第2の実施例のための不完全な3段実施ブロック図は図4で与えられ、それは上記方程式の組を実施するために必要ないくつかの数学の演算を示す。さらなる演算が上の方程式の組から必要であることは明らかである。第1の実施例と同様に、上の方程式の組がMPEGデコーダで実行されるべき逆DCTの必要性を取り替えて、したがって、発明の第2の実施例はまた、MPEGかJPEGデコーダの中で図1で示された全体のIDCTブロック10が、図4で部分的に示され、上の方程式によって完全に説明された数学の演算を単に実行するハードウェアかソフトウェアの機能的な要素により置換されることができる。この構成は2つの掛け算と28の加算のみを必要とすることが分かるが、抽出されたビデオフレーム品質は2×2ブロックにおける抽出のものよりもはるかに良く、そこでは使用される4分の1が異なっているが、4つの係数がまた使用される。本発明によって得られた結果に関する例は後でより詳細に議論する。

【0077】

第3の実施例

第3の実施例は第2の実施例に似ており、それはDCT係数入力の各8×8ブロックについて4×4ブロックに画素を抽出するが、それが9つの係数、Cuv:(u,v)∈[0,2]を考えるという点において第2の実施例と異なっている。以下の方程式によって16画素を抽出することができる:

【数26】

【0078】

不完全な実施ブロック図が図5で与えられ、それは構造が非常に簡単であることが分かるであろう。第2の実施例と同様に、図5で示されない演算は上記方程式の組から明らかである。第1と第2の実施例の両方と同様に、上の方程式の組がMPEGデコーダで実行されるべき逆DCTの必要性を取り替えて、したがって、発明の第3の実施例はまた、MPEGかJPEGデコーダの中で図1で示された全体のIDCTブロック10が、図5で部分的に示され、上の方程式によって完全に説明された数学の演算を単に実行するハードウェアかソフトウェアの機能的な要素により置換されることができる。第3の実施例のコストを計算する合計が5つの掛算と、42の加算と9の右シフトに達することが分かる。0.176xが(x > > 3)+(x > > 5)によって近似されるなら、計算コストは47の加算と19の右シフト、しかし掛算なしとなる。視覚検査から、これらの2つの実施にはどんなめぼしい差異もない。

【0079】

第4の実施例

第4の実施例は第3の実施例に密接に関連するが、16の係数のすべて、Cuv:(u,v)∈[0,3]を考慮する。しかしながら、すべての16の係数の包含は加算と掛算の数をほとんど倍にする。2つの方式間のほとんど目だたない視覚品質の違いは、計算量のそのような増加を正当化せず、したがって第4の実施例は好ましくない。

【0080】

以前に落とされた他の7つの係数を含むために、抽出方程式は以下の通り変更される:

【数27】

【0081】

前の実施例と同様に、上の方程式の組がMPEGデコーダで実行されるべき逆DCTの必要性を取り替えて、したがって、発明の第4の実施例はまた、MPEGかJPEGデコーダの中で図1で示された全体のIDCTブロック10が、上の方程式によって記述された数学の演算を単に実行するハードウェアかソフトウェアの機能的な要素により置換されることができる。3つの実数0.085、0.042、および0.18がそれぞれ1/16、1/32、および1/8により近似されるならば、上の方程式の実施コストは45の加算と17の右シフト演算である。しかしながら、以上のように、これらの余分な7つの係数の使用はその抽出されたフレームの品質になんらめぼしい改良も起こさないので、この方式はさらなる議論から除かれる。

【0082】

したがって、概要として本発明の実施例に従って、4つのビデオ抽出方式が提供され、その内3つの方式はそれぞれ4、9、および16 DCT係数を使用して4×4ブロックでビデオフレームを抽出し、1つの方式は4つのDCT係数を使用して2×2ブロックでビデオフレームを抽出する。4つの実施例が単なる例であり、より多いまたはより少ない数のDCT係数を使用して異なったサイズのブロックを生成する同様の方式が、ここに記述されたような本発明の数学の原則を適用することによって設計されることができ、かかる代替の方式は本発明の中に取り囲まれるように意図されることが理解されるべきである。

【0083】

結果

本発明の第1乃至第3の実施例により提供される結果は、図11、12、13、および14の各々で示される例示フレーム(a)、(b)、および(c) に関してこれから説明される。なお特に、図11は第1の実施例によって発生された3個のフレームを示し、図12は第2の実施例によって発生された同じ3個のフレームを示し、図13は第3の実施例にしたがって発生されたフレームを示す。比較のために、図14は従来技術の完全なIDCTを使用して抽出された同じフレームを示し、同じサイズで抽出されたフレームと比較のために288×352のオリジナルサイズから2だけダウンサンプルされている。

【0084】

上記のような画像を発生させるために、各実施例はインターネットからダウンロードされたオリジナルのMPEG-2デコーダのCソースコードに基づくMicrosoft(登録商標)Visual C+ +環境で実施された。したがってこの点で、特定の実施は以前に図9に関して説明されたソフトウェア実施に対応している。公平な比較を確実にするために、さらに各フレームは同じサイズに拡大され、この拡大は必要なサイズに達するまで横と縦方向の両方に沿って同じ画素を繰り返すことにより達成された。したがって、2×2画素ブロックがそれへのDCT係数入力の各8×8ブロックのために抽出されるところでは、抽出された画素をソース画像と同じサイズに拡大するために、各画素は縦4回および横4回繰り返され、16の同じ画素をもたらす。4×4ブロックが抽出されたところでは、各画素は各方向に2回だけ繰り返される必要がある。発明によって提供される画素を単に繰り返して拡大するこのモードは計算上分かり易く、非常に少ない間接費を支持し、その結果、発明の直接画素抽出の技術を使用して獲得されるコンピュータの効率の増加を危険にさらすことなく、拡大が実行されることを許容する。

【0085】

静止ビデオフレーム間の広範囲の再生と比較の後に、抽出されたビデオがその抽出されたサイズで再生されるならば、視覚認識によるビデオ画像の品質が64のDCT係数で逆圧縮された完全なIDCTのそれとほとんど同じであることを我々は観測した。拡大されたサイズの再生に関しては、わずかな歪みがいくつかのフレームに観察されたが、品質は許容できる。例えば、第1の実施例によって発生された図11から、解像度が他の例よりもかなり劣ることが分かるであろう。しかしながら、第3の実施例を使用して発生される図13からは、完全なIDCTを使用して発生されたフレームとほとんどどんな顕著な違いも起こらない。

【0086】

実験結果と視覚比較から、ビデオ抽出アルゴリズムのために以下のさらなる結論を下すことができる:

・第1と第3の実施例の2つのビデオ抽出アルゴリズムが、抽出されたサイズの再生で、即ち、第1の実施例に関してH/4×W/4、および第3の実施例に関してH/2×W/2でほぼ完全に逆圧縮ビデオ画像品質を達成する。

【0087】

・第2の実施例に関しては、抽出されたサイズの再生は完全に逆圧縮されたビデオフレームと比較して許容できる知覚の品質を持っており、第1の実施例のそれより良い品質を達成する。4分の1がC20対C11で異なっているが、両方の方式が4つのDCT係数を使用することに注意を要す。

【0088】

・2×2ブロックでのビデオ抽出、即ち第1の実施例はH/2×W/2の再生について許容できる知覚の品質を維持する。

【0089】

・4×4ブロックでのビデオ抽出、即ち第3の実施例は許容できる知覚の品質を有してフルサイズビデオフレーム再生を与えることができる。

【0090】

例証目的のために、研究された3つのビデオ抽出方式と文献で引用された他の速いIDCTコンピューティングアルゴリズムに関してコンピュータのコスト(しかし、複雑さでない)を表1にまとめた。

【表1】

【0091】

表において、参照[a],[b],および[c]はそれぞれ従来発行された論文:M. Vetterli,“Fast 2-D discrete cosine transform”,in Proc. ICASSP’85,Mar.1985; P. Duhamel and C. Guillemot,“Polynomial transform computation of 2-D DCT”,in Proc. ICASSP’90,pp.1515-1518, Apr. 1990;およびN.I.Cho and S.U.Lee,“Fast algorithm and implementation of 2-D discrete cosine transform”,IEEE Trans.Circuits Syst., vol.CAS-40, pp.259-266,Apr.1991,に関連し、それらは各々速い逆DCT演算に関する従来技術の例について説明する。

【0092】

表の結果は以下の通り批評される: 参照[a]乃至[c] での速いIDCT実施のための請求は、ソフトウェア実施と同様に理論上の試験によって慎重に確かめられる必要があることに特に注意を要す。速い速度は低い実施の複雑さを必ずしも意味するわけではない。速いIDCTコンピューティングの大多数はまだ高い計算量を被っている。即ち、速さが掛算と足し算の数によってのみ測定されるので、それらの係数または画素の再順序付け、多量の実数などを予め計算しかつ予め記憶することのような他の背景計算が無視された。その結果、大きいメモリ消費が必要とされることになった。そこで、これらの公開された速いIDCTコンピューティングアルゴリズムの大部分は価格を支払わないで速くすることはできない。対照的に、ここに発明された技術は、それらの実施の構造が非常に簡単であるので、DCTに関する少しも知識のない者でも容易について行くことができ、本当に低いコストを持つように容易に確かめることができる。どんな背景計算もなく、それらの係数または画素のなんら他の移動もなく、付加的メモリ消費もない。その上、第3の実施例のために必要とされるわずか5つの掛け算が10の右シフトに置換されることができる。これは、どんな掛算も全く必要でないことを意味する。しかも、知覚の品質は抽出されたサイズ表示において完全に逆圧縮されているものに拮抗しかつ非常に近い。我々はどんなに速いIDCTベースの速いコンピューティングもこれを達成することができたとは思わない。

【0093】

したがって、本発明は、逆DCTを受ける必要がなく、コード化されたMPEGかJPEG画像のDCT係数から直接抽出されるべき画素値を許容する方法と装置を提示する。発明のコンピュータの効率は従来技術の速いIDCTの技術に関して非常に高められ、発生されたDCT係数の部分集合だけを使用する能力は、MPEGとJPEGコード化画像およびビデオの今後の伝送に必要である帯域幅が非常に減少されるであろうことを意味する。発明は多くの潜在的な将来の応用があり、我々はDCT領域からの画像の速くて効率的な抽出を達成することが望ましいどんな将来の装置にも、発明により提供される技術の応用を考える。

【特許請求の範囲】

【請求項1】

ソース画像における画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する方法であって、

それぞれ値が抽出されるべきである特定の画素に関連づけられる複数の予め計算されたパラメタを記憶し;

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算するステップを含む方法。

【請求項2】

予め計算されたパラメタが複数の予め定義された関係に従ってDCT係数に対して抽出されるべき画素値に関係する請求項1による方法。

【請求項3】

抽出された画素値がソース画像における一組の画素のそれぞれの値の平均値である請求項1または2による方法。

【請求項4】

計算するステップが、1つ以上の前記DCT係数の係数として1つ以上の前記予め定義されたパラメタを組み込んでいる予め定義された一次方程式を使用して抽出されるべき画素値を直接計算することをさらに含む、請求項1乃至3のいずれか1項による方法。

【請求項5】

DCT係数がソース画像においてa×b画素のブロックから得られ、そのブロックについてa/x×b/y画素の合計が抽出される請求項1乃至4のいずれか1項による方法。

【請求項6】

a=b=8、およびx=y∈{2,4}である請求項5による方法。

【請求項7】

計算するステップで使用される信号の中に含まれたそれらのDCT係数だけを選択し、残りを廃棄することをさらに含む請求項1乃至6のいずれか1項による方法。

【請求項8】

計算するステップで使用されるDCT係数の少なくとも1つが0のインデックス値を有する請求項1乃至7のいずれか1項による方法。

【請求項9】

計算するステップで使用されるDCT係数がDCT変換に関して最も高いエネルギーを表すそれらである請求項1乃至8のいずれか1項による方法。

【請求項10】

DCT係数の予め選択された部分集合が画素値を計算するために使用される請求項1乃至9のいずれか1項による方法。

【請求項11】

8×8DCT係数のブロックに関して2×2画素のブロックが抽出され、画素値が以下の方程式にしたがって計算される請求項1乃至10のいずれか1項による方法;

【数1】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)である。

【請求項12】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算される請求項1乃至10のいずれか1項による方法;

【数2】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項13】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算される請求項1乃至10のいずれか1項による方法;

【数3】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項14】

ソース画像における画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出するコンピュータプログラムであって、コンピュータ上で実行されるとき請求項1乃至13のいずれかの方法にしたがってコンピュータに演算させる命令を含むコンピュータプログラム。

【請求項15】

請求項14によるコンピュータプログラムを記憶するコンピュータ読み込み可能な記憶媒体。

【請求項16】

ソース画像において画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する装置であって、

それぞれ値が抽出されるべきである特定の画素に関連づけられた複数の予め計算されたパラメタを記憶する記憶装置手段と、

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算する計算手段とを含む装置。

【請求項17】

予め計算されたパラメタが複数の予め定義された関係に従ってDCT係数に対して抽出されるべき画素値に関係し、前記予め定義された関係が記憶装置手段に記憶されている請求項16による装置。

【請求項18】

抽出された画素値がソース画像の一組の画素のそれぞれの値の平均値である請求項16または17による装置。

【請求項19】

計算手段が、1つ以上の前記DCT係数の係数として1つ以上の前記予め定義されたパラメタを組み込んでいる予め定義された一次方程式を使用して抽出されるべき画素値を直接計算するようにさらに配置される、請求項16乃至18のいずれか1項による装置。

【請求項20】

DCT係数がソース画像においてa×b画素のブロックから得られ、各ブロックについてa/x×b/y画素の合計が抽出される請求項16乃至19のいずれか1項による装置。

【請求項21】

a=b=8、およびx=y∈{2,4}である請求項20による装置。

【請求項22】

計算手段で使用される信号の中に含まれたそれらのDCT係数だけを選択し、残りを廃棄するDCT係数選択手段をさらに含む請求項16乃至21のいずれか1項による装置。

【請求項23】

計算手段で使用されるDCT係数の少なくとも1つが0のインデックス値を有する請求項16乃至22のいずれか1項による装置。

【請求項24】

計算手段で使用されるDCT係数がDCT変換に関して最も高いエネルギーを表すそれらである請求項16乃至23のいずれか1項による装置。

【請求項25】

計算手段が画素値を計算するためにDCT係数の予め選択された部分集合を使用する請求項16乃至24のいずれか1項による装置。

【請求項26】

8×8DCT係数のブロックに関して2×2画素のブロックが抽出され、画素値が以下の方程式にしたがって計算手段により計算されるようにさらに配置される請求項16乃至25のいずれか1項による装置;

【数4】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)である。

【請求項27】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算手段により計算されるようにさらに配置される請求項16乃至25のいずれか1項による装置;

【数5】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項28】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算手段により計算されるようにさらに配置された請求項16乃至25のいずれか1項による装置;

【数6】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項1】

ソース画像における画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する方法であって、

それぞれ値が抽出されるべきである特定の画素に関連づけられる複数の予め計算されたパラメタを記憶し;

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算するステップを含む方法。

【請求項2】

予め計算されたパラメタが複数の予め定義された関係に従ってDCT係数に対して抽出されるべき画素値に関係する請求項1による方法。

【請求項3】

抽出された画素値がソース画像における一組の画素のそれぞれの値の平均値である請求項1または2による方法。

【請求項4】

計算するステップが、1つ以上の前記DCT係数の係数として1つ以上の前記予め定義されたパラメタを組み込んでいる予め定義された一次方程式を使用して抽出されるべき画素値を直接計算することをさらに含む、請求項1乃至3のいずれか1項による方法。

【請求項5】

DCT係数がソース画像においてa×b画素のブロックから得られ、そのブロックについてa/x×b/y画素の合計が抽出される請求項1乃至4のいずれか1項による方法。

【請求項6】

a=b=8、およびx=y∈{2,4}である請求項5による方法。

【請求項7】

計算するステップで使用される信号の中に含まれたそれらのDCT係数だけを選択し、残りを廃棄することをさらに含む請求項1乃至6のいずれか1項による方法。

【請求項8】

計算するステップで使用されるDCT係数の少なくとも1つが0のインデックス値を有する請求項1乃至7のいずれか1項による方法。

【請求項9】

計算するステップで使用されるDCT係数がDCT変換に関して最も高いエネルギーを表すそれらである請求項1乃至8のいずれか1項による方法。

【請求項10】

DCT係数の予め選択された部分集合が画素値を計算するために使用される請求項1乃至9のいずれか1項による方法。

【請求項11】

8×8DCT係数のブロックに関して2×2画素のブロックが抽出され、画素値が以下の方程式にしたがって計算される請求項1乃至10のいずれか1項による方法;

【数1】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)である。

【請求項12】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算される請求項1乃至10のいずれか1項による方法;

【数2】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項13】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算される請求項1乃至10のいずれか1項による方法;

【数3】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項14】

ソース画像における画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出するコンピュータプログラムであって、コンピュータ上で実行されるとき請求項1乃至13のいずれかの方法にしたがってコンピュータに演算させる命令を含むコンピュータプログラム。

【請求項15】

請求項14によるコンピュータプログラムを記憶するコンピュータ読み込み可能な記憶媒体。

【請求項16】

ソース画像において画素の値から得られる複数の離散コサイン変換(DCT)係数を含む信号から画素値を抽出する装置であって、

それぞれ値が抽出されるべきである特定の画素に関連づけられた複数の予め計算されたパラメタを記憶する記憶装置手段と、

抽出されるべきどんな特定の画素値についても、1つ以上のDCT係数と共にそこで関連する予め計算されたパラメタを使用して画素値を計算する計算手段とを含む装置。

【請求項17】

予め計算されたパラメタが複数の予め定義された関係に従ってDCT係数に対して抽出されるべき画素値に関係し、前記予め定義された関係が記憶装置手段に記憶されている請求項16による装置。

【請求項18】

抽出された画素値がソース画像の一組の画素のそれぞれの値の平均値である請求項16または17による装置。

【請求項19】

計算手段が、1つ以上の前記DCT係数の係数として1つ以上の前記予め定義されたパラメタを組み込んでいる予め定義された一次方程式を使用して抽出されるべき画素値を直接計算するようにさらに配置される、請求項16乃至18のいずれか1項による装置。

【請求項20】

DCT係数がソース画像においてa×b画素のブロックから得られ、各ブロックについてa/x×b/y画素の合計が抽出される請求項16乃至19のいずれか1項による装置。

【請求項21】

a=b=8、およびx=y∈{2,4}である請求項20による装置。

【請求項22】

計算手段で使用される信号の中に含まれたそれらのDCT係数だけを選択し、残りを廃棄するDCT係数選択手段をさらに含む請求項16乃至21のいずれか1項による装置。

【請求項23】

計算手段で使用されるDCT係数の少なくとも1つが0のインデックス値を有する請求項16乃至22のいずれか1項による装置。

【請求項24】

計算手段で使用されるDCT係数がDCT変換に関して最も高いエネルギーを表すそれらである請求項16乃至23のいずれか1項による装置。

【請求項25】

計算手段が画素値を計算するためにDCT係数の予め選択された部分集合を使用する請求項16乃至24のいずれか1項による装置。

【請求項26】

8×8DCT係数のブロックに関して2×2画素のブロックが抽出され、画素値が以下の方程式にしたがって計算手段により計算されるようにさらに配置される請求項16乃至25のいずれか1項による装置;

【数4】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)である。

【請求項27】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算手段により計算されるようにさらに配置される請求項16乃至25のいずれか1項による装置;

【数5】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【請求項28】

8×8DCT係数のブロックに関して4×4画素のブロックが抽出され、画素の値が以下の方程式にしたがって計算手段により計算されるようにさらに配置された請求項16乃至25のいずれか1項による装置;

【数6】

ここに、x(i,j)は画素(i,j)の抽出された値、C(u,v)はDCT係数のブロックに関するDCT係数(u,v)であり、>>xは2xによる有効な分割を表す。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7(a)】

【図7(b)】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7(a)】

【図7(b)】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2010−81618(P2010−81618A)

【公開日】平成22年4月8日(2010.4.8)

【国際特許分類】

【外国語出願】

【出願番号】特願2009−239212(P2009−239212)

【出願日】平成21年10月16日(2009.10.16)

【分割の表示】特願2003−559156(P2003−559156)の分割

【原出願日】平成14年12月24日(2002.12.24)

【出願人】(390028587)ブリティッシュ・テレコミュニケーションズ・パブリック・リミテッド・カンパニー (104)

【氏名又は名称原語表記】BRITISH TELECOMMUNICATIONS PUBLIC LIMITED COMPANY

【Fターム(参考)】

【公開日】平成22年4月8日(2010.4.8)

【国際特許分類】

【出願番号】特願2009−239212(P2009−239212)

【出願日】平成21年10月16日(2009.10.16)

【分割の表示】特願2003−559156(P2003−559156)の分割

【原出願日】平成14年12月24日(2002.12.24)

【出願人】(390028587)ブリティッシュ・テレコミュニケーションズ・パブリック・リミテッド・カンパニー (104)

【氏名又は名称原語表記】BRITISH TELECOMMUNICATIONS PUBLIC LIMITED COMPANY

【Fターム(参考)】

[ Back to top ]