発振回路

【課題】発振立ち上がり時間を大幅に短縮し、発振起動直後から発振出力が得られる発振回路を得ること。

【解決手段】反転増幅器1の入力端子電圧バイアス手段としてその入出力端子間に短絡手段7を併設するとともに、反転増幅器1出力を受け発振出力を行う出力バッファ回路を反転増幅器1の微小振幅出力を常に増幅し得る構成とし、発振起動時には反転増幅器1を活性化するとともに発振子5両端に電位差を与えて発振子5を励磁し、しかる後に上記短絡手段7を所定の期間のみ動作させ反転増幅器1の入出力端子間を短絡する。これによって、発振子5内の共振電流ピークが増大して発振子5の微小振動が助長されるので、早期の発振開始が可能となる。

【解決手段】反転増幅器1の入力端子電圧バイアス手段としてその入出力端子間に短絡手段7を併設するとともに、反転増幅器1出力を受け発振出力を行う出力バッファ回路を反転増幅器1の微小振幅出力を常に増幅し得る構成とし、発振起動時には反転増幅器1を活性化するとともに発振子5両端に電位差を与えて発振子5を励磁し、しかる後に上記短絡手段7を所定の期間のみ動作させ反転増幅器1の入出力端子間を短絡する。これによって、発振子5内の共振電流ピークが増大して発振子5の微小振動が助長されるので、早期の発振開始が可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、水晶発振子またはセラミック発振子等を使用した発振回路に関し、特にマイクロプロセッサ等の半導体集積回路に組み込むのに好適な発振回路に関する。

【背景技術】

【0002】

CMOSゲートによる一般的な発振回路を図11に示す。

【0003】

図11において、端子T1と端子T2との間に水晶発振子またはセラミック発振子(以下、発振子と記す)5と帰還抵抗4とが並列接続し、端子T1と接地(以下、GNDと記す)との間、及び端子T2とGNDとの間にそれぞれ容量61,62が接続している。また2入力NORゲートG1によって反転増幅器1が構成され、その一方の入力は端子T1に、もう一方は制御端子C1に接続し、またその出力は抵抗3を介して端子T2へ、及びインバータG2,G3等から成る出力バッファ回路2を介して発振出力端子OUTへ接続している。

【0004】

図11では反転増幅器としてNORゲートを用いた例を示したがこの他インバータ,NANDゲート,クロックドインバータなどによるものも一般的に用いられている。制御端子C1は発振回路の停止,起動を制御するために設けられたものであり、これは例えばマイクロプロセッサなどに組み込まれた発振回路を動作モードに応じて停止,起動制御を行い消費電力の低減を図る場合などに用いられる。抵抗3はスプリアス発振などの異常発振を防止する目的などで設けられるが省略される場合もある。

【0005】

図11の発振回路を半導体集積回路上に形成する場合、通常NORゲートG1,インバータG2,G3等のCMOSゲート及び抵抗3などが半導体集積回路上に形成され、その他の部品は外付けされる。帰還抵抗4については半導体集積回路上に形成される場合もある。

【0006】

図11の発振回路の動作につき以下説明する。

【0007】

まず制御端子C1がHighレベルにバイアスされている場合、NORゲートG1出力はGNDレベル固定となり、よってNORゲートG1は反転増幅器として機能せず発振回路は停止状態にある。このとき端子T2は当然GNDレベルにあるが、帰還抵抗4により端子T1側もGNDレベルにバイアスされる。

【0008】

次いで制御端子C1がLowレベルにバイアスされると、NORゲートG1は活性化され反転増幅器として機能し得る状態となるが、端子T1側がGNDレベルにバイアスされていたためNORゲートG1出力すなわち端子T2側は一旦VCCレベルに上昇する。この端子T2の電位上昇に伴って、端子T1側も帰還抵抗4により容量61等が充電され電位が徐々に上昇する。端子T1側の電位上昇に伴いNORゲートG1出力すなわち端子T2電位は逆に下降することになる。そして端子T1,端子T2両者の電位がNORゲートG1の論理しきい値電圧(以下、VLT1と記す)程度となった時点で安定する。このときNORゲートG1の反転増幅器としてのゲインは最大となり、NORゲートG1すなわち反転増幅器1と発振子5との間で正帰還ループが形成され発振が開始される。発振開始当初はVLT1レベルを中心電圧とした微小振動であるが、上記正帰還ループにより発振振幅は徐々に拡大し最終的には電源VCC振幅にまで成長する。反転増幅器1の出力振幅が出力バッファ2内インバータG2の論理しきい値電圧(以下、VLT2と記す)を横切って振動するようになるとインバータG2,G3等による発振振幅の増幅及び波形整形が行われ発振出力端子OUTにVCC振幅の発振出力が出現する。

【0009】

以上の概略動作波形を図11内に示した。出力端子OUTの波形を実線及び点線で示しているがいずれを取るかは出力バッファ2内のインバータ段数による。

【発明の開示】

【発明が解決しようとする課題】

【0010】

図11の発振回路においては、制御端子C1がLowレベルとなり発振回路が起動されても端子T1電位がVLT1近傍にバイアスされるまで反転増幅器1は十分なゲインを持ち得ず発振開始に必要な正帰還ループを形成できない。端子T2側もVCCレベルから徐々に低下してくるからその間に反転増幅器1による微小振動の増幅が行われたとしてもその出力振幅がVLT2を横切るものでなければインバータG2による増幅は行われず発振出力は得られない。また端子T1,T2がVLT1にバイアスされ反転増幅器1と発振子5の正帰還ループによる発振を開始しても、VLT1とVLT2との電圧差に相当する振幅にまで発振振幅が増幅されないとやはりインバータG2による増幅は行われず発振出力を取り出すことはできない。

【0011】

端子T1電位がVLT1近傍にバイアスされるまでの時定数は帰還抵抗4に依存するが帰還抵抗4は通常1MΩ程度の値が用いられ、上記時定数は比較的大きいものとなる。さらに正帰還ループの増幅遅れも加味され図11波形における発振立ち上がり時間は、通常数百μs〜数十msを要する。

【0012】

マイクロプロセッサなどに上記発振回路を組み込みその発振出力をシステムクロック源として使用する場合など、上記発振立ち上がり時間の期間中はクロックパルスが得られないことになり、処理は実行不能の状態にある。よって図11に示した従来例では、発振起動後すぐに発振出力を使用して何らかの処理を実行したいといった用途には対応することができない。また発振立ち上がり時間の期間中は、端子T1,T2の電位は中間電位にあるからNORゲートG1やインバータG2などのCMOSゲート部分で貫通電流が流れている。発振出力が得られないにもかかわらず発振回路が電流を消費していることになり、これはまったくの無効な電流消費となってしまう。

【0013】

本発明の目的は、上記発振立ち上がり時間を大幅に短縮し、発振起動直後から発振出力が得られる発振回路を提供すること、及びそれにより無効な電流消費を削減した発振回路を提供することにある。そしてさらにそれらを低電圧動作においても実現し得る発振回路を提供することにある。

【課題を解決するための手段】

【0014】

本願において開示される発明における一実施の形態の概要を簡単に説明すれば、次の通りである。

【0015】

上記目的は、反転増幅器の入力端子電位を反転増幅器の動作電圧(例えば論理しきい値電圧)近傍にバイアスするための回路手段と、反転増幅器の微小振幅出力を常に増幅,波形整形して発振出力端子へ送出し得る出力バッファ回路とを設け、発振起動時に反転増幅器を活性化するとともに端子間(すなわち発振子の両端子間)に電位差を与えて発振子を励磁し、しかる後に上記回路手段を発振子が動作するのに十分な励磁電流が流れる状態となるように所定の期間動作させて反転増幅器の入力端子電位をその動作電圧にバイアスすることにより達成される。

【0016】

なお、低電圧動作に対応する具体的手段、及び上記出力バッファ回路の具体的構成については実施例のなかで明らかにする。

【0017】

発振起動時に反転増幅器を活性化するとともに端子間に電位差を与えることにより発振子に励磁電流が流れ、発振子は微小振動を開始する。その振動周波数は発振子の等価インダクタンス,容量などから決まる共振周波数となる。この発振子の励磁直後においては、端子間の電位差はまだ開いたままであり、帰還抵抗によって両端子電位は緩やかに反転増幅器の動作電圧へ向かって変位を始める。しかる後に、上記回路手段を所定の期間動作させて反転増幅器の入力端子電位を反転増幅器が動作するような所定の電位(例えばVLT1近傍)に強制的にバイアスすることにより、反転増幅器としての機能開始を早めることができるので、反転増幅器と発振子との正帰還ループを早期に形成することができる。さらにその反転増幅器出力を常に増幅可能な出力バッファ回路を設けることにより発振子自体の振幅がまだ微小であっても、電源振幅の発振出力を早期に取り出すことが可能となる。

【発明の効果】

【0018】

本発明の一実施の形態によれば、反転増幅器と発振子との正帰還ループを早期に形成して発振開始を早め、また反転増幅器1からの微小発振出力を増幅,波形整形して発振起動から利用し得る発振出力が得られるまでの発振立ち上がり時間を大幅に短縮した発振回路を得ることができる。

【0019】

また本発明の一実施の形態によれば、反転増幅器からの微小発振出力を増幅,波形整形する出力バッファ回路部分の消費電流を低減した発振回路を得ることができる。

【0020】

また本発明の一実施の形態によれば、発振振幅の増幅にカレントミラー回路を用いたことにより、低電圧下でも上記発振立ち上がり時間を短縮し、良好な発振出力特性を維持し得る発振回路を得ることができる。

【発明を実施するための最良の形態】

【0021】

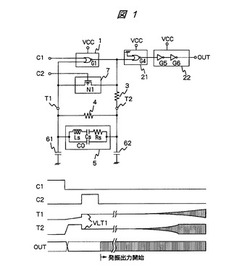

以下、本発明の第1の実施例を図1により説明する。

【0022】

図1において、端子T1と端子T2との間に発振子5と帰還抵抗4とが並列接続し、端子T1及び端子T2とGNDとの間にそれぞれ容量61,62が接続している。発振子5は等価インダクタンス,容量による等価回路を示した。反転増幅器1は2入力NORゲートG1によって構成され、その一方の入力は端子T1に、もう一方は制御端子C1に接続し、その出力は抵抗3を介して端子T2へ接続している。またその端子T1側の入力と出力との間には短絡手段7が並列接続されている。短絡手段7は、ゲートを制御端子C2へ、ソース,ドレインを反転増幅器1の端子T1側入力とその出力とにそれぞれ接続したNMOSトランジスタN1によって構成されている。また反転増幅器1出力には発振検出ゲート21が接続し、さらにその出力はバッファ回路22を介して発振出力端子OUTに接続されており、発振検出ゲート21とバッファ回路22とで図11における出力バッファ回路2を構成した形となっている。発振検出ゲート21は反転増幅器1を構成する2入力NORゲートG1と同構成の2入力NORゲートG4によって構成され、一方の入力はGNDにバイアスされている。バッファ回路22はインバータG5,G6等で構成しているが、これは発振検出ゲート21の出力をさらに増幅,波形整形して発振出力を得るために設けたものであり、その構成インバータ段数等は必要に応じて適宜設定すれば良い。

【0023】

以下、本実施例の動作につき説明する。

【0024】

まず制御端子C1がHighレベルにバイアスされている場合、NORゲートG1出力はGNDレベル固定となり、よってNORゲートG1は反転増幅器として機能せず発振回路は停止状態にある。このとき端子T2および端子T1は、帰還抵抗4により共にGNDレベルにバイアスされる。NORゲートG1すなわち反転増幅器1出力がGNDレベルのためNORゲートG4すなわち発振検出ゲート21出力はHighレベル(電源VCCレベル)固定となり、発振出力OUTはバッファ回路22のインバータ段数に応じてHighレベルもしくはGNDレベルのいずれかに固定される。

【0025】

発振起動時は、まず制御端子C1をLowレベル(またはGNDレベル)にバイアスすることによりNORゲートG1を活性化する。このとき端子T1側がGNDレベルにバイアスされていたためNORゲートG1出力すなわち端子T2側は、一旦VCCレベルに上昇する。このときの端子T2と端子T1との間に生じた電位差によって発振子5に励磁電流が供給され、発振子は固有周波数すなわち等価インダクタンス,容量などによって決まる共振周波数で微小振動を開始する。端子T1側も帰還抵抗4により容量61等が充電され徐々に電位上昇を始めるが、NORゲートG1が活性化した直後ではまだGNDレベル近傍にあり、NORゲートG1はまだ反転増幅器として機能することができない状態にある。

【0026】

しかる後に図1内波形に示した様に制御端子C2にワンショットパルスを印加し、NMOSトランジスタN1すなわち短絡手段7を所定の期間のみONさせる。NMOSトランジスタN1のONにより、NORゲートG1の入出力間が短絡され端子T1,T2は共にVLT1レベルにバイアスされる。またこのとき容量61,62及び発振子5の閉ループで流れていた発振子5の共振電流は短絡手段7側にバイパスできるようになり、共振電流パスのインピーダンスが下がり共振電流ピークは増大する。これにより発振子5の等価インダクタンスLs等における電圧振幅も増大し発振出力開始に有利となる。

【0027】

制御端子C2のワンショットパルスが終了し元のレベルに復帰すると、NMOSトランジスタN1はOFFするがこのとき端子T1及び端子T2電位はほぼVLT1レベルにあるからNORゲートG1すなわち反転増幅器1のゲインは最大となり、反転増幅器1と発振子5との間で正帰還ループが形成され発振が即開始される。発振開始当初、反転増幅器1出力はVLT1レベルを中心電圧とした微小振動ではあるが、これを受ける発振検出ゲート21が反転増幅器1を構成するNORゲートG1と同構成のNORゲートG4で構成しているためそれらの論理しきい値電圧は等しく、よってVLT1レベルを中心電圧とした反転増幅器1出力の微小振動をすぐに増幅することができる。バッファ回路22内インバータG5,G6等の論理しきい値電圧がVLT1からずれていたとしても発振検出ゲート21によって反転増幅器1出力振幅が一旦増幅されているからバッファ回路22による発振振幅の増幅及び波形整形もすぐに開始することができる。

【0028】

制御端子C2のワンショットパルス幅は端子T1,T2をVLT1レベルにバイアスするのに必要十分な程度のパルス幅とすれば良く、例えば数μs程度以下とすることもできる。よって図11従来例に比べ、制御端子C1による発振回路起動開始から早期に発振出力を得ることができる。

【0029】

以上の如く本実施例によれば、発振起動から早期に反転増幅器1と発振子5との正帰還ループを形成することができ、また反転増幅器1出力を直ちに増幅して出力端子OUTに送出できるので、発振起動から発振出力開始までの時間すなわち発振立ち上がり時間を大幅に短縮した発振回路を得ることができる。またそれゆえ発振開始までの無効な電流消費を低減した発振回路を得ることができる。

【0030】

なお図1において、反転増幅器1及び発振検出ゲート21をNORゲートで構成したがこれに限定されるものではなく、インバータ,NANDゲート,クロックドインバータ、または負荷MOS型インバータなど低電圧動作にも対応したゲートなど、他のゲート構成によっても同様の効果を得ることができる。短絡手段7についてもNMOSトランジスタN1による構成以外に例えばPMOSトランジスタ、あるいはPMOSトランジスタとNMOSトランジスタを並列接続したトランスファゲート、などによっても同様の作用を実現できる。また抵抗3は発振安定化のために必要に応じて設定すべきものであり省略することもできる。なお、これらは以降の実施例においても同様である。

【0031】

本発明の第2の実施例を図2に示す。

【0032】

本実施例は上記図1に示した第1の実施例に対し、制御端子C3にゲートを、電源VCC及び反転増幅器1出力にソース及びドレインをそれぞれ接続したPMOSトランジスタP1から成る励磁電流供給手段18を付加した構成となっている。図2には制御端子C1,C2,C3への印加信号タイミング例も示している。

【0033】

発振停止状態においては、制御端子C1,C3をHighレベルにバイアスすることにより第1の実施例同様反転増幅器1出力をGNDレベル固定とし、またPMOSトランジスタP1すなわち励磁電流供給手段18はOFF状態としておく。

【0034】

次いで発振起動時は制御端子C1をLowレベルとしてNORゲートG1を活性化するとともに制御端子C3にLowレベルのワンショットパルスを印加する。制御端子C3がLowレベルの期間中はPMOSトランジスタP1もONすることにより端子T2部を急速に充電すると共に発振子5に励磁電流を供給する。

【0035】

制御端子C3がHighレベルに復帰しPMOSトランジスタP1がOFFした後は第1の実施例同様、制御端子C2にワンショットパルスを印加してNORゲートG1の入出力間を短絡し、端子T1,T2をVLT1にバイアスすることによって反転増幅器1と発振子5との正帰還ループを早期に形成する。

【0036】

本実施例によれば前記第1の実施例の効果に加え、励磁電流供給手段18を設けたことにより反転増幅器1を構成するゲートから起動時の発振子励磁電流を供給する必要が無くなったため反転増幅器1を構成するゲートの電流駆動能力を発振状態を維持し得る程度に設定することができ、消費電流を低減した発振回路を得ることができる。

【0037】

本実施例においては端子T2側に励磁電流供給手段18を設けたが、これを端子T1側に設けても同様の効果を得ることができる。その場合NORゲートG1の活性化と同時に励磁電流供給手段18により端子T1側がVCCレベルにバイアスされることになり、励磁電流供給手段18がONしている間NORゲートG1出力はGNDレベルとなるとともに端子T1,T2間に電位差が与えられ発振子5の励磁が行われる。

【0038】

なお、反転増幅器1としてNANDゲートを用いた場合、発振停止状態はNORゲートG1の場合とは逆にNANDゲート入力につながる制御端子をLowレベルとすることにより、端子T1,T2電位が共にHighレベル側に固定されることになるから、この場合励磁電流供給手段18は端子T1、若しくは端子T2とGNDとの間に設け、発振起動時に発振子の励磁電流をGND側に引き抜くことになる。

【0039】

なお、図2における励磁電流供給手段18はPMOSトランジスタP1で構成したが、これに限られるものではなく例えばNMOSトランジスタ等を用いても良い。

【0040】

また以降の実施例においては特に必要の無い限り励磁電流供給手段18の記載を省略するが、いずれの実施例においてもこれを併設することは可能であり本実施例の効果を享受できることは言うまでもない。

【0041】

本発明の第3の実施例を図3に示す。

【0042】

図3において、反転増幅器1,短絡手段7、及び帰還抵抗4,発振子5、及び容量61,62等の接続構成は図1の第1の実施例同様であるが、反転増幅器1出力はカップリング容量8を介して発振検出ゲート21に接続し、発振検出ゲート21の入出力間には帰還抵抗9と短絡手段10とが並列接続している。短絡手段10はゲートを制御端子C4へ、ソース,ドレインを発振検出ゲート21の入力,出力へそれぞれ接続したNMOSトランジスタN2によって構成されている。また発振検出ゲート21は、NORゲートG7で構成され一方の入力がカップリング容量8へ、もう一方の入力が制御端子C1へ接続している。その出力を受けるバッファ回路22については図1の第1の実施例同様である。

【0043】

以下本実施例の動作につき説明する。

【0044】

発振停止状態においては、制御端子C1をHighレベルにバイアスすることによりNORゲートG1から成る反転増幅器1出力、及びNORゲートG7から成る発振検出ゲート21出力をGNDレベル固定とし、また制御端子C2,C4はLowレベルにバイアスしてNMOSトランジスタN1,N2から成る短絡手段7,10をOFF状態としておく。

【0045】

発振起動時においては図1の第1の実施例同様、制御端子C1をLowレベルとしてNORゲートG1を活性化して発振子5を励磁し、しかる後に制御端子C2へワンショットパルスを印加して短絡手段7により所定の期間端子T1,T2間の短絡を行う。このとき制御端子C1へ入力を接続するNORゲートG7もNORゲートG1と同時に活性化し、またその後制御端子C4へもワンショットパルスを印加してNMOSトランジスタN2から成る短絡手段10によりNORゲートG7の入出力動作点をその論理しきい値電圧に急速にバイアスする。制御端子C4のワンショットパルスが復帰するとNORゲートG7の入力電位はその論理しきい値電圧となっているからすぐに発振検出ゲートとして機能し始める。

【0046】

発振検出ゲート21によって反転増幅器1の微小出力振幅を増幅しているときに、端子T1側のリーク電流等によって反転増幅器1の出力振幅中心電圧が変動した場合、図1,図2に示した実施例においては発振検出ゲート21の入力電圧レベルがその論理しきい値電圧から変動することとなり、発振検出ゲート21が感応できなくなって発振出力不能となる可能性がある。しかし本実施例によれば、発振検出ゲート21に帰還抵抗9を設けることで発振検出ゲート21の入力インピーダンスが低減され、かつカップリング容量8を介して反転増幅器1出力を受けていることにより、上記の様な反転増幅器1の出力電圧レベル変動による発振検出ゲート21の入力電圧レベルへの影響はほとんど無く、発振検出ゲート21は常にその論理しきい値電圧を中心電圧とした動作点で安定な増幅を行うことができる。また短絡手段10により、発振起動時に発振検出ゲート21の動作点を速やかに確定することができ、発振立ち上がり時間を延ばすことなく発振検出ゲート21の安定化を図ることができる。

【0047】

なお、帰還抵抗9を帰還抵抗4などに比べて低抵抗設定とし、発振検出ゲート21の動作点確定が速やかに行える様にすることにより、短絡手段10及び制御端子C4を省略することも可能である。

【0048】

また制御端子C4のワンショットパルスの立下がりすなわち短絡手段10のOFFタイミングを、図3内タイミングに示した様に制御端子C2の立下がりすなわち短絡手段7のOFFタイミングより遅らせることにより、制御端子C2電位変動に伴う雑音電荷の影響、すなわち発振検出ゲート21入力電圧の一時的な低下等を防止することもできる。

【0049】

本実施例によれば、前記第1の実施例の効果に加え、発振子の端子電圧のレベル変動に対しても安定に発振出力を成し得る発振回路を得ることができる。

【0050】

なお本実施例においては制御端子C1によって発振検出ゲート21の制御を行ったがこれに限定されるものではなく、発振検出ゲート21の活性化が反転増幅器1と同時でなくても良い。

【0051】

本発明の第4の実施例を図4に示す。

【0052】

図4においては、上記図3の第3の実施例におけるバッファ回路22に代えてPMOSトランジスタP2とPMOSトランジスタP3との互いのゲートを接続しPMOSトランジスタP2側のゲート,ドレインを短絡接続して成るカレントミラー回路と、PMOSトランジスタP2のドレインと発振検出ゲート21出力との間に接続するカップリング容量11と、PMOSトランジスタP2のドレインとGNDとの間に接続するバイアス手段12と、PMOSトランジスタP3のドレインとGNDとの間に接続するバイアス手段13と、を設け、PMOSトランジスタP3とバイアス手段13との接続点を出力OUTとして発振出力を取り出す構成としている。またバイアス手段12,13はそれぞれ抵抗RB1,RB2で構成されている。

【0053】

本実施例における発振停止及び起動制御については、上記図3の第3の実施例同様である。発振起動直後における状態についてみると、いずれの実施例においても反転増幅器1の微小出力振幅を発振検出ゲート21が増幅はするものの振幅は小さくその出力電圧振幅レベルはまだ発振検出ゲート21の論理しきい値電圧近傍にある。発振検出ゲート21の出力振幅が拡大するには反転増幅器1の微小出力振幅自体の拡大が必要であり電源VCC振幅にまで拡大するには相当な時間を要する。前記図3の第3の実施例等においてはその発振検出ゲート21出力振幅拡大までの期間、発振検出ゲート21出力を受けるバッファ回路22内インバータG5からみれば中間レベルの入力電圧が印加されていることになり、インバータG5等がCMOS構成であれば貫通電流が流れることになる。インバータG5出力振幅が電源VCC振幅にまで増幅されていなければさらにインバータG6部でも貫通電流が流れることになる。

【0054】

また前記図3の第3の実施例等においては、発振検出ゲート21とバッファ回路22内インバータG5との各論理しきい値電圧の差がデバイスばらつき等によって拡大すればその分インバータG5が感応する電圧レベルにまで発振検出ゲート21出力振幅が拡大するまでの時間が必要となり、発振出力開始に遅れを来すことになる。すなわちインバータG5の論理しきい値電圧は常に発振検出ゲート21の発振出力の中心電圧レベル近傍にあることが必要とされる。

【0055】

本実施例は上記問題を対策しようとするものである。

【0056】

図4において、バイアス手段12は消費電流上さほど問題にならない程度、例えば数μA程度の電流バイアスをPMOSトランジスタP2に与える様設定し、PMOSトランジスタP2を能動状態におく。これによりPMOSトランジスタP2動作点すなわちそのドレイン電圧は電源VCCからPMOSトランジスタP2のゲート,ドレイン間電圧VGS分低下したレベルにバイアスされる。一方、発振検出ゲート21出力は発振起動後その論理しきい値電圧を中心電圧とした電圧振動を開始するが、その発振検出ゲート21の出力電圧変動は、カップリング容量11部の変位電流を介してPMOSトランジスタP2のドレイン電流変動に変換されることになる。すなわち発振検出ゲート21の出力電圧が上昇方向に変動するときはカップリング容量11部の変位電流は発振検出ゲート21出力側からPMOSトランジスタP2のドレイン側に向かう方向に流れ、PMOSトランジスタP2のドレイン電流を減衰させる。逆に発振検出ゲート21の出力電圧が下降方向に変動するときはカップリング容量11部の変位電流は上記とは逆にPMOSトランジスタP2のドレイン側から発振検出ゲート21出力側に向かう方向に流れ、PMOSトランジスタP2のドレイン電流を増加させる。このPMOSトランジスタP2のドレイン電流変動はカレントミラー接続されたPMOSトランジスタP3側へ伝達され、ミラー比倍されてPMOSトランジスタP3の出力電流変動となって現われる。PMOSトランジスタP3側には、バイアス手段12によるPMOSトランジスタP2部のバイアス電流のミラー比倍に相当するドレイン電流が流れることになるが、上記変動分がそれに重畳するかたちになる。このPMOSトランジスタP3のドレイン電流は抵抗RB2から成るバイアス手段13へ流れ電圧振幅に変換されて出力端子OUTから取り出されることになる。以上の様に本実施例によれば、発振検出ゲート21の出力電圧変動分をPMOSトランジスタP2の出力電流変動に変換し、これを増幅する機構であるため、発振検出ゲート21の発振出力の中心電圧レベルに依存することなく発振振幅の増幅が可能となる。

【0057】

図4に示した実施例においては、バイアス手段12による直流バイアス電流成分も抵抗RB2から成るバイアス手段13に流れ、これによる電位降下が発生する。またPMOSトランジスタP3ドレイン電流のピーク時点でも出力端子OUT電位はPMOSトランジスタP3のオン抵抗成分と抵抗RB2との分圧電位となるから、図4における出力端子OUTの発振出力電圧振幅は電源VCC電圧とGND間の振幅よりは狭まったものとなる。しかし出力端子OUTにCMOSインバータ等を付加すれば容易に波形整形が可能であり、また発振検出ゲート21の出力振幅に比べ十分拡大された電圧振幅が得られるから出力端子OUTを受けるCMOSインバータ等のゲート部分での貫通電流は前記図3等におけるインバータG5におけるものより大幅に低減されたものとなる。

【0058】

なお上記図4に示す構成においては、バイアス手段12,13等に流れる直流バイアス電流を抑制し、またPMOSトランジスタP3の出力電流振幅から大きな電圧振幅を得るためにも抵抗RB1,RB2を比較的高抵抗とする必要があるが、これは集積化の点で不利となる。そこで図5に示す様に抵抗RB1,RB2をMOSトランジスタによる定電流回路に置き換えた構成とすることもできる。以下、図5に示す構成につき説明する。

【0059】

図5において、上記図4におけるバイアス手段12,13はそれぞれNMOSトランジスタN4,N5で構成されている。PMOSトランジスタP2ドレインとGNDにNMOSトランジスタN4のドレイン,ソースが、またPMOSトランジスタP3ドレインとGNDにNMOSトランジスタN5のドレイン,ソースがそれぞれ接続し、NMOSトランジスタN4,N5の各ゲートは、ゲート,ドレインを短絡接続しソースをGNDに接続するNMOSトランジスタN3のゲートへ共通接続している。NMOSトランジスタN3のドレインと電源VCCとの間には電流源14が設けられている。

【0060】

NMOSトランジスタN3とNMOSトランジスタN4、及びNMOSトランジスタN5はカレントミラー接続となっているから、NMOSトランジスタN4、及びNMOSトランジスタN5のドレイン電流すなわちPMOSトランジスタP2とPMOSトランジスタP3のバイアス電流は電流源14の電流とそれらのミラー比によって決まる。いまNMOSトランジスタN4とNMOSトランジスタN5とのミラー比を、PMOSトランジスタP2とPMOSトランジスタP3のミラー比と同じに設定すれば、NMOSトランジスタN4とPMOSトランジスタP2のドレイン電流は同値であるからそれらをそれぞれミラー比倍したNMOSトランジスタN5とPMOSトランジスタP3の各ドレイン電流も等しいことになる。このようなバイアス設定によれば、以下に詳しく述べるが発振時にPMOSトランジスタP3のドレイン電流に重畳する電流振動を過不足無く電圧振幅に変換することができる。しかもこのバイアス設定は発振電流増幅を行うPMOSトランジスタP2,P3とバイアス電流源のNMOSトランジスタN4,N5の各MOSトランジスタ寸法によるミラー比設定によって実現され、電流源14等の絶対値には依らないので集積化には極めて好適である。本構成による増幅動作につき以下説明する。

【0061】

発振検出ゲート21の出力が仮にまだ振動を開始していない状態を想定すると、このときPMOSトランジスタP3とNMOSトランジスタN5の各ドレイン電流駆動能力は上記の如くちょうどつりあった状態にある。その状態から発振が開始して発振検出ゲート21の発振出力電圧振動が電圧下降方向に振れ、PMOSトランジスタP3のドレイン電流が増加方向に振れたとすると、NMOSトランジスタN5に対しPMOSトランジスタP3のドレイン電流駆動能力が上回ることになるから出力端子OUTの動作点は急速に電源VCCに向かって上昇する。そしてNMOSトランジスタN5のドレイン電流を供給し得るPMOSトランジスタP3のドレイン−ソース間電圧VDS分だけ電源VCCから低下した電位まで上昇して安定する。逆に発振検出ゲート21の発振出力電圧振動が電圧上昇方向に振れ、PMOSトランジスタP3のドレイン電流が減少方向に振れたときは、PMOSトランジスタP3のドレイン電流駆動能力がNMOSトランジスタN5よりも下回ることになり出力端子OUTの動作点は急速にGND電位に向かって下降する。そしてPMOSトランジスタP3のドレイン電流を流し得るNMOSトランジスタN5のドレイン−ソース間電圧VDS分だけGNDから浮いた電位で安定する。上記PMOSトランジスタP3及びNMOSトランジスタN5のVDS電圧については、いずれも非飽和領域の動作となるからその値は比較的小さく、よって出力端子OUTの電圧振幅としては電源VCC電圧に近い振幅を得ることができる。

【0062】

以上の如く図4または図5に示す第4の実施例によれば前記第3の実施例の効果に加え、CMOSゲートに替えてカレントミラー回路を利用して微小発振電圧振幅の増幅を行ったことにより、CMOSゲートによる場合の貫通電流の問題を回避でき消費電流低減に有効な発振回路を得ることができる。また発振電圧振動をカップリング容量を介して電流振動に変換して増幅したことにより、発振電圧振動の中心電圧レベルに依存せずにその電圧変動分のみを抽出して増幅することができ、デバイスばらつきによる発振動作点レベルの変動等に対しても安定に発振出力が得られる発振回路を得ることができる。

【0063】

また前記図3の第3の実施例等において反転増幅器1及び発振検出ゲート21に負荷MOS型インバータ等のゲートを用い、例えば2V以下程度の低電圧下で発振動作を行おうとした場合、バッファ回路22をCMOSゲートで構成すれば発振検出ゲート21の出力振幅が十分拡大しないとCMOSゲートが感応せず、よって発振出力開始が遅れることになる。またバッファ回路22にも負荷MOS型インバータ等のゲートを用いて低電圧下における感度を上げようとすればその分消費電流増大につながってしまう。

【0064】

上記本実施例によれば、カレントミラー回路がそれを構成するMOSトランジスタのしきい値電圧Vth以上の電圧があれば動作可能であるため、上記の様な低電圧下における発振にも好適な発振回路が得られるという効果も有している。

【0065】

なお図4及び図5においては、図3に示されたカップリング容量8と発振検出ゲート21の構成を反転増幅器1の出力バッファとして流用したが、PMOSトランジスタP2,P3のカレントミラー回路による増幅に問題がなければこれを使用しなくても良い。すなわちカップリング容量8と発振検出ゲート21を廃し、カップリング容量11を反転増幅器1出力に直結しても良い。これは適宜設計上決められるべきことである。また図4,図5においてはカレントミラー回路の出力を発振出力端子OUTとしているが、上記説明でも述べた様に特に発振開始直後の発振電圧振幅が微小な期間においてはバイアス電流のために発振出力端子OUTの動作点振幅は中間レベルにあり電源VCC振幅にはならない。そこで図4,図5における端子OUTにCMOSゲートなどを設けてそのゲートの出力を発振出力端子として電源VCC振幅の発振出力を得るようにしても良い。ただいずれの実施例においても当該発振回路を半導体基板上に集積化して利用する場合その発振出力端子OUTには必ずそれを受けるCMOSゲート等が存在し、該CMOSゲート等において波形整形が為されることになる。図4以降に示す本発明の実施例においてはそれらの波形整形用バッファゲートについては記載を省略し、本発明の特徴を成す構成要素のみの記載としている。

【0066】

本発明の第5の実施例を図6に示す。

【0067】

図6において、発振子5周辺から発振検出ゲート21までの構成は前記図3の第3の実施例同様である。そしてPMOSトランジスタP2とPMOSトランジスタP3の互いのゲートを接続しPMOSトランジスタP2側のゲート,ドレインを短絡接続して成る第1のカレントミラー回路と、PMOSトランジスタP2のドレインとGNDとの間に接続するバイアス電流源16と、NMOSトランジスタN6とNMOSトランジスタN7の互いのゲートを接続しNMOSトランジスタN6側のゲート,ドレインを短絡接続して成る第2のカレントミラー回路と、NMOSトランジスタN6のドレインと電源VCCとの間に接続するバイアス電流源17と、PMOSトランジスタP2のドレインと発振検出ゲート21出力との間に接続するカップリング容量11と、NMOSトランジスタN6のドレインと発振検出ゲート21出力との間に接続するカップリング容量15と、を設けPMOSトランジスタP3ドレインとNMOSトランジスタN7ドレインとを接続して発振出力端子OUTとしている。

【0068】

以下本実施例の動作につき説明する。なお発振停止,起動等の制御については上記第3,第4の実施例同様であるので説明は省略する。

【0069】

上記第1のカレントミラー回路と第2のカレントミラー回路のミラー比が同じになる様各MOSトランジスタ寸法が設定され、またバイアス電流源16,17の各電流値が同程度に設定されているものとすると、各カレントミラー回路出力すなわちPMOSトランジスタP3とNMOSトランジスタN7のドレイン電流はほぼ等しい状態となる。この状態において、発振検出ゲート21が発振出力を開始したときの動作を以下説明する。なお、ここでバイアス電流源16,17はPMOSトランジスタP2及びNMOSトランジスタN6を能動状態におくためのバイアス電流を供給するものであり、前記図4,図5におけるバイアス手段12と同様の目的で設けているものである。

【0070】

まず発振検出ゲート21の発振出力電圧振動が上昇方向に振れると、カップリング容量11,15にはそれぞれ発振検出ゲート21出力からPMOSトランジスタP2ドレインへ、及び発振検出ゲート21出力からNMOSトランジスタN6ドレインへ向かう変位電流が生じる。これによりPMOSトランジスタP2側のドレイン電流は減衰方向、NMOSトランジスタN6側のドレイン電流は増加方向に変動し、その電流変動はミラー比倍されてそれらとカレントミラー接続したPMOSトランジスタP3及びNMOSトランジスタN7のドレイン電流変動となる。その結果NMOSトランジスタN7のドレイン電流駆動能力がPMOSトランジスタP3のドレイン電流駆動能力を上回ることになり発振出力端子OUTの動作点は急速にGND電位に向かって下降する。

【0071】

次いで発振検出ゲート21の発振出力電圧振動が下降方向に振れると、カップリング容量11,15にはそれぞれPMOSトランジスタP2ドレインから発振検出ゲート21出力へ、及びNMOSトランジスタN6ドレインから発振検出ゲート21出力へ向かう変位電流が生じる。これによりPMOSトランジスタP2側のドレイン電流は増加方向、NMOSトランジスタN6側のドレイン電流は減衰方向に変動し、その電流変動はやはりミラー比倍されてそれらとカレントミラー接続したPMOSトランジスタP3及びNMOSトランジスタN7のドレイン電流変動となる。その結果今度はPMOSトランジスタP3のドレイン電流駆動能力がNMOSトランジスタN7のドレイン電流駆動能力を上回ることになり発振出力端子OUTの動作点は急速に電源VCC電位に向かって上昇する。

【0072】

本実施例においては、PMOSトランジスタP3とNMOSトランジスタN7とが排他的に動作することになるため、発振出力端子OUTの負荷駆動能力を向上できるとともに、前記第4の実施例に比べより拡大した発振出力振幅を得ることができる。これは例えばPMOSトランジスタP3側の電流駆動能力が増加して発振出力端子OUTの電位を上昇させようとするとき、NMOSトランジスタN7側のドレイン電流が減衰するからPMOSトランジスタP3にとっての負荷電流が減衰することになり相対的にPMOSトランジスタP3の負荷駆動能力が向上して発振出力端子OUT電位を急速に上昇させる。またこのときPMOSトランジスタP3の負荷電流が減衰したことによりPMOSトランジスタP3のソース−ドレイン間の電位降下が減少し、よって発振出力端子OUTの到達電位はより電源VCCに近づくことになる。NMOSトランジスタN7側の電流駆動能力が増加する場合についても同様であり、よりGND電位に近づくことになるから、結局第4の実施例に比べて発振出力電圧振幅を拡大することができる。

【0073】

なお、発振検出ゲート21の発振出力電圧振幅によるカップリング容量11,15の変位電流が、電流源16,17の電流値を超える程度まで発振電圧振幅が拡大してくるとPMOSトランジスタP2またはNMOSトランジスタN6のいずれかが遮断状態になるからPMOSトランジスタP3とNMOSトランジスタN7は完全に排他動作となり、発振出力端子OUTには電源VCC電圧振幅の発振出力が得られることになる。

【0074】

本実施例によれば、前記第4の実施例の効果に加えさらに発振出力特性を改善した発振回路を得ることができる。

【0075】

本発明の第6の実施例を図7に示す。

【0076】

図7においては、上記図6の構成に加えPMOSトランジスタP4とPMOSトランジスタP5の互いのゲートを接続しPMOSトランジスタP4側のゲート,ドレインを短絡接続して成る第3のカレントミラー回路と、NMOSトランジスタN8とNMOSトランジスタN9の互いのゲートを接続しNMOSトランジスタN8側のゲート,ドレインを短絡接続して成る第4のカレントミラー回路と、を設け、PMOSトランジスタP3のドレインはNMOSトランジスタN8のドレインへ、NMOSトランジスタN7のドレインはPMOSトランジスタP4のドレインへそれぞれ分離接続し、PMOSトランジスタP5のドレインとNMOSトランジスタN9のドレインとを接続して発振出力端子OUTとしている。

【0077】

発振検出ゲート21からの発振電圧振動をPMOSトランジスタP3及びNMOSトランジスタN7のドレイン電流変動に変換増幅するまでは上記図6に示した第5の実施例と同様である。図7においてはそれらドレイン電流をさらにNMOSトランジスタN8及びPMOSトランジスタP4のドレイン電流として与え、それぞれNMOSトランジスタN8,N9及びPMOSトランジスタP4,P5の各カレントミラー回路によりNMOSトランジスタN9及びPMOSトランジスタP5側へ増幅伝達する。PMOSトランジスタP3とNMOSトランジスタN7とは上記第5の実施例において述べた様に排他的に動作しているのでそれらの各ドレイン電流を増幅したPMOSトランジスタP5とNMOSトランジスタN9も排他的に動作することとなり、発振出力端子OUTに電圧振幅を出力する。

【0078】

上記図6の第5の実施例においては、PMOSトランジスタP2,P3及びNMOSトランジスタN6,N7の各カレントミラー回路の増幅率がほぼ一致していることが必要である。もしその増幅率が違っていると出力側のPMOSトランジスタP3若しくはNMOSトランジスタN7のいずれかにより多くの電流バイアスがかかり、結果として出力電圧振幅が電源VCC側若しくはGND側に片寄ったものとなり極端な場合は振幅がつぶれて発振出力が得られなくなってしまう。そこでPMOSトランジスタP2,P3及びNMOSトランジスタN6,N7の各MOSトランジスタ寸法比を同じにしてミラー比、すなわち上記増幅率を合わせる様に設定しているわけであるが、各カレントミラー回路を構成するMOSトランジスタの種類がPMOS,NMOSと異なっているためそのデバイス特性ばらつき等によって上記増幅率に差異を生じる場合がある。例えば図6におけるPMOSトランジスタP2とP3、及びNMOSトランジスタN6とN7についてみると、各MOSトランジスタにおけるドレイン−ソース間電圧は異なっている。よってPMOSトランジスタ,NMOSトランジスタ特性においてドレイン−ソース間電圧に対するドレイン電流変化率(若しくはアーリー電圧)に差があると、PMOSトランジスタP2,P3及びNMOSトランジスタN6,N7のミラー比を同じ設定としても各カレントミラー回路の増幅率に差異を生じることになる。

【0079】

これに対して図7においては、PMOSトランジスタP2,P3のカレントミラー回路出力がNMOSトランジスタN8,N9のカレントミラー回路を介して、またNMOSトランジスタN6,N7のカレントミラー回路出力がPMOSトランジスタP4,P5のカレントミラー回路を介して出力される構成としたことにより、PMOSトランジスタP2,P3とNMOSトランジスタN6,N7の各初段のカレントミラー回路の増幅率に差異があったとしても、その出力を増幅する次段のカレントミラー回路が逆極性のMOSトランジスタによる構成であるため上記初段のカレントミラー回路における増幅率の差異を補償することができる。すなわちPMOSトランジスタP2,P3による第1のカレントミラー回路とNMOSトランジスタN8,N9による第4のカレントミラー回路、及びNMOSトランジスタN6,N7による第2のカレントミラー回路とPMOSトランジスタP4,P5による第3のカレントミラー回路、の各カレントミラー回路組み合わせによる発振電流増幅パスはいずれもPMOSトランジスタとNMOSトランジスタとの組み合わせで構成されるためPMOS/NMOS間の各デバイス特性ばらつきを補償できる。

【0080】

本実施例によれば、前記第5の実施例の効果に加えデバイス特性ばらつきによる発振出力特性変動を抑制した発振回路を得ることができる。

【0081】

以上述べてきた本発明の第4,第5,第6の実施例におけるカップリング容量とカレントミラー回路による発振電圧振幅の増幅回路は、図11に示した従来の発振回路において出力バッファ回路2に替えて反転増幅器1出力に設けても反転増幅器1の出力が振動を開始すれば即座にそれを増幅して出力することができるので、従来に比べ発振立ち上がり時間を短縮する効果を有していることは言うまでもない。

【0082】

本発明の第7の実施例を図8に示す。

【0083】

本実施例は、例えば2V以下程度の低電圧下でも動作可能な発振回路に関するものである。上記本発明の他の実施例との相違点としては、昇圧手段30,レベルシフタ31を設けて短絡手段7を構成するNMOSトランジスタN1のゲートを電源VCC電圧以上の昇圧電圧によって駆動していること、及び反転増幅器1や発振検出ゲート21を負荷MOS型インバータで構成している点である。

【0084】

短絡手段7を構成するNMOSトランジスタN1が十分な短絡性能を発揮するためにはそのドレイン,ソース端子電位とゲート端子電位との間にしきい値電圧Vthを上回る十分な電位差が必要である。しかし低電圧下においてはその電位差は縮小し、場合によってはしきい値電圧Vthを下回ってしまうことにもなりかねない。こういった状態においてはNMOSトランジスタN1のドレイン,ソース間が高インピーダンスとなり、それによって短絡動作時に反転増幅器1の入出力がその論理しきい値電圧VLT1にバイアスされるまでの時間が大幅に増大し、本発明の目的である発振立ち上がり時間の短縮に重大な影響を及ぼすことになる。

【0085】

これに対し本実施例の如く、昇圧手段30の昇圧出力電圧によってNMOSトランジスタN1のゲートを駆動することにより、NMOSトランジスタN1のドレイン,ソース端子電位とゲート端子電位との電位差を確保することができ、よって低電圧下であってもNMOSトランジスタN1のドレイン,ソース間を低インピーダンスに保った状態で反転増幅器1の入出力間短絡動作を行うことができる。

【0086】

また反転増幅器1、及び発振検出ゲート21はそれぞれPMOSトランジスタP6とNMOSトランジスタN10、及びPMOSトランジスタP7とNMOSトランジスタN11とから成る負荷MOS型インバータで構成されるが、それら負荷MOS型インバータはその入力電圧レベルがNMOSトランジスタのしきい値電圧Vth以上の電圧範囲においてゲインを有するため、2V以下程度の低電圧下においても反転増幅器としての機能を確保することができる。図8においては、それら負荷MOS型インバータは、PMOSトランジスタP6とPMOSトランジスタP7の各ゲートに共通接続した制御端子C1をLowレベルとすることで活性化される。

【0087】

なお、図8において発振検出ゲート21は他の実施例同様、その入力をカップリング容量8を介して反転増幅器1出力に接続され、入出力間には帰還抵抗9が設けられているが、入出力間短絡手段10は省略されている。これは本発明の第3の実施例の説明でも述べた様に、帰還抵抗9を比較的低い抵抗値に設定することで、必ずしも発振検出ゲート21側の入出力間短絡手段10が必要とは限らないことによる。もちろん短絡手段10を設けても良いわけであるが、その場合短絡手段7同様、低電圧動作時の短絡性能確保のため昇圧手段30の昇圧出力電圧による制御駆動が必要となる。

【0088】

また図8において、発振検出ゲート21と発振出力端子OUTとの間に設けた出力回路20は、発振検出ゲート21の出力振幅を増幅または波形整形して発振回路出力を送出するためのものであり、図1におけるインバータG5,G6等、または図4以降におけるカップリング容量とカレントミラー回路による増幅段構成、などによって構成されるものである。また図8においては、発振検出ゲート21を設けたがこれは必須の構成要素ではなく、出力回路20を反転増幅器1出力に直結した構成も有り得る。これらは目標とする発振回路仕様に応じて適宜設計すれば良い。

【0089】

本実施例によれば、低電圧下でも短絡手段7の短絡性能、及び反転増幅器1の機能を確保できるので、低電圧下においても発振立ち上がり時間を短縮した発振回路を得ることができる。

【0090】

本発明の第8の実施例を図9に示す。

【0091】

図9は、上記図8の第7の実施例における反転増幅器1,発振検出ゲート21を定電流負荷型インバータ構成としたものである。すなわち図9において、反転増幅器1、及び発振検出ゲート21は図8同様PMOSトランジスタP6とNMOSトランジスタN10、及びPMOSトランジスタP7とNMOSトランジスタN11によって構成されているが、PMOSトランジスタP6とPMOSトランジスタP7のゲートは、そのゲート,ドレインを短絡したPMOSトランジスタP8のゲートへ共通接続し、PMOSトランジスタP8とPMOSトランジスタP6,P7とがカレントミラー回路を形成している。PMOSトランジスタP8のドレインは、ゲートをリファレンス電圧源Vrefに、ソースをGNDにそれぞれ接続したNMOSトランジスタN12のドレインに接続し、またPMOSトランジスタP8のゲートへは、ゲートを制御端子C1に接続したPMOSトランジスタP9のドレインが接続している。ここでPMOSトランジスタP9は制御端子C1がLowレベルのときONしてPMOSトランジスタP6,P7,P8のゲートを電源VCC電圧にバイアスし、反転増幅器1、及び発振検出ゲート21の動作を停止するために設けたものである。このとき例えばリファレンス電圧源VrefもLow(GND)レベルに制御すれば、PMOSトランジスタP9とNMOSトランジスタN12間の貫通電流を防止できるが、本実施例の特徴を成すものではないため詳細の記載は省略した。

【0092】

図9においては、NMOSトランジスタN12が基準電流源となり、NMOSトランジスタN12とPMOSトランジスタP8間に流れる電流のミラー比倍が反転増幅器1,発振検出ゲート21の各バイアス電流となっている。すなわち反転増幅器1,発振検出ゲート21を構成するNMOSトランジスタN10,N11の負荷電流が、NMOSトランジスタN12によって規定されている。

【0093】

一方、前記図8における実施例では、上記NMOSトランジスタN10,N11の負荷電流はそれぞれPMOSトランジスタP6,P7が規定しており、この場合PMOSトランジスタ,NMOSトランジスタ間のデバイス特性ばらつきによって反転増幅器としてのゲインに大幅な変動を来たす可能性がある。

【0094】

図9の本実施例では、上記の如く信号を受ける側の能動デバイス、すなわち図9におけるNMOSトランジスタN10,N11と同種のデバイス、すなわちNMOSトランジスタN12によって負荷電流を規定していることから、PMOSトランジスタ,NMOSトランジスタ間のデバイス特性ばらつきの影響を抑制することができ、ゲインの安定化が図れる。すなわち図9においてカレントミラーを形成しているPMOSトランジスタP6,P7,P8のデバイス特性がばらついたとしても、各PMOSトランジスタ間の相対的なばらつきが生じない限りミラー比に変動は無く、よって上記負荷電流の変動も無いからゲインの変動も生じない。

【0095】

反転増幅器1のゲインを安定に保つことは、発振起動時の発振子5との正帰還ループの形成やその後の発振振幅の拡大にとって重要であり、発振立ち上がり特性の安定化につながる。

【0096】

本実施例によれば、デバイス特性ばらつきに対する反転増幅器のゲイン安定化を図ることができるので、前記第7の実施例の効果に加え、デバイスばらつきに対して安定な発振立ち上がり特性を有した発振回路を得ることができる。

【0097】

本発明の第9の実施例を図10に示す。

【0098】

いままで述べてきた他の実施例は、発振起動時いずれも短絡手段7によって反転増幅器1の入出力端子電位をその論理しきい値電圧VLT1にバイアスし、これにより反転増幅器1と発振子5との正帰還ループを早期に形成して発振開始を早めている。しかし電源VCCが低電圧域では、前記第7の実施例で述べた様に短絡手段7のインピーダンス増大の問題があり、これを防止するために昇圧手段30などが必要となる。また昇圧手段30から昇圧出力電圧を発生させるためには、昇圧手段30を動作させるクロックパルス源も通常必要となる。当該発振回路を組み込んだマイクロプロセッサ等の半導体集積回路においては、システムクロック源となる発振回路の起動時に昇圧出力電圧が必要となるわけであるから、例えばリングオシレータ等の自走式の発振回路、または外部クロック等、昇圧手段30を事前に動作させるためのパルス源を別に持たなくてはならない。

【0099】

本実施例は上記の様な回路要素の増大を回避し得る発振回路に関するものである。以下本実施例につき説明する。

【0100】

図10において、端子T1と端子T2との間に他の実施例同様、発振子5と帰還抵抗4とが並列接続し、端子T1及び端子T2とGNDとの間に容量61,62が接続している。反転増幅器1は前記図8の第7の実施例同様PMOSトランジスタP6とNMOSトランジスタN10とから成る負荷MOS型インバータで構成され、NMOSトランジスタN10側のゲートが端子T1に、PMOSトランジスタP6のゲートが制御端子C1に、出力すなわちPMOSトランジスタP6とNMOSトランジスタN10のドレインが抵抗3を介して端子T2に、それぞれ接続している。また発振検出ゲート21も前記図8の第7の実施例同様PMOSトランジスタP7とNMOSトランジスタN11とから成る負荷MOS型インバータで構成され、NMOSトランジスタN11のゲートがカップリング容量8を介して反転増幅器1出力に、PMOSトランジスタP7のゲートが制御端子C1にそれぞれ接続している。そしてその出力すなわちPMOSトランジスタP7とNMOSトランジスタN11のドレインは出力回路20を介して発振出力端子OUTに接続し、またその入力すなわちNMOSトランジスタN11のゲートと出力との間には帰還抵抗9が接続している。出力回路20の構成については第7の実施例の説明で述べた通りである。さらに、反転増幅器1の入力すなわちNMOSトランジスタN10のゲートにドレインを接続するPMOSトランジスタP10から成るスイッチング素子19と、反転増幅器1出力電位を検出して前記スイッチング素子19を制御するための検出回路32と、制御端子C3にゲートを接続したPMOSトランジスタP1から成る励磁電流供給手段18と、制御端子C5にゲートを、反転増幅器1出力にドレインを、GNDにソースをそれぞれ接続したNMOSトランジスタN13と、が設けられている。検出回路32は、スイッチング素子19内PMOSトランジスタP10のゲートにその出力を接続し、一方の入力を制御端子C6に接続したNANDゲートG10と、出力を上記NANDゲートG10のもう一方の入力に接続し、一方の入力を制御端子C6に接続したNANDゲートG8と、出力を上記NANDゲートG8のもう一方の入力に接続し、一方の入力を上記NANDゲートG8の出力に、もう一方の入力を反転増幅器1の出力にそれぞれ接続したNANDゲートG9とから構成されている。

【0101】

以下、本実施例の動作につき説明する。

【0102】

まず発振回路を停止状態におく場合は、制御端子C1,C3,C5をHighレベルに、C6をLowレベルにそれぞれバイアスする。このときPMOSトランジスタP6,P7はOFF状態にあるから反転増幅器1、及び発振検出ゲート21は機能しない。またPMOSトランジスタP1がOFF、NMOSトランジスタN13がON状態にあるから端子T2側電位はGNDレベルとなる。またNANDゲートG10出力がHighとなるからPMOSトランジスタP10はOFF状態にあり、よって帰還抵抗4により端子T1側電位もGNDレベルにある。

【0103】

次いで発振回路を起動する場合、制御端子C5をLowとしてNMOSトランジスタN13をOFFとするとともに、制御端子C3にLowレベルのワンショットパルスを印加し、PMOSトランジスタP1を所定の期間のみONさせて発振子5に励磁電流を供給する。これにより端子T2側電位は電源VCC電位に向かって急峻に上昇するが、端子T1側は帰還抵抗4が高抵抗のためゆるやかに電位上昇を始める。しかる後に制御端子C1をLowとして反転増幅器1,発振検出ゲート21を活性化するが、この時点では端子T1側電位がGNDレベル近傍にあり、反転増幅器1はまだ機能することはできない。

【0104】

このとき、すなわち反転増幅器1を活性化した直後に制御端子C6をHighにすると、NANDゲートG10出力がLowとなりPMOSトランジスタP10がONして端子T1側の電位上昇を加速する。ここでNANDゲートG10出力がLowに反転するのは、制御端子C6をHighにする直前、NANDゲートG8出力がHigh、端子T2電位がHigh、よってNANDゲートG9出力がLowとなっているが、この状態で制御端子C6をHighにすると、NANDゲートG9のLow出力によりNANDゲートG8出力はHighを維持し、よってNANDゲートG10の2入力が共にHighとなってNANDゲートG10出力がLowに反転するものである。そして制御端子C6のバイアスをそのままHighレベルに維持すれば、端子T2電位がLowに反転しない限りこの状態は保持されることになる。

【0105】

上記PMOSトランジスタP10すなわちスイッチング素子19のONにより、端子T1側の電位が上昇して反転増幅器1の論理しきい値電圧VLT1に到達すると、反転増幅器1の出力すなわち端子T2側電位はHighレベルからLowレベルに反転し始める。この端子T2側電位のLow反転を受けてNANDゲートG9出力がHighとなり、これによりNANDゲートG8の2入力が共にHighとなってNANDゲートG8出力がLow、よってNANDゲートG10出力がHighへ復帰してPMOSトランジスタP10がOFFする。この時点で端子T1側の電位上昇は停止し、結果的に端子T1側の電位は反転増幅器1の論理しきい値電圧VLT1近傍にバイアスされた状態となる。端子T2側についてはGNDレベル若しくはその近傍にまで電位が一旦変動し得るが、端子T1側すなわち反転増幅器1の入力電位がVLT1近傍にあることから、反転増幅器1出力すなわち端子T2側電位もやがてはVLT1近傍に安定化される。スイッチング素子19がOFFした時点から反転増幅器1の入力電位はVLT1近傍にあるから、端子T2側の電位変動に依らず反転増幅器1のゲインは確保され発振を開始することができる。図10に示した様にカップリング容量8を介して反転増幅器1出力を受ければ、その出力の電位変動に関わらず反転増幅器1の微小発振振動成分を取り出し、これを発振検出ゲート21、及び出力回路20などによって増幅,波形整形して出力端子OUTに伝達することができる。

【0106】

なお、スイッチング素子19のONにより一旦Lowレベルに反転した端子T2側電位が発振振幅の拡大などによって再びHighレベルになることがあっても、制御端子C6を発振回路の動作期間中Highレベルとすることにより、NANDゲートG8がLow出力を維持するからNANDゲートG9,G10出力がHigh固定となってスイッチング素子19のOFF状態は保持される。

【0107】

また検出回路32は、反転増幅器1の出力反転を検出できれば良いので、通常のCMOSゲート構成としても低電圧動作にも十分対応が可能である。

【0108】

なお図10においては、反転増幅器1、及び発振検出ゲート21を低電圧動作を考慮して第7の実施例同様負荷MOS型インバータのゲート構成としたが、これに限定されるものではなく、例えば図3の第3の実施例に示した様なCMOS構成のゲートによっても同様の動作を得ることができる。但し電源VCC電圧に関し、動作下限値は異なってくる。励磁電流供給手段18、及びNMOSトランジスタN13については、反転増幅器1が活性化されたとき十分な励磁電流供給能力を有し、また停止状態では端子T1,T2電位を固定し得るゲート構成であれば、省略しても良い。また発振検出ゲート21,出力回路20の構成方法についても第7の実施例で述べた様に適宜設計すれば良い。

【0109】

また図10においては、反転増幅器1、及び発振検出ゲート21をPMOS負荷型として発振停止時は端子T1,T2を共にGNDレベルに固定したため、発振起動においてスイッチング素子19には端子T1電位をプルアップする機能を持たせたが、これに限定されるものではなく、例えば反転増幅器1、及び発振検出ゲート21をNMOS負荷型(この場合PMOSトランジスタ側のゲートに端子T1が接続する。)として発振停止時に端子T1,T2を共に電源VCC電位側に固定した様な場合は、励磁電流供給手段18も端子T2とGNDとの間に設けて端子T2側をGNDレベルにバイアスして発振子5の励磁を行うであろうし、この場合端子T1電位はHighレベル側から遷移することになるからスイッチング素子19には端子T1電位をプルダウンする機能を持たせることになる。具体的には図10におけるPMOSトランジスタP10に替えて端子T2とGNDとの間にNMOSトランジスタを設ければ容易にプルダウン機能を有するスイッチング素子19を構成できる。またこの場合反転増幅器1のHighレベル側への出力反転を検出してスイッチング素子19をOFF制御することになるから、検出回路32もそれに見合った構成をとる必要がある。その一例としては、NANDゲートG8,G9,G10をすべてNORゲートに置き換え、図10とは逆に制御端子C6をLowとすることで起動を行う様にすれば良い。

【0110】

本実施例によれば、反転増幅器1の入出力間短絡手段7を用いることなく発振起動時に反転増幅器1の入力電位をその論理しきい値電圧VLT1近傍にバイアスすることができ、他の実施例同様発振立ち上がり時間を短縮した発振回路が得られるとともに、低電圧動作についても、前記第7,第8の実施例の如く昇圧手段30などの回路要素を付加することなく対応が可能であり、比較的小さな回路規模で集積化に有利な発振回路を得ることができる。

【図面の簡単な説明】

【0111】

【図1】本発明の第1の実施例の構成を示す回路図。

【図2】本発明の第2の実施例の構成を示す回路図。

【図3】本発明の第3の実施例の構成を示す回路図。

【図4】本発明の第4の実施例の構成を示す回路図。

【図5】本発明の第4の実施例の構成を示す回路図。

【図6】本発明の第5の実施例の構成を示す回路図。

【図7】本発明の第6の実施例の構成を示す回路図。

【図8】本発明の第7の実施例の構成を示す回路図。

【図9】本発明の第8の実施例の構成を示す回路図。

【図10】本発明の第9の実施例の構成を示す回路図。

【図11】従来の構成を示す回路図。

【符号の説明】

【0112】

1…反転増幅器、2…出力バッファ回路、3…抵抗、4,9…帰還抵抗、5…発振子、7,10…短絡手段、8,11,15…カップリング容量、12,13…バイアス手段、14,16,17…電流源、18…励磁電流供給手段、19…スイッチング素子、20…出力回路、21…発振検出ゲート、22…バッファ回路、30…昇圧手段、31…レベルシフタ、32…検出回路、61,62…容量、C1,C2,C3,C4,C5,C6…制御端子、P1,P2,P3,P4,P5,P6,P7,P8,P9,P10…PMOSトランジスタ、N1,N2,N3,N4,N5,N6,N7,N8,N9,N10,N11,N12,N13…NMOSトランジスタ、OUT…発振出力端子、VCC…電源。

【技術分野】

【0001】

本発明は、水晶発振子またはセラミック発振子等を使用した発振回路に関し、特にマイクロプロセッサ等の半導体集積回路に組み込むのに好適な発振回路に関する。

【背景技術】

【0002】

CMOSゲートによる一般的な発振回路を図11に示す。

【0003】

図11において、端子T1と端子T2との間に水晶発振子またはセラミック発振子(以下、発振子と記す)5と帰還抵抗4とが並列接続し、端子T1と接地(以下、GNDと記す)との間、及び端子T2とGNDとの間にそれぞれ容量61,62が接続している。また2入力NORゲートG1によって反転増幅器1が構成され、その一方の入力は端子T1に、もう一方は制御端子C1に接続し、またその出力は抵抗3を介して端子T2へ、及びインバータG2,G3等から成る出力バッファ回路2を介して発振出力端子OUTへ接続している。

【0004】

図11では反転増幅器としてNORゲートを用いた例を示したがこの他インバータ,NANDゲート,クロックドインバータなどによるものも一般的に用いられている。制御端子C1は発振回路の停止,起動を制御するために設けられたものであり、これは例えばマイクロプロセッサなどに組み込まれた発振回路を動作モードに応じて停止,起動制御を行い消費電力の低減を図る場合などに用いられる。抵抗3はスプリアス発振などの異常発振を防止する目的などで設けられるが省略される場合もある。

【0005】

図11の発振回路を半導体集積回路上に形成する場合、通常NORゲートG1,インバータG2,G3等のCMOSゲート及び抵抗3などが半導体集積回路上に形成され、その他の部品は外付けされる。帰還抵抗4については半導体集積回路上に形成される場合もある。

【0006】

図11の発振回路の動作につき以下説明する。

【0007】

まず制御端子C1がHighレベルにバイアスされている場合、NORゲートG1出力はGNDレベル固定となり、よってNORゲートG1は反転増幅器として機能せず発振回路は停止状態にある。このとき端子T2は当然GNDレベルにあるが、帰還抵抗4により端子T1側もGNDレベルにバイアスされる。

【0008】

次いで制御端子C1がLowレベルにバイアスされると、NORゲートG1は活性化され反転増幅器として機能し得る状態となるが、端子T1側がGNDレベルにバイアスされていたためNORゲートG1出力すなわち端子T2側は一旦VCCレベルに上昇する。この端子T2の電位上昇に伴って、端子T1側も帰還抵抗4により容量61等が充電され電位が徐々に上昇する。端子T1側の電位上昇に伴いNORゲートG1出力すなわち端子T2電位は逆に下降することになる。そして端子T1,端子T2両者の電位がNORゲートG1の論理しきい値電圧(以下、VLT1と記す)程度となった時点で安定する。このときNORゲートG1の反転増幅器としてのゲインは最大となり、NORゲートG1すなわち反転増幅器1と発振子5との間で正帰還ループが形成され発振が開始される。発振開始当初はVLT1レベルを中心電圧とした微小振動であるが、上記正帰還ループにより発振振幅は徐々に拡大し最終的には電源VCC振幅にまで成長する。反転増幅器1の出力振幅が出力バッファ2内インバータG2の論理しきい値電圧(以下、VLT2と記す)を横切って振動するようになるとインバータG2,G3等による発振振幅の増幅及び波形整形が行われ発振出力端子OUTにVCC振幅の発振出力が出現する。

【0009】

以上の概略動作波形を図11内に示した。出力端子OUTの波形を実線及び点線で示しているがいずれを取るかは出力バッファ2内のインバータ段数による。

【発明の開示】

【発明が解決しようとする課題】

【0010】

図11の発振回路においては、制御端子C1がLowレベルとなり発振回路が起動されても端子T1電位がVLT1近傍にバイアスされるまで反転増幅器1は十分なゲインを持ち得ず発振開始に必要な正帰還ループを形成できない。端子T2側もVCCレベルから徐々に低下してくるからその間に反転増幅器1による微小振動の増幅が行われたとしてもその出力振幅がVLT2を横切るものでなければインバータG2による増幅は行われず発振出力は得られない。また端子T1,T2がVLT1にバイアスされ反転増幅器1と発振子5の正帰還ループによる発振を開始しても、VLT1とVLT2との電圧差に相当する振幅にまで発振振幅が増幅されないとやはりインバータG2による増幅は行われず発振出力を取り出すことはできない。

【0011】

端子T1電位がVLT1近傍にバイアスされるまでの時定数は帰還抵抗4に依存するが帰還抵抗4は通常1MΩ程度の値が用いられ、上記時定数は比較的大きいものとなる。さらに正帰還ループの増幅遅れも加味され図11波形における発振立ち上がり時間は、通常数百μs〜数十msを要する。

【0012】

マイクロプロセッサなどに上記発振回路を組み込みその発振出力をシステムクロック源として使用する場合など、上記発振立ち上がり時間の期間中はクロックパルスが得られないことになり、処理は実行不能の状態にある。よって図11に示した従来例では、発振起動後すぐに発振出力を使用して何らかの処理を実行したいといった用途には対応することができない。また発振立ち上がり時間の期間中は、端子T1,T2の電位は中間電位にあるからNORゲートG1やインバータG2などのCMOSゲート部分で貫通電流が流れている。発振出力が得られないにもかかわらず発振回路が電流を消費していることになり、これはまったくの無効な電流消費となってしまう。

【0013】

本発明の目的は、上記発振立ち上がり時間を大幅に短縮し、発振起動直後から発振出力が得られる発振回路を提供すること、及びそれにより無効な電流消費を削減した発振回路を提供することにある。そしてさらにそれらを低電圧動作においても実現し得る発振回路を提供することにある。

【課題を解決するための手段】

【0014】

本願において開示される発明における一実施の形態の概要を簡単に説明すれば、次の通りである。

【0015】

上記目的は、反転増幅器の入力端子電位を反転増幅器の動作電圧(例えば論理しきい値電圧)近傍にバイアスするための回路手段と、反転増幅器の微小振幅出力を常に増幅,波形整形して発振出力端子へ送出し得る出力バッファ回路とを設け、発振起動時に反転増幅器を活性化するとともに端子間(すなわち発振子の両端子間)に電位差を与えて発振子を励磁し、しかる後に上記回路手段を発振子が動作するのに十分な励磁電流が流れる状態となるように所定の期間動作させて反転増幅器の入力端子電位をその動作電圧にバイアスすることにより達成される。

【0016】

なお、低電圧動作に対応する具体的手段、及び上記出力バッファ回路の具体的構成については実施例のなかで明らかにする。

【0017】

発振起動時に反転増幅器を活性化するとともに端子間に電位差を与えることにより発振子に励磁電流が流れ、発振子は微小振動を開始する。その振動周波数は発振子の等価インダクタンス,容量などから決まる共振周波数となる。この発振子の励磁直後においては、端子間の電位差はまだ開いたままであり、帰還抵抗によって両端子電位は緩やかに反転増幅器の動作電圧へ向かって変位を始める。しかる後に、上記回路手段を所定の期間動作させて反転増幅器の入力端子電位を反転増幅器が動作するような所定の電位(例えばVLT1近傍)に強制的にバイアスすることにより、反転増幅器としての機能開始を早めることができるので、反転増幅器と発振子との正帰還ループを早期に形成することができる。さらにその反転増幅器出力を常に増幅可能な出力バッファ回路を設けることにより発振子自体の振幅がまだ微小であっても、電源振幅の発振出力を早期に取り出すことが可能となる。

【発明の効果】

【0018】

本発明の一実施の形態によれば、反転増幅器と発振子との正帰還ループを早期に形成して発振開始を早め、また反転増幅器1からの微小発振出力を増幅,波形整形して発振起動から利用し得る発振出力が得られるまでの発振立ち上がり時間を大幅に短縮した発振回路を得ることができる。

【0019】

また本発明の一実施の形態によれば、反転増幅器からの微小発振出力を増幅,波形整形する出力バッファ回路部分の消費電流を低減した発振回路を得ることができる。

【0020】

また本発明の一実施の形態によれば、発振振幅の増幅にカレントミラー回路を用いたことにより、低電圧下でも上記発振立ち上がり時間を短縮し、良好な発振出力特性を維持し得る発振回路を得ることができる。

【発明を実施するための最良の形態】

【0021】

以下、本発明の第1の実施例を図1により説明する。

【0022】

図1において、端子T1と端子T2との間に発振子5と帰還抵抗4とが並列接続し、端子T1及び端子T2とGNDとの間にそれぞれ容量61,62が接続している。発振子5は等価インダクタンス,容量による等価回路を示した。反転増幅器1は2入力NORゲートG1によって構成され、その一方の入力は端子T1に、もう一方は制御端子C1に接続し、その出力は抵抗3を介して端子T2へ接続している。またその端子T1側の入力と出力との間には短絡手段7が並列接続されている。短絡手段7は、ゲートを制御端子C2へ、ソース,ドレインを反転増幅器1の端子T1側入力とその出力とにそれぞれ接続したNMOSトランジスタN1によって構成されている。また反転増幅器1出力には発振検出ゲート21が接続し、さらにその出力はバッファ回路22を介して発振出力端子OUTに接続されており、発振検出ゲート21とバッファ回路22とで図11における出力バッファ回路2を構成した形となっている。発振検出ゲート21は反転増幅器1を構成する2入力NORゲートG1と同構成の2入力NORゲートG4によって構成され、一方の入力はGNDにバイアスされている。バッファ回路22はインバータG5,G6等で構成しているが、これは発振検出ゲート21の出力をさらに増幅,波形整形して発振出力を得るために設けたものであり、その構成インバータ段数等は必要に応じて適宜設定すれば良い。

【0023】

以下、本実施例の動作につき説明する。

【0024】

まず制御端子C1がHighレベルにバイアスされている場合、NORゲートG1出力はGNDレベル固定となり、よってNORゲートG1は反転増幅器として機能せず発振回路は停止状態にある。このとき端子T2および端子T1は、帰還抵抗4により共にGNDレベルにバイアスされる。NORゲートG1すなわち反転増幅器1出力がGNDレベルのためNORゲートG4すなわち発振検出ゲート21出力はHighレベル(電源VCCレベル)固定となり、発振出力OUTはバッファ回路22のインバータ段数に応じてHighレベルもしくはGNDレベルのいずれかに固定される。

【0025】

発振起動時は、まず制御端子C1をLowレベル(またはGNDレベル)にバイアスすることによりNORゲートG1を活性化する。このとき端子T1側がGNDレベルにバイアスされていたためNORゲートG1出力すなわち端子T2側は、一旦VCCレベルに上昇する。このときの端子T2と端子T1との間に生じた電位差によって発振子5に励磁電流が供給され、発振子は固有周波数すなわち等価インダクタンス,容量などによって決まる共振周波数で微小振動を開始する。端子T1側も帰還抵抗4により容量61等が充電され徐々に電位上昇を始めるが、NORゲートG1が活性化した直後ではまだGNDレベル近傍にあり、NORゲートG1はまだ反転増幅器として機能することができない状態にある。

【0026】

しかる後に図1内波形に示した様に制御端子C2にワンショットパルスを印加し、NMOSトランジスタN1すなわち短絡手段7を所定の期間のみONさせる。NMOSトランジスタN1のONにより、NORゲートG1の入出力間が短絡され端子T1,T2は共にVLT1レベルにバイアスされる。またこのとき容量61,62及び発振子5の閉ループで流れていた発振子5の共振電流は短絡手段7側にバイパスできるようになり、共振電流パスのインピーダンスが下がり共振電流ピークは増大する。これにより発振子5の等価インダクタンスLs等における電圧振幅も増大し発振出力開始に有利となる。

【0027】

制御端子C2のワンショットパルスが終了し元のレベルに復帰すると、NMOSトランジスタN1はOFFするがこのとき端子T1及び端子T2電位はほぼVLT1レベルにあるからNORゲートG1すなわち反転増幅器1のゲインは最大となり、反転増幅器1と発振子5との間で正帰還ループが形成され発振が即開始される。発振開始当初、反転増幅器1出力はVLT1レベルを中心電圧とした微小振動ではあるが、これを受ける発振検出ゲート21が反転増幅器1を構成するNORゲートG1と同構成のNORゲートG4で構成しているためそれらの論理しきい値電圧は等しく、よってVLT1レベルを中心電圧とした反転増幅器1出力の微小振動をすぐに増幅することができる。バッファ回路22内インバータG5,G6等の論理しきい値電圧がVLT1からずれていたとしても発振検出ゲート21によって反転増幅器1出力振幅が一旦増幅されているからバッファ回路22による発振振幅の増幅及び波形整形もすぐに開始することができる。

【0028】

制御端子C2のワンショットパルス幅は端子T1,T2をVLT1レベルにバイアスするのに必要十分な程度のパルス幅とすれば良く、例えば数μs程度以下とすることもできる。よって図11従来例に比べ、制御端子C1による発振回路起動開始から早期に発振出力を得ることができる。

【0029】

以上の如く本実施例によれば、発振起動から早期に反転増幅器1と発振子5との正帰還ループを形成することができ、また反転増幅器1出力を直ちに増幅して出力端子OUTに送出できるので、発振起動から発振出力開始までの時間すなわち発振立ち上がり時間を大幅に短縮した発振回路を得ることができる。またそれゆえ発振開始までの無効な電流消費を低減した発振回路を得ることができる。

【0030】

なお図1において、反転増幅器1及び発振検出ゲート21をNORゲートで構成したがこれに限定されるものではなく、インバータ,NANDゲート,クロックドインバータ、または負荷MOS型インバータなど低電圧動作にも対応したゲートなど、他のゲート構成によっても同様の効果を得ることができる。短絡手段7についてもNMOSトランジスタN1による構成以外に例えばPMOSトランジスタ、あるいはPMOSトランジスタとNMOSトランジスタを並列接続したトランスファゲート、などによっても同様の作用を実現できる。また抵抗3は発振安定化のために必要に応じて設定すべきものであり省略することもできる。なお、これらは以降の実施例においても同様である。

【0031】

本発明の第2の実施例を図2に示す。

【0032】

本実施例は上記図1に示した第1の実施例に対し、制御端子C3にゲートを、電源VCC及び反転増幅器1出力にソース及びドレインをそれぞれ接続したPMOSトランジスタP1から成る励磁電流供給手段18を付加した構成となっている。図2には制御端子C1,C2,C3への印加信号タイミング例も示している。

【0033】

発振停止状態においては、制御端子C1,C3をHighレベルにバイアスすることにより第1の実施例同様反転増幅器1出力をGNDレベル固定とし、またPMOSトランジスタP1すなわち励磁電流供給手段18はOFF状態としておく。

【0034】

次いで発振起動時は制御端子C1をLowレベルとしてNORゲートG1を活性化するとともに制御端子C3にLowレベルのワンショットパルスを印加する。制御端子C3がLowレベルの期間中はPMOSトランジスタP1もONすることにより端子T2部を急速に充電すると共に発振子5に励磁電流を供給する。

【0035】

制御端子C3がHighレベルに復帰しPMOSトランジスタP1がOFFした後は第1の実施例同様、制御端子C2にワンショットパルスを印加してNORゲートG1の入出力間を短絡し、端子T1,T2をVLT1にバイアスすることによって反転増幅器1と発振子5との正帰還ループを早期に形成する。

【0036】

本実施例によれば前記第1の実施例の効果に加え、励磁電流供給手段18を設けたことにより反転増幅器1を構成するゲートから起動時の発振子励磁電流を供給する必要が無くなったため反転増幅器1を構成するゲートの電流駆動能力を発振状態を維持し得る程度に設定することができ、消費電流を低減した発振回路を得ることができる。

【0037】

本実施例においては端子T2側に励磁電流供給手段18を設けたが、これを端子T1側に設けても同様の効果を得ることができる。その場合NORゲートG1の活性化と同時に励磁電流供給手段18により端子T1側がVCCレベルにバイアスされることになり、励磁電流供給手段18がONしている間NORゲートG1出力はGNDレベルとなるとともに端子T1,T2間に電位差が与えられ発振子5の励磁が行われる。

【0038】

なお、反転増幅器1としてNANDゲートを用いた場合、発振停止状態はNORゲートG1の場合とは逆にNANDゲート入力につながる制御端子をLowレベルとすることにより、端子T1,T2電位が共にHighレベル側に固定されることになるから、この場合励磁電流供給手段18は端子T1、若しくは端子T2とGNDとの間に設け、発振起動時に発振子の励磁電流をGND側に引き抜くことになる。

【0039】

なお、図2における励磁電流供給手段18はPMOSトランジスタP1で構成したが、これに限られるものではなく例えばNMOSトランジスタ等を用いても良い。

【0040】

また以降の実施例においては特に必要の無い限り励磁電流供給手段18の記載を省略するが、いずれの実施例においてもこれを併設することは可能であり本実施例の効果を享受できることは言うまでもない。

【0041】

本発明の第3の実施例を図3に示す。

【0042】

図3において、反転増幅器1,短絡手段7、及び帰還抵抗4,発振子5、及び容量61,62等の接続構成は図1の第1の実施例同様であるが、反転増幅器1出力はカップリング容量8を介して発振検出ゲート21に接続し、発振検出ゲート21の入出力間には帰還抵抗9と短絡手段10とが並列接続している。短絡手段10はゲートを制御端子C4へ、ソース,ドレインを発振検出ゲート21の入力,出力へそれぞれ接続したNMOSトランジスタN2によって構成されている。また発振検出ゲート21は、NORゲートG7で構成され一方の入力がカップリング容量8へ、もう一方の入力が制御端子C1へ接続している。その出力を受けるバッファ回路22については図1の第1の実施例同様である。

【0043】

以下本実施例の動作につき説明する。

【0044】

発振停止状態においては、制御端子C1をHighレベルにバイアスすることによりNORゲートG1から成る反転増幅器1出力、及びNORゲートG7から成る発振検出ゲート21出力をGNDレベル固定とし、また制御端子C2,C4はLowレベルにバイアスしてNMOSトランジスタN1,N2から成る短絡手段7,10をOFF状態としておく。

【0045】

発振起動時においては図1の第1の実施例同様、制御端子C1をLowレベルとしてNORゲートG1を活性化して発振子5を励磁し、しかる後に制御端子C2へワンショットパルスを印加して短絡手段7により所定の期間端子T1,T2間の短絡を行う。このとき制御端子C1へ入力を接続するNORゲートG7もNORゲートG1と同時に活性化し、またその後制御端子C4へもワンショットパルスを印加してNMOSトランジスタN2から成る短絡手段10によりNORゲートG7の入出力動作点をその論理しきい値電圧に急速にバイアスする。制御端子C4のワンショットパルスが復帰するとNORゲートG7の入力電位はその論理しきい値電圧となっているからすぐに発振検出ゲートとして機能し始める。

【0046】

発振検出ゲート21によって反転増幅器1の微小出力振幅を増幅しているときに、端子T1側のリーク電流等によって反転増幅器1の出力振幅中心電圧が変動した場合、図1,図2に示した実施例においては発振検出ゲート21の入力電圧レベルがその論理しきい値電圧から変動することとなり、発振検出ゲート21が感応できなくなって発振出力不能となる可能性がある。しかし本実施例によれば、発振検出ゲート21に帰還抵抗9を設けることで発振検出ゲート21の入力インピーダンスが低減され、かつカップリング容量8を介して反転増幅器1出力を受けていることにより、上記の様な反転増幅器1の出力電圧レベル変動による発振検出ゲート21の入力電圧レベルへの影響はほとんど無く、発振検出ゲート21は常にその論理しきい値電圧を中心電圧とした動作点で安定な増幅を行うことができる。また短絡手段10により、発振起動時に発振検出ゲート21の動作点を速やかに確定することができ、発振立ち上がり時間を延ばすことなく発振検出ゲート21の安定化を図ることができる。

【0047】

なお、帰還抵抗9を帰還抵抗4などに比べて低抵抗設定とし、発振検出ゲート21の動作点確定が速やかに行える様にすることにより、短絡手段10及び制御端子C4を省略することも可能である。

【0048】

また制御端子C4のワンショットパルスの立下がりすなわち短絡手段10のOFFタイミングを、図3内タイミングに示した様に制御端子C2の立下がりすなわち短絡手段7のOFFタイミングより遅らせることにより、制御端子C2電位変動に伴う雑音電荷の影響、すなわち発振検出ゲート21入力電圧の一時的な低下等を防止することもできる。

【0049】

本実施例によれば、前記第1の実施例の効果に加え、発振子の端子電圧のレベル変動に対しても安定に発振出力を成し得る発振回路を得ることができる。

【0050】

なお本実施例においては制御端子C1によって発振検出ゲート21の制御を行ったがこれに限定されるものではなく、発振検出ゲート21の活性化が反転増幅器1と同時でなくても良い。

【0051】

本発明の第4の実施例を図4に示す。

【0052】

図4においては、上記図3の第3の実施例におけるバッファ回路22に代えてPMOSトランジスタP2とPMOSトランジスタP3との互いのゲートを接続しPMOSトランジスタP2側のゲート,ドレインを短絡接続して成るカレントミラー回路と、PMOSトランジスタP2のドレインと発振検出ゲート21出力との間に接続するカップリング容量11と、PMOSトランジスタP2のドレインとGNDとの間に接続するバイアス手段12と、PMOSトランジスタP3のドレインとGNDとの間に接続するバイアス手段13と、を設け、PMOSトランジスタP3とバイアス手段13との接続点を出力OUTとして発振出力を取り出す構成としている。またバイアス手段12,13はそれぞれ抵抗RB1,RB2で構成されている。

【0053】

本実施例における発振停止及び起動制御については、上記図3の第3の実施例同様である。発振起動直後における状態についてみると、いずれの実施例においても反転増幅器1の微小出力振幅を発振検出ゲート21が増幅はするものの振幅は小さくその出力電圧振幅レベルはまだ発振検出ゲート21の論理しきい値電圧近傍にある。発振検出ゲート21の出力振幅が拡大するには反転増幅器1の微小出力振幅自体の拡大が必要であり電源VCC振幅にまで拡大するには相当な時間を要する。前記図3の第3の実施例等においてはその発振検出ゲート21出力振幅拡大までの期間、発振検出ゲート21出力を受けるバッファ回路22内インバータG5からみれば中間レベルの入力電圧が印加されていることになり、インバータG5等がCMOS構成であれば貫通電流が流れることになる。インバータG5出力振幅が電源VCC振幅にまで増幅されていなければさらにインバータG6部でも貫通電流が流れることになる。

【0054】

また前記図3の第3の実施例等においては、発振検出ゲート21とバッファ回路22内インバータG5との各論理しきい値電圧の差がデバイスばらつき等によって拡大すればその分インバータG5が感応する電圧レベルにまで発振検出ゲート21出力振幅が拡大するまでの時間が必要となり、発振出力開始に遅れを来すことになる。すなわちインバータG5の論理しきい値電圧は常に発振検出ゲート21の発振出力の中心電圧レベル近傍にあることが必要とされる。

【0055】

本実施例は上記問題を対策しようとするものである。

【0056】

図4において、バイアス手段12は消費電流上さほど問題にならない程度、例えば数μA程度の電流バイアスをPMOSトランジスタP2に与える様設定し、PMOSトランジスタP2を能動状態におく。これによりPMOSトランジスタP2動作点すなわちそのドレイン電圧は電源VCCからPMOSトランジスタP2のゲート,ドレイン間電圧VGS分低下したレベルにバイアスされる。一方、発振検出ゲート21出力は発振起動後その論理しきい値電圧を中心電圧とした電圧振動を開始するが、その発振検出ゲート21の出力電圧変動は、カップリング容量11部の変位電流を介してPMOSトランジスタP2のドレイン電流変動に変換されることになる。すなわち発振検出ゲート21の出力電圧が上昇方向に変動するときはカップリング容量11部の変位電流は発振検出ゲート21出力側からPMOSトランジスタP2のドレイン側に向かう方向に流れ、PMOSトランジスタP2のドレイン電流を減衰させる。逆に発振検出ゲート21の出力電圧が下降方向に変動するときはカップリング容量11部の変位電流は上記とは逆にPMOSトランジスタP2のドレイン側から発振検出ゲート21出力側に向かう方向に流れ、PMOSトランジスタP2のドレイン電流を増加させる。このPMOSトランジスタP2のドレイン電流変動はカレントミラー接続されたPMOSトランジスタP3側へ伝達され、ミラー比倍されてPMOSトランジスタP3の出力電流変動となって現われる。PMOSトランジスタP3側には、バイアス手段12によるPMOSトランジスタP2部のバイアス電流のミラー比倍に相当するドレイン電流が流れることになるが、上記変動分がそれに重畳するかたちになる。このPMOSトランジスタP3のドレイン電流は抵抗RB2から成るバイアス手段13へ流れ電圧振幅に変換されて出力端子OUTから取り出されることになる。以上の様に本実施例によれば、発振検出ゲート21の出力電圧変動分をPMOSトランジスタP2の出力電流変動に変換し、これを増幅する機構であるため、発振検出ゲート21の発振出力の中心電圧レベルに依存することなく発振振幅の増幅が可能となる。

【0057】

図4に示した実施例においては、バイアス手段12による直流バイアス電流成分も抵抗RB2から成るバイアス手段13に流れ、これによる電位降下が発生する。またPMOSトランジスタP3ドレイン電流のピーク時点でも出力端子OUT電位はPMOSトランジスタP3のオン抵抗成分と抵抗RB2との分圧電位となるから、図4における出力端子OUTの発振出力電圧振幅は電源VCC電圧とGND間の振幅よりは狭まったものとなる。しかし出力端子OUTにCMOSインバータ等を付加すれば容易に波形整形が可能であり、また発振検出ゲート21の出力振幅に比べ十分拡大された電圧振幅が得られるから出力端子OUTを受けるCMOSインバータ等のゲート部分での貫通電流は前記図3等におけるインバータG5におけるものより大幅に低減されたものとなる。

【0058】

なお上記図4に示す構成においては、バイアス手段12,13等に流れる直流バイアス電流を抑制し、またPMOSトランジスタP3の出力電流振幅から大きな電圧振幅を得るためにも抵抗RB1,RB2を比較的高抵抗とする必要があるが、これは集積化の点で不利となる。そこで図5に示す様に抵抗RB1,RB2をMOSトランジスタによる定電流回路に置き換えた構成とすることもできる。以下、図5に示す構成につき説明する。

【0059】

図5において、上記図4におけるバイアス手段12,13はそれぞれNMOSトランジスタN4,N5で構成されている。PMOSトランジスタP2ドレインとGNDにNMOSトランジスタN4のドレイン,ソースが、またPMOSトランジスタP3ドレインとGNDにNMOSトランジスタN5のドレイン,ソースがそれぞれ接続し、NMOSトランジスタN4,N5の各ゲートは、ゲート,ドレインを短絡接続しソースをGNDに接続するNMOSトランジスタN3のゲートへ共通接続している。NMOSトランジスタN3のドレインと電源VCCとの間には電流源14が設けられている。

【0060】

NMOSトランジスタN3とNMOSトランジスタN4、及びNMOSトランジスタN5はカレントミラー接続となっているから、NMOSトランジスタN4、及びNMOSトランジスタN5のドレイン電流すなわちPMOSトランジスタP2とPMOSトランジスタP3のバイアス電流は電流源14の電流とそれらのミラー比によって決まる。いまNMOSトランジスタN4とNMOSトランジスタN5とのミラー比を、PMOSトランジスタP2とPMOSトランジスタP3のミラー比と同じに設定すれば、NMOSトランジスタN4とPMOSトランジスタP2のドレイン電流は同値であるからそれらをそれぞれミラー比倍したNMOSトランジスタN5とPMOSトランジスタP3の各ドレイン電流も等しいことになる。このようなバイアス設定によれば、以下に詳しく述べるが発振時にPMOSトランジスタP3のドレイン電流に重畳する電流振動を過不足無く電圧振幅に変換することができる。しかもこのバイアス設定は発振電流増幅を行うPMOSトランジスタP2,P3とバイアス電流源のNMOSトランジスタN4,N5の各MOSトランジスタ寸法によるミラー比設定によって実現され、電流源14等の絶対値には依らないので集積化には極めて好適である。本構成による増幅動作につき以下説明する。

【0061】

発振検出ゲート21の出力が仮にまだ振動を開始していない状態を想定すると、このときPMOSトランジスタP3とNMOSトランジスタN5の各ドレイン電流駆動能力は上記の如くちょうどつりあった状態にある。その状態から発振が開始して発振検出ゲート21の発振出力電圧振動が電圧下降方向に振れ、PMOSトランジスタP3のドレイン電流が増加方向に振れたとすると、NMOSトランジスタN5に対しPMOSトランジスタP3のドレイン電流駆動能力が上回ることになるから出力端子OUTの動作点は急速に電源VCCに向かって上昇する。そしてNMOSトランジスタN5のドレイン電流を供給し得るPMOSトランジスタP3のドレイン−ソース間電圧VDS分だけ電源VCCから低下した電位まで上昇して安定する。逆に発振検出ゲート21の発振出力電圧振動が電圧上昇方向に振れ、PMOSトランジスタP3のドレイン電流が減少方向に振れたときは、PMOSトランジスタP3のドレイン電流駆動能力がNMOSトランジスタN5よりも下回ることになり出力端子OUTの動作点は急速にGND電位に向かって下降する。そしてPMOSトランジスタP3のドレイン電流を流し得るNMOSトランジスタN5のドレイン−ソース間電圧VDS分だけGNDから浮いた電位で安定する。上記PMOSトランジスタP3及びNMOSトランジスタN5のVDS電圧については、いずれも非飽和領域の動作となるからその値は比較的小さく、よって出力端子OUTの電圧振幅としては電源VCC電圧に近い振幅を得ることができる。

【0062】

以上の如く図4または図5に示す第4の実施例によれば前記第3の実施例の効果に加え、CMOSゲートに替えてカレントミラー回路を利用して微小発振電圧振幅の増幅を行ったことにより、CMOSゲートによる場合の貫通電流の問題を回避でき消費電流低減に有効な発振回路を得ることができる。また発振電圧振動をカップリング容量を介して電流振動に変換して増幅したことにより、発振電圧振動の中心電圧レベルに依存せずにその電圧変動分のみを抽出して増幅することができ、デバイスばらつきによる発振動作点レベルの変動等に対しても安定に発振出力が得られる発振回路を得ることができる。

【0063】

また前記図3の第3の実施例等において反転増幅器1及び発振検出ゲート21に負荷MOS型インバータ等のゲートを用い、例えば2V以下程度の低電圧下で発振動作を行おうとした場合、バッファ回路22をCMOSゲートで構成すれば発振検出ゲート21の出力振幅が十分拡大しないとCMOSゲートが感応せず、よって発振出力開始が遅れることになる。またバッファ回路22にも負荷MOS型インバータ等のゲートを用いて低電圧下における感度を上げようとすればその分消費電流増大につながってしまう。

【0064】

上記本実施例によれば、カレントミラー回路がそれを構成するMOSトランジスタのしきい値電圧Vth以上の電圧があれば動作可能であるため、上記の様な低電圧下における発振にも好適な発振回路が得られるという効果も有している。

【0065】

なお図4及び図5においては、図3に示されたカップリング容量8と発振検出ゲート21の構成を反転増幅器1の出力バッファとして流用したが、PMOSトランジスタP2,P3のカレントミラー回路による増幅に問題がなければこれを使用しなくても良い。すなわちカップリング容量8と発振検出ゲート21を廃し、カップリング容量11を反転増幅器1出力に直結しても良い。これは適宜設計上決められるべきことである。また図4,図5においてはカレントミラー回路の出力を発振出力端子OUTとしているが、上記説明でも述べた様に特に発振開始直後の発振電圧振幅が微小な期間においてはバイアス電流のために発振出力端子OUTの動作点振幅は中間レベルにあり電源VCC振幅にはならない。そこで図4,図5における端子OUTにCMOSゲートなどを設けてそのゲートの出力を発振出力端子として電源VCC振幅の発振出力を得るようにしても良い。ただいずれの実施例においても当該発振回路を半導体基板上に集積化して利用する場合その発振出力端子OUTには必ずそれを受けるCMOSゲート等が存在し、該CMOSゲート等において波形整形が為されることになる。図4以降に示す本発明の実施例においてはそれらの波形整形用バッファゲートについては記載を省略し、本発明の特徴を成す構成要素のみの記載としている。

【0066】

本発明の第5の実施例を図6に示す。

【0067】

図6において、発振子5周辺から発振検出ゲート21までの構成は前記図3の第3の実施例同様である。そしてPMOSトランジスタP2とPMOSトランジスタP3の互いのゲートを接続しPMOSトランジスタP2側のゲート,ドレインを短絡接続して成る第1のカレントミラー回路と、PMOSトランジスタP2のドレインとGNDとの間に接続するバイアス電流源16と、NMOSトランジスタN6とNMOSトランジスタN7の互いのゲートを接続しNMOSトランジスタN6側のゲート,ドレインを短絡接続して成る第2のカレントミラー回路と、NMOSトランジスタN6のドレインと電源VCCとの間に接続するバイアス電流源17と、PMOSトランジスタP2のドレインと発振検出ゲート21出力との間に接続するカップリング容量11と、NMOSトランジスタN6のドレインと発振検出ゲート21出力との間に接続するカップリング容量15と、を設けPMOSトランジスタP3ドレインとNMOSトランジスタN7ドレインとを接続して発振出力端子OUTとしている。

【0068】

以下本実施例の動作につき説明する。なお発振停止,起動等の制御については上記第3,第4の実施例同様であるので説明は省略する。

【0069】

上記第1のカレントミラー回路と第2のカレントミラー回路のミラー比が同じになる様各MOSトランジスタ寸法が設定され、またバイアス電流源16,17の各電流値が同程度に設定されているものとすると、各カレントミラー回路出力すなわちPMOSトランジスタP3とNMOSトランジスタN7のドレイン電流はほぼ等しい状態となる。この状態において、発振検出ゲート21が発振出力を開始したときの動作を以下説明する。なお、ここでバイアス電流源16,17はPMOSトランジスタP2及びNMOSトランジスタN6を能動状態におくためのバイアス電流を供給するものであり、前記図4,図5におけるバイアス手段12と同様の目的で設けているものである。

【0070】

まず発振検出ゲート21の発振出力電圧振動が上昇方向に振れると、カップリング容量11,15にはそれぞれ発振検出ゲート21出力からPMOSトランジスタP2ドレインへ、及び発振検出ゲート21出力からNMOSトランジスタN6ドレインへ向かう変位電流が生じる。これによりPMOSトランジスタP2側のドレイン電流は減衰方向、NMOSトランジスタN6側のドレイン電流は増加方向に変動し、その電流変動はミラー比倍されてそれらとカレントミラー接続したPMOSトランジスタP3及びNMOSトランジスタN7のドレイン電流変動となる。その結果NMOSトランジスタN7のドレイン電流駆動能力がPMOSトランジスタP3のドレイン電流駆動能力を上回ることになり発振出力端子OUTの動作点は急速にGND電位に向かって下降する。

【0071】

次いで発振検出ゲート21の発振出力電圧振動が下降方向に振れると、カップリング容量11,15にはそれぞれPMOSトランジスタP2ドレインから発振検出ゲート21出力へ、及びNMOSトランジスタN6ドレインから発振検出ゲート21出力へ向かう変位電流が生じる。これによりPMOSトランジスタP2側のドレイン電流は増加方向、NMOSトランジスタN6側のドレイン電流は減衰方向に変動し、その電流変動はやはりミラー比倍されてそれらとカレントミラー接続したPMOSトランジスタP3及びNMOSトランジスタN7のドレイン電流変動となる。その結果今度はPMOSトランジスタP3のドレイン電流駆動能力がNMOSトランジスタN7のドレイン電流駆動能力を上回ることになり発振出力端子OUTの動作点は急速に電源VCC電位に向かって上昇する。

【0072】

本実施例においては、PMOSトランジスタP3とNMOSトランジスタN7とが排他的に動作することになるため、発振出力端子OUTの負荷駆動能力を向上できるとともに、前記第4の実施例に比べより拡大した発振出力振幅を得ることができる。これは例えばPMOSトランジスタP3側の電流駆動能力が増加して発振出力端子OUTの電位を上昇させようとするとき、NMOSトランジスタN7側のドレイン電流が減衰するからPMOSトランジスタP3にとっての負荷電流が減衰することになり相対的にPMOSトランジスタP3の負荷駆動能力が向上して発振出力端子OUT電位を急速に上昇させる。またこのときPMOSトランジスタP3の負荷電流が減衰したことによりPMOSトランジスタP3のソース−ドレイン間の電位降下が減少し、よって発振出力端子OUTの到達電位はより電源VCCに近づくことになる。NMOSトランジスタN7側の電流駆動能力が増加する場合についても同様であり、よりGND電位に近づくことになるから、結局第4の実施例に比べて発振出力電圧振幅を拡大することができる。

【0073】

なお、発振検出ゲート21の発振出力電圧振幅によるカップリング容量11,15の変位電流が、電流源16,17の電流値を超える程度まで発振電圧振幅が拡大してくるとPMOSトランジスタP2またはNMOSトランジスタN6のいずれかが遮断状態になるからPMOSトランジスタP3とNMOSトランジスタN7は完全に排他動作となり、発振出力端子OUTには電源VCC電圧振幅の発振出力が得られることになる。

【0074】

本実施例によれば、前記第4の実施例の効果に加えさらに発振出力特性を改善した発振回路を得ることができる。

【0075】

本発明の第6の実施例を図7に示す。

【0076】

図7においては、上記図6の構成に加えPMOSトランジスタP4とPMOSトランジスタP5の互いのゲートを接続しPMOSトランジスタP4側のゲート,ドレインを短絡接続して成る第3のカレントミラー回路と、NMOSトランジスタN8とNMOSトランジスタN9の互いのゲートを接続しNMOSトランジスタN8側のゲート,ドレインを短絡接続して成る第4のカレントミラー回路と、を設け、PMOSトランジスタP3のドレインはNMOSトランジスタN8のドレインへ、NMOSトランジスタN7のドレインはPMOSトランジスタP4のドレインへそれぞれ分離接続し、PMOSトランジスタP5のドレインとNMOSトランジスタN9のドレインとを接続して発振出力端子OUTとしている。

【0077】

発振検出ゲート21からの発振電圧振動をPMOSトランジスタP3及びNMOSトランジスタN7のドレイン電流変動に変換増幅するまでは上記図6に示した第5の実施例と同様である。図7においてはそれらドレイン電流をさらにNMOSトランジスタN8及びPMOSトランジスタP4のドレイン電流として与え、それぞれNMOSトランジスタN8,N9及びPMOSトランジスタP4,P5の各カレントミラー回路によりNMOSトランジスタN9及びPMOSトランジスタP5側へ増幅伝達する。PMOSトランジスタP3とNMOSトランジスタN7とは上記第5の実施例において述べた様に排他的に動作しているのでそれらの各ドレイン電流を増幅したPMOSトランジスタP5とNMOSトランジスタN9も排他的に動作することとなり、発振出力端子OUTに電圧振幅を出力する。

【0078】

上記図6の第5の実施例においては、PMOSトランジスタP2,P3及びNMOSトランジスタN6,N7の各カレントミラー回路の増幅率がほぼ一致していることが必要である。もしその増幅率が違っていると出力側のPMOSトランジスタP3若しくはNMOSトランジスタN7のいずれかにより多くの電流バイアスがかかり、結果として出力電圧振幅が電源VCC側若しくはGND側に片寄ったものとなり極端な場合は振幅がつぶれて発振出力が得られなくなってしまう。そこでPMOSトランジスタP2,P3及びNMOSトランジスタN6,N7の各MOSトランジスタ寸法比を同じにしてミラー比、すなわち上記増幅率を合わせる様に設定しているわけであるが、各カレントミラー回路を構成するMOSトランジスタの種類がPMOS,NMOSと異なっているためそのデバイス特性ばらつき等によって上記増幅率に差異を生じる場合がある。例えば図6におけるPMOSトランジスタP2とP3、及びNMOSトランジスタN6とN7についてみると、各MOSトランジスタにおけるドレイン−ソース間電圧は異なっている。よってPMOSトランジスタ,NMOSトランジスタ特性においてドレイン−ソース間電圧に対するドレイン電流変化率(若しくはアーリー電圧)に差があると、PMOSトランジスタP2,P3及びNMOSトランジスタN6,N7のミラー比を同じ設定としても各カレントミラー回路の増幅率に差異を生じることになる。

【0079】

これに対して図7においては、PMOSトランジスタP2,P3のカレントミラー回路出力がNMOSトランジスタN8,N9のカレントミラー回路を介して、またNMOSトランジスタN6,N7のカレントミラー回路出力がPMOSトランジスタP4,P5のカレントミラー回路を介して出力される構成としたことにより、PMOSトランジスタP2,P3とNMOSトランジスタN6,N7の各初段のカレントミラー回路の増幅率に差異があったとしても、その出力を増幅する次段のカレントミラー回路が逆極性のMOSトランジスタによる構成であるため上記初段のカレントミラー回路における増幅率の差異を補償することができる。すなわちPMOSトランジスタP2,P3による第1のカレントミラー回路とNMOSトランジスタN8,N9による第4のカレントミラー回路、及びNMOSトランジスタN6,N7による第2のカレントミラー回路とPMOSトランジスタP4,P5による第3のカレントミラー回路、の各カレントミラー回路組み合わせによる発振電流増幅パスはいずれもPMOSトランジスタとNMOSトランジスタとの組み合わせで構成されるためPMOS/NMOS間の各デバイス特性ばらつきを補償できる。

【0080】

本実施例によれば、前記第5の実施例の効果に加えデバイス特性ばらつきによる発振出力特性変動を抑制した発振回路を得ることができる。

【0081】

以上述べてきた本発明の第4,第5,第6の実施例におけるカップリング容量とカレントミラー回路による発振電圧振幅の増幅回路は、図11に示した従来の発振回路において出力バッファ回路2に替えて反転増幅器1出力に設けても反転増幅器1の出力が振動を開始すれば即座にそれを増幅して出力することができるので、従来に比べ発振立ち上がり時間を短縮する効果を有していることは言うまでもない。

【0082】

本発明の第7の実施例を図8に示す。

【0083】

本実施例は、例えば2V以下程度の低電圧下でも動作可能な発振回路に関するものである。上記本発明の他の実施例との相違点としては、昇圧手段30,レベルシフタ31を設けて短絡手段7を構成するNMOSトランジスタN1のゲートを電源VCC電圧以上の昇圧電圧によって駆動していること、及び反転増幅器1や発振検出ゲート21を負荷MOS型インバータで構成している点である。

【0084】

短絡手段7を構成するNMOSトランジスタN1が十分な短絡性能を発揮するためにはそのドレイン,ソース端子電位とゲート端子電位との間にしきい値電圧Vthを上回る十分な電位差が必要である。しかし低電圧下においてはその電位差は縮小し、場合によってはしきい値電圧Vthを下回ってしまうことにもなりかねない。こういった状態においてはNMOSトランジスタN1のドレイン,ソース間が高インピーダンスとなり、それによって短絡動作時に反転増幅器1の入出力がその論理しきい値電圧VLT1にバイアスされるまでの時間が大幅に増大し、本発明の目的である発振立ち上がり時間の短縮に重大な影響を及ぼすことになる。

【0085】

これに対し本実施例の如く、昇圧手段30の昇圧出力電圧によってNMOSトランジスタN1のゲートを駆動することにより、NMOSトランジスタN1のドレイン,ソース端子電位とゲート端子電位との電位差を確保することができ、よって低電圧下であってもNMOSトランジスタN1のドレイン,ソース間を低インピーダンスに保った状態で反転増幅器1の入出力間短絡動作を行うことができる。

【0086】

また反転増幅器1、及び発振検出ゲート21はそれぞれPMOSトランジスタP6とNMOSトランジスタN10、及びPMOSトランジスタP7とNMOSトランジスタN11とから成る負荷MOS型インバータで構成されるが、それら負荷MOS型インバータはその入力電圧レベルがNMOSトランジスタのしきい値電圧Vth以上の電圧範囲においてゲインを有するため、2V以下程度の低電圧下においても反転増幅器としての機能を確保することができる。図8においては、それら負荷MOS型インバータは、PMOSトランジスタP6とPMOSトランジスタP7の各ゲートに共通接続した制御端子C1をLowレベルとすることで活性化される。

【0087】

なお、図8において発振検出ゲート21は他の実施例同様、その入力をカップリング容量8を介して反転増幅器1出力に接続され、入出力間には帰還抵抗9が設けられているが、入出力間短絡手段10は省略されている。これは本発明の第3の実施例の説明でも述べた様に、帰還抵抗9を比較的低い抵抗値に設定することで、必ずしも発振検出ゲート21側の入出力間短絡手段10が必要とは限らないことによる。もちろん短絡手段10を設けても良いわけであるが、その場合短絡手段7同様、低電圧動作時の短絡性能確保のため昇圧手段30の昇圧出力電圧による制御駆動が必要となる。

【0088】

また図8において、発振検出ゲート21と発振出力端子OUTとの間に設けた出力回路20は、発振検出ゲート21の出力振幅を増幅または波形整形して発振回路出力を送出するためのものであり、図1におけるインバータG5,G6等、または図4以降におけるカップリング容量とカレントミラー回路による増幅段構成、などによって構成されるものである。また図8においては、発振検出ゲート21を設けたがこれは必須の構成要素ではなく、出力回路20を反転増幅器1出力に直結した構成も有り得る。これらは目標とする発振回路仕様に応じて適宜設計すれば良い。

【0089】

本実施例によれば、低電圧下でも短絡手段7の短絡性能、及び反転増幅器1の機能を確保できるので、低電圧下においても発振立ち上がり時間を短縮した発振回路を得ることができる。

【0090】

本発明の第8の実施例を図9に示す。

【0091】

図9は、上記図8の第7の実施例における反転増幅器1,発振検出ゲート21を定電流負荷型インバータ構成としたものである。すなわち図9において、反転増幅器1、及び発振検出ゲート21は図8同様PMOSトランジスタP6とNMOSトランジスタN10、及びPMOSトランジスタP7とNMOSトランジスタN11によって構成されているが、PMOSトランジスタP6とPMOSトランジスタP7のゲートは、そのゲート,ドレインを短絡したPMOSトランジスタP8のゲートへ共通接続し、PMOSトランジスタP8とPMOSトランジスタP6,P7とがカレントミラー回路を形成している。PMOSトランジスタP8のドレインは、ゲートをリファレンス電圧源Vrefに、ソースをGNDにそれぞれ接続したNMOSトランジスタN12のドレインに接続し、またPMOSトランジスタP8のゲートへは、ゲートを制御端子C1に接続したPMOSトランジスタP9のドレインが接続している。ここでPMOSトランジスタP9は制御端子C1がLowレベルのときONしてPMOSトランジスタP6,P7,P8のゲートを電源VCC電圧にバイアスし、反転増幅器1、及び発振検出ゲート21の動作を停止するために設けたものである。このとき例えばリファレンス電圧源VrefもLow(GND)レベルに制御すれば、PMOSトランジスタP9とNMOSトランジスタN12間の貫通電流を防止できるが、本実施例の特徴を成すものではないため詳細の記載は省略した。

【0092】

図9においては、NMOSトランジスタN12が基準電流源となり、NMOSトランジスタN12とPMOSトランジスタP8間に流れる電流のミラー比倍が反転増幅器1,発振検出ゲート21の各バイアス電流となっている。すなわち反転増幅器1,発振検出ゲート21を構成するNMOSトランジスタN10,N11の負荷電流が、NMOSトランジスタN12によって規定されている。

【0093】

一方、前記図8における実施例では、上記NMOSトランジスタN10,N11の負荷電流はそれぞれPMOSトランジスタP6,P7が規定しており、この場合PMOSトランジスタ,NMOSトランジスタ間のデバイス特性ばらつきによって反転増幅器としてのゲインに大幅な変動を来たす可能性がある。

【0094】

図9の本実施例では、上記の如く信号を受ける側の能動デバイス、すなわち図9におけるNMOSトランジスタN10,N11と同種のデバイス、すなわちNMOSトランジスタN12によって負荷電流を規定していることから、PMOSトランジスタ,NMOSトランジスタ間のデバイス特性ばらつきの影響を抑制することができ、ゲインの安定化が図れる。すなわち図9においてカレントミラーを形成しているPMOSトランジスタP6,P7,P8のデバイス特性がばらついたとしても、各PMOSトランジスタ間の相対的なばらつきが生じない限りミラー比に変動は無く、よって上記負荷電流の変動も無いからゲインの変動も生じない。

【0095】

反転増幅器1のゲインを安定に保つことは、発振起動時の発振子5との正帰還ループの形成やその後の発振振幅の拡大にとって重要であり、発振立ち上がり特性の安定化につながる。

【0096】

本実施例によれば、デバイス特性ばらつきに対する反転増幅器のゲイン安定化を図ることができるので、前記第7の実施例の効果に加え、デバイスばらつきに対して安定な発振立ち上がり特性を有した発振回路を得ることができる。

【0097】

本発明の第9の実施例を図10に示す。

【0098】

いままで述べてきた他の実施例は、発振起動時いずれも短絡手段7によって反転増幅器1の入出力端子電位をその論理しきい値電圧VLT1にバイアスし、これにより反転増幅器1と発振子5との正帰還ループを早期に形成して発振開始を早めている。しかし電源VCCが低電圧域では、前記第7の実施例で述べた様に短絡手段7のインピーダンス増大の問題があり、これを防止するために昇圧手段30などが必要となる。また昇圧手段30から昇圧出力電圧を発生させるためには、昇圧手段30を動作させるクロックパルス源も通常必要となる。当該発振回路を組み込んだマイクロプロセッサ等の半導体集積回路においては、システムクロック源となる発振回路の起動時に昇圧出力電圧が必要となるわけであるから、例えばリングオシレータ等の自走式の発振回路、または外部クロック等、昇圧手段30を事前に動作させるためのパルス源を別に持たなくてはならない。

【0099】

本実施例は上記の様な回路要素の増大を回避し得る発振回路に関するものである。以下本実施例につき説明する。

【0100】

図10において、端子T1と端子T2との間に他の実施例同様、発振子5と帰還抵抗4とが並列接続し、端子T1及び端子T2とGNDとの間に容量61,62が接続している。反転増幅器1は前記図8の第7の実施例同様PMOSトランジスタP6とNMOSトランジスタN10とから成る負荷MOS型インバータで構成され、NMOSトランジスタN10側のゲートが端子T1に、PMOSトランジスタP6のゲートが制御端子C1に、出力すなわちPMOSトランジスタP6とNMOSトランジスタN10のドレインが抵抗3を介して端子T2に、それぞれ接続している。また発振検出ゲート21も前記図8の第7の実施例同様PMOSトランジスタP7とNMOSトランジスタN11とから成る負荷MOS型インバータで構成され、NMOSトランジスタN11のゲートがカップリング容量8を介して反転増幅器1出力に、PMOSトランジスタP7のゲートが制御端子C1にそれぞれ接続している。そしてその出力すなわちPMOSトランジスタP7とNMOSトランジスタN11のドレインは出力回路20を介して発振出力端子OUTに接続し、またその入力すなわちNMOSトランジスタN11のゲートと出力との間には帰還抵抗9が接続している。出力回路20の構成については第7の実施例の説明で述べた通りである。さらに、反転増幅器1の入力すなわちNMOSトランジスタN10のゲートにドレインを接続するPMOSトランジスタP10から成るスイッチング素子19と、反転増幅器1出力電位を検出して前記スイッチング素子19を制御するための検出回路32と、制御端子C3にゲートを接続したPMOSトランジスタP1から成る励磁電流供給手段18と、制御端子C5にゲートを、反転増幅器1出力にドレインを、GNDにソースをそれぞれ接続したNMOSトランジスタN13と、が設けられている。検出回路32は、スイッチング素子19内PMOSトランジスタP10のゲートにその出力を接続し、一方の入力を制御端子C6に接続したNANDゲートG10と、出力を上記NANDゲートG10のもう一方の入力に接続し、一方の入力を制御端子C6に接続したNANDゲートG8と、出力を上記NANDゲートG8のもう一方の入力に接続し、一方の入力を上記NANDゲートG8の出力に、もう一方の入力を反転増幅器1の出力にそれぞれ接続したNANDゲートG9とから構成されている。

【0101】

以下、本実施例の動作につき説明する。

【0102】

まず発振回路を停止状態におく場合は、制御端子C1,C3,C5をHighレベルに、C6をLowレベルにそれぞれバイアスする。このときPMOSトランジスタP6,P7はOFF状態にあるから反転増幅器1、及び発振検出ゲート21は機能しない。またPMOSトランジスタP1がOFF、NMOSトランジスタN13がON状態にあるから端子T2側電位はGNDレベルとなる。またNANDゲートG10出力がHighとなるからPMOSトランジスタP10はOFF状態にあり、よって帰還抵抗4により端子T1側電位もGNDレベルにある。

【0103】

次いで発振回路を起動する場合、制御端子C5をLowとしてNMOSトランジスタN13をOFFとするとともに、制御端子C3にLowレベルのワンショットパルスを印加し、PMOSトランジスタP1を所定の期間のみONさせて発振子5に励磁電流を供給する。これにより端子T2側電位は電源VCC電位に向かって急峻に上昇するが、端子T1側は帰還抵抗4が高抵抗のためゆるやかに電位上昇を始める。しかる後に制御端子C1をLowとして反転増幅器1,発振検出ゲート21を活性化するが、この時点では端子T1側電位がGNDレベル近傍にあり、反転増幅器1はまだ機能することはできない。

【0104】

このとき、すなわち反転増幅器1を活性化した直後に制御端子C6をHighにすると、NANDゲートG10出力がLowとなりPMOSトランジスタP10がONして端子T1側の電位上昇を加速する。ここでNANDゲートG10出力がLowに反転するのは、制御端子C6をHighにする直前、NANDゲートG8出力がHigh、端子T2電位がHigh、よってNANDゲートG9出力がLowとなっているが、この状態で制御端子C6をHighにすると、NANDゲートG9のLow出力によりNANDゲートG8出力はHighを維持し、よってNANDゲートG10の2入力が共にHighとなってNANDゲートG10出力がLowに反転するものである。そして制御端子C6のバイアスをそのままHighレベルに維持すれば、端子T2電位がLowに反転しない限りこの状態は保持されることになる。

【0105】

上記PMOSトランジスタP10すなわちスイッチング素子19のONにより、端子T1側の電位が上昇して反転増幅器1の論理しきい値電圧VLT1に到達すると、反転増幅器1の出力すなわち端子T2側電位はHighレベルからLowレベルに反転し始める。この端子T2側電位のLow反転を受けてNANDゲートG9出力がHighとなり、これによりNANDゲートG8の2入力が共にHighとなってNANDゲートG8出力がLow、よってNANDゲートG10出力がHighへ復帰してPMOSトランジスタP10がOFFする。この時点で端子T1側の電位上昇は停止し、結果的に端子T1側の電位は反転増幅器1の論理しきい値電圧VLT1近傍にバイアスされた状態となる。端子T2側についてはGNDレベル若しくはその近傍にまで電位が一旦変動し得るが、端子T1側すなわち反転増幅器1の入力電位がVLT1近傍にあることから、反転増幅器1出力すなわち端子T2側電位もやがてはVLT1近傍に安定化される。スイッチング素子19がOFFした時点から反転増幅器1の入力電位はVLT1近傍にあるから、端子T2側の電位変動に依らず反転増幅器1のゲインは確保され発振を開始することができる。図10に示した様にカップリング容量8を介して反転増幅器1出力を受ければ、その出力の電位変動に関わらず反転増幅器1の微小発振振動成分を取り出し、これを発振検出ゲート21、及び出力回路20などによって増幅,波形整形して出力端子OUTに伝達することができる。

【0106】

なお、スイッチング素子19のONにより一旦Lowレベルに反転した端子T2側電位が発振振幅の拡大などによって再びHighレベルになることがあっても、制御端子C6を発振回路の動作期間中Highレベルとすることにより、NANDゲートG8がLow出力を維持するからNANDゲートG9,G10出力がHigh固定となってスイッチング素子19のOFF状態は保持される。

【0107】

また検出回路32は、反転増幅器1の出力反転を検出できれば良いので、通常のCMOSゲート構成としても低電圧動作にも十分対応が可能である。

【0108】

なお図10においては、反転増幅器1、及び発振検出ゲート21を低電圧動作を考慮して第7の実施例同様負荷MOS型インバータのゲート構成としたが、これに限定されるものではなく、例えば図3の第3の実施例に示した様なCMOS構成のゲートによっても同様の動作を得ることができる。但し電源VCC電圧に関し、動作下限値は異なってくる。励磁電流供給手段18、及びNMOSトランジスタN13については、反転増幅器1が活性化されたとき十分な励磁電流供給能力を有し、また停止状態では端子T1,T2電位を固定し得るゲート構成であれば、省略しても良い。また発振検出ゲート21,出力回路20の構成方法についても第7の実施例で述べた様に適宜設計すれば良い。

【0109】

また図10においては、反転増幅器1、及び発振検出ゲート21をPMOS負荷型として発振停止時は端子T1,T2を共にGNDレベルに固定したため、発振起動においてスイッチング素子19には端子T1電位をプルアップする機能を持たせたが、これに限定されるものではなく、例えば反転増幅器1、及び発振検出ゲート21をNMOS負荷型(この場合PMOSトランジスタ側のゲートに端子T1が接続する。)として発振停止時に端子T1,T2を共に電源VCC電位側に固定した様な場合は、励磁電流供給手段18も端子T2とGNDとの間に設けて端子T2側をGNDレベルにバイアスして発振子5の励磁を行うであろうし、この場合端子T1電位はHighレベル側から遷移することになるからスイッチング素子19には端子T1電位をプルダウンする機能を持たせることになる。具体的には図10におけるPMOSトランジスタP10に替えて端子T2とGNDとの間にNMOSトランジスタを設ければ容易にプルダウン機能を有するスイッチング素子19を構成できる。またこの場合反転増幅器1のHighレベル側への出力反転を検出してスイッチング素子19をOFF制御することになるから、検出回路32もそれに見合った構成をとる必要がある。その一例としては、NANDゲートG8,G9,G10をすべてNORゲートに置き換え、図10とは逆に制御端子C6をLowとすることで起動を行う様にすれば良い。

【0110】

本実施例によれば、反転増幅器1の入出力間短絡手段7を用いることなく発振起動時に反転増幅器1の入力電位をその論理しきい値電圧VLT1近傍にバイアスすることができ、他の実施例同様発振立ち上がり時間を短縮した発振回路が得られるとともに、低電圧動作についても、前記第7,第8の実施例の如く昇圧手段30などの回路要素を付加することなく対応が可能であり、比較的小さな回路規模で集積化に有利な発振回路を得ることができる。

【図面の簡単な説明】

【0111】

【図1】本発明の第1の実施例の構成を示す回路図。

【図2】本発明の第2の実施例の構成を示す回路図。

【図3】本発明の第3の実施例の構成を示す回路図。

【図4】本発明の第4の実施例の構成を示す回路図。

【図5】本発明の第4の実施例の構成を示す回路図。

【図6】本発明の第5の実施例の構成を示す回路図。

【図7】本発明の第6の実施例の構成を示す回路図。

【図8】本発明の第7の実施例の構成を示す回路図。

【図9】本発明の第8の実施例の構成を示す回路図。

【図10】本発明の第9の実施例の構成を示す回路図。

【図11】従来の構成を示す回路図。

【符号の説明】

【0112】

1…反転増幅器、2…出力バッファ回路、3…抵抗、4,9…帰還抵抗、5…発振子、7,10…短絡手段、8,11,15…カップリング容量、12,13…バイアス手段、14,16,17…電流源、18…励磁電流供給手段、19…スイッチング素子、20…出力回路、21…発振検出ゲート、22…バッファ回路、30…昇圧手段、31…レベルシフタ、32…検出回路、61,62…容量、C1,C2,C3,C4,C5,C6…制御端子、P1,P2,P3,P4,P5,P6,P7,P8,P9,P10…PMOSトランジスタ、N1,N2,N3,N4,N5,N6,N7,N8,N9,N10,N11,N12,N13…NMOSトランジスタ、OUT…発振出力端子、VCC…電源。

【特許請求の範囲】

【請求項1】

反転増幅器と、反転増幅器の入出力端子間に並列接続する発振子との正帰還ループを形成して発振動作を行う発振回路において、

ソースを第1の基準電位に接続した第1導電型の第1のトランジスタと、同じくソースを第1の基準電位に接続した第1導電型の第2のトランジスタの互いのゲートを接続し、第1のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第2のトランジスタのドレインを出力端子とする第1のカレントミラー回路と、

ソースを第2の基準電位に接続した第2導電型の第3のトランジスタと、同じくソースを第2の基準電位に接続した第2導電型の第4のトランジスタの互いのゲートを接続し、第3のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第4のトランジスタのドレインを出力端子とする第2のカレントミラー回路と、

第1のカレントミラー回路の入力端子と第2の基準電位との間に接続した第1の電流バイアス手段と、

第2のカレントミラー回路の入力端子と第1の基準電位との間に接続した第2の電流バイアス手段と、

第1のカレントミラー回路の入力端子と第2のカレントミラー回路の入力端子との間に直列接続して設けられた第1,第2の結合容量と、から成り、

第1,第2の結合容量の共通接続点を入力端子とし、第1,第2の各カレントミラー回路の出力端子を共通接続して出力端子とした増幅回路を設け、

前記反転増幅器出力を源とする発振電圧振動を前記増幅回路の入力端子へ入力し、前記増幅回路の出力端子から発振出力を取り出すことを特徴とする発振回路。

【請求項2】

反転増幅器と、反転増幅器の入出力端子間に並列接続する発振子との正帰還ループを形成して発振動作を行う発振回路において、

ソースを第1の基準電位に接続した第1導電型の第1のトランジスタと、同じくソースを第1の基準電位に接続した第1導電型の第2のトランジスタの互いのゲートを接続し、第1のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第2のトランジスタのドレインを出力端子とする第1のカレントミラー回路と、

ソースを第2の基準電位に接続した第2導電型の第3のトランジスタと、同じくソースを第2の基準電位に接続した第2導電型の第4のトランジスタの互いのゲートを接続し、第3のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第4のトランジスタのドレインを出力端子とする第2のカレントミラー回路と、

ソースを第1の基準電位に接続した第1導電型の第5のトランジスタと、同じくソースを第1の基準電位に接続した第1導電型の第6のトランジスタの互いのゲートを接続し、第5のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第6のトランジスタのドレインを出力端子とする第3のカレントミラー回路と、

ソースを第2の基準電位に接続した第2導電型の第7のトランジスタと、同じくソースを第2の基準電位に接続した第2導電型の第8のトランジスタの互いのゲートを接続し、第7のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第8のトランジスタのドレインを出力端子とする第4のカレントミラー回路と、

第1のカレントミラー回路の入力端子と第2の基準電位との間に接続した第1の電流バイアス手段と、

第2のカレントミラー回路の入力端子と第1の基準電位との間に接続した第2の電流バイアス手段と、

第1のカレントミラー回路の入力端子と第2のカレントミラー回路の入力端子との間に直列接続して設けられた第1,第2の結合容量と、

から成り、第1,第2の結合容量の共通接続点を入力端子とし、第1のカレントミラー回路の出力端子を第4のカレントミラー回路の入力端子へ、また第2のカレントミラー回路の出力端子を第3のカレントミラー回路の入力端子へそれぞれ接続し、さらに第3,第4の各カレントミラー回路の出力端子を共通接続して出力端子とした増幅回路を設け、

前記反転増幅器出力を源とする発振電圧振動を前記増幅回路の入力端子へ入力し、前記増幅回路の出力端子から発振出力を取り出すことを特徴とする発振回路。

【請求項3】

前記反転増幅器は、発振起動時、発振子を励磁した後に反転増幅器の入力端子を所定電位にバイアスする電圧バイアス手段を具備して成ることを特徴とする請求項1または2に記載の発振回路。

【請求項4】

前記反転増幅器は、

第1導電型の第1のMOSトランジスタと、

ドレインを第1のMOSトランジスタのドレインに接続した第2導電型の第2のMOSトランジスタと、

ゲート,ドレインを短絡し、かつそのゲートを第2のMOSトランジスタのゲートに接続して第2のMOSトランジスタとカレントミラーを構成する第2導電型の第3のMOSトランジスタと、

ゲートを基準電圧源に、ドレインを第3のMOSトランジスタのドレインに、それぞれ接続した第1導電型の第4のMOSトランジスタと、

から構成し、第1のMOSトランジスタのゲートを入力端子,ドレインを出力端子としたことを特徴とする請求項1または2に記載の発振回路。

【請求項1】

反転増幅器と、反転増幅器の入出力端子間に並列接続する発振子との正帰還ループを形成して発振動作を行う発振回路において、

ソースを第1の基準電位に接続した第1導電型の第1のトランジスタと、同じくソースを第1の基準電位に接続した第1導電型の第2のトランジスタの互いのゲートを接続し、第1のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第2のトランジスタのドレインを出力端子とする第1のカレントミラー回路と、

ソースを第2の基準電位に接続した第2導電型の第3のトランジスタと、同じくソースを第2の基準電位に接続した第2導電型の第4のトランジスタの互いのゲートを接続し、第3のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第4のトランジスタのドレインを出力端子とする第2のカレントミラー回路と、

第1のカレントミラー回路の入力端子と第2の基準電位との間に接続した第1の電流バイアス手段と、

第2のカレントミラー回路の入力端子と第1の基準電位との間に接続した第2の電流バイアス手段と、

第1のカレントミラー回路の入力端子と第2のカレントミラー回路の入力端子との間に直列接続して設けられた第1,第2の結合容量と、から成り、

第1,第2の結合容量の共通接続点を入力端子とし、第1,第2の各カレントミラー回路の出力端子を共通接続して出力端子とした増幅回路を設け、

前記反転増幅器出力を源とする発振電圧振動を前記増幅回路の入力端子へ入力し、前記増幅回路の出力端子から発振出力を取り出すことを特徴とする発振回路。

【請求項2】

反転増幅器と、反転増幅器の入出力端子間に並列接続する発振子との正帰還ループを形成して発振動作を行う発振回路において、

ソースを第1の基準電位に接続した第1導電型の第1のトランジスタと、同じくソースを第1の基準電位に接続した第1導電型の第2のトランジスタの互いのゲートを接続し、第1のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第2のトランジスタのドレインを出力端子とする第1のカレントミラー回路と、

ソースを第2の基準電位に接続した第2導電型の第3のトランジスタと、同じくソースを第2の基準電位に接続した第2導電型の第4のトランジスタの互いのゲートを接続し、第3のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第4のトランジスタのドレインを出力端子とする第2のカレントミラー回路と、

ソースを第1の基準電位に接続した第1導電型の第5のトランジスタと、同じくソースを第1の基準電位に接続した第1導電型の第6のトランジスタの互いのゲートを接続し、第5のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第6のトランジスタのドレインを出力端子とする第3のカレントミラー回路と、

ソースを第2の基準電位に接続した第2導電型の第7のトランジスタと、同じくソースを第2の基準電位に接続した第2導電型の第8のトランジスタの互いのゲートを接続し、第7のトランジスタのゲート,ドレインを短絡接続して入力端子とし、第8のトランジスタのドレインを出力端子とする第4のカレントミラー回路と、

第1のカレントミラー回路の入力端子と第2の基準電位との間に接続した第1の電流バイアス手段と、

第2のカレントミラー回路の入力端子と第1の基準電位との間に接続した第2の電流バイアス手段と、

第1のカレントミラー回路の入力端子と第2のカレントミラー回路の入力端子との間に直列接続して設けられた第1,第2の結合容量と、

から成り、第1,第2の結合容量の共通接続点を入力端子とし、第1のカレントミラー回路の出力端子を第4のカレントミラー回路の入力端子へ、また第2のカレントミラー回路の出力端子を第3のカレントミラー回路の入力端子へそれぞれ接続し、さらに第3,第4の各カレントミラー回路の出力端子を共通接続して出力端子とした増幅回路を設け、

前記反転増幅器出力を源とする発振電圧振動を前記増幅回路の入力端子へ入力し、前記増幅回路の出力端子から発振出力を取り出すことを特徴とする発振回路。

【請求項3】

前記反転増幅器は、発振起動時、発振子を励磁した後に反転増幅器の入力端子を所定電位にバイアスする電圧バイアス手段を具備して成ることを特徴とする請求項1または2に記載の発振回路。

【請求項4】

前記反転増幅器は、

第1導電型の第1のMOSトランジスタと、

ドレインを第1のMOSトランジスタのドレインに接続した第2導電型の第2のMOSトランジスタと、

ゲート,ドレインを短絡し、かつそのゲートを第2のMOSトランジスタのゲートに接続して第2のMOSトランジスタとカレントミラーを構成する第2導電型の第3のMOSトランジスタと、

ゲートを基準電圧源に、ドレインを第3のMOSトランジスタのドレインに、それぞれ接続した第1導電型の第4のMOSトランジスタと、

から構成し、第1のMOSトランジスタのゲートを入力端子,ドレインを出力端子としたことを特徴とする請求項1または2に記載の発振回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2008−92605(P2008−92605A)

【公開日】平成20年4月17日(2008.4.17)

【国際特許分類】

【出願番号】特願2007−331859(P2007−331859)

【出願日】平成19年12月25日(2007.12.25)

【分割の表示】特願平9−322678の分割

【原出願日】平成9年11月25日(1997.11.25)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【出願人】(390023928)日立エンジニアリング株式会社 (134)

【出願人】(000233273)日立原町電子工業株式会社 (15)

【Fターム(参考)】

【公開日】平成20年4月17日(2008.4.17)

【国際特許分類】

【出願日】平成19年12月25日(2007.12.25)

【分割の表示】特願平9−322678の分割

【原出願日】平成9年11月25日(1997.11.25)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【出願人】(390023928)日立エンジニアリング株式会社 (134)

【出願人】(000233273)日立原町電子工業株式会社 (15)

【Fターム(参考)】

[ Back to top ]