記憶装置、通信システムおよび記憶装置の制御方法

【課題】リセット信号線を接続するための端子や配線等の回路構成がなく、簡易な構成をもつ記憶装置、カートリッジ、通信システムおよび記憶装置の制御方法を提供すること。

【解決手段】記憶装置20は、クロック信号SCKおよびデータ信号SDAが入力され、リセットにより初期化された後にクロック信号SCKに同期したデータ通信を開始するよう構成されている。この記憶装置20は、クロック信号SCKがハイのレベルを維持する期間において、データ信号SDAに複数回のレベル変化を生じたか否かを判定し、複数回のレベル変化を生じていた場合に、記憶装置20のリセットを実行するリセット処理ユニット27を備えている。

【解決手段】記憶装置20は、クロック信号SCKおよびデータ信号SDAが入力され、リセットにより初期化された後にクロック信号SCKに同期したデータ通信を開始するよう構成されている。この記憶装置20は、クロック信号SCKがハイのレベルを維持する期間において、データ信号SDAに複数回のレベル変化を生じたか否かを判定し、複数回のレベル変化を生じていた場合に、記憶装置20のリセットを実行するリセット処理ユニット27を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ホストコンピューターとのデータ通信を行う記憶装置、カートリッジ、通信システムおよび記憶装置の制御方法に関する。

【背景技術】

【0002】

記憶装置と、記憶装置を制御するホストコンピューターとの間の通信を、クロック信号線、データ信号線、リセット信号線の3線を用いて行うようにしたシステムが知られている(例えば、特許文献1参照)。

【0003】

特許文献1に記載のシステムは、インクジェットプリンターのインクカートリッジに備わる記憶装置と、プリンターの本体側に備わるホストコンピューターとの通信を、クロック信号線、データ信号線、リセット信号線の3線を用いて行うものである。このシステムでは、ホストコンピューターから記憶装置にアクセスする際、ホストコンピューターはリセット信号線を介して記憶装置にリセット信号を送出する。記憶装置は、リセット信号を受信するとリセットを実行し、例えば、記憶装置の内部に備わるレジスターをクリアすることによって記憶装置の初期化が行われる。記憶装置が初期化された後、記憶装置とホストコンピューターとの間でクロック信号に同期させたデータ通信が開始されて、このデータ通信により、ホストコンピューターが記憶装置のメモリーアレイにアクセスできるよう構成されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−14870号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載のシステムは、クロック信号線、データ信号線、リセット信号線の3つの信号線を実装する必要があるため、記憶装置やホストコンピューター側の配線や端子などの回路構成が複雑化するという課題があった。このため、回路設計の設計工数の増大や製品コストの増大などをもたらすこととなっていた。

【0006】

また、例えば、インク色ごとに異なるインクカートリッジが装着されるインクジェットプリンターのように、1つのプリンターに対して複数のインクカートリッジが装着される場合、1つのホストコンピューターに対して複数の記憶装置が備わるシステムとなる。このシステムにおいて、各記憶装置に対してクロック信号線、データ信号線およびリセット信号線を配線した場合、回路構成の複雑化がより顕著になってしまう。

【課題を解決するための手段】

【0007】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0008】

[適用例1]クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置であって、前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする記憶装置。

【0009】

この構成によれば、クロック信号が所定のレベルを維持する期間にデータ信号に複数回のレベル変化を生じた場合にリセットが実行されて、リセットした後に記憶装置の記憶部にアクセスするデータ通信が開始される。したがって、クロック信号およびデータ信号によって記憶装置の記憶部にアクセスすることが可能であり、特許文献1に記載の記憶装置に比べると、リセット信号線を接続するための端子や配線等の回路構成がない簡易な構成の記憶装置を得ることができる。また、回路構成を簡易化できるため、記憶装置の設計工数を削減できるとともに、製品コストの低廉化を実現できる。

【0010】

[適用例2]上記記憶装置において、前記リセット実行部は、前記クロック信号が前記所定のレベルに変化した後の前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させることを特徴とする記憶装置。

【0011】

この構成によれば、クロック信号が所定のレベルに変化したレベル変化も用いて、リセットを実行するタイミングをより正確に判断することができる。

【0012】

[適用例3]上記記憶装置において、前記記憶部は、第1識別情報を記憶し、前記通信制御部は、前記第1識別情報と、前記データ信号により入力される第2識別情報とを比較して、前記第1識別情報と前記第2識別情報とが一致する場合に、前記データ通信における前記記憶部へのアクセスを許可することを特徴とする記憶装置。

【0013】

この構成によれば、記憶部に記憶された第1識別情報と、データ信号により入力された第2識別情報とが一致する場合に、データ通信による記憶部へのアクセスが許可されるので、記憶部へのアクセスを適切に管理することができる。

【0014】

[適用例4]上記記憶装置において、前記データ通信を開始した後、前記データ信号のレベルが変化した回数をカウントするカウント部を備え、前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【0015】

この構成によれば、データ通信を開始した後に、データ信号のレベルが変化した回数に応じて第2識別情報が取得され、第1識別情報および第2識別情報により記憶部へのアクセスが許可される。したがって、記憶部へのアクセスを適切に管理することができる。

【0016】

[適用例5]上記記憶装置において、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号のレベルが変化した回数をカウントするカウント部を備え、前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【0017】

この構成によれば、クロック信号が所定のレベルを維持する期間に、レベルが変化した回数に応じて第2識別情報が取得され、第1識別情報および第2識別情報により記憶部へのアクセスが許可される。したがって、記憶部へのアクセスを適切に管理することができる。

【0018】

[適用例6]クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置を備えるカートリッジであって、前記記憶装置は、前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とするカートリッジ。

【0019】

この構成によれば、リセット信号線を接続するための端子や配線等の回路構成がない簡易な構成のカートリッジを実現することができる。

【0020】

[適用例7]記憶部を有する記憶装置とホスト装置とがクロック信号線およびデータ信号線を介して接続される通信システムであって、前記記憶装置は、前記クロック信号線のクロック信号および前記データ信号線のデータ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする通信システム。

【0021】

この構成によれば、記憶装置またはホスト装置、もしくは記憶装置とホスト装置の間に、リセット信号線を接続するための端子や配線等の回路構成がない簡易な構成の通信システムを実現することができる。

【0022】

[適用例8]クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置の制御方法であって、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、リセットを実行するステップと、前記リセットにより初期化した後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始するステップと、を含むことを特徴とする記憶装置の制御方法。

【0023】

このようにすれば、リセットにより初期化された後にデータ通信によって記憶部にアクセスできるよう構成された記憶装置に対して、リセット信号を用いることなく、クロック信号およびデータ信号によってアクセスすることができる。

【図面の簡単な説明】

【0024】

【図1】第1の実施形態に係る通信システムの概略構成を示したブロック図である。

【図2】インクカートリッジの概観斜視図である。

【図3】ホストコンピューターの構成を示したブロック図である。

【図4】データ列のデータ構造を示したブロック図である。

【図5】記憶装置内部の回路構成を示したブロック図である。

【図6】クロック信号とデータ信号の一例を示したタイミングチャートである。

【図7】リセット処理ユニットの構成を示したブロック図である。

【図8】ホストコンピューターによって行われる処理および記憶装置によって行われる処理の手順を示したフローチャートである。

【図9】第2の実施形態におけるクロック信号とデータ信号の一例を示したタイミングチャートである。

【図10】リセット処理ユニットの構成を示したブロック図である。

【図11】第3の実施形態におけるクロック信号とデータ信号の一例を示したタイミングチャートである。

【図12】ホストコンピューターによって行われる処理および記憶装置によって行われる処理の手順を示したフローチャートである。

【図13】第1の変形例を説明する説明図である。

【発明を実施するための形態】

【0025】

(第1の実施形態)

以下、本発明の実施形態について図面を参照して説明する。なお、本実施形態では、通信システムの一例として、インクジェットプリンターに備わる通信システムについて説明する。

【0026】

図1は、第1の実施形態に係る通信システムの概略構成を示した図である。図1に示すように、通信システム1は、複数の記憶装置20(20a〜20d)と、記憶装置20のホスト装置としてのホストコンピューター10とを含む。記憶装置20は、図2に示すように、4色のインクカートリッジC1〜C4にそれぞれ備えられるものである。例えば、シアンのインクを収容したインクカートリッジC1には記憶装置20a、マゼンタのインクを収容したインクカートリッジC2には記憶装置20b、イエローのインクを収容したインクカートリッジC3には記憶装置20c、ブラックのインクを収容したインクカートリッジC4には記憶装置20dが備えられる。もっとも、記憶装置20の数およびカートリッジの種類についてはこれに限られるものではない。また、ホストコンピューター10の例としては、インクジェットプリンターの本体側に配置されたプリンタコントローラーなどが挙げられる。

【0027】

記憶装置20(20a〜20d)は、インクカートリッジCに設けられたメモリモジュール基板上に配置され、クロック信号端子(第1端子)CTおよびデータ信号端子(第2端子)DTを有している。クロック信号端子CTにはクロック信号線CLが接続されており、クロック信号線CLはクロックバスCBを介してホストコンピューター10に接続されている。一方、データ信号端子DTにはデータ信号線DLが接続されており、データ信号線DLはデータバスDBを介してホストコンピューター10に接続されている。

【0028】

図3は、ホストコンピューター10の構成を示した図である。図3に示すように、ホストコンピューター10は、クロック信号生成回路11、電源回路12、電源補償回路13、データ記憶回路14および各回路を制御する制御回路15を備える制御装置である。ホストコンピューター10は、印刷制御の他、記憶装置20a〜20dへのアクセス制御や、インク消費量、インクカートリッジCの装着時間といったデータを記憶装置20から取得してデータ記憶回路14に記憶する制御などを行う。

【0029】

電源補償回路13は、電源の供給が遮断された場合にも所定の期間(例えば、0.3s)、記憶装置20に電源を供給する。これにより、停電、電源プラグが抜かれることによってデータ書き込み中の電源が遮断されても、上述した所定期間の間に書き込みを優先すべきデータの書き込みを完了することができる。電源補償回路13としては、例えば、コンデンサーが用いられる。

【0030】

制御回路15は、電源回路12を制御して正電源の出力を制御する。ホストコンピューター10は、各記憶装置20a〜20dに対して常時電源を供給しておらず、記憶装置20a〜20dに対するアクセス要求が発生した場合にのみ、記憶装置20a〜20dに対して正電源を供給する。

【0031】

クロック信号生成回路11は、クロック信号SCKを生成する。生成されたクロック信号SCKは、クロック信号線CLを介して各記憶装置20a〜20dに供給される。

【0032】

また、制御回路15は、記憶装置20とのデータ通信を制御する。制御回路15は、記憶装置20とデータ通信する際、所定のフォーマットに従うデータ列を送出する。

【0033】

次に、ホストコンピューター10と記憶装置20との間のデータ通信で用いられるデータ列のデータ構造について説明する。図4は、データ列のデータ構造を示した図である。図4に示すように、データ列100には、IDデータ(第2識別情報)110と、読み出し/書き込みコマンド120と、処理データ130と、ACKデータ140と、が含まれる。IDデータ110は、例えば、3ビットのデータであり、プリンターに装着された複数のインクカートリッジの各記憶装置20a〜20dのうちから、データの読み出しや書き込みの対象とする記憶装置20を指定するための識別情報である。読み出し/書き込みコマンド120は、記憶装置20に対しての読み出しまたは書き込みの処理種別を指定するコマンドである。処理データ130は、読み出し/書き込みコマンド120で指定された処理の対象となるデータである。なお、読み出し/書き込みコマンド120と処理データ130とは対になっており、データ列100には、読み出し/書き込みコマンド120と処理データ130を含む組が繰り返し含まれる。ACKデータ140は、記憶装置20からホストコンピューター10に送出されるデータ列100の最後に付加されるものであり、ホストコンピューター10が送出したデータ列100に従う処理が正常に行われたことを示す。ホストコンピューター10は、上述したデータ列100を構成するデータを、クロック信号SCKに同期させてデータ信号SDAにより記憶装置20に順次送出する。これにより、ホストコンピューター10と、記憶装置20との間でクロック信号SCKに同期したデータ通信が行われる。

【0034】

制御回路15は、インクジェットプリンターの電源投入時、インクカートリッジの交換時、印刷ジョブの終了時、インクジェットプリンターの電源遮断時などに、上述したデータ列100に従うデータ通信により記憶装置20a〜20dに対するアクセスを実行する。

【0035】

ここで、ホストコンピューター10から記憶装置20にアクセスする場合、ホストコンピューター10は、データ通信によるアクセスに先立ち、記憶装置20にリセットを実行させる必要がある。すなわち、記憶装置20は、リセットにより初期化された後にクロック信号SCKに同期したデータ通信によるアクセスが可能に構成されている。詳細は後述するが、これは、記憶装置20とのデータ通信を開始するには、リセットによって記憶装置20内部に備わるレジスターなどを初期化することによって、記憶装置20を新たなアクセスに対して対処可能な状態としておく必要があるからである。このため、制御回路15は、インクジェットプリンターの電源投入時、インクカートリッジの交換時、印刷ジョブの終了時、インクジェットプリンターの電源遮断時など、ホストコンピューター10から記憶装置20にアクセスする場合に記憶装置20に対してリセットを要求する。

【0036】

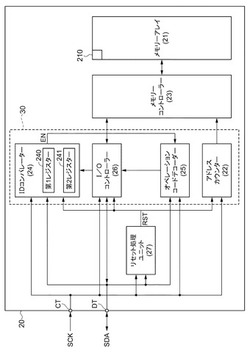

次に、記憶装置20の内部構成について説明する。図5は、記憶装置20内部の回路構成を示したブロック図である。なお、以下では、1つの記憶装置20の内部構成を例に挙げて説明するが、各記憶装置20a〜20dの内部構成は、メモリーアレイに格納されているデータを除いて同じである。

【0037】

図5に示すように、記憶装置20は、メモリーアレイ21と、アドレスカウンター22と、メモリーコントローラー23と、IDコンパレーター24と、オペレーションコードデコーダー25と、I/Oコントローラー26と、リセット処理ユニット27と、を備えている。なお、記憶装置20の構成のうち、アドレスカウンター22、IDコンパレーター24、オペレーションコードデコーダー25およびI/Oコントローラー26が、メモリーアレイ21にアクセスするデータ通信を制御する通信制御部30に相当する。

【0038】

メモリーアレイ21は、EEPROMやフラッシュROMなど、不揮発的に記憶内容を保持すると共に記憶内容を書き換え可能なメモリーであり、記憶装置20の記憶部である。メモリーアレイ21は、例えば、256ビットなどの所定容量の記憶領域を有し、先頭アドレスから順次アクセスが可能、すなわちシーケンシャルにアクセス可能に構成されている。先頭から3ビットの記憶領域には、インクカートリッジCの種類またはインクカートリッジCが収容するインクの種類に応じて予め決められた識別データ(第1識別情報)210が格納されている。先頭から4ビット目の記憶領域は無効領域とされている。なお、本実施形態では、記憶装置20のメモリーアレイ200自体に識別データ210を記憶する構成としたが、メモリーアレイ200とは別に設けた記憶素子に識別データ210を記憶するようにしてもよい。

【0039】

アドレスカウンター22は、クロック信号SCKに同期してそのカウント値をインクリメントする回路であり、クロック信号端子CT、メモリーアレイ21およびリセット処理ユニット27と接続されている。アドレスカウンター22のカウント値とメモリーアレイ21の記憶領域位置(アドレス)とは関連付けられており、アドレスカウンター22のカウント値によってメモリーアレイ21における書き込み位置または読み出し位置を指定することができる。

【0040】

また、アドレスカウンター22は、リセット処理ユニット27からのリセット信号RSTが入力されると、カウント値を初期値にリセットすることにより初期化を行う。ここで、初期値はメモリーアレイ21の先頭位置と関連付けられていればどのような値でもよく、例えば、”0”が初期値として用いられる。

【0041】

メモリーコントローラー23は、メモリーアレイ21、アドレスカウンター22およびI/Oコントローラー26に接続されており、I/Oコントローラー26の制御に従ってメモリーアレイ21の記憶領域のうち、アドレスカウンター22が指定するアドレスの領域への情報の書き込み/読み出しを実行する。具体的には、メモリーアレイ21から情報を読み出してI/Oコントローラー26に受け渡す処理や、I/Oコントローラー26から書き込み対象の情報を受け取ってメモリーアレイ21の記憶領域に書き込む処理などを行う。

【0042】

IDコンパレーター24は、クロック信号端子CT、データ信号端子DT、I/Oコントローラー26およびオペレーションコードデコーダー25と接続されており、データ信号端子DTを介して入力されるデータ列100に含まれるIDデータ110とメモリーアレイ21に格納されている識別データ210とを比較して一致するか否かを判定する。また、IDコンパレーター24は、ホストコンピューター10から入力されたIDデータ110を格納する3ビットの第1レジスター240と、I/Oコントローラー26を介してメモリーアレイ21から取得した識別データ210を格納する第2レジスター241とを有している。IDコンパレーター24は、第1レジスター240に格納されたIDデータ110と、第2レジスター241に格納された識別データ210とが一致する場合に、ホストコンピューター10からメモリーアレイ21へのアクセスを許可する旨のアクセス許可信号ENをオペレーションコードデコーダー25に送出する。

【0043】

なお、IDコンパレーター24は、リセット処理ユニット27からのリセット信号RSTの入力により初期化を行う。IDコンパレーター24の初期化は、第1レジスター240および第2レジスター241に格納された情報をクリアすることによって行われる。初期化後のIDコンパレーター24は新たなIDデータ110の入力待ちの状態となり、この状態においてホストコンピューター10からデータ列100が送出されると、データ列100に含まれるIDデータ110を取得して第1レジスター240に格納するよう構成されている。また、IDコンパレーター24は、IDデータ110を第1レジスター240に格納した後などの所定のタイミングで、I/Oコントローラー26を介してメモリーアレイ21から識別データ210を取得して第2レジスター241に格納する。

【0044】

オペレーションコードデコーダー25は、クロック信号端子CT、データ信号端子DT、IDコンパレーター24およびI/Oコントローラー26と接続されており、ホストコンピューター10から送出されたデータ列100より読み出し/書き込みコマンド120を取得する。オペレーションコードデコーダー25は、IDコンパレーター24からアクセス許可信号ENが入力されると、取得した読み出し/書き込みコマンド120を解析して、解析結果に応じて書き込み処理要求または読み出し処理要求をI/Oコントローラー26に送出する。

【0045】

I/Oコントローラー26は、クロック信号端子CT、データ信号端子DT、メモリーコントローラー23、オペレーションコードデコーダー25およびリセット処理ユニット27と接続されており、オペレーションコードデコーダー25からの要求に従ってメモリーアレイ21に対するデータ転送方向ならびにデータ信号端子DTに対するデータ転送方向を切り換え制御する。

【0046】

また、I/Oコントローラー26は、リセット処理ユニット27からのリセット信号RSTの入力により初期化を行う。I/Oコントローラー26の初期化は、メモリーアレイ21に対するデータ転送方向を読み出し方向に設定し、データ信号端子DTと接続されている信号線をハイインピーダンスとすることでデータ信号端子DTに対するデータ転送を禁止することによって行われる。こうして初期化した状態は、オペレーションコードデコーダー25から書き込み処理要求または読み出し処理要求が入力されるまで維持される。したがって、リセット信号RSTが入力された後にデータ信号端子DTを介して入力されるデータ列100の先頭4ビットのデータ(すなわち、IDデータ110および読み出し/書き込みコマンド120)はメモリーアレイ21に書き込まれることはない。一方で、メモリーアレイ21の先頭4ビット(内4ビット目は無効データ)に格納されているデータは、読み出し専用となり、IDコンパレーター24に送出される。

【0047】

ここで、上述したように、本実施形態の通信システム1では、ホストコンピューター10から記憶装置20にアクセスする際、アクセスに先立って記憶装置20の第1レジスター240に格納された情報をクリアさせることによって、IDコンパレーター24をIDデータ110の入力待ちの状態としておく必要がある。このため、ホストコンピューター10から記憶装置20に新たにアクセスして、メモリーアレイ21に対して情報の読み出しや書き込みをする際、ホストコンピューター10は、データ通信によるアクセスに先立って、記憶装置20にリセットを要求して、記憶装置20を初期化する必要がある。

【0048】

しかしながら、上述した構成の通信システム1は、特許文献1に記載のシステムのように、ホストコンピューター10と記憶装置20と間にリセット信号線が設けられていないため、リセット信号線を介してホストコンピューター10から記憶装置20にリセット信号を送出することはできない。

【0049】

そこで、本実施形態に係る通信システム1では、ホストコンピューター10から記憶装置20に対してアクセスを開始する際に、クロック信号のレベル(ハイ/ロー)とデータ信号のレベル(ハイ/ロー)に、クロック信号SCKに同期しないレベル変化の組み合わせをリセット要求として用いる。

【0050】

図6は、リセット要求に対応するクロック信号とデータ信号の組み合わせの一例を示したタイミングチャートである。図6に示すように、本実施形態では、リセット要求に対応する信号の組み合わせとして、クロック信号SCKを立ち上げてハイを維持する期間(時刻T1〜T4)に、データ信号SDAに対しては、ローからハイに立ち上げて(時刻T2)からローに立ち下げる(時刻T3)ことにより複数回のレベル変化を生じさせる。この一連のレベル変化の組み合わせを、リセット要求とする。すなわち、ホストコンピューター10と記憶装置20との間では、図6の時刻T1〜T4に示すクロック信号SCKとデータ信号SDAのレベル変化が、リセット要求に対応すると予め取り決められている。ホストコンピューター10は、記憶装置20に対してアクセスを開始する際、データ通信に先立ち、クロック信号SCKおよびデータ信号SDAに上述したレベル変化を生じさせることにより、ホストコンピューター10は記憶装置20に対してリセットを要求する。これにより、ホストコンピューター10、記憶装置20間にリセット信号用の信号線が接続されていなくとも、ホストコンピューター10から記憶装置20に対してリセットが要求される。

【0051】

ホストコンピューター10は、クロック信号SCKとデータ信号SDAにリセット要求に対応するレベル変化を生じさせた後、クロック信号SCKに同期させてデータ信号SDAによるデータ通信を行う(図6の時刻T5以降)。ホストコンピューター10から記憶装置20に送信するデータのフォーマットは上述したデータ列100に従うため、図6の時刻T5にデータ通信を開始した後、クロック信号SCKの立ち上がりに同期して、データ列100を構成するデータのうち先頭のIDデータ110から順番にデータを送信することにより、ホストコンピューター10は記憶装置20のメモリーアレイ21へのアクセスを行う。なお、データ通信におけるクロック信号SCKの同期方法としては、クロック信号SCKの立ち上がりのタイミングに同期させる方法に限られることなく、クロック信号の立ち下がりのタイミング、もしくは立ち上がりと立ち下がりの両方のタイミングに同期させるようにしてもよい。

【0052】

また、記憶装置20には、上述したリセット要求に対応して記憶装置20にリセットを実行させる処理を行うため、リセット処理ユニット27が備えられている。リセット処理ユニット27は、クロック信号端子CT、データ信号端子DT、アドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26と接続されており、図7に示すように、リセット要求判定部270と、リセット実行部271と、を有している。

【0053】

リセット要求判定部270は、クロック信号SCKとデータ信号SDAとを監視し、上述したリセット要求に対応するレベル変化を生じたか否かを判定する。リセット実行部271は、リセット要求判定部270の判定によって、クロック信号SCKおよびデータ信号SDAにリセット要求に対応するレベル変化を生じていた場合に、アドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26にリセット信号RSTを送出する。これにより、アドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26の各構成にリセットを実行させる。

【0054】

次に、通信システム1の動作について詳細に説明する。図8は、ホストコンピューター10によって行われる処理および記憶装置20によって行われる処理の手順を示したフローチャートである。以下、図6に示した信号波形例および図8のフローチャートに従って説明する。

【0055】

インクジェットプリンターの電源投入時、インクカートリッジの交換時、印刷ジョブの終了時、インクジェットプリンターの電源遮断時などに、図8の処理が開始される。処理が開始されると、ホストコンピューター10は、クロック信号SCKおよびデータ信号SDAを、図6に示したリセット要求に対応する組み合わせとすることにより記憶装置20に対してリセットを要求する。すなわち、ホストコンピューター10の制御回路15は、クロック信号生成回路11を制御してクロック信号SCKのレベルをローからハイに立ち上げる(時刻T1、ステップS10)。クロック信号SCKを立ち上がった後、制御回路15は、データ信号SDAをローからハイ、さらにローへと変化させてから(時刻T2,T3、ステップS11)、クロック信号SCKのレベルをハイからローに立ち下げる(時刻T4、ステップS12)。なお、クロック信号SCKをハイに立ち上げてからローに戻る期間(時刻T1〜T4)については、データ信号SDAのレベル変化を記憶装置20側で確実に検出できるよう、通常のデータ通信で用いられる1クロックより長い期間とすることが好ましい。

【0056】

一方、記憶装置20側では、リセット要求判定部270が、クロック信号SCKおよびデータ信号SDAを監視しており、クロック信号SCKの立ち上がりを検出してから(時刻T1、ステップS20)、データ信号SDAよりリセット要求に対応するレベル変化、すなわち、ロー、ハイ、ローのレベル変化を検出する(時刻T2,T3、ステップS21)と、ステップS20,S21にて検出された一連のレベル変化が、ホストコンピューター10からのリセット要求であると判定する。この場合、リセット実行部271は、リセット信号RSTを送出することにより、記憶装置20をリセットする(ステップS22)。もっとも、図8の処理では、データ信号SDAのロー、ハイ、ローのレベル変化を検出した後に記憶装置20をリセットしたが、クロック信号SCKの立ち上がり、データ信号SDAのロー、ハイ、ローのレベル変化を検出した後、さらにクロック信号SCKの立ち下がりを検出した後に、記憶装置20をリセットするようにしてもよい。

【0057】

記憶装置20のリセットは、リセット実行部271が、通信制御部30の各構成、すなわちアドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26に対してリセット信号RSTを送出して、初期化を実行させることにより行われる。このリセットにより、アドレスカウンター22はカウント値をクリアし、IDコンパレーター24は第1レジスター240および第2レジスター241をクリアする。I/Oコントローラー26は、メモリーアレイ21に対するデータ転送方向を読み出し方向に設定すると共に、データ信号端子DTと接続されている信号線をハイインピーダンスにしてデータ転送を禁止する。

【0058】

なお、リセット要求判定部270が、クロック信号SCKの立ち上がりを検出した後、データ信号SDAにロー、ハイ、ローのレベル変化が生じるより前に、クロック信号SCKの立ち下がりを検出した場合、これは、クロック信号SCKに同期させた通常のデータ通信で起こりうるレベル変化であり、上述したリセット要求に対応するレベル変化ではないので、リセットは行われない。

【0059】

記憶装置20がリセットされると、次に、ホストコンピューター10、記憶装置20間においてデータ列100に従うデータ通信が開始される。ホストコンピューター10は、クロック信号SCKに同期したデータ信号SDAのデータ通信によりIDデータ110を送信する(ステップS13)。記憶装置20は、ホストコンピューター10からIDデータ110を受信して、IDコンパレーター24はIDデータ110を第1レジスター240に格納する(ステップS23)。

【0060】

次に、IDコンパレーター24は、I/Oコントローラー26を介してメモリーアレイ21に記憶された識別データ210を取得して第2レジスター241に格納し、第1レジスター240に格納したIDデータ110と、第2レジスター241に格納した識別データ210とが一致しているか否かを判定する(ステップS24)。IDデータ110と識別データ210とが一致していれば(ステップS24:Yes)、ホストコンピューター10と記憶装置20との間でデータ列100に従うデータ通信が行われて、メモリーアレイ21へのアクセス制御が行われる。より詳細には、ホストコンピューター10は、データ列100に従って、読み出し/書き込みコマンド120、処理データ130、ACKデータ140を順次送出することにより記憶装置20とのデータ通信を行う(ステップS14)。記憶装置20側では、オペレーションコードデコーダー25およびI/Oコントローラー26が、受信した読み出し/書き込みコマンド120、処理データ130、ACKデータ140に応じた処理を行うことにより、ホストコンピューター10からメモリーアレイ21への情報の書き込みや読み出しなどのアクセスを制御する(ステップS25)。そして、記憶装置20のオペレーションコードデコーダー25が、送出されたデータ列100に含まれるACKデータ140を解釈すると、ホストコンピューター10からメモリーアレイ21へのアクセスが完了したと判断して、図8の処理が終了する。

【0061】

なお、ステップS24の判断において、IDデータ110と識別データ210とが一致していない場合は(ステップS24:No)、ホストコンピューター10からメモリーアレイ21へのアクセスが禁止されて、図8の処理が終了する。

【0062】

以上に述べた第1の実施形態によれば、記憶装置20は、リセットにより初期化された後に、ホストコンピューター10とのデータ通信を開始して、ホストコンピューター10からメモリーアレイ21に対するアクセスが行われるよう構成されている。一方、ホストコンピューター10は、記憶装置20のメモリーアレイ21に対するアクセスに先立ち、クロック信号SCKを立ち上げてハイの状態を維持する間に、データ信号SDAをローからハイにいったん立ち上げてからローに立ち下がるレベル変化、すなわち2回のレベル変化を生じさせることによって記憶装置20にリセットを要求している。このリセット要求が、記憶装置20側で検出されると、記憶装置20にはリセットが実行される。したがって、ホストコンピューター10、記憶装置20間にリセット信号用の信号線が接続されていなくとも、ホストコンピューター10は、記憶装置20にリセットを要求してリセットさせてから記憶装置20とのデータ通信を開始し、メモリーアレイ21へのアクセス、すなわちメモリーアレイ21から情報を読み出したり、メモリーアレイ21に情報を書き込んだりすることができる。また、記憶装置20またはホストコンピューター10、もしくは記憶装置20とホストコンピューター10との間の回路基板に、リセット信号線やリセット信号線を接続するための端子や配線等をなくすることができる。このため、記憶装置20およびホストコンピューター10を含めた通信システム1の回路構成を簡素化して、設計工数の削減および製品コストの低廉化を図ることができる。

【0063】

また、ホストコンピューター10は、記憶装置20とのデータ通信を開始すると、クロック信号SCKに同期させたデータ通信によりIDデータ110を送出し、記憶装置20は、メモリーアレイ21に記憶される識別データ210と、IDデータ110とが一致する場合に、データ通信によるメモリーアレイ21へのアクセスが許可される。したがって、ホストコンピューター10から記憶装置20へのアクセス、すなわちメモリーアレイ21へのアクセスを適切に管理することができる。

【0064】

(第2の実施形態)

次に、本発明の第2の実施形態について説明する。上記第1の実施形態では、ホストコンピューター10は記憶装置20に対してリセット要求を行った後、クロック信号SCKに同期させたデータ通信により、記憶装置20にIDデータ110を送信するようにしたが、第2の実施形態では、データ信号SDAのレベルをローからハイ、さらにハイからローに変化させるレベル変化をIDデータに対応する回数だけ繰り返し生じさせることにより、記憶装置20にIDデータ110を送信する。なお、以下では、第1の実施形態と同様の構成については、同じ符号を付与し、詳細な説明を省略することとする。

【0065】

図9は、第2の実施形態で用いられるクロック信号とデータ信号の一例を示したタイミングチャートである。図9に示すように、クロック信号SCKが、ローからハイに立ち上がり、ハイの信号状態を維持する間(時刻T10〜T13)に、データ信号SDAは、ローからハイに立ち上げて(時刻T11)からローに立ち下がる(時刻T2)レベル変化を生じた場合に、この信号の組み合わせをリセット要求とする。これは第1の実施形態と同様である。

【0066】

第2の実施形態では、リセット要求がされた後、ホストコンピューター10は、クロック信号SCKをローとした状態で、IDデータ110に対応する回数だけ、ローからハイ、ハイからローとするレベル変化をデータ信号SDAに生じさせる。図9の例では、IDデータが”2”である場合に対応して、ローからハイ、ハイからローへと変化するレベル変化が時刻T14〜T15と時刻T16〜T17の計2回発生させている。こうして、ホストコンピューター10は、記憶装置20にリセットを要求するとともに、レベル変化の回数の形式でIDデータ110を記憶装置20に送出する。

【0067】

また、第2の実施形態に係る通信システムの記憶装置側には、上述したようにデータ信号のレベル変化の回数として送出されたIDデータに対応する処理を行うため、第1の実施形態のリセット処理ユニット27に替えて、図10に示したリセット処理ユニット27’が設けられる。リセット処理ユニット27’は、リセット要求判定部270と、リセット実行部271と、パルス数カウンター272と、IDデータ送出部273とを有している。なお、リセット要求判定部270、リセット実行部271については第1の実施形態と同様である。

【0068】

パルス数カウンター272は、リセット要求がされた後のデータ信号SDAについて、ローからハイ、ハイからローにレベル変化した回数をカウントする。IDデータ送出部273は、パルス数カウンター272からカウント値を受け取り、このカウント値をIDデータ110としてIDコンパレーター24に送出する。

【0069】

IDコンパレーター24は、リセット処理ユニット27’から受け取ったIDデータ110を第1レジスター240に格納し、IDデータ110と第2レジスター241に格納した識別データ210とが一致するかの判定を行う。この判定でIDデータ110と識別データ210とが一致した場合に、ホストコンピューター10と記憶装置20との間で行われるデータ通信については、第1の実施形態と同様であるため、詳細な説明は省略する。

【0070】

以上に述べた第2の実施形態によれば、ホストコンピューター10は、記憶装置20にクロック信号SCKおよびデータ信号SDAを用いてリセットを要求した後、IDデータ110に対応する回数のレベル変化をデータ信号SDAに生じさせることにより、記憶装置20のメモリーアレイ21にアクセスすることができる。したがって、第1の実施形態と同様の効果を得ることができる。また、データ信号SDAのレベル変化により、IDデータ110を記憶装置20に送出するようにしているので、クロック信号SCKが安定していない状況においても、IDデータ110を確実に送出することができる。

【0071】

(第3の実施形態)

次に、本発明の第3の実施形態について説明する。上記第2の実施形態では、ホストコンピューター10は記憶装置20に対してリセット要求を行った後、IDデータ110に対応する回数だけデータ信号SDAにレベル変化を生じさせることによって記憶装置20にIDデータ110を送信するようにしたが、第3の実施形態では、リセット要求とともに、IDデータ110に応じた回数分だけデータ信号SDAのレベル変化を生じさせることにより、IDデータ110を送信する。

【0072】

図11に、第3の実施形態で用いられるクロック信号とデータ信号の一例を示す。図示するように、クロック信号SCKが、ローからハイに立ち上がり、ハイの状態を維持する期間(時刻T20〜T25)に、データ信号SDAは、ローからハイに立ち上げてからローに立ち下がるレベル変化(時刻T21〜T22)を生じた場合に、この信号の組み合わせをリセット要求とする。これは第1の実施形態および第2の実施形態と同様である。

【0073】

さらに、ホストコンピューター10は、リセット要求においてクロック信号SCKがハイとなっている期間に、IDデータ110に対応する回数分だけ、ローからハイ、ハイからローとするレベル変化をデータ信号SDAに生じさせる。図11の例では、IDデータ110が”2”である場合に対応して、ローからハイ、ハイからローへのレベル変化を時刻T21〜T22と時刻T23〜T24の計2回発生させている。こうして、ホストコンピューター10は、記憶装置20にリセット要求とともに、IDデータ110をレベル変化の回数として記憶装置20に送出する。なお、本実施形態では、リセット要求で用いられたデータ信号SDAのレベル変化(時刻T21〜T22)も1回分に含めてカウントしているが、リセット要求で用いられたレベル変化はIDデータ110に対応するレベル変化の回数には含めないようにしてもよい。

【0074】

また、第3の実施形態の通信システムの記憶装置側には、第2の実施形態と同様に、リセット要求判定部270と、リセット実行部271と、パルス数カウンター(カウント部)272と、IDデータ送出部273と、を有したリセット処理ユニット27’が設けられる。

【0075】

第3の実施形態においては、パルス数カウンター272が行う処理が第2の実施形態と異なる。すなわち、上述したように、パルス数カウンター272は、リセット要求のためクロック信号SCKがハイとなっている期間に、ローからハイ、ハイからローとするレベル変化の回数をカウントする。この他の構成(リセット要求判定部270、リセット実行部271、IDデータ送出部273)については第2の実施形態と同様である。

【0076】

次に、通信システム1の動作について説明する。図12は、ホストコンピューター10および記憶装置20によって実行される処理の手順を示したフローチャートである。以下、図11に示した信号波形例および図12のフローチャートに従って説明する。

【0077】

図12の処理が開始されると、ホストコンピューター10は、クロック信号SCKおよびデータ信号SDAにより記憶装置20にリセットを要求する。このため、ホストコンピューター10は、まず、クロック信号SCKのレベルをローからハイに立ち上げ(時刻T20、ステップS30)、クロック信号SCKの立ち上げ後に、IDデータ110に対応する回数だけ、データ信号SDAをローからハイ、さらにハイからローにレベル変化させる(時刻T21〜24、ステップS31)。その後、クロック信号SCKのレベルをハイからローに立ち下げる(時刻T25、ステップS32)。

【0078】

一方、記憶装置20側では、リセット処理ユニット27のリセット要求判定部270が、クロック信号SCKおよびデータ信号SDAを監視しており、クロック信号SCKの立ち上がりを検出すると(時刻T20、ステップS40)、パルス数カウンター272は、データ信号SDAがレベル変化した回数をカウントする(時刻T21〜24、ステップS41)。リセット要求判定部270は、クロック信号SCKの立ち下げを検出すると(時刻T25、ステップS42)、リセット要求判定部270は、ステップS40からS42にて検出した一連のレベル変化が、ホストコンピューター10からのリセット要求であると判定して、記憶装置20をリセットする(ステップS43)。なお、ステップS41のカウントは、ステップS42においてクロック信号SCKの立ち下げを検出するまで行われる。

【0079】

次に、IDデータ送出部273は、パルス数カウンター272のカウント値、すなわちクロック信号SCKがハイを維持する期間にデータ信号SDAに生じたレベル変化の回数をIDデータ110として、IDデータ110をIDコンパレーター24に送出する(ステップS44)。

【0080】

以降の処理のステップS45,S46,S33については、第1の実施形態におけるステップS24,S25,S14と同様である。すなわち、IDコンパレーター24は、第1レジスター240に格納したIDデータ110と、第2レジスター241に格納した識別データ210とを比較して、一致しているか否かを判定する(ステップS45)。IDデータ110と識別データ210とが一致していれば(ステップS45:Yes)、ホストコンピューター10と記憶装置20との間でデータ通信が開始されて、ホストコンピューター10は、読み出し/書き込みコマンド120、処理データ130、ACKデータ140を送出する(ステップS33)。記憶装置20側では、オペレーションコードデコーダー25およびI/Oコントローラー26が、受信した読み出し/書き込みコマンド120、処理データ130、ACKデータ140に応じた処理を行うことにより、ホストコンピューター10からメモリーアレイ21への情報の書き込みや読み出しなどのアクセスを制御する(ステップS46)。そして、記憶装置20のオペレーションコードデコーダー25が、送出されたデータ列100に含まれるACKデータ140を解釈した場合、または、ステップS45の判断において、IDデータ110と識別データ210とが一致しない場合に(ステップS25:No)、図12の処理が終了する。

【0081】

以上に述べた第3の実施形態によれば、ホストコンピューター10は、記憶装置20にリセットを要求するとともに、データ信号SDAのレベルがローからハイ、ハイからローに変化したレベル変化を、IDデータに対応する回数分だけ生じさせることにより、記憶装置20とのデータ通信を行ってメモリーアレイ21にアクセスすることができる。したがって、第1の実施形態および第2の実施形態と同様の効果を得ることができる。また、第1の実施形態や第2の実施形態とは異なり、リセット要求とともにIDデータ110を記憶装置20に伝えるようにしているので、メモリーアレイ21へのアクセスをより早いタイミングで開始することができる。

【0082】

以上、本発明の第1ないし第3の実施形態について説明したが、本発明はこれらの形態に限られることなく、その趣旨並びに特許請求の範囲を逸脱することなく、変更、改良され得ると共に、本発明にはその等価物が含まれることはもちろんである。その趣旨に逸脱しない範囲で様々な態様とすることもできる。以下、変形例について説明する。

【0083】

(変形例1)

上記第1ないし第3の実施形態では、クロック信号SCKをハイにした状態で、データ信号SDAにロー、ハイ、ローとなるレベル変化を、ホストコンピューター10から記憶装置20へのリセット要求としたが、リセット要求に対応させるクロック信号SCKとデータ信号SDAの組み合わせはこれに限られるものではない。すなわち、クロック信号SCKに同期させたデータ信号SDAによるデータ通信において、通常は用いられない信号の組み合わせをリセット要求とすることを、ホストコンピューター10と記憶装置20との間で予め取り決めておけばよい。例えば、図13(a)に示すように、クロック信号SCKをハイから立ち下げてローになっている期間(時刻T30〜T33)に、データ信号SDAがロー、ハイ、ローと変化する2回のレベル変化(時刻T31,T32)を、リセット要求としてもよい。また、図13(b)に示すように、クロック信号SCKをローから立ち上げてハイになっている期間(時刻T40〜T43)に、データ信号SDAがハイ、ロー、ハイと変化する2回のレベル変化(時刻T41,T42)を、リセット要求としてもよい。もっとも、リセット要求においてデータ信号SDAのレベルを変化させる回数は2回に限られることなく、より多くの回数のレベル変化をリセット要求に含めるようにしてもよい。

【0084】

また、クロック信号SCKのレベルを変化させずに、データ信号SDAだけを複数回レベル変化させることにより、リセット要求としてもよい。このようにしても、クロック信号SCKとデータ信号SDAの組み合わせが、クロックに同期させたデータ通信では用いられないものであるので、記憶装置20側において、クロックに同期したデータ通信の信号と混同することなく、リセット要求を正しく認識することができる。もっとも、上記第1ないし第3の実施形態のように、クロック信号SCKをハイまたはローのレベルに変化させた後にそのレベルを維持するようにした場合には、クロック信号SCKのレベル変化も用いてリセット要求が判定されるので、リセット要求の判定をより確実に行うことができる。

【0085】

(変形例2)

上記第2および第3の実施形態では、データ信号SDAはローからハイへのレベル変化と、ハイからローへのレベル変化とを含めて1回としてカウントして、このカウント値をIDデータとしたが、ローからハイにレベル変化した回数とハイからローになったレベル変化の回数を別々にカウントして、両カウント値を合計した値をIDデータとしてもよい。また、一方のレベル変化のみをカウントするようにしてもよい。

【0086】

(変形例3)

上記第1ないし第3の実施形態では、メモリーアレイ200へのアクセスを許可するために用いられる識別データ210を、記憶装置20のメモリーアレイ200自体に記憶する構成としたが、メモリーアレイ200とは別に設けた記憶部に識別データ210を記憶する構成としてもよい。

【0087】

(変形例4)

上記第1ないし第3の実施形態では、インクジェットプリンター用のインクカートリッジにインクカートリッジ情報を格納するための記憶装置20を備えた構成について説明したが、本発明に係る記憶装置および通信システムはこの態様に限られるものではない。本発明は、例えば、レーザープリンターのトナーカートリッジや現像ユニットなど、様々な交換部品に設けられる記憶装置、およびこの記憶装置を含む通信システムに適用することができる。

【符号の説明】

【0088】

1…通信システム、10…ホストコンピューター、20…記憶装置、21…記憶部としてのメモリーアレイ、22…アドレスカウンター、23…メモリーコントローラー、24…IDコンパレーター、25…オペレーションコードデコーダー、26…I/Oコントローラー、27…リセット処理ユニット、30…通信制御部、100…データ列、110…第2識別情報としてのIDデータ、120…読み出し/書き込みコマンド、130…処理データ、210…第1識別情報としての識別データ、270…リセット要求判定部、271…リセット実行部、272…カウント部としてのパルス数カウンター、273…IDデータ送出部、CT…第1端子としてのクロック信号端子、DT…第2端子としてのデータ信号端子、SCK…クロック信号、SDA…データ信号。

【技術分野】

【0001】

本発明は、ホストコンピューターとのデータ通信を行う記憶装置、カートリッジ、通信システムおよび記憶装置の制御方法に関する。

【背景技術】

【0002】

記憶装置と、記憶装置を制御するホストコンピューターとの間の通信を、クロック信号線、データ信号線、リセット信号線の3線を用いて行うようにしたシステムが知られている(例えば、特許文献1参照)。

【0003】

特許文献1に記載のシステムは、インクジェットプリンターのインクカートリッジに備わる記憶装置と、プリンターの本体側に備わるホストコンピューターとの通信を、クロック信号線、データ信号線、リセット信号線の3線を用いて行うものである。このシステムでは、ホストコンピューターから記憶装置にアクセスする際、ホストコンピューターはリセット信号線を介して記憶装置にリセット信号を送出する。記憶装置は、リセット信号を受信するとリセットを実行し、例えば、記憶装置の内部に備わるレジスターをクリアすることによって記憶装置の初期化が行われる。記憶装置が初期化された後、記憶装置とホストコンピューターとの間でクロック信号に同期させたデータ通信が開始されて、このデータ通信により、ホストコンピューターが記憶装置のメモリーアレイにアクセスできるよう構成されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−14870号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載のシステムは、クロック信号線、データ信号線、リセット信号線の3つの信号線を実装する必要があるため、記憶装置やホストコンピューター側の配線や端子などの回路構成が複雑化するという課題があった。このため、回路設計の設計工数の増大や製品コストの増大などをもたらすこととなっていた。

【0006】

また、例えば、インク色ごとに異なるインクカートリッジが装着されるインクジェットプリンターのように、1つのプリンターに対して複数のインクカートリッジが装着される場合、1つのホストコンピューターに対して複数の記憶装置が備わるシステムとなる。このシステムにおいて、各記憶装置に対してクロック信号線、データ信号線およびリセット信号線を配線した場合、回路構成の複雑化がより顕著になってしまう。

【課題を解決するための手段】

【0007】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0008】

[適用例1]クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置であって、前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする記憶装置。

【0009】

この構成によれば、クロック信号が所定のレベルを維持する期間にデータ信号に複数回のレベル変化を生じた場合にリセットが実行されて、リセットした後に記憶装置の記憶部にアクセスするデータ通信が開始される。したがって、クロック信号およびデータ信号によって記憶装置の記憶部にアクセスすることが可能であり、特許文献1に記載の記憶装置に比べると、リセット信号線を接続するための端子や配線等の回路構成がない簡易な構成の記憶装置を得ることができる。また、回路構成を簡易化できるため、記憶装置の設計工数を削減できるとともに、製品コストの低廉化を実現できる。

【0010】

[適用例2]上記記憶装置において、前記リセット実行部は、前記クロック信号が前記所定のレベルに変化した後の前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させることを特徴とする記憶装置。

【0011】

この構成によれば、クロック信号が所定のレベルに変化したレベル変化も用いて、リセットを実行するタイミングをより正確に判断することができる。

【0012】

[適用例3]上記記憶装置において、前記記憶部は、第1識別情報を記憶し、前記通信制御部は、前記第1識別情報と、前記データ信号により入力される第2識別情報とを比較して、前記第1識別情報と前記第2識別情報とが一致する場合に、前記データ通信における前記記憶部へのアクセスを許可することを特徴とする記憶装置。

【0013】

この構成によれば、記憶部に記憶された第1識別情報と、データ信号により入力された第2識別情報とが一致する場合に、データ通信による記憶部へのアクセスが許可されるので、記憶部へのアクセスを適切に管理することができる。

【0014】

[適用例4]上記記憶装置において、前記データ通信を開始した後、前記データ信号のレベルが変化した回数をカウントするカウント部を備え、前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【0015】

この構成によれば、データ通信を開始した後に、データ信号のレベルが変化した回数に応じて第2識別情報が取得され、第1識別情報および第2識別情報により記憶部へのアクセスが許可される。したがって、記憶部へのアクセスを適切に管理することができる。

【0016】

[適用例5]上記記憶装置において、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号のレベルが変化した回数をカウントするカウント部を備え、前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【0017】

この構成によれば、クロック信号が所定のレベルを維持する期間に、レベルが変化した回数に応じて第2識別情報が取得され、第1識別情報および第2識別情報により記憶部へのアクセスが許可される。したがって、記憶部へのアクセスを適切に管理することができる。

【0018】

[適用例6]クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置を備えるカートリッジであって、前記記憶装置は、前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とするカートリッジ。

【0019】

この構成によれば、リセット信号線を接続するための端子や配線等の回路構成がない簡易な構成のカートリッジを実現することができる。

【0020】

[適用例7]記憶部を有する記憶装置とホスト装置とがクロック信号線およびデータ信号線を介して接続される通信システムであって、前記記憶装置は、前記クロック信号線のクロック信号および前記データ信号線のデータ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする通信システム。

【0021】

この構成によれば、記憶装置またはホスト装置、もしくは記憶装置とホスト装置の間に、リセット信号線を接続するための端子や配線等の回路構成がない簡易な構成の通信システムを実現することができる。

【0022】

[適用例8]クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置の制御方法であって、前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、リセットを実行するステップと、前記リセットにより初期化した後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始するステップと、を含むことを特徴とする記憶装置の制御方法。

【0023】

このようにすれば、リセットにより初期化された後にデータ通信によって記憶部にアクセスできるよう構成された記憶装置に対して、リセット信号を用いることなく、クロック信号およびデータ信号によってアクセスすることができる。

【図面の簡単な説明】

【0024】

【図1】第1の実施形態に係る通信システムの概略構成を示したブロック図である。

【図2】インクカートリッジの概観斜視図である。

【図3】ホストコンピューターの構成を示したブロック図である。

【図4】データ列のデータ構造を示したブロック図である。

【図5】記憶装置内部の回路構成を示したブロック図である。

【図6】クロック信号とデータ信号の一例を示したタイミングチャートである。

【図7】リセット処理ユニットの構成を示したブロック図である。

【図8】ホストコンピューターによって行われる処理および記憶装置によって行われる処理の手順を示したフローチャートである。

【図9】第2の実施形態におけるクロック信号とデータ信号の一例を示したタイミングチャートである。

【図10】リセット処理ユニットの構成を示したブロック図である。

【図11】第3の実施形態におけるクロック信号とデータ信号の一例を示したタイミングチャートである。

【図12】ホストコンピューターによって行われる処理および記憶装置によって行われる処理の手順を示したフローチャートである。

【図13】第1の変形例を説明する説明図である。

【発明を実施するための形態】

【0025】

(第1の実施形態)

以下、本発明の実施形態について図面を参照して説明する。なお、本実施形態では、通信システムの一例として、インクジェットプリンターに備わる通信システムについて説明する。

【0026】

図1は、第1の実施形態に係る通信システムの概略構成を示した図である。図1に示すように、通信システム1は、複数の記憶装置20(20a〜20d)と、記憶装置20のホスト装置としてのホストコンピューター10とを含む。記憶装置20は、図2に示すように、4色のインクカートリッジC1〜C4にそれぞれ備えられるものである。例えば、シアンのインクを収容したインクカートリッジC1には記憶装置20a、マゼンタのインクを収容したインクカートリッジC2には記憶装置20b、イエローのインクを収容したインクカートリッジC3には記憶装置20c、ブラックのインクを収容したインクカートリッジC4には記憶装置20dが備えられる。もっとも、記憶装置20の数およびカートリッジの種類についてはこれに限られるものではない。また、ホストコンピューター10の例としては、インクジェットプリンターの本体側に配置されたプリンタコントローラーなどが挙げられる。

【0027】

記憶装置20(20a〜20d)は、インクカートリッジCに設けられたメモリモジュール基板上に配置され、クロック信号端子(第1端子)CTおよびデータ信号端子(第2端子)DTを有している。クロック信号端子CTにはクロック信号線CLが接続されており、クロック信号線CLはクロックバスCBを介してホストコンピューター10に接続されている。一方、データ信号端子DTにはデータ信号線DLが接続されており、データ信号線DLはデータバスDBを介してホストコンピューター10に接続されている。

【0028】

図3は、ホストコンピューター10の構成を示した図である。図3に示すように、ホストコンピューター10は、クロック信号生成回路11、電源回路12、電源補償回路13、データ記憶回路14および各回路を制御する制御回路15を備える制御装置である。ホストコンピューター10は、印刷制御の他、記憶装置20a〜20dへのアクセス制御や、インク消費量、インクカートリッジCの装着時間といったデータを記憶装置20から取得してデータ記憶回路14に記憶する制御などを行う。

【0029】

電源補償回路13は、電源の供給が遮断された場合にも所定の期間(例えば、0.3s)、記憶装置20に電源を供給する。これにより、停電、電源プラグが抜かれることによってデータ書き込み中の電源が遮断されても、上述した所定期間の間に書き込みを優先すべきデータの書き込みを完了することができる。電源補償回路13としては、例えば、コンデンサーが用いられる。

【0030】

制御回路15は、電源回路12を制御して正電源の出力を制御する。ホストコンピューター10は、各記憶装置20a〜20dに対して常時電源を供給しておらず、記憶装置20a〜20dに対するアクセス要求が発生した場合にのみ、記憶装置20a〜20dに対して正電源を供給する。

【0031】

クロック信号生成回路11は、クロック信号SCKを生成する。生成されたクロック信号SCKは、クロック信号線CLを介して各記憶装置20a〜20dに供給される。

【0032】

また、制御回路15は、記憶装置20とのデータ通信を制御する。制御回路15は、記憶装置20とデータ通信する際、所定のフォーマットに従うデータ列を送出する。

【0033】

次に、ホストコンピューター10と記憶装置20との間のデータ通信で用いられるデータ列のデータ構造について説明する。図4は、データ列のデータ構造を示した図である。図4に示すように、データ列100には、IDデータ(第2識別情報)110と、読み出し/書き込みコマンド120と、処理データ130と、ACKデータ140と、が含まれる。IDデータ110は、例えば、3ビットのデータであり、プリンターに装着された複数のインクカートリッジの各記憶装置20a〜20dのうちから、データの読み出しや書き込みの対象とする記憶装置20を指定するための識別情報である。読み出し/書き込みコマンド120は、記憶装置20に対しての読み出しまたは書き込みの処理種別を指定するコマンドである。処理データ130は、読み出し/書き込みコマンド120で指定された処理の対象となるデータである。なお、読み出し/書き込みコマンド120と処理データ130とは対になっており、データ列100には、読み出し/書き込みコマンド120と処理データ130を含む組が繰り返し含まれる。ACKデータ140は、記憶装置20からホストコンピューター10に送出されるデータ列100の最後に付加されるものであり、ホストコンピューター10が送出したデータ列100に従う処理が正常に行われたことを示す。ホストコンピューター10は、上述したデータ列100を構成するデータを、クロック信号SCKに同期させてデータ信号SDAにより記憶装置20に順次送出する。これにより、ホストコンピューター10と、記憶装置20との間でクロック信号SCKに同期したデータ通信が行われる。

【0034】

制御回路15は、インクジェットプリンターの電源投入時、インクカートリッジの交換時、印刷ジョブの終了時、インクジェットプリンターの電源遮断時などに、上述したデータ列100に従うデータ通信により記憶装置20a〜20dに対するアクセスを実行する。

【0035】

ここで、ホストコンピューター10から記憶装置20にアクセスする場合、ホストコンピューター10は、データ通信によるアクセスに先立ち、記憶装置20にリセットを実行させる必要がある。すなわち、記憶装置20は、リセットにより初期化された後にクロック信号SCKに同期したデータ通信によるアクセスが可能に構成されている。詳細は後述するが、これは、記憶装置20とのデータ通信を開始するには、リセットによって記憶装置20内部に備わるレジスターなどを初期化することによって、記憶装置20を新たなアクセスに対して対処可能な状態としておく必要があるからである。このため、制御回路15は、インクジェットプリンターの電源投入時、インクカートリッジの交換時、印刷ジョブの終了時、インクジェットプリンターの電源遮断時など、ホストコンピューター10から記憶装置20にアクセスする場合に記憶装置20に対してリセットを要求する。

【0036】

次に、記憶装置20の内部構成について説明する。図5は、記憶装置20内部の回路構成を示したブロック図である。なお、以下では、1つの記憶装置20の内部構成を例に挙げて説明するが、各記憶装置20a〜20dの内部構成は、メモリーアレイに格納されているデータを除いて同じである。

【0037】

図5に示すように、記憶装置20は、メモリーアレイ21と、アドレスカウンター22と、メモリーコントローラー23と、IDコンパレーター24と、オペレーションコードデコーダー25と、I/Oコントローラー26と、リセット処理ユニット27と、を備えている。なお、記憶装置20の構成のうち、アドレスカウンター22、IDコンパレーター24、オペレーションコードデコーダー25およびI/Oコントローラー26が、メモリーアレイ21にアクセスするデータ通信を制御する通信制御部30に相当する。

【0038】

メモリーアレイ21は、EEPROMやフラッシュROMなど、不揮発的に記憶内容を保持すると共に記憶内容を書き換え可能なメモリーであり、記憶装置20の記憶部である。メモリーアレイ21は、例えば、256ビットなどの所定容量の記憶領域を有し、先頭アドレスから順次アクセスが可能、すなわちシーケンシャルにアクセス可能に構成されている。先頭から3ビットの記憶領域には、インクカートリッジCの種類またはインクカートリッジCが収容するインクの種類に応じて予め決められた識別データ(第1識別情報)210が格納されている。先頭から4ビット目の記憶領域は無効領域とされている。なお、本実施形態では、記憶装置20のメモリーアレイ200自体に識別データ210を記憶する構成としたが、メモリーアレイ200とは別に設けた記憶素子に識別データ210を記憶するようにしてもよい。

【0039】

アドレスカウンター22は、クロック信号SCKに同期してそのカウント値をインクリメントする回路であり、クロック信号端子CT、メモリーアレイ21およびリセット処理ユニット27と接続されている。アドレスカウンター22のカウント値とメモリーアレイ21の記憶領域位置(アドレス)とは関連付けられており、アドレスカウンター22のカウント値によってメモリーアレイ21における書き込み位置または読み出し位置を指定することができる。

【0040】

また、アドレスカウンター22は、リセット処理ユニット27からのリセット信号RSTが入力されると、カウント値を初期値にリセットすることにより初期化を行う。ここで、初期値はメモリーアレイ21の先頭位置と関連付けられていればどのような値でもよく、例えば、”0”が初期値として用いられる。

【0041】

メモリーコントローラー23は、メモリーアレイ21、アドレスカウンター22およびI/Oコントローラー26に接続されており、I/Oコントローラー26の制御に従ってメモリーアレイ21の記憶領域のうち、アドレスカウンター22が指定するアドレスの領域への情報の書き込み/読み出しを実行する。具体的には、メモリーアレイ21から情報を読み出してI/Oコントローラー26に受け渡す処理や、I/Oコントローラー26から書き込み対象の情報を受け取ってメモリーアレイ21の記憶領域に書き込む処理などを行う。

【0042】

IDコンパレーター24は、クロック信号端子CT、データ信号端子DT、I/Oコントローラー26およびオペレーションコードデコーダー25と接続されており、データ信号端子DTを介して入力されるデータ列100に含まれるIDデータ110とメモリーアレイ21に格納されている識別データ210とを比較して一致するか否かを判定する。また、IDコンパレーター24は、ホストコンピューター10から入力されたIDデータ110を格納する3ビットの第1レジスター240と、I/Oコントローラー26を介してメモリーアレイ21から取得した識別データ210を格納する第2レジスター241とを有している。IDコンパレーター24は、第1レジスター240に格納されたIDデータ110と、第2レジスター241に格納された識別データ210とが一致する場合に、ホストコンピューター10からメモリーアレイ21へのアクセスを許可する旨のアクセス許可信号ENをオペレーションコードデコーダー25に送出する。

【0043】

なお、IDコンパレーター24は、リセット処理ユニット27からのリセット信号RSTの入力により初期化を行う。IDコンパレーター24の初期化は、第1レジスター240および第2レジスター241に格納された情報をクリアすることによって行われる。初期化後のIDコンパレーター24は新たなIDデータ110の入力待ちの状態となり、この状態においてホストコンピューター10からデータ列100が送出されると、データ列100に含まれるIDデータ110を取得して第1レジスター240に格納するよう構成されている。また、IDコンパレーター24は、IDデータ110を第1レジスター240に格納した後などの所定のタイミングで、I/Oコントローラー26を介してメモリーアレイ21から識別データ210を取得して第2レジスター241に格納する。

【0044】

オペレーションコードデコーダー25は、クロック信号端子CT、データ信号端子DT、IDコンパレーター24およびI/Oコントローラー26と接続されており、ホストコンピューター10から送出されたデータ列100より読み出し/書き込みコマンド120を取得する。オペレーションコードデコーダー25は、IDコンパレーター24からアクセス許可信号ENが入力されると、取得した読み出し/書き込みコマンド120を解析して、解析結果に応じて書き込み処理要求または読み出し処理要求をI/Oコントローラー26に送出する。

【0045】

I/Oコントローラー26は、クロック信号端子CT、データ信号端子DT、メモリーコントローラー23、オペレーションコードデコーダー25およびリセット処理ユニット27と接続されており、オペレーションコードデコーダー25からの要求に従ってメモリーアレイ21に対するデータ転送方向ならびにデータ信号端子DTに対するデータ転送方向を切り換え制御する。

【0046】

また、I/Oコントローラー26は、リセット処理ユニット27からのリセット信号RSTの入力により初期化を行う。I/Oコントローラー26の初期化は、メモリーアレイ21に対するデータ転送方向を読み出し方向に設定し、データ信号端子DTと接続されている信号線をハイインピーダンスとすることでデータ信号端子DTに対するデータ転送を禁止することによって行われる。こうして初期化した状態は、オペレーションコードデコーダー25から書き込み処理要求または読み出し処理要求が入力されるまで維持される。したがって、リセット信号RSTが入力された後にデータ信号端子DTを介して入力されるデータ列100の先頭4ビットのデータ(すなわち、IDデータ110および読み出し/書き込みコマンド120)はメモリーアレイ21に書き込まれることはない。一方で、メモリーアレイ21の先頭4ビット(内4ビット目は無効データ)に格納されているデータは、読み出し専用となり、IDコンパレーター24に送出される。

【0047】

ここで、上述したように、本実施形態の通信システム1では、ホストコンピューター10から記憶装置20にアクセスする際、アクセスに先立って記憶装置20の第1レジスター240に格納された情報をクリアさせることによって、IDコンパレーター24をIDデータ110の入力待ちの状態としておく必要がある。このため、ホストコンピューター10から記憶装置20に新たにアクセスして、メモリーアレイ21に対して情報の読み出しや書き込みをする際、ホストコンピューター10は、データ通信によるアクセスに先立って、記憶装置20にリセットを要求して、記憶装置20を初期化する必要がある。

【0048】

しかしながら、上述した構成の通信システム1は、特許文献1に記載のシステムのように、ホストコンピューター10と記憶装置20と間にリセット信号線が設けられていないため、リセット信号線を介してホストコンピューター10から記憶装置20にリセット信号を送出することはできない。

【0049】

そこで、本実施形態に係る通信システム1では、ホストコンピューター10から記憶装置20に対してアクセスを開始する際に、クロック信号のレベル(ハイ/ロー)とデータ信号のレベル(ハイ/ロー)に、クロック信号SCKに同期しないレベル変化の組み合わせをリセット要求として用いる。

【0050】

図6は、リセット要求に対応するクロック信号とデータ信号の組み合わせの一例を示したタイミングチャートである。図6に示すように、本実施形態では、リセット要求に対応する信号の組み合わせとして、クロック信号SCKを立ち上げてハイを維持する期間(時刻T1〜T4)に、データ信号SDAに対しては、ローからハイに立ち上げて(時刻T2)からローに立ち下げる(時刻T3)ことにより複数回のレベル変化を生じさせる。この一連のレベル変化の組み合わせを、リセット要求とする。すなわち、ホストコンピューター10と記憶装置20との間では、図6の時刻T1〜T4に示すクロック信号SCKとデータ信号SDAのレベル変化が、リセット要求に対応すると予め取り決められている。ホストコンピューター10は、記憶装置20に対してアクセスを開始する際、データ通信に先立ち、クロック信号SCKおよびデータ信号SDAに上述したレベル変化を生じさせることにより、ホストコンピューター10は記憶装置20に対してリセットを要求する。これにより、ホストコンピューター10、記憶装置20間にリセット信号用の信号線が接続されていなくとも、ホストコンピューター10から記憶装置20に対してリセットが要求される。

【0051】

ホストコンピューター10は、クロック信号SCKとデータ信号SDAにリセット要求に対応するレベル変化を生じさせた後、クロック信号SCKに同期させてデータ信号SDAによるデータ通信を行う(図6の時刻T5以降)。ホストコンピューター10から記憶装置20に送信するデータのフォーマットは上述したデータ列100に従うため、図6の時刻T5にデータ通信を開始した後、クロック信号SCKの立ち上がりに同期して、データ列100を構成するデータのうち先頭のIDデータ110から順番にデータを送信することにより、ホストコンピューター10は記憶装置20のメモリーアレイ21へのアクセスを行う。なお、データ通信におけるクロック信号SCKの同期方法としては、クロック信号SCKの立ち上がりのタイミングに同期させる方法に限られることなく、クロック信号の立ち下がりのタイミング、もしくは立ち上がりと立ち下がりの両方のタイミングに同期させるようにしてもよい。

【0052】

また、記憶装置20には、上述したリセット要求に対応して記憶装置20にリセットを実行させる処理を行うため、リセット処理ユニット27が備えられている。リセット処理ユニット27は、クロック信号端子CT、データ信号端子DT、アドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26と接続されており、図7に示すように、リセット要求判定部270と、リセット実行部271と、を有している。

【0053】

リセット要求判定部270は、クロック信号SCKとデータ信号SDAとを監視し、上述したリセット要求に対応するレベル変化を生じたか否かを判定する。リセット実行部271は、リセット要求判定部270の判定によって、クロック信号SCKおよびデータ信号SDAにリセット要求に対応するレベル変化を生じていた場合に、アドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26にリセット信号RSTを送出する。これにより、アドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26の各構成にリセットを実行させる。

【0054】

次に、通信システム1の動作について詳細に説明する。図8は、ホストコンピューター10によって行われる処理および記憶装置20によって行われる処理の手順を示したフローチャートである。以下、図6に示した信号波形例および図8のフローチャートに従って説明する。

【0055】

インクジェットプリンターの電源投入時、インクカートリッジの交換時、印刷ジョブの終了時、インクジェットプリンターの電源遮断時などに、図8の処理が開始される。処理が開始されると、ホストコンピューター10は、クロック信号SCKおよびデータ信号SDAを、図6に示したリセット要求に対応する組み合わせとすることにより記憶装置20に対してリセットを要求する。すなわち、ホストコンピューター10の制御回路15は、クロック信号生成回路11を制御してクロック信号SCKのレベルをローからハイに立ち上げる(時刻T1、ステップS10)。クロック信号SCKを立ち上がった後、制御回路15は、データ信号SDAをローからハイ、さらにローへと変化させてから(時刻T2,T3、ステップS11)、クロック信号SCKのレベルをハイからローに立ち下げる(時刻T4、ステップS12)。なお、クロック信号SCKをハイに立ち上げてからローに戻る期間(時刻T1〜T4)については、データ信号SDAのレベル変化を記憶装置20側で確実に検出できるよう、通常のデータ通信で用いられる1クロックより長い期間とすることが好ましい。

【0056】

一方、記憶装置20側では、リセット要求判定部270が、クロック信号SCKおよびデータ信号SDAを監視しており、クロック信号SCKの立ち上がりを検出してから(時刻T1、ステップS20)、データ信号SDAよりリセット要求に対応するレベル変化、すなわち、ロー、ハイ、ローのレベル変化を検出する(時刻T2,T3、ステップS21)と、ステップS20,S21にて検出された一連のレベル変化が、ホストコンピューター10からのリセット要求であると判定する。この場合、リセット実行部271は、リセット信号RSTを送出することにより、記憶装置20をリセットする(ステップS22)。もっとも、図8の処理では、データ信号SDAのロー、ハイ、ローのレベル変化を検出した後に記憶装置20をリセットしたが、クロック信号SCKの立ち上がり、データ信号SDAのロー、ハイ、ローのレベル変化を検出した後、さらにクロック信号SCKの立ち下がりを検出した後に、記憶装置20をリセットするようにしてもよい。

【0057】

記憶装置20のリセットは、リセット実行部271が、通信制御部30の各構成、すなわちアドレスカウンター22、IDコンパレーター24およびI/Oコントローラー26に対してリセット信号RSTを送出して、初期化を実行させることにより行われる。このリセットにより、アドレスカウンター22はカウント値をクリアし、IDコンパレーター24は第1レジスター240および第2レジスター241をクリアする。I/Oコントローラー26は、メモリーアレイ21に対するデータ転送方向を読み出し方向に設定すると共に、データ信号端子DTと接続されている信号線をハイインピーダンスにしてデータ転送を禁止する。

【0058】

なお、リセット要求判定部270が、クロック信号SCKの立ち上がりを検出した後、データ信号SDAにロー、ハイ、ローのレベル変化が生じるより前に、クロック信号SCKの立ち下がりを検出した場合、これは、クロック信号SCKに同期させた通常のデータ通信で起こりうるレベル変化であり、上述したリセット要求に対応するレベル変化ではないので、リセットは行われない。

【0059】

記憶装置20がリセットされると、次に、ホストコンピューター10、記憶装置20間においてデータ列100に従うデータ通信が開始される。ホストコンピューター10は、クロック信号SCKに同期したデータ信号SDAのデータ通信によりIDデータ110を送信する(ステップS13)。記憶装置20は、ホストコンピューター10からIDデータ110を受信して、IDコンパレーター24はIDデータ110を第1レジスター240に格納する(ステップS23)。

【0060】

次に、IDコンパレーター24は、I/Oコントローラー26を介してメモリーアレイ21に記憶された識別データ210を取得して第2レジスター241に格納し、第1レジスター240に格納したIDデータ110と、第2レジスター241に格納した識別データ210とが一致しているか否かを判定する(ステップS24)。IDデータ110と識別データ210とが一致していれば(ステップS24:Yes)、ホストコンピューター10と記憶装置20との間でデータ列100に従うデータ通信が行われて、メモリーアレイ21へのアクセス制御が行われる。より詳細には、ホストコンピューター10は、データ列100に従って、読み出し/書き込みコマンド120、処理データ130、ACKデータ140を順次送出することにより記憶装置20とのデータ通信を行う(ステップS14)。記憶装置20側では、オペレーションコードデコーダー25およびI/Oコントローラー26が、受信した読み出し/書き込みコマンド120、処理データ130、ACKデータ140に応じた処理を行うことにより、ホストコンピューター10からメモリーアレイ21への情報の書き込みや読み出しなどのアクセスを制御する(ステップS25)。そして、記憶装置20のオペレーションコードデコーダー25が、送出されたデータ列100に含まれるACKデータ140を解釈すると、ホストコンピューター10からメモリーアレイ21へのアクセスが完了したと判断して、図8の処理が終了する。

【0061】

なお、ステップS24の判断において、IDデータ110と識別データ210とが一致していない場合は(ステップS24:No)、ホストコンピューター10からメモリーアレイ21へのアクセスが禁止されて、図8の処理が終了する。

【0062】

以上に述べた第1の実施形態によれば、記憶装置20は、リセットにより初期化された後に、ホストコンピューター10とのデータ通信を開始して、ホストコンピューター10からメモリーアレイ21に対するアクセスが行われるよう構成されている。一方、ホストコンピューター10は、記憶装置20のメモリーアレイ21に対するアクセスに先立ち、クロック信号SCKを立ち上げてハイの状態を維持する間に、データ信号SDAをローからハイにいったん立ち上げてからローに立ち下がるレベル変化、すなわち2回のレベル変化を生じさせることによって記憶装置20にリセットを要求している。このリセット要求が、記憶装置20側で検出されると、記憶装置20にはリセットが実行される。したがって、ホストコンピューター10、記憶装置20間にリセット信号用の信号線が接続されていなくとも、ホストコンピューター10は、記憶装置20にリセットを要求してリセットさせてから記憶装置20とのデータ通信を開始し、メモリーアレイ21へのアクセス、すなわちメモリーアレイ21から情報を読み出したり、メモリーアレイ21に情報を書き込んだりすることができる。また、記憶装置20またはホストコンピューター10、もしくは記憶装置20とホストコンピューター10との間の回路基板に、リセット信号線やリセット信号線を接続するための端子や配線等をなくすることができる。このため、記憶装置20およびホストコンピューター10を含めた通信システム1の回路構成を簡素化して、設計工数の削減および製品コストの低廉化を図ることができる。

【0063】

また、ホストコンピューター10は、記憶装置20とのデータ通信を開始すると、クロック信号SCKに同期させたデータ通信によりIDデータ110を送出し、記憶装置20は、メモリーアレイ21に記憶される識別データ210と、IDデータ110とが一致する場合に、データ通信によるメモリーアレイ21へのアクセスが許可される。したがって、ホストコンピューター10から記憶装置20へのアクセス、すなわちメモリーアレイ21へのアクセスを適切に管理することができる。

【0064】

(第2の実施形態)

次に、本発明の第2の実施形態について説明する。上記第1の実施形態では、ホストコンピューター10は記憶装置20に対してリセット要求を行った後、クロック信号SCKに同期させたデータ通信により、記憶装置20にIDデータ110を送信するようにしたが、第2の実施形態では、データ信号SDAのレベルをローからハイ、さらにハイからローに変化させるレベル変化をIDデータに対応する回数だけ繰り返し生じさせることにより、記憶装置20にIDデータ110を送信する。なお、以下では、第1の実施形態と同様の構成については、同じ符号を付与し、詳細な説明を省略することとする。

【0065】

図9は、第2の実施形態で用いられるクロック信号とデータ信号の一例を示したタイミングチャートである。図9に示すように、クロック信号SCKが、ローからハイに立ち上がり、ハイの信号状態を維持する間(時刻T10〜T13)に、データ信号SDAは、ローからハイに立ち上げて(時刻T11)からローに立ち下がる(時刻T2)レベル変化を生じた場合に、この信号の組み合わせをリセット要求とする。これは第1の実施形態と同様である。

【0066】

第2の実施形態では、リセット要求がされた後、ホストコンピューター10は、クロック信号SCKをローとした状態で、IDデータ110に対応する回数だけ、ローからハイ、ハイからローとするレベル変化をデータ信号SDAに生じさせる。図9の例では、IDデータが”2”である場合に対応して、ローからハイ、ハイからローへと変化するレベル変化が時刻T14〜T15と時刻T16〜T17の計2回発生させている。こうして、ホストコンピューター10は、記憶装置20にリセットを要求するとともに、レベル変化の回数の形式でIDデータ110を記憶装置20に送出する。

【0067】

また、第2の実施形態に係る通信システムの記憶装置側には、上述したようにデータ信号のレベル変化の回数として送出されたIDデータに対応する処理を行うため、第1の実施形態のリセット処理ユニット27に替えて、図10に示したリセット処理ユニット27’が設けられる。リセット処理ユニット27’は、リセット要求判定部270と、リセット実行部271と、パルス数カウンター272と、IDデータ送出部273とを有している。なお、リセット要求判定部270、リセット実行部271については第1の実施形態と同様である。

【0068】

パルス数カウンター272は、リセット要求がされた後のデータ信号SDAについて、ローからハイ、ハイからローにレベル変化した回数をカウントする。IDデータ送出部273は、パルス数カウンター272からカウント値を受け取り、このカウント値をIDデータ110としてIDコンパレーター24に送出する。

【0069】

IDコンパレーター24は、リセット処理ユニット27’から受け取ったIDデータ110を第1レジスター240に格納し、IDデータ110と第2レジスター241に格納した識別データ210とが一致するかの判定を行う。この判定でIDデータ110と識別データ210とが一致した場合に、ホストコンピューター10と記憶装置20との間で行われるデータ通信については、第1の実施形態と同様であるため、詳細な説明は省略する。

【0070】

以上に述べた第2の実施形態によれば、ホストコンピューター10は、記憶装置20にクロック信号SCKおよびデータ信号SDAを用いてリセットを要求した後、IDデータ110に対応する回数のレベル変化をデータ信号SDAに生じさせることにより、記憶装置20のメモリーアレイ21にアクセスすることができる。したがって、第1の実施形態と同様の効果を得ることができる。また、データ信号SDAのレベル変化により、IDデータ110を記憶装置20に送出するようにしているので、クロック信号SCKが安定していない状況においても、IDデータ110を確実に送出することができる。

【0071】

(第3の実施形態)

次に、本発明の第3の実施形態について説明する。上記第2の実施形態では、ホストコンピューター10は記憶装置20に対してリセット要求を行った後、IDデータ110に対応する回数だけデータ信号SDAにレベル変化を生じさせることによって記憶装置20にIDデータ110を送信するようにしたが、第3の実施形態では、リセット要求とともに、IDデータ110に応じた回数分だけデータ信号SDAのレベル変化を生じさせることにより、IDデータ110を送信する。

【0072】

図11に、第3の実施形態で用いられるクロック信号とデータ信号の一例を示す。図示するように、クロック信号SCKが、ローからハイに立ち上がり、ハイの状態を維持する期間(時刻T20〜T25)に、データ信号SDAは、ローからハイに立ち上げてからローに立ち下がるレベル変化(時刻T21〜T22)を生じた場合に、この信号の組み合わせをリセット要求とする。これは第1の実施形態および第2の実施形態と同様である。

【0073】

さらに、ホストコンピューター10は、リセット要求においてクロック信号SCKがハイとなっている期間に、IDデータ110に対応する回数分だけ、ローからハイ、ハイからローとするレベル変化をデータ信号SDAに生じさせる。図11の例では、IDデータ110が”2”である場合に対応して、ローからハイ、ハイからローへのレベル変化を時刻T21〜T22と時刻T23〜T24の計2回発生させている。こうして、ホストコンピューター10は、記憶装置20にリセット要求とともに、IDデータ110をレベル変化の回数として記憶装置20に送出する。なお、本実施形態では、リセット要求で用いられたデータ信号SDAのレベル変化(時刻T21〜T22)も1回分に含めてカウントしているが、リセット要求で用いられたレベル変化はIDデータ110に対応するレベル変化の回数には含めないようにしてもよい。

【0074】

また、第3の実施形態の通信システムの記憶装置側には、第2の実施形態と同様に、リセット要求判定部270と、リセット実行部271と、パルス数カウンター(カウント部)272と、IDデータ送出部273と、を有したリセット処理ユニット27’が設けられる。

【0075】

第3の実施形態においては、パルス数カウンター272が行う処理が第2の実施形態と異なる。すなわち、上述したように、パルス数カウンター272は、リセット要求のためクロック信号SCKがハイとなっている期間に、ローからハイ、ハイからローとするレベル変化の回数をカウントする。この他の構成(リセット要求判定部270、リセット実行部271、IDデータ送出部273)については第2の実施形態と同様である。

【0076】

次に、通信システム1の動作について説明する。図12は、ホストコンピューター10および記憶装置20によって実行される処理の手順を示したフローチャートである。以下、図11に示した信号波形例および図12のフローチャートに従って説明する。

【0077】

図12の処理が開始されると、ホストコンピューター10は、クロック信号SCKおよびデータ信号SDAにより記憶装置20にリセットを要求する。このため、ホストコンピューター10は、まず、クロック信号SCKのレベルをローからハイに立ち上げ(時刻T20、ステップS30)、クロック信号SCKの立ち上げ後に、IDデータ110に対応する回数だけ、データ信号SDAをローからハイ、さらにハイからローにレベル変化させる(時刻T21〜24、ステップS31)。その後、クロック信号SCKのレベルをハイからローに立ち下げる(時刻T25、ステップS32)。

【0078】

一方、記憶装置20側では、リセット処理ユニット27のリセット要求判定部270が、クロック信号SCKおよびデータ信号SDAを監視しており、クロック信号SCKの立ち上がりを検出すると(時刻T20、ステップS40)、パルス数カウンター272は、データ信号SDAがレベル変化した回数をカウントする(時刻T21〜24、ステップS41)。リセット要求判定部270は、クロック信号SCKの立ち下げを検出すると(時刻T25、ステップS42)、リセット要求判定部270は、ステップS40からS42にて検出した一連のレベル変化が、ホストコンピューター10からのリセット要求であると判定して、記憶装置20をリセットする(ステップS43)。なお、ステップS41のカウントは、ステップS42においてクロック信号SCKの立ち下げを検出するまで行われる。

【0079】

次に、IDデータ送出部273は、パルス数カウンター272のカウント値、すなわちクロック信号SCKがハイを維持する期間にデータ信号SDAに生じたレベル変化の回数をIDデータ110として、IDデータ110をIDコンパレーター24に送出する(ステップS44)。

【0080】

以降の処理のステップS45,S46,S33については、第1の実施形態におけるステップS24,S25,S14と同様である。すなわち、IDコンパレーター24は、第1レジスター240に格納したIDデータ110と、第2レジスター241に格納した識別データ210とを比較して、一致しているか否かを判定する(ステップS45)。IDデータ110と識別データ210とが一致していれば(ステップS45:Yes)、ホストコンピューター10と記憶装置20との間でデータ通信が開始されて、ホストコンピューター10は、読み出し/書き込みコマンド120、処理データ130、ACKデータ140を送出する(ステップS33)。記憶装置20側では、オペレーションコードデコーダー25およびI/Oコントローラー26が、受信した読み出し/書き込みコマンド120、処理データ130、ACKデータ140に応じた処理を行うことにより、ホストコンピューター10からメモリーアレイ21への情報の書き込みや読み出しなどのアクセスを制御する(ステップS46)。そして、記憶装置20のオペレーションコードデコーダー25が、送出されたデータ列100に含まれるACKデータ140を解釈した場合、または、ステップS45の判断において、IDデータ110と識別データ210とが一致しない場合に(ステップS25:No)、図12の処理が終了する。

【0081】

以上に述べた第3の実施形態によれば、ホストコンピューター10は、記憶装置20にリセットを要求するとともに、データ信号SDAのレベルがローからハイ、ハイからローに変化したレベル変化を、IDデータに対応する回数分だけ生じさせることにより、記憶装置20とのデータ通信を行ってメモリーアレイ21にアクセスすることができる。したがって、第1の実施形態および第2の実施形態と同様の効果を得ることができる。また、第1の実施形態や第2の実施形態とは異なり、リセット要求とともにIDデータ110を記憶装置20に伝えるようにしているので、メモリーアレイ21へのアクセスをより早いタイミングで開始することができる。

【0082】

以上、本発明の第1ないし第3の実施形態について説明したが、本発明はこれらの形態に限られることなく、その趣旨並びに特許請求の範囲を逸脱することなく、変更、改良され得ると共に、本発明にはその等価物が含まれることはもちろんである。その趣旨に逸脱しない範囲で様々な態様とすることもできる。以下、変形例について説明する。

【0083】

(変形例1)

上記第1ないし第3の実施形態では、クロック信号SCKをハイにした状態で、データ信号SDAにロー、ハイ、ローとなるレベル変化を、ホストコンピューター10から記憶装置20へのリセット要求としたが、リセット要求に対応させるクロック信号SCKとデータ信号SDAの組み合わせはこれに限られるものではない。すなわち、クロック信号SCKに同期させたデータ信号SDAによるデータ通信において、通常は用いられない信号の組み合わせをリセット要求とすることを、ホストコンピューター10と記憶装置20との間で予め取り決めておけばよい。例えば、図13(a)に示すように、クロック信号SCKをハイから立ち下げてローになっている期間(時刻T30〜T33)に、データ信号SDAがロー、ハイ、ローと変化する2回のレベル変化(時刻T31,T32)を、リセット要求としてもよい。また、図13(b)に示すように、クロック信号SCKをローから立ち上げてハイになっている期間(時刻T40〜T43)に、データ信号SDAがハイ、ロー、ハイと変化する2回のレベル変化(時刻T41,T42)を、リセット要求としてもよい。もっとも、リセット要求においてデータ信号SDAのレベルを変化させる回数は2回に限られることなく、より多くの回数のレベル変化をリセット要求に含めるようにしてもよい。

【0084】

また、クロック信号SCKのレベルを変化させずに、データ信号SDAだけを複数回レベル変化させることにより、リセット要求としてもよい。このようにしても、クロック信号SCKとデータ信号SDAの組み合わせが、クロックに同期させたデータ通信では用いられないものであるので、記憶装置20側において、クロックに同期したデータ通信の信号と混同することなく、リセット要求を正しく認識することができる。もっとも、上記第1ないし第3の実施形態のように、クロック信号SCKをハイまたはローのレベルに変化させた後にそのレベルを維持するようにした場合には、クロック信号SCKのレベル変化も用いてリセット要求が判定されるので、リセット要求の判定をより確実に行うことができる。

【0085】

(変形例2)

上記第2および第3の実施形態では、データ信号SDAはローからハイへのレベル変化と、ハイからローへのレベル変化とを含めて1回としてカウントして、このカウント値をIDデータとしたが、ローからハイにレベル変化した回数とハイからローになったレベル変化の回数を別々にカウントして、両カウント値を合計した値をIDデータとしてもよい。また、一方のレベル変化のみをカウントするようにしてもよい。

【0086】

(変形例3)

上記第1ないし第3の実施形態では、メモリーアレイ200へのアクセスを許可するために用いられる識別データ210を、記憶装置20のメモリーアレイ200自体に記憶する構成としたが、メモリーアレイ200とは別に設けた記憶部に識別データ210を記憶する構成としてもよい。

【0087】

(変形例4)

上記第1ないし第3の実施形態では、インクジェットプリンター用のインクカートリッジにインクカートリッジ情報を格納するための記憶装置20を備えた構成について説明したが、本発明に係る記憶装置および通信システムはこの態様に限られるものではない。本発明は、例えば、レーザープリンターのトナーカートリッジや現像ユニットなど、様々な交換部品に設けられる記憶装置、およびこの記憶装置を含む通信システムに適用することができる。

【符号の説明】

【0088】

1…通信システム、10…ホストコンピューター、20…記憶装置、21…記憶部としてのメモリーアレイ、22…アドレスカウンター、23…メモリーコントローラー、24…IDコンパレーター、25…オペレーションコードデコーダー、26…I/Oコントローラー、27…リセット処理ユニット、30…通信制御部、100…データ列、110…第2識別情報としてのIDデータ、120…読み出し/書き込みコマンド、130…処理データ、210…第1識別情報としての識別データ、270…リセット要求判定部、271…リセット実行部、272…カウント部としてのパルス数カウンター、273…IDデータ送出部、CT…第1端子としてのクロック信号端子、DT…第2端子としてのデータ信号端子、SCK…クロック信号、SDA…データ信号。

【特許請求の範囲】

【請求項1】

クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置であって、

前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする記憶装置。

【請求項2】

請求項1に記載の記憶装置において、

前記リセット実行部は、前記クロック信号が前記所定のレベルに変化した後の前記所定のレベルを維持する期間において、前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させることを特徴とする記憶装置。

【請求項3】

請求項1または2に記載の記憶装置において、

前記記憶部は、第1識別情報を記憶し、

前記通信制御部は、前記第1識別情報と、前記データ信号により入力される第2識別情報とを比較して、前記第1識別情報と前記第2識別情報とが一致する場合に、前記データ通信における前記記憶部へのアクセスを許可することを特徴とする記憶装置。

【請求項4】

請求項3に記載の記憶装置において、

前記データ通信を開始した後、前記データ信号のレベルが変化した回数をカウントするカウント部を備え、

前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【請求項5】

請求項3に記載の記憶装置において、

前記クロック信号が前記所定のレベルを維持する期間において、前記データ信号のレベルが変化した回数をカウントするカウント部を備え、

前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【請求項6】

クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置を備えるカートリッジであって、

前記記憶装置は、

前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とするカートリッジ。

【請求項7】

記憶部を有する記憶装置とホスト装置とがクロック信号線およびデータ信号線を介して接続される通信システムであって、

前記記憶装置は、

前記クロック信号線のクロック信号および前記データ信号線のデータ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする通信システム。

【請求項8】

クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置の制御方法であって、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、リセットを実行するステップと、

前記リセットにより初期化した後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始するステップと、を含むことを特徴とする記憶装置の制御方法。

【請求項1】

クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置であって、

前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする記憶装置。

【請求項2】

請求項1に記載の記憶装置において、

前記リセット実行部は、前記クロック信号が前記所定のレベルに変化した後の前記所定のレベルを維持する期間において、前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させることを特徴とする記憶装置。

【請求項3】

請求項1または2に記載の記憶装置において、

前記記憶部は、第1識別情報を記憶し、

前記通信制御部は、前記第1識別情報と、前記データ信号により入力される第2識別情報とを比較して、前記第1識別情報と前記第2識別情報とが一致する場合に、前記データ通信における前記記憶部へのアクセスを許可することを特徴とする記憶装置。

【請求項4】

請求項3に記載の記憶装置において、

前記データ通信を開始した後、前記データ信号のレベルが変化した回数をカウントするカウント部を備え、

前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【請求項5】

請求項3に記載の記憶装置において、

前記クロック信号が前記所定のレベルを維持する期間において、前記データ信号のレベルが変化した回数をカウントするカウント部を備え、

前記通信制御部は、前記カウント部のカウント値に基づいて前記第2識別情報を取得することを特徴とする記憶装置。

【請求項6】

クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置を備えるカートリッジであって、

前記記憶装置は、

前記クロック信号および前記データ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とするカートリッジ。

【請求項7】

記憶部を有する記憶装置とホスト装置とがクロック信号線およびデータ信号線を介して接続される通信システムであって、

前記記憶装置は、

前記クロック信号線のクロック信号および前記データ信号線のデータ信号によるデータ通信を制御し、リセットにより初期化された後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始する通信制御部と、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、前記通信制御部に前記リセットを実行させるリセット実行部と、を備えることを特徴とする通信システム。

【請求項8】

クロック信号が入力される第1端子と、データ信号が入力される第2端子と、記憶部とを有する記憶装置の制御方法であって、

前記クロック信号が前記所定のレベルを維持する期間において前記データ信号に複数回のレベル変化が生じた場合に、リセットを実行するステップと、

前記リセットにより初期化した後に前記クロック信号に同期させた前記データ信号により前記記憶部にアクセスするデータ通信を開始するステップと、を含むことを特徴とする記憶装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−12114(P2013−12114A)

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願番号】特願2011−145372(P2011−145372)

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]