記憶装置および記憶装置制御方法

【課題】消費電力の低減を図ることが可能な記憶装置を提供する。

【解決手段】初期化時の予備テストとして'0'および'1'の試験データをメモリ2に書き込み、書き込み時点から一定時間経過後のそれぞれのメモリ2の温度を比較した結果を搭載メモリ電力保持回路8に搭載メモリ電力特性80として保持し、以降、メモリ2にデータを書き込む際に、データ解析回路7にて書き込みデータの'0'と'1'との個数を抽出して、保持した搭載メモリ電力特性80に基づき書き込みデータをそのまま書き込むかまたは'0'と'1'とを反転した反転データとして書き込むかを判別し、判別した結果をデータ選択信号70として出力し、書き込みデータセレクタG1にて、書き込みデータの'0'と'1'とを反転させた反転データを生成した後、出力されたデータ選択信号70に基づき書き込みデータそのままかまたは前記反転データかのいずれかを選択してメモリ2に書き込む。

【解決手段】初期化時の予備テストとして'0'および'1'の試験データをメモリ2に書き込み、書き込み時点から一定時間経過後のそれぞれのメモリ2の温度を比較した結果を搭載メモリ電力保持回路8に搭載メモリ電力特性80として保持し、以降、メモリ2にデータを書き込む際に、データ解析回路7にて書き込みデータの'0'と'1'との個数を抽出して、保持した搭載メモリ電力特性80に基づき書き込みデータをそのまま書き込むかまたは'0'と'1'とを反転した反転データとして書き込むかを判別し、判別した結果をデータ選択信号70として出力し、書き込みデータセレクタG1にて、書き込みデータの'0'と'1'とを反転させた反転データを生成した後、出力されたデータ選択信号70に基づき書き込みデータそのままかまたは前記反転データかのいずれかを選択してメモリ2に書き込む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記憶装置および記憶装置制御方法に関し、特に、ランダムアクセスが可能なメモリを搭載した記憶装置として低消費電力化が可能な記憶装置および記憶装置制御方法に関する。

【背景技術】

【0002】

従来の記憶装置の構成を、図6を参照しながら説明する。図6は、従来の記憶装置のブロック構成を示すブロック構成図であり、特許文献1の特開2010−176577号公報「省電力記憶装置とこれを備えた情報処理装置、記憶装置の省電力制御方法およびプログラム」等にも類似の構成が示されている。

【0003】

図6において、RAM制御信号生成回路1Aは、上位装置からのリクエストを受け付け、メモリアクセスコマンド10Aとメモリアクセスアドレス11Aとをメモリ2Aに対して送出する。メモリ2Aは、RAM制御信号生成回路1Aから送出されたメモリアクセスコマンド10Aに従い、RAM制御信号生成回路1Aからのメモリアクセスアドレス11Aで示されたアドレスからの読み書きを行う。

【0004】

すなわち、メモリアクセスコマンド10Aが読み出しリクエストであった場合は、メモリアクセスアドレス11Aで示されたアドレスから(メモリデータ+チェックビット)20A(図6では、(メモリデータ+CB)20Aと略記する)を読み出して、ECC回路5Aに送出する。ECC回路5Aは、メモリ2Aより読み出された(メモリデータ+チェックビット)20Aを受け取って、受け取ったチェックビットによるメモリデータのチェックを行い、メモリデータに異常があった場合には受け取ったメモリデータを訂正し、読み出しデータ50Aとして読み出しデータ制御回路6Aに送出する。読み出しデータ制御回路6Aは、ECC回路5Aからの読み出しデータ50Aを受け取って、読み出しリクエストに対する応答を示すリプライデータとして上位装置へ送出する。

【0005】

一方、メモリアクセスコマンド10Aが書き込みリクエストであった場合は、書き込みデータ制御回路3AとECG回路4Aとから送出された(書き込みデータ30A+書き込みチェックビット40A(図6では、書き込みCB 40Aと略記する))をメモリアクセスアドレス11Aで示されたアドレスに書き込む。ここで、書き込みデータ制御回路3Aは、上位装置からの書き込みデータを受け付け、メモリ2AとECG回路4Aとに書き込みデータ30Aとして送出している。

【0006】

ECG回路4Aは、書き込みデータ制御回路3Aからの書き込みデータ30Aを受け取り、書き込みデータ30Aに対するチェックビット(CB:Check Bit)を生成して、書き込み用の書き込みチェックビット40Aとしてメモリ2Aに送出する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−176577号公報(第10−13頁)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来の記憶装置は、記憶装置の低消費電力化に関して、次のような課題がある。

【0009】

第1の課題は、一般に、記憶装置に搭載するメモリは多種多様(マルチベンダー化)であるため、当該メモリの消費電力の特性が判らないことにある。つまり、搭載したメモリが'0'/'1'のいずれのデータを保持した時の消費電力が多いのか/少ないのかを判別することができなかったため、消費電力が多い方のデータを数多く書き込んでいる可能性があり、余分な電力を消費している恐れがあるということにある。

【0010】

第2の課題は、たとえ、書き込みデータ/読み出しデータの'0'と'1'とを反転させたデータを自在に生成して書き込んだり読み出したりすることができたとしても、'0'/'1'いづれのデータを保持した際に消費電力が少なくなるかが分らないということである。

【0011】

第3の課題は、たとえ、何らかの手段によって書き込みデータの'0'と'1'とを反転させることができたとしても、データを反転した際に、搭載したメモリの消費電力特性によって、データを反転したという履歴が残すことができないということである。

【0012】

(本発明の目的)

本発明は、かかる課題に鑑みてなされたものであり、消費電力の低減を図ることが可能な記憶装置および記憶装置制御方法を提供することを、その目的としている。

【課題を解決するための手段】

【0013】

前述の課題を解決するため、本発明による記憶装置および記憶装置制御方法は、主に、次のような特徴的な構成を採用している。

【0014】

(1)本発明による記憶装置は、ランダムアクセスが可能なメモリを搭載した記憶装置であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持する搭載メモリ電力特性保持手段と、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、前記搭載メモリ電力特性保持手段に保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として出力するデータ解析手段と、前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、前記データ解析手段から出力された前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込む書き込みデータ選択手段と、を少なくとも備えていることを特徴とする。

【0015】

(2)本発明による記憶装置制御方法は、ランダムアクセスが可能なメモリを搭載した記憶装置の動作を制御する記憶装置制御方法であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持しておき、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として書き込みデータ選択手段に対して出力し、該書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、出力されてきた前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込むことを特徴とする。

【発明の効果】

【0016】

本発明の記憶装置および記憶装置制御方法によれば、以下のような効果を奏することができる。

【0017】

第1の効果は、記憶装置の初期化時に、該記憶装置に搭載したメモリが'0'のデータを保持する場合と'1'のデータを保持する場合とのいずれが、消費電力がより少なくなるのかを予備テストによって、メモリの消費電力特性として事前に把握することができることにある。

【0018】

第2の効果は、前記予備テストにより事前に把握したメモリの消費電力特性を基にして、初期化段階以降において、書き込みデータとその反転データとを比較して、記憶装置のメモリにデータを保持する際の消費電力が少なくなる方のデータを常にメモリに書き込む動作を行うことによって、記憶装置の消費電力を削減することができることである。

【0019】

第3の効果は、記憶装置の以降の初期化を実施するに当たって、前記予備テストにより事前に把握したメモリの消費電力特性を基にして、書き込みデータとその反転データとを比較して、記憶装置のメモリにデータを保持する際の消費電力が少ない方のデータを常にメモリに書き込む動作を行うことによって、記憶装置の初期化段階においても消費電力を削減することができることである。

【図面の簡単な説明】

【0020】

【図1】本発明による記憶装置のブロック構成の一例を示すブロック構成図である。

【図2】図1の記憶装置のさらに詳細なブロック構成を示すブロック構成図である。

【図3】図2の記憶装置の動作の一例を説明するためのフローチャートである。

【図4】図2の記憶装置における図3のフローチャートに引き続く動作の一例を説明するためのフローチャートである。

【図5】本発明による記憶装置の図2とは異なるブロック構成例を示すブロック構成図である。

【図6】従来の記憶装置のブロック構成を示すブロック構成図である。

【発明を実施するための形態】

【0021】

以下、本発明による記憶装置および記憶装置制御方法の好適な実施形態について添付図を参照して説明する。

【0022】

(本発明の特徴)

本発明の実施形態の説明に先立って、本発明の特徴についてその概要をまず説明する。本発明は、ランダムアクセスが可能なメモリが搭載された記憶装置において、'0'と'1'とのいずれのデータを保持した時の消費電力が少ないかを記憶装置の初期化段階の予備テストにおいてあらかじめ判定し、消費電力の少ない方のデータを当該記憶装置のメモリの消費電力特性を示す特性値としてあらかじめ書き込んでおき、以降のメモリへのデータ書き込み時において、メモリの消費電力特性を示す特性値を基にして、書き込みデータの'0'/'1'の個数を比較することによって、通常の書き込みデータと該書き込みデータの'0'と'1'とを反転した反転データとのうち、いずれのデータが消費電力が低くなるかを判別し、消費電力が少ないと判別した方のデータを、常にメモリに書き込む仕組みを備えることによって、記憶装置の低消費電力化を実現することを主要な特徴としている。

【0023】

より具体的には、記憶装置の初期化段階であらかじめALL'0'とALL'1'との双方の試験データを書き込む予備テストを実施し、それぞれの試験データをメモリに保持した時の記憶装置の温度(すなわち消費電力)を測定することによって、ALL'0'/ALL'1'の試験データのうちいずれの試験データを保持した際の記憶装置の消費電力が少なくなるかを判別し、メモリの電力特性として当該予備テスト結果を記憶する搭載メモリ電力特性保持手段言い換えると低消費電力データ判別手段を備えている。しかる後、(初期化処理も含めて)以降の処理で、或るアドレスにデータを書き込む際に、書き込みデータの'0'と'1'との双方の個数を求めて、前記搭載メモリ電力特性保持手段にて記憶したメモリの電力特性に基づいて、通常の書き込みデータとその'0'と'1'とを反転させた反転データとのうち、いずれのデータが、消費電力が少なくなるかを判別するデータ解析手段を備え、該データ解析手段の判別結果に基づいて、通常の書き込みデータとその反転データとのうち、消費電力が少ないと判別した方のデータを選択してメモリに書き込むための書き込みデータ選択手段をさらに備えていることを主要な特徴としている。

【0024】

さらに、以降の当該アドレスからの読み出し動作に備えて、データの'0'と'1'とを反転してメモリに書き込んだか否かの履歴情報をメモリアドレスごとに記憶する履歴記憶手段としてデータ反転情報保持手段を備えている。そして、メモリの或るアドレスからデータ読み出しを行う際は、該データ反転情報保持手段にて記憶されている履歴情報を参照することによって、当該アドレスのデータを反転して記憶したか否かを確認し、確認した結果に基づいて、メモリから読み出した読み出しデータかまたは該読み出しデータの'0'と'1'とを反転した反転データかのいずれかを選択して上位装置に送信するための読み出しデータ選択手段をさらに備えていることも主要な特徴としている。

【0025】

かくのごとき仕組みを備えることによって、記憶装置の消費電力の低減を図ることが可能になる。

【0026】

(本発明の実施形態の構成例)

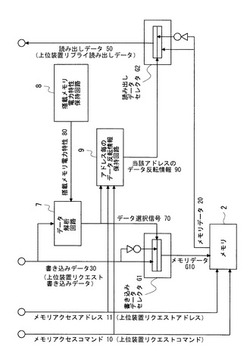

次に、本発明の実施形態の構成例として、本発明による記憶装置のブロック構成の一例について、図1および図2を用いて詳細に説明する。図1は、本発明による記憶装置のブロック構成の一例を示すブロック構成図であり、図2は、図1の記憶装置のさらに詳細なブロック構成を示すブロック構成図である。ここで、図2は、図1の記憶装置の各機能ブロックに対して、図6に示した従来の記憶装置の場合と同様、上位装置とのインタフェース回路であるRAM制御信号生成回路1、書き込みデータ制御回路3、読み出しデータ制御回路6を追加するとともに、記憶装置内部に誤り訂正用の機能を実施するためのECG回路4およびECC回路5を追加している場合を示している。以下の説明においては、図2に示した記憶装置について詳細に説明することにする。

【0027】

図2に示す記憶装置は、ランダムアクセスが可能なメモリを搭載した記憶装置であり、図6に示した従来の記憶装置の場合と同様、RAM制御信号生成回路1、メモリ2、書き込みデータ制御回路3、ECG回路4、ECC回路5、読み出しデータ制御回路6の各機能ブロックを備えている他、さらに、本発明に特有の機能ブロックとして、データ解析回路7、搭載メモリ電力特性保持回路8、アドレス毎のデータ反転情報保持回路9、書き込みデータセレクタG1、読み出しデータセレクタG2を少なくとも含んで構成している。

【0028】

まず、RAM制御信号生成回路1は、上位装置から、記憶装置に対するコマンド内容を示す上位装置リクエストコマンドおよびアクセスすべきアドレスを示す上位装置リクエストアドレスを受け付けると、それぞれ、メモリアクセスコマンド10およびメモリアクセスアドレス11として、メモリ2と、該メモリ2のアドレスごとに対応付けて、データを反転して記憶したか否かを示すデータ反転情報を記憶するための記憶領域を備えているアドレス毎のデータ反転情報保持回路9と、に対して送出する。

【0029】

また、メモリ2は、上位装置からの上位装置リクエストコマンドとしてRAM制御信号生成回路1から送出されてきたメモリアクセスコマンド10および上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されてきたメモリアクセスアドレス11と、書き込みデータセレクタG1から送出されてきた(メモリデータ+チェックビット)G10(図2では、(メモリデータ+CB)G10と略記する)とを入力信号として入力し、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが書き込みリクエストであった場合には、書き込みデータセレクタG1から送出されてきた(メモリデータ+チェックビット)G10をメモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているメモリ2の当該アドレスに書き込む。

【0030】

一方、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが読み出しリクエストであった場合には、メモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているメモリ2の当該アドレスに保持されているデータを読み出して、(メモリデータ+チェックビット)20(図2では、(メモリデータ+CB)20と略記する)として、読み出しデータセレクタG2に対して送出する。

【0031】

また、書き込みデータ制御回路3は、上位装置から、書き込むべきデータを示す上位装置リクエスト書き込みデータを受け付けると、書き込みデータ30として、誤り訂正用のチェックビットを生成するECG回路4、書き込みデータセレクタG1およびデータ解析回路7に対して送出する。

【0032】

また、ECG回路4は、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30を入力信号として入力し、該書き込みデータ30の誤り訂正用のチェックビットとして書き込みチェックビット40(図2では、書き込みCB40と略記する)を生成して、書き込みデータセレクタG1とデータ解析回路7とに対して送出する。

【0033】

また、ECC回路5は、読み出しデータセレクタG2から送出されてくる(ECC入力データ+チェックビット)G20を入力信号として入力し、チェックビットに基づいてECC入力データの誤りを訂正して、読み出しデータ50として、読み出しデータ制御回路6に対して送出する。

【0034】

また、読み出しデータ制御回路6は、ECC回路5から読み出しデータ50が送出されてくると、該読み出しデータ50を、上位装置リプライ読み出しデータとして、上位装置に対して送信する。

【0035】

また、データ解析回路7は、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30とECG回路4から送出されてくる書き込みチェックビット40と搭載メモリ電力特性保持回路8から送出されてくる搭載メモリ電力特性80とを入力信号として入力とし、それぞれの入力信号を基にして、データ選択信号70を生成し、書き込みデータセレクタG1とアドレス毎のデータ反転情報保持回路9とに対して送出する。

【0036】

ここで、データ解析回路7が生成するデータ選択信号70の生成例を、表1に示している。

【0037】

【表1】

なお、記憶装置の初期化時の予備テストにおいてALL'0'とALL'1'との双方の試験データの書き込みテストをあらかじめ行い、メモリデータ+チェックビットとして保持した時点からあらかじめ定めた一定時間が経過した後の温度(すなわち、消費電力)を測定し、温度がより低くなっている(すなわち、消費電力がより少なくなっている)方の試験データを示す情報を搭載メモリ電力特性80として搭載メモリ電力特性保持回路8にあらかじめ記憶している。

【0038】

つまり、'0'を保持した場合の方が、消費電力が少ないと判別した場合には、搭載メモリ電力特性保持回路8には、搭載メモリ電力特性80を示すメモリ電力特性ビットとして'0'を記憶し、逆に、'1'を保持した場合の方が、消費電力が少ないと判別した場合には、搭載メモリ電力特性保持回路8には、搭載メモリ電力特性80を示すメモリ電力特性ビットとして'1'を記憶している。また、データ解析回路7は、上位装置から上位装置リクエスト書き込みデータとして送信されてくる書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40の各ビットの内容を解析して、'0'の個数と'1'の個数とのいずれが多いかを判別している。

【0039】

したがって、表1に示すように、搭載メモリ電力特性保持回路8から送出されてくる搭載メモリ電力特性80として、'0'を保持した場合の方が、消費電力が少なくなる場合には、データ解析回路7における書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータの確認結果として、'0'の個数が多ければ、データ選択信号70として'0'を生成して、書き込みデータ30すなわち上位装置リクエスト書き込みデータをそのままメモリ2に書き込むことを指示し、逆に、'1'の個数が多ければ、データ選択信号70として'1'を生成して、書き込みデータ30すなわち上位装置リクエスト書き込みデータを反転してメモリ2に書き込むことを指示する。

【0040】

また、搭載メモリ電力特性保持回路8から送出されてくる搭載メモリ電力特性80として、'1'を保持した場合の方が、消費電力が少なくなる場合には、データ解析回路7における書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータの確認結果として、'0'の個数が多ければ、データ選択信号70として'1'を生成して、書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータを反転してメモリ2に書き込むことを指示し、逆に、'1'の個数が多ければ、データ選択信号70として'0'を生成して、書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータをそのままメモリ2に書き込むことを指示する。

【0041】

また、搭載メモリ電力特性保持回路8は、前述したように、記憶装置の初期化段階の予備テストにおいて判別した消費電力が少なくなる方の試験データを示す情報すなわち'0'または'1'のいずれかのメモリ電力特性ビットを搭載メモリ電力特性80として記憶装置がリセットされるまで保持して、該搭載メモリ電力特性80をデータ解析回路7に対して送出する。

【0042】

また、メモリ2のアドレスごとに対応して記憶領域が設けられているアドレス毎のデータ反転情報保持回路9は、上位装置からの上位装置リクエストコマンドとしてRAM制御信号生成回路1から送出されてくるメモリアクセスコマンド10および上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されてくるメモリアクセスアドレス11とデータ解析回路7から送出されてくるデータ選択信号70とを入力信号として入力し、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが"書き込み"を要求している場合には、メモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているアドレスに該当するアドレス毎のデータ反転情報保持回路9内の記憶領域に、メモリ2の当該アドレスにデータを書き込む際に使用したデータ選択信号70の信号値('0':そのまま書き込み、'1':反転書き込み)を記憶し、メモリアクセスコマンド10すなわち上位装置リクエストコマンドとして当該アドレスへの次の書き込みリクエストが送信されてくるまで、その値を保持する。

【0043】

一方、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが"読み出し"を要求している場合は、メモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているアドレスに該当するアドレス毎のデータ反転情報保持回路9内の記憶領域に記憶されていたデータ選択信号70の信号値('0':そのまま書き込んでいた場合、'1':反転書き込みしていた場合)を読み出して、メモリ2の当該アドレスから読み出した(メモリデータ+チェックビット)20に関する当該アドレスのデータ反転情報90として、読み出しデータセレクタG2に対して送出する。

【0044】

また、書き込みデータセレクタG1は、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30とECG回路4から送出されてくる書き込みチェックビット40とデータ解析回路7から送出されてくるデータ選択信号70とを入力信号として入力し、書き込みデータ30すなわち上位装置リクエスト書き込みデータ+チェックビット40を反転した反転データを作成するとともに、データ解析回路7から送出されてきたデータ選択信号70の値に基づいて、書き込みデータ30すなわち上位装置リクエスト書き込みデータ+チェックビット40またはその反転データのいずれかを選択して、メモリ2に書き込むべき(メモリデータ+チェックビット)G10(図2では、(メモリデータ+CB)G10と略記する)として、メモリ2に対して送出する。

【0045】

また、読み出しデータセレクタG2は、メモリ2から送出されてくる(メモリデータ+チェックビット)20とアドレス毎のデータ反転情報保持回路9から送出されてくる当該アドレスのデータ反転情報90とを入力信号として入力し、(メモリデータ+チェックビット)20の'0'と'1'とを反転させたメモリ反転データを作成するとともに、アドレス毎のデータ反転情報保持回路9から送出されてきた当該アドレスのデータ反転情報90の値に基づいて、(メモリデータ+チェックビット)20またはその(メモリデータ+チェックビット)20の'0'と'1'とを反転させたメモリ反転データのいずれかを選択して、(ECC入力データ+チェックビット)G20(図2では、(ECC入力データ+CB)G20と略記する)として、ECC回路5に対して送出する。

【0046】

以上のような記憶装置の構成とすることによって、記憶装置の初期化段階の予備テストにおいて、当該記憶装置に搭載したメモリが、'0'/'1'のいずれのデータを保持する方が、消費電力が少なくなるのかを判定して、判定結果を搭載メモリ電力特性80としてあらかじめ搭載メモリ電力特性保持回路8に記憶するとともに、消費電力が少ないと判定した値を用いてメモリ2の記憶内容の初期化を実施し、以降の実際のデータの書き込み動作時には、書き込み用の通常データの'0'の個数と'1'の個数とを比較し、通常データと該通常データの'0'と'1'とを反転させた反転データとのうち消費電力が少なくなる方のデータをメモリ2に書き込むように制御することを可能にしている。而して、記憶装置の消費電力の低減化を図ることができる。

【0047】

なお、図1および図2に示すブロック構成においては、データの書き込み対象の記憶メディアとして、通常のランダムアクセス用のメモリ2を用いる場合を示しているが、場合によっては、ハードウェアマクロ等からなるデータ記憶部として構成しても良い。

【0048】

(本発明の実施形態の動作の説明)

次に、本発明の一実施形態として図2に示した記憶装置の動作について、その一例を、図3および図4のフローチャートを用いて説明する。図3は、図2の記憶装置の動作の一例を説明するためのフローチャートであり、初期化段階の動作を、メモリ2の消費電力特性をあらかじめ調査するために実施する予備テストの動作を中心にして示している。また、図4は、図2の記憶装置における図3のフローチャートに引き続く動作の一例を説明するためのフローチャートであり、初期化終了後の通常の運用段階で、図3の予備テスト結果を利用して、記憶装置のメモリ2への読み書き動作を制御して、消費電力の低減を図っている動作例を示している。

【0049】

図3のフローチャートにおいて、まず、記憶装置の初期化が開始されると(ステップS1)、記憶装置の初期設定が実施される(ステップS2)。しかる後、初期化時の動作の一つとして、メモリ2における消費電力が少なくなるデータの保持方法をあらかじめ調査するための予備テストを実施する。まず、装置データ反転ビットの初期値すなわち搭載メモリ電力特性保持回路8に記憶する搭載メモリ電力特性80を示すメモリ電力特性ビットの初期値として'0'を設定した後(ステップS3)、記憶装置のメモリ2の全アドレスに対してALL'0'のデータを書き込む(ステップS4)。しかる後、あらかじめ定めた一定時間が経過した時点で、記憶装置の温度(すなわち、消費電力)を測定して結果Aとして保存する(ステップS5)。

【0050】

次いで、記憶装置のメモリ2の全アドレスに対してALL'1'のデータを書き込む(ステップS6)。しかる後、あらかじめ定めた前記一定時間が経過した時点で、記憶装置の温度(すなわち、消費電力)を測定して結果Bとして保存する(ステップS7)。

【0051】

ALL'0'のデータを保持している際の記憶装置の温度(消費電力)の測定結果である結果AとALL'1'のデータを保持している際の記憶装置の温度(消費電力)の測定結果である結果Bとを比較して(ステップS8)、結果Aの方が結果Bよりも温度が高い場合には(ステップS8のYes)、メモリ2に'1'のデータを保持する場合の方が、消費電力が少なくなるものと判定して、装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶する搭載メモリ電力特性80を示すメモリ電力特性ビットとして、初期値の'0'から'1'に書き替えて、以降、記憶装置のリセットが実施されるまで、搭載メモリ電力特性80としてこの値を保持する(ステップS9)。この段階では、メモリ2の全アドレスが、消費電力が低減されるALL'1'のデータを保持した状態に設定されているので、その状態を継続して、ステップS11に移行する。

【0052】

逆に、結果Aの方が結果Bよりも温度が高くなかった場合には(ステップS8のNo)、メモリ2に'0'のデータを保持する場合の方が、消費電力が少なくなるものと判定して、装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶する搭載メモリ電力特性80を示すメモリ電力特性ビットとして、初期値の'0'をそのまま継続して、以降、記憶装置のリセットが実施されるまで、搭載メモリ電力特性80としてこの値を保持する(ステップS10)。しかる後、メモリ2の全アドレスが、消費電力が多いALL'1'のデータを保持した状態に設定されているので、消費電力を低減するために、全アドレスに再度ALL'0'のデータを書き込む(ステップS11)。

【0053】

ステップS12に移行すると、消費電力が少なくなるデータの保持方法を調べるための予備テストを終了して、記憶装置の残りの初期化処理を継続して実施し(ステップS12)、すべての初期化処理が終了すると、記憶装置の初期設定を終了する(ステップS13)。

【0054】

次に、図3の初期化時の予備テストを実施した後の通常の運用段階における動作について、図4のフローチャートを用いて詳細に説明する。

【0055】

図4のフローチャートにおいて、まず、RAM制御信号生成回路1が上位装置からの上位装置リクエストコマンドとして送信されてくるメモリアクセスコマンド10の受付を開始して(ステップ21)、上位装置からの上位装置リクエストコマンドすなわちメモリアクセスコマンド10が送信されてくると、受け付けた当該メモリアクセスコマンド10がメモリ2への書き込み命令であるか否かを確認する(ステップS22)。

【0056】

受け付けた当該メモリアクセスコマンド10がメモリ2への書き込み命令であった場合は(ステップS22のYes)、データ解析回路7において、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30とECG回路4から送出されてくる書き込みチェックビット40とを合わせたデータについて、'0'のデータと'1'のデータとのいずれの個数が多いかを確認する(ステップS23)。

【0057】

(書き込みデータ30+書き込みチェックビット40)について、'0'のデータの個数が多いと判定された場合は(ステップS24のYes)、次に、'0'のデータと'1'のデータのうち消費電力が少ない方のデータ値を示す装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶している搭載メモリ電力特性80を示すメモリ電力特性ビットが'0'であったか否かを確認する(ステップS25)。

【0058】

装置データ反転ビットすなわちメモリ電力特性ビットが'0'であった場合には(ステップS25のYes)、消費電力が少ない'0'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)を、そのまま、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS26)。

【0059】

一方、装置データ反転ビットすなわちメモリ電力特性ビットが'0'ではなかった場合には(ステップS25のNo)、消費電力が少ない'1'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データを、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS28)。

【0060】

また、ステップS24において、(書き込みデータ30+書き込みチェックビット40)について、'0'のデータの個数が多くないと判定された場合は(ステップS24のNo)、'1'の個数が多い場合であり、次に、'0'のデータと'1'のデータのうち消費電力が少ない方のデータ値を示す装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶している搭載メモリ電力特性80を示すメモリ電力特性ビットが'1'であったか否かを確認する(ステップS27)。

【0061】

装置データ反転ビットすなわちメモリ電力特性ビットが'1'であった場合には(ステップS27のYes)、消費電力が少ない'1'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)を、そのまま、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS26)。

【0062】

一方、装置データ反転ビットすなわちメモリ電力特性ビットが'1'ではなかった場合には(ステップS27のNo)、消費電力が少ない'0'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データを、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS28)。

【0063】

また、ステップS22において、受け付けた当該メモリアクセスコマンド10がメモリ2への書き込み命令ではなかった場合は(ステップS22のNo)、受け付けた当該メモリアクセスコマンド10は、メモリ2からのデータの読み出し命令であるものと判別する(ステップS29)。次に、メモリ2のアドレスごとに対応して記憶領域が設けられているアドレス毎のデータ反転情報保持回路9から、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに対応する記憶領域に記憶されている当該アドレスのデータ反転情報90(すなわち、メモリ2の当該アドレスへのデータ書き込み時に、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだか、または、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データとして書き込んだかを示す情報)を読み出して、当該アドレスのデータ反転情報90すなわち当該アドレスのデータ反転情報ビットが'0'であるか否かを確認する(ステップS30)。

【0064】

当該アドレスのデータ反転情報90すなわち当該アドレスのデータ反転情報ビットが'0'であった場合は(ステップS30のYes)、メモリ2への当該アドレスへのデータ書き込み時に、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだ場合であり、読み出しデータセレクタG2においては、上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスから読み出した(メモリデータ+チェックビット)20を、そのまま、(ECC入力データ+チェックビット)G20として、ECC回路5に対して送出する(ステップS31)。しかる後、ECC回路5においては、送出されてきた(ECC入力データ+チェックビット)G20をチェックして、誤りがあれば訂正を行った後、読み出しデータ50として、読み出しデータ制御回路6に送出し、読み出しデータ制御回路6は、上位装置リプライ読み出しデータとして上位装置に対して送信する。

【0065】

一方、当該アドレスのデータ反転情報90すなわち当該アドレスのデータ反転情報ビットが'0'ではなかった場合は(ステップS30のNo)、メモリ2への当該アドレスへのデータ書き込み時に、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データとして書き込んだ場合であり、読み出しデータセレクタG2においては、上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスから読み出した(メモリデータ+チェックビット)20の'0'と'1'とを反転させて元のデータに戻してから、(ECC入力データ+チェックビット)G20として、ECC回路5に対して送出する(ステップS32)。しかる後、ECC回路5においては、送出されてきた(ECC入力データ+チェックビット)G20をチェックして、誤りがあれば訂正を行った後、読み出しデータ50として、読み出しデータ制御回路6に送出し、読み出しデータ制御回路6は、上位装置リプライ読み出しデータとして上位装置に対して送信する。

【0066】

以上のように動作することにより、図2に示した記憶装置においては、図3のフローチャートにて説明したように、記憶装置の初期化段階の予備テストにおいて、当該記憶装置に搭載したメモリが、'0'/'1'のいずれのデータを保持する方が、消費電力が少なくなるのかを判定して、その判定結果を搭載メモリ電力特性80としてあらかじめ搭載メモリ電力特性保持回路8に記憶するとともに、消費電力が少ないと判定した値を用いてメモリ2の記憶内容の初期化を実施し、以降の実際のデータの書き込み動作時には、図4のフローチャートにて説明したように、書き込み用の通常データの'0'、'1'の個数を比較し、通常データと該通常データの'0'と'1'とを反転した反転データとのうち消費電力が少なくなる方のデータをメモリ2に書き込むように制御することを可能にしている。而して、記憶装置の消費電力の低減化を図ることができる。

【0067】

(実施形態の効果の説明)

以上に詳細に説明したように、本実施形態においては、以下に記載するような効果を奏することができる。

【0068】

第1の効果は、記憶装置の初期化時に、該記憶装置に搭載したメモリ2が'0'のデータを保持する場合と'1'のデータを保持する場合とのいずれが、消費電力がより少なくなるのかを予備テストによって、メモリ2の消費電力特性を示す搭載メモリ電力特性80として事前に把握することができることにある。

【0069】

第2の効果は、前記予備テストにより事前に把握したメモリ2の消費電力特性を基にして、初期化段階以降において、書き込みデータとその反転データとを比較して、記憶装置のメモリ2にデータを保持する際の消費電力が少なくなる方のデータを常にメモリ2に書き込む動作を行うことによって、記憶装置の消費電力を削減することができることである。

【0070】

第3の効果は、記憶装置の以降の初期化を実施するに当たって、前記予備テストにより事前に把握したメモリ2の消費電力特性を基にして、書き込みデータとその反転データとを比較して、記憶装置のメモリ2にデータを保持する際の消費電力が少ない方のデータを常にメモリに書き込む動作を行うことによって、記憶装置の初期化段階においても消費電力を削減することができることである。

【0071】

(本発明の他の実施形態)

次に、本発明の他の実施形態について説明する。記憶装置の基本的構成は、前記の図2の場合と同じであるが、アドレス毎のデータ反転情報保持回路9の設置については、さらに工夫して、異なる構成とすることも可能である。その構成例について図5に示している。図5は、本発明による記憶装置の図2とは異なるブロック構成例を示すブロック構成図である。

【0072】

つまり、図5の記憶装置の場合、アドレス毎のデータ反転情報保持回路9を設置しない形式とし、書き込みリクエストの際には、(メモリデータ+チェックビット)G20とともに、データ解析回路7から送出されているデータ選択信号70(すなわち、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだか、または、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転させた反転データとして書き込んだかを示す信号)も、同時に、RAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む構成としている。

【0073】

かかる構成を用いる場合、メモリ2からのデータ読み出しの際は、(メモリデータ+チェックビット)20とともに、当該アドレスに同時に書き込まれていたデータ選択信号70(すなわち、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだか、または、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転させた反転データとして書き込んだかを示す信号)も、データ選択信号25としてメモリ2から読み出して、読み出した該データ選択信号25を読み出しデータセレクタG2に入力信号として入力することによって、読み出しデータセレクタG2において、メモリ2から読み出した(メモリデータ+チェックビット)20をそのまま出力するか、あるいは、(メモリデータ+チェックビット)20の'0'と'1'とを反転して出力するかのいずれかを選択することを可能にしている。

【0074】

かくのごときデータの読み書き制御方式を採用することによって、アドレス毎のデータ反転情報保持回路9を備えることに伴う複雑な回路構成を用いる必要がなく、ハードウェア量の削減が可能になる。

【0075】

なお、図5に示す記憶装置においては、図2の場合とは異なり、ECC回路5と読み出しデータセレクタG2との配置を入れ替えて、メモリ2からの読み出しデータすなわち(メモリデータ+チェックビット)20をまずECC回路5に入力して、誤り訂正を行った後、読み出しデータセレクタG2において、ECC回路5からの読み出しデータをそのまま送出するかまたは反転してから送出するかのいずれかを選択して、読み出しデータ50として読み出しデータ制御回路6に対して送出するように構成している場合を示している。

【0076】

以上、本発明の好適な実施形態の構成を説明した。しかし、かかる実施形態は、本発明の単なる例示に過ぎず、何ら本発明を限定するものではないことに留意されたい。本発明の要旨を逸脱することなく、特定用途に応じて種々の変形変更が可能であることが、当業者には容易に理解できよう。

【符号の説明】

【0077】

1 RAM制御信号生成回路

1A RAM制御信号生成回路

2 メモリ

2A メモリ

3 書き込みデータ制御回路

3A 書き込みデータ制御回路

4 ECG回路

4A ECG回路

5 ECC回路

5A ECC回路

6 読み出しデータ制御回路

6A 読み出しデータ制御回路

7 データ解析回路

8 搭載メモリ電力特性保持回路

9 アドレス毎のデータ反転情報保持回路

10 メモリアクセスコマンド(上位装置リクエストコマンド)

10A メモリアクセスコマンド

11 メモリアクセスアドレス(上位装置リクエストアドレス)

11A メモリアクセスアドレス

20 メモリデータ+チェックビット(メモリデータ+CB)

20A メモリデータ+チェックビット(メモリデータ+CB)

30 書き込みデータ(上位装置リクエスト書き込みデータ)

30A 書き込みデータ

40 書き込みチェックビット(書き込みCB)

40A 書き込みチェックビット(書き込みCB)

50 読み出しデータ(上位装置リプライ読み出しデータ)

50A 読み出しデータ

70 データ選択信号

80 搭載メモリ電力特性

90 データ反転情報

G1 書き込みデータセレクタ

G10 メモリデータ+チェックビット(メモリデータ+CB)

G2 読み出しデータセレクタ

G20 ECC入力データ+チェックビット(ECC入力データ+CB)

【技術分野】

【0001】

本発明は、記憶装置および記憶装置制御方法に関し、特に、ランダムアクセスが可能なメモリを搭載した記憶装置として低消費電力化が可能な記憶装置および記憶装置制御方法に関する。

【背景技術】

【0002】

従来の記憶装置の構成を、図6を参照しながら説明する。図6は、従来の記憶装置のブロック構成を示すブロック構成図であり、特許文献1の特開2010−176577号公報「省電力記憶装置とこれを備えた情報処理装置、記憶装置の省電力制御方法およびプログラム」等にも類似の構成が示されている。

【0003】

図6において、RAM制御信号生成回路1Aは、上位装置からのリクエストを受け付け、メモリアクセスコマンド10Aとメモリアクセスアドレス11Aとをメモリ2Aに対して送出する。メモリ2Aは、RAM制御信号生成回路1Aから送出されたメモリアクセスコマンド10Aに従い、RAM制御信号生成回路1Aからのメモリアクセスアドレス11Aで示されたアドレスからの読み書きを行う。

【0004】

すなわち、メモリアクセスコマンド10Aが読み出しリクエストであった場合は、メモリアクセスアドレス11Aで示されたアドレスから(メモリデータ+チェックビット)20A(図6では、(メモリデータ+CB)20Aと略記する)を読み出して、ECC回路5Aに送出する。ECC回路5Aは、メモリ2Aより読み出された(メモリデータ+チェックビット)20Aを受け取って、受け取ったチェックビットによるメモリデータのチェックを行い、メモリデータに異常があった場合には受け取ったメモリデータを訂正し、読み出しデータ50Aとして読み出しデータ制御回路6Aに送出する。読み出しデータ制御回路6Aは、ECC回路5Aからの読み出しデータ50Aを受け取って、読み出しリクエストに対する応答を示すリプライデータとして上位装置へ送出する。

【0005】

一方、メモリアクセスコマンド10Aが書き込みリクエストであった場合は、書き込みデータ制御回路3AとECG回路4Aとから送出された(書き込みデータ30A+書き込みチェックビット40A(図6では、書き込みCB 40Aと略記する))をメモリアクセスアドレス11Aで示されたアドレスに書き込む。ここで、書き込みデータ制御回路3Aは、上位装置からの書き込みデータを受け付け、メモリ2AとECG回路4Aとに書き込みデータ30Aとして送出している。

【0006】

ECG回路4Aは、書き込みデータ制御回路3Aからの書き込みデータ30Aを受け取り、書き込みデータ30Aに対するチェックビット(CB:Check Bit)を生成して、書き込み用の書き込みチェックビット40Aとしてメモリ2Aに送出する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−176577号公報(第10−13頁)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来の記憶装置は、記憶装置の低消費電力化に関して、次のような課題がある。

【0009】

第1の課題は、一般に、記憶装置に搭載するメモリは多種多様(マルチベンダー化)であるため、当該メモリの消費電力の特性が判らないことにある。つまり、搭載したメモリが'0'/'1'のいずれのデータを保持した時の消費電力が多いのか/少ないのかを判別することができなかったため、消費電力が多い方のデータを数多く書き込んでいる可能性があり、余分な電力を消費している恐れがあるということにある。

【0010】

第2の課題は、たとえ、書き込みデータ/読み出しデータの'0'と'1'とを反転させたデータを自在に生成して書き込んだり読み出したりすることができたとしても、'0'/'1'いづれのデータを保持した際に消費電力が少なくなるかが分らないということである。

【0011】

第3の課題は、たとえ、何らかの手段によって書き込みデータの'0'と'1'とを反転させることができたとしても、データを反転した際に、搭載したメモリの消費電力特性によって、データを反転したという履歴が残すことができないということである。

【0012】

(本発明の目的)

本発明は、かかる課題に鑑みてなされたものであり、消費電力の低減を図ることが可能な記憶装置および記憶装置制御方法を提供することを、その目的としている。

【課題を解決するための手段】

【0013】

前述の課題を解決するため、本発明による記憶装置および記憶装置制御方法は、主に、次のような特徴的な構成を採用している。

【0014】

(1)本発明による記憶装置は、ランダムアクセスが可能なメモリを搭載した記憶装置であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持する搭載メモリ電力特性保持手段と、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、前記搭載メモリ電力特性保持手段に保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として出力するデータ解析手段と、前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、前記データ解析手段から出力された前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込む書き込みデータ選択手段と、を少なくとも備えていることを特徴とする。

【0015】

(2)本発明による記憶装置制御方法は、ランダムアクセスが可能なメモリを搭載した記憶装置の動作を制御する記憶装置制御方法であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持しておき、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として書き込みデータ選択手段に対して出力し、該書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、出力されてきた前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込むことを特徴とする。

【発明の効果】

【0016】

本発明の記憶装置および記憶装置制御方法によれば、以下のような効果を奏することができる。

【0017】

第1の効果は、記憶装置の初期化時に、該記憶装置に搭載したメモリが'0'のデータを保持する場合と'1'のデータを保持する場合とのいずれが、消費電力がより少なくなるのかを予備テストによって、メモリの消費電力特性として事前に把握することができることにある。

【0018】

第2の効果は、前記予備テストにより事前に把握したメモリの消費電力特性を基にして、初期化段階以降において、書き込みデータとその反転データとを比較して、記憶装置のメモリにデータを保持する際の消費電力が少なくなる方のデータを常にメモリに書き込む動作を行うことによって、記憶装置の消費電力を削減することができることである。

【0019】

第3の効果は、記憶装置の以降の初期化を実施するに当たって、前記予備テストにより事前に把握したメモリの消費電力特性を基にして、書き込みデータとその反転データとを比較して、記憶装置のメモリにデータを保持する際の消費電力が少ない方のデータを常にメモリに書き込む動作を行うことによって、記憶装置の初期化段階においても消費電力を削減することができることである。

【図面の簡単な説明】

【0020】

【図1】本発明による記憶装置のブロック構成の一例を示すブロック構成図である。

【図2】図1の記憶装置のさらに詳細なブロック構成を示すブロック構成図である。

【図3】図2の記憶装置の動作の一例を説明するためのフローチャートである。

【図4】図2の記憶装置における図3のフローチャートに引き続く動作の一例を説明するためのフローチャートである。

【図5】本発明による記憶装置の図2とは異なるブロック構成例を示すブロック構成図である。

【図6】従来の記憶装置のブロック構成を示すブロック構成図である。

【発明を実施するための形態】

【0021】

以下、本発明による記憶装置および記憶装置制御方法の好適な実施形態について添付図を参照して説明する。

【0022】

(本発明の特徴)

本発明の実施形態の説明に先立って、本発明の特徴についてその概要をまず説明する。本発明は、ランダムアクセスが可能なメモリが搭載された記憶装置において、'0'と'1'とのいずれのデータを保持した時の消費電力が少ないかを記憶装置の初期化段階の予備テストにおいてあらかじめ判定し、消費電力の少ない方のデータを当該記憶装置のメモリの消費電力特性を示す特性値としてあらかじめ書き込んでおき、以降のメモリへのデータ書き込み時において、メモリの消費電力特性を示す特性値を基にして、書き込みデータの'0'/'1'の個数を比較することによって、通常の書き込みデータと該書き込みデータの'0'と'1'とを反転した反転データとのうち、いずれのデータが消費電力が低くなるかを判別し、消費電力が少ないと判別した方のデータを、常にメモリに書き込む仕組みを備えることによって、記憶装置の低消費電力化を実現することを主要な特徴としている。

【0023】

より具体的には、記憶装置の初期化段階であらかじめALL'0'とALL'1'との双方の試験データを書き込む予備テストを実施し、それぞれの試験データをメモリに保持した時の記憶装置の温度(すなわち消費電力)を測定することによって、ALL'0'/ALL'1'の試験データのうちいずれの試験データを保持した際の記憶装置の消費電力が少なくなるかを判別し、メモリの電力特性として当該予備テスト結果を記憶する搭載メモリ電力特性保持手段言い換えると低消費電力データ判別手段を備えている。しかる後、(初期化処理も含めて)以降の処理で、或るアドレスにデータを書き込む際に、書き込みデータの'0'と'1'との双方の個数を求めて、前記搭載メモリ電力特性保持手段にて記憶したメモリの電力特性に基づいて、通常の書き込みデータとその'0'と'1'とを反転させた反転データとのうち、いずれのデータが、消費電力が少なくなるかを判別するデータ解析手段を備え、該データ解析手段の判別結果に基づいて、通常の書き込みデータとその反転データとのうち、消費電力が少ないと判別した方のデータを選択してメモリに書き込むための書き込みデータ選択手段をさらに備えていることを主要な特徴としている。

【0024】

さらに、以降の当該アドレスからの読み出し動作に備えて、データの'0'と'1'とを反転してメモリに書き込んだか否かの履歴情報をメモリアドレスごとに記憶する履歴記憶手段としてデータ反転情報保持手段を備えている。そして、メモリの或るアドレスからデータ読み出しを行う際は、該データ反転情報保持手段にて記憶されている履歴情報を参照することによって、当該アドレスのデータを反転して記憶したか否かを確認し、確認した結果に基づいて、メモリから読み出した読み出しデータかまたは該読み出しデータの'0'と'1'とを反転した反転データかのいずれかを選択して上位装置に送信するための読み出しデータ選択手段をさらに備えていることも主要な特徴としている。

【0025】

かくのごとき仕組みを備えることによって、記憶装置の消費電力の低減を図ることが可能になる。

【0026】

(本発明の実施形態の構成例)

次に、本発明の実施形態の構成例として、本発明による記憶装置のブロック構成の一例について、図1および図2を用いて詳細に説明する。図1は、本発明による記憶装置のブロック構成の一例を示すブロック構成図であり、図2は、図1の記憶装置のさらに詳細なブロック構成を示すブロック構成図である。ここで、図2は、図1の記憶装置の各機能ブロックに対して、図6に示した従来の記憶装置の場合と同様、上位装置とのインタフェース回路であるRAM制御信号生成回路1、書き込みデータ制御回路3、読み出しデータ制御回路6を追加するとともに、記憶装置内部に誤り訂正用の機能を実施するためのECG回路4およびECC回路5を追加している場合を示している。以下の説明においては、図2に示した記憶装置について詳細に説明することにする。

【0027】

図2に示す記憶装置は、ランダムアクセスが可能なメモリを搭載した記憶装置であり、図6に示した従来の記憶装置の場合と同様、RAM制御信号生成回路1、メモリ2、書き込みデータ制御回路3、ECG回路4、ECC回路5、読み出しデータ制御回路6の各機能ブロックを備えている他、さらに、本発明に特有の機能ブロックとして、データ解析回路7、搭載メモリ電力特性保持回路8、アドレス毎のデータ反転情報保持回路9、書き込みデータセレクタG1、読み出しデータセレクタG2を少なくとも含んで構成している。

【0028】

まず、RAM制御信号生成回路1は、上位装置から、記憶装置に対するコマンド内容を示す上位装置リクエストコマンドおよびアクセスすべきアドレスを示す上位装置リクエストアドレスを受け付けると、それぞれ、メモリアクセスコマンド10およびメモリアクセスアドレス11として、メモリ2と、該メモリ2のアドレスごとに対応付けて、データを反転して記憶したか否かを示すデータ反転情報を記憶するための記憶領域を備えているアドレス毎のデータ反転情報保持回路9と、に対して送出する。

【0029】

また、メモリ2は、上位装置からの上位装置リクエストコマンドとしてRAM制御信号生成回路1から送出されてきたメモリアクセスコマンド10および上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されてきたメモリアクセスアドレス11と、書き込みデータセレクタG1から送出されてきた(メモリデータ+チェックビット)G10(図2では、(メモリデータ+CB)G10と略記する)とを入力信号として入力し、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが書き込みリクエストであった場合には、書き込みデータセレクタG1から送出されてきた(メモリデータ+チェックビット)G10をメモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているメモリ2の当該アドレスに書き込む。

【0030】

一方、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが読み出しリクエストであった場合には、メモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているメモリ2の当該アドレスに保持されているデータを読み出して、(メモリデータ+チェックビット)20(図2では、(メモリデータ+CB)20と略記する)として、読み出しデータセレクタG2に対して送出する。

【0031】

また、書き込みデータ制御回路3は、上位装置から、書き込むべきデータを示す上位装置リクエスト書き込みデータを受け付けると、書き込みデータ30として、誤り訂正用のチェックビットを生成するECG回路4、書き込みデータセレクタG1およびデータ解析回路7に対して送出する。

【0032】

また、ECG回路4は、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30を入力信号として入力し、該書き込みデータ30の誤り訂正用のチェックビットとして書き込みチェックビット40(図2では、書き込みCB40と略記する)を生成して、書き込みデータセレクタG1とデータ解析回路7とに対して送出する。

【0033】

また、ECC回路5は、読み出しデータセレクタG2から送出されてくる(ECC入力データ+チェックビット)G20を入力信号として入力し、チェックビットに基づいてECC入力データの誤りを訂正して、読み出しデータ50として、読み出しデータ制御回路6に対して送出する。

【0034】

また、読み出しデータ制御回路6は、ECC回路5から読み出しデータ50が送出されてくると、該読み出しデータ50を、上位装置リプライ読み出しデータとして、上位装置に対して送信する。

【0035】

また、データ解析回路7は、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30とECG回路4から送出されてくる書き込みチェックビット40と搭載メモリ電力特性保持回路8から送出されてくる搭載メモリ電力特性80とを入力信号として入力とし、それぞれの入力信号を基にして、データ選択信号70を生成し、書き込みデータセレクタG1とアドレス毎のデータ反転情報保持回路9とに対して送出する。

【0036】

ここで、データ解析回路7が生成するデータ選択信号70の生成例を、表1に示している。

【0037】

【表1】

なお、記憶装置の初期化時の予備テストにおいてALL'0'とALL'1'との双方の試験データの書き込みテストをあらかじめ行い、メモリデータ+チェックビットとして保持した時点からあらかじめ定めた一定時間が経過した後の温度(すなわち、消費電力)を測定し、温度がより低くなっている(すなわち、消費電力がより少なくなっている)方の試験データを示す情報を搭載メモリ電力特性80として搭載メモリ電力特性保持回路8にあらかじめ記憶している。

【0038】

つまり、'0'を保持した場合の方が、消費電力が少ないと判別した場合には、搭載メモリ電力特性保持回路8には、搭載メモリ電力特性80を示すメモリ電力特性ビットとして'0'を記憶し、逆に、'1'を保持した場合の方が、消費電力が少ないと判別した場合には、搭載メモリ電力特性保持回路8には、搭載メモリ電力特性80を示すメモリ電力特性ビットとして'1'を記憶している。また、データ解析回路7は、上位装置から上位装置リクエスト書き込みデータとして送信されてくる書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40の各ビットの内容を解析して、'0'の個数と'1'の個数とのいずれが多いかを判別している。

【0039】

したがって、表1に示すように、搭載メモリ電力特性保持回路8から送出されてくる搭載メモリ電力特性80として、'0'を保持した場合の方が、消費電力が少なくなる場合には、データ解析回路7における書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータの確認結果として、'0'の個数が多ければ、データ選択信号70として'0'を生成して、書き込みデータ30すなわち上位装置リクエスト書き込みデータをそのままメモリ2に書き込むことを指示し、逆に、'1'の個数が多ければ、データ選択信号70として'1'を生成して、書き込みデータ30すなわち上位装置リクエスト書き込みデータを反転してメモリ2に書き込むことを指示する。

【0040】

また、搭載メモリ電力特性保持回路8から送出されてくる搭載メモリ電力特性80として、'1'を保持した場合の方が、消費電力が少なくなる場合には、データ解析回路7における書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータの確認結果として、'0'の個数が多ければ、データ選択信号70として'1'を生成して、書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータを反転してメモリ2に書き込むことを指示し、逆に、'1'の個数が多ければ、データ選択信号70として'0'を生成して、書き込みデータ30とECG回路から送信されてくる書き込みチェックビット40すなわち上位装置リクエスト書き込みデータをそのままメモリ2に書き込むことを指示する。

【0041】

また、搭載メモリ電力特性保持回路8は、前述したように、記憶装置の初期化段階の予備テストにおいて判別した消費電力が少なくなる方の試験データを示す情報すなわち'0'または'1'のいずれかのメモリ電力特性ビットを搭載メモリ電力特性80として記憶装置がリセットされるまで保持して、該搭載メモリ電力特性80をデータ解析回路7に対して送出する。

【0042】

また、メモリ2のアドレスごとに対応して記憶領域が設けられているアドレス毎のデータ反転情報保持回路9は、上位装置からの上位装置リクエストコマンドとしてRAM制御信号生成回路1から送出されてくるメモリアクセスコマンド10および上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されてくるメモリアクセスアドレス11とデータ解析回路7から送出されてくるデータ選択信号70とを入力信号として入力し、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが"書き込み"を要求している場合には、メモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているアドレスに該当するアドレス毎のデータ反転情報保持回路9内の記憶領域に、メモリ2の当該アドレスにデータを書き込む際に使用したデータ選択信号70の信号値('0':そのまま書き込み、'1':反転書き込み)を記憶し、メモリアクセスコマンド10すなわち上位装置リクエストコマンドとして当該アドレスへの次の書き込みリクエストが送信されてくるまで、その値を保持する。

【0043】

一方、メモリアクセスコマンド10すなわち上位装置リクエストコマンドが"読み出し"を要求している場合は、メモリアクセスアドレス11すなわち上位装置リクエストアドレスが指定しているアドレスに該当するアドレス毎のデータ反転情報保持回路9内の記憶領域に記憶されていたデータ選択信号70の信号値('0':そのまま書き込んでいた場合、'1':反転書き込みしていた場合)を読み出して、メモリ2の当該アドレスから読み出した(メモリデータ+チェックビット)20に関する当該アドレスのデータ反転情報90として、読み出しデータセレクタG2に対して送出する。

【0044】

また、書き込みデータセレクタG1は、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30とECG回路4から送出されてくる書き込みチェックビット40とデータ解析回路7から送出されてくるデータ選択信号70とを入力信号として入力し、書き込みデータ30すなわち上位装置リクエスト書き込みデータ+チェックビット40を反転した反転データを作成するとともに、データ解析回路7から送出されてきたデータ選択信号70の値に基づいて、書き込みデータ30すなわち上位装置リクエスト書き込みデータ+チェックビット40またはその反転データのいずれかを選択して、メモリ2に書き込むべき(メモリデータ+チェックビット)G10(図2では、(メモリデータ+CB)G10と略記する)として、メモリ2に対して送出する。

【0045】

また、読み出しデータセレクタG2は、メモリ2から送出されてくる(メモリデータ+チェックビット)20とアドレス毎のデータ反転情報保持回路9から送出されてくる当該アドレスのデータ反転情報90とを入力信号として入力し、(メモリデータ+チェックビット)20の'0'と'1'とを反転させたメモリ反転データを作成するとともに、アドレス毎のデータ反転情報保持回路9から送出されてきた当該アドレスのデータ反転情報90の値に基づいて、(メモリデータ+チェックビット)20またはその(メモリデータ+チェックビット)20の'0'と'1'とを反転させたメモリ反転データのいずれかを選択して、(ECC入力データ+チェックビット)G20(図2では、(ECC入力データ+CB)G20と略記する)として、ECC回路5に対して送出する。

【0046】

以上のような記憶装置の構成とすることによって、記憶装置の初期化段階の予備テストにおいて、当該記憶装置に搭載したメモリが、'0'/'1'のいずれのデータを保持する方が、消費電力が少なくなるのかを判定して、判定結果を搭載メモリ電力特性80としてあらかじめ搭載メモリ電力特性保持回路8に記憶するとともに、消費電力が少ないと判定した値を用いてメモリ2の記憶内容の初期化を実施し、以降の実際のデータの書き込み動作時には、書き込み用の通常データの'0'の個数と'1'の個数とを比較し、通常データと該通常データの'0'と'1'とを反転させた反転データとのうち消費電力が少なくなる方のデータをメモリ2に書き込むように制御することを可能にしている。而して、記憶装置の消費電力の低減化を図ることができる。

【0047】

なお、図1および図2に示すブロック構成においては、データの書き込み対象の記憶メディアとして、通常のランダムアクセス用のメモリ2を用いる場合を示しているが、場合によっては、ハードウェアマクロ等からなるデータ記憶部として構成しても良い。

【0048】

(本発明の実施形態の動作の説明)

次に、本発明の一実施形態として図2に示した記憶装置の動作について、その一例を、図3および図4のフローチャートを用いて説明する。図3は、図2の記憶装置の動作の一例を説明するためのフローチャートであり、初期化段階の動作を、メモリ2の消費電力特性をあらかじめ調査するために実施する予備テストの動作を中心にして示している。また、図4は、図2の記憶装置における図3のフローチャートに引き続く動作の一例を説明するためのフローチャートであり、初期化終了後の通常の運用段階で、図3の予備テスト結果を利用して、記憶装置のメモリ2への読み書き動作を制御して、消費電力の低減を図っている動作例を示している。

【0049】

図3のフローチャートにおいて、まず、記憶装置の初期化が開始されると(ステップS1)、記憶装置の初期設定が実施される(ステップS2)。しかる後、初期化時の動作の一つとして、メモリ2における消費電力が少なくなるデータの保持方法をあらかじめ調査するための予備テストを実施する。まず、装置データ反転ビットの初期値すなわち搭載メモリ電力特性保持回路8に記憶する搭載メモリ電力特性80を示すメモリ電力特性ビットの初期値として'0'を設定した後(ステップS3)、記憶装置のメモリ2の全アドレスに対してALL'0'のデータを書き込む(ステップS4)。しかる後、あらかじめ定めた一定時間が経過した時点で、記憶装置の温度(すなわち、消費電力)を測定して結果Aとして保存する(ステップS5)。

【0050】

次いで、記憶装置のメモリ2の全アドレスに対してALL'1'のデータを書き込む(ステップS6)。しかる後、あらかじめ定めた前記一定時間が経過した時点で、記憶装置の温度(すなわち、消費電力)を測定して結果Bとして保存する(ステップS7)。

【0051】

ALL'0'のデータを保持している際の記憶装置の温度(消費電力)の測定結果である結果AとALL'1'のデータを保持している際の記憶装置の温度(消費電力)の測定結果である結果Bとを比較して(ステップS8)、結果Aの方が結果Bよりも温度が高い場合には(ステップS8のYes)、メモリ2に'1'のデータを保持する場合の方が、消費電力が少なくなるものと判定して、装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶する搭載メモリ電力特性80を示すメモリ電力特性ビットとして、初期値の'0'から'1'に書き替えて、以降、記憶装置のリセットが実施されるまで、搭載メモリ電力特性80としてこの値を保持する(ステップS9)。この段階では、メモリ2の全アドレスが、消費電力が低減されるALL'1'のデータを保持した状態に設定されているので、その状態を継続して、ステップS11に移行する。

【0052】

逆に、結果Aの方が結果Bよりも温度が高くなかった場合には(ステップS8のNo)、メモリ2に'0'のデータを保持する場合の方が、消費電力が少なくなるものと判定して、装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶する搭載メモリ電力特性80を示すメモリ電力特性ビットとして、初期値の'0'をそのまま継続して、以降、記憶装置のリセットが実施されるまで、搭載メモリ電力特性80としてこの値を保持する(ステップS10)。しかる後、メモリ2の全アドレスが、消費電力が多いALL'1'のデータを保持した状態に設定されているので、消費電力を低減するために、全アドレスに再度ALL'0'のデータを書き込む(ステップS11)。

【0053】

ステップS12に移行すると、消費電力が少なくなるデータの保持方法を調べるための予備テストを終了して、記憶装置の残りの初期化処理を継続して実施し(ステップS12)、すべての初期化処理が終了すると、記憶装置の初期設定を終了する(ステップS13)。

【0054】

次に、図3の初期化時の予備テストを実施した後の通常の運用段階における動作について、図4のフローチャートを用いて詳細に説明する。

【0055】

図4のフローチャートにおいて、まず、RAM制御信号生成回路1が上位装置からの上位装置リクエストコマンドとして送信されてくるメモリアクセスコマンド10の受付を開始して(ステップ21)、上位装置からの上位装置リクエストコマンドすなわちメモリアクセスコマンド10が送信されてくると、受け付けた当該メモリアクセスコマンド10がメモリ2への書き込み命令であるか否かを確認する(ステップS22)。

【0056】

受け付けた当該メモリアクセスコマンド10がメモリ2への書き込み命令であった場合は(ステップS22のYes)、データ解析回路7において、上位装置からの上位装置リクエスト書き込みデータとして書き込みデータ制御回路3から送出されてくる書き込みデータ30とECG回路4から送出されてくる書き込みチェックビット40とを合わせたデータについて、'0'のデータと'1'のデータとのいずれの個数が多いかを確認する(ステップS23)。

【0057】

(書き込みデータ30+書き込みチェックビット40)について、'0'のデータの個数が多いと判定された場合は(ステップS24のYes)、次に、'0'のデータと'1'のデータのうち消費電力が少ない方のデータ値を示す装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶している搭載メモリ電力特性80を示すメモリ電力特性ビットが'0'であったか否かを確認する(ステップS25)。

【0058】

装置データ反転ビットすなわちメモリ電力特性ビットが'0'であった場合には(ステップS25のYes)、消費電力が少ない'0'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)を、そのまま、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS26)。

【0059】

一方、装置データ反転ビットすなわちメモリ電力特性ビットが'0'ではなかった場合には(ステップS25のNo)、消費電力が少ない'1'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データを、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS28)。

【0060】

また、ステップS24において、(書き込みデータ30+書き込みチェックビット40)について、'0'のデータの個数が多くないと判定された場合は(ステップS24のNo)、'1'の個数が多い場合であり、次に、'0'のデータと'1'のデータのうち消費電力が少ない方のデータ値を示す装置データ反転ビットすなわち搭載メモリ電力特性保持回路8に記憶している搭載メモリ電力特性80を示すメモリ電力特性ビットが'1'であったか否かを確認する(ステップS27)。

【0061】

装置データ反転ビットすなわちメモリ電力特性ビットが'1'であった場合には(ステップS27のYes)、消費電力が少ない'1'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)を、そのまま、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS26)。

【0062】

一方、装置データ反転ビットすなわちメモリ電力特性ビットが'1'ではなかった場合には(ステップS27のNo)、消費電力が少ない'0'のデータの個数が多い状態でメモリ2に書き込むことが望ましいので、書き込みデータセレクタG1において、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データを、(メモリデータ+チェックビット)G10として出力して、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む(ステップS28)。

【0063】

また、ステップS22において、受け付けた当該メモリアクセスコマンド10がメモリ2への書き込み命令ではなかった場合は(ステップS22のNo)、受け付けた当該メモリアクセスコマンド10は、メモリ2からのデータの読み出し命令であるものと判別する(ステップS29)。次に、メモリ2のアドレスごとに対応して記憶領域が設けられているアドレス毎のデータ反転情報保持回路9から、上位装置からの上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに対応する記憶領域に記憶されている当該アドレスのデータ反転情報90(すなわち、メモリ2の当該アドレスへのデータ書き込み時に、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだか、または、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データとして書き込んだかを示す情報)を読み出して、当該アドレスのデータ反転情報90すなわち当該アドレスのデータ反転情報ビットが'0'であるか否かを確認する(ステップS30)。

【0064】

当該アドレスのデータ反転情報90すなわち当該アドレスのデータ反転情報ビットが'0'であった場合は(ステップS30のYes)、メモリ2への当該アドレスへのデータ書き込み時に、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだ場合であり、読み出しデータセレクタG2においては、上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスから読み出した(メモリデータ+チェックビット)20を、そのまま、(ECC入力データ+チェックビット)G20として、ECC回路5に対して送出する(ステップS31)。しかる後、ECC回路5においては、送出されてきた(ECC入力データ+チェックビット)G20をチェックして、誤りがあれば訂正を行った後、読み出しデータ50として、読み出しデータ制御回路6に送出し、読み出しデータ制御回路6は、上位装置リプライ読み出しデータとして上位装置に対して送信する。

【0065】

一方、当該アドレスのデータ反転情報90すなわち当該アドレスのデータ反転情報ビットが'0'ではなかった場合は(ステップS30のNo)、メモリ2への当該アドレスへのデータ書き込み時に、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転した反転データとして書き込んだ場合であり、読み出しデータセレクタG2においては、上位装置リクエストアドレスとしてRAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスから読み出した(メモリデータ+チェックビット)20の'0'と'1'とを反転させて元のデータに戻してから、(ECC入力データ+チェックビット)G20として、ECC回路5に対して送出する(ステップS32)。しかる後、ECC回路5においては、送出されてきた(ECC入力データ+チェックビット)G20をチェックして、誤りがあれば訂正を行った後、読み出しデータ50として、読み出しデータ制御回路6に送出し、読み出しデータ制御回路6は、上位装置リプライ読み出しデータとして上位装置に対して送信する。

【0066】

以上のように動作することにより、図2に示した記憶装置においては、図3のフローチャートにて説明したように、記憶装置の初期化段階の予備テストにおいて、当該記憶装置に搭載したメモリが、'0'/'1'のいずれのデータを保持する方が、消費電力が少なくなるのかを判定して、その判定結果を搭載メモリ電力特性80としてあらかじめ搭載メモリ電力特性保持回路8に記憶するとともに、消費電力が少ないと判定した値を用いてメモリ2の記憶内容の初期化を実施し、以降の実際のデータの書き込み動作時には、図4のフローチャートにて説明したように、書き込み用の通常データの'0'、'1'の個数を比較し、通常データと該通常データの'0'と'1'とを反転した反転データとのうち消費電力が少なくなる方のデータをメモリ2に書き込むように制御することを可能にしている。而して、記憶装置の消費電力の低減化を図ることができる。

【0067】

(実施形態の効果の説明)

以上に詳細に説明したように、本実施形態においては、以下に記載するような効果を奏することができる。

【0068】

第1の効果は、記憶装置の初期化時に、該記憶装置に搭載したメモリ2が'0'のデータを保持する場合と'1'のデータを保持する場合とのいずれが、消費電力がより少なくなるのかを予備テストによって、メモリ2の消費電力特性を示す搭載メモリ電力特性80として事前に把握することができることにある。

【0069】

第2の効果は、前記予備テストにより事前に把握したメモリ2の消費電力特性を基にして、初期化段階以降において、書き込みデータとその反転データとを比較して、記憶装置のメモリ2にデータを保持する際の消費電力が少なくなる方のデータを常にメモリ2に書き込む動作を行うことによって、記憶装置の消費電力を削減することができることである。

【0070】

第3の効果は、記憶装置の以降の初期化を実施するに当たって、前記予備テストにより事前に把握したメモリ2の消費電力特性を基にして、書き込みデータとその反転データとを比較して、記憶装置のメモリ2にデータを保持する際の消費電力が少ない方のデータを常にメモリに書き込む動作を行うことによって、記憶装置の初期化段階においても消費電力を削減することができることである。

【0071】

(本発明の他の実施形態)

次に、本発明の他の実施形態について説明する。記憶装置の基本的構成は、前記の図2の場合と同じであるが、アドレス毎のデータ反転情報保持回路9の設置については、さらに工夫して、異なる構成とすることも可能である。その構成例について図5に示している。図5は、本発明による記憶装置の図2とは異なるブロック構成例を示すブロック構成図である。

【0072】

つまり、図5の記憶装置の場合、アドレス毎のデータ反転情報保持回路9を設置しない形式とし、書き込みリクエストの際には、(メモリデータ+チェックビット)G20とともに、データ解析回路7から送出されているデータ選択信号70(すなわち、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだか、または、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転させた反転データとして書き込んだかを示す信号)も、同時に、RAM制御信号生成回路1から送出されているメモリアクセスアドレス11が示すメモリ2のアドレスに書き込む構成としている。

【0073】

かかる構成を用いる場合、メモリ2からのデータ読み出しの際は、(メモリデータ+チェックビット)20とともに、当該アドレスに同時に書き込まれていたデータ選択信号70(すなわち、(書き込みデータ30+書き込みチェックビット40)をそのまま書き込んだか、または、(書き込みデータ30+書き込みチェックビット40)の'0'と'1'とを反転させた反転データとして書き込んだかを示す信号)も、データ選択信号25としてメモリ2から読み出して、読み出した該データ選択信号25を読み出しデータセレクタG2に入力信号として入力することによって、読み出しデータセレクタG2において、メモリ2から読み出した(メモリデータ+チェックビット)20をそのまま出力するか、あるいは、(メモリデータ+チェックビット)20の'0'と'1'とを反転して出力するかのいずれかを選択することを可能にしている。

【0074】

かくのごときデータの読み書き制御方式を採用することによって、アドレス毎のデータ反転情報保持回路9を備えることに伴う複雑な回路構成を用いる必要がなく、ハードウェア量の削減が可能になる。

【0075】

なお、図5に示す記憶装置においては、図2の場合とは異なり、ECC回路5と読み出しデータセレクタG2との配置を入れ替えて、メモリ2からの読み出しデータすなわち(メモリデータ+チェックビット)20をまずECC回路5に入力して、誤り訂正を行った後、読み出しデータセレクタG2において、ECC回路5からの読み出しデータをそのまま送出するかまたは反転してから送出するかのいずれかを選択して、読み出しデータ50として読み出しデータ制御回路6に対して送出するように構成している場合を示している。

【0076】

以上、本発明の好適な実施形態の構成を説明した。しかし、かかる実施形態は、本発明の単なる例示に過ぎず、何ら本発明を限定するものではないことに留意されたい。本発明の要旨を逸脱することなく、特定用途に応じて種々の変形変更が可能であることが、当業者には容易に理解できよう。

【符号の説明】

【0077】

1 RAM制御信号生成回路

1A RAM制御信号生成回路

2 メモリ

2A メモリ

3 書き込みデータ制御回路

3A 書き込みデータ制御回路

4 ECG回路

4A ECG回路

5 ECC回路

5A ECC回路

6 読み出しデータ制御回路

6A 読み出しデータ制御回路

7 データ解析回路

8 搭載メモリ電力特性保持回路

9 アドレス毎のデータ反転情報保持回路

10 メモリアクセスコマンド(上位装置リクエストコマンド)

10A メモリアクセスコマンド

11 メモリアクセスアドレス(上位装置リクエストアドレス)

11A メモリアクセスアドレス

20 メモリデータ+チェックビット(メモリデータ+CB)

20A メモリデータ+チェックビット(メモリデータ+CB)

30 書き込みデータ(上位装置リクエスト書き込みデータ)

30A 書き込みデータ

40 書き込みチェックビット(書き込みCB)

40A 書き込みチェックビット(書き込みCB)

50 読み出しデータ(上位装置リプライ読み出しデータ)

50A 読み出しデータ

70 データ選択信号

80 搭載メモリ電力特性

90 データ反転情報

G1 書き込みデータセレクタ

G10 メモリデータ+チェックビット(メモリデータ+CB)

G2 読み出しデータセレクタ

G20 ECC入力データ+チェックビット(ECC入力データ+CB)

【特許請求の範囲】

【請求項1】

ランダムアクセスが可能なメモリを搭載した記憶装置であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持する搭載メモリ電力特性保持手段と、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、前記搭載メモリ電力特性保持手段に保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として出力するデータ解析手段と、前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、前記データ解析手段から出力された前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込む書き込みデータ選択手段と、を少なくとも備えていることを特徴とする記憶装置。

【請求項2】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込んだかという情報を、データ反転情報として前記メモリのアドレスごとに対応する記憶領域に保持するデータ反転情報保持手段を備え、前記予備テスト以降において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、前記データ反転情報保持手段に前記メモリのアドレスごとに対応して保持している前記データ反転情報に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力する読み出しデータ選択手段、を少なくとも備えていることを特徴とする請求項1に記載の記憶装置。

【請求項3】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込む際に、前記データ解析手段が出力する前記データ選択信号も、同時に、前記メモリの当該アドレスに書き込み、しかる後において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、当該アドレスに書き込まれていた前記データ選択信号も同時に読み出し、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、当該アドレスから同時に読み出した前記データ選択信号に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力する読み出しデータ選択手段、を少なくとも備えていることを特徴とする請求項1に記載の記憶装置。

【請求項4】

前記データ解析手段において前記書き込みデータの'0'の個数と'1'の個数とを抽出する際に、当該書き込みデータに関する誤り訂正用として付加されるチェックビットを含めて'0'の個数と'1'の個数とを抽出して、前記データ選択信号を生成するとともに、前記書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成する際に、前記書き込みデータに付加された前記チェックビットも含めて反転させたデータを生成し、前記メモリに書き込む際に、前記書き込みデータに付加された前記チェックビットも含めてそのままかまたは反転させたデータかのいずれかを選択して、書き込むことを特徴とする請求項1ないし3のいずれかに記載の記憶装置。

【請求項5】

ランダムアクセスが可能なメモリを搭載した記憶装置の動作を制御する記憶装置制御方法であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持しておき、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として書き込みデータ選択手段に対して出力し、該書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、出力されてきた前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込むことを特徴とする記憶装置制御方法。

【請求項6】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込んだかという情報を、データ反転情報として前記メモリのアドレスごとに対応して設けた記憶領域に保持し、前記予備テスト以降において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、前記メモリのアドレスごとに対応して保持している前記データ反転情報に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力することを特徴とする請求項5に記載の記憶装置制御方法。

【請求項7】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込む際に、前記データ選択信号も、同時に、前記メモリの当該アドレスに書き込み、しかる後において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、当該アドレスに書き込まれていた前記データ選択信号も同時に読み出し、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、当該アドレスから同時に読み出した前記データ選択信号に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力することを特徴とする請求項5に記載の記憶装置制御方法。

【請求項8】

前記書き込みデータの'0'の個数と'1'の個数とを抽出する際に、当該書き込みデータに関する誤り訂正用として付加されるチェックビットを含めて'0'の個数と'1'の個数とを抽出して、前記データ選択信号を生成するとともに、前記書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成する際に、前記書き込みデータに付加された前記チェックビットも含めて反転させたデータを生成し、前記メモリに書き込む際に、前記書き込みデータに付加された前記チェックビットも含めてそのままかまたは反転させたデータかのいずれかを選択して、書き込むことを特徴とする請求項5ないし7のいずれかに記載の記憶装置制御方法。

【請求項1】

ランダムアクセスが可能なメモリを搭載した記憶装置であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持する搭載メモリ電力特性保持手段と、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、前記搭載メモリ電力特性保持手段に保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として出力するデータ解析手段と、前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、前記データ解析手段から出力された前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込む書き込みデータ選択手段と、を少なくとも備えていることを特徴とする記憶装置。

【請求項2】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込んだかという情報を、データ反転情報として前記メモリのアドレスごとに対応する記憶領域に保持するデータ反転情報保持手段を備え、前記予備テスト以降において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、前記データ反転情報保持手段に前記メモリのアドレスごとに対応して保持している前記データ反転情報に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力する読み出しデータ選択手段、を少なくとも備えていることを特徴とする請求項1に記載の記憶装置。

【請求項3】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込む際に、前記データ解析手段が出力する前記データ選択信号も、同時に、前記メモリの当該アドレスに書き込み、しかる後において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、当該アドレスに書き込まれていた前記データ選択信号も同時に読み出し、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、当該アドレスから同時に読み出した前記データ選択信号に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力する読み出しデータ選択手段、を少なくとも備えていることを特徴とする請求項1に記載の記憶装置。

【請求項4】

前記データ解析手段において前記書き込みデータの'0'の個数と'1'の個数とを抽出する際に、当該書き込みデータに関する誤り訂正用として付加されるチェックビットを含めて'0'の個数と'1'の個数とを抽出して、前記データ選択信号を生成するとともに、前記書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成する際に、前記書き込みデータに付加された前記チェックビットも含めて反転させたデータを生成し、前記メモリに書き込む際に、前記書き込みデータに付加された前記チェックビットも含めてそのままかまたは反転させたデータかのいずれかを選択して、書き込むことを特徴とする請求項1ないし3のいずれかに記載の記憶装置。

【請求項5】

ランダムアクセスが可能なメモリを搭載した記憶装置の動作を制御する記憶装置制御方法であって、初期化時に前記メモリにALL'0'およびALL'1'の双方の試験データを書き込む予備テストを実施し、ALL'0'およびALL'1'の試験データそれぞれにおいて書き込み終了時点からあらかじめ定めた一定時間経過後のそれぞれの試験データ保持時における前記メモリの温度を測定し、ALL'0'書き込み時の温度とALL'1'書き込み時の温度とを比較して、温度が低い方のデータを示す情報を、前記メモリの消費電力が少なくなる特性を示す搭載メモリ電力特性としてあらかじめ保持しておき、前記予備テスト以降において、前記メモリの任意のアドレスに書き込みデータを書き込む際に、該書き込みデータの'0'の個数と'1'の個数とを抽出して、保持されている前記搭載メモリ電力特性に基づいて、当該書き込みデータをそのまま前記メモリに書き込むべきかあるいは当該書き込みデータの'0'と'1'とを反転した反転データとして前記メモリに書き込むべきかを判別して、判別した結果をデータ選択信号として書き込みデータ選択手段に対して出力し、該書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成した後、出力されてきた前記データ選択信号に基づいて、前記書き込みデータそのままかまたは前記反転データかのいずれかを選択して、前記メモリに書き込むことを特徴とする記憶装置制御方法。

【請求項6】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込んだかという情報を、データ反転情報として前記メモリのアドレスごとに対応して設けた記憶領域に保持し、前記予備テスト以降において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、前記メモリのアドレスごとに対応して保持している前記データ反転情報に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力することを特徴とする請求項5に記載の記憶装置制御方法。

【請求項7】

前記予備テストの結果を基に、前記書き込みデータ選択手段において前記メモリの任意のアドレスに前記書き込みデータそのままかまたは前記反転データかのいずれを選択して書き込む際に、前記データ選択信号も、同時に、前記メモリの当該アドレスに書き込み、しかる後において、前記メモリの任意のアドレスからデータをメモリデータとして読み出した際に、当該アドレスに書き込まれていた前記データ選択信号も同時に読み出し、前記メモリから読み出した前記メモリデータの'0'と'1'とを反転させたメモリ反転データを生成した後、当該アドレスから同時に読み出した前記データ選択信号に基づいて、前記メモリから読み出した前記メモリデータそのままかまたは前記メモリ反転データかのいずれかを選択して、読み出しデータとして出力することを特徴とする請求項5に記載の記憶装置制御方法。

【請求項8】

前記書き込みデータの'0'の個数と'1'の個数とを抽出する際に、当該書き込みデータに関する誤り訂正用として付加されるチェックビットを含めて'0'の個数と'1'の個数とを抽出して、前記データ選択信号を生成するとともに、前記書き込みデータ選択手段において前記書き込みデータの'0'と'1'とを反転させた前記反転データを生成する際に、前記書き込みデータに付加された前記チェックビットも含めて反転させたデータを生成し、前記メモリに書き込む際に、前記書き込みデータに付加された前記チェックビットも含めてそのままかまたは反転させたデータかのいずれかを選択して、書き込むことを特徴とする請求項5ないし7のいずれかに記載の記憶装置制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−58115(P2013−58115A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−196661(P2011−196661)

【出願日】平成23年9月9日(2011.9.9)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月9日(2011.9.9)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]