電力増幅装置

【課題】 平均電力に対するピーク電力の比が高い信号を増幅する際の電力変換効率を向上させることができる電力増幅装置を提供する。

【解決手段】 異なる入力レベルの信号を飽和に近い動作で増幅する増幅器21〜23と、入力信号をレベルに応じて適切な増幅器に出力する信号分割処理部1と、各増幅器からの出力を低損失で合成する信号合成部3とを備え、増幅器21〜23の出力インピーダンスを同一の値とし、信号合成部3の位相調整線路301〜303と出力線路304の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、合成点305におけるインピーダンスが、動作していない増幅器に対して開放となるよう位相調整線路301〜303のインピーダンスが調整され、動作している増幅器に対して増幅器の出力インピーダンスとなるよう出力線路304のインピーダンスが調整されている電力増幅装置としている。

【解決手段】 異なる入力レベルの信号を飽和に近い動作で増幅する増幅器21〜23と、入力信号をレベルに応じて適切な増幅器に出力する信号分割処理部1と、各増幅器からの出力を低損失で合成する信号合成部3とを備え、増幅器21〜23の出力インピーダンスを同一の値とし、信号合成部3の位相調整線路301〜303と出力線路304の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、合成点305におけるインピーダンスが、動作していない増幅器に対して開放となるよう位相調整線路301〜303のインピーダンスが調整され、動作している増幅器に対して増幅器の出力インピーダンスとなるよう出力線路304のインピーダンスが調整されている電力増幅装置としている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力増幅装置に係り、特に電力変換効率を向上させることができる電力増幅装置に関する。

【背景技術】

【0002】

[先行技術の説明]

無線機に用いられる送信用電力増幅装置は、高周波信号を所要の送信電力に増幅するものであり、ほとんどの無線機において最も多くの電力を消費する部分である。

電力増幅装置が消費する電力は、高周波出力に変換されるだけでなく、内部損失となる熱として放出される。そのため、消費電力の低減や信頼性の向上を図るために、電力増幅装置の電力変換効率を上げて、無駄な内部損失を抑えることが要求されている。

【0003】

ところで、CDMA(Code Division Multiple Access)や、OFDM(Orthogonal Frequency Division Multiplexing)等のように、平均電力に対するピーク電力の比(PAPR:Peak to Average Power Ratio)が高い信号を増幅するには、増幅器の平均出力電力より増幅器の飽和レベルを高くする(バックオフを取る)必要がある。しかし、バックオフを取って使用すると、増幅器の効率は低下してしまう。

【0004】

例えば、単純なB級増幅器では、飽和動作時には理論的な最大効率は78%であるが、バックオフ10dBでの動作時における最大理論効率は26%となる。

CDMAやOFDM等の信号を増幅する基地局用高出力増幅装置等では、ピーク電力比の大きな信号を低歪みで増幅する必要があるため、バックオフを大きく取らなければならず、効率が低くなってしまう。

【0005】

[関連技術]

効率を向上させる増幅装置に関する先行技術としては、特開2009−55515号公報(出願人:株式会社日立国際電気、特許文献1)がある。

特許文献1には、複数のピーク増幅器を備えたドハティ増幅器において、各増幅器からの出力を線路上で合成することが記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−55515号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記従来の電力増幅装置では、CDMAやOFDMのように、PAPRが高い信号を増幅する場合にはバックオフを大きく取らなければならず、電力変換効率が低くなってしまうという問題点があった。

【0008】

尚、特許文献1には、複数の増幅器の出力インピーダンスを同一の値とし、合成点において、増幅器が動作していない場合に開放となるよう調整された位相調整線路と、増幅器が動作している場合に増幅器の出力インピーダンスとするよう調整された出力線路を備え、低損失で合成することは記載されていない。

【0009】

本発明は、上記実状に鑑みて為されたもので、平均電力に対するピーク電力の比が高い信号を増幅する際の電力変換効率を向上させることができる電力増幅装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記従来例の問題点を解決するための本発明は、高周波信号を増幅する電力増幅装置であって、互いに異なる電力レベルの信号を入力し、入力された信号を飽和に近い状態でそれぞれ増幅する複数の増幅器と、入力信号を信号レベルに応じて複数の増幅器のいずれかに出力する信号分割処理部と、各増幅器に対応して設けられ、対応する増幅器からの出力信号の位相を調整する複数の位相調整線路と、複数の位相調整線路からの出力を合成する合成点と、合成点からの出力のインピーダンスを調整する出力線路とを有する信号合成部とを備え、複数の増幅器の出力インピーダンスを同一の値とし、複数の位相調整線路と、出力線路の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、位相調整回路のインピーダンスが、対応する増幅器が動作していない場合に合成点における当該増幅器のインピーダンスを開放とするよう調整され、出力線路のインピーダンスが、動作している増幅器の合成点におけるインピーダンスを増幅器の出力インピーダンスとするよう調整されていることを特徴としている。

【発明の効果】

【0011】

本発明によれば、高周波信号を増幅する電力増幅装置であって、互いに異なる電力レベルの信号を入力し、入力された信号を飽和に近い状態でそれぞれ増幅する複数の増幅器と、入力信号を信号レベルに応じて複数の増幅器のいずれかに出力する信号分割処理部と、増幅器からの出力を合成する信号合成部とを備え、信号合成部が、各増幅器に対応して設けられ、対応する増幅器からの出力信号の位相を調整する複数の位相調整線路と、複数の位相調整線路からの出力を合成する合成点と、合成点からの出力のインピーダンスを調整する出力線路とを有し、複数の増幅器の出力インピーダンスを同一の値とし、複数の位相調整線路と、出力線路の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、位相調整回路のインピーダンスが、対応する増幅器が動作していない場合に合成点における当該増幅器のインピーダンスを開放とするよう調整され、出力線路のインピーダンスが、動作している増幅器の合成点におけるインピーダンスを増幅器の出力インピーダンスとするよう調整されている電力増幅装置としているので、各増幅器がそれぞれ飽和に近い動作で増幅を行い、信号合成部で低損失で合成することにより増幅装置全体の効率を向上させ、平均電力に対するピーク電力の比が高い信号を増幅する場合の電力変換効率を向上させることができる効果がある。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の形態に係る電力増幅装置の構成ブロック図である。

【図2】本電力増幅装置における信号波形の分割及び合成を示す説明図である。

【図3】アナログ回路で構成された信号分割処理部1の構成を示す回路図である。

【図4】電源回路26の回路図である。

【図5】増幅器23に供給されるゲート電圧波形の例を示す説明図である。

【図6】増幅器21が信号を出力している場合の信号合成部における信号合成例を示す説明図である。

【図7】増幅器22が信号を出力している場合の信号合成例を示す説明図である。

【図8】増幅器23が信号を出力している場合の信号合成例を示す説明図である。

【図9】増幅器21が信号を出力している場合のインピーダンスを示すスミスチャートである。

【発明を実施するための形態】

【0013】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係る電力増幅装置は、ピーク対平均電力比の大きい信号を増幅するものであって、異なる入力レベルの信号を飽和に近い動作で増幅する複数の増幅器と、入力信号を信号レベルに応じて適切な増幅器に出力する分配部と、複数の増幅器からの出力信号を線路上で低損失に合成する信号合成部とを備え、信号合成部が、各増幅器からの出力の位相を調整する複数の位相調整線路と、複数の位相調整線路の出力を合成する合成点と、合成点の出力のインピーダンスを調整する出力線路とを備え、位相調整線路のインピーダンスは、合成点におけるインピーダンスが、動作していない増幅器に対して開放となるよう調整され、出力線路のインピーダンスは、動作している増幅器に対して増幅器の出力インピーダンスとなるよう調整されているものであり、各増幅器が常に飽和に近い動作を行うと共に、信号合成部が各増幅器の出力を線路上において低損失で合成して、PAPRの大きい信号を効率的に増幅して合成することができ、増幅器全体の効率を向上させることができるものである。

【0014】

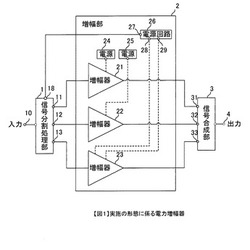

[実施の形態に係る電力増幅装置の構成:図1]

本発明の実施の形態に係る電力増幅装置の構成について図1を用いて説明する。図1は、本発明の実施の形態に係る電力増幅装置の構成ブロック図である。

図1に示すように、本発明の実施の形態に係る電力増幅装置(本電力増幅装置)は、主として、入力端子10と、信号分割処理部1と、増幅部2と、信号合成部3と、出力端子4とを備えている。

更に、増幅部2は、増幅器21,22,23と、電源24,25と、電源回路26とを備えている。

【0015】

本電力増幅装置の各部について説明する。

信号分割処理部1は、入力端子10から入力された信号を包絡線検波して、包絡線の電力レベルを検出し、検出された電力レベルに応じて、増幅器21,22,23のいずれに出力するか判定し、分配出力端子11,12,13から出力する。信号分割処理部1の構成及び動作については後述する。

【0016】

信号分割処理部1は、アナログ回路またはデジタル回路で構成され、出力端子4を基準として位相と振幅を調整し、各段の増幅器21〜23や信号合成部3の遅延差を調整した信号を出力する機能を有するものである。

【0017】

増幅部2の増幅器21,22,23は、互いに異なる特定範囲の入力レベルの信号を入力して、それぞれ当該入力レベルにおいて飽和に近い状態で増幅するものであり、増幅器2の特性(種類)やバイアス電圧及びドレイン電圧が適宜選択/設定されている。増幅器21,22,23は常に飽和に近い動作を行うため、いずれも高効率で動作する。

【0018】

具体的には、増幅器21は、大信号を増幅するため出力電力が大きいデバイスを用いて設計し、増幅器22は、増幅器21よりも出力電力の少ないデバイスを用い、増幅器23は更に出力電力の少ないデバイスを用いる。

このとき、電源24、電源25、電源回路26から供給する電源電圧は、信号分割処理部1から出力される分割信号波形15、分割信号波形16、分割信号波形17が、飽和電力に近い状態で増幅するよう設定する。よって、増幅器21、増幅器22、増幅器23はすべて飽和電力に近い状態で増幅するため、高効率動作が可能となる。

【0019】

増幅器21は、電源24から一定の電圧が供給され、C級動作にて増幅を行う。

増幅器22は、電源25から一定の電圧が供給され、C級動作にて増幅を行う。

増幅器23は、電源回路26から搬送波が存在する時間のみ動作するよう制御された電圧を供給され、搬送波が存在する場合のみAB級で増幅を行う。

【0020】

電源24は、増幅器21に適切な電圧値の一定電圧をドレイン電圧として供給する。

同様に、電源25は、増幅器22に適切な電圧値の一定電圧をドレイン電圧として供給する。

電源回路26は、信号分割処理部1からの信号に基づいて、搬送波がある場合のみ動作するよう、増幅器23のゲート電圧を制御すると共に、ドレイン電圧を供給する。

【0021】

信号合成部3は、増幅部2の増幅器21,22,23で増幅された信号を、入力端子31,32,33から入力し、線路上で低損失に合成し、出力端子4から出力する。

【0022】

本電力増幅装置では、増幅部2の各増幅器21,22,23がいずれも飽和電力に近い状態で動作し、更に、信号合成部3で各増幅信号を低損失で合成するので、OFDMやCDMAのようにPAPRの大きい信号であっても高効率で増幅可能な送信機を実現できるものである。

【0023】

[本電力増幅装置における信号波形分割合成例:図2]

本電力増幅装置における信号波形の分割及び合成の概略について図2を用いて説明する。図2は、本電力増幅装置における信号波形の分割及び合成を示す説明図である。

図2に示すように、信号分割処理部1では、入力された変調信号波形14を検波して、信号レベルを検出し、予め記憶されているしきい値th1、th2(th1<th2)と比較して、信号レベルに応じて信号を時間軸で分割し、出力端子11,12,13のいずれかに出力する。

【0024】

図2の例では、入力信号は、信号レベルがth1より小さい場合(分割信号波形17)、信号レベルがth1とth2の間の場合(分割信号波形16)、信号レベルがth2より大きい場合(分割信号波形15)の3通りに分割されて、それぞれ、分配出力端子13,12,11に出力されるようになっている。

【0025】

そして、各分配出力端子11〜13から出力された分割信号15〜17は、増幅部2の増幅器21〜23で増幅され、信号合成部3で低損失に合成されて、増幅された変調信号波形19が得られるものである。

【0026】

[信号分割処理部1の構成例:図3]

次に、本電力増幅装置の信号分割処理部1の構成について図3を用いて説明する。図3は、アナログ回路で構成された信号分割処理部1の構成を示す回路図である。

図3に示すように、信号分割処理部1は、入力端子10と、ディバイダ102と、検波器103と、コンパレータ104,105,106,107と、AND回路108と、スイッチ109,110,111と、位相振幅調整回路113,114,115と、分配出力端子11,12,13とを備えている。

また、信号分割処理部1は、図1に示した電源回路26に対して、信号を分岐して出力する出力端子18を備えている。

図1,2と同じ部分については同一の符号を付している。

【0027】

ディバイダ102は入力端子10からの入力信号(変調信号波形)14を2つに分岐する。

検波器103は、分岐された一方の入力信号を検波して入力レベル(a)を検出する。検出された入力レベルは、コンパレータ104,105,106,107に入力される。

【0028】

そして、本実施例では、コンパレータ104〜107によって、入力レベルaをしきい値th1、th2と比較して、その大小に基づいてスイッチ109,110,111のいずれかをオンとして、位相及び振幅を調整した後、分配出力端子11,12,13のいずれかに出力する。

【0029】

コンパレータ104には、+端子に第1のしきい値th1が設定されており、−端子から入力される入力レベルaがth1より小さい(a<th1)場合に、出力信号がHレベルとなる。すなわち、検波信号の信号波形が、信号波形112b(小信号)のときにスイッチ109がオンとなり、他のスイッチ110,111はオフとなる。

【0030】

コンパレータ105は、−端子に第1のしきい値th1が設定されており、+端子から入力される入力レベルaがth1より大きい(a>th1)場合に、Hレベル信号が出力される。

また、コンパレータ106には、+端子に第2のしきい値th2が設定されており、−端子から入力される入力レベルaがth2より小さい(a<th2)場合に、Hレベル信号が出力される。

【0031】

そして、コンパレータ105とコンパレータ106からの出力が両方ともHレベルの場合(th1<a<th2)のみに、AND回路108からの出力がHレベルとなる。つまり、検波出力が信号波形112c(中信号)のときにスイッチ110がオンとなり、他のスイッチ109,111はオフとなる。

【0032】

コンパレータ107は、−端子に第2のしきい値th2が設定されており、+端子から入力される入力レベルaがth2より大きい(a>th2)場合に、出力信号がHレベルとなる。つまり、検波出力が信号波形112d(大信号)のときにスイッチ111がオンとなり、他のスイッチ109,110はオフとなる。

【0033】

スイッチ109は、コンパレータ104からの出力がHレベルの場合にオンとなり、ディバイダ102で分岐された入力信号を分配出力端子15に出力する。

スイッチ110は、AND回路108からの出力がHレベルの場合にオンとなり、入力信号を分配出力端子14に出力する。

スイッチ111は、コンパレータ107からの出力がHレベルの場合にオンとなり、入力信号を分配出力端子13に出力する。

【0034】

位相振幅調整回路113〜115は、アナログ回路またはデジタル回路で構成され、出力端子4を基準として位相と振幅を調整し、各段の増幅器や信号合成部の遅延差を調整した信号を出力する。

【0035】

上記構成の信号分配部12の動作について説明する。

入力端子10から入力された信号は、ディバイダ102で2つに分岐されて、一方の分岐信号は、検波器110で検波されて入力レベル(a)が検出される。

入力レベルaがth1より小さい場合には(a<th1,信号波形112b)、コンパレータ104の出力のみがHレベルとなり、スイッチ109がオンとなって、ディバイダ102で分岐された他方の入力信号は位相振幅調整回路115から分配出力端子13に出力される。

更に、コンパレータ104の出力は、出力端子18を介して電源回路26に供給される。

【0036】

また、入力レベルaがth1とth2の間(th1<a<th2,信号波形112c)の場合には、コンパレータ105,106がHレベルとなり、スイッチ110がオンとなって入力信号は位相振幅調整回路114から分配出力端子12に出力される。

入力レベルaがth2より大きい(a>th2,信号波形112d)場合には、コンパレータ107がHレベルとなり、スイッチ111がオンとなって入力信号は位相振幅調整回路113から分配出力端子11に出力される。

上記以外の状態においては、スイッチ109〜111はオフとなる。

【0037】

このようにして、本電力増幅装置では、入力信号が入力レベルに応じて最適な増幅器の経路に分配され、図1に示した増幅器21,22,23のいずれかにおいて飽和に近い状態で効率よく増幅されるものである。

【0038】

[電源回路26:図1、図3、図4]

次に、電源回路26について図1、図3、図4を用いて説明する。図4は、電源回路26の回路図である。

図1に示した電源回路26は、搬送波が存在する時間のみ動作するよう、増幅器23のゲート電圧を制御する。

具体的には、電源回路26は、ゲート電圧制御回路を備えており、ゲート電圧制御回路が、コンパレータ104からの信号を信号分割処理部1の出力端子18と電源回路26の入力端子27を介して入力し、当該信号を用いてゲート電圧を制御する。

ゲート電圧の制御回路は、アナログ回路もしくはデジタル回路で構成される。

【0039】

[電源回路26の構成:図4]

図4では、アナログ回路で構成された電源回路26の例を示している。

図4に示すように、電源回路26は、直流電圧源204と、電源供給端子29とからなる電源供給部と、直流電圧源205と、抵抗201,202と、スイッチ203と、入力端子27と、ゲート電圧制御端子28とを備えたゲート電圧制御回路とを備えている。

【0040】

電源供給部は、電源供給端子29から増幅器23に安定したドレイン電圧を供給する。

ゲート電圧制御回路は、直流電圧源203からの電圧を、抵抗201、抵抗202によって分圧し、入力端子27から入力されるコントロール信号によってスイッチ203を制御して、2段階の電圧の内適切なゲート電圧に切り替えて出力端子28から出力する。

具体的には、スイッチ203が直流電圧源205側に切り替えられると、AB級に対応した電圧が出力され、スイッチ203が分圧側に切り替えられるとC級に対応した電圧が出力されて、増幅器23にゲート電圧として供給される。

【0041】

そして、電源回路26では、入力端子27からコンパレータ104の出力が入力された場合(搬送波がある場合)には、スイッチ203を電源電圧側に切り替えて、AB級のゲート電圧を供給し、入力端子27からの入力がない場合には、スイッチ203を分圧側に切り替えてC級のゲート電圧を供給する。

【0042】

[増幅器23のゲート電圧の例:図5]

ここで、増幅器23に供給されるゲート電圧波形の例について図5を用いて説明する。図5は、増幅器23に供給されるゲート電圧波形の例を示す説明図である。

図5に示すように、増幅器23のゲート電圧波形210は、AB級バイアスである電圧H−VGSと、C級バイアスである電圧L−VGSを切り替えることによって生成される。

【0043】

つまり、コンパレータ104の出力信号(搬送波)17が存在する時間は、増幅器23のゲート電圧は電圧H−VGSとなってAB級で動作し、コンパレータ104の出力信号17がない時間は、ゲート電圧は電圧L−VGSとなってC級で動作する。

これにより、後述するように、増幅器23が増幅動作を行っていない場合のインピーダンスを開放にして、低損失とすることができるものである。

【0044】

[信号合成部3:図6,7,8]

次に、本電力増幅装置の特徴部分である信号合成部3について図6〜8を用いて説明する。図6〜8は、信号合成部3の構成及び合成の動作を示す説明図であり、図6は、増幅器21が信号を出力している場合の信号合成例を示し、図7は、増幅器22が信号を出力している場合の信号合成例を示し、図8は、増幅器23が信号を出力している場合の信号合成例を示している。

本電力増幅装置の信号合成部3は、増幅部2の3つの増幅器21,22,23の内、一つの増幅器が信号を出力している場合には、他の増幅器からの出力はないという条件で、低損失に合成する機能を有するものである。

【0045】

[信号合成部3の構成]

図6に示すように、信号合成部3は、入力端子31,32,33と、位相調整線路301,302,303と、合成点305と、出力線路304とを備えている。

入力端子31,32,33は、それぞれ、増幅器21,22,23からの信号を入力する。

位相調整線路301,302,303は、それぞれ、入力端子31,32,33からの信号の位相を調整する。

合成点305は、位相調整線路301,302,303からの信号を合成する。

出力線路304は、出力端子4に出力する増幅器出力のインピーダンスを調整する。

【0046】

[信号合成部3の動作]

次に、信号合成部3における合成の動作について図6〜8を用いて具体的に説明する。まず、本電力増幅装置における動作の前提について説明する。

増幅器21〜23は、時間分割された分割波形15〜17を増幅するため、1つの増幅器が増幅動作を行っている場合は他の2つの増幅器は増幅動作していない。

また、ここでは、増幅器21〜23は、増幅動作をしている場合には、出力インピーダンスが50Ohmとなるよう、増幅器内部の出力整合回路が調整されている。尚、ここでは、増幅器21〜23の出力インピーダンスを50Ohmとしているが、これに限るものではない。

【0047】

増幅器21,22はC級増幅器であり、また、増幅器23は、上述した電源回路26によるゲート電圧制御に基づいて、AB級又はC級動作を行う。

位相調整線路301,302,303の特性インピーダンスは、それぞれ50Ohmである。

また、出力線路304の特性インピーダンスも増幅器の出力インピーダンスと同じく、50Ohmとしている。

【0048】

[増幅器21が信号を出力している場合のインピーダンス:図6、図9]

[増幅器21のインピーダンス]

上述した前提条件を踏まえ、増幅器21が信号を出力している場合の、合成点305から各増幅器を見たインピーダンスについて図6及び図9を用いて説明する。

図9は、増幅器21が信号を出力している場合のインピーダンスを示すスミスチャートである。

入力端子31から位相調整線路301を見たインピーダンスをZin、位相調整線路301の特性インピーダンスをZ0、位相調整線路301の電気長をθ、出力線路304の特性インピーダンスをZLとすると、Zinは(式1)で表される。

【0049】

【数1】

【0050】

位相調整線路301と出力線路304の特性インピーダンスは等しく、共に50Ohmなので、θの値を変えても、Zin=Z0=ZL=50Ohmとなる。

よって、増幅器21が動作している場合、位相調整線路301の長さに関わらず、入力端子31から見た負荷インピーダンス(図6ではZt1)は50Ohmとなる。

同様に、合成点305から増幅器21を見たインピーダンスも50Ohmとなる。

また、入力端子31、合成点305のインピーダンスをスミスチャートに示すと、図9のインピーダンス306となる。

【0051】

[増幅器22のインピーダンス:図4、図9]

次に、増幅器21が信号を出力している場合の増幅器22のインピーダンスについて説明する。

増幅器21が信号を出力している場合、C級にバイアスされた増幅器22は信号を出力しておらず、ドレイン電流がほとんど流れていないため、増幅素子出力端でのインピーダンスは理想的には無限大(∞)となる。

しかし、増幅素子の内部抵抗や整合回路により、実際の出力インピーダンスは無限大にはならない。そのため、入力端子32から増幅器22を見たインピーダンスは、図9のインピーダンス309となる。

【0052】

ここで、合成点305から増幅動作をしていない増幅器22を見たインピーダンスを算出する。

合成点305のインピーダンスをZinとし、位相調整線路302の特性インピーダンスをZ0、位相調整線路302の電気長をθ、入力端子32から増幅器22を見たインピーダンス(インピーダンス309)をZLとすると、(式1)より、Zinは、位相調整線路302の長さを変えることにより変化する。

【0053】

すなわち、合成点305から増幅器22を見たインピーダンスは、図9のインピーダンス309から伸びた破線のように回る。

インピーダンス309がインピーダンス310となるよう位相調整線路302の電気長を調整し、後述する(式2)を用いて合成点305での反射係数Γrを計算する。

【0054】

合成点305で観測されるインピーダンスをZout、合成点305から増幅器22をみたインピーダンスをZrとすると、反射係数Γrは以下のように表される。

【数2】

【0055】

合成点305で観測されるインピーダンスは、上述したように50Ohmであり、インピーダンス310はハイインピーダンスであって、Zoutに比べて十分大きいため、反射係数Γrは、Γr≒+1となる。

つまり、本増幅装置では、位相調整線路302の電気長を調整することにより、増幅器22が信号を出力していない場合、合成点305から増幅器22を見たインピーダンスを開放とするものである。

図6ではZr2=∞と表している。

【0056】

[増幅器23のインピーダンス:図4、図9]

次に、増幅器21が信号を出力している場合の増幅器23のインピーダンスについて説明する。

AB級に設定された増幅器23では、C級と違って、信号を出力していない場合でもドレイン電流が流れている。

入力端子33から増幅器23を見たインピーダンスは、図9のインピーダンス307となる。増幅器22と同様に合成点305で開放とするため、位相調整線路303の電気長を調整すると、インピーダンス307からインピーダンス308に伸びた破線のようにまわり、ハイインピーダンスとはならないので、合成点305から増幅器21を見たインピーダンスは開放とならない。

【0057】

そこで、本電力増幅装置では、上述したように、電源回路26で増幅器23のゲート電圧を制御して、動作していない時はC級に設定するようにしている。

増幅器23をC級とすることで、増幅器22の場合と同様に、位相調整線路303の電気長を調整することによって、インピーダンス310に調整することが可能となり、合成点305から動作していない増幅器23を見たインピーダンスは開放となる。図6ではZr3=∞と表している。

【0058】

[負荷の反射係数]

上述した各増幅器のインピーダンスを踏まえ、増幅器21が増幅動作を行っている場合の負荷の反射係数を算出する。

増幅器21が増幅動作している場合の出力インピーダンスをZout、入力端子31から出力端子4までの負荷インピーダンスをZrとして、負荷の反射係数Γrを(式2)を用いて算出する。

【0059】

上述したように、増幅器22、23は、合成点305で開放となるので接続されていないものとみなすと、Zout=Zr=50Ohmとなるため、(式2)より、反射係数は、

Γr=0となる。

よって、増幅器21の出力信号は、入力端子31、位相調整線路301、合成点305、出力線路304を損失なく通過して、出力端子4に入力されることになる。

【0060】

[増幅器22が信号を出力している場合:図7]

増幅器22が増幅動作を行う場合には、図7に示すように、合成点305から見た増幅器21,23のインピーダンスは開放となる(Zr1=∞,Zr3=∞)ので、増幅器22のみが接続されているとみなすことができる。

よって、図6の場合と同様に、入力端子32から出力端子4までの負荷インピーダンスは増幅器22の出力インピーダンスと同じ50Ohm(Zt2=50Ohm)となり、信号合成部3に入力された増幅信号は、損失なく出力端子4に入力される。

【0061】

[増幅器23が信号を出力している場合:図8]

同様に、増幅器23が増幅動作を行う場合には、図8に示すように、合成点305から見た増幅器21,22のインピーダンスは開放(Zr1=∞,Zr2=∞)、入力端子33から出力端子4までの負荷インピーダンスは、増幅器23の出力インピーダンスと等しい50Ohmとなり(Zt3=50Ohm)、増幅信号は損失なく出力端子4に入力される。

【0062】

すなわち、本電力増幅装置では、入力信号の信号レベルに応じて、当該信号レベルで飽和に近い動作を行う増幅器が増幅動作を行い、図6,7,8のいずれかの状態で合成が行われるため、合成による損失はなく、動作している増幅器で増幅された信号は低損失で出力され、高効率の電力増幅装置を実現することができるものである。

理想的には、位相調整線路301〜303と出力線路304の通過損失のみが合成損失となるため、低損失での合成が可能となる。

【0063】

[実施の形態の効果]

本発明の実施の形態に係る電力増幅装置によれば、異なる入力レベルの信号を飽和に近い動作で増幅する複数の増幅器21,22,23と、入力信号を信号レベルに応じて適切な増幅器に出力する信号分割処理部1と、各増幅器からの出力を合成する信号合成部3とを備え、信号合成部3が、増幅器21,22,23の出力信号の位相を調整する位相調整線路301,302,303と、位相調整線路301,302,303からの出力を合成する合成点305と、合成点305からの出力のインピーダンスを調整する出力線路304とを備え、増幅器21,22,23の出力インピーダンスを同一の値とすると共に、位相調整線路301,302,303及び出力線路304の特性インピーダンスを増幅器の出力インピーダンスと同一の値としておき、合成点305におけるインピーダンスが、動作していない増幅器に対して開放となるよう位相調整線路301,302,303の電気長が調整され、動作している増幅器に対して増幅器の出力インピーダンスとなるよう出力線路304の電気長が調整されているので、各増幅器21〜23が常に飽和に近い動作を行うと共に、信号合成部が各増幅器21〜23からの出力を線路上で低損失で合成して、PAPRの大きい信号であっても高効率で増幅して合成することができ、増幅器全体の電力変換効率を向上させることができる効果がある。

【産業上の利用可能性】

【0064】

本発明は、平均電力に対するピーク電力の比が高い信号を増幅する際の電力変換効率を向上させることができる電力増幅装置に適している。

【符号の説明】

【0065】

1...信号分割処理部、 2...増幅部、 3...信号合成部、 4,18...出力端子、 10,27,31,32,33...入力端子、 21,22,23...増幅器、 24,25...電源、 26...電源回路、 28...ゲート電圧制御端子、 29...電源供給端子、 11,12,13...分配出力端子、 14...変調信号波形、 15,16,17...分割信号波形、 102...ディバイダ、 103...検波器、 104,105,106,107...コンパレータ、 108...AND回路、 109,110,111...スイッチ、 112...信号波形、 113,114,115...位相振幅調整回路、 201,202...抵抗、 203...スイッチ、 204,205...直流電圧源、 210...ゲート電圧波形、 301,302,303...位相調整線路、 304...出力線路、 305...合成点、 306,307,308,309,310...インピーダンス

【技術分野】

【0001】

本発明は、電力増幅装置に係り、特に電力変換効率を向上させることができる電力増幅装置に関する。

【背景技術】

【0002】

[先行技術の説明]

無線機に用いられる送信用電力増幅装置は、高周波信号を所要の送信電力に増幅するものであり、ほとんどの無線機において最も多くの電力を消費する部分である。

電力増幅装置が消費する電力は、高周波出力に変換されるだけでなく、内部損失となる熱として放出される。そのため、消費電力の低減や信頼性の向上を図るために、電力増幅装置の電力変換効率を上げて、無駄な内部損失を抑えることが要求されている。

【0003】

ところで、CDMA(Code Division Multiple Access)や、OFDM(Orthogonal Frequency Division Multiplexing)等のように、平均電力に対するピーク電力の比(PAPR:Peak to Average Power Ratio)が高い信号を増幅するには、増幅器の平均出力電力より増幅器の飽和レベルを高くする(バックオフを取る)必要がある。しかし、バックオフを取って使用すると、増幅器の効率は低下してしまう。

【0004】

例えば、単純なB級増幅器では、飽和動作時には理論的な最大効率は78%であるが、バックオフ10dBでの動作時における最大理論効率は26%となる。

CDMAやOFDM等の信号を増幅する基地局用高出力増幅装置等では、ピーク電力比の大きな信号を低歪みで増幅する必要があるため、バックオフを大きく取らなければならず、効率が低くなってしまう。

【0005】

[関連技術]

効率を向上させる増幅装置に関する先行技術としては、特開2009−55515号公報(出願人:株式会社日立国際電気、特許文献1)がある。

特許文献1には、複数のピーク増幅器を備えたドハティ増幅器において、各増幅器からの出力を線路上で合成することが記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−55515号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記従来の電力増幅装置では、CDMAやOFDMのように、PAPRが高い信号を増幅する場合にはバックオフを大きく取らなければならず、電力変換効率が低くなってしまうという問題点があった。

【0008】

尚、特許文献1には、複数の増幅器の出力インピーダンスを同一の値とし、合成点において、増幅器が動作していない場合に開放となるよう調整された位相調整線路と、増幅器が動作している場合に増幅器の出力インピーダンスとするよう調整された出力線路を備え、低損失で合成することは記載されていない。

【0009】

本発明は、上記実状に鑑みて為されたもので、平均電力に対するピーク電力の比が高い信号を増幅する際の電力変換効率を向上させることができる電力増幅装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記従来例の問題点を解決するための本発明は、高周波信号を増幅する電力増幅装置であって、互いに異なる電力レベルの信号を入力し、入力された信号を飽和に近い状態でそれぞれ増幅する複数の増幅器と、入力信号を信号レベルに応じて複数の増幅器のいずれかに出力する信号分割処理部と、各増幅器に対応して設けられ、対応する増幅器からの出力信号の位相を調整する複数の位相調整線路と、複数の位相調整線路からの出力を合成する合成点と、合成点からの出力のインピーダンスを調整する出力線路とを有する信号合成部とを備え、複数の増幅器の出力インピーダンスを同一の値とし、複数の位相調整線路と、出力線路の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、位相調整回路のインピーダンスが、対応する増幅器が動作していない場合に合成点における当該増幅器のインピーダンスを開放とするよう調整され、出力線路のインピーダンスが、動作している増幅器の合成点におけるインピーダンスを増幅器の出力インピーダンスとするよう調整されていることを特徴としている。

【発明の効果】

【0011】

本発明によれば、高周波信号を増幅する電力増幅装置であって、互いに異なる電力レベルの信号を入力し、入力された信号を飽和に近い状態でそれぞれ増幅する複数の増幅器と、入力信号を信号レベルに応じて複数の増幅器のいずれかに出力する信号分割処理部と、増幅器からの出力を合成する信号合成部とを備え、信号合成部が、各増幅器に対応して設けられ、対応する増幅器からの出力信号の位相を調整する複数の位相調整線路と、複数の位相調整線路からの出力を合成する合成点と、合成点からの出力のインピーダンスを調整する出力線路とを有し、複数の増幅器の出力インピーダンスを同一の値とし、複数の位相調整線路と、出力線路の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、位相調整回路のインピーダンスが、対応する増幅器が動作していない場合に合成点における当該増幅器のインピーダンスを開放とするよう調整され、出力線路のインピーダンスが、動作している増幅器の合成点におけるインピーダンスを増幅器の出力インピーダンスとするよう調整されている電力増幅装置としているので、各増幅器がそれぞれ飽和に近い動作で増幅を行い、信号合成部で低損失で合成することにより増幅装置全体の効率を向上させ、平均電力に対するピーク電力の比が高い信号を増幅する場合の電力変換効率を向上させることができる効果がある。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の形態に係る電力増幅装置の構成ブロック図である。

【図2】本電力増幅装置における信号波形の分割及び合成を示す説明図である。

【図3】アナログ回路で構成された信号分割処理部1の構成を示す回路図である。

【図4】電源回路26の回路図である。

【図5】増幅器23に供給されるゲート電圧波形の例を示す説明図である。

【図6】増幅器21が信号を出力している場合の信号合成部における信号合成例を示す説明図である。

【図7】増幅器22が信号を出力している場合の信号合成例を示す説明図である。

【図8】増幅器23が信号を出力している場合の信号合成例を示す説明図である。

【図9】増幅器21が信号を出力している場合のインピーダンスを示すスミスチャートである。

【発明を実施するための形態】

【0013】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係る電力増幅装置は、ピーク対平均電力比の大きい信号を増幅するものであって、異なる入力レベルの信号を飽和に近い動作で増幅する複数の増幅器と、入力信号を信号レベルに応じて適切な増幅器に出力する分配部と、複数の増幅器からの出力信号を線路上で低損失に合成する信号合成部とを備え、信号合成部が、各増幅器からの出力の位相を調整する複数の位相調整線路と、複数の位相調整線路の出力を合成する合成点と、合成点の出力のインピーダンスを調整する出力線路とを備え、位相調整線路のインピーダンスは、合成点におけるインピーダンスが、動作していない増幅器に対して開放となるよう調整され、出力線路のインピーダンスは、動作している増幅器に対して増幅器の出力インピーダンスとなるよう調整されているものであり、各増幅器が常に飽和に近い動作を行うと共に、信号合成部が各増幅器の出力を線路上において低損失で合成して、PAPRの大きい信号を効率的に増幅して合成することができ、増幅器全体の効率を向上させることができるものである。

【0014】

[実施の形態に係る電力増幅装置の構成:図1]

本発明の実施の形態に係る電力増幅装置の構成について図1を用いて説明する。図1は、本発明の実施の形態に係る電力増幅装置の構成ブロック図である。

図1に示すように、本発明の実施の形態に係る電力増幅装置(本電力増幅装置)は、主として、入力端子10と、信号分割処理部1と、増幅部2と、信号合成部3と、出力端子4とを備えている。

更に、増幅部2は、増幅器21,22,23と、電源24,25と、電源回路26とを備えている。

【0015】

本電力増幅装置の各部について説明する。

信号分割処理部1は、入力端子10から入力された信号を包絡線検波して、包絡線の電力レベルを検出し、検出された電力レベルに応じて、増幅器21,22,23のいずれに出力するか判定し、分配出力端子11,12,13から出力する。信号分割処理部1の構成及び動作については後述する。

【0016】

信号分割処理部1は、アナログ回路またはデジタル回路で構成され、出力端子4を基準として位相と振幅を調整し、各段の増幅器21〜23や信号合成部3の遅延差を調整した信号を出力する機能を有するものである。

【0017】

増幅部2の増幅器21,22,23は、互いに異なる特定範囲の入力レベルの信号を入力して、それぞれ当該入力レベルにおいて飽和に近い状態で増幅するものであり、増幅器2の特性(種類)やバイアス電圧及びドレイン電圧が適宜選択/設定されている。増幅器21,22,23は常に飽和に近い動作を行うため、いずれも高効率で動作する。

【0018】

具体的には、増幅器21は、大信号を増幅するため出力電力が大きいデバイスを用いて設計し、増幅器22は、増幅器21よりも出力電力の少ないデバイスを用い、増幅器23は更に出力電力の少ないデバイスを用いる。

このとき、電源24、電源25、電源回路26から供給する電源電圧は、信号分割処理部1から出力される分割信号波形15、分割信号波形16、分割信号波形17が、飽和電力に近い状態で増幅するよう設定する。よって、増幅器21、増幅器22、増幅器23はすべて飽和電力に近い状態で増幅するため、高効率動作が可能となる。

【0019】

増幅器21は、電源24から一定の電圧が供給され、C級動作にて増幅を行う。

増幅器22は、電源25から一定の電圧が供給され、C級動作にて増幅を行う。

増幅器23は、電源回路26から搬送波が存在する時間のみ動作するよう制御された電圧を供給され、搬送波が存在する場合のみAB級で増幅を行う。

【0020】

電源24は、増幅器21に適切な電圧値の一定電圧をドレイン電圧として供給する。

同様に、電源25は、増幅器22に適切な電圧値の一定電圧をドレイン電圧として供給する。

電源回路26は、信号分割処理部1からの信号に基づいて、搬送波がある場合のみ動作するよう、増幅器23のゲート電圧を制御すると共に、ドレイン電圧を供給する。

【0021】

信号合成部3は、増幅部2の増幅器21,22,23で増幅された信号を、入力端子31,32,33から入力し、線路上で低損失に合成し、出力端子4から出力する。

【0022】

本電力増幅装置では、増幅部2の各増幅器21,22,23がいずれも飽和電力に近い状態で動作し、更に、信号合成部3で各増幅信号を低損失で合成するので、OFDMやCDMAのようにPAPRの大きい信号であっても高効率で増幅可能な送信機を実現できるものである。

【0023】

[本電力増幅装置における信号波形分割合成例:図2]

本電力増幅装置における信号波形の分割及び合成の概略について図2を用いて説明する。図2は、本電力増幅装置における信号波形の分割及び合成を示す説明図である。

図2に示すように、信号分割処理部1では、入力された変調信号波形14を検波して、信号レベルを検出し、予め記憶されているしきい値th1、th2(th1<th2)と比較して、信号レベルに応じて信号を時間軸で分割し、出力端子11,12,13のいずれかに出力する。

【0024】

図2の例では、入力信号は、信号レベルがth1より小さい場合(分割信号波形17)、信号レベルがth1とth2の間の場合(分割信号波形16)、信号レベルがth2より大きい場合(分割信号波形15)の3通りに分割されて、それぞれ、分配出力端子13,12,11に出力されるようになっている。

【0025】

そして、各分配出力端子11〜13から出力された分割信号15〜17は、増幅部2の増幅器21〜23で増幅され、信号合成部3で低損失に合成されて、増幅された変調信号波形19が得られるものである。

【0026】

[信号分割処理部1の構成例:図3]

次に、本電力増幅装置の信号分割処理部1の構成について図3を用いて説明する。図3は、アナログ回路で構成された信号分割処理部1の構成を示す回路図である。

図3に示すように、信号分割処理部1は、入力端子10と、ディバイダ102と、検波器103と、コンパレータ104,105,106,107と、AND回路108と、スイッチ109,110,111と、位相振幅調整回路113,114,115と、分配出力端子11,12,13とを備えている。

また、信号分割処理部1は、図1に示した電源回路26に対して、信号を分岐して出力する出力端子18を備えている。

図1,2と同じ部分については同一の符号を付している。

【0027】

ディバイダ102は入力端子10からの入力信号(変調信号波形)14を2つに分岐する。

検波器103は、分岐された一方の入力信号を検波して入力レベル(a)を検出する。検出された入力レベルは、コンパレータ104,105,106,107に入力される。

【0028】

そして、本実施例では、コンパレータ104〜107によって、入力レベルaをしきい値th1、th2と比較して、その大小に基づいてスイッチ109,110,111のいずれかをオンとして、位相及び振幅を調整した後、分配出力端子11,12,13のいずれかに出力する。

【0029】

コンパレータ104には、+端子に第1のしきい値th1が設定されており、−端子から入力される入力レベルaがth1より小さい(a<th1)場合に、出力信号がHレベルとなる。すなわち、検波信号の信号波形が、信号波形112b(小信号)のときにスイッチ109がオンとなり、他のスイッチ110,111はオフとなる。

【0030】

コンパレータ105は、−端子に第1のしきい値th1が設定されており、+端子から入力される入力レベルaがth1より大きい(a>th1)場合に、Hレベル信号が出力される。

また、コンパレータ106には、+端子に第2のしきい値th2が設定されており、−端子から入力される入力レベルaがth2より小さい(a<th2)場合に、Hレベル信号が出力される。

【0031】

そして、コンパレータ105とコンパレータ106からの出力が両方ともHレベルの場合(th1<a<th2)のみに、AND回路108からの出力がHレベルとなる。つまり、検波出力が信号波形112c(中信号)のときにスイッチ110がオンとなり、他のスイッチ109,111はオフとなる。

【0032】

コンパレータ107は、−端子に第2のしきい値th2が設定されており、+端子から入力される入力レベルaがth2より大きい(a>th2)場合に、出力信号がHレベルとなる。つまり、検波出力が信号波形112d(大信号)のときにスイッチ111がオンとなり、他のスイッチ109,110はオフとなる。

【0033】

スイッチ109は、コンパレータ104からの出力がHレベルの場合にオンとなり、ディバイダ102で分岐された入力信号を分配出力端子15に出力する。

スイッチ110は、AND回路108からの出力がHレベルの場合にオンとなり、入力信号を分配出力端子14に出力する。

スイッチ111は、コンパレータ107からの出力がHレベルの場合にオンとなり、入力信号を分配出力端子13に出力する。

【0034】

位相振幅調整回路113〜115は、アナログ回路またはデジタル回路で構成され、出力端子4を基準として位相と振幅を調整し、各段の増幅器や信号合成部の遅延差を調整した信号を出力する。

【0035】

上記構成の信号分配部12の動作について説明する。

入力端子10から入力された信号は、ディバイダ102で2つに分岐されて、一方の分岐信号は、検波器110で検波されて入力レベル(a)が検出される。

入力レベルaがth1より小さい場合には(a<th1,信号波形112b)、コンパレータ104の出力のみがHレベルとなり、スイッチ109がオンとなって、ディバイダ102で分岐された他方の入力信号は位相振幅調整回路115から分配出力端子13に出力される。

更に、コンパレータ104の出力は、出力端子18を介して電源回路26に供給される。

【0036】

また、入力レベルaがth1とth2の間(th1<a<th2,信号波形112c)の場合には、コンパレータ105,106がHレベルとなり、スイッチ110がオンとなって入力信号は位相振幅調整回路114から分配出力端子12に出力される。

入力レベルaがth2より大きい(a>th2,信号波形112d)場合には、コンパレータ107がHレベルとなり、スイッチ111がオンとなって入力信号は位相振幅調整回路113から分配出力端子11に出力される。

上記以外の状態においては、スイッチ109〜111はオフとなる。

【0037】

このようにして、本電力増幅装置では、入力信号が入力レベルに応じて最適な増幅器の経路に分配され、図1に示した増幅器21,22,23のいずれかにおいて飽和に近い状態で効率よく増幅されるものである。

【0038】

[電源回路26:図1、図3、図4]

次に、電源回路26について図1、図3、図4を用いて説明する。図4は、電源回路26の回路図である。

図1に示した電源回路26は、搬送波が存在する時間のみ動作するよう、増幅器23のゲート電圧を制御する。

具体的には、電源回路26は、ゲート電圧制御回路を備えており、ゲート電圧制御回路が、コンパレータ104からの信号を信号分割処理部1の出力端子18と電源回路26の入力端子27を介して入力し、当該信号を用いてゲート電圧を制御する。

ゲート電圧の制御回路は、アナログ回路もしくはデジタル回路で構成される。

【0039】

[電源回路26の構成:図4]

図4では、アナログ回路で構成された電源回路26の例を示している。

図4に示すように、電源回路26は、直流電圧源204と、電源供給端子29とからなる電源供給部と、直流電圧源205と、抵抗201,202と、スイッチ203と、入力端子27と、ゲート電圧制御端子28とを備えたゲート電圧制御回路とを備えている。

【0040】

電源供給部は、電源供給端子29から増幅器23に安定したドレイン電圧を供給する。

ゲート電圧制御回路は、直流電圧源203からの電圧を、抵抗201、抵抗202によって分圧し、入力端子27から入力されるコントロール信号によってスイッチ203を制御して、2段階の電圧の内適切なゲート電圧に切り替えて出力端子28から出力する。

具体的には、スイッチ203が直流電圧源205側に切り替えられると、AB級に対応した電圧が出力され、スイッチ203が分圧側に切り替えられるとC級に対応した電圧が出力されて、増幅器23にゲート電圧として供給される。

【0041】

そして、電源回路26では、入力端子27からコンパレータ104の出力が入力された場合(搬送波がある場合)には、スイッチ203を電源電圧側に切り替えて、AB級のゲート電圧を供給し、入力端子27からの入力がない場合には、スイッチ203を分圧側に切り替えてC級のゲート電圧を供給する。

【0042】

[増幅器23のゲート電圧の例:図5]

ここで、増幅器23に供給されるゲート電圧波形の例について図5を用いて説明する。図5は、増幅器23に供給されるゲート電圧波形の例を示す説明図である。

図5に示すように、増幅器23のゲート電圧波形210は、AB級バイアスである電圧H−VGSと、C級バイアスである電圧L−VGSを切り替えることによって生成される。

【0043】

つまり、コンパレータ104の出力信号(搬送波)17が存在する時間は、増幅器23のゲート電圧は電圧H−VGSとなってAB級で動作し、コンパレータ104の出力信号17がない時間は、ゲート電圧は電圧L−VGSとなってC級で動作する。

これにより、後述するように、増幅器23が増幅動作を行っていない場合のインピーダンスを開放にして、低損失とすることができるものである。

【0044】

[信号合成部3:図6,7,8]

次に、本電力増幅装置の特徴部分である信号合成部3について図6〜8を用いて説明する。図6〜8は、信号合成部3の構成及び合成の動作を示す説明図であり、図6は、増幅器21が信号を出力している場合の信号合成例を示し、図7は、増幅器22が信号を出力している場合の信号合成例を示し、図8は、増幅器23が信号を出力している場合の信号合成例を示している。

本電力増幅装置の信号合成部3は、増幅部2の3つの増幅器21,22,23の内、一つの増幅器が信号を出力している場合には、他の増幅器からの出力はないという条件で、低損失に合成する機能を有するものである。

【0045】

[信号合成部3の構成]

図6に示すように、信号合成部3は、入力端子31,32,33と、位相調整線路301,302,303と、合成点305と、出力線路304とを備えている。

入力端子31,32,33は、それぞれ、増幅器21,22,23からの信号を入力する。

位相調整線路301,302,303は、それぞれ、入力端子31,32,33からの信号の位相を調整する。

合成点305は、位相調整線路301,302,303からの信号を合成する。

出力線路304は、出力端子4に出力する増幅器出力のインピーダンスを調整する。

【0046】

[信号合成部3の動作]

次に、信号合成部3における合成の動作について図6〜8を用いて具体的に説明する。まず、本電力増幅装置における動作の前提について説明する。

増幅器21〜23は、時間分割された分割波形15〜17を増幅するため、1つの増幅器が増幅動作を行っている場合は他の2つの増幅器は増幅動作していない。

また、ここでは、増幅器21〜23は、増幅動作をしている場合には、出力インピーダンスが50Ohmとなるよう、増幅器内部の出力整合回路が調整されている。尚、ここでは、増幅器21〜23の出力インピーダンスを50Ohmとしているが、これに限るものではない。

【0047】

増幅器21,22はC級増幅器であり、また、増幅器23は、上述した電源回路26によるゲート電圧制御に基づいて、AB級又はC級動作を行う。

位相調整線路301,302,303の特性インピーダンスは、それぞれ50Ohmである。

また、出力線路304の特性インピーダンスも増幅器の出力インピーダンスと同じく、50Ohmとしている。

【0048】

[増幅器21が信号を出力している場合のインピーダンス:図6、図9]

[増幅器21のインピーダンス]

上述した前提条件を踏まえ、増幅器21が信号を出力している場合の、合成点305から各増幅器を見たインピーダンスについて図6及び図9を用いて説明する。

図9は、増幅器21が信号を出力している場合のインピーダンスを示すスミスチャートである。

入力端子31から位相調整線路301を見たインピーダンスをZin、位相調整線路301の特性インピーダンスをZ0、位相調整線路301の電気長をθ、出力線路304の特性インピーダンスをZLとすると、Zinは(式1)で表される。

【0049】

【数1】

【0050】

位相調整線路301と出力線路304の特性インピーダンスは等しく、共に50Ohmなので、θの値を変えても、Zin=Z0=ZL=50Ohmとなる。

よって、増幅器21が動作している場合、位相調整線路301の長さに関わらず、入力端子31から見た負荷インピーダンス(図6ではZt1)は50Ohmとなる。

同様に、合成点305から増幅器21を見たインピーダンスも50Ohmとなる。

また、入力端子31、合成点305のインピーダンスをスミスチャートに示すと、図9のインピーダンス306となる。

【0051】

[増幅器22のインピーダンス:図4、図9]

次に、増幅器21が信号を出力している場合の増幅器22のインピーダンスについて説明する。

増幅器21が信号を出力している場合、C級にバイアスされた増幅器22は信号を出力しておらず、ドレイン電流がほとんど流れていないため、増幅素子出力端でのインピーダンスは理想的には無限大(∞)となる。

しかし、増幅素子の内部抵抗や整合回路により、実際の出力インピーダンスは無限大にはならない。そのため、入力端子32から増幅器22を見たインピーダンスは、図9のインピーダンス309となる。

【0052】

ここで、合成点305から増幅動作をしていない増幅器22を見たインピーダンスを算出する。

合成点305のインピーダンスをZinとし、位相調整線路302の特性インピーダンスをZ0、位相調整線路302の電気長をθ、入力端子32から増幅器22を見たインピーダンス(インピーダンス309)をZLとすると、(式1)より、Zinは、位相調整線路302の長さを変えることにより変化する。

【0053】

すなわち、合成点305から増幅器22を見たインピーダンスは、図9のインピーダンス309から伸びた破線のように回る。

インピーダンス309がインピーダンス310となるよう位相調整線路302の電気長を調整し、後述する(式2)を用いて合成点305での反射係数Γrを計算する。

【0054】

合成点305で観測されるインピーダンスをZout、合成点305から増幅器22をみたインピーダンスをZrとすると、反射係数Γrは以下のように表される。

【数2】

【0055】

合成点305で観測されるインピーダンスは、上述したように50Ohmであり、インピーダンス310はハイインピーダンスであって、Zoutに比べて十分大きいため、反射係数Γrは、Γr≒+1となる。

つまり、本増幅装置では、位相調整線路302の電気長を調整することにより、増幅器22が信号を出力していない場合、合成点305から増幅器22を見たインピーダンスを開放とするものである。

図6ではZr2=∞と表している。

【0056】

[増幅器23のインピーダンス:図4、図9]

次に、増幅器21が信号を出力している場合の増幅器23のインピーダンスについて説明する。

AB級に設定された増幅器23では、C級と違って、信号を出力していない場合でもドレイン電流が流れている。

入力端子33から増幅器23を見たインピーダンスは、図9のインピーダンス307となる。増幅器22と同様に合成点305で開放とするため、位相調整線路303の電気長を調整すると、インピーダンス307からインピーダンス308に伸びた破線のようにまわり、ハイインピーダンスとはならないので、合成点305から増幅器21を見たインピーダンスは開放とならない。

【0057】

そこで、本電力増幅装置では、上述したように、電源回路26で増幅器23のゲート電圧を制御して、動作していない時はC級に設定するようにしている。

増幅器23をC級とすることで、増幅器22の場合と同様に、位相調整線路303の電気長を調整することによって、インピーダンス310に調整することが可能となり、合成点305から動作していない増幅器23を見たインピーダンスは開放となる。図6ではZr3=∞と表している。

【0058】

[負荷の反射係数]

上述した各増幅器のインピーダンスを踏まえ、増幅器21が増幅動作を行っている場合の負荷の反射係数を算出する。

増幅器21が増幅動作している場合の出力インピーダンスをZout、入力端子31から出力端子4までの負荷インピーダンスをZrとして、負荷の反射係数Γrを(式2)を用いて算出する。

【0059】

上述したように、増幅器22、23は、合成点305で開放となるので接続されていないものとみなすと、Zout=Zr=50Ohmとなるため、(式2)より、反射係数は、

Γr=0となる。

よって、増幅器21の出力信号は、入力端子31、位相調整線路301、合成点305、出力線路304を損失なく通過して、出力端子4に入力されることになる。

【0060】

[増幅器22が信号を出力している場合:図7]

増幅器22が増幅動作を行う場合には、図7に示すように、合成点305から見た増幅器21,23のインピーダンスは開放となる(Zr1=∞,Zr3=∞)ので、増幅器22のみが接続されているとみなすことができる。

よって、図6の場合と同様に、入力端子32から出力端子4までの負荷インピーダンスは増幅器22の出力インピーダンスと同じ50Ohm(Zt2=50Ohm)となり、信号合成部3に入力された増幅信号は、損失なく出力端子4に入力される。

【0061】

[増幅器23が信号を出力している場合:図8]

同様に、増幅器23が増幅動作を行う場合には、図8に示すように、合成点305から見た増幅器21,22のインピーダンスは開放(Zr1=∞,Zr2=∞)、入力端子33から出力端子4までの負荷インピーダンスは、増幅器23の出力インピーダンスと等しい50Ohmとなり(Zt3=50Ohm)、増幅信号は損失なく出力端子4に入力される。

【0062】

すなわち、本電力増幅装置では、入力信号の信号レベルに応じて、当該信号レベルで飽和に近い動作を行う増幅器が増幅動作を行い、図6,7,8のいずれかの状態で合成が行われるため、合成による損失はなく、動作している増幅器で増幅された信号は低損失で出力され、高効率の電力増幅装置を実現することができるものである。

理想的には、位相調整線路301〜303と出力線路304の通過損失のみが合成損失となるため、低損失での合成が可能となる。

【0063】

[実施の形態の効果]

本発明の実施の形態に係る電力増幅装置によれば、異なる入力レベルの信号を飽和に近い動作で増幅する複数の増幅器21,22,23と、入力信号を信号レベルに応じて適切な増幅器に出力する信号分割処理部1と、各増幅器からの出力を合成する信号合成部3とを備え、信号合成部3が、増幅器21,22,23の出力信号の位相を調整する位相調整線路301,302,303と、位相調整線路301,302,303からの出力を合成する合成点305と、合成点305からの出力のインピーダンスを調整する出力線路304とを備え、増幅器21,22,23の出力インピーダンスを同一の値とすると共に、位相調整線路301,302,303及び出力線路304の特性インピーダンスを増幅器の出力インピーダンスと同一の値としておき、合成点305におけるインピーダンスが、動作していない増幅器に対して開放となるよう位相調整線路301,302,303の電気長が調整され、動作している増幅器に対して増幅器の出力インピーダンスとなるよう出力線路304の電気長が調整されているので、各増幅器21〜23が常に飽和に近い動作を行うと共に、信号合成部が各増幅器21〜23からの出力を線路上で低損失で合成して、PAPRの大きい信号であっても高効率で増幅して合成することができ、増幅器全体の電力変換効率を向上させることができる効果がある。

【産業上の利用可能性】

【0064】

本発明は、平均電力に対するピーク電力の比が高い信号を増幅する際の電力変換効率を向上させることができる電力増幅装置に適している。

【符号の説明】

【0065】

1...信号分割処理部、 2...増幅部、 3...信号合成部、 4,18...出力端子、 10,27,31,32,33...入力端子、 21,22,23...増幅器、 24,25...電源、 26...電源回路、 28...ゲート電圧制御端子、 29...電源供給端子、 11,12,13...分配出力端子、 14...変調信号波形、 15,16,17...分割信号波形、 102...ディバイダ、 103...検波器、 104,105,106,107...コンパレータ、 108...AND回路、 109,110,111...スイッチ、 112...信号波形、 113,114,115...位相振幅調整回路、 201,202...抵抗、 203...スイッチ、 204,205...直流電圧源、 210...ゲート電圧波形、 301,302,303...位相調整線路、 304...出力線路、 305...合成点、 306,307,308,309,310...インピーダンス

【特許請求の範囲】

【請求項1】

高周波信号を増幅する電力増幅装置であって、

互いに異なる電力レベルの信号を入力し、前記入力された信号を飽和に近い状態でそれぞれ増幅する複数の増幅器と、

入力信号を信号レベルに応じて前記複数の増幅器のいずれかに出力する信号分割処理部と、

前記各増幅器に対応して設けられ、前記対応する増幅器からの出力信号の位相を調整する複数の位相調整線路と、前記複数の位相調整線路からの出力を合成する合成点と、前記合成点からの出力のインピーダンスを調整する出力線路とを有する信号合成部と備え、

前記複数の増幅器の出力インピーダンスを同一の値とし、

前記複数の位相調整線路と、前記出力線路の特性インピーダンスを前記増幅器の出力インピーダンスと同一の値とし、

前記位相調整回路のインピーダンスが、前記対応する増幅器が動作していない場合に前記合成点における当該増幅器のインピーダンスを開放とするよう調整され、

前記出力線路のインピーダンスが、動作している増幅器の前記合成点におけるインピーダンスを前記増幅器の出力インピーダンスとするよう調整されていることを特徴とする電力増幅装置。

【請求項1】

高周波信号を増幅する電力増幅装置であって、

互いに異なる電力レベルの信号を入力し、前記入力された信号を飽和に近い状態でそれぞれ増幅する複数の増幅器と、

入力信号を信号レベルに応じて前記複数の増幅器のいずれかに出力する信号分割処理部と、

前記各増幅器に対応して設けられ、前記対応する増幅器からの出力信号の位相を調整する複数の位相調整線路と、前記複数の位相調整線路からの出力を合成する合成点と、前記合成点からの出力のインピーダンスを調整する出力線路とを有する信号合成部と備え、

前記複数の増幅器の出力インピーダンスを同一の値とし、

前記複数の位相調整線路と、前記出力線路の特性インピーダンスを前記増幅器の出力インピーダンスと同一の値とし、

前記位相調整回路のインピーダンスが、前記対応する増幅器が動作していない場合に前記合成点における当該増幅器のインピーダンスを開放とするよう調整され、

前記出力線路のインピーダンスが、動作している増幅器の前記合成点におけるインピーダンスを前記増幅器の出力インピーダンスとするよう調整されていることを特徴とする電力増幅装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−110487(P2013−110487A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−252287(P2011−252287)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000001122)株式会社日立国際電気 (5,007)

【出願人】(504173471)国立大学法人北海道大学 (971)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000001122)株式会社日立国際電気 (5,007)

【出願人】(504173471)国立大学法人北海道大学 (971)

【Fターム(参考)】

[ Back to top ]