電源故障検出回路および電源故障検出方法

【課題】電源回路がショート状態になる故障が発生しても、入力電圧がそのまま負荷側に出力されることを確実に防止可能な電源故障検出回路を提供する。

【解決手段】前置直列スイッチング素子Q1と前置並列スイッチング素子Q2とチョークコイルL1と平滑コンデンサC1とを少なくとも備えている降圧型のDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出回路として、負荷側へ出力する出力線に直列接続した後置直列スイッチング素子Q3と、前置直列スイッチング素子Q1に流れ込む入力電流値を電流検出回路IDETによって測定した結果と前置直列スイッチング素子Q1の両端に掛かる電圧値を電圧検出回路VDETによって測定した結果とに基づいて前置直列スイッチング素子Q1の故障の前兆を検出する故障検出回路Z2とを備え、故障検出回路Z2の検出結果に基づいて、後置スイッチング素子Q3のオンオフを制御する。

【解決手段】前置直列スイッチング素子Q1と前置並列スイッチング素子Q2とチョークコイルL1と平滑コンデンサC1とを少なくとも備えている降圧型のDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出回路として、負荷側へ出力する出力線に直列接続した後置直列スイッチング素子Q3と、前置直列スイッチング素子Q1に流れ込む入力電流値を電流検出回路IDETによって測定した結果と前置直列スイッチング素子Q1の両端に掛かる電圧値を電圧検出回路VDETによって測定した結果とに基づいて前置直列スイッチング素子Q1の故障の前兆を検出する故障検出回路Z2とを備え、故障検出回路Z2の検出結果に基づいて、後置スイッチング素子Q3のオンオフを制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源故障検出回路および電源故障検出方法に関し、特に、降圧型のDC−DCコンバータからなる電源回路の故障発生時において入力電圧がそのまま負荷側に出力されてしまうことを防止可能とする電源故障検出回路および電源故障検出方法に関する。

【背景技術】

【0002】

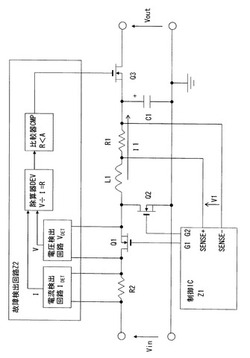

図3は、特許文献1の特開平09−284994号公報「過電圧保護回路」等に記載されている従来の電源故障検出回路の回路構成を示している。図3において、電源回路は、直並列接続したFET(Field Effect Transistor)からなる直列スイッチング素子Q1、並列スイッチング素子Q2を制御IC回路Z1により制御することにより、入力電圧Vinを、チョーククコイルL1と平滑コンデンサC1とを介して、所望の出力電圧Voutとして負荷側に出力するように構成されている。

【0003】

つまり、制御IC回路Z1は、所望の出力電圧Voutを生成するために必要とするスイッチングパルスを生成して、端子G1、G2ピンそれぞれから直列スイッチング素子Q1、並列スイッチング素子Q2それぞれを構成するFETのゲートに出力することにより、直列スイッチング素子Q1、並列スイッチング素子Q2のオン、オフ動作を制御している。

【0004】

ここで、電源回路に過電流が発生する故障を検出するために、チョーククコイルL1の後段に電流検出抵抗R1を直列接続しており、電流検出抵抗R1の両端には、当該電源回路に流れる電源電流I1に比例した検出電圧V1が発生し、発生した検出電圧V1は、制御IC回路Z1のセンス端子SENSE+、SENSE−ピン間の電圧として、制御IC回路Z1にフィードバックされるように構成されている。

【0005】

制御IC回路Z1は、センス端子SENSE+、SENSE−ピンにフィードバックされてくる検出電圧V1を常時監視していて、過電流検出用としてあらかじめ定めた電圧閾値以上の電圧値になったことを検出すると、過電流が流れる故障が発生したものと判定して、制御IC回路Z1の過電流保護機能が働いて、スイッチングパルスの生成動作を停止する。その結果、端子G1、G2ピンから直列スイッチング素子Q1、並列スイッチング素子Q2それぞれに出力されていたスイッチングパルスによる直列スイッチング素子Q1、並列スイッチング素子Q2のオンオフ動作が停止し、直列スイッチング素子Q1はオフ状態(開放状態)、並列スイッチング素子Q2はオン状態(閉成状態)を継続する状態になる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平09−284994号公報(第3−4頁)

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、図3に示したような従来の電源故障検出回路の場合、次のような課題がある。すなわち、直列スイッチング素子Q1のFETの故障が発生してから、電流検出抵抗R1の両端の検出電圧V1の検出結果に基づいて制御IC回路Z1内の過電流保護機能が動作するまでの動作速度が遅いために、TOP側に位置する直列スイッチング素子Q1のFETがショート故障していた場合には、入力電圧Vinが即時に出力電圧Voutとして負荷側に出力されてしまう可能性があり、電源回路を降圧型DC−DCコンバータとして構成していた場合においては、負荷側の回路素子を破損してしまう事態を招いてしまう可能性がある。

【0008】

(本発明の目的)

本発明は、かかる課題に鑑みてなされたものであり、電源回路がショート状態になる故障が発生しても、入力電圧がそのまま負荷側に出力されることを確実に防止することが可能な電源故障検出回路および電源故障検出方法を提供することを、その目的としている。

【課題を解決するための手段】

【0009】

前述の課題を解決するため、本発明による電源故障検出回路および電源故障検出方法は、主に、次のような特徴的な構成を採用している。

【0010】

(1)本発明による電源故障検出回路は、前置直列スイッチング素子と前置並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出回路であって、前記負荷側へ出力する出力線に直列接続した後置直列スイッチング素子と、前記前置直列スイッチング素子に流れ込む入力電流と前記前置直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記前置直列スイッチング素子の故障の前兆を検出する故障検出回路とを、さらに備え、前記故障検出回路の検出結果に基づいて、前記後置スイッチング素子のオンオフを制御することを特徴とする。

【0011】

(2)本発明による電源故障検出方法は、直列スイッチング素子と並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出方法であって、前記直列スイッチング素子に流れ込む入力電流と前記直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記直列スイッチング素子の故障の前兆を検出して、前記負荷側への出力の可否を制御することを特徴とする。

【発明の効果】

【0012】

本発明の電源故障検出回路および電源故障検出方法によれば、以下のような効果を奏することができる。

【0013】

すなわち、入力側のTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)に故障が発生して、該直列スイッチング素子(前置直列スイッチング素子)の抵抗値が正常動作時における許容範囲内を示す抵抗値としてあらかじめ定めた抵抗値閾値よりも低下したことを検出した際に、該直列スイッチング素子(前置直列スイッチング素子)の故障が発生する前兆と看做して、直ちに、負荷側への出力遮断用として出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子をオフ(開放)させることにより、入力側のTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)が完全にショート状態になる前に、入力電圧がそのまま負荷側へ出力してしまうことを事前にかつ確実に遮断することができる。

【0014】

而して、電源回路が降圧型DC−DCコンバータとして構成されているような場合であっても、電源回路の故障時に、高い入力電圧が電圧降下することなくそのまま負荷側の回路素子に印加されてしまう事態が発生することはなく、負荷側の回路素子が破損することを確実に防ぐことができる。

【図面の簡単な説明】

【0015】

【図1】本発明による電源故障検出回路の回路構成の一例を示す回路構成図である。

【図2】本発明による電源故障検出回路の回路構成の他の例を示す回路構成図である。

【図3】従来の電源故障検出回路の回路構成を示す回路構成図である。

【発明を実施するための形態】

【0016】

以下、本発明による電源故障検出回路および電源故障検出方法の好適な実施形態について添付図を参照して説明する。

【0017】

(本発明の特徴)

本発明の実施形態の説明に先立って、本発明の特徴についてその概要をまず説明する。本発明による電源故障検出回路および電源故障検出方法は、入力側のTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)に流れる電流と該直列スイッチング素子(前置直列スイッチング素子)の両端にかかる電圧とを観測することにより得られる、該直列スイッチング素子(前置直列スイッチング素子)の抵抗値が、正常動作時の許容範囲内の抵抗値としてあらかじめ定めた抵抗値閾値よりも低下したことを検知した際に、故障発生の前兆と看做して、直ちに、負荷側への出力を遮断する故障検出回路を備え、故障によりTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)が完全なショート状態に陥る前に、入力電圧がそのまま負荷側へ出力されることを事前に防止することを可能にすることを主要な特徴としている。

【0018】

つまり、本発明は、電源回路において、入力側のTOP側に位置している前置直列スイッチング素子を構成する例えばFET(Field Effect Transistor)のドレイン−ソース間の抵抗値が、通常の許容範囲内の抵抗値すなわち抵抗値閾値よりも少しでも低下したことを検出した場合、ショート状態の故障が発生する前兆であると看做して、出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子を直ちに強制的にオフすることによって、入力電圧がそのまま負荷側に出力することを事前に防止する故障検出回路を備えることを主要な特徴としている。

【0019】

ここで、電源回路が、高い電圧値の入力電圧を低下させて負荷側に供給する降圧型DC−DCコンバータからなる電源回路に特に効果的であり、電源回路の故障により、高い入力電圧がそのまま負荷側に出力されて、負荷側の回路素子が破損してしまう事態が生じることを確実に防止することを可能にしている。

【0020】

(実施形態の構成例)

次に、本発明による電源故障検出回路の回路構成の一例について、図1を用いて説明する。図1は、本発明による電源故障検出回路の回路構成の一例を示す回路構成図であり、図3に示した電源回路と同様のDC−DCコンバータからなる電源回路においてショート故障を事前に検出して負荷側への出力を遮断する回路構成例を示しており、図3の電源回路と同じ機能を有する部位には、図3と同じ符号を付して示している。

【0021】

つまり、図1に示す電源回路は、図3の電源回路と同様、入力側のTOP側に位置する直並列接続したFET(Field Effect Transistor)からなる前置直列スイッチング素子Q1、前置並列スイッチング素子Q2を、制御IC回路Z1の端子G1、G2ピンそれぞれから出力されるスイッチングパルスによりスイッチング制御することにより、入力電圧Vinを、チョーククコイルL1と平滑コンデンサC1とを介して、所望の出力電圧Voutとして負荷側に出力するように構成されている。

【0022】

ここで、図1に示す電源回路においても、図3の電源回路と同様、電源回路に過電流が発生する故障を検出するために、チョーククコイルL1の後段に電流検出抵抗R1を直列接続しており、電流検出抵抗R1の両端には、当該電源回路に流れる電源電流I1に比例した検出電圧V1が発生し、発生した検出電圧V1は、制御IC回路Z1のセンス端子SENSE+、SENSE−ピン間の電圧として、制御IC回路Z1にフィードバックされるように構成されている。

【0023】

制御IC回路Z1は、図3の電源回路と同様、センス端子SENSE+、SENSE−ピンにフィードバックされてくる検出電圧V1を常時監視していて、過電流検出用としてあらかじめ定めた電圧閾値以上の電圧値になったことを検出すると、過電流が流れる故障が発生したものと判定して、制御IC回路Z1の過電流保護機能が働いて、スイッチングパルスの生成動作を停止する。その結果、端子G1、G2ピンから前置直列スイッチング素子Q1、前置並列スイッチング素子Q2それぞれに出力されていたスイッチングパルスによる前置直列スイッチング素子Q1、並列スイッチング素子Q2のオンオフ動作が停止し、前置直列スイッチング素子Q1はオフ状態(開放状態)、前置並列スイッチング素子Q2はオン状態(閉成状態)を継続する状態になる。

【0024】

さらに、図1に示す電源回路においては、故障発生時における制御IC回路Z1による出力停止動作の遅さを補うために、当該電源回路のショート故障の発生を事前に検出する故障検出回路Z2が制御IC回路Z1とは別個に備えられている。そして、入力側のTOP側に位置している前置直列スイッチング素子Q1の前段に、前置直列スイッチング素子Q1に流れ込む入力電流の入力電流値Iを検出するための入力電流検出抵抗R2が直列接続されるとともに、出力側のBOTTOM側の電流検出抵抗R1と平滑コンデンサC1との接続点と出力端子との間には、負荷側への出力を遮断するための後置直列スイッチング素子Q3が直列接続されている。ここで、本実施形態においては、後置直列スイッチング素子Q3も、前置直列スイッチング素子Q1、前置並列スイッチング素子Q2と同様、FETを用いて構成している。

【0025】

故障検出回路Z2は、電流検出回路IDET、電圧検出回路VDET、除算器DEV、比較器CMPを少なくとも含んで構成されている。電流検出回路IDETは、前置直列スイッチング素子Q1の前段に直列接続されている入力電流検出抵抗R2の両端の電圧を引き込むことにより、入力端子から前置直列スイッチング素子Q1に流れ込む入力電流値Iを検出する。電圧検出回路VDETは、前置直列スイッチング素子Q1のドレイン、ソースそれぞれの電圧を引き込むことにより、前置直列スイッチング素子Q1のドレイン−ソース間の電圧値Vを検出する。

【0026】

除算器DEVは、電流検出回路IDETが検出した入力電流値Iと電圧検出回路VDETが検出した前置直列スイッチング素子Q1のドレイン、ソース間の電圧値Vとを入力して、(V/I=R)の除算演算を行い、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rを算出する。比較器CMPは、除算器DEVによって算出された前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが、正常動作時の許容範囲内を示す抵抗値としてあらかじめ定めた抵抗値閾値Aと比較して、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが抵抗値閾値Aよりも低下したことを検出した場合は、前置直列スイッチング素子Q1がショート故障に陥る前兆であるものと看做して、出力側のBOTTOM側に直列接続されている後置直列スイッチング素子Q3を開放(オフ)して、負荷側への出力を遮断する。

【0027】

(実施形態の動作の説明)

次に、図1に示した電源故障検出回路の動作の一例についてさらに詳細に説明する。図1の電源故障検出回路においては、故障検出回路Z2により前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rの変化を常時監視していて、該抵抗値Rが、正常動作時の許容範囲内の抵抗値すなわち抵抗値閾値Aよりも少しでも低下したことを検出した場合には、電源回路のショート状態の故障が発生する前兆であると看做して、出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子Q3を直ちに強制的にオフ(開放)することによって、出力側との接続を遮断して、入力電圧がそのまま負荷側に出力することを事前に防止している。

【0028】

すなわち、入力電圧Vinが印加された入力端子から流れ込んでくる入力電流の電流値を検出するために入力側のTOP側に直列接続した入力電流検出抵抗R2の両端の電圧を、故障検出回路Z2の電流検出回路IDETに引き込むことにより、電流検出回路IDETにおいて入力電流値Iを常時検出している。同時に、入力電流検出抵抗R2の後段に直列接続されている前置直列スイッチング素子Q1のドレインの電圧とソースの電圧との双方の電圧を、故障検出回路Z2の電圧検出回路VDETに引き込むことにより、電圧検出回路VDETにおいて前置直列スイッチング素子Q1のドレイン−ソース間の電圧値Vを常時検出している。

【0029】

電流検出回路IDETが検出した入力電流値Iと電圧検出回路VDETが検出した前置直列スイッチング素子Q1のドレイン−ソース間の電圧値Vとは、故障検出回路Z2の除算器DEVに入力され、除算器DEVにおいて、(V/I=R)の除算が行われることによって、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが直ちに算出される。除算器DEVによって算出された前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rは、故障検出回路Z2の比較器CMPにおいてあらかじめ定めた抵抗値閾値Aと比較され、該抵抗値閾値Aよりも少しでも低いと判定された場合には、前記直列スイッチング素子Q1のショート故障が発生する前兆であるものと看做して、直ちに、OFF信号(LOW)がFETからなる後置直列スイッチング素子Q3のゲート端子に印加される。

【0030】

この結果、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが抵抗値閾値Aよりも少しでも低下したことを検知すると、瞬時に、出力側のBOTTOM側に直列接続されている後置直列スイッチング素子Q3はオン状態からオフ状態に切り替わり、出力側との接続を遮断する。而して、しかる後に、たとえ、前置直列スイッチング素子Q1が完全なショート状態に陥ったとしても、入力電圧Vinがそのまま負荷側に出力される事態が発生することを事前に確実に防止することができる。

【0031】

なお、図1に示す電源故障検出回路においては、入力電流の電流値を検出するために、TOP側の入力側に入力電流検出抵抗R2を直列接続している場合について示したが、本発明は、かかる場合のみに限るものではない。例えば、図2に示すように、入力電流検出抵抗R2の代わりにカレントトランスCT1を用いて構成するようにしても良い。図2は、本発明による電源故障検出回路の回路構成の他の例を示す回路構成図であり、図1における入力電流検出抵抗R2の代わりにカレントトランスCT1を用いて構成している構成例を示している。

【0032】

図2のような回路構成にして、入力電流検出抵抗R2の代わりにカレントトランスCT1を用いて入力電流を検出することにすれば、入力電流検出抵抗R2において発生していた電力損失を低減することが可能になるという効果が得られる。

【0033】

また、図1に示す電源故障検出回路において、前置直列スイッチング素子Q1、前置並列スイッチング素子Q2、後置直列スイッチング素子Q3を、FETを用いて構成する場合について説明したが、本発明は、かかる前置直列スイッチング素子Q1、前置並列スイッチング素子Q2、後置直列スイッチング素子Q3を、MOSFET(Metal Oxide Semiconductor Field Effect Transistor:金属酸化物半導体電界効果トランジスタ)のみならず、IGBT(Insulated Gate Bipolar Transistor:絶縁型ゲート・バイポーラトランジスタ)や、場合によっては、MEMS(Micro ElectroMechanical Systems)型スイッチング素子を用いて構成するようにしても良い。

【0034】

(本実施形態の効果の説明)

以上に詳細に説明したように、本実施形態においては、以下に記載するような効果が得られる。

【0035】

すなわち、入力側のTOP側に位置する前置直列スイッチング素子Q1を構成するFETに故障が発生して、前置直列スイッチング素子Q1としてのFETのドレイン−ソース間の抵抗値Rが正常動作時における許容範囲内を示す抵抗値としてあらかじめ定めた抵抗値閾値Aよりも低下したことを検出した際に、直ちに、負荷側への出力遮断用として出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子Q3をオフ(開放)させることにより、前置直列スイッチング素子Q1が完全にショート状態になる前に、入力電圧Vinがそのまま負荷側へ出力してしまうことを事前にかつ確実に遮断することができる。

【0036】

而して、電源回路が降圧型DC−DCコンバータとして構成されているような場合であっても、電源回路の故障時に、高い入力電圧Vinが電圧降下することなくそのまま負荷側の回路素子に印加されてしまう事態が発生することはなく、負荷側の回路素子が破損することを確実に防ぐことができる。

【0037】

以上、本発明の好適な実施形態の構成を説明した。しかし、かかる実施形態は、本発明の単なる例示に過ぎず、何ら本発明を限定するものではないことに留意されたい。本発明の要旨を逸脱することなく、特定用途に応じて種々の変形変更が可能であることが、当業者には容易に理解できよう。

【符号の説明】

【0038】

A 抵抗値閾値

C1 平滑コンデンサ

CMP 比較器

CT1 カレントトランス

DEV 除算器

G1 端子

G2 端子

I 入力電流値

I1 電源電流

IDET 電流検出回路

L1 チョーククコイル

Q1 直列スイッチング素子(前置直列スイッチング素子)

Q2 並列スイッチング素子(前置並列スイッチング素子)

Q3 後置直列スイッチング素子

R 抵抗値

R1 電流検出抵抗

R2 入力電流検出抵抗

SENSE+ センス端子

SENSE− センス端子

V 電圧値

Vin 入力電圧

Vout 出力電圧

V1 検出電圧

VDET 電圧検出回路

Z1 制御IC回路

Z2 故障検出回路

【技術分野】

【0001】

本発明は、電源故障検出回路および電源故障検出方法に関し、特に、降圧型のDC−DCコンバータからなる電源回路の故障発生時において入力電圧がそのまま負荷側に出力されてしまうことを防止可能とする電源故障検出回路および電源故障検出方法に関する。

【背景技術】

【0002】

図3は、特許文献1の特開平09−284994号公報「過電圧保護回路」等に記載されている従来の電源故障検出回路の回路構成を示している。図3において、電源回路は、直並列接続したFET(Field Effect Transistor)からなる直列スイッチング素子Q1、並列スイッチング素子Q2を制御IC回路Z1により制御することにより、入力電圧Vinを、チョーククコイルL1と平滑コンデンサC1とを介して、所望の出力電圧Voutとして負荷側に出力するように構成されている。

【0003】

つまり、制御IC回路Z1は、所望の出力電圧Voutを生成するために必要とするスイッチングパルスを生成して、端子G1、G2ピンそれぞれから直列スイッチング素子Q1、並列スイッチング素子Q2それぞれを構成するFETのゲートに出力することにより、直列スイッチング素子Q1、並列スイッチング素子Q2のオン、オフ動作を制御している。

【0004】

ここで、電源回路に過電流が発生する故障を検出するために、チョーククコイルL1の後段に電流検出抵抗R1を直列接続しており、電流検出抵抗R1の両端には、当該電源回路に流れる電源電流I1に比例した検出電圧V1が発生し、発生した検出電圧V1は、制御IC回路Z1のセンス端子SENSE+、SENSE−ピン間の電圧として、制御IC回路Z1にフィードバックされるように構成されている。

【0005】

制御IC回路Z1は、センス端子SENSE+、SENSE−ピンにフィードバックされてくる検出電圧V1を常時監視していて、過電流検出用としてあらかじめ定めた電圧閾値以上の電圧値になったことを検出すると、過電流が流れる故障が発生したものと判定して、制御IC回路Z1の過電流保護機能が働いて、スイッチングパルスの生成動作を停止する。その結果、端子G1、G2ピンから直列スイッチング素子Q1、並列スイッチング素子Q2それぞれに出力されていたスイッチングパルスによる直列スイッチング素子Q1、並列スイッチング素子Q2のオンオフ動作が停止し、直列スイッチング素子Q1はオフ状態(開放状態)、並列スイッチング素子Q2はオン状態(閉成状態)を継続する状態になる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平09−284994号公報(第3−4頁)

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、図3に示したような従来の電源故障検出回路の場合、次のような課題がある。すなわち、直列スイッチング素子Q1のFETの故障が発生してから、電流検出抵抗R1の両端の検出電圧V1の検出結果に基づいて制御IC回路Z1内の過電流保護機能が動作するまでの動作速度が遅いために、TOP側に位置する直列スイッチング素子Q1のFETがショート故障していた場合には、入力電圧Vinが即時に出力電圧Voutとして負荷側に出力されてしまう可能性があり、電源回路を降圧型DC−DCコンバータとして構成していた場合においては、負荷側の回路素子を破損してしまう事態を招いてしまう可能性がある。

【0008】

(本発明の目的)

本発明は、かかる課題に鑑みてなされたものであり、電源回路がショート状態になる故障が発生しても、入力電圧がそのまま負荷側に出力されることを確実に防止することが可能な電源故障検出回路および電源故障検出方法を提供することを、その目的としている。

【課題を解決するための手段】

【0009】

前述の課題を解決するため、本発明による電源故障検出回路および電源故障検出方法は、主に、次のような特徴的な構成を採用している。

【0010】

(1)本発明による電源故障検出回路は、前置直列スイッチング素子と前置並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出回路であって、前記負荷側へ出力する出力線に直列接続した後置直列スイッチング素子と、前記前置直列スイッチング素子に流れ込む入力電流と前記前置直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記前置直列スイッチング素子の故障の前兆を検出する故障検出回路とを、さらに備え、前記故障検出回路の検出結果に基づいて、前記後置スイッチング素子のオンオフを制御することを特徴とする。

【0011】

(2)本発明による電源故障検出方法は、直列スイッチング素子と並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出方法であって、前記直列スイッチング素子に流れ込む入力電流と前記直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記直列スイッチング素子の故障の前兆を検出して、前記負荷側への出力の可否を制御することを特徴とする。

【発明の効果】

【0012】

本発明の電源故障検出回路および電源故障検出方法によれば、以下のような効果を奏することができる。

【0013】

すなわち、入力側のTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)に故障が発生して、該直列スイッチング素子(前置直列スイッチング素子)の抵抗値が正常動作時における許容範囲内を示す抵抗値としてあらかじめ定めた抵抗値閾値よりも低下したことを検出した際に、該直列スイッチング素子(前置直列スイッチング素子)の故障が発生する前兆と看做して、直ちに、負荷側への出力遮断用として出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子をオフ(開放)させることにより、入力側のTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)が完全にショート状態になる前に、入力電圧がそのまま負荷側へ出力してしまうことを事前にかつ確実に遮断することができる。

【0014】

而して、電源回路が降圧型DC−DCコンバータとして構成されているような場合であっても、電源回路の故障時に、高い入力電圧が電圧降下することなくそのまま負荷側の回路素子に印加されてしまう事態が発生することはなく、負荷側の回路素子が破損することを確実に防ぐことができる。

【図面の簡単な説明】

【0015】

【図1】本発明による電源故障検出回路の回路構成の一例を示す回路構成図である。

【図2】本発明による電源故障検出回路の回路構成の他の例を示す回路構成図である。

【図3】従来の電源故障検出回路の回路構成を示す回路構成図である。

【発明を実施するための形態】

【0016】

以下、本発明による電源故障検出回路および電源故障検出方法の好適な実施形態について添付図を参照して説明する。

【0017】

(本発明の特徴)

本発明の実施形態の説明に先立って、本発明の特徴についてその概要をまず説明する。本発明による電源故障検出回路および電源故障検出方法は、入力側のTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)に流れる電流と該直列スイッチング素子(前置直列スイッチング素子)の両端にかかる電圧とを観測することにより得られる、該直列スイッチング素子(前置直列スイッチング素子)の抵抗値が、正常動作時の許容範囲内の抵抗値としてあらかじめ定めた抵抗値閾値よりも低下したことを検知した際に、故障発生の前兆と看做して、直ちに、負荷側への出力を遮断する故障検出回路を備え、故障によりTOP側に位置する直列スイッチング素子(前置直列スイッチング素子)が完全なショート状態に陥る前に、入力電圧がそのまま負荷側へ出力されることを事前に防止することを可能にすることを主要な特徴としている。

【0018】

つまり、本発明は、電源回路において、入力側のTOP側に位置している前置直列スイッチング素子を構成する例えばFET(Field Effect Transistor)のドレイン−ソース間の抵抗値が、通常の許容範囲内の抵抗値すなわち抵抗値閾値よりも少しでも低下したことを検出した場合、ショート状態の故障が発生する前兆であると看做して、出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子を直ちに強制的にオフすることによって、入力電圧がそのまま負荷側に出力することを事前に防止する故障検出回路を備えることを主要な特徴としている。

【0019】

ここで、電源回路が、高い電圧値の入力電圧を低下させて負荷側に供給する降圧型DC−DCコンバータからなる電源回路に特に効果的であり、電源回路の故障により、高い入力電圧がそのまま負荷側に出力されて、負荷側の回路素子が破損してしまう事態が生じることを確実に防止することを可能にしている。

【0020】

(実施形態の構成例)

次に、本発明による電源故障検出回路の回路構成の一例について、図1を用いて説明する。図1は、本発明による電源故障検出回路の回路構成の一例を示す回路構成図であり、図3に示した電源回路と同様のDC−DCコンバータからなる電源回路においてショート故障を事前に検出して負荷側への出力を遮断する回路構成例を示しており、図3の電源回路と同じ機能を有する部位には、図3と同じ符号を付して示している。

【0021】

つまり、図1に示す電源回路は、図3の電源回路と同様、入力側のTOP側に位置する直並列接続したFET(Field Effect Transistor)からなる前置直列スイッチング素子Q1、前置並列スイッチング素子Q2を、制御IC回路Z1の端子G1、G2ピンそれぞれから出力されるスイッチングパルスによりスイッチング制御することにより、入力電圧Vinを、チョーククコイルL1と平滑コンデンサC1とを介して、所望の出力電圧Voutとして負荷側に出力するように構成されている。

【0022】

ここで、図1に示す電源回路においても、図3の電源回路と同様、電源回路に過電流が発生する故障を検出するために、チョーククコイルL1の後段に電流検出抵抗R1を直列接続しており、電流検出抵抗R1の両端には、当該電源回路に流れる電源電流I1に比例した検出電圧V1が発生し、発生した検出電圧V1は、制御IC回路Z1のセンス端子SENSE+、SENSE−ピン間の電圧として、制御IC回路Z1にフィードバックされるように構成されている。

【0023】

制御IC回路Z1は、図3の電源回路と同様、センス端子SENSE+、SENSE−ピンにフィードバックされてくる検出電圧V1を常時監視していて、過電流検出用としてあらかじめ定めた電圧閾値以上の電圧値になったことを検出すると、過電流が流れる故障が発生したものと判定して、制御IC回路Z1の過電流保護機能が働いて、スイッチングパルスの生成動作を停止する。その結果、端子G1、G2ピンから前置直列スイッチング素子Q1、前置並列スイッチング素子Q2それぞれに出力されていたスイッチングパルスによる前置直列スイッチング素子Q1、並列スイッチング素子Q2のオンオフ動作が停止し、前置直列スイッチング素子Q1はオフ状態(開放状態)、前置並列スイッチング素子Q2はオン状態(閉成状態)を継続する状態になる。

【0024】

さらに、図1に示す電源回路においては、故障発生時における制御IC回路Z1による出力停止動作の遅さを補うために、当該電源回路のショート故障の発生を事前に検出する故障検出回路Z2が制御IC回路Z1とは別個に備えられている。そして、入力側のTOP側に位置している前置直列スイッチング素子Q1の前段に、前置直列スイッチング素子Q1に流れ込む入力電流の入力電流値Iを検出するための入力電流検出抵抗R2が直列接続されるとともに、出力側のBOTTOM側の電流検出抵抗R1と平滑コンデンサC1との接続点と出力端子との間には、負荷側への出力を遮断するための後置直列スイッチング素子Q3が直列接続されている。ここで、本実施形態においては、後置直列スイッチング素子Q3も、前置直列スイッチング素子Q1、前置並列スイッチング素子Q2と同様、FETを用いて構成している。

【0025】

故障検出回路Z2は、電流検出回路IDET、電圧検出回路VDET、除算器DEV、比較器CMPを少なくとも含んで構成されている。電流検出回路IDETは、前置直列スイッチング素子Q1の前段に直列接続されている入力電流検出抵抗R2の両端の電圧を引き込むことにより、入力端子から前置直列スイッチング素子Q1に流れ込む入力電流値Iを検出する。電圧検出回路VDETは、前置直列スイッチング素子Q1のドレイン、ソースそれぞれの電圧を引き込むことにより、前置直列スイッチング素子Q1のドレイン−ソース間の電圧値Vを検出する。

【0026】

除算器DEVは、電流検出回路IDETが検出した入力電流値Iと電圧検出回路VDETが検出した前置直列スイッチング素子Q1のドレイン、ソース間の電圧値Vとを入力して、(V/I=R)の除算演算を行い、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rを算出する。比較器CMPは、除算器DEVによって算出された前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが、正常動作時の許容範囲内を示す抵抗値としてあらかじめ定めた抵抗値閾値Aと比較して、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが抵抗値閾値Aよりも低下したことを検出した場合は、前置直列スイッチング素子Q1がショート故障に陥る前兆であるものと看做して、出力側のBOTTOM側に直列接続されている後置直列スイッチング素子Q3を開放(オフ)して、負荷側への出力を遮断する。

【0027】

(実施形態の動作の説明)

次に、図1に示した電源故障検出回路の動作の一例についてさらに詳細に説明する。図1の電源故障検出回路においては、故障検出回路Z2により前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rの変化を常時監視していて、該抵抗値Rが、正常動作時の許容範囲内の抵抗値すなわち抵抗値閾値Aよりも少しでも低下したことを検出した場合には、電源回路のショート状態の故障が発生する前兆であると看做して、出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子Q3を直ちに強制的にオフ(開放)することによって、出力側との接続を遮断して、入力電圧がそのまま負荷側に出力することを事前に防止している。

【0028】

すなわち、入力電圧Vinが印加された入力端子から流れ込んでくる入力電流の電流値を検出するために入力側のTOP側に直列接続した入力電流検出抵抗R2の両端の電圧を、故障検出回路Z2の電流検出回路IDETに引き込むことにより、電流検出回路IDETにおいて入力電流値Iを常時検出している。同時に、入力電流検出抵抗R2の後段に直列接続されている前置直列スイッチング素子Q1のドレインの電圧とソースの電圧との双方の電圧を、故障検出回路Z2の電圧検出回路VDETに引き込むことにより、電圧検出回路VDETにおいて前置直列スイッチング素子Q1のドレイン−ソース間の電圧値Vを常時検出している。

【0029】

電流検出回路IDETが検出した入力電流値Iと電圧検出回路VDETが検出した前置直列スイッチング素子Q1のドレイン−ソース間の電圧値Vとは、故障検出回路Z2の除算器DEVに入力され、除算器DEVにおいて、(V/I=R)の除算が行われることによって、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが直ちに算出される。除算器DEVによって算出された前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rは、故障検出回路Z2の比較器CMPにおいてあらかじめ定めた抵抗値閾値Aと比較され、該抵抗値閾値Aよりも少しでも低いと判定された場合には、前記直列スイッチング素子Q1のショート故障が発生する前兆であるものと看做して、直ちに、OFF信号(LOW)がFETからなる後置直列スイッチング素子Q3のゲート端子に印加される。

【0030】

この結果、前置直列スイッチング素子Q1のドレイン−ソース間の抵抗値Rが抵抗値閾値Aよりも少しでも低下したことを検知すると、瞬時に、出力側のBOTTOM側に直列接続されている後置直列スイッチング素子Q3はオン状態からオフ状態に切り替わり、出力側との接続を遮断する。而して、しかる後に、たとえ、前置直列スイッチング素子Q1が完全なショート状態に陥ったとしても、入力電圧Vinがそのまま負荷側に出力される事態が発生することを事前に確実に防止することができる。

【0031】

なお、図1に示す電源故障検出回路においては、入力電流の電流値を検出するために、TOP側の入力側に入力電流検出抵抗R2を直列接続している場合について示したが、本発明は、かかる場合のみに限るものではない。例えば、図2に示すように、入力電流検出抵抗R2の代わりにカレントトランスCT1を用いて構成するようにしても良い。図2は、本発明による電源故障検出回路の回路構成の他の例を示す回路構成図であり、図1における入力電流検出抵抗R2の代わりにカレントトランスCT1を用いて構成している構成例を示している。

【0032】

図2のような回路構成にして、入力電流検出抵抗R2の代わりにカレントトランスCT1を用いて入力電流を検出することにすれば、入力電流検出抵抗R2において発生していた電力損失を低減することが可能になるという効果が得られる。

【0033】

また、図1に示す電源故障検出回路において、前置直列スイッチング素子Q1、前置並列スイッチング素子Q2、後置直列スイッチング素子Q3を、FETを用いて構成する場合について説明したが、本発明は、かかる前置直列スイッチング素子Q1、前置並列スイッチング素子Q2、後置直列スイッチング素子Q3を、MOSFET(Metal Oxide Semiconductor Field Effect Transistor:金属酸化物半導体電界効果トランジスタ)のみならず、IGBT(Insulated Gate Bipolar Transistor:絶縁型ゲート・バイポーラトランジスタ)や、場合によっては、MEMS(Micro ElectroMechanical Systems)型スイッチング素子を用いて構成するようにしても良い。

【0034】

(本実施形態の効果の説明)

以上に詳細に説明したように、本実施形態においては、以下に記載するような効果が得られる。

【0035】

すなわち、入力側のTOP側に位置する前置直列スイッチング素子Q1を構成するFETに故障が発生して、前置直列スイッチング素子Q1としてのFETのドレイン−ソース間の抵抗値Rが正常動作時における許容範囲内を示す抵抗値としてあらかじめ定めた抵抗値閾値Aよりも低下したことを検出した際に、直ちに、負荷側への出力遮断用として出力側のBOTTOM側に追加して直列接続した後置直列スイッチング素子Q3をオフ(開放)させることにより、前置直列スイッチング素子Q1が完全にショート状態になる前に、入力電圧Vinがそのまま負荷側へ出力してしまうことを事前にかつ確実に遮断することができる。

【0036】

而して、電源回路が降圧型DC−DCコンバータとして構成されているような場合であっても、電源回路の故障時に、高い入力電圧Vinが電圧降下することなくそのまま負荷側の回路素子に印加されてしまう事態が発生することはなく、負荷側の回路素子が破損することを確実に防ぐことができる。

【0037】

以上、本発明の好適な実施形態の構成を説明した。しかし、かかる実施形態は、本発明の単なる例示に過ぎず、何ら本発明を限定するものではないことに留意されたい。本発明の要旨を逸脱することなく、特定用途に応じて種々の変形変更が可能であることが、当業者には容易に理解できよう。

【符号の説明】

【0038】

A 抵抗値閾値

C1 平滑コンデンサ

CMP 比較器

CT1 カレントトランス

DEV 除算器

G1 端子

G2 端子

I 入力電流値

I1 電源電流

IDET 電流検出回路

L1 チョーククコイル

Q1 直列スイッチング素子(前置直列スイッチング素子)

Q2 並列スイッチング素子(前置並列スイッチング素子)

Q3 後置直列スイッチング素子

R 抵抗値

R1 電流検出抵抗

R2 入力電流検出抵抗

SENSE+ センス端子

SENSE− センス端子

V 電圧値

Vin 入力電圧

Vout 出力電圧

V1 検出電圧

VDET 電圧検出回路

Z1 制御IC回路

Z2 故障検出回路

【特許請求の範囲】

【請求項1】

前置直列スイッチング素子と前置並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出回路であって、前記負荷側へ出力する出力線に直列接続した後置直列スイッチング素子と、前記前置直列スイッチング素子に流れ込む入力電流と前記前置直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記前置直列スイッチング素子の故障の前兆を検出する故障検出回路とを、さらに備え、前記故障検出回路の検出結果に基づいて、前記後置スイッチング素子のオンオフを制御することを特徴とする電源故障検出回路。

【請求項2】

前記故障検出回路は、前記前置直列スイッチング素子に流れ込む入力電流の入力電流値を検出する電流検出回路と、前記前置直列スイッチング素子の両端に掛かる電圧の電圧値を検出する電圧検出回路と、前記電圧検出回路が検出した前記電圧値を前記電流検出回路が検出した前記入力電流値で除算することによって前記前置直列スイッチング素子の抵抗値を算出する除算器と、前記除算器が算出した前記前置直列スイッチング素子の抵抗値があらかじめ定めた抵抗値閾値よりも低下したか否かを比較する比較器とからなり、前記比較器の比較結果として、前記前置直列スイッチング素子の抵抗値が前記抵抗値閾値よりも低下したことを検出した場合、前記前置直列スイッチング素子の故障が発生する前兆と看做して、前記後置スイッチング素子をオフし、前記負荷側への出力を停止することを特徴とする請求項1に記載の電源故障検出回路。

【請求項3】

前記電流検出回路により前記前置直列スイッチング素子に流れ込む入力電流の入力電流値を検出するために、前記前置直列スイッチング素子の前段に電流検出用の抵抗またはカレントトランスを直列接続し、該抵抗またはカレントトランスの両端に掛かる電圧を前記電流検出回路に取り込む構成とすることを特徴とする請求項2に記載の電源故障検出回路。

【請求項4】

前記前置直列スイッチング素子、前記前置並列スイッチング素子、前記後置直列スイッチング素子を、MOSFET(Metal Oxide Semiconductor Field Effect Transistor:金属酸化物半導体電界効果トランジスタ)、IGBT(Insulated Gate Bipolar Transistor:絶縁型ゲート・バイポーラトランジスタ)、MEMS(Micro ElectroMechanical Systems)型スイッチング素子のいずれかを用いて構成することを特徴とする請求項1ないし3のいずれかに記載の電源故障検出回路。

【請求項5】

直列スイッチング素子と並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出方法であって、前記直列スイッチング素子に流れ込む入力電流と前記直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記直列スイッチング素子の故障の前兆を検出して、前記負荷側への出力の可否を制御することを特徴とする電源故障検出方法。

【請求項6】

前記直列スイッチング素子に流れ込む入力電流値と前記直列スイッチング素子の両端に掛かる電圧値との測定結果に基づいて前記負荷側への出力の可否を制御する際に、前記直列スイッチング素子の両端に掛かる電圧の電圧値を前記直列スイッチング素子に流れ込む入力電流の入力電流値で除算することによって算出した前記直列スイッチング素子の抵抗値が、あらかじめ定めた抵抗値閾値よりも低下したか否かを比較し、前記直列スイッチング素子の抵抗値が前記抵抗値閾値よりも低下したことを検出した場合に、前記直列スイッチング素子の故障が発生する前兆と看做して、前記負荷側への出力を停止することを特徴とする請求項5に記載の電源故障検出方法。

【請求項7】

前記直列スイッチング素子の前段に電流検出用の抵抗またはカレントトランスを直列接続し、該抵抗またはカレントトランスの両端に掛かる電圧を測定することにより、前記直列スイッチング素子に流れ込む入力電流の入力電流値を検出することを特徴とする請求項6に記載の電源故障検出方法。

【請求項1】

前置直列スイッチング素子と前置並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出回路であって、前記負荷側へ出力する出力線に直列接続した後置直列スイッチング素子と、前記前置直列スイッチング素子に流れ込む入力電流と前記前置直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記前置直列スイッチング素子の故障の前兆を検出する故障検出回路とを、さらに備え、前記故障検出回路の検出結果に基づいて、前記後置スイッチング素子のオンオフを制御することを特徴とする電源故障検出回路。

【請求項2】

前記故障検出回路は、前記前置直列スイッチング素子に流れ込む入力電流の入力電流値を検出する電流検出回路と、前記前置直列スイッチング素子の両端に掛かる電圧の電圧値を検出する電圧検出回路と、前記電圧検出回路が検出した前記電圧値を前記電流検出回路が検出した前記入力電流値で除算することによって前記前置直列スイッチング素子の抵抗値を算出する除算器と、前記除算器が算出した前記前置直列スイッチング素子の抵抗値があらかじめ定めた抵抗値閾値よりも低下したか否かを比較する比較器とからなり、前記比較器の比較結果として、前記前置直列スイッチング素子の抵抗値が前記抵抗値閾値よりも低下したことを検出した場合、前記前置直列スイッチング素子の故障が発生する前兆と看做して、前記後置スイッチング素子をオフし、前記負荷側への出力を停止することを特徴とする請求項1に記載の電源故障検出回路。

【請求項3】

前記電流検出回路により前記前置直列スイッチング素子に流れ込む入力電流の入力電流値を検出するために、前記前置直列スイッチング素子の前段に電流検出用の抵抗またはカレントトランスを直列接続し、該抵抗またはカレントトランスの両端に掛かる電圧を前記電流検出回路に取り込む構成とすることを特徴とする請求項2に記載の電源故障検出回路。

【請求項4】

前記前置直列スイッチング素子、前記前置並列スイッチング素子、前記後置直列スイッチング素子を、MOSFET(Metal Oxide Semiconductor Field Effect Transistor:金属酸化物半導体電界効果トランジスタ)、IGBT(Insulated Gate Bipolar Transistor:絶縁型ゲート・バイポーラトランジスタ)、MEMS(Micro ElectroMechanical Systems)型スイッチング素子のいずれかを用いて構成することを特徴とする請求項1ないし3のいずれかに記載の電源故障検出回路。

【請求項5】

直列スイッチング素子と並列スイッチング素子とチョークコイルと平滑コンデンサとを少なくとも備えているDC−DCコンバータからなる電源の故障を検出し、負荷側への出力を停止する電源故障検出方法であって、前記直列スイッチング素子に流れ込む入力電流と前記直列スイッチング素子の両端に掛かる電圧との測定結果に基づいて前記直列スイッチング素子の故障の前兆を検出して、前記負荷側への出力の可否を制御することを特徴とする電源故障検出方法。

【請求項6】

前記直列スイッチング素子に流れ込む入力電流値と前記直列スイッチング素子の両端に掛かる電圧値との測定結果に基づいて前記負荷側への出力の可否を制御する際に、前記直列スイッチング素子の両端に掛かる電圧の電圧値を前記直列スイッチング素子に流れ込む入力電流の入力電流値で除算することによって算出した前記直列スイッチング素子の抵抗値が、あらかじめ定めた抵抗値閾値よりも低下したか否かを比較し、前記直列スイッチング素子の抵抗値が前記抵抗値閾値よりも低下したことを検出した場合に、前記直列スイッチング素子の故障が発生する前兆と看做して、前記負荷側への出力を停止することを特徴とする請求項5に記載の電源故障検出方法。

【請求項7】

前記直列スイッチング素子の前段に電流検出用の抵抗またはカレントトランスを直列接続し、該抵抗またはカレントトランスの両端に掛かる電圧を測定することにより、前記直列スイッチング素子に流れ込む入力電流の入力電流値を検出することを特徴とする請求項6に記載の電源故障検出方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−78203(P2013−78203A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−216429(P2011−216429)

【出願日】平成23年9月30日(2011.9.30)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]