電界効果トランジスタ

【課題】電流利得遮断周波数fTの改良された値を示すことのできる、別の形のFETを提供する。

【解決手段】電界効果トランジスタ(FET)は、ベースバイアスを使用して伝導への真性の寄与を低減させ漏れ電流を減少させる種類のものであり、連続した4層102から108を含む。すなわち、p+InSbベース層102、p+InAlSb障壁層104、π真性層106および絶縁SiO2層108である。p+のソースおよびドレイン層110、112が、真性層106にイオン注入される。FETは、エンハンスメントモードMISFET100であり、バイアスによって真性層106にFETチャネルが形成される。絶縁層108の表面はほぼ平坦であり、ゲートコンタクト116を支持する。これによって、ゲート溝の侵入によって引き起こされるチャネルの直線性からのずれをなくし、または減少させ、高い値の電流利得遮断周波数を得ることができるようにする。

【解決手段】電界効果トランジスタ(FET)は、ベースバイアスを使用して伝導への真性の寄与を低減させ漏れ電流を減少させる種類のものであり、連続した4層102から108を含む。すなわち、p+InSbベース層102、p+InAlSb障壁層104、π真性層106および絶縁SiO2層108である。p+のソースおよびドレイン層110、112が、真性層106にイオン注入される。FETは、エンハンスメントモードMISFET100であり、バイアスによって真性層106にFETチャネルが形成される。絶縁層108の表面はほぼ平坦であり、ゲートコンタクト116を支持する。これによって、ゲート溝の侵入によって引き起こされるチャネルの直線性からのずれをなくし、または減少させ、高い値の電流利得遮断周波数を得ることができるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電界効果トランジスタ(FET)に関する。より詳細には、本発明は、限定はしないが、狭いバンドギャップ半導体材料、すなわち0.5eV付近またはそれより小さなバンドギャップEGの半導体材料で作成された、MISFETのようなFETに関する。また、本発明は、室温よりも高い動作温度で使用するために、より広いバンドギャップ材料で作成されたFETにも関連する。

【背景技術】

【0002】

インジウムアンチモン(InSb)のような狭いバンドギャップ半導体には、非常に小さな電子有効質量、非常に大きな電子移動度および大きな飽和速度のような有用な性質がある。これらの性質は、超高速度の応用分野にとっては潜在的に非常に興味のあるものである。特にInSbは、高速超低消費電力トランジタ用の有望な材料である。なぜなら、GaAsはこれらの点で優れた性質を持っているが、低電界でのInSbの電子移動度μcはGaAsの9倍であり、その飽和速度vsatは5倍よりも大きい。また、InSbは、0.5μmを超える大きな弾道平均自由行程をもつと予測される。このことは、InSbは、低電力消費を可能にして非常に低い電圧で高速動作をする可能性を持っていることを示唆している。これにより、InSbは携帯型で高密度の応用分野にとって理想的であるはずである。295K(室温)でのシリコン、GaAsおよびInSbのいくつかの特性を、次の表1で比較する。

【表1】

【0003】

最近まで、InSbのバンドギャップが小さく、その結果真性キャリア濃度(〜2×1016cm−3)が高いために、SiおよびGaAsよりもそれぞれ6桁および9桁大きい、室温でInSbの潜在的に貴重な特性を得ることができなかった。この大きな真性キャリア濃度により、InSbデバイスは295Kの室温またはそれに近い通常動作温度で、少数キャリア濃度が通常のドーピングレベルで必要とされる値よりも遥かに大きく、大きな漏れ電流を示すことになる。これは、InSbおよびその他の狭いバンドギャップ材料を室温以上でデバイスで使用することを妨げる基本的な問題であると何年も考えられていた。しかし、米国特許第5,382,814号の主題の発明によって、その問題は克服された。該特許は、キャリア濃度への真性の寄与を平衡レベルよりずっと弱めるために、キャリアの排除(exclusion)および抽出(extraction)の現象を使用する、非平衡金属−絶縁体−半導体電界効果トランジスタ(non−equilibrium metal−insulator−semiconductor field effect transustor、MISFET)を開示する。この従来技術のMISFETは、逆バイアスされたp+p+πn+の構造である。ここで、pはInSb層を示し、pはひずみIn1−xAlxSb層であり(アンダーラインの付いたpは、pよりもバンドギャップが広いことを示す)、πは室温動作温度で真性である弱ドープp型領域を示し、さらに、+の上付き文字は高いドーパント濃度を示す。これら4つの層により、それぞれの隣合う層の対の間に3つの接合が画定される。すなわち、それぞれp+p+、p+πおよびπn+接合である。デバイスの活性領域はπ領域であり、少数キャリアは、抽出コンタクト(extracting contact)として作用するπn+接合でπ領域から取り去られる。p+π接合は、これらのキャリアの再導入を阻止する排除コンタクト(excluding contact)である。その結果、デバイスに印加されたバイアスの下で、少数キャリア濃度は減少し、多数キャリア濃度は、電荷中性を維持するように少数キャリア濃度とともに減少する。これによって、真性レベルよりも低いキャリア濃度が生成される。同様の効果は、冷却することで作り出される。ここで、「真性」という表現は、キャリアが主として価電子状態の活性化により発生し、ほぼ等しい数の少数キャリアと多数キャリアが半導体材料中に存在することを意味する、通常の解釈で使用されている。この表現は、単にドーピングレベルが低いことを示すために外因性材料(例えば、Si)について間違って使用されることがある。しかし、外因性材料では、キャリアは、主としてドナー状態かアクセプタ状態の活性化によって発生し、1つのタイプのキャリア(電子または正孔)が支配的である。

【0004】

米国特許第No.5,382,814号に開示されているデバイスは、1μm凹みゲート型エンハンスメントモードMISFET構造である。研究のために、この種の様々なデバイスが製造された。この種のデバイスで電流利得が1になる周波数fTは、55GHzであると理論的に予測されたが、たかだか10GHz付近の測定値が得られた。fTの値は、高周波トランジスタの当業者が性能指数として扱っている。ゲートコンタクト金属のオーバラップと関係するデバイス容量を、ソース領域とドレイン領域上に制限するようにしたにもかかわらず、これらのデバイスのどれでも、得られたfTの最もよい値は17GHzであった。このことは、InSbMISFETの高周波の可能性を完全に実現することは困難であることを示している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第5,382,814号

【発明の概要】

【発明が解決しようとする課題】

【0006】

電流利得遮断周波数fTの改良された値を示すことのできる、別の形のFETを提供することが本発明の目的である。

【課題を解決するための手段】

【0007】

本発明は、その電界効果トランジスタ(FET)の動作温度でバイアスされていない時に真性導電率を有する領域と、真性領域中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段とを含む種類の電界効果トランジスタであって、そのFETは、また、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmより大きくない、ソース領域とドレイン領域の間に延びるチャネルを画定する手段を含むことを特徴とする電界効果トランジスタ(FET)を提供する。そのようなチャネルの直線性からのずれは、限度において5nmより大きくないことが好ましい。「限度」という表現は、チャネルの任意の2つの領域、例えばチャネルの中心領域とソースまたはドレインに隣接する領域の間との最も大きな高さの差を意味する。

【0008】

本発明は、非常に改良された高周波性能を示し、従来技術に比べて非常に大きな値の電流利得遮断周波数を実現することができるという利点を提供する。従来技術によるMISFETは、特に、理論的な期待値よりも遥かに低い高周波で、期待はずれの性能をもつことが分かった。この理由は、当初理解されていなかった。しかし、その問題を解決しようとして、かなりの数の仮説が研究された。これらの仮説の1つが、MISFETゲート凹部をオーバエッチングすると、高周波性能を劣化させる可能性があるというものであった。介在するゲート溝の侵入なしに製造される本発明のデバイスは、高周波で遥かに優れた性能を示し、ゲート溝形成が性能に及ぼす有害な影響の仮説が、確認されたと推測される。

【0009】

1つの態様では、本発明のFETは、エンハンスメントモードMISFETである。本発明のFETは、真性領域を組み込んでいる層に高濃度のドーピングを導入することで作成される、ソースおよびドレイン領域を組み込むことができる。ソースおよびドレイン領域は、イオン注入、拡散ドーピング、合金化または損傷の導入によって作成することができる。真性領域は、残留としてp型にドープされ、ソースおよびドレイン領域と抽出コンタクト手段を形成してもよく、バイアスに応じて真性領域に形成されるチャネルはn型になるだろう。

【0010】

好ましい実施形態では、真性領域は、それ自体がベース領域との界面を有する障壁領域との界面を有し、真性、障壁およびベース領域(106、104、102)は同じ導電型であり、障壁領域は、真性およびベース領域よりも比較的広いバンドギャップをもち、かつ真性領域に対する排除コンタクトを提供する。

【0011】

本発明のFETは、動作時にエンハンスメントチャネルをその間に画定するように、ソース領域とドレイン領域の間にある真性領域の部分から絶縁され、かつ少なくともその部分にわたって延びる、ゲートコンタクトを含んでもよい。ベース領域は、少なくとも5×1017cm−3のドーパント濃度を含むp+InSbであってもよい。障壁領域は、少なくとも5×1017cm−3のドーパント濃度を含む、0.05から0.25の範囲のxをもつp+In1−xAlxSbであってもよい。真性領域は、5×1017cm−3より少ないドーパント濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のドーパント濃度を含む、πInSbであってもよい。さらに、ソースおよびドレイン領域は、少なくとも5×1017cm−3のドーパント濃度を含むn+InSbであってもよい。

【0012】

ベース、障壁および真性領域は、好ましくは層構造中に連続して配置され、ソースおよびドレイン領域は、イオン注入、拡散、合金化または損傷によって真性領域に作成され、さらに真性領域は好ましくはゲート絶縁層およびゲートコンタクトを支持するほぼ平坦な表面部分を有する。

【0013】

他の態様で、本発明のFETは、関連したチャネル領域を有するデプレッションモードMISFETである。そのFETは、真性領域かチャネル領域のいずれかの上に形成された高濃度にドープされたアウトグロースである、ソースおよびドレイン領域を組み込んでもよい。もしくは、これらの領域は、イオン注入、拡散、合金化または損傷によって作成されてよい。それらは、ゲートコンタクトを収容するゲート凹部をその間に画定してもよい。

【0014】

真性領域はp型であってもよく、それ自体かチャネル領域のいずれかが、ソースおよびドレイン領域と抽出コンタクト手段を形成してもよい。

【0015】

好ましい実施形態では、真性領域は、それ自体がベース領域との界面を有する障壁領域との界面を有し、真性、障壁およびベース領域が同じ導電型であり、障壁領域は、真性およびベース領域よりも比較的広いバンドギャップをもち、かつ真性領域に対する排除コンタクトを提供する。この実施形態では、

ベース領域は、少なくとも5×1017cm−3のアクセプタを含むp+InSbであってもよく、

障壁領域は、0.05から0.25の範囲のxを有するp+In1−xAlxSbであり、少なくとも5×1017cm−3のアクセプタを有してもよく、

真性領域は、5×1017cm−3より小さなアクセプタ、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタを含むπInSbであり、

ソースおよびドレイン領域は、少なくとも5×1017cm−3のドナーを含むn+InSbである。

【0016】

真性領域は、チャネル領域を支持してもよく、ベース、障壁、真性およびチャネル領域は層構造中に連続して配置され、ソースおよびドレイン領域はチャネル領域上に成長され、さらにチャネル領域は、ゲート絶縁層およびゲートコンタクトを支持するほぼ平坦な表面部分を有する。

【0017】

ソースおよびドレイン領域は、その間にゲート凹部を画定してもよく、チャネル領域は、ゲート絶縁層およびゲートコンタクトを支持する凹部の端部に表面部分を有する。

【0018】

チャネル領域は、真性領域の部分の間にあってもよく、真性領域は、ソースおよびドレイン領域との組合せで抽出コンタクト手段を形成する。

【0019】

ベース、障壁および真性領域は、好ましくは層構造中に連続して配置され、真性領域はチャネル領域を含み、ソースおよびドレイン領域を支持する。

【0020】

真性領域中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段は、基板バイアス電圧変化によるゲート閾値電圧の変化が最小となる無限大の差動インピーダンスの点で、FETをバイアスするように構成されるのが好ましい。

【0021】

他の態様で、本発明は、その真性領域中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段を含む種類のFETを作成する方法であって、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmより大きくないように、ソース領域とドレイン領域の間に延びるチャネルを画定することを含むことを特徴とする方法を提供する。チャネルの直線性からのそのようなずれは、限度において5nmより大きくないことが好ましい。

【0022】

本発明をより十分に理解するために、添付の図面を参照して単なる例として本発明の実施形態を次に説明する。

【図面の簡単な説明】

【0023】

【図1】一定の縮尺で描かれていない従来技術MISFETの模式的な断面図である。

【図2】拡大して図1の従来技術MISFETのゲートを示す図である。

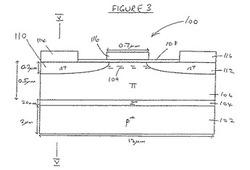

【図3】凹状でも凸状でもない層をもつ理想的な形で図示された、本発明のnチャネルエンハンスメントモードMISFETの模式的な断面図である(一定の縮尺で描かれていない)。

【図4】小程度のゲート領域凹面を示す、本発明のnチャネルエンハンスメントモードMISFETの中心領域の模式的な断面図である。

【図5】本発明の逆バイアスされたp+p+πn+MISFET構造のバンド構造図であり、図3の線V−Vの断面に対応する。

【図6】図3のMISFETの出力特性を示す図である。

【図7】図3のMISFETの伝達特性を示す図である。

【図8】図3のMISFETおよび同様のモデル化されたデバイスについて、ゲート長による電流利得遮断周波数の変化を示す図である。

【図9】図3のMISFETについて、周波数による交流利得パラメータの変化を示す図である。

【図10】本発明のnチャネルデプレッションモードMISFETの模式的な断面図である(一定の縮尺で描かれていない)。

【図11】様々なデバイス技術について、測定されたものとモデル化されたもの両方で、ゲート長(μm)の関数として電流利得遮断周波数fT(GHz)の変化を示す図である。

【図12】キャリア濃度を排除と抽出で低減させた種類のMISFETについて、理論的に達成できるベース電流/電圧特性を示す図である。

【発明を実施するための形態】

【0024】

次に図1を参照して、米国特許第5,382,814号に開示された種類の従来技術MISFET10が示されている。MISFET10は、インジウムアンチモン(InSb)およびインジウムアルミニウムアンチモン(In1−xAlxSb)の層から成る。MISFET10は、次のような4層の半導体材料を支持する基板(図示されない)を有する。すなわち、高濃度にドープされた狭いバンドギャップp型(p+)ベース層12、比較的広いバンドギャップで高濃度にドープされたp型(p+)障壁層14、低濃度にドープされたp型(π)活性層16および高濃度にドープされた狭いバンドギャップのn型(n+)ソース/ドレイン層18である。層12、16および18はInSbであり、層14はIn1−xAlxSbである。π活性層16は、295Kの室温で主に真性導電率をもつが、一方でその他の層12、14および18は、この温度で主に外因性導電率をもつ。隣接する層の対12/14、14/16および16/18の間の界面は、それぞれp+p+、p+π、およびπn+接合であり、これらの最初の2つはヘテロ接合であり、最後のものはホモ接合である。p+π接合14/16およびπn+接合16/18は、それぞれ排除コンタクトと抽出コンタクトである。

【0025】

MISFET10には、それぞれコンタクト24を有するソース領域20とコンタクト26を有するドレイン領域22があり、それらの領域は、n+層18を通り越してエッチングして形成された間にあるゲート凹部または溝28を有する。ゲート凹部の底および側面は、シリコン酸化膜ゲート絶縁物30および金属ゲートコンタクト32で覆われている。ソース20とドレイン22の間に短絡ができないように、凹部28がn+層18を完全に(または、ほぼ完全に)通り越して延びることが、MISFET10の動作のために必要である。

【0026】

通常の動作でバイアスが加えられた時に、キャリアの抽出および排除が、MISFET10で起きる。層12から18までで、p+p+πn+ダイオードが形成され、そのダイオードは動作状態では逆バイアスされる。すなわち、ベース層12がソース領域20に対して負にバイアスされる。このバイアスの下で、πn+接合16/18は、抽出コンタクトとして作用してπ層16から電子(少数キャリア)を取り去る。そのような電子をp+障壁層14から補充することはできない。何故ならば、p+障壁層14は、p+ベース層12と組み合わさって排除コンタクトとして作用し、π層16への電子の流れに対して電位障壁を形成するからである。このようにして、MISFET10がバイアスされたときに、π層16の電子濃度は減少し、それと共にπ層16の正孔濃度は電荷中性の理由ために減少する。

【0027】

このために層16の導電率は非常に減少し、したがって、ソース20とドレイン22の間の漏れ電流が減る。

【0028】

述べたように、製造されたMISFET10の試験例は、期待を裏切る高周波での性能を示した。これらのデバイスの電流利得遮断周波数fT(その周波数で電流利得が1になる)の理論的な値は、55GHzであったが、ゲート金属のオーバラップに関連するデバイス容量を、ソースとドレイン領域上に制限するようにしたにもかかわらず、測定値は10GHz付近に過ぎなかった。この理由は理解されていなかった。しかし、不満足な高周波性能の原因であるアーチファクト候補を特定しようとして、かなりの数の仮説が提起され、理論的に研究された。これらの仮説の1つが、ゲート凹部または溝の深さと関連付けられた。理論的な計算により、ゲート凹部が深くエッチングされすぎると(それは制御し測定するのが難しい)、高周波性能は劣化することが示された。理論的な状況を図2に示す。ここでは、ゲート凹部28を拡大して示す。

【0029】

MISFET10が成り立つためには、ゲート凹部28は、ソースとドレインの間に短絡が生じないないようにn+領域18のほとんどを通り越して、好ましくは完全に通り越して、延びなければならない。この凹部がオーバエッチングされると、凹部はπ領域16の中まで続き、試験デバイスでは深さが100nm程度の反転ステップ34が形成されたと見なされている。そうなれば、ソース20とドレイン22の間のMISFETチャネル(図示されない)は、意図した通りの直線ではなくてU字状になるはずである(エンハンスメントモードMISFETでは、バイアスの印加に応じた動作状態でだけ、ゲート電極の下にチャネルが形成される)。

【0030】

ソースとドレインの間の電荷キャリアの走行時間を最小にするためには、ソース−ドレイン電界は、チャネルの長手方向に向いているべきであるが、このことは、この電界と平行に延びるU字状チャネルの部分だけで可能になる。そのようなチャネルでは、チヤネルがソース−ドレイン方向に延びない領域があるはずであり、したがって、ソース−ドレイン電界は、チャネルの長手方向に対して傾いている。その結果、長手方向の電界成分は、電界がこの方向に平行である場合よりも弱くなる。それによって、電界が完全に長手方向にある場合に比べると、ソースとドレインの間の電荷キャリアの走行時間は長くなる。このようにして、fTはこの走行時間と関連するので、U字状チャネルでfTは下がると推定される。正しければ、この理論的な解析は、エッチングされたゲート凹部を避けるべきであることを示している。この仮説は、以下に述べる本発明の例の製造で検証した。

【0031】

次に図3を参照して、本発明のエンハンスメントモードMISFETを、一般的に100で示す。それは弱くドープしたp型InSb基板(図示されない)を含み、そのp型InSb基板の上に、下記の厚さと組成を有する第1の層102、第2の層104、第3の層106および第4の層108を連続して成長させる。すなわち、

第1の(ベース)層102、p+InSb厚さ2μm、Beドーパント濃度3×1018cm−3、

第2の(障壁)層104、p+In0.85Al0.15Sb厚さ20nm、Beドーパント濃度3×1018cm−3、

第3の(真性)層106、πInSb厚さ0.5μm、Beドーパント濃度1×1015cm−3、および

第4の(絶縁)層108、SiO2厚さ70nm、

である。

【0032】

より一般的には、本発明のInSb/InAlSbFETの適当な組成は次のようである。すなわち、

ベース領域、少なくとも5×1017cm−3のアクセプタ濃度を有するp+InSb、

障壁領域、0.05から0.25の範囲のxを有するp+In1−xAlxSbであり、少なくとも5×1017cm−3のアクセプタ濃度を有する、および

真性領域、5×1017cm−3よりも小さなアクセプタ濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタ濃度をもつπInSbである。

【0033】

MISFET100は、絶縁層108近くの電荷キャリアの閉込めを向上させるために、真性層106の中に埋込みp型層109(鎖線で示されている)を任意に含むことができる。MISFET100は、それぞれが少なくとも5×1017cm−3の中性アクセプタ濃度を有し厚さがほぼ0.2μmである、n+のソース領域110およびドレイン領域112を含む。MISFET100は、連続したCrとAuの層(図示されない)から成る、ソースコンタクト114、ゲートコンタクト116およびドレインコンタクト118を有する。MISFET100のメサ長は12μmであり、これが図面の面内で全幅となっている。そのメサ(およびゲート)幅は50μmであり、これは図面の面に垂直に延びる寸法である。ゲートコンタクト116(図面の面内の水平寸法)の長さは、公称0.7μmである。ここで、「公称」とは、必要な長さを作成するのに適当な寸法のリソグラフィマスクが使用されたことを意味し、長さは測定しなかった。公称ゲート長が0.7から2μmの範囲で、メサ幅が100μmである、同様な構造および種類の他のデバイスも製造した。層102から108は、分子線エピタキシで成長させた。ソース領域110およびドレイン領域112は、単位面積当たり5×1013cm−2の線量の70keVS32イオンを使用してイオン注入で作った。イオンは、基板温度100℃で、結晶の<110>方向に対する垂線から10゜の角度で自然陽極酸化マスクを通して注入した。これに続いて、ドーパントを活性化し損傷を取り除くために、Si3N4キャップを付けた状態で420℃で10秒間の急速熱アニールを行った。次にサンプルを陽極酸化し、酸化膜をはがして、コンタクトを付ける前に損傷を受けた材料を取り除いた。MISFET100を製造するプロセスにより、層106および108は少しばかりの凹面となった。しかし、チャネルの中心領域(ゲートバイアス電圧に応じて形成された)とソースおよびドレインに隣接するチャネルの外側領域との間に、50nmよりも大きな高さの差は生じなかった。注入によって、ソース領域110およびドレイン領域112へのコンタクトを可能にする伝導経路を形成した。

【0034】

第4の層108は、30nmの陽極酸化膜の表面に堆積された40nmのスパッタSiO2で構成された。層108全体としては、光分解SiO2が好ましかっただろうが、これは利用できなかった。

【0035】

ゲートコンタクト116は、ソース領域110とドレイン領域112の間にあり、これらの領域と少しオーバラップしている第3の層すなわちπ層106の部分の全体にわたって広がっている。理想的には、デバイス容量を最小にするために、オーバラップはゼロであるべきであるが、エンハンスメントモードデバイスでは、動作時にチャネル領域を要求されるように形成することができるように、ゲートコンタクトは、これらの領域の間に十分に広がっていることが重要である。

【0036】

MISFET100では、ソース領域110とドレイン領域112の間の直線性が、ゲート116の形状で大きくぼかされることはなく、従来技術デバイス10で経験された100nmの程度まではないことは確かである。

【0037】

図3は理想化された図である。実際には、本発明のFETは、製造プロセスでの不正確さによって生じた理想的な形状寸法からのずれによる、平面でない層を有してもよい。すなわち、チャネルのひどすぎる変形を引き起こさない限りは、真性領域は、凹状でも、凸状でも、または起伏があってもよい。図4に凹面を示す。ここでは、図3に関して記述されたものと同等な部分は、接尾文字Rを付けて同じように参照する。図4は、実際のデバイスにより近いことを除いては、MISFET100と同等のFETの中心領域120を示す。真性層106R、ゲート絶縁層108Rおよびゲートコンタクト116Rが含まれ、それらは全て凹状でV字形凹部122を画定している。凹部122の底は、絶縁層108Rの中心にある頂点124で画定されている。凹部122の深さはHで示され、それは50nmよりも大きくない。ゲートバイアス電圧の印加に応じて、チャネル(図示されない)が形成されたときに、頂点124の下のチャネル(図示されない)の中心領域と、ソース110Rとドレイン112Rに隣接するチャネルの外側領域との間に、図面内の上下方向に存在する50nmよりも大きな差が、凹部122によって、もたらされることはない。言い換えると、ゲート領域が平面でないことで生じるチャネルの直線性からのずれは、50nmよりも小さい。ここで、チャネルが形成され、チャネルの形状を決定するゲート領域は、ゲート絶縁層108Rに隣接する真性層106Rの上部である。本発明の他の実施形態では、それはチャネルの中心部分を収容するデバイスの活性領域である。

【0038】

凹部深さHおよび結果的なチャネルの直線性からのずれは、5nmよりも大きくないことが好ましい。その結果、形成されたチャネルは、ソース、ゲートおよびドレインの電圧で決定されるように、ほぼ延びることができる。後で説明するように、これによって、従来技術デバイス10に比べて著しく改良された性能を生じる。

【0039】

図5は、MISFET100で、第1の層102の下端から測定されたμm単位の上下方向の距離xの関数として、バンド構造図および関連した電荷キャリア密度を示す。この図面に示されるデータは、逆バイアスされたp+p+πn+構造に関するものである。そのデータは、第1(p+)の層102、第2(p+)の層104および第3(π)の層106、さらに(n+)ソース領域110を通って延びる、図3の線V−Vに沿ったMISFET100の垂直断面に関する。右手の縦座標は、1012から1019cm−3を示す1E+12から1E+19で目盛られている。図面は、次の変化を示している。すなわち、それぞれグラフ140は伝導帯のエネルギーおよびグラフ142は荷電子帯のエネルギー、グラフ144は正味のドーパント濃度、およびグラフ146は正孔の濃度とグラフ148は電子の濃度である。

【0040】

InSbの295K(室温)での真性キャリア濃度は、2×1016cm−3である。グラフ146および148は、動作時の実際のキャリア濃度が、第3の層106の活性π領域のほぼ全体にわたって、この値よりも最高で2桁少ないことを示している。これは、グラフ144のほぼ平坦な部分に対応する。このことは、p+π接合104/106およびπn+接合106/112でそれぞれ起きるキャリアの排除と抽出によって、層106のπ領域中のキャリア濃度が低下していることを実証している。

【0041】

MISFET100は、キャリア抽出を行うように、ベース層102がソース114に対して約−0.35Vにバイアスされる、共通ソース構成で試験した。この電圧はVbsと規定され、ベース層102とソース110またはドレイン112で与えられる、ダイオード構造の最大動抵抗の位置に対応する。次に、通常極性のドレイン電圧およびゲート電圧を加えた。すなわち、小さな負のゲート−ソース電圧を使用した1つの場合を除いて、ドレインとゲートは、両方ともソース110に対して正にバイアスした。

【0042】

MISFET100の出力特性を図6に示す。図6は、隣り合うグラフの間の0.2Vのステップによる−0.2Vから1.4Vまでの一定ゲート電圧Vgsで、ドレイン電圧Vdsによるドレイン電流Idの変化を示す、160および162などの9つのグラフを含む。各グラフの僅かな屈曲部で示されるように、ドレイン電流は、約0.15Vのドレイン電圧で飽和し始めるのが理解できる。これは飽和が始まる非常に低い電圧であり、それは一般的に言って、InSbでは電子移動度が非常に大きいことによっている。それは、MISFET100が小さな電力を必要とすることを意味しているので有利である。出力特性は、一般にMISFETの伝統的な形のものであり、それはものになるMISFETが製造された証拠である。0.3Vのドレイン電圧Vdsで、ゲート電圧Vgsを−0.2から1.2Vに変えることで、約10と110mAmm−1の間でドレイン電流を切り換えることができる。

【0043】

MISFET100の伝達特性を図7に示す。図7は、一定ドレイン電圧のときにゲート電圧Vgsによる相互コンダクタンスgmの変化を示す、170および172などの5つのグラフを示す。ドレイン電圧は、隣り合うグラフの間で、0.1Vのステップで0.1Vから0.5Vまで変化する。MISFET100の最大直流相互コンダクタンスは、約120mSmm−1であり、閾値ゲート電圧は約0.4Vであることが理解できる。

【0044】

図6の電流軸上の交点で示されるように、MISFET100の漏れペデスタルは、約8mAmm−1である。最大ドレイン電流は約120mAmm−1であり、ゲート電圧とともに増加しなくなるドレイン電流で決定される。高いドレイン電圧で、電流/電圧のグラフの上向きの湾曲で示されるように、デバイスは、約0.5Vのドレイン電圧でゆっくりとブレークダウンし始める。これはバンド間トンネリングおよび表面漏れ(多分、表面トンネリングの発生)によるが、これらの両方を減らすことは可能である。MISFET100は、チャネルと直列に各々の側に、ベース−ソース/ドレインダイオードを順方向バイアスして測定された、約2.5オームのかなり大きな抵抗を有する。これは主に、コンタクトをとるプロセスによると考えられ、これによって理想的な値よりも相互コンダクタンス(したがってfT)は減少する。

【0045】

異なるゲート長をもつかなりの数の本発明のエンハンスメントモードMISFETの交流パラメータを、ドレイン電圧0.5VでSパラメータ法で測定し、ゲート電圧は最大のS21に合せた。結果は、Kooln法を用いて寄生ボンデイングパッド容量から分離した。図8は、ゲート長の関数として測定された最大電流利得遮断周波数fTを示す。結果は、下の方の線180で示されるように、LG−2依存性にしたがっている。これは、ピンチオフで速度が飽和していない場合に、理論的に期待される通りである。また、これらのMISFETについて、ゲート長の関数としてfTの値を計算し(モデル化の結果)、上の方の線182で示した。これらは、おそらく使用したチャネル移動度が比較的高かったために、速度飽和の影響を確かに示しているが、実験値と見事に一致している。このことは、ゲート長を減少させることで、更なる改良が可能であることを意味している。

【0046】

MISFET100の交流パラメータを図9に示す。測定された電流利得遮断周波数fTは74GHzである。現在知られている限りで、この値は、トランジスタの種類または材料に関係なく、ゲート長0.7μmのどのFETに関しても測定された最も高いfTである。この値は、研究目的で製造された従来技術のどのデバイス10で得られた最も優れた値(17GHz)よりも4倍以上大きく、さらに、これらのデバイスの代表的な値(10GHz)よりも7倍以上大きい。チャネルと直列になっている抵抗を減らすことで、さらにfTを大きくすることが当然可能である。単方向電力利得が1になる周波数fmaxは89GHzである。この値は、チャネル直列抵抗と現在は比較的小さい出力コンダクタンスとで制限されている。したがって、本発明のデバイスで、より大きなfmaxを達成することは当然可能である。fTおよびfmaxのこれらの値は、現在の従来技術に優る大きな改良を表している。したがって、本発明のデバイスで、より大きなfmaxを達成することは当然可能である。fTおよびfmaxのこれらの値は、従来技術に優る大きな改良を表し、さらに従来技術デバイスの性能にゲート溝形成が有害な影響及ぼすという仮説の正しいことを確認するものと推測される。

【0047】

本発明のデバイスについて得られた結果は、非常に有望であり、高速低電力デバイスを実現する本発明の可能性を示した。デバイス特性のモデリング、すなわち計算が、InSb材料のパラメータについて発表された結果または測定された結果を使用して、ATLAS、Silvaco Internationalからの2Dドリフト−拡散デバイスシュミレータを使用して行われた。モデル化された結果は、実験のp+p+πn+ダイオードおよび従来技術MISFETに対して試験し、漏れ電流、相互コンダクタンスおよびfTの点でよく一致していることが分かった。図3に示されるものに似ているが、ゲート長が1μmおよび0.25μmであるイオン注入エンハンスメントモードMISFET構造のモデル化の結果を、次の表2に示す。この表は、最大gm、fTおよびfmaxの理論的に達成可能な値を示す。0.25μmゲート長についての値は、ゲート絶縁物酸化膜厚さが、ゲート長と同じ係数で縮小されるものと仮定している。

【表2】

【0048】

これらの最大相互コンダクタンス値は、米国特許第5,382,814号の従来技術デバイスについて引用された25mSmm−1の値に比べてかなりの改良を表している。

【0049】

格子整合する必要はない。より小さなバンドギャップは、十分に狭いはずなので、FETの動作温度で真性導電率を支配的に示すのに十分なくらいに材料を精製することは可能である(現在Siでは不可能である)。このことは、295Kの室温で動作するデバイスに関して、0.5eV付近またはそれよりも小さなバンドギャップを意味するが、より高い動作温度のために、より大きなバンドギップの材料を使用してもよい。

【0050】

本発明のFETを製造するために使用できる材料の組合せには、PbSe/PbS、In1−yAlySb/In1−xAlxSb、InAs/InAs1−xPx、InAs1−xSbx/In1−yAlySb、InAs1−xSbx/InAs1−yPy、GaAs/Ga1−xAlxAs、In1−xGaxSb/In1−yAlySb、およびHg1−xCdxTe/Hg1−yCdyTeが含まれる。組成パラメータx、またはxとyの値は、適当に選ばなければならない。ゼロに等しいパラメータyを有するこれらの第1番目の特殊な場合である、InSb/In1−xAlxSbで、MISFETは構成された。

【0051】

次に、図10を参照して、本発明のデプレッションモードMISFETが、一般的に200で示されている。そのデプレッションモードMISFETは、弱くドープされたp型InSb基板(図示されない)を含み、その上に下記の厚さと組成を有する5つの連続した層202、204、206、208および210が成長される。すなわち、

第1の(ベース)層202、p+InSb厚さ2μm、Beドーパント濃度3×1018cm−3、

第2の(障壁)層204、p+In0.85Al0.15Sb厚さ20nm、Beドーパント濃度3×1018cm−3、

第3の(真性)層206、πInSb厚さ0.5μm、Beドーパント濃度1×1015cm−3、および

第4の(チャネル)層208、pInSb厚さ20nm、Siドーパント濃度3×1017cm−3、

第5の(ゲート絶縁)層210:SiO2厚さ70nm

である。

【0052】

MISFET200は、ゲート絶縁層210近くの電荷キャリアの閉じ込めを向上させるために、真性層206内に埋込みp型層211(鎖線で示される)を任意に含むことができる。MISFET200は、n+のソースおよびドレイン領域212および214を含み、それぞれは厚さが約0.2μmでSiドーパント濃度が2×1018cm−3であり、チャネル層208に対して抽出コンタクトを形成する。これらの領域が、チャネル層208を介して真性層206内でキャリア抽出を実現する。MISFET200は、連続したCrとAuの層(図示されない)からなる、ソースコンタクト216、ゲートコンタクト218およびドレインコンタクト220を有する。上に示した点を除けば、MISFET200は、前に述べたエンハンスメントモードデバイスに似た寸法である。メサ長12μm、メサ(およびゲート)幅50μmおよびゲートコンタクト長公称0.7μmを有する。層202から208は、分子線エピタキシー(MBE)で成長させた。ソース領域212およびドレイン領域214は、チャネル層208の中心領域をその上に成長しないようにマスクして、チャネル層208上にMBE成長で作った。このマスクを取り除いた後で、ゲート絶縁層210および電極218を堆積した。ソース領域212およびドレイン領域214は、その間にゲート凹部222を画定し、そのゲート凹部222内に、ゲート絶縁層210およびゲートコンタクト218が、チャネル層208に支持されて位置付けられている。凹部は、ゲート電極層218の高さよりも多少深くてもよい。ゲート凹部222が従来技術のようにエッチングで作成された溝でなく、サイドを立ち上げる成長で画定された凹部であること留意することが重要である。その結果、凹部222の形成は、チャネル形状に影響を及ぼす深すぎる溝に関連した問題を含まない。

【0053】

第5の層210は、30nmの陽極酸化膜の表面に堆積された、40nmのスパッタSiO2からなる。ゲートコンタクト218は、チャネル層208のソース領域212とドレイン領域214の間にある部分の大部分にわたって広がっている。エンハンスメントモードデバイスではソースとドレインの間に完成したチャネルを形成することが必要とされるのに対して、ゲートコンタクト218は存在するデバイスチャネルの変調/デプレッションに必要とされるだけであるから、ゲートコンタクト218の広がりの程度は余り重要でない。

【0054】

MISFET200では、電子の利用可能な供給源を形成するためにチャネル層208が使用される。一方で、この電子の供給源が、ゲート電極電位で電荷キャリアを欠乏させることができるソース212からドレイン214までの伝導経路を形成する。この経路は、チャネル層208または真性層206内に全部があってもよいし、またはこれらの層の一方に一部がありまた他方に一部があってもよい。MISFET200の閾値電圧は、チャネル層208の単位面積当たりのドーピングで決定される。すなわち、その層の厚さとゲート電極電位による電荷キャリアの欠乏可能度との積で決定される。この経路は、チャネル層208または真性層206内に全部があってもよいし、または、これらの層の一方に一部が、他方に一部があってもよい。MISFET200の閾値電圧は、チャネル層208の単位面積当たりのドーピングで決定される。すなわち、その層の厚さと単位体積当たりのドーピングの積で決定される。チャネル層208は、ゲート電圧の無い状態で、ソースドレイン電圧で生成された電界の方向にほぼ沿って延びる。この層は許容できないほどにU字形ではない。すなわち、この層内のどの凹部も、または凸部も、限度において50nmより小さい。

【0055】

ゲート絶縁酸化膜厚さがデバイス100のそれに等しいと仮定して、デプレッションモードMISFET200のモデル化された、すなわち理論的な、性能指数を得た。これらの指数を次の表3に示す。

【表3】

【0056】

次に図11を参照して、次のような実際の、またはモデル化された様々なデバイス技術に関して、ゲート長(μm)の関数として電流利得遮断周波数fT(GHz)を示す。すなわち、理想的なInSb(ゲート長とキャリア速度だけから計算された)、モデル化されたInSbエンハンスメントモードおよびデプレッションモードMISFET、InSbエンハンスメントモードMISFET100、InPおよびGaAsをベースにしたHEMT、およびシリコンNMOSである。

【0057】

MISFET100のfTに関する表2の結果は、図11の理想的な傾向線よりもほんの僅かに下にあり、オーバラップ容量による僅かな漸減を伴っており、MISFET100のようなエンハンスメントモードデバイスに見られる飽和作用を受ける。これはMISFET100の入力容量が小さいことによる。

【0058】

MISFET200は、異なる形のチャネルをもつことができる。厚さ20nmのチャネル層208は、ドーパント濃度が1×1015cm−3で厚さが20nmのπInSb層で、ゲート酸化膜層210から分離されたSiドーパント濃度2×1018cm−3厚さ3nmのInSbチャネル層と取り替えることができる。これは、厚さを減少させ真性π層206の中に埋め込んだチャネル層と同等であり、30%の動作速度向上をもたらすと推定される。この場合に、ソース領域212およびドレイン領域214は、真性層206と抽出コンタクトを形成する。

【0059】

次に図12を参照して、排除と抽出によってキャリア濃度が低下した種類のMISFETで、理論的に達成することができるベース電流/電圧IBVBS特性250を示す。ここで、ベース電流は、ベース層とソース領域の間を流れるものである。この電流は、MISFETのソース、ゲートおよびドレインを相互にバイアスするためではない。そうではなくて、真性デバイス領域のキャリア濃度および漏れ電流を減少させるためである。特性250は、現在達成可能なものよりもさらに低いショットキー/リードトラップ密度を含むデバイスに対応する。デバイスは、動作時に逆バイアスされるp+p+πn+ダイオード構造である。すなわち、そのデバイスのベース層はそのソース領域に対して負にバイアスされる。このバイアスのもとで、キャリアの抽出と排除が真性層で起り、抽出コンタクトとして作用する関連したπn+接合により、その真性層から電子(少数キャリア)が取り去られる。

【0060】

点252で、IBVBS特性250の勾配はゼロになり、無限大の差動インピーダンスを示す。この点で、「バックゲート」と呼ばれる、ベースバイアス電圧VBSによるゲート閾値電圧の変化は最小になるので、この点はベースバイアスの好ましい動作点である。

【0061】

上で参照されたモデル化の結果は、ドリフト−拡散シミュレーションによって得られ、約0.5μmのゲート長では顕著になると思われる弾道効果を無視している。この効果は、平均飽和速度を増加させ、したがって、より大きな性能向上の可能性につながるgmおよびfTを大きくする。

【0062】

本発明のトランジスタは、高速アナログデバイスの応用分野に潜在的に応用可能である。半絶縁基板または仮想基板上に成長すると、マイクロ波集積回路で使用できるだろう。InSbデバイスは、0.5Vよりも小さな低電圧で動作できるので、電池寿命を長くして、手持ち式の応用分野のために非常に有用な低電力消費を特徴とする。また、InSbデバイスは高い電子移動度をもち、それによってより高い最大の周波数を達成することを可能にし、あるいは、より丈夫な比較的長いゲート長で必要とされる動作速度を実現する。また、本発明のトランジスタは、ディジタルデバイスとしても、特に複雑さの少ない回路で、使用することができる。潜在的にPτ積が非常に小さいので、高速低電力の用途では非常に魅力がある。ここで、Pはスイッチング動作で消費されるエネルギーであり、τはスイッチ時間である。

【0063】

本発明は、高速で、低電力消費であり、InSb/In1−xAlxSbの固有の高電子移動度および飽和速度を利用する、FETを提供する。これらのFETは、高速低電力の性能を与え、キャリア排除と抽出の方法を組み込むことにより、InSb/In1−xAlxSbに通常関連したレベルよりも遥かに小さなオフ状態漏れ電流を示す。ゲート長が0.7μmの本発明のMISFETは、このゲート長に関してこれまで報告された最も高いfT値をもち、速度とオフ状態漏れの両方のさらなる向上を得ることができるものと期待される。

【技術分野】

【0001】

本発明は、電界効果トランジスタ(FET)に関する。より詳細には、本発明は、限定はしないが、狭いバンドギャップ半導体材料、すなわち0.5eV付近またはそれより小さなバンドギャップEGの半導体材料で作成された、MISFETのようなFETに関する。また、本発明は、室温よりも高い動作温度で使用するために、より広いバンドギャップ材料で作成されたFETにも関連する。

【背景技術】

【0002】

インジウムアンチモン(InSb)のような狭いバンドギャップ半導体には、非常に小さな電子有効質量、非常に大きな電子移動度および大きな飽和速度のような有用な性質がある。これらの性質は、超高速度の応用分野にとっては潜在的に非常に興味のあるものである。特にInSbは、高速超低消費電力トランジタ用の有望な材料である。なぜなら、GaAsはこれらの点で優れた性質を持っているが、低電界でのInSbの電子移動度μcはGaAsの9倍であり、その飽和速度vsatは5倍よりも大きい。また、InSbは、0.5μmを超える大きな弾道平均自由行程をもつと予測される。このことは、InSbは、低電力消費を可能にして非常に低い電圧で高速動作をする可能性を持っていることを示唆している。これにより、InSbは携帯型で高密度の応用分野にとって理想的であるはずである。295K(室温)でのシリコン、GaAsおよびInSbのいくつかの特性を、次の表1で比較する。

【表1】

【0003】

最近まで、InSbのバンドギャップが小さく、その結果真性キャリア濃度(〜2×1016cm−3)が高いために、SiおよびGaAsよりもそれぞれ6桁および9桁大きい、室温でInSbの潜在的に貴重な特性を得ることができなかった。この大きな真性キャリア濃度により、InSbデバイスは295Kの室温またはそれに近い通常動作温度で、少数キャリア濃度が通常のドーピングレベルで必要とされる値よりも遥かに大きく、大きな漏れ電流を示すことになる。これは、InSbおよびその他の狭いバンドギャップ材料を室温以上でデバイスで使用することを妨げる基本的な問題であると何年も考えられていた。しかし、米国特許第5,382,814号の主題の発明によって、その問題は克服された。該特許は、キャリア濃度への真性の寄与を平衡レベルよりずっと弱めるために、キャリアの排除(exclusion)および抽出(extraction)の現象を使用する、非平衡金属−絶縁体−半導体電界効果トランジスタ(non−equilibrium metal−insulator−semiconductor field effect transustor、MISFET)を開示する。この従来技術のMISFETは、逆バイアスされたp+p+πn+の構造である。ここで、pはInSb層を示し、pはひずみIn1−xAlxSb層であり(アンダーラインの付いたpは、pよりもバンドギャップが広いことを示す)、πは室温動作温度で真性である弱ドープp型領域を示し、さらに、+の上付き文字は高いドーパント濃度を示す。これら4つの層により、それぞれの隣合う層の対の間に3つの接合が画定される。すなわち、それぞれp+p+、p+πおよびπn+接合である。デバイスの活性領域はπ領域であり、少数キャリアは、抽出コンタクト(extracting contact)として作用するπn+接合でπ領域から取り去られる。p+π接合は、これらのキャリアの再導入を阻止する排除コンタクト(excluding contact)である。その結果、デバイスに印加されたバイアスの下で、少数キャリア濃度は減少し、多数キャリア濃度は、電荷中性を維持するように少数キャリア濃度とともに減少する。これによって、真性レベルよりも低いキャリア濃度が生成される。同様の効果は、冷却することで作り出される。ここで、「真性」という表現は、キャリアが主として価電子状態の活性化により発生し、ほぼ等しい数の少数キャリアと多数キャリアが半導体材料中に存在することを意味する、通常の解釈で使用されている。この表現は、単にドーピングレベルが低いことを示すために外因性材料(例えば、Si)について間違って使用されることがある。しかし、外因性材料では、キャリアは、主としてドナー状態かアクセプタ状態の活性化によって発生し、1つのタイプのキャリア(電子または正孔)が支配的である。

【0004】

米国特許第No.5,382,814号に開示されているデバイスは、1μm凹みゲート型エンハンスメントモードMISFET構造である。研究のために、この種の様々なデバイスが製造された。この種のデバイスで電流利得が1になる周波数fTは、55GHzであると理論的に予測されたが、たかだか10GHz付近の測定値が得られた。fTの値は、高周波トランジスタの当業者が性能指数として扱っている。ゲートコンタクト金属のオーバラップと関係するデバイス容量を、ソース領域とドレイン領域上に制限するようにしたにもかかわらず、これらのデバイスのどれでも、得られたfTの最もよい値は17GHzであった。このことは、InSbMISFETの高周波の可能性を完全に実現することは困難であることを示している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第5,382,814号

【発明の概要】

【発明が解決しようとする課題】

【0006】

電流利得遮断周波数fTの改良された値を示すことのできる、別の形のFETを提供することが本発明の目的である。

【課題を解決するための手段】

【0007】

本発明は、その電界効果トランジスタ(FET)の動作温度でバイアスされていない時に真性導電率を有する領域と、真性領域中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段とを含む種類の電界効果トランジスタであって、そのFETは、また、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmより大きくない、ソース領域とドレイン領域の間に延びるチャネルを画定する手段を含むことを特徴とする電界効果トランジスタ(FET)を提供する。そのようなチャネルの直線性からのずれは、限度において5nmより大きくないことが好ましい。「限度」という表現は、チャネルの任意の2つの領域、例えばチャネルの中心領域とソースまたはドレインに隣接する領域の間との最も大きな高さの差を意味する。

【0008】

本発明は、非常に改良された高周波性能を示し、従来技術に比べて非常に大きな値の電流利得遮断周波数を実現することができるという利点を提供する。従来技術によるMISFETは、特に、理論的な期待値よりも遥かに低い高周波で、期待はずれの性能をもつことが分かった。この理由は、当初理解されていなかった。しかし、その問題を解決しようとして、かなりの数の仮説が研究された。これらの仮説の1つが、MISFETゲート凹部をオーバエッチングすると、高周波性能を劣化させる可能性があるというものであった。介在するゲート溝の侵入なしに製造される本発明のデバイスは、高周波で遥かに優れた性能を示し、ゲート溝形成が性能に及ぼす有害な影響の仮説が、確認されたと推測される。

【0009】

1つの態様では、本発明のFETは、エンハンスメントモードMISFETである。本発明のFETは、真性領域を組み込んでいる層に高濃度のドーピングを導入することで作成される、ソースおよびドレイン領域を組み込むことができる。ソースおよびドレイン領域は、イオン注入、拡散ドーピング、合金化または損傷の導入によって作成することができる。真性領域は、残留としてp型にドープされ、ソースおよびドレイン領域と抽出コンタクト手段を形成してもよく、バイアスに応じて真性領域に形成されるチャネルはn型になるだろう。

【0010】

好ましい実施形態では、真性領域は、それ自体がベース領域との界面を有する障壁領域との界面を有し、真性、障壁およびベース領域(106、104、102)は同じ導電型であり、障壁領域は、真性およびベース領域よりも比較的広いバンドギャップをもち、かつ真性領域に対する排除コンタクトを提供する。

【0011】

本発明のFETは、動作時にエンハンスメントチャネルをその間に画定するように、ソース領域とドレイン領域の間にある真性領域の部分から絶縁され、かつ少なくともその部分にわたって延びる、ゲートコンタクトを含んでもよい。ベース領域は、少なくとも5×1017cm−3のドーパント濃度を含むp+InSbであってもよい。障壁領域は、少なくとも5×1017cm−3のドーパント濃度を含む、0.05から0.25の範囲のxをもつp+In1−xAlxSbであってもよい。真性領域は、5×1017cm−3より少ないドーパント濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のドーパント濃度を含む、πInSbであってもよい。さらに、ソースおよびドレイン領域は、少なくとも5×1017cm−3のドーパント濃度を含むn+InSbであってもよい。

【0012】

ベース、障壁および真性領域は、好ましくは層構造中に連続して配置され、ソースおよびドレイン領域は、イオン注入、拡散、合金化または損傷によって真性領域に作成され、さらに真性領域は好ましくはゲート絶縁層およびゲートコンタクトを支持するほぼ平坦な表面部分を有する。

【0013】

他の態様で、本発明のFETは、関連したチャネル領域を有するデプレッションモードMISFETである。そのFETは、真性領域かチャネル領域のいずれかの上に形成された高濃度にドープされたアウトグロースである、ソースおよびドレイン領域を組み込んでもよい。もしくは、これらの領域は、イオン注入、拡散、合金化または損傷によって作成されてよい。それらは、ゲートコンタクトを収容するゲート凹部をその間に画定してもよい。

【0014】

真性領域はp型であってもよく、それ自体かチャネル領域のいずれかが、ソースおよびドレイン領域と抽出コンタクト手段を形成してもよい。

【0015】

好ましい実施形態では、真性領域は、それ自体がベース領域との界面を有する障壁領域との界面を有し、真性、障壁およびベース領域が同じ導電型であり、障壁領域は、真性およびベース領域よりも比較的広いバンドギャップをもち、かつ真性領域に対する排除コンタクトを提供する。この実施形態では、

ベース領域は、少なくとも5×1017cm−3のアクセプタを含むp+InSbであってもよく、

障壁領域は、0.05から0.25の範囲のxを有するp+In1−xAlxSbであり、少なくとも5×1017cm−3のアクセプタを有してもよく、

真性領域は、5×1017cm−3より小さなアクセプタ、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタを含むπInSbであり、

ソースおよびドレイン領域は、少なくとも5×1017cm−3のドナーを含むn+InSbである。

【0016】

真性領域は、チャネル領域を支持してもよく、ベース、障壁、真性およびチャネル領域は層構造中に連続して配置され、ソースおよびドレイン領域はチャネル領域上に成長され、さらにチャネル領域は、ゲート絶縁層およびゲートコンタクトを支持するほぼ平坦な表面部分を有する。

【0017】

ソースおよびドレイン領域は、その間にゲート凹部を画定してもよく、チャネル領域は、ゲート絶縁層およびゲートコンタクトを支持する凹部の端部に表面部分を有する。

【0018】

チャネル領域は、真性領域の部分の間にあってもよく、真性領域は、ソースおよびドレイン領域との組合せで抽出コンタクト手段を形成する。

【0019】

ベース、障壁および真性領域は、好ましくは層構造中に連続して配置され、真性領域はチャネル領域を含み、ソースおよびドレイン領域を支持する。

【0020】

真性領域中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段は、基板バイアス電圧変化によるゲート閾値電圧の変化が最小となる無限大の差動インピーダンスの点で、FETをバイアスするように構成されるのが好ましい。

【0021】

他の態様で、本発明は、その真性領域中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段を含む種類のFETを作成する方法であって、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmより大きくないように、ソース領域とドレイン領域の間に延びるチャネルを画定することを含むことを特徴とする方法を提供する。チャネルの直線性からのそのようなずれは、限度において5nmより大きくないことが好ましい。

【0022】

本発明をより十分に理解するために、添付の図面を参照して単なる例として本発明の実施形態を次に説明する。

【図面の簡単な説明】

【0023】

【図1】一定の縮尺で描かれていない従来技術MISFETの模式的な断面図である。

【図2】拡大して図1の従来技術MISFETのゲートを示す図である。

【図3】凹状でも凸状でもない層をもつ理想的な形で図示された、本発明のnチャネルエンハンスメントモードMISFETの模式的な断面図である(一定の縮尺で描かれていない)。

【図4】小程度のゲート領域凹面を示す、本発明のnチャネルエンハンスメントモードMISFETの中心領域の模式的な断面図である。

【図5】本発明の逆バイアスされたp+p+πn+MISFET構造のバンド構造図であり、図3の線V−Vの断面に対応する。

【図6】図3のMISFETの出力特性を示す図である。

【図7】図3のMISFETの伝達特性を示す図である。

【図8】図3のMISFETおよび同様のモデル化されたデバイスについて、ゲート長による電流利得遮断周波数の変化を示す図である。

【図9】図3のMISFETについて、周波数による交流利得パラメータの変化を示す図である。

【図10】本発明のnチャネルデプレッションモードMISFETの模式的な断面図である(一定の縮尺で描かれていない)。

【図11】様々なデバイス技術について、測定されたものとモデル化されたもの両方で、ゲート長(μm)の関数として電流利得遮断周波数fT(GHz)の変化を示す図である。

【図12】キャリア濃度を排除と抽出で低減させた種類のMISFETについて、理論的に達成できるベース電流/電圧特性を示す図である。

【発明を実施するための形態】

【0024】

次に図1を参照して、米国特許第5,382,814号に開示された種類の従来技術MISFET10が示されている。MISFET10は、インジウムアンチモン(InSb)およびインジウムアルミニウムアンチモン(In1−xAlxSb)の層から成る。MISFET10は、次のような4層の半導体材料を支持する基板(図示されない)を有する。すなわち、高濃度にドープされた狭いバンドギャップp型(p+)ベース層12、比較的広いバンドギャップで高濃度にドープされたp型(p+)障壁層14、低濃度にドープされたp型(π)活性層16および高濃度にドープされた狭いバンドギャップのn型(n+)ソース/ドレイン層18である。層12、16および18はInSbであり、層14はIn1−xAlxSbである。π活性層16は、295Kの室温で主に真性導電率をもつが、一方でその他の層12、14および18は、この温度で主に外因性導電率をもつ。隣接する層の対12/14、14/16および16/18の間の界面は、それぞれp+p+、p+π、およびπn+接合であり、これらの最初の2つはヘテロ接合であり、最後のものはホモ接合である。p+π接合14/16およびπn+接合16/18は、それぞれ排除コンタクトと抽出コンタクトである。

【0025】

MISFET10には、それぞれコンタクト24を有するソース領域20とコンタクト26を有するドレイン領域22があり、それらの領域は、n+層18を通り越してエッチングして形成された間にあるゲート凹部または溝28を有する。ゲート凹部の底および側面は、シリコン酸化膜ゲート絶縁物30および金属ゲートコンタクト32で覆われている。ソース20とドレイン22の間に短絡ができないように、凹部28がn+層18を完全に(または、ほぼ完全に)通り越して延びることが、MISFET10の動作のために必要である。

【0026】

通常の動作でバイアスが加えられた時に、キャリアの抽出および排除が、MISFET10で起きる。層12から18までで、p+p+πn+ダイオードが形成され、そのダイオードは動作状態では逆バイアスされる。すなわち、ベース層12がソース領域20に対して負にバイアスされる。このバイアスの下で、πn+接合16/18は、抽出コンタクトとして作用してπ層16から電子(少数キャリア)を取り去る。そのような電子をp+障壁層14から補充することはできない。何故ならば、p+障壁層14は、p+ベース層12と組み合わさって排除コンタクトとして作用し、π層16への電子の流れに対して電位障壁を形成するからである。このようにして、MISFET10がバイアスされたときに、π層16の電子濃度は減少し、それと共にπ層16の正孔濃度は電荷中性の理由ために減少する。

【0027】

このために層16の導電率は非常に減少し、したがって、ソース20とドレイン22の間の漏れ電流が減る。

【0028】

述べたように、製造されたMISFET10の試験例は、期待を裏切る高周波での性能を示した。これらのデバイスの電流利得遮断周波数fT(その周波数で電流利得が1になる)の理論的な値は、55GHzであったが、ゲート金属のオーバラップに関連するデバイス容量を、ソースとドレイン領域上に制限するようにしたにもかかわらず、測定値は10GHz付近に過ぎなかった。この理由は理解されていなかった。しかし、不満足な高周波性能の原因であるアーチファクト候補を特定しようとして、かなりの数の仮説が提起され、理論的に研究された。これらの仮説の1つが、ゲート凹部または溝の深さと関連付けられた。理論的な計算により、ゲート凹部が深くエッチングされすぎると(それは制御し測定するのが難しい)、高周波性能は劣化することが示された。理論的な状況を図2に示す。ここでは、ゲート凹部28を拡大して示す。

【0029】

MISFET10が成り立つためには、ゲート凹部28は、ソースとドレインの間に短絡が生じないないようにn+領域18のほとんどを通り越して、好ましくは完全に通り越して、延びなければならない。この凹部がオーバエッチングされると、凹部はπ領域16の中まで続き、試験デバイスでは深さが100nm程度の反転ステップ34が形成されたと見なされている。そうなれば、ソース20とドレイン22の間のMISFETチャネル(図示されない)は、意図した通りの直線ではなくてU字状になるはずである(エンハンスメントモードMISFETでは、バイアスの印加に応じた動作状態でだけ、ゲート電極の下にチャネルが形成される)。

【0030】

ソースとドレインの間の電荷キャリアの走行時間を最小にするためには、ソース−ドレイン電界は、チャネルの長手方向に向いているべきであるが、このことは、この電界と平行に延びるU字状チャネルの部分だけで可能になる。そのようなチャネルでは、チヤネルがソース−ドレイン方向に延びない領域があるはずであり、したがって、ソース−ドレイン電界は、チャネルの長手方向に対して傾いている。その結果、長手方向の電界成分は、電界がこの方向に平行である場合よりも弱くなる。それによって、電界が完全に長手方向にある場合に比べると、ソースとドレインの間の電荷キャリアの走行時間は長くなる。このようにして、fTはこの走行時間と関連するので、U字状チャネルでfTは下がると推定される。正しければ、この理論的な解析は、エッチングされたゲート凹部を避けるべきであることを示している。この仮説は、以下に述べる本発明の例の製造で検証した。

【0031】

次に図3を参照して、本発明のエンハンスメントモードMISFETを、一般的に100で示す。それは弱くドープしたp型InSb基板(図示されない)を含み、そのp型InSb基板の上に、下記の厚さと組成を有する第1の層102、第2の層104、第3の層106および第4の層108を連続して成長させる。すなわち、

第1の(ベース)層102、p+InSb厚さ2μm、Beドーパント濃度3×1018cm−3、

第2の(障壁)層104、p+In0.85Al0.15Sb厚さ20nm、Beドーパント濃度3×1018cm−3、

第3の(真性)層106、πInSb厚さ0.5μm、Beドーパント濃度1×1015cm−3、および

第4の(絶縁)層108、SiO2厚さ70nm、

である。

【0032】

より一般的には、本発明のInSb/InAlSbFETの適当な組成は次のようである。すなわち、

ベース領域、少なくとも5×1017cm−3のアクセプタ濃度を有するp+InSb、

障壁領域、0.05から0.25の範囲のxを有するp+In1−xAlxSbであり、少なくとも5×1017cm−3のアクセプタ濃度を有する、および

真性領域、5×1017cm−3よりも小さなアクセプタ濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタ濃度をもつπInSbである。

【0033】

MISFET100は、絶縁層108近くの電荷キャリアの閉込めを向上させるために、真性層106の中に埋込みp型層109(鎖線で示されている)を任意に含むことができる。MISFET100は、それぞれが少なくとも5×1017cm−3の中性アクセプタ濃度を有し厚さがほぼ0.2μmである、n+のソース領域110およびドレイン領域112を含む。MISFET100は、連続したCrとAuの層(図示されない)から成る、ソースコンタクト114、ゲートコンタクト116およびドレインコンタクト118を有する。MISFET100のメサ長は12μmであり、これが図面の面内で全幅となっている。そのメサ(およびゲート)幅は50μmであり、これは図面の面に垂直に延びる寸法である。ゲートコンタクト116(図面の面内の水平寸法)の長さは、公称0.7μmである。ここで、「公称」とは、必要な長さを作成するのに適当な寸法のリソグラフィマスクが使用されたことを意味し、長さは測定しなかった。公称ゲート長が0.7から2μmの範囲で、メサ幅が100μmである、同様な構造および種類の他のデバイスも製造した。層102から108は、分子線エピタキシで成長させた。ソース領域110およびドレイン領域112は、単位面積当たり5×1013cm−2の線量の70keVS32イオンを使用してイオン注入で作った。イオンは、基板温度100℃で、結晶の<110>方向に対する垂線から10゜の角度で自然陽極酸化マスクを通して注入した。これに続いて、ドーパントを活性化し損傷を取り除くために、Si3N4キャップを付けた状態で420℃で10秒間の急速熱アニールを行った。次にサンプルを陽極酸化し、酸化膜をはがして、コンタクトを付ける前に損傷を受けた材料を取り除いた。MISFET100を製造するプロセスにより、層106および108は少しばかりの凹面となった。しかし、チャネルの中心領域(ゲートバイアス電圧に応じて形成された)とソースおよびドレインに隣接するチャネルの外側領域との間に、50nmよりも大きな高さの差は生じなかった。注入によって、ソース領域110およびドレイン領域112へのコンタクトを可能にする伝導経路を形成した。

【0034】

第4の層108は、30nmの陽極酸化膜の表面に堆積された40nmのスパッタSiO2で構成された。層108全体としては、光分解SiO2が好ましかっただろうが、これは利用できなかった。

【0035】

ゲートコンタクト116は、ソース領域110とドレイン領域112の間にあり、これらの領域と少しオーバラップしている第3の層すなわちπ層106の部分の全体にわたって広がっている。理想的には、デバイス容量を最小にするために、オーバラップはゼロであるべきであるが、エンハンスメントモードデバイスでは、動作時にチャネル領域を要求されるように形成することができるように、ゲートコンタクトは、これらの領域の間に十分に広がっていることが重要である。

【0036】

MISFET100では、ソース領域110とドレイン領域112の間の直線性が、ゲート116の形状で大きくぼかされることはなく、従来技術デバイス10で経験された100nmの程度まではないことは確かである。

【0037】

図3は理想化された図である。実際には、本発明のFETは、製造プロセスでの不正確さによって生じた理想的な形状寸法からのずれによる、平面でない層を有してもよい。すなわち、チャネルのひどすぎる変形を引き起こさない限りは、真性領域は、凹状でも、凸状でも、または起伏があってもよい。図4に凹面を示す。ここでは、図3に関して記述されたものと同等な部分は、接尾文字Rを付けて同じように参照する。図4は、実際のデバイスにより近いことを除いては、MISFET100と同等のFETの中心領域120を示す。真性層106R、ゲート絶縁層108Rおよびゲートコンタクト116Rが含まれ、それらは全て凹状でV字形凹部122を画定している。凹部122の底は、絶縁層108Rの中心にある頂点124で画定されている。凹部122の深さはHで示され、それは50nmよりも大きくない。ゲートバイアス電圧の印加に応じて、チャネル(図示されない)が形成されたときに、頂点124の下のチャネル(図示されない)の中心領域と、ソース110Rとドレイン112Rに隣接するチャネルの外側領域との間に、図面内の上下方向に存在する50nmよりも大きな差が、凹部122によって、もたらされることはない。言い換えると、ゲート領域が平面でないことで生じるチャネルの直線性からのずれは、50nmよりも小さい。ここで、チャネルが形成され、チャネルの形状を決定するゲート領域は、ゲート絶縁層108Rに隣接する真性層106Rの上部である。本発明の他の実施形態では、それはチャネルの中心部分を収容するデバイスの活性領域である。

【0038】

凹部深さHおよび結果的なチャネルの直線性からのずれは、5nmよりも大きくないことが好ましい。その結果、形成されたチャネルは、ソース、ゲートおよびドレインの電圧で決定されるように、ほぼ延びることができる。後で説明するように、これによって、従来技術デバイス10に比べて著しく改良された性能を生じる。

【0039】

図5は、MISFET100で、第1の層102の下端から測定されたμm単位の上下方向の距離xの関数として、バンド構造図および関連した電荷キャリア密度を示す。この図面に示されるデータは、逆バイアスされたp+p+πn+構造に関するものである。そのデータは、第1(p+)の層102、第2(p+)の層104および第3(π)の層106、さらに(n+)ソース領域110を通って延びる、図3の線V−Vに沿ったMISFET100の垂直断面に関する。右手の縦座標は、1012から1019cm−3を示す1E+12から1E+19で目盛られている。図面は、次の変化を示している。すなわち、それぞれグラフ140は伝導帯のエネルギーおよびグラフ142は荷電子帯のエネルギー、グラフ144は正味のドーパント濃度、およびグラフ146は正孔の濃度とグラフ148は電子の濃度である。

【0040】

InSbの295K(室温)での真性キャリア濃度は、2×1016cm−3である。グラフ146および148は、動作時の実際のキャリア濃度が、第3の層106の活性π領域のほぼ全体にわたって、この値よりも最高で2桁少ないことを示している。これは、グラフ144のほぼ平坦な部分に対応する。このことは、p+π接合104/106およびπn+接合106/112でそれぞれ起きるキャリアの排除と抽出によって、層106のπ領域中のキャリア濃度が低下していることを実証している。

【0041】

MISFET100は、キャリア抽出を行うように、ベース層102がソース114に対して約−0.35Vにバイアスされる、共通ソース構成で試験した。この電圧はVbsと規定され、ベース層102とソース110またはドレイン112で与えられる、ダイオード構造の最大動抵抗の位置に対応する。次に、通常極性のドレイン電圧およびゲート電圧を加えた。すなわち、小さな負のゲート−ソース電圧を使用した1つの場合を除いて、ドレインとゲートは、両方ともソース110に対して正にバイアスした。

【0042】

MISFET100の出力特性を図6に示す。図6は、隣り合うグラフの間の0.2Vのステップによる−0.2Vから1.4Vまでの一定ゲート電圧Vgsで、ドレイン電圧Vdsによるドレイン電流Idの変化を示す、160および162などの9つのグラフを含む。各グラフの僅かな屈曲部で示されるように、ドレイン電流は、約0.15Vのドレイン電圧で飽和し始めるのが理解できる。これは飽和が始まる非常に低い電圧であり、それは一般的に言って、InSbでは電子移動度が非常に大きいことによっている。それは、MISFET100が小さな電力を必要とすることを意味しているので有利である。出力特性は、一般にMISFETの伝統的な形のものであり、それはものになるMISFETが製造された証拠である。0.3Vのドレイン電圧Vdsで、ゲート電圧Vgsを−0.2から1.2Vに変えることで、約10と110mAmm−1の間でドレイン電流を切り換えることができる。

【0043】

MISFET100の伝達特性を図7に示す。図7は、一定ドレイン電圧のときにゲート電圧Vgsによる相互コンダクタンスgmの変化を示す、170および172などの5つのグラフを示す。ドレイン電圧は、隣り合うグラフの間で、0.1Vのステップで0.1Vから0.5Vまで変化する。MISFET100の最大直流相互コンダクタンスは、約120mSmm−1であり、閾値ゲート電圧は約0.4Vであることが理解できる。

【0044】

図6の電流軸上の交点で示されるように、MISFET100の漏れペデスタルは、約8mAmm−1である。最大ドレイン電流は約120mAmm−1であり、ゲート電圧とともに増加しなくなるドレイン電流で決定される。高いドレイン電圧で、電流/電圧のグラフの上向きの湾曲で示されるように、デバイスは、約0.5Vのドレイン電圧でゆっくりとブレークダウンし始める。これはバンド間トンネリングおよび表面漏れ(多分、表面トンネリングの発生)によるが、これらの両方を減らすことは可能である。MISFET100は、チャネルと直列に各々の側に、ベース−ソース/ドレインダイオードを順方向バイアスして測定された、約2.5オームのかなり大きな抵抗を有する。これは主に、コンタクトをとるプロセスによると考えられ、これによって理想的な値よりも相互コンダクタンス(したがってfT)は減少する。

【0045】

異なるゲート長をもつかなりの数の本発明のエンハンスメントモードMISFETの交流パラメータを、ドレイン電圧0.5VでSパラメータ法で測定し、ゲート電圧は最大のS21に合せた。結果は、Kooln法を用いて寄生ボンデイングパッド容量から分離した。図8は、ゲート長の関数として測定された最大電流利得遮断周波数fTを示す。結果は、下の方の線180で示されるように、LG−2依存性にしたがっている。これは、ピンチオフで速度が飽和していない場合に、理論的に期待される通りである。また、これらのMISFETについて、ゲート長の関数としてfTの値を計算し(モデル化の結果)、上の方の線182で示した。これらは、おそらく使用したチャネル移動度が比較的高かったために、速度飽和の影響を確かに示しているが、実験値と見事に一致している。このことは、ゲート長を減少させることで、更なる改良が可能であることを意味している。

【0046】

MISFET100の交流パラメータを図9に示す。測定された電流利得遮断周波数fTは74GHzである。現在知られている限りで、この値は、トランジスタの種類または材料に関係なく、ゲート長0.7μmのどのFETに関しても測定された最も高いfTである。この値は、研究目的で製造された従来技術のどのデバイス10で得られた最も優れた値(17GHz)よりも4倍以上大きく、さらに、これらのデバイスの代表的な値(10GHz)よりも7倍以上大きい。チャネルと直列になっている抵抗を減らすことで、さらにfTを大きくすることが当然可能である。単方向電力利得が1になる周波数fmaxは89GHzである。この値は、チャネル直列抵抗と現在は比較的小さい出力コンダクタンスとで制限されている。したがって、本発明のデバイスで、より大きなfmaxを達成することは当然可能である。fTおよびfmaxのこれらの値は、現在の従来技術に優る大きな改良を表している。したがって、本発明のデバイスで、より大きなfmaxを達成することは当然可能である。fTおよびfmaxのこれらの値は、従来技術に優る大きな改良を表し、さらに従来技術デバイスの性能にゲート溝形成が有害な影響及ぼすという仮説の正しいことを確認するものと推測される。

【0047】

本発明のデバイスについて得られた結果は、非常に有望であり、高速低電力デバイスを実現する本発明の可能性を示した。デバイス特性のモデリング、すなわち計算が、InSb材料のパラメータについて発表された結果または測定された結果を使用して、ATLAS、Silvaco Internationalからの2Dドリフト−拡散デバイスシュミレータを使用して行われた。モデル化された結果は、実験のp+p+πn+ダイオードおよび従来技術MISFETに対して試験し、漏れ電流、相互コンダクタンスおよびfTの点でよく一致していることが分かった。図3に示されるものに似ているが、ゲート長が1μmおよび0.25μmであるイオン注入エンハンスメントモードMISFET構造のモデル化の結果を、次の表2に示す。この表は、最大gm、fTおよびfmaxの理論的に達成可能な値を示す。0.25μmゲート長についての値は、ゲート絶縁物酸化膜厚さが、ゲート長と同じ係数で縮小されるものと仮定している。

【表2】

【0048】

これらの最大相互コンダクタンス値は、米国特許第5,382,814号の従来技術デバイスについて引用された25mSmm−1の値に比べてかなりの改良を表している。

【0049】

格子整合する必要はない。より小さなバンドギャップは、十分に狭いはずなので、FETの動作温度で真性導電率を支配的に示すのに十分なくらいに材料を精製することは可能である(現在Siでは不可能である)。このことは、295Kの室温で動作するデバイスに関して、0.5eV付近またはそれよりも小さなバンドギャップを意味するが、より高い動作温度のために、より大きなバンドギップの材料を使用してもよい。

【0050】

本発明のFETを製造するために使用できる材料の組合せには、PbSe/PbS、In1−yAlySb/In1−xAlxSb、InAs/InAs1−xPx、InAs1−xSbx/In1−yAlySb、InAs1−xSbx/InAs1−yPy、GaAs/Ga1−xAlxAs、In1−xGaxSb/In1−yAlySb、およびHg1−xCdxTe/Hg1−yCdyTeが含まれる。組成パラメータx、またはxとyの値は、適当に選ばなければならない。ゼロに等しいパラメータyを有するこれらの第1番目の特殊な場合である、InSb/In1−xAlxSbで、MISFETは構成された。

【0051】

次に、図10を参照して、本発明のデプレッションモードMISFETが、一般的に200で示されている。そのデプレッションモードMISFETは、弱くドープされたp型InSb基板(図示されない)を含み、その上に下記の厚さと組成を有する5つの連続した層202、204、206、208および210が成長される。すなわち、

第1の(ベース)層202、p+InSb厚さ2μm、Beドーパント濃度3×1018cm−3、

第2の(障壁)層204、p+In0.85Al0.15Sb厚さ20nm、Beドーパント濃度3×1018cm−3、

第3の(真性)層206、πInSb厚さ0.5μm、Beドーパント濃度1×1015cm−3、および

第4の(チャネル)層208、pInSb厚さ20nm、Siドーパント濃度3×1017cm−3、

第5の(ゲート絶縁)層210:SiO2厚さ70nm

である。

【0052】

MISFET200は、ゲート絶縁層210近くの電荷キャリアの閉じ込めを向上させるために、真性層206内に埋込みp型層211(鎖線で示される)を任意に含むことができる。MISFET200は、n+のソースおよびドレイン領域212および214を含み、それぞれは厚さが約0.2μmでSiドーパント濃度が2×1018cm−3であり、チャネル層208に対して抽出コンタクトを形成する。これらの領域が、チャネル層208を介して真性層206内でキャリア抽出を実現する。MISFET200は、連続したCrとAuの層(図示されない)からなる、ソースコンタクト216、ゲートコンタクト218およびドレインコンタクト220を有する。上に示した点を除けば、MISFET200は、前に述べたエンハンスメントモードデバイスに似た寸法である。メサ長12μm、メサ(およびゲート)幅50μmおよびゲートコンタクト長公称0.7μmを有する。層202から208は、分子線エピタキシー(MBE)で成長させた。ソース領域212およびドレイン領域214は、チャネル層208の中心領域をその上に成長しないようにマスクして、チャネル層208上にMBE成長で作った。このマスクを取り除いた後で、ゲート絶縁層210および電極218を堆積した。ソース領域212およびドレイン領域214は、その間にゲート凹部222を画定し、そのゲート凹部222内に、ゲート絶縁層210およびゲートコンタクト218が、チャネル層208に支持されて位置付けられている。凹部は、ゲート電極層218の高さよりも多少深くてもよい。ゲート凹部222が従来技術のようにエッチングで作成された溝でなく、サイドを立ち上げる成長で画定された凹部であること留意することが重要である。その結果、凹部222の形成は、チャネル形状に影響を及ぼす深すぎる溝に関連した問題を含まない。

【0053】

第5の層210は、30nmの陽極酸化膜の表面に堆積された、40nmのスパッタSiO2からなる。ゲートコンタクト218は、チャネル層208のソース領域212とドレイン領域214の間にある部分の大部分にわたって広がっている。エンハンスメントモードデバイスではソースとドレインの間に完成したチャネルを形成することが必要とされるのに対して、ゲートコンタクト218は存在するデバイスチャネルの変調/デプレッションに必要とされるだけであるから、ゲートコンタクト218の広がりの程度は余り重要でない。

【0054】

MISFET200では、電子の利用可能な供給源を形成するためにチャネル層208が使用される。一方で、この電子の供給源が、ゲート電極電位で電荷キャリアを欠乏させることができるソース212からドレイン214までの伝導経路を形成する。この経路は、チャネル層208または真性層206内に全部があってもよいし、またはこれらの層の一方に一部がありまた他方に一部があってもよい。MISFET200の閾値電圧は、チャネル層208の単位面積当たりのドーピングで決定される。すなわち、その層の厚さとゲート電極電位による電荷キャリアの欠乏可能度との積で決定される。この経路は、チャネル層208または真性層206内に全部があってもよいし、または、これらの層の一方に一部が、他方に一部があってもよい。MISFET200の閾値電圧は、チャネル層208の単位面積当たりのドーピングで決定される。すなわち、その層の厚さと単位体積当たりのドーピングの積で決定される。チャネル層208は、ゲート電圧の無い状態で、ソースドレイン電圧で生成された電界の方向にほぼ沿って延びる。この層は許容できないほどにU字形ではない。すなわち、この層内のどの凹部も、または凸部も、限度において50nmより小さい。

【0055】

ゲート絶縁酸化膜厚さがデバイス100のそれに等しいと仮定して、デプレッションモードMISFET200のモデル化された、すなわち理論的な、性能指数を得た。これらの指数を次の表3に示す。

【表3】

【0056】

次に図11を参照して、次のような実際の、またはモデル化された様々なデバイス技術に関して、ゲート長(μm)の関数として電流利得遮断周波数fT(GHz)を示す。すなわち、理想的なInSb(ゲート長とキャリア速度だけから計算された)、モデル化されたInSbエンハンスメントモードおよびデプレッションモードMISFET、InSbエンハンスメントモードMISFET100、InPおよびGaAsをベースにしたHEMT、およびシリコンNMOSである。

【0057】

MISFET100のfTに関する表2の結果は、図11の理想的な傾向線よりもほんの僅かに下にあり、オーバラップ容量による僅かな漸減を伴っており、MISFET100のようなエンハンスメントモードデバイスに見られる飽和作用を受ける。これはMISFET100の入力容量が小さいことによる。

【0058】

MISFET200は、異なる形のチャネルをもつことができる。厚さ20nmのチャネル層208は、ドーパント濃度が1×1015cm−3で厚さが20nmのπInSb層で、ゲート酸化膜層210から分離されたSiドーパント濃度2×1018cm−3厚さ3nmのInSbチャネル層と取り替えることができる。これは、厚さを減少させ真性π層206の中に埋め込んだチャネル層と同等であり、30%の動作速度向上をもたらすと推定される。この場合に、ソース領域212およびドレイン領域214は、真性層206と抽出コンタクトを形成する。

【0059】

次に図12を参照して、排除と抽出によってキャリア濃度が低下した種類のMISFETで、理論的に達成することができるベース電流/電圧IBVBS特性250を示す。ここで、ベース電流は、ベース層とソース領域の間を流れるものである。この電流は、MISFETのソース、ゲートおよびドレインを相互にバイアスするためではない。そうではなくて、真性デバイス領域のキャリア濃度および漏れ電流を減少させるためである。特性250は、現在達成可能なものよりもさらに低いショットキー/リードトラップ密度を含むデバイスに対応する。デバイスは、動作時に逆バイアスされるp+p+πn+ダイオード構造である。すなわち、そのデバイスのベース層はそのソース領域に対して負にバイアスされる。このバイアスのもとで、キャリアの抽出と排除が真性層で起り、抽出コンタクトとして作用する関連したπn+接合により、その真性層から電子(少数キャリア)が取り去られる。

【0060】

点252で、IBVBS特性250の勾配はゼロになり、無限大の差動インピーダンスを示す。この点で、「バックゲート」と呼ばれる、ベースバイアス電圧VBSによるゲート閾値電圧の変化は最小になるので、この点はベースバイアスの好ましい動作点である。

【0061】

上で参照されたモデル化の結果は、ドリフト−拡散シミュレーションによって得られ、約0.5μmのゲート長では顕著になると思われる弾道効果を無視している。この効果は、平均飽和速度を増加させ、したがって、より大きな性能向上の可能性につながるgmおよびfTを大きくする。

【0062】

本発明のトランジスタは、高速アナログデバイスの応用分野に潜在的に応用可能である。半絶縁基板または仮想基板上に成長すると、マイクロ波集積回路で使用できるだろう。InSbデバイスは、0.5Vよりも小さな低電圧で動作できるので、電池寿命を長くして、手持ち式の応用分野のために非常に有用な低電力消費を特徴とする。また、InSbデバイスは高い電子移動度をもち、それによってより高い最大の周波数を達成することを可能にし、あるいは、より丈夫な比較的長いゲート長で必要とされる動作速度を実現する。また、本発明のトランジスタは、ディジタルデバイスとしても、特に複雑さの少ない回路で、使用することができる。潜在的にPτ積が非常に小さいので、高速低電力の用途では非常に魅力がある。ここで、Pはスイッチング動作で消費されるエネルギーであり、τはスイッチ時間である。

【0063】

本発明は、高速で、低電力消費であり、InSb/In1−xAlxSbの固有の高電子移動度および飽和速度を利用する、FETを提供する。これらのFETは、高速低電力の性能を与え、キャリア排除と抽出の方法を組み込むことにより、InSb/In1−xAlxSbに通常関連したレベルよりも遥かに小さなオフ状態漏れ電流を示す。ゲート長が0.7μmの本発明のMISFETは、このゲート長に関してこれまで報告された最も高いfT値をもち、速度とオフ状態漏れの両方のさらなる向上を得ることができるものと期待される。

【特許請求の範囲】

【請求項1】

電界効果トランジスタ(FET)の動作温度でバイアスされていない時に真性導電率を有する領域(106)と、真性領域(106)中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段とを含む種類の電界効果トランジスタ(FET)であって、FET(100)が、また、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmよりも大きくない、ソース領域(110)とドレイン領域(112)の間に延びるチャネルを画定するための手段を含むことを特徴とする電界効果トランジスタ。

【請求項2】

チャネルの直線性からのずれが、限度において5nmより大きくないことを特徴とする請求項1に記載のFET。

【請求項3】

エンハンスメントモードMISFET(100)であることを特徴とする請求項1または2に記載のFET。

【請求項4】

高濃度n型であるソースおよびドレイン領域(110、112)を組み込んでいることを特徴とする請求項1、2または3に記載のFET。

【請求項5】

真性領域(106)がp型であり、ソースおよびドレイン領域(110、112)との組合せで抽出コンタクト手段を形成することを特徴とする請求項1から4のいずれか一項に記載のFET。

【請求項6】

真性領域(106)が、それ自体がベース領域(102)との界面を有する障壁領域(104)との界面を有し、真性、障壁およびベースの領域(106、104、102)が同じ導電型であり、障壁領域(104)が真性およびベースの領域(106、102)よりも比較的広いバンドギャップをもち、かつ真性領域(106)に対する排除コンタクトを提供することを特徴とする請求項1から5のいずれか一項に記載のFET。

【請求項7】

動作時にエンハンスメントチャネルをソースとドレイン領域(110、112)の間に画定するように、ソースとドレイン領域(110、112)の間の真性領域(106)の部分から絶縁され、かつ少なくともその部分にわたって延びる、ゲートコンタクト(116)を含むことを特徴とする請求項6に記載のFET。

【請求項8】

a)ベース領域(102)が、p+InSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

b)障壁領域(104)が、0.05から0.25の範囲のxをもつp+In1−xAlxSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

c)真性領域(106)が、5×1017cm−3より少ないアクセプタ濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタ濃度をもつπInSbであり、

d)ソースおよびドレイン領域(110、112)が、少なくとも5×1017cm−3のドーパント濃度をもつn+InSbであることを特徴とする請求項6または7に記載のFET。

【請求項9】

ベース、障壁および真性領域(102、104、106)が、層構造中に連続して配置され、真性領域(106)が、ゲート絶縁層(108)およびゲートコンタクト(116)を支持するほぼ平坦な表面部分を有することを特徴とする請求項5、6、7または8に記載のFET。

【請求項10】

結合されたチャネル領域(208)を有するデプレッションモードMISFET(200)であることを特徴とする請求項1または2に記載のFET。

【請求項11】

真性領域(206)かチャネル領域(208)のいずれかの上に形成された高濃度にドープされたアウトグロースであるソースおよびドレイン領域(212、214)を組み込み、アウトグロースがゲートコンタクト(218)を収容するゲート凹部(222)をその間に画定することを特徴とする請求項10に記載のFET。

【請求項12】

真性領域(206)がp型であり、それ自体かチャネル領域(208)のいずれかが、ソースおよびドレイン領域(212、214)と抽出コンタクト手段を形成することを特徴とする請求項10または11に記載のFET。

【請求項13】

真性領域(206)が、それ自体がベース領域(102)との界面を有する障壁領域(204)との界面を有し、真性、障壁およびベース領域(206、204、202)が同じ導電型であり、障壁領域(204)が真性およびベース領域(206、202)よりも比較的広いバンドギャップをもち、かつ真性領域(206)に対する排除コンタクトを提供することを特徴とする請求項10、11または12に記載のFET。

【請求項14】

a)ベース領域(102)が、p+InSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

b)障壁領域(104)が、0.05から0.25の範囲のxをもつp+In1−xAlxSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

c)真性領域(106)が、5×1017cm−3より小さなアクセプタ濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタ濃度を含むπInSbであり、

d)ソースおよびドレイン領域(110、112)が、少なくとも5×1017cm−3のドナー濃度をもつn+InSbであることを特徴とする請求項13に記載のFET。

【請求項15】

真性領域(206)が、チャネル領域(208)を支持し、ベース、障壁、真性およびチャネル領域(202、204、206、208)が層構造中に連続して配置され、ソースおよびドレイン領域(212、214)がチャネル領域(208)上で成長され、チャネル領域(208)が、ゲート絶縁層(210)およびゲートコンタクト(218)を支持するほぼ平坦な表面部分を有することを特徴とする請求項13または14に記載のFET。

【請求項16】

ソースおよびドレイン領域(212、214)が、その間にゲート凹部(222)を画定し、チャネル領域(208)が、ゲート絶縁層(208)およびゲートコンタクト(210)を支持する凹部(222)の端部に表面部分を有することを特徴とする請求項15に記載のFET。

【請求項17】

チャネル領域が、真性領域の部分の間にあり、真性領域が、ソースおよびドレイン領域(212、214)との組合せで抽出コンタクト手段を形成することを特徴とする請求項10、11または12に記載のFET。

【請求項18】

ベース、障壁および真性領域(202、204、206)が層構造中に連続して配置され、真性領域(206)がチャネル領域(208)を含み、ソースおよびドレイン領域(212、214)が真性領域(206)で支持され、その間にゲート凹部(222)を画定し、真性領域(206)が、ゲート絶縁層(208)およびゲートコンタクト(210)を支持する凹部(222)の端部に表面部分を有することを特徴とする請求項17に記載のFET。

【請求項19】

真性領域(106、206)中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段が、基板バイアス電圧変化によるゲート閾値電圧の変化が最小となる無限大の差動インピーダンスの点で、FET(100、200)をバイアスするように構成されることを特徴とする請求項1から18のいずれか一項に記載のFET。

【請求項20】

真性領域(106)中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段を含む種類のFETを作成する方法であって、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmより大きくないように、ソース領域(110)とドレイン領域(112)の間に延びるチャネルを画定することを含むことを特徴とする方法。

【請求項21】

チャネルの直線性からのずれが、限度において5nmより大きくないことを特徴とする請求項20に記載のFETを作成する方法。

【請求項1】

電界効果トランジスタ(FET)の動作温度でバイアスされていない時に真性導電率を有する領域(106)と、真性領域(106)中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段とを含む種類の電界効果トランジスタ(FET)であって、FET(100)が、また、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmよりも大きくない、ソース領域(110)とドレイン領域(112)の間に延びるチャネルを画定するための手段を含むことを特徴とする電界効果トランジスタ。

【請求項2】

チャネルの直線性からのずれが、限度において5nmより大きくないことを特徴とする請求項1に記載のFET。

【請求項3】

エンハンスメントモードMISFET(100)であることを特徴とする請求項1または2に記載のFET。

【請求項4】

高濃度n型であるソースおよびドレイン領域(110、112)を組み込んでいることを特徴とする請求項1、2または3に記載のFET。

【請求項5】

真性領域(106)がp型であり、ソースおよびドレイン領域(110、112)との組合せで抽出コンタクト手段を形成することを特徴とする請求項1から4のいずれか一項に記載のFET。

【請求項6】

真性領域(106)が、それ自体がベース領域(102)との界面を有する障壁領域(104)との界面を有し、真性、障壁およびベースの領域(106、104、102)が同じ導電型であり、障壁領域(104)が真性およびベースの領域(106、102)よりも比較的広いバンドギャップをもち、かつ真性領域(106)に対する排除コンタクトを提供することを特徴とする請求項1から5のいずれか一項に記載のFET。

【請求項7】

動作時にエンハンスメントチャネルをソースとドレイン領域(110、112)の間に画定するように、ソースとドレイン領域(110、112)の間の真性領域(106)の部分から絶縁され、かつ少なくともその部分にわたって延びる、ゲートコンタクト(116)を含むことを特徴とする請求項6に記載のFET。

【請求項8】

a)ベース領域(102)が、p+InSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

b)障壁領域(104)が、0.05から0.25の範囲のxをもつp+In1−xAlxSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

c)真性領域(106)が、5×1017cm−3より少ないアクセプタ濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタ濃度をもつπInSbであり、

d)ソースおよびドレイン領域(110、112)が、少なくとも5×1017cm−3のドーパント濃度をもつn+InSbであることを特徴とする請求項6または7に記載のFET。

【請求項9】

ベース、障壁および真性領域(102、104、106)が、層構造中に連続して配置され、真性領域(106)が、ゲート絶縁層(108)およびゲートコンタクト(116)を支持するほぼ平坦な表面部分を有することを特徴とする請求項5、6、7または8に記載のFET。

【請求項10】

結合されたチャネル領域(208)を有するデプレッションモードMISFET(200)であることを特徴とする請求項1または2に記載のFET。

【請求項11】

真性領域(206)かチャネル領域(208)のいずれかの上に形成された高濃度にドープされたアウトグロースであるソースおよびドレイン領域(212、214)を組み込み、アウトグロースがゲートコンタクト(218)を収容するゲート凹部(222)をその間に画定することを特徴とする請求項10に記載のFET。

【請求項12】

真性領域(206)がp型であり、それ自体かチャネル領域(208)のいずれかが、ソースおよびドレイン領域(212、214)と抽出コンタクト手段を形成することを特徴とする請求項10または11に記載のFET。

【請求項13】

真性領域(206)が、それ自体がベース領域(102)との界面を有する障壁領域(204)との界面を有し、真性、障壁およびベース領域(206、204、202)が同じ導電型であり、障壁領域(204)が真性およびベース領域(206、202)よりも比較的広いバンドギャップをもち、かつ真性領域(206)に対する排除コンタクトを提供することを特徴とする請求項10、11または12に記載のFET。

【請求項14】

a)ベース領域(102)が、p+InSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

b)障壁領域(104)が、0.05から0.25の範囲のxをもつp+In1−xAlxSbであり、かつ少なくとも5×1017cm−3のアクセプタ濃度を有し、

c)真性領域(106)が、5×1017cm−3より小さなアクセプタ濃度、好ましくは1×1015cm−3から5×1016cm−3の範囲のアクセプタ濃度を含むπInSbであり、

d)ソースおよびドレイン領域(110、112)が、少なくとも5×1017cm−3のドナー濃度をもつn+InSbであることを特徴とする請求項13に記載のFET。

【請求項15】

真性領域(206)が、チャネル領域(208)を支持し、ベース、障壁、真性およびチャネル領域(202、204、206、208)が層構造中に連続して配置され、ソースおよびドレイン領域(212、214)がチャネル領域(208)上で成長され、チャネル領域(208)が、ゲート絶縁層(210)およびゲートコンタクト(218)を支持するほぼ平坦な表面部分を有することを特徴とする請求項13または14に記載のFET。

【請求項16】

ソースおよびドレイン領域(212、214)が、その間にゲート凹部(222)を画定し、チャネル領域(208)が、ゲート絶縁層(208)およびゲートコンタクト(210)を支持する凹部(222)の端部に表面部分を有することを特徴とする請求項15に記載のFET。

【請求項17】

チャネル領域が、真性領域の部分の間にあり、真性領域が、ソースおよびドレイン領域(212、214)との組合せで抽出コンタクト手段を形成することを特徴とする請求項10、11または12に記載のFET。

【請求項18】

ベース、障壁および真性領域(202、204、206)が層構造中に連続して配置され、真性領域(206)がチャネル領域(208)を含み、ソースおよびドレイン領域(212、214)が真性領域(206)で支持され、その間にゲート凹部(222)を画定し、真性領域(206)が、ゲート絶縁層(208)およびゲートコンタクト(210)を支持する凹部(222)の端部に表面部分を有することを特徴とする請求項17に記載のFET。

【請求項19】

真性領域(106、206)中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段が、基板バイアス電圧変化によるゲート閾値電圧の変化が最小となる無限大の差動インピーダンスの点で、FET(100、200)をバイアスするように構成されることを特徴とする請求項1から18のいずれか一項に記載のFET。

【請求項20】

真性領域(106)中の電荷キャリア濃度への真性の寄与を弱めるためのバイアス手段を含む種類のFETを作成する方法であって、高い値の電流利得遮断周波数を得ることができるのに適当なように、チャネルの直線性からの介在するずれが限度において50nmより大きくないように、ソース領域(110)とドレイン領域(112)の間に延びるチャネルを画定することを含むことを特徴とする方法。

【請求項21】

チャネルの直線性からのずれが、限度において5nmより大きくないことを特徴とする請求項20に記載のFETを作成する方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−49599(P2011−49599A)

【公開日】平成23年3月10日(2011.3.10)

【国際特許分類】

【外国語出願】

【出願番号】特願2010−269978(P2010−269978)

【出願日】平成22年12月3日(2010.12.3)

【分割の表示】特願2009−97671(P2009−97671)の分割

【原出願日】平成10年6月10日(1998.6.10)

【出願人】(501352882)キネテイツク・リミテツド (93)

【Fターム(参考)】

【公開日】平成23年3月10日(2011.3.10)

【国際特許分類】

【出願番号】特願2010−269978(P2010−269978)

【出願日】平成22年12月3日(2010.12.3)

【分割の表示】特願2009−97671(P2009−97671)の分割

【原出願日】平成10年6月10日(1998.6.10)

【出願人】(501352882)キネテイツク・リミテツド (93)

【Fターム(参考)】

[ Back to top ]