静電容量圧力変換器における定電力損失

静電容量圧力変換器のセンサインタフェースボードにわたって電力損失を実質的に一定に維持するためのシステム及び方法が記載される。短絡ダイヤフラムレベル検出器が、1つ又は複数の基準電極へのダイヤフラムの短絡を検出する。静電容量圧力変換器内の静電容量検出回路を駆動する発振器の近くに、電力散逸抵抗器が配置される。この抵抗器は、短絡が検出されると、電源に接続するように切り替えられ、それによって、ダイヤフラムが短絡すると、電流が抵抗器を通じて流れるようにし、発振器による電力損失を実質的に一定に維持するだけの十分な量だけ電力を加えることができるようにする。

【発明の詳細な説明】

【背景技術】

【0001】

静電容量圧力変換器は、ダイヤフラムと隣接する電極との間の静電容量の変化を測定することによって、気体及び蒸気の圧力を測定することができる。

熱の発生及び流動時に変化が生じないようにするために、一旦変換器が安定して作動したら、センサインタフェースボード上で一定の電力損失を維持することが望ましい。電力損失を一定に維持することは、低レンジ、高利得の圧力変換器の場合に特に望ましい。

【0002】

圧力が0であるときの温度の影響を排除するか、又は最小限に抑えて、圧力が0であるときに変換器が熱の流れの変化に影響を受けないようにし、それによって電力損失を一定に維持するために、様々な試みがなされてきた。しかしながら、圧力が0のときに温度の影響が排除される場合であっても、他の圧力点が試験されないままであり、依然として一時的なシフトを受けやすいことがある。

【0003】

電力損失を一定に維持するために、センサインタフェースボードとセンサとの間に特別な熱分離を追加する試みがなされてきた場合もある。しかしながら、これは、電子機器を温度制御することによって得られるかもしれない、安定性に関する他の改善を危険に曝す傾向がある。

【発明の概要】

【発明が解決しようとする課題】

【0004】

したがって、静電容量圧力変換器内の電力損失を制御するための改善された方法及びシステムが必要とされている。

【課題を解決するための手段】

【0005】

ダイヤフラムと基準電極との間の静電容量の変化を検出するように構成される静電容量検出回路を有する静電容量圧力変換器において電力損失を制御するためのシステムが説明される。システムは、基準電極へのダイヤフラムの短絡を検出するように構成される短絡ダイヤフラムレベル検出器を備える。システムは、ダイヤフラムの短絡が検出されたときに、電流が抵抗器を通じて流れるようにし、それによって、ダイヤフラムが短絡するときに、変換器内の電力損失を実質的に一定に維持するように構成される、スイッチをさらに備える。

【0006】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定する静電容量圧力変換器において電力損失を制御するためのシステムが説明される。システムは、基準電極へのダイヤフラムの短絡を検出するように構成される短絡検出回路を備える。システムは、ダイヤフラムが基準電極に短絡したことが検出されたときに静電容量検出回路を駆動する発振器に接続される抵抗器を通じて電流を流すことによって、静電容量圧力変換器に電力を加えるように構成される電力損失回路をさらに備える。

【0007】

静電容量圧力変換器が、ダイヤフラムと、1つ又は複数の基準電極と、ダイヤフラム及び基準電極間の静電容量の変化を検出するように構成される静電容量検出回路であって、当該静電容量の変化はダイヤフラムにかけられる圧力に比例する、静電容量検出回路とを備える。変換器は、静電容量検出回路を駆動するように構成される発振器と、基準電極へのダイヤフラムの短絡を検出するように構成される、短絡ダイヤフラムレベル検出器とをさらに備える。変換器は、発振器に結合される抵抗器と、ダイヤフラムが短絡するときに、変換器による電力損失を実質的に一定に維持するように、ダイヤフラムの短絡を検出するのに応答して、電流が抵抗器を通じて流れることができるように構成される、スイッチとをさらに備える。

【0008】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定するように構成される静電容量圧力変換器において電力損失を制御する方法が説明される。該方法は、基準電極へのダイヤフラムの短絡を検出する動作を含む。該方法は、ダイヤフラムの短絡によって引き起こされる変換器内の電力損失の減少を補償するだけの十分な量だけ変換器において電力損失を加える動作であって、それによって変換器内の電力損失を実質的に一定に維持する、動作をさらに含む。

【図面の簡単な説明】

【0009】

【図1A】静電容量圧力変換器の一例の機能ブロック図である。

【図1B】図1Bに示される静電容量圧力変換器のための電子回路を示すブロック図である。

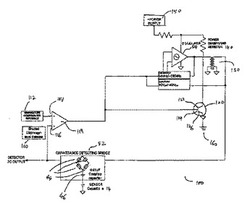

【図2】図1A及び図1Bに示される静電容量圧力変換器内の電力損失を制御するためのシステムの回路図である。

【発明を実施するための形態】

【0010】

静電容量圧力変換器内のセンサインタフェースボードにわたって電力損失を実質的に一定に維持するための方法及びシステムが説明される。

図1Aは、静電容量圧力変換器10の一例の機能ブロック図である。静電容量圧力変換器10は、ダイヤフラム12と、電極14のアセンブリとを備える。ダイヤフラム12として金属ダイヤフラム12を用いることができ、容量性電極14は、金属ダイヤフラム12の背面又は基準面16に正確に取り付けることができる。望ましくない粒子又はエネルギーが侵入するのを阻止するために、バッフル17を設けることができる。

【0011】

静電容量圧力変換器10は、測定される圧力に比例する出力信号を供給するように構成される。ダイヤフラム12に圧力がかけられると、その撓みが、電極とダイヤフラムとの間の距離の変化を生み出し、それによって、結果として生成される静電容量が変化する。図1Bとの関連でさらに詳細に示されるように、かけられる圧力によって引き起こされる静電容量の変化は、キャパシタンスブリッジ回路及び前置増幅器によってAC電圧に変換することができ、それらの回路は発振器によって励起される。その後、このAC信号を増幅及び同期復調することができ、結果として、非常に安定したDC出力(約0ボルト〜10ボルト)が生成され、このDC出力は圧力に正比例する。この出力信号は、正確に圧力制御するために、データ収集システム、読出し機器若しくは電源機器、又はコントローラが直接読み取ることができる。

【0012】

静電容量圧力変換器10は、約±15ボルト電源を必要とする独立型の変換器とすることができる。静電容量圧力変換器10は、力/単位面積と定義される圧力を測定することができる。静電容量圧力変換器10による圧力測定は、測定される気体のタイプには影響を受けないようにすることができる。電極アセンブリ14は、メタル・オン・セラミック電極構造を有することができる。変換器10の基準面(又は背面)16は、内部化学ゲッタポンプ18によって、マノメータの寿命にわたって非常に高い真空に維持することができる。ダイヤフラム12として、極めて低いヒステリシス、高い再現性、高い分解能及び速い応答を与えるように設計される、径方向に引っ張られたダイヤフラムを用いることができる。

【0013】

図1Bは、図1Aに示される静電容量圧力変換器10のための電子回路50を示すブロック図である。電子回路50は、たとえば、センサインタフェースボード上に、センサに隣接して配置することができる。電子回路50は、静電容量検出回路52と、発振器54と、基準部56と、バッファ、スケーリング及び増幅回路58とを備えることができる。静電容量検出回路52は、図1Aに示されるダイヤフラム12と電極14との間の静電容量の変化を検出する。静電容量検出回路52として、ブリッジ構成に配列される複数のダイオード素子と、1つ又は複数の結合コンデンサとを備える、従来のダイオードブリッジ回路を用いることができる。

【0014】

発振器54はブリッジ回路を駆動するように構成され、高精度の固定周波数発振器とすることができる。基準部56は基準レベルを与えるように構成され、そのレベルから変換器電極静電容量の不均衡を測定することができる。センサ電極静電容量の不均衡は差出力を生成し、その出力を、バッファ、スケーリング及び増幅回路58によって増幅することができる。結果として生成される出力信号のオフセット、利得及び線形性をそれぞれ、ゼロポテンショメータ66、スパンポテンショメータ62、及び線形性ポテンショメータ64によって調整することができる。これらの調整によって、圧力入力と電圧出力との間の適切な対応を確保することができる。

【0015】

図1Bに示されるセンサ電子回路を含むセンサインタフェースボードにおいて定電力損失を維持することが望ましい。この場合には、一旦変換器10が安定して作動すると、熱の発生及び流動時に何も変化が生じない。これまで、定電力損失の維持に失敗したのは、低レンジ且つ高利得の圧力変換器において最も顕著であったといえる。電力損失を一定に維持するための要件は、非加熱式の変換器にとって特に重要であり得るが、加熱式のユニットにとっても重要であることがわかってきた。

【0016】

図2は、静電容量圧力変換器において電力損失を制御するためのシステム100の一実施形態のブロック図である。全体として、システム100は、短絡ダイヤフラムレベル検出器110と;発振器駆動増幅器54の近くに配置され、電源150とグランド160との間に接続することができる電力散逸抵抗器140と;昇圧変圧器130と;トランジスタスイッチ120とを備える。

【0017】

システム100は、ダイヤフラム12が電極14に短絡したために、センサインタフェースボード上に電力を加える必要があるときに、電力散逸抵抗器140(発振器駆動増幅器54の近くに配置される)を電源150に接続するように切り替えるよう構成される。ダイヤフラム12が電極14に短絡する結果として、変換器10の容量性負荷がはるかに高くなる。詳細には、システム100は、1)電極14へのダイヤフラム12の短絡を検出すると共に、2)短絡条件が検出されたときに、V+電源150とグランド160との間に抵抗器140を接続して、発振器54において低下した電力損失を補償するように構成される。

【0018】

励起発振器が静電容量圧力変換器10の典型的な静電容量範囲において動作するとき、ダイヤフラムが短絡し、回路が、より低いピーク・ツー・ピーク電圧及び発振器周波数に切り替わるときに比べて、発振器駆動増幅器において散逸される電力は著しく少ない。たとえば、40Vp−p(ピーク・ツー・ピーク)、250kHz励起発振器が、100mT変換器の典型的な120pF静電容量範囲において動作するとき、ダイヤフラムが短絡し、昇圧変圧器140を有する回路が、16kHzで10Vp−pに切り替わり得るときに比べて、発振器駆動増幅器において約2倍だけ高い電力が散逸されることになる。この電圧及び周波数変化の結果として、システムにおいて散逸される全電力は、通常(ダイヤフラムが短絡しないとき)の電力の約1/2になる。システム100は、ロジックを通じて、ダイヤフラムが電極に短絡したことを検出すると共に、トランジスタ120にベース駆動を印加して、抵抗器140をV+電源150からグランド160に接続するように構成される。抵抗器140は、電力損失を実質的に一定に維持するために必要とされる付加電力を作り出すように選択される。

【0019】

システム100は、発振器励起を最適化するための昇圧変圧器130を備える。発振器振幅を最大にすることによって、静電容量に基づく圧力変換器の信号対雑音比が直接改善されることが知られており、変換器の出力は、発振器励起振幅に正比例する。この最大化は、ダイオードブリッジ回路52において生じる全ての条件の場合に、最大効率及び最小電力損失で果たされることが望ましい。

【0020】

最大限利用可能な発振器振幅を達成するために、いくつかの従来のシステムは電源電圧を最大にすることがある。しかしながら、電源電圧を最大にすることによって、より低い電圧において動作し、それゆえ信頼性がより高い、より現代的な部品を使用するのが妨げられることがある。これらの従来のシステムは、通常の動作中に、又はセンサ短絡条件の場合に、電力損失への配慮がなされないことがある。

【0021】

例示される実施形態では、昇圧変圧器130として単純な5:1単巻変圧器を用いることができ、この変圧器は、250kHzの高い励起周波数用に設計されることがある。変圧器130のサイズ及びインダクタンスは小さく抑えることができる。変圧器は、一度の機械作業において低コストで製造することができ、コストに関して大きな利益を与える単純な環状コイルとすることができる。

【0022】

昇圧比を5:1とし、単巻変圧器の形態にするとき、低電圧演算増幅器を用いて、最高限度に高い励起電圧を生成することができる。発振器駆動増幅器54は、ビデオ増幅器においてよく見られることがあるように、高い出力電流能力を必要とする。例示される実施形態では、発振器54として、低レンジ(<1Torr)静電容量マノメータを励起するために用いられる、250kHzにおいて40Vp−pで発振する発振器を用いることができる。言い換えると、発振器54は、通常の動作中に、約40ボルトのピーク・ツー・ピーク電圧及び約250kHzの駆動周波数でブリッジ回路を駆動するように構成される。他の全ての変換器レンジの場合に、他の発振器振幅、10Vp−pが用いられてもよく、その振幅は、レンジに応じてデジタル形式で設定することもできる。

【0023】

変圧器130の二次インダクタンスは、動作している静電容量変換器の容量性負荷に共振するように最適化される。ダイヤフラムが短絡し、より大きな結合コンデンサが負荷を形成するときに、二次共振点が測定される。

【0024】

例示される回路構成では、40Vp−p、250kHz発振器信号は、変圧器130の二次側からもたらされる。それゆえ、発振器増幅器54は、変圧器130の一次側を8Vp−p(すなわち、40ボルトを5で除算した値)で駆動しなければならず、その電流はブリッジインピーダンス及び変換器10を通じて流れることになる電流よりも5倍大きい。変換器10が、センサコンデンサ14当たり約60pF〜65pFを有する場合には、発振器54から見ると、約130pFになる。250kHzでは、これは、約5000オームのインピーダンスを表す。したがって、40Vp−p発振器54は、約5000オームの中に20ボルトピークを、すなわち約4ミリアンペアを供給しなければならない。その際、発振器回路は、±4Vにおいて、一次側に5×4=20mAを与えなければならない。これは、市販されている低電圧、高効率オペアンプによって容易に実行することができ、ブリッジ回路52は、所望によって、高い電圧駆動信号を与えられることができる。

【0025】

上記の高出力電流能力を用いて、ダイヤフラム短絡の発生を能動的に解決して、電力損失をさらに制限しなければならない。例示される実施形態では、発振器周波数を約16kHzの「短絡した」共振点まで低減されるようにネットワークにおいて切り替えるために、飽和したブリッジ出力によって短絡条件が検出されなければならない。さらに、発振器が40Vp−pにあった場合には、その振幅は、別個のロジックにおいて、又はCPU(図示せず)の制御下で、10Vp−pまで低減される。低レンジ(<1Torr)変換器の場合に、この条件下で電力損失は半分に削減され、他の全てのレンジの場合に実質的に同じままである。

【0026】

短絡ダイヤフラムレベル検出器110は、ダイヤフラム12が電極14に短絡したことを検出するように構成される短絡検出器回路とすることができる。例示される実施形態では、短絡ダイヤフラムレベル検出器110は、第1の入力114が温度補償された基準部に結合されており、第2の入力116が静電容量検出回路52の出力に結合されている、電圧比較器である。

【0027】

ダイヤフラムが基準電極に短絡することによって、キャパシタンスブリッジ回路52が飽和するときに、電圧比較器119はハイに切り替わるように構成される。静電容量検出回路52は、ブリッジ構成に配列される複数のダイオード構成要素44と、少なくとも1つの結合コンデンサ46とを備える。静電容量変換器10の一方又は両方の電極14が短絡するとき、結合コンデンサ46は、ブリッジ回路52において観察される静電容量を劇的に、典型的には100倍よりも大きく変化させる。この結果として、ブリッジダイオード構成要素44が飽和する。このタイプの飽和は、短絡条件中にのみ生じる。短絡検出器回路110内の温度補償された基準部112は、比較器119上に、飽和を示す電圧を設定する。このようにして、短絡条件が満たされるとき、比較器119はハイに切り替わる。温度補償された基準部112は、ブリッジ飽和が大きく温度に依存するという事実に対する調整を行う。

【0028】

短絡が検出されると、×100より大きな静電容量で発振器振幅をさらに低減することによって、ブリッジ52が飽和した状態に保持されるであろう。しかし、発振器54の振幅を10Vp−pまで低減すること、及び周波数を16kHzの新たな共振点に切り替えることによって、発振器回路によって変圧器130の一次側に供給される電力は、通常の動作値の約1/2まで低減される。

【0029】

スイッチ120は、電源抵抗器140をグランドに接続し、抵抗器が通常の電力の残りの半分を散逸するようにする。このようにして、発振器ドライバ54及び電源抵抗器140を含む全回路ブロックは、結局、通常の条件下と同じ電力を散逸し、回路基板上の温度は変化しないようになる。

【0030】

1Torrセンサのために10Vp−p励起発振器が用いられる場合に、上記で説明されたように、ダイヤフラムが短絡するときに通常の動作時の250kHzから16kHzまで上記のように切り替えることによって、発振器は適切な発振器振幅を維持することができるため、発振器ドライバ増幅器54内の電力損失が同じに保持される。1つの利点は、センサが短絡したにもかかわらず、全ての回路が、その通常のレベル下で動作していることである。

【0031】

例示される実施形態では、スイッチ120はトランジスタであるが、他の実施形態は他のタイプのスイッチを用いることができる。トランジスタ120は、電圧比較器119に結合されるベース端子124と、抵抗器130に結合されるコレクタ端子122と、グランド160に結合されるエミッタ端子126とを有する。ベース124に小さな電流又は電圧を印加することによって、他の2つのリードの中に、すなわちコレクタ122からエミッタ126まで、それよりも大きな電流又は電圧を流すことができることが知られている。ダイヤフラムが短絡したことが短絡検出回路によって検出されると、ベース端子124に駆動信号が印加されるときに、トランジスタ120は、電流が抵抗器130を通じて、エミッタ端子126からコレクタ端子122まで流れることができるように構成される。

【0032】

要するに、ダイヤフラムが電極上に短絡するときに、ダイヤフラムの短絡を検出すること、及び電源抵抗器が電源に接続するように切り替えて、センサインタフェースボードに電力を加えることによって、静電容量圧力変換器のセンサインタフェースボードにわたって電力損失を実質的に一定に維持するためのシステム及び方法が説明されてきた。

【0033】

上記のシステム及び方法によれば、センサインタフェースボード上の温度勾配を補償し、それによって、熱に関する過渡的な挙動を実質的に排除することができるようになる。センサインタフェースボード上の全電力が最小限に抑えられ、それによって、変換器構成要素の温度上昇を最小限に抑えると共に信頼性を向上させることができる。また、熱パッケージに対する変更がないことによって、変換器温度環境をより良好に制御することができるようになる。さらに、昇圧変圧器を使用することによって、低レンジ(又は高利得)変換器のための励起利得が高くなる直接の結果として、信号対雑音比が大きく改善される。また、昇圧変圧器を用いることによって、発振器回路内の電力損失も制限され、それによって、変換器の熱的挙動が改善される。

【0034】

電力損失を一定に維持するためのシステム及び方法に関する或る特定の実施形態が説明されてきたが、これらの実施形態に内在する概念は他の実施形態においても同じように用いることができることは理解されたい。本願の保護は、以下の特許請求の範囲によってのみ限定される。

【0035】

当該特許請求の範囲において、具体的に言及されない限り、単数形の構成要素を参照することは、「唯一」ではなく、「1つ又は複数」を意味することを意図するものである。当業者に知られているか、又は後に知られるようになる、本開示全体を通じて説明される種々の実施形態の構成要素に対する全ての構造的及び機能的な均等物は、参照によって本明細書に明示的に援用され、特許請求の範囲によって包含されることが意図されている。さらに、特許請求の範囲において明らかに列挙されているか否かにかかわらず、本明細書において開示される内容を公共のものとして提供することは意図していない。その要素が、「〜のための手段」という言い回しを用いて明らかに列挙されない限り、又は方法クレームに関する請求項の場合には、その要素が、「〜のためのステップ」という言い回しを用いて列挙されない限り、請求項の要素は、米国特許法第112条第6項の規定するところに従って解釈されるべきではない。

【背景技術】

【0001】

静電容量圧力変換器は、ダイヤフラムと隣接する電極との間の静電容量の変化を測定することによって、気体及び蒸気の圧力を測定することができる。

熱の発生及び流動時に変化が生じないようにするために、一旦変換器が安定して作動したら、センサインタフェースボード上で一定の電力損失を維持することが望ましい。電力損失を一定に維持することは、低レンジ、高利得の圧力変換器の場合に特に望ましい。

【0002】

圧力が0であるときの温度の影響を排除するか、又は最小限に抑えて、圧力が0であるときに変換器が熱の流れの変化に影響を受けないようにし、それによって電力損失を一定に維持するために、様々な試みがなされてきた。しかしながら、圧力が0のときに温度の影響が排除される場合であっても、他の圧力点が試験されないままであり、依然として一時的なシフトを受けやすいことがある。

【0003】

電力損失を一定に維持するために、センサインタフェースボードとセンサとの間に特別な熱分離を追加する試みがなされてきた場合もある。しかしながら、これは、電子機器を温度制御することによって得られるかもしれない、安定性に関する他の改善を危険に曝す傾向がある。

【発明の概要】

【発明が解決しようとする課題】

【0004】

したがって、静電容量圧力変換器内の電力損失を制御するための改善された方法及びシステムが必要とされている。

【課題を解決するための手段】

【0005】

ダイヤフラムと基準電極との間の静電容量の変化を検出するように構成される静電容量検出回路を有する静電容量圧力変換器において電力損失を制御するためのシステムが説明される。システムは、基準電極へのダイヤフラムの短絡を検出するように構成される短絡ダイヤフラムレベル検出器を備える。システムは、ダイヤフラムの短絡が検出されたときに、電流が抵抗器を通じて流れるようにし、それによって、ダイヤフラムが短絡するときに、変換器内の電力損失を実質的に一定に維持するように構成される、スイッチをさらに備える。

【0006】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定する静電容量圧力変換器において電力損失を制御するためのシステムが説明される。システムは、基準電極へのダイヤフラムの短絡を検出するように構成される短絡検出回路を備える。システムは、ダイヤフラムが基準電極に短絡したことが検出されたときに静電容量検出回路を駆動する発振器に接続される抵抗器を通じて電流を流すことによって、静電容量圧力変換器に電力を加えるように構成される電力損失回路をさらに備える。

【0007】

静電容量圧力変換器が、ダイヤフラムと、1つ又は複数の基準電極と、ダイヤフラム及び基準電極間の静電容量の変化を検出するように構成される静電容量検出回路であって、当該静電容量の変化はダイヤフラムにかけられる圧力に比例する、静電容量検出回路とを備える。変換器は、静電容量検出回路を駆動するように構成される発振器と、基準電極へのダイヤフラムの短絡を検出するように構成される、短絡ダイヤフラムレベル検出器とをさらに備える。変換器は、発振器に結合される抵抗器と、ダイヤフラムが短絡するときに、変換器による電力損失を実質的に一定に維持するように、ダイヤフラムの短絡を検出するのに応答して、電流が抵抗器を通じて流れることができるように構成される、スイッチとをさらに備える。

【0008】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定するように構成される静電容量圧力変換器において電力損失を制御する方法が説明される。該方法は、基準電極へのダイヤフラムの短絡を検出する動作を含む。該方法は、ダイヤフラムの短絡によって引き起こされる変換器内の電力損失の減少を補償するだけの十分な量だけ変換器において電力損失を加える動作であって、それによって変換器内の電力損失を実質的に一定に維持する、動作をさらに含む。

【図面の簡単な説明】

【0009】

【図1A】静電容量圧力変換器の一例の機能ブロック図である。

【図1B】図1Bに示される静電容量圧力変換器のための電子回路を示すブロック図である。

【図2】図1A及び図1Bに示される静電容量圧力変換器内の電力損失を制御するためのシステムの回路図である。

【発明を実施するための形態】

【0010】

静電容量圧力変換器内のセンサインタフェースボードにわたって電力損失を実質的に一定に維持するための方法及びシステムが説明される。

図1Aは、静電容量圧力変換器10の一例の機能ブロック図である。静電容量圧力変換器10は、ダイヤフラム12と、電極14のアセンブリとを備える。ダイヤフラム12として金属ダイヤフラム12を用いることができ、容量性電極14は、金属ダイヤフラム12の背面又は基準面16に正確に取り付けることができる。望ましくない粒子又はエネルギーが侵入するのを阻止するために、バッフル17を設けることができる。

【0011】

静電容量圧力変換器10は、測定される圧力に比例する出力信号を供給するように構成される。ダイヤフラム12に圧力がかけられると、その撓みが、電極とダイヤフラムとの間の距離の変化を生み出し、それによって、結果として生成される静電容量が変化する。図1Bとの関連でさらに詳細に示されるように、かけられる圧力によって引き起こされる静電容量の変化は、キャパシタンスブリッジ回路及び前置増幅器によってAC電圧に変換することができ、それらの回路は発振器によって励起される。その後、このAC信号を増幅及び同期復調することができ、結果として、非常に安定したDC出力(約0ボルト〜10ボルト)が生成され、このDC出力は圧力に正比例する。この出力信号は、正確に圧力制御するために、データ収集システム、読出し機器若しくは電源機器、又はコントローラが直接読み取ることができる。

【0012】

静電容量圧力変換器10は、約±15ボルト電源を必要とする独立型の変換器とすることができる。静電容量圧力変換器10は、力/単位面積と定義される圧力を測定することができる。静電容量圧力変換器10による圧力測定は、測定される気体のタイプには影響を受けないようにすることができる。電極アセンブリ14は、メタル・オン・セラミック電極構造を有することができる。変換器10の基準面(又は背面)16は、内部化学ゲッタポンプ18によって、マノメータの寿命にわたって非常に高い真空に維持することができる。ダイヤフラム12として、極めて低いヒステリシス、高い再現性、高い分解能及び速い応答を与えるように設計される、径方向に引っ張られたダイヤフラムを用いることができる。

【0013】

図1Bは、図1Aに示される静電容量圧力変換器10のための電子回路50を示すブロック図である。電子回路50は、たとえば、センサインタフェースボード上に、センサに隣接して配置することができる。電子回路50は、静電容量検出回路52と、発振器54と、基準部56と、バッファ、スケーリング及び増幅回路58とを備えることができる。静電容量検出回路52は、図1Aに示されるダイヤフラム12と電極14との間の静電容量の変化を検出する。静電容量検出回路52として、ブリッジ構成に配列される複数のダイオード素子と、1つ又は複数の結合コンデンサとを備える、従来のダイオードブリッジ回路を用いることができる。

【0014】

発振器54はブリッジ回路を駆動するように構成され、高精度の固定周波数発振器とすることができる。基準部56は基準レベルを与えるように構成され、そのレベルから変換器電極静電容量の不均衡を測定することができる。センサ電極静電容量の不均衡は差出力を生成し、その出力を、バッファ、スケーリング及び増幅回路58によって増幅することができる。結果として生成される出力信号のオフセット、利得及び線形性をそれぞれ、ゼロポテンショメータ66、スパンポテンショメータ62、及び線形性ポテンショメータ64によって調整することができる。これらの調整によって、圧力入力と電圧出力との間の適切な対応を確保することができる。

【0015】

図1Bに示されるセンサ電子回路を含むセンサインタフェースボードにおいて定電力損失を維持することが望ましい。この場合には、一旦変換器10が安定して作動すると、熱の発生及び流動時に何も変化が生じない。これまで、定電力損失の維持に失敗したのは、低レンジ且つ高利得の圧力変換器において最も顕著であったといえる。電力損失を一定に維持するための要件は、非加熱式の変換器にとって特に重要であり得るが、加熱式のユニットにとっても重要であることがわかってきた。

【0016】

図2は、静電容量圧力変換器において電力損失を制御するためのシステム100の一実施形態のブロック図である。全体として、システム100は、短絡ダイヤフラムレベル検出器110と;発振器駆動増幅器54の近くに配置され、電源150とグランド160との間に接続することができる電力散逸抵抗器140と;昇圧変圧器130と;トランジスタスイッチ120とを備える。

【0017】

システム100は、ダイヤフラム12が電極14に短絡したために、センサインタフェースボード上に電力を加える必要があるときに、電力散逸抵抗器140(発振器駆動増幅器54の近くに配置される)を電源150に接続するように切り替えるよう構成される。ダイヤフラム12が電極14に短絡する結果として、変換器10の容量性負荷がはるかに高くなる。詳細には、システム100は、1)電極14へのダイヤフラム12の短絡を検出すると共に、2)短絡条件が検出されたときに、V+電源150とグランド160との間に抵抗器140を接続して、発振器54において低下した電力損失を補償するように構成される。

【0018】

励起発振器が静電容量圧力変換器10の典型的な静電容量範囲において動作するとき、ダイヤフラムが短絡し、回路が、より低いピーク・ツー・ピーク電圧及び発振器周波数に切り替わるときに比べて、発振器駆動増幅器において散逸される電力は著しく少ない。たとえば、40Vp−p(ピーク・ツー・ピーク)、250kHz励起発振器が、100mT変換器の典型的な120pF静電容量範囲において動作するとき、ダイヤフラムが短絡し、昇圧変圧器140を有する回路が、16kHzで10Vp−pに切り替わり得るときに比べて、発振器駆動増幅器において約2倍だけ高い電力が散逸されることになる。この電圧及び周波数変化の結果として、システムにおいて散逸される全電力は、通常(ダイヤフラムが短絡しないとき)の電力の約1/2になる。システム100は、ロジックを通じて、ダイヤフラムが電極に短絡したことを検出すると共に、トランジスタ120にベース駆動を印加して、抵抗器140をV+電源150からグランド160に接続するように構成される。抵抗器140は、電力損失を実質的に一定に維持するために必要とされる付加電力を作り出すように選択される。

【0019】

システム100は、発振器励起を最適化するための昇圧変圧器130を備える。発振器振幅を最大にすることによって、静電容量に基づく圧力変換器の信号対雑音比が直接改善されることが知られており、変換器の出力は、発振器励起振幅に正比例する。この最大化は、ダイオードブリッジ回路52において生じる全ての条件の場合に、最大効率及び最小電力損失で果たされることが望ましい。

【0020】

最大限利用可能な発振器振幅を達成するために、いくつかの従来のシステムは電源電圧を最大にすることがある。しかしながら、電源電圧を最大にすることによって、より低い電圧において動作し、それゆえ信頼性がより高い、より現代的な部品を使用するのが妨げられることがある。これらの従来のシステムは、通常の動作中に、又はセンサ短絡条件の場合に、電力損失への配慮がなされないことがある。

【0021】

例示される実施形態では、昇圧変圧器130として単純な5:1単巻変圧器を用いることができ、この変圧器は、250kHzの高い励起周波数用に設計されることがある。変圧器130のサイズ及びインダクタンスは小さく抑えることができる。変圧器は、一度の機械作業において低コストで製造することができ、コストに関して大きな利益を与える単純な環状コイルとすることができる。

【0022】

昇圧比を5:1とし、単巻変圧器の形態にするとき、低電圧演算増幅器を用いて、最高限度に高い励起電圧を生成することができる。発振器駆動増幅器54は、ビデオ増幅器においてよく見られることがあるように、高い出力電流能力を必要とする。例示される実施形態では、発振器54として、低レンジ(<1Torr)静電容量マノメータを励起するために用いられる、250kHzにおいて40Vp−pで発振する発振器を用いることができる。言い換えると、発振器54は、通常の動作中に、約40ボルトのピーク・ツー・ピーク電圧及び約250kHzの駆動周波数でブリッジ回路を駆動するように構成される。他の全ての変換器レンジの場合に、他の発振器振幅、10Vp−pが用いられてもよく、その振幅は、レンジに応じてデジタル形式で設定することもできる。

【0023】

変圧器130の二次インダクタンスは、動作している静電容量変換器の容量性負荷に共振するように最適化される。ダイヤフラムが短絡し、より大きな結合コンデンサが負荷を形成するときに、二次共振点が測定される。

【0024】

例示される回路構成では、40Vp−p、250kHz発振器信号は、変圧器130の二次側からもたらされる。それゆえ、発振器増幅器54は、変圧器130の一次側を8Vp−p(すなわち、40ボルトを5で除算した値)で駆動しなければならず、その電流はブリッジインピーダンス及び変換器10を通じて流れることになる電流よりも5倍大きい。変換器10が、センサコンデンサ14当たり約60pF〜65pFを有する場合には、発振器54から見ると、約130pFになる。250kHzでは、これは、約5000オームのインピーダンスを表す。したがって、40Vp−p発振器54は、約5000オームの中に20ボルトピークを、すなわち約4ミリアンペアを供給しなければならない。その際、発振器回路は、±4Vにおいて、一次側に5×4=20mAを与えなければならない。これは、市販されている低電圧、高効率オペアンプによって容易に実行することができ、ブリッジ回路52は、所望によって、高い電圧駆動信号を与えられることができる。

【0025】

上記の高出力電流能力を用いて、ダイヤフラム短絡の発生を能動的に解決して、電力損失をさらに制限しなければならない。例示される実施形態では、発振器周波数を約16kHzの「短絡した」共振点まで低減されるようにネットワークにおいて切り替えるために、飽和したブリッジ出力によって短絡条件が検出されなければならない。さらに、発振器が40Vp−pにあった場合には、その振幅は、別個のロジックにおいて、又はCPU(図示せず)の制御下で、10Vp−pまで低減される。低レンジ(<1Torr)変換器の場合に、この条件下で電力損失は半分に削減され、他の全てのレンジの場合に実質的に同じままである。

【0026】

短絡ダイヤフラムレベル検出器110は、ダイヤフラム12が電極14に短絡したことを検出するように構成される短絡検出器回路とすることができる。例示される実施形態では、短絡ダイヤフラムレベル検出器110は、第1の入力114が温度補償された基準部に結合されており、第2の入力116が静電容量検出回路52の出力に結合されている、電圧比較器である。

【0027】

ダイヤフラムが基準電極に短絡することによって、キャパシタンスブリッジ回路52が飽和するときに、電圧比較器119はハイに切り替わるように構成される。静電容量検出回路52は、ブリッジ構成に配列される複数のダイオード構成要素44と、少なくとも1つの結合コンデンサ46とを備える。静電容量変換器10の一方又は両方の電極14が短絡するとき、結合コンデンサ46は、ブリッジ回路52において観察される静電容量を劇的に、典型的には100倍よりも大きく変化させる。この結果として、ブリッジダイオード構成要素44が飽和する。このタイプの飽和は、短絡条件中にのみ生じる。短絡検出器回路110内の温度補償された基準部112は、比較器119上に、飽和を示す電圧を設定する。このようにして、短絡条件が満たされるとき、比較器119はハイに切り替わる。温度補償された基準部112は、ブリッジ飽和が大きく温度に依存するという事実に対する調整を行う。

【0028】

短絡が検出されると、×100より大きな静電容量で発振器振幅をさらに低減することによって、ブリッジ52が飽和した状態に保持されるであろう。しかし、発振器54の振幅を10Vp−pまで低減すること、及び周波数を16kHzの新たな共振点に切り替えることによって、発振器回路によって変圧器130の一次側に供給される電力は、通常の動作値の約1/2まで低減される。

【0029】

スイッチ120は、電源抵抗器140をグランドに接続し、抵抗器が通常の電力の残りの半分を散逸するようにする。このようにして、発振器ドライバ54及び電源抵抗器140を含む全回路ブロックは、結局、通常の条件下と同じ電力を散逸し、回路基板上の温度は変化しないようになる。

【0030】

1Torrセンサのために10Vp−p励起発振器が用いられる場合に、上記で説明されたように、ダイヤフラムが短絡するときに通常の動作時の250kHzから16kHzまで上記のように切り替えることによって、発振器は適切な発振器振幅を維持することができるため、発振器ドライバ増幅器54内の電力損失が同じに保持される。1つの利点は、センサが短絡したにもかかわらず、全ての回路が、その通常のレベル下で動作していることである。

【0031】

例示される実施形態では、スイッチ120はトランジスタであるが、他の実施形態は他のタイプのスイッチを用いることができる。トランジスタ120は、電圧比較器119に結合されるベース端子124と、抵抗器130に結合されるコレクタ端子122と、グランド160に結合されるエミッタ端子126とを有する。ベース124に小さな電流又は電圧を印加することによって、他の2つのリードの中に、すなわちコレクタ122からエミッタ126まで、それよりも大きな電流又は電圧を流すことができることが知られている。ダイヤフラムが短絡したことが短絡検出回路によって検出されると、ベース端子124に駆動信号が印加されるときに、トランジスタ120は、電流が抵抗器130を通じて、エミッタ端子126からコレクタ端子122まで流れることができるように構成される。

【0032】

要するに、ダイヤフラムが電極上に短絡するときに、ダイヤフラムの短絡を検出すること、及び電源抵抗器が電源に接続するように切り替えて、センサインタフェースボードに電力を加えることによって、静電容量圧力変換器のセンサインタフェースボードにわたって電力損失を実質的に一定に維持するためのシステム及び方法が説明されてきた。

【0033】

上記のシステム及び方法によれば、センサインタフェースボード上の温度勾配を補償し、それによって、熱に関する過渡的な挙動を実質的に排除することができるようになる。センサインタフェースボード上の全電力が最小限に抑えられ、それによって、変換器構成要素の温度上昇を最小限に抑えると共に信頼性を向上させることができる。また、熱パッケージに対する変更がないことによって、変換器温度環境をより良好に制御することができるようになる。さらに、昇圧変圧器を使用することによって、低レンジ(又は高利得)変換器のための励起利得が高くなる直接の結果として、信号対雑音比が大きく改善される。また、昇圧変圧器を用いることによって、発振器回路内の電力損失も制限され、それによって、変換器の熱的挙動が改善される。

【0034】

電力損失を一定に維持するためのシステム及び方法に関する或る特定の実施形態が説明されてきたが、これらの実施形態に内在する概念は他の実施形態においても同じように用いることができることは理解されたい。本願の保護は、以下の特許請求の範囲によってのみ限定される。

【0035】

当該特許請求の範囲において、具体的に言及されない限り、単数形の構成要素を参照することは、「唯一」ではなく、「1つ又は複数」を意味することを意図するものである。当業者に知られているか、又は後に知られるようになる、本開示全体を通じて説明される種々の実施形態の構成要素に対する全ての構造的及び機能的な均等物は、参照によって本明細書に明示的に援用され、特許請求の範囲によって包含されることが意図されている。さらに、特許請求の範囲において明らかに列挙されているか否かにかかわらず、本明細書において開示される内容を公共のものとして提供することは意図していない。その要素が、「〜のための手段」という言い回しを用いて明らかに列挙されない限り、又は方法クレームに関する請求項の場合には、その要素が、「〜のためのステップ」という言い回しを用いて列挙されない限り、請求項の要素は、米国特許法第112条第6項の規定するところに従って解釈されるべきではない。

【特許請求の範囲】

【請求項1】

ダイヤフラムと基準電極との間の静電容量の変化を検出するように構成される静電容量検出回路を有する静電容量圧力変換器において電力損失を制御するためのシステムであって、

前記基準電極への前記ダイヤフラムの短絡を検出するように構成される短絡ダイヤフラムレベル検出器と、

前記ダイヤフラムの前記短絡が検出されたときに、電流が抵抗器を通じて流れるようにし、それによって、前記ダイヤフラムが短絡するときに、前記変換器内の電力損失を実質的に一定に維持するように構成されるスイッチとを備える、システム。

【請求項2】

請求項1に記載のシステムにおいて、前記抵抗器は、前記ダイヤフラムの短絡の結果として生じる前記圧力変換器内の電力損失の減少を補償するだけの十分な抵抗率を有する、システム。

【請求項3】

請求項1に記載のシステムにおいて、前記短絡ダイヤフラムレベル検出器は、電圧比較器と、温度補償された基準部とを備える、システム。

【請求項4】

請求項3に記載のシステムであって、前記発振器に電力を供給するように構成される電源をさらに備え、前記スイッチは、前記ダイヤフラムの前記短絡に検出に応答して、前記電源とグランドとの間に前記抵抗器を接続して、前記電流が該抵抗器を通じて流れるようにする、システム。

【請求項5】

請求項3に記載のシステムにおいて、前記静電容量検出回路は、キャパシタンスブリッジ回路を含み、前記ダイヤフラムが前記基準電極に短絡することによって、前記キャパシタンスブリッジ回路が飽和するときに、前記電圧比較器はハイに切り替わるように構成される、システム。

【請求項6】

請求項4に記載のシステムにおいて、前記電圧比較器は、第1の入力と、第2の入力と、出力とを有し、該電圧比較器の該第1の入力は、前記温度補償された基準部に結合され、前記電圧比較器の前記第2の入力は、前記静電容量検出回路の出力に結合され、前記電圧比較器の前記出力は、前記トランジスタの前記ベース端子に結合される、システム。

【請求項7】

請求項5に記載のシステムにおいて、前記キャパシタンスブリッジ回路は、ブリッジ構成に配列される複数のダイオード素子と、1つ又は複数の結合コンデンサとを備え、該結合コンデンサは、前記ダイヤフラムが前記基準電極に短絡すると、前記ブリッジ回路によって検出される静電容量の値を約100倍だけ増加させるように構成される、システム。

【請求項8】

請求項1に記載のシステムであって、前記発振器と前記キャパシタンスブリッジ回路との間に結合される昇圧変圧器をさらに備える、システム。

【請求項9】

請求項8に記載のシステムにおいて、前記昇圧変圧器は、約5:1の昇圧比を有し、前記昇圧変圧器の二次インダクタンスは、前記静電容量変換器の第1の容量性負荷に共振する第1の共振点と、前記静電容量変換器の第2の容量性負荷に共振する第2の共振点とを有する、システム。

【請求項10】

請求項9に記載のシステムにおいて、前記第1の容量性負荷は、前記ダイヤフラムが前記基準電極に短絡していなかった時点の前記静電容量変換器の容量性負荷を含み、該第2の容量性負荷は、前記ダイヤフラムが前記基準電極に短絡した時点の前記変換器の容量性負荷を含む、システム。

【請求項11】

請求項1に記載のシステムにおいて、前記短絡ダイヤフラムレベル検出器の出力は、前記発振器の励起振幅に比例し、該発振器は、前記ダイヤフラムが前記基準電極に短絡していなかったときに、約40ボルトのピーク・ツー・ピーク電圧、及び約250kHzの駆動周波数において、前記キャパシタンスブリッジ回路を駆動するようにさらに構成される、システム。

【請求項12】

請求項1に記載のシステムにおいて、前記発振器は、前記ダイヤフラムが前記基準電極に短絡していなかったときに、約10ボルトのピーク・ツー・ピーク電圧、及び約16kHzの駆動周波数において、前記キャパシタンスブリッジ回路を駆動するようにさらに構成される、システム。

【請求項13】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定する静電容量圧力変換器において電力損失を制御するためのシステムであって、

前記ダイヤフラムが前記基準電極に短絡したことを検出するように構成される検出回路と、

前記基準電極への前記ダイヤフラムの前記短絡が検出されたときに、前記ダイヤフラムと前記基準電極との間の前記静電容量の変化を検出するキャパシタンスブリッジ回路を駆動する発振器に接続される抵抗器を通じて電流を流すことによって、前記静電容量圧力変換器に電力を加えるように構成される電力損失回路とを備える、システム。

【請求項14】

請求項13に記載のシステムにおいて、前記検出回路は、電圧比較器と、温度補償された基準部とを備え、該電圧比較器は、前記ダイヤフラムが前記基準電極に短絡することによって前記キャパシタンスブリッジ回路が飽和するときに、ハイに切り替わるように構成される、システム。

【請求項15】

請求項14に記載のシステムにおいて、前記電力損失回路は、前記静電容量検出回路を駆動するように構成される発振器に結合される抵抗器と、前記ダイヤフラムの前記短絡が検出されたときに電流が前記抵抗器を通じて流れるようにし、それによって、前記ダイヤフラムが短絡するときに前記変換器内の電力損失を実質的に一定に維持するように構成されるスイッチとを備える、システム。

【請求項16】

静電容量圧力変換器であって、

ダイヤフラムと、

1つ又は複数の基準電極と、

前記ダイヤフラムと前記基準電極との間の静電容量の変化を検出するように構成される静電容量検出回路であって、該静電容量の変化は前記ダイヤフラムにかけられる圧力に比例する、静電容量検出回路と、

前記静電容量検出回路を駆動するように構成される発振器と、

前記基準電極への前記ダイヤフラムの短絡を検出するように構成される短絡ダイヤフラムレベル検出器と、

前記発振器に結合される抵抗器と、

前記ダイヤフラムが短絡するときに、前記変換器による電力損失を実質的に一定に維持するように、前記ダイヤフラムの前記短絡を検出するのに応答して、電流が前記抵抗器を通じて流れることができるように構成されるスイッチとを備える、静電容量圧力変換器。

【請求項17】

請求項16に記載の静電容量圧力変換器であって、前記発振器と前記キャパシタンスブリッジ回路との間に結合される昇圧変圧器をさらに備える、静電容量圧力変換器。

【請求項18】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定するように構成される静電容量圧力変換器において電力損失を制御する方法であって、

前記基準電極への前記ダイヤフラムの短絡を検出する動作、及び

前記ダイヤフラムの前記短絡によって引き起こされる前記変換器内の電力損失の減少を補償するだけの十分な量だけ該変換器において電力損失を加える動作であって、それによって前記変換器内の電力損失を実質的に一定に維持する、動作を含む、方法。

【請求項19】

請求項18に記載の方法において、前記変換器に電力を加える動作は、前記ダイヤフラムと前記基準電極との間の前記静電容量の変化を検出する静電容量検出回路を駆動するようになっている発振器に結合される抵抗器を通じて電流を流す動作を含む、方法。

【請求項20】

請求項19に記載の方法において、前記抵抗器を通じて電流を流す動作は、トランジスタのベース端子に駆動信号を印加する動作であって、電流が、前記抵抗器を通じて、該トランジスタの前記エミッタ端子から該トランジスタの前記コレクタ端子まで流れることができるようにし、それによって、前記電流が前記抵抗器を通じて流れるのに応じて十分な量の電力が散逸される、動作を含む、方法。

【請求項1】

ダイヤフラムと基準電極との間の静電容量の変化を検出するように構成される静電容量検出回路を有する静電容量圧力変換器において電力損失を制御するためのシステムであって、

前記基準電極への前記ダイヤフラムの短絡を検出するように構成される短絡ダイヤフラムレベル検出器と、

前記ダイヤフラムの前記短絡が検出されたときに、電流が抵抗器を通じて流れるようにし、それによって、前記ダイヤフラムが短絡するときに、前記変換器内の電力損失を実質的に一定に維持するように構成されるスイッチとを備える、システム。

【請求項2】

請求項1に記載のシステムにおいて、前記抵抗器は、前記ダイヤフラムの短絡の結果として生じる前記圧力変換器内の電力損失の減少を補償するだけの十分な抵抗率を有する、システム。

【請求項3】

請求項1に記載のシステムにおいて、前記短絡ダイヤフラムレベル検出器は、電圧比較器と、温度補償された基準部とを備える、システム。

【請求項4】

請求項3に記載のシステムであって、前記発振器に電力を供給するように構成される電源をさらに備え、前記スイッチは、前記ダイヤフラムの前記短絡に検出に応答して、前記電源とグランドとの間に前記抵抗器を接続して、前記電流が該抵抗器を通じて流れるようにする、システム。

【請求項5】

請求項3に記載のシステムにおいて、前記静電容量検出回路は、キャパシタンスブリッジ回路を含み、前記ダイヤフラムが前記基準電極に短絡することによって、前記キャパシタンスブリッジ回路が飽和するときに、前記電圧比較器はハイに切り替わるように構成される、システム。

【請求項6】

請求項4に記載のシステムにおいて、前記電圧比較器は、第1の入力と、第2の入力と、出力とを有し、該電圧比較器の該第1の入力は、前記温度補償された基準部に結合され、前記電圧比較器の前記第2の入力は、前記静電容量検出回路の出力に結合され、前記電圧比較器の前記出力は、前記トランジスタの前記ベース端子に結合される、システム。

【請求項7】

請求項5に記載のシステムにおいて、前記キャパシタンスブリッジ回路は、ブリッジ構成に配列される複数のダイオード素子と、1つ又は複数の結合コンデンサとを備え、該結合コンデンサは、前記ダイヤフラムが前記基準電極に短絡すると、前記ブリッジ回路によって検出される静電容量の値を約100倍だけ増加させるように構成される、システム。

【請求項8】

請求項1に記載のシステムであって、前記発振器と前記キャパシタンスブリッジ回路との間に結合される昇圧変圧器をさらに備える、システム。

【請求項9】

請求項8に記載のシステムにおいて、前記昇圧変圧器は、約5:1の昇圧比を有し、前記昇圧変圧器の二次インダクタンスは、前記静電容量変換器の第1の容量性負荷に共振する第1の共振点と、前記静電容量変換器の第2の容量性負荷に共振する第2の共振点とを有する、システム。

【請求項10】

請求項9に記載のシステムにおいて、前記第1の容量性負荷は、前記ダイヤフラムが前記基準電極に短絡していなかった時点の前記静電容量変換器の容量性負荷を含み、該第2の容量性負荷は、前記ダイヤフラムが前記基準電極に短絡した時点の前記変換器の容量性負荷を含む、システム。

【請求項11】

請求項1に記載のシステムにおいて、前記短絡ダイヤフラムレベル検出器の出力は、前記発振器の励起振幅に比例し、該発振器は、前記ダイヤフラムが前記基準電極に短絡していなかったときに、約40ボルトのピーク・ツー・ピーク電圧、及び約250kHzの駆動周波数において、前記キャパシタンスブリッジ回路を駆動するようにさらに構成される、システム。

【請求項12】

請求項1に記載のシステムにおいて、前記発振器は、前記ダイヤフラムが前記基準電極に短絡していなかったときに、約10ボルトのピーク・ツー・ピーク電圧、及び約16kHzの駆動周波数において、前記キャパシタンスブリッジ回路を駆動するようにさらに構成される、システム。

【請求項13】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定する静電容量圧力変換器において電力損失を制御するためのシステムであって、

前記ダイヤフラムが前記基準電極に短絡したことを検出するように構成される検出回路と、

前記基準電極への前記ダイヤフラムの前記短絡が検出されたときに、前記ダイヤフラムと前記基準電極との間の前記静電容量の変化を検出するキャパシタンスブリッジ回路を駆動する発振器に接続される抵抗器を通じて電流を流すことによって、前記静電容量圧力変換器に電力を加えるように構成される電力損失回路とを備える、システム。

【請求項14】

請求項13に記載のシステムにおいて、前記検出回路は、電圧比較器と、温度補償された基準部とを備え、該電圧比較器は、前記ダイヤフラムが前記基準電極に短絡することによって前記キャパシタンスブリッジ回路が飽和するときに、ハイに切り替わるように構成される、システム。

【請求項15】

請求項14に記載のシステムにおいて、前記電力損失回路は、前記静電容量検出回路を駆動するように構成される発振器に結合される抵抗器と、前記ダイヤフラムの前記短絡が検出されたときに電流が前記抵抗器を通じて流れるようにし、それによって、前記ダイヤフラムが短絡するときに前記変換器内の電力損失を実質的に一定に維持するように構成されるスイッチとを備える、システム。

【請求項16】

静電容量圧力変換器であって、

ダイヤフラムと、

1つ又は複数の基準電極と、

前記ダイヤフラムと前記基準電極との間の静電容量の変化を検出するように構成される静電容量検出回路であって、該静電容量の変化は前記ダイヤフラムにかけられる圧力に比例する、静電容量検出回路と、

前記静電容量検出回路を駆動するように構成される発振器と、

前記基準電極への前記ダイヤフラムの短絡を検出するように構成される短絡ダイヤフラムレベル検出器と、

前記発振器に結合される抵抗器と、

前記ダイヤフラムが短絡するときに、前記変換器による電力損失を実質的に一定に維持するように、前記ダイヤフラムの前記短絡を検出するのに応答して、電流が前記抵抗器を通じて流れることができるように構成されるスイッチとを備える、静電容量圧力変換器。

【請求項17】

請求項16に記載の静電容量圧力変換器であって、前記発振器と前記キャパシタンスブリッジ回路との間に結合される昇圧変圧器をさらに備える、静電容量圧力変換器。

【請求項18】

ダイヤフラムと基準電極との間の静電容量の変化を検出することによって圧力を測定するように構成される静電容量圧力変換器において電力損失を制御する方法であって、

前記基準電極への前記ダイヤフラムの短絡を検出する動作、及び

前記ダイヤフラムの前記短絡によって引き起こされる前記変換器内の電力損失の減少を補償するだけの十分な量だけ該変換器において電力損失を加える動作であって、それによって前記変換器内の電力損失を実質的に一定に維持する、動作を含む、方法。

【請求項19】

請求項18に記載の方法において、前記変換器に電力を加える動作は、前記ダイヤフラムと前記基準電極との間の前記静電容量の変化を検出する静電容量検出回路を駆動するようになっている発振器に結合される抵抗器を通じて電流を流す動作を含む、方法。

【請求項20】

請求項19に記載の方法において、前記抵抗器を通じて電流を流す動作は、トランジスタのベース端子に駆動信号を印加する動作であって、電流が、前記抵抗器を通じて、該トランジスタの前記エミッタ端子から該トランジスタの前記コレクタ端子まで流れることができるようにし、それによって、前記電流が前記抵抗器を通じて流れるのに応じて十分な量の電力が散逸される、動作を含む、方法。

【図1A】

【図1B】

【図2】

【図1B】

【図2】

【公表番号】特表2010−500564(P2010−500564A)

【公表日】平成22年1月7日(2010.1.7)

【国際特許分類】

【出願番号】特願2009−523843(P2009−523843)

【出願日】平成19年8月9日(2007.8.9)

【国際出願番号】PCT/US2007/017708

【国際公開番号】WO2008/021178

【国際公開日】平成20年2月21日(2008.2.21)

【出願人】(592053963)エム ケー エス インストルメンツ インコーポレーテッド (114)

【氏名又は名称原語表記】MKS INSTRUMENTS,INCORPORATED

【Fターム(参考)】

【公表日】平成22年1月7日(2010.1.7)

【国際特許分類】

【出願日】平成19年8月9日(2007.8.9)

【国際出願番号】PCT/US2007/017708

【国際公開番号】WO2008/021178

【国際公開日】平成20年2月21日(2008.2.21)

【出願人】(592053963)エム ケー エス インストルメンツ インコーポレーテッド (114)

【氏名又は名称原語表記】MKS INSTRUMENTS,INCORPORATED

【Fターム(参考)】

[ Back to top ]