高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、半導体処理の分野に関し、より詳細には、トランジスタのゲートスタックにおける金属ゲート電極のような導体構造の堆積に関する。

【背景技術】

【0002】

演算能力の増加及び集積回路サイズの低減の継続的な要求により、集積回路を形成する電子デバイスのサイズを低減する継続的な要求が存在する。例えば、トランジスタのサイズは、例えば集積回路のトランジスタ密度を増加させ、演算能力を増加させるために、低減されることが継続されている。トランジスタのサイズが小さくなるため、トランジスタのゲート電極からトランジスタのチャネル領域を別にしたゲート誘電体層のような、これらの構成要素も同様である。ゲート誘電体層における望まれない電流リークを防ぐために、より薄い誘電体層は、通常、高い誘電率(high−k)材料を使用することを要求する。しかし、high−k材料がいくつかの従来のシリコンベースのゲート電極材料に用いられた場合、high−k材料を有するトランジスタは、低いパフォーマンス特性となってしまう。したがって、トランジスタのような電子デバイスのhigh−kゲート誘電体材料での使用に適切である、導体ゲート電極のような導電材料に対する継続的な需要が存在する。

【発明の概要】

【0003】

いくつかの実施形態によれば、半導体処理の方法(process)が提供される。本方法は、基板にゲート電極を形成する工程を含む。ゲート電極を形成する工程は、ゲート誘電体を有する基板を反応チャンバ内に提供する工程を含む。遷移金属化合物を含む第1の層は、堆積中に、基板をプラズマ又はプラズマ発生(plasma−generated)ラジカルに露出せずに、ゲート誘電体に堆積される。第1の層は、その後、水素含有ガスに露出される。次いで、遷移金属化合物を含む第2の層は、堆積される。

【0004】

他のいくつかの実施形態によれば、半導体処理の方法が提供される。この方法は、金属電極を堆積する工程を含む。金属電極を堆積する工程は、ゲート誘電体に金属材料を堆積する工程を含む。金属材料を堆積するための前駆体は、プラズマ活性化されていない。金属材料は、励起された水素含有種に露出される。次いで、金属材料を励起された水素含有種に露出した後に、さらなる金属は、金属材料に堆積される。

【図面の簡単な説明】

【0005】

本発明の制限されず、包括的でない実施形態は、以下の図面を参照して説明され、全体にわたって同じ参照番号は、同じ部材に示される。

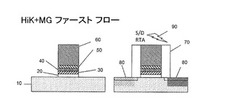

【図1a】図1aは、金属ゲート電極を形成する各種処理フローの例を示す図である。

【図1b】図1bは、金属ゲート電極を形成する各種処理フローの例を示す図である。

【図1c】図1cは、金属ゲート電極を形成する各種処理フローの例を示す図である。

【図2】図2は、導電材料を堆積する各種処理シーケンスの例を示す図である。

【図3】図3は、図2に示すシーケンスの結果の図解の例を示す図である。

【図4】図4は、導電材料を堆積するさらなる処理シーケンスの例を示す図である。

【図5】図5は、図4に示すシーケンスの結果の図解の例を示す図である。

【図6】図6は、図2及び4の処理シーケンスのいくつかの状態を示す図である。

【図7】図7は、励起された水素含有種を発生するピーク間(peak−to−peak)電圧が変化するときの仕事関数の変化についての図解の例を示す図である。

【図8】図8は、励起された水素含有種を発生するピーク間電圧が変化すると共に、励起された水素含有種の各パルスを発生するために印加される電力の持続期間が変化するときの有効仕事関数の変化についての図解の例を示す図である。

【図9】図9A−9Dは、ゲート電極スタックの断面斜視図の例を示す図である。

【図10】図10は、ゲート電極スタックの断面斜視図の例を示す図である。

【図11】図11は、ゲート電極スタックの断面斜視図の例を示す図である。

【図12】図12は、ゲート電極スタックの断面斜視図の例を示す図である。

【発明を実施するための形態】

【0006】

いくつかの実施形態によれば、導電材料の第1の層を堆積し、第1の層を(ガス状の水素含有種を含む)水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、導体構造が形成される。いくつかの実施形態では、導体構造は、誘電体層に形成される。例えば、導体構造は、トランジスタの一部として、high−kゲート誘電体のようなゲート誘電体に形成されたゲート電極であってもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカル(すなわち、プラズマにより発生されたラジカル)に露出されないノン−プラズマ又はノン−ラジカル処理を用いて堆積されてもよい。第1の層は、その後、水素含有種に露出される。いくつかの実施形態では、水素含有種は、水素含有プラズマの一部である励起された水素含有種であってもよい。いくつかの実施形態では、水素含有種は、遠隔プラズマ発生器で発生され、その後、第1の層を含む反応チャンバへ流される水素含有ラジカルを含む。

【0007】

有利には、導電材料がトランジスタの金属ゲートを形成するために用いられた場合、ゲートスタックのゲート電極の仕事関数は、約4.85eV以上、又は約5eV以上であってもよい。いくつかの実施形態では、第1の層の厚さは、約5nm未満、約4nm未満、約3nm未満、又は約1−3nm未満である。第1の層は、第1の層を形成する材料の単分子層よりも薄いことが好ましい。

【0008】

いくつかの実施形態では、ノン−プラズマ処理により第1の層を形成することに加えて、第2の層もまた、基板がプラズマ又はプラズマ発生ラジカルに露出されないノン−プラズマ処理により形成されてもよい。いくつかの実施形態では、第2の層は、プラズマ又はラジカルへの露出により形成されてもよい。

【0009】

導体構造を形成する導体材料は、遷移金属化合物のような金属材料であってもよい。遷移金属は、制限されないが、チタン、タンタル、ニオブ、モリブデン、ハフニウム、ジルコニウム及びタングステンのような高融点金属であってもよい。いくつかの実施形態では、導体材料は、金属を窒化することにより形成された窒化物であってもよい。いくつかの実施形態では、導電材料が炭化金属又は窒炭化金属になりうるように、炭素のような他の元素は、導電材料に組み込まれてもよい。このような材料の制限されない例は、窒化タンタル、炭化タンタル、窒炭化タンタル、窒化チタニウム、炭化チタニウム、窒炭化チタニウムを含む。材料の制限されない他の例は、窒化ニオブ、炭化ニオブ、窒炭化ニオブ、窒化モリブデン、炭化モリブデン、窒炭化モリブデン、窒化ハフニウム、窒化ジルコニウム、タングステン、窒化タングステンを含む。

【0010】

第1の層は、また、第2の層の堆積前に、酸素のような各種の他の化学種に露出されてもよい。いくつかの実施形態では、導電材料の一又はそれ以上の層は、第1の層と第2の層との間に堆積されてもよい。

【0011】

いくつかの実施形態では、金属ゲート又は金属電極は、実質的に同一な化合物である第1及び第2の層で形成されてもよく、第1及び第2の層は、金属材料の均質な層でありうる金属材料の単層を形成する。いくつかの実施形態では、第1及び第2の層は、異なる遷移金属化合物を含む異なる金属材料で形成されてもよい。異なる遷移金属化合物は、異なる遷移金属を含んでもよく、及び/又は層と層との間で異なる他の元素を含んでもよい。いくつかの実施形態では、第1及び第2の層の一方又は双方は、異なる材料のサブレイヤーで形成されるラミネート層であってもよい。例えば、ラミネート層は、異なる遷移金属化合物のサブレイヤーで形成されてもよい。いくつかの実施形態では、第1及び第2の層は、同一の又は異なるラミネート層で形成されてもよい。

【0012】

high−K(HiK)金属ゲート(MG)相補型金属酸化半導体(CMOS)技術は、高容量な集積回路の製造において、従来の酸窒化ポリシリコン(poly−SiON)トランジスタデバイスに対する代替技術を提供することがわかる。High−k誘電体は、トランジスタのゲート誘電体を形成するために用いられてもよく、本明細書で記述した遷移金属化合物のような金属材料は、トランジスタのゲート電極を形成するために用いられてもよい。これらのhigh−k誘電体及びゲート電極は、いわゆる“ゲート−ファースト”フロー及び“ゲート−ラスト”フローの2つを含む各種のHiK−MG集積フローを用いてトランジスタデバイスに組み込まれてもよい。後者のアプローチは、Replaceable Metal Gate (RMG)とも呼ばれ、順に“HiK−ファースト”及び“HiK−ラスト”という2つのサブアプローチを有する。

【0013】

各種のHiK−MG処理フローは、図1a−1cに図示される。全てのこれらのHiK−MG処理フローは、HiK誘電体層の上部に堆積される共通の金属電極を有する。以下に詳細を記載するように、フロー間で異なる点の一つは、High Thermal Budgetステップ(基板が段階的な温度に露出される処理ステップ)の行われるタイミングである。高温アニール、典型的には、Rapid Thermal Anneal(RTA)は、ソース及びドレイン領域を形成するために行われる。“ゲート−ファースト”処理フローでは、先に金属電極が堆積され、その後、高温アニール工程に露出されるが、“ゲート−ラスト”フローでは、金属電極は、高温アニール工程の後に、堆積される。二つの処理フロー間の他の異なる点は、“ゲート−ラスト”フローでは、高い金属ゲートコンフォーマリティに対する要求が相対的に高く、そのため、このフローでは、金属電極層は、高いアスペクト比を有する相対的に狭いトレンチに堆積される(図1b)。

【0014】

図1a−1cは、ここで、より詳細に説明される。各処理フローの各図示された構造は、処理フローの各種の時間におけるトランジスタの断面図を示し、左から右へ時間が進む。最も左の構造は、最先に形成された図示された構造であり、最も右の構造は、最後に形成された図示された構造である。

【0015】

図1aは、“ゲートファースト”処理フローを図示している。一番目に図示された位置では、基板10が提供され、二酸化シリコンインターフェース層から形成された覆っているゲートスタック20と、high−k誘電体層30と、仕事関数をチューニングする誘電体キャップ40と、金属電極層50と、ポリシリコン層60と、を有する。二番目に図示された位置では、側壁スペーサ70及びソース/ドレイン領域80は、次いで形成される。ソース/ドレイン領域の活性化及び形成のためのRapid Thermal Annealは、符号90により示される。

【0016】

図1bは、high−k誘電体が初めに形成される“ゲート−ラスト”処理フローを図示する。図1bの図示された一番目の位置では、基板10は、二酸化シリコンインターフェース層から形成された覆っているゲートスタック20と、high−k誘電体層30と、エッチストップ層52と、ポリシリコン層62と、が形成される。図1bの図示された二番目の位置では、側壁スペーサ70及びソース/ドレイン領域80は、次いで形成される。ソース/ドレイン領域は、Rapid Thermal Annealにより形成され、符号90により示される。図1bの図示された三番目の位置では、ポリシリコン層62が除去され、その跡にトレンチ64が残る図1bの図示された四番目の位置では、金属電極54は、トレンチに堆積され、金属充填56は、残りのトレンチの容積を充填するために堆積される。

【0017】

図1cは、high−k誘電体が最後に形成される“ゲート−ラスト”処理フローを図示する。図1cの図示された一番目の位置では、基板10は、二酸化シリコンインターフェース層から形成された覆っているゲートスタック20と、ポリシリコン層66とが形成される。図1cの図示された二番目の位置では、側壁スペーサ70及びソース/ドレイン領域80が形成される。ソース/ドレイン領域は、Rapid Thermal Annealにより形成され、符号90により示される。図1cの図示された三番目の位置では、ポリシリコン層66が除去され、トレンチ68が残る。図1cの図示された四番目の位置では、high−k誘電体層30は、トレンチに堆積され、金属電極層54は、high−k誘電体層30上にわたって堆積され、金属充填56は、残りのトレンチを充填するように堆積される。

【0018】

図1a−1cを参照すると、二酸化シリコンインターフェース層20は、酸素種を有する既存の堆積及び/又は反応を含む各種の処理により形成されてもよい。例えば、二酸化シリコンインターフェース層20は、使用される処理フロー及び二酸化シリコンインターフェース層の所望の特性に応じた、化学的な酸化、CVD酸化、熱酸化であってもよい。

【0019】

CMOS動作のためのターゲット閾値電圧(Vt)を達成するために、適切な有効仕事関数(Effective Work Functions (EWF))が要求される。例えば、平面ハイパフォーマンス(High Performance(HP))CMOSロジックデバイスに対しては、NMOS及びPMOS EWFターゲットは、それぞれ4.2eV及び5.1eVであってもよい。このような仕事関数値は、しばしば、Siの伝導帯及び価電子帯のエッジそれぞれに近い“バンド−エッジ(band−edge)”と呼ばれる。“ゲート−ラスト”フローを用いて形成されるトランジスタデバイスのコンフォーマリティ要求に合致する特定の金属材料である、単一のPMOSバンド−エッジ金属材料の例は知られていない。

【0020】

例としては、窒化チタン(TiN)は、HiK−MGデバイス用の金属材料に通常用いられる。TiCl4−NH3に基づくALD TiN(Ti前駆体としてTiCl4を用い、N前駆体としてNH3を用い、ALD処理を用いて堆積されたTiN)は、単一のウェーハ又はバッチ型リアクタにおけるRMGデバイスの狭トレンチにコンフォーマリィに堆積されてもよい。しかし、堆積方法及び/又は処理状態に関わらず、TiNの典型的なEWF値4.7−4.75eVは、low−Vt(HP)デバイス用に所望される5.1eVを下回ることがわかっている。Hinkle et al., ECS Transactions, 35(2) 285−295 (2011)は、N2中に、残留する又は10%O2にを有する酸素含有環境でアニールを行い、Wの上部金属層(クラッド層)を堆積することにより、TiN膜のEWFが約5eVの値で増加しうることを実証している。10%濃度のO2を有する大気を用いることによるアグレッシブなアニール及び/又は450℃又は500℃のアニール温度を用いることは、EWFを増加させることが報告されている。しかし、TiNが酸化に影響を受けやすいため、450℃でのN2に10%のO2でのアグレッシブなアニールは、TiN層全体を酸化してしまい、これは、望まれていない。

【0021】

有利には、本明細書に記載されるいくつかの実施形態は、450℃以上の温度での明白な酸化状態に金属層全体を露出することなく、金属電極又は金属電極の金属下部層を用いて、ゲートスタックのEWFのチューニングを可能にする。いくつかの実施形態では、このようなチューニングは、約450℃以下、約420℃以下、又は約400℃以下の温度で行われうる。

【0022】

いくつかの実施形態では、金属材料(例えば、遷移金属化合物)の第1の層は、堆積中に、プラズマ又はラジカルのような励起種に基板を露出することなく基板に堆積される。第1の層は、いくつかの実施形態では、約5nm未満、約4nm未満、約3nm未満、約1−3nm未満の厚さである。いくつかの実施形態では、厚さ約2nmである。その後、この第1の層は、処理される。He又はArのような不活性ガスと混合するか否かにかかわらず、この処理は、薄い金属層を、水素含有ガス、より好ましくは、水素含有ラジカル又は水素含有プラズマのような励起された水素含有種に露出することを含む。励起種の露出は、所望の温度及び所望時間でのプラズマ電力で行われてもよい。いくつかの実施形態では、プラズマ電力は、4秒以下のパルスで印加される。励起種は、基板として同一反応チャンバ内に形成されるプラズマの一つであってもよく、遠隔で発生され反応チャンバへ流入されてもよい。水素含有ガスは、いくつかの実施形態では、例えば、水素又はアンモニアであってもよい。続いて、金属材料(例えば、第2の遷移金属化合物)の第2の層は、金属材料の第1の層に堆積される。これらの3つのステップは、同一又は異なる温度で、同一又は異なるリアクタで行われてもよい。

【0023】

励起種の露出の前及び/又は後に、酸素含有ガスへの基板の露出が行われてもよく、トリートメントが酸素含有ガスへの露出なしで行われてもよい。若しくは、酸素含有ガスへの露出は、所望の状態及び所望の期間下での反応チャンバ内において、制御された手法で行われてもよい。酸素含有ガスは、いくつかの実施形態では、酸素ガス及び窒素ガスの混合物であってもよい。いくつかの実施形態では、酸素含有ガスは、ある量の水蒸気を含んでもよい。酸素含有ガスへの露出は、金属材料を堆積するために用いる堆積チャンバにおいて、イン−サイチュで行われてもよい。これに代えて、基板は、反応チャンバからの基板の搬出及びクリーンルームエアへの露出(いわゆる“エアブレイク”工程により、酸素含有ガスへ露出されてもよい。

【0024】

金属材料の第1の層は、物理気相堆積(PVD)、化学気相堆積(CVD)、パルス化CVD又は原子層堆積(ALD)により堆積されてもよい。金属材料の第2の層は、プラズマエンハンスドCVDやプラズマエンハンスドALDを含む、PVD、CVD、パルス化CVD、又はALDにより堆積されてもよい。いくつかの実施形態では、金属層は、ALDにより堆積され、高いステップカバレージを達成する。前駆体は、交互に連続的に、一時的に分離されたパルスで反応チャンバへ流入されうる。いくつかの実施形態では、化合物の約単分子層又はそれ未満のものは、各前駆体の1つのパルスシーケンスで、堆積サイクル単位で形成される。例えば、TiNは、一時的に分離されたパルスでの前駆体としてのTiCl4及びNH3を用いて形成されうる。本明細書で述べたように、いくつかの実施形態では、金属材料は、窒化タンタル、炭化タンタル、窒炭化タンタル、炭化チタン、窒炭化チタン、窒化ニオブ、炭化ニオブ、窒炭化ニオブ、窒化モリブデン、炭化モリブデン、窒炭化モリブデン、窒化ハフニウム、窒化ジルコニウム、タングステン、及び窒化タングステンを含みうる。いくつかの実施形態では、第1及び第2の層は、単一材料で形成されてもよい。いくつかの実施形態では、第1及び第2の層の一方又は双方は、複数のサブレイヤーで形成されたラミネート層であってもよい。

【0025】

例としては、各種金属の堆積が調査され、これらの層を形成する堆積シーケンスは、図2及び4に詳述される。図2及び4に示された処理の後、全てのサンプルは、形成ガス(N2中に4%のH2)で420℃、30分のアニールを受けた。還元環境での堆積及び処理は、ASM International’s EmerALD(登録商標)のALD用シングルウェーハリアクタシステムで行われ、これは、また、プラズマが反応チャンバ内で発生されうるプラズマオプションを提供する。EmerALD(登録商標) シングル ウェーハ リアクタシステムは、ASM International N.V., Almere, The Netherlands から入手可能である。図2、4及び6は、TiN堆積のための各種詳細を提供する。他のいくつかの実施形態では、窒化タンタル、炭化タンタル、窒炭化タンタル、炭化チタン、窒炭化チタン、窒化ニオブ、炭化ニオブ、窒炭化ニオブ、窒化モリブデン、炭化モリブデン、窒炭化モリブデン、窒化ハフニウム、窒化ジルコニウム、タングステン、及び窒化タングステンのような金属材料は、同様の結果を達成するために同様の工程ステップ及び条件を用いてTiNと結合して、又はそれに代えて形成される。

【0026】

本明細書に開示された実施形態に係る堆積は、EWFで野増加を提供することがわかる。有効仕事関数(EWF)値及び等価酸化厚さ(equivalent oxide thickness、EOT)は、C−V測定及びMIS構造から抽出される。金属電極は、シリコン基板上の2nmのHfO2層の上部及び1nmの界面SiO2に堆積される。図2を参照すると、全てのTiN堆積は、390℃で行われ、エアブレイクは、第1のTiN層堆積と膜処理工程との間、及び膜処理工程と第2のTiN層堆積工程との間の両方で適用される。単一の10nm厚さのALD TiN層は、通常、約4.7−4.75eV(1F)の仕事関数を与える。しかし、本明細書に開示された実施形態に係る堆積は、より大きなEWFをもたらす。例えば、2nmのALD TiN層、それに続くエアブレイク、H2/Arプラズマトリートメント(2秒ごとに32パルス)、第2のエアブレイク及び10nmのALD TiN層は、4.96eV(1F)の格段に大きなEWFを示す。

【0027】

EWFの増加は、励起された水素種への露出にあると考えられうる。図3を参照すると、下部及び上部ALD TiN層間での32サイクルのプラズマ−エンハンスドALD(PEALD)による薄いTaCN層の成長によっても、4.98eV(1C)又は5.04eV(1B)のより大きなEWF値が達成されることがわかる。サーマルALD TaCNによるPEALD TaCN層の置換は、低い仕事関数をもたらし、単一の10nmのALD TiN層(1D及び1E)の仕事関数と近い。これらの結果は、PEALD TaCNで得られたより大きなEWFが、下部(第1の)TiN層に対するPEALD TaCN 堆積時のAr/H2含有プラズマ活性への露出にあると考えられうる。また、2から3又は4へのプラズマパルスの増加した期間が、増加した等価酸化厚さ(equivalent oxide thickness、EOT)での増加EWFを導くことがわかる。最後に、2nmの第1のTiN層と薄い第2のTiN層との間のみのエアブレイクの適用は、プラズマトリートメント工程(1G)を適用することがなく、EWFの増加を招かないことが観察される。

【0028】

また、上述したTiN層用のプロセスと同様のプロセスを用いて、TiN/TaCNの二つの層及びTaC層の仕事関数は、増加しうることがわかる。TiN/TaCNの二つの層及びTaC層は、プラズマにより発生されたラジカル無しの熱活性プロセス、及び水素含有ガスでの層のトリートメントにより堆積され、このトリートメントは、水素ラジカル又は水素含有プラズマへの層の露出を含む。仕事関数は、また、熱活性水素含有ガスへの層の露出により増加されうる。

【0029】

他の実験では、その結果が図4に示され、以下のパラメータの影響が、また、調査された。

・エアブレイクの回数及びそれらの位置(場所)の効果:

Ar/H2プラズマトリートメントの前後;

プラズマトリートメントの前;

プラズマトリートメントの後;

エアブレイクなし;

・TiN堆積温度(325度 対 390℃)の効果、及び

・Ar/H2プラズマトリートメント(325度 対 390℃)時のウェーハ温度の効果。

Ar/H2プラズマは、2秒ごとの32パルスでのパルスワイズ(pulse−wise)で適用される。

【0030】

図5で観察されるように、TiN膜の325℃の堆積温度は、体系的に、より大きなEOT値をもたらす。有益なEWF/EOTトレードオフは、以下のシーケンス(図4の2C)で達成されうる。

第1及び第2の層の双方は、390℃で成長した;

Ar/H2プラズマトリートメントは、390℃で行われた;及び

二つのエアブレイク(Ar/H2プラズマトリートメントの前後)。

【0031】

同様の条件で処理されたサンプルの図2と図4との結果(図2の1F 対 図4の2B)には差異が存在することがわかる。これらの変位は、図2と図4の実験の時間間隔によるものである。また、図4の実験のエアブレイク(1−2日)は、図2の実験のエアブレイク(1−2週間)よりも短い。それにも関わらず、各セットの実験では、Ar/H2プラズマへの露出を有する全てのシーケンスは、このような露出を有さないセット(図2の1A、図4の2A及び2E)よりEWFの増加を提供する。

【0032】

図2及び4で説明された実験で用いられた各種の追加プロセス条件は、図6に総括される。TBTDETは、第三級ブチルイミド トリス(ジメチルアミノ)タンタル、Ta[N(C2H5)2]3[=NC(CH3)3]であることがわかる。異なる温度及びわずかな(又は全く無い)エアブレイクにおいて、所望の大きなEWFは、各種トリートメントパラメータを調整することにより達成されてもよいと考えられる。プロセスパラメータのいくつかの例は、1)下部TiN層厚さの変更、2)熱のみのトリートメント(プラズマ無し)を含む、プラズマ電力及び時間の変更、3)リアクタ内のO2,N2及びH2量の変更を含むように変更されうるが、これに限定されない。上述した実験では、EWF/EOT近似曲線が観察され、高いEWFが高いEOT値で観察される。一方、いくつかの用途では、低いEOT値での高いEWFを達成することが望まれる。上記のパラメータのバリエーションは、高いEWF及び低いEOT間での有利なトレードオフを可能にしうる。

【0033】

理論による制限無しでは、エアブレイクと水素含有ガスへの露出との組み合わせは、EWFにも影響しうると考えられる。例えば、エアブレイクの後に、Ar/H2プラズマトリートメント、別のエアブレイクが続き、グレインサイズ/モフォロジー及び/又は金属含有スタックのO及びN量が変化し、その結果、スタックのEWF(例えば、TiNスタック)は増加しうる。さらに、エアブレイクにより、第1の金属層を水素含有ガス又は水素含有プラズマに露出する工程時に、酸素又は水素含有不純物(例えば、O2又はH2O)が存在するようになる。これらの不純物は、所望のスタック特性を達成する役割を果たしてもよい。

【0034】

例えば、理論による制限を求めること無しでは、EWFのいくつかの増加は、第1の金属層とそれに続く金属層との間の界面でのH−Oダイポールの形成の結果であってもよいと考えられる。低い濃度の酸素が提供されてもよく、低い濃度の酸素は、リアクタ及び/又は第1の金属層の残りの酸素の存在から生じうる、又は、水素ラジカル又はプラズマトリートメントの前、最中、又は後の金属層の酸素への意図的な露出から生じうる。酸素は、水素トリートメントの前及び/又は後のエアブレイクから生じうる。好ましくは、酸素濃度は、十分に低いレベルで維持されて、金属層の参加が制限され、これは、所望されないEOTの増加をもたらしうる。

【0035】

図7では、プラズマトリートメント時のVpp(ピーク間電圧、peak−to−peak Voltage)は、より決定的な要因であり、EWFとの相関よりもプラズマ電力のほうが好ましい、つまり、より高いEWFがより高いVppのために得られる、ことが示される。さらなる結果は、390℃で堆積されたTiNについて図8に示される。2nm厚さの第1のTiN膜は堆積され、その後、32パルスのプラズマ露出は、図8に示すようなVpp及びパルス期間で適用され、その後、10nm厚さの第2のTiN膜は堆積される。エアブレイクは、水素プラズマトリートメントの前後に適用される。水素プラズマトリートメントは、0.5Torrでの水素/Ar混合物が適用される。図8からは、高いVpp及び/又は長いパルス期間は高いEWFをもたらすことが観察されうる。いくつかの実施形態では、Vppは、約110V以上、約130V以上、約160V以上、又は約200V以上でありうる。いくつかの実施形態では、励起された水素種を露出する期間は、約2秒以上、約4秒以上、又は約2−4秒でありうる。リファレンスとして、プラズマに露出せずに形成されたTiNは、上述したように、約4.7又は4.73の低いEWFを有する。

【0036】

図1b−1cを再度参照すると、いくつかの実施形態では、第1及び第2の層の堆積により形成された金属材料は、電極54として用いられてもよいことがわかる。よって、いくつかの実施形態では、第1及び第2の層の堆積は、誘電体材料で形成されたスペーサにより規定される狭トレンチで行われてもよく、金属は、続いて、ゲート電極54により規定される開口に堆積されてもよい。

【0037】

CMOSプロセスでの金属電極スタックの堆積のいくつかの例は、以下の図9a−12を参照して提供される。同一のハッチング及び網掛けは、同一の層を示す。プロセスフローは、高い仕事関数を有するPMOS金属電極及び低い仕事関数を有するNMOS金属電極の堆積を含む。以下で説明する金属は、例示であり、他の金属も用いることができる。例えば、各種の他の金属は、本明細書で説明したように、TiNの代わりに用いられてもよい。

【0038】

(実施例1)

実施例1は、図9a−9cを参照して説明する。ゲート誘電体は、HfO2を含んでもよい。PMOS金属電極は、下部から上部へ向かって、2nmTiN層、1nmTaCN層、4nmTiN層、5nmTiAl層、及び充填金属の層の堆積により形成される。NMOS金属電極は、下部から上部へ向かって、2nmTiN層、1nmTaCN層、5nmTiAl層、及び充填金属の層の堆積により形成される。TiAlは、NMOSについての低い仕事関数を提供する。PMOSスタックでは、しかし、TiAl層は、HfO2/金属電極界面から離れており、HfO2/金属電極界面での仕事関数の影響は制限されている。PMOSスタックでのAr/H*でのトリートメント(H*はプラズマでの水素ラジカルのような励起された水素含有種を示す)は、プラズマエンハンスド堆積プロセスがTaCN層(図9c)又はTaCN層堆積の後に(図9d)の形成に用いられた場合のTaCN層堆積時に、TaCN層堆積の前に適用されてもよい。

【0039】

図9aのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.水素含有ガスでの第1のTiN層のトリートメント;

3.サーマルプロセスによるTaCN層の堆積及び第2のTiN層の堆積;

4.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;及び

5.TiAl層の堆積及び金属を充填。

【0040】

図9bのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.NMOSデバイスの保護層(例えば、フォトレジスト又はSiO2層)を形成するためのリソグラフィ及びエッチング;

3.水素含有ガスでのTiN層のトリートメント;

4.保護層の除去;

5.サーマルプロセスによるTaCN層の堆積及び第2のTiN層の堆積;

6.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;及び

7.TiAl層の堆積及び金属を充填。

【0041】

図9cのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.水素含有プラズマエンハンスドプロセスによるTaCN層の堆積;

3.第2のTiN層の堆積;

4.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;及び

5.TiAl層の堆積及び金属を充填。

【0042】

図9dのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層及びTaCN層の堆積;

2.NMOSデバイスの保護層(例えば、フォトレジスト又はSiO2層)を形成するためのリソグラフィ及びエッチング;

3.水素含有ガスでのトリートメント;

4.保護層の除去;

5.第2のTiN層の堆積;

6.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;

7.(残りのTaCN層の厚さを削減するための追加エッチング);

8.TiAl層(nEWF)の堆積及び金属層の前に薄いバリア金属層(例えば、TiN層)を堆積し、追加で金属を充填する。

【0043】

(実施例2)

実施例2は、図10を参照して説明する。ゲート誘電体層は、HfO2を含んでもよい。PMOS金属電極は、2nmTiN層の堆積、水素含有ガスによるTiN層のトリートメント、4nmTiN層の堆積、及び充填金属の堆積により形成される。NMOS金属電極は、2nmの第1のTiN層、5nmのTiAl層、4nmのTiN層、及び充填金属層を含む。

図10のスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層及びTiAl層の堆積;

2.NMOSデバイスの保護層(例えば、フォトレジスト又はSiO2層)を形成するためのリソグラフィ及びエッチング;

3.PMOSデバイスからTiAl層をTiN層のエッチストップと共に除去;

4.水素含有ガスでのトリートメント;

5.保護層の除去;及び

6.第2のTiN層の堆積及び金属を充填。

【0044】

(実施例3)

実施例3は、図11を参照して説明する。PMOS電極は、2nmのTiN層の堆積、水素含有ガスによるTiN層のトリートメント、5nmTaC層の堆積、及び充填金属の堆積により形成される。NMOSスタックは、5nmのTaC層及び充填金属の層を含んでもよい。TaC層は、また、NMOSデバイスにとって好ましい、低い仕事関数を提供し、TiAlに相当する。しかし、TaCはALDにより堆積されうるのに対して、TiAlは通常PVDプロセスにより堆積される点で有利である。

図11のスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.水素含有ガスでのトリートメント;

3.NMOSデバイスからTiNをHfO2のエッチストップと共に除去するためのリソグラフィ及びエッチング(追加でSiO2ハードマスク);

4.(SiO2ハードマスクを適用可能な場合には、追加でハードマスクの除去);

5.NMOSデバイスのEWFを設定するためにTaC層を堆積;及び

6.充填金属を堆積。

【0045】

(実施例4)

実施例4は、図12を参照して説明する。PMOS金属電極は、5nmのTaC層の堆積、水素含有ガスでのトリートメント、及び充填金属の堆積により形成される。NMOS金属電極は、5nmのTaC層及び充填金属を含み、NMOS金属電極での唯一の差異は、水素含有ガスでのトリートメントを行わないことである。水素含有ガスでのトリートメントのみで、TaC層の仕事関数は、十分に変化し、PMOS及びNMOSデバイスのための適切な仕事関数を達成しうることを意図する。

図12のスタックは、以下のプロセスフローを用いて製造されうる。

1.(nEWFを有する)TaC層の堆積;

2.NMOSデバイスを保護層(例えば、フォトレジスト又はSiO2層)と共にマスクするためのリソグラフィ及びエッチング;

3.PMOSデバイスのためのEWFを調整するために水素含有ガスでのトリートメント;

4.NMOSデバイスから保護層の除去;及び

5.充填金属を堆積。

【0046】

図1から図4の全ての実施例に対して、図9a−12に示すように、例えば、2nmのTiN層のような薄いバリア層は、充填金属層の堆積前に追加で堆積されてもよい。理論により制限されず、このようなバリア層は、充填金属からの不純物の不拡散(in−diffusion)に対する仕事関数が変化しやすい(sensitive)層を保護しうることが考えられる。

【0047】

本明細書に記載されたプロセスは、PMOS及びNMOSデバイスの有効仕事関数を同時に調整するために用いられてもよい。また、異なる仕事関数を有する異なるデバイスのグループが形成されてもよい。異なる仕事関数は、トランジスタデバイスのための異なる閾値電圧を提供しうることがわかる。したがって、いくつかの実施形態では、高速及び高電力消費をもたらす低いVt(Vt=閾値電圧)を有するデバイスのグループ、中程度の速度及び中程度の電力消費をもたらす中程度のVtを有するデバイスのグループ、及び低速及び低電力消費をもたらす高いVtを有するデバイスのグループを形成することが可能であり、全てのグループはプロセスフローにより同一基板に形成される。異なるグループは、本明細書で説明したプロセスに係る異なる水素トリートメントに露出されてもよく、又は本明細書で説明したプロセスに係る異なるスタックは、各グループのために形成されてもよい。例えば、各種グループのための電極層は、同時に堆積されてもよく、一又はそれ以上のグループは、保護層で保護される一方で、一又はそれ以上の他のグループは、本明細書で説明したように、水素含有ガスでのトリートメントに露出されてもよい。したがって、露出したグループは、保護され、保護層は、一又はそれ以上の他のグループから除去され、これらの他のグループは、水素含有ガスでトリートメントされることができる。このプロセスは、全てのグループが、所望の水素含有ガスに露出されるまで繰り返されてもよい。各グループに対する露出パラメータは、変化するため、異なる閾値電圧を異なるグループのための実現することが可能となる。

【0048】

いくつかの他の実施では、異なるグループのための電極スタックは、別々に形成される。各スタックの形成時に水素含有ガスへの露出に対する異なる条件を提供することにより、異なる閾値電圧は提供される。

【0049】

当業者にとっては明白となるように、様々な省略、追加および修正を、本発明の範囲から逸脱することなく、上記の方法に対して行うことができる。すべてのかかる修正、および変更が、添付の特許請求の範囲によって定義されるように、本発明の範囲内に含まれることを意図する。

【技術分野】

【0001】

本開示は、半導体処理の分野に関し、より詳細には、トランジスタのゲートスタックにおける金属ゲート電極のような導体構造の堆積に関する。

【背景技術】

【0002】

演算能力の増加及び集積回路サイズの低減の継続的な要求により、集積回路を形成する電子デバイスのサイズを低減する継続的な要求が存在する。例えば、トランジスタのサイズは、例えば集積回路のトランジスタ密度を増加させ、演算能力を増加させるために、低減されることが継続されている。トランジスタのサイズが小さくなるため、トランジスタのゲート電極からトランジスタのチャネル領域を別にしたゲート誘電体層のような、これらの構成要素も同様である。ゲート誘電体層における望まれない電流リークを防ぐために、より薄い誘電体層は、通常、高い誘電率(high−k)材料を使用することを要求する。しかし、high−k材料がいくつかの従来のシリコンベースのゲート電極材料に用いられた場合、high−k材料を有するトランジスタは、低いパフォーマンス特性となってしまう。したがって、トランジスタのような電子デバイスのhigh−kゲート誘電体材料での使用に適切である、導体ゲート電極のような導電材料に対する継続的な需要が存在する。

【発明の概要】

【0003】

いくつかの実施形態によれば、半導体処理の方法(process)が提供される。本方法は、基板にゲート電極を形成する工程を含む。ゲート電極を形成する工程は、ゲート誘電体を有する基板を反応チャンバ内に提供する工程を含む。遷移金属化合物を含む第1の層は、堆積中に、基板をプラズマ又はプラズマ発生(plasma−generated)ラジカルに露出せずに、ゲート誘電体に堆積される。第1の層は、その後、水素含有ガスに露出される。次いで、遷移金属化合物を含む第2の層は、堆積される。

【0004】

他のいくつかの実施形態によれば、半導体処理の方法が提供される。この方法は、金属電極を堆積する工程を含む。金属電極を堆積する工程は、ゲート誘電体に金属材料を堆積する工程を含む。金属材料を堆積するための前駆体は、プラズマ活性化されていない。金属材料は、励起された水素含有種に露出される。次いで、金属材料を励起された水素含有種に露出した後に、さらなる金属は、金属材料に堆積される。

【図面の簡単な説明】

【0005】

本発明の制限されず、包括的でない実施形態は、以下の図面を参照して説明され、全体にわたって同じ参照番号は、同じ部材に示される。

【図1a】図1aは、金属ゲート電極を形成する各種処理フローの例を示す図である。

【図1b】図1bは、金属ゲート電極を形成する各種処理フローの例を示す図である。

【図1c】図1cは、金属ゲート電極を形成する各種処理フローの例を示す図である。

【図2】図2は、導電材料を堆積する各種処理シーケンスの例を示す図である。

【図3】図3は、図2に示すシーケンスの結果の図解の例を示す図である。

【図4】図4は、導電材料を堆積するさらなる処理シーケンスの例を示す図である。

【図5】図5は、図4に示すシーケンスの結果の図解の例を示す図である。

【図6】図6は、図2及び4の処理シーケンスのいくつかの状態を示す図である。

【図7】図7は、励起された水素含有種を発生するピーク間(peak−to−peak)電圧が変化するときの仕事関数の変化についての図解の例を示す図である。

【図8】図8は、励起された水素含有種を発生するピーク間電圧が変化すると共に、励起された水素含有種の各パルスを発生するために印加される電力の持続期間が変化するときの有効仕事関数の変化についての図解の例を示す図である。

【図9】図9A−9Dは、ゲート電極スタックの断面斜視図の例を示す図である。

【図10】図10は、ゲート電極スタックの断面斜視図の例を示す図である。

【図11】図11は、ゲート電極スタックの断面斜視図の例を示す図である。

【図12】図12は、ゲート電極スタックの断面斜視図の例を示す図である。

【発明を実施するための形態】

【0006】

いくつかの実施形態によれば、導電材料の第1の層を堆積し、第1の層を(ガス状の水素含有種を含む)水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、導体構造が形成される。いくつかの実施形態では、導体構造は、誘電体層に形成される。例えば、導体構造は、トランジスタの一部として、high−kゲート誘電体のようなゲート誘電体に形成されたゲート電極であってもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカル(すなわち、プラズマにより発生されたラジカル)に露出されないノン−プラズマ又はノン−ラジカル処理を用いて堆積されてもよい。第1の層は、その後、水素含有種に露出される。いくつかの実施形態では、水素含有種は、水素含有プラズマの一部である励起された水素含有種であってもよい。いくつかの実施形態では、水素含有種は、遠隔プラズマ発生器で発生され、その後、第1の層を含む反応チャンバへ流される水素含有ラジカルを含む。

【0007】

有利には、導電材料がトランジスタの金属ゲートを形成するために用いられた場合、ゲートスタックのゲート電極の仕事関数は、約4.85eV以上、又は約5eV以上であってもよい。いくつかの実施形態では、第1の層の厚さは、約5nm未満、約4nm未満、約3nm未満、又は約1−3nm未満である。第1の層は、第1の層を形成する材料の単分子層よりも薄いことが好ましい。

【0008】

いくつかの実施形態では、ノン−プラズマ処理により第1の層を形成することに加えて、第2の層もまた、基板がプラズマ又はプラズマ発生ラジカルに露出されないノン−プラズマ処理により形成されてもよい。いくつかの実施形態では、第2の層は、プラズマ又はラジカルへの露出により形成されてもよい。

【0009】

導体構造を形成する導体材料は、遷移金属化合物のような金属材料であってもよい。遷移金属は、制限されないが、チタン、タンタル、ニオブ、モリブデン、ハフニウム、ジルコニウム及びタングステンのような高融点金属であってもよい。いくつかの実施形態では、導体材料は、金属を窒化することにより形成された窒化物であってもよい。いくつかの実施形態では、導電材料が炭化金属又は窒炭化金属になりうるように、炭素のような他の元素は、導電材料に組み込まれてもよい。このような材料の制限されない例は、窒化タンタル、炭化タンタル、窒炭化タンタル、窒化チタニウム、炭化チタニウム、窒炭化チタニウムを含む。材料の制限されない他の例は、窒化ニオブ、炭化ニオブ、窒炭化ニオブ、窒化モリブデン、炭化モリブデン、窒炭化モリブデン、窒化ハフニウム、窒化ジルコニウム、タングステン、窒化タングステンを含む。

【0010】

第1の層は、また、第2の層の堆積前に、酸素のような各種の他の化学種に露出されてもよい。いくつかの実施形態では、導電材料の一又はそれ以上の層は、第1の層と第2の層との間に堆積されてもよい。

【0011】

いくつかの実施形態では、金属ゲート又は金属電極は、実質的に同一な化合物である第1及び第2の層で形成されてもよく、第1及び第2の層は、金属材料の均質な層でありうる金属材料の単層を形成する。いくつかの実施形態では、第1及び第2の層は、異なる遷移金属化合物を含む異なる金属材料で形成されてもよい。異なる遷移金属化合物は、異なる遷移金属を含んでもよく、及び/又は層と層との間で異なる他の元素を含んでもよい。いくつかの実施形態では、第1及び第2の層の一方又は双方は、異なる材料のサブレイヤーで形成されるラミネート層であってもよい。例えば、ラミネート層は、異なる遷移金属化合物のサブレイヤーで形成されてもよい。いくつかの実施形態では、第1及び第2の層は、同一の又は異なるラミネート層で形成されてもよい。

【0012】

high−K(HiK)金属ゲート(MG)相補型金属酸化半導体(CMOS)技術は、高容量な集積回路の製造において、従来の酸窒化ポリシリコン(poly−SiON)トランジスタデバイスに対する代替技術を提供することがわかる。High−k誘電体は、トランジスタのゲート誘電体を形成するために用いられてもよく、本明細書で記述した遷移金属化合物のような金属材料は、トランジスタのゲート電極を形成するために用いられてもよい。これらのhigh−k誘電体及びゲート電極は、いわゆる“ゲート−ファースト”フロー及び“ゲート−ラスト”フローの2つを含む各種のHiK−MG集積フローを用いてトランジスタデバイスに組み込まれてもよい。後者のアプローチは、Replaceable Metal Gate (RMG)とも呼ばれ、順に“HiK−ファースト”及び“HiK−ラスト”という2つのサブアプローチを有する。

【0013】

各種のHiK−MG処理フローは、図1a−1cに図示される。全てのこれらのHiK−MG処理フローは、HiK誘電体層の上部に堆積される共通の金属電極を有する。以下に詳細を記載するように、フロー間で異なる点の一つは、High Thermal Budgetステップ(基板が段階的な温度に露出される処理ステップ)の行われるタイミングである。高温アニール、典型的には、Rapid Thermal Anneal(RTA)は、ソース及びドレイン領域を形成するために行われる。“ゲート−ファースト”処理フローでは、先に金属電極が堆積され、その後、高温アニール工程に露出されるが、“ゲート−ラスト”フローでは、金属電極は、高温アニール工程の後に、堆積される。二つの処理フロー間の他の異なる点は、“ゲート−ラスト”フローでは、高い金属ゲートコンフォーマリティに対する要求が相対的に高く、そのため、このフローでは、金属電極層は、高いアスペクト比を有する相対的に狭いトレンチに堆積される(図1b)。

【0014】

図1a−1cは、ここで、より詳細に説明される。各処理フローの各図示された構造は、処理フローの各種の時間におけるトランジスタの断面図を示し、左から右へ時間が進む。最も左の構造は、最先に形成された図示された構造であり、最も右の構造は、最後に形成された図示された構造である。

【0015】

図1aは、“ゲートファースト”処理フローを図示している。一番目に図示された位置では、基板10が提供され、二酸化シリコンインターフェース層から形成された覆っているゲートスタック20と、high−k誘電体層30と、仕事関数をチューニングする誘電体キャップ40と、金属電極層50と、ポリシリコン層60と、を有する。二番目に図示された位置では、側壁スペーサ70及びソース/ドレイン領域80は、次いで形成される。ソース/ドレイン領域の活性化及び形成のためのRapid Thermal Annealは、符号90により示される。

【0016】

図1bは、high−k誘電体が初めに形成される“ゲート−ラスト”処理フローを図示する。図1bの図示された一番目の位置では、基板10は、二酸化シリコンインターフェース層から形成された覆っているゲートスタック20と、high−k誘電体層30と、エッチストップ層52と、ポリシリコン層62と、が形成される。図1bの図示された二番目の位置では、側壁スペーサ70及びソース/ドレイン領域80は、次いで形成される。ソース/ドレイン領域は、Rapid Thermal Annealにより形成され、符号90により示される。図1bの図示された三番目の位置では、ポリシリコン層62が除去され、その跡にトレンチ64が残る図1bの図示された四番目の位置では、金属電極54は、トレンチに堆積され、金属充填56は、残りのトレンチの容積を充填するために堆積される。

【0017】

図1cは、high−k誘電体が最後に形成される“ゲート−ラスト”処理フローを図示する。図1cの図示された一番目の位置では、基板10は、二酸化シリコンインターフェース層から形成された覆っているゲートスタック20と、ポリシリコン層66とが形成される。図1cの図示された二番目の位置では、側壁スペーサ70及びソース/ドレイン領域80が形成される。ソース/ドレイン領域は、Rapid Thermal Annealにより形成され、符号90により示される。図1cの図示された三番目の位置では、ポリシリコン層66が除去され、トレンチ68が残る。図1cの図示された四番目の位置では、high−k誘電体層30は、トレンチに堆積され、金属電極層54は、high−k誘電体層30上にわたって堆積され、金属充填56は、残りのトレンチを充填するように堆積される。

【0018】

図1a−1cを参照すると、二酸化シリコンインターフェース層20は、酸素種を有する既存の堆積及び/又は反応を含む各種の処理により形成されてもよい。例えば、二酸化シリコンインターフェース層20は、使用される処理フロー及び二酸化シリコンインターフェース層の所望の特性に応じた、化学的な酸化、CVD酸化、熱酸化であってもよい。

【0019】

CMOS動作のためのターゲット閾値電圧(Vt)を達成するために、適切な有効仕事関数(Effective Work Functions (EWF))が要求される。例えば、平面ハイパフォーマンス(High Performance(HP))CMOSロジックデバイスに対しては、NMOS及びPMOS EWFターゲットは、それぞれ4.2eV及び5.1eVであってもよい。このような仕事関数値は、しばしば、Siの伝導帯及び価電子帯のエッジそれぞれに近い“バンド−エッジ(band−edge)”と呼ばれる。“ゲート−ラスト”フローを用いて形成されるトランジスタデバイスのコンフォーマリティ要求に合致する特定の金属材料である、単一のPMOSバンド−エッジ金属材料の例は知られていない。

【0020】

例としては、窒化チタン(TiN)は、HiK−MGデバイス用の金属材料に通常用いられる。TiCl4−NH3に基づくALD TiN(Ti前駆体としてTiCl4を用い、N前駆体としてNH3を用い、ALD処理を用いて堆積されたTiN)は、単一のウェーハ又はバッチ型リアクタにおけるRMGデバイスの狭トレンチにコンフォーマリィに堆積されてもよい。しかし、堆積方法及び/又は処理状態に関わらず、TiNの典型的なEWF値4.7−4.75eVは、low−Vt(HP)デバイス用に所望される5.1eVを下回ることがわかっている。Hinkle et al., ECS Transactions, 35(2) 285−295 (2011)は、N2中に、残留する又は10%O2にを有する酸素含有環境でアニールを行い、Wの上部金属層(クラッド層)を堆積することにより、TiN膜のEWFが約5eVの値で増加しうることを実証している。10%濃度のO2を有する大気を用いることによるアグレッシブなアニール及び/又は450℃又は500℃のアニール温度を用いることは、EWFを増加させることが報告されている。しかし、TiNが酸化に影響を受けやすいため、450℃でのN2に10%のO2でのアグレッシブなアニールは、TiN層全体を酸化してしまい、これは、望まれていない。

【0021】

有利には、本明細書に記載されるいくつかの実施形態は、450℃以上の温度での明白な酸化状態に金属層全体を露出することなく、金属電極又は金属電極の金属下部層を用いて、ゲートスタックのEWFのチューニングを可能にする。いくつかの実施形態では、このようなチューニングは、約450℃以下、約420℃以下、又は約400℃以下の温度で行われうる。

【0022】

いくつかの実施形態では、金属材料(例えば、遷移金属化合物)の第1の層は、堆積中に、プラズマ又はラジカルのような励起種に基板を露出することなく基板に堆積される。第1の層は、いくつかの実施形態では、約5nm未満、約4nm未満、約3nm未満、約1−3nm未満の厚さである。いくつかの実施形態では、厚さ約2nmである。その後、この第1の層は、処理される。He又はArのような不活性ガスと混合するか否かにかかわらず、この処理は、薄い金属層を、水素含有ガス、より好ましくは、水素含有ラジカル又は水素含有プラズマのような励起された水素含有種に露出することを含む。励起種の露出は、所望の温度及び所望時間でのプラズマ電力で行われてもよい。いくつかの実施形態では、プラズマ電力は、4秒以下のパルスで印加される。励起種は、基板として同一反応チャンバ内に形成されるプラズマの一つであってもよく、遠隔で発生され反応チャンバへ流入されてもよい。水素含有ガスは、いくつかの実施形態では、例えば、水素又はアンモニアであってもよい。続いて、金属材料(例えば、第2の遷移金属化合物)の第2の層は、金属材料の第1の層に堆積される。これらの3つのステップは、同一又は異なる温度で、同一又は異なるリアクタで行われてもよい。

【0023】

励起種の露出の前及び/又は後に、酸素含有ガスへの基板の露出が行われてもよく、トリートメントが酸素含有ガスへの露出なしで行われてもよい。若しくは、酸素含有ガスへの露出は、所望の状態及び所望の期間下での反応チャンバ内において、制御された手法で行われてもよい。酸素含有ガスは、いくつかの実施形態では、酸素ガス及び窒素ガスの混合物であってもよい。いくつかの実施形態では、酸素含有ガスは、ある量の水蒸気を含んでもよい。酸素含有ガスへの露出は、金属材料を堆積するために用いる堆積チャンバにおいて、イン−サイチュで行われてもよい。これに代えて、基板は、反応チャンバからの基板の搬出及びクリーンルームエアへの露出(いわゆる“エアブレイク”工程により、酸素含有ガスへ露出されてもよい。

【0024】

金属材料の第1の層は、物理気相堆積(PVD)、化学気相堆積(CVD)、パルス化CVD又は原子層堆積(ALD)により堆積されてもよい。金属材料の第2の層は、プラズマエンハンスドCVDやプラズマエンハンスドALDを含む、PVD、CVD、パルス化CVD、又はALDにより堆積されてもよい。いくつかの実施形態では、金属層は、ALDにより堆積され、高いステップカバレージを達成する。前駆体は、交互に連続的に、一時的に分離されたパルスで反応チャンバへ流入されうる。いくつかの実施形態では、化合物の約単分子層又はそれ未満のものは、各前駆体の1つのパルスシーケンスで、堆積サイクル単位で形成される。例えば、TiNは、一時的に分離されたパルスでの前駆体としてのTiCl4及びNH3を用いて形成されうる。本明細書で述べたように、いくつかの実施形態では、金属材料は、窒化タンタル、炭化タンタル、窒炭化タンタル、炭化チタン、窒炭化チタン、窒化ニオブ、炭化ニオブ、窒炭化ニオブ、窒化モリブデン、炭化モリブデン、窒炭化モリブデン、窒化ハフニウム、窒化ジルコニウム、タングステン、及び窒化タングステンを含みうる。いくつかの実施形態では、第1及び第2の層は、単一材料で形成されてもよい。いくつかの実施形態では、第1及び第2の層の一方又は双方は、複数のサブレイヤーで形成されたラミネート層であってもよい。

【0025】

例としては、各種金属の堆積が調査され、これらの層を形成する堆積シーケンスは、図2及び4に詳述される。図2及び4に示された処理の後、全てのサンプルは、形成ガス(N2中に4%のH2)で420℃、30分のアニールを受けた。還元環境での堆積及び処理は、ASM International’s EmerALD(登録商標)のALD用シングルウェーハリアクタシステムで行われ、これは、また、プラズマが反応チャンバ内で発生されうるプラズマオプションを提供する。EmerALD(登録商標) シングル ウェーハ リアクタシステムは、ASM International N.V., Almere, The Netherlands から入手可能である。図2、4及び6は、TiN堆積のための各種詳細を提供する。他のいくつかの実施形態では、窒化タンタル、炭化タンタル、窒炭化タンタル、炭化チタン、窒炭化チタン、窒化ニオブ、炭化ニオブ、窒炭化ニオブ、窒化モリブデン、炭化モリブデン、窒炭化モリブデン、窒化ハフニウム、窒化ジルコニウム、タングステン、及び窒化タングステンのような金属材料は、同様の結果を達成するために同様の工程ステップ及び条件を用いてTiNと結合して、又はそれに代えて形成される。

【0026】

本明細書に開示された実施形態に係る堆積は、EWFで野増加を提供することがわかる。有効仕事関数(EWF)値及び等価酸化厚さ(equivalent oxide thickness、EOT)は、C−V測定及びMIS構造から抽出される。金属電極は、シリコン基板上の2nmのHfO2層の上部及び1nmの界面SiO2に堆積される。図2を参照すると、全てのTiN堆積は、390℃で行われ、エアブレイクは、第1のTiN層堆積と膜処理工程との間、及び膜処理工程と第2のTiN層堆積工程との間の両方で適用される。単一の10nm厚さのALD TiN層は、通常、約4.7−4.75eV(1F)の仕事関数を与える。しかし、本明細書に開示された実施形態に係る堆積は、より大きなEWFをもたらす。例えば、2nmのALD TiN層、それに続くエアブレイク、H2/Arプラズマトリートメント(2秒ごとに32パルス)、第2のエアブレイク及び10nmのALD TiN層は、4.96eV(1F)の格段に大きなEWFを示す。

【0027】

EWFの増加は、励起された水素種への露出にあると考えられうる。図3を参照すると、下部及び上部ALD TiN層間での32サイクルのプラズマ−エンハンスドALD(PEALD)による薄いTaCN層の成長によっても、4.98eV(1C)又は5.04eV(1B)のより大きなEWF値が達成されることがわかる。サーマルALD TaCNによるPEALD TaCN層の置換は、低い仕事関数をもたらし、単一の10nmのALD TiN層(1D及び1E)の仕事関数と近い。これらの結果は、PEALD TaCNで得られたより大きなEWFが、下部(第1の)TiN層に対するPEALD TaCN 堆積時のAr/H2含有プラズマ活性への露出にあると考えられうる。また、2から3又は4へのプラズマパルスの増加した期間が、増加した等価酸化厚さ(equivalent oxide thickness、EOT)での増加EWFを導くことがわかる。最後に、2nmの第1のTiN層と薄い第2のTiN層との間のみのエアブレイクの適用は、プラズマトリートメント工程(1G)を適用することがなく、EWFの増加を招かないことが観察される。

【0028】

また、上述したTiN層用のプロセスと同様のプロセスを用いて、TiN/TaCNの二つの層及びTaC層の仕事関数は、増加しうることがわかる。TiN/TaCNの二つの層及びTaC層は、プラズマにより発生されたラジカル無しの熱活性プロセス、及び水素含有ガスでの層のトリートメントにより堆積され、このトリートメントは、水素ラジカル又は水素含有プラズマへの層の露出を含む。仕事関数は、また、熱活性水素含有ガスへの層の露出により増加されうる。

【0029】

他の実験では、その結果が図4に示され、以下のパラメータの影響が、また、調査された。

・エアブレイクの回数及びそれらの位置(場所)の効果:

Ar/H2プラズマトリートメントの前後;

プラズマトリートメントの前;

プラズマトリートメントの後;

エアブレイクなし;

・TiN堆積温度(325度 対 390℃)の効果、及び

・Ar/H2プラズマトリートメント(325度 対 390℃)時のウェーハ温度の効果。

Ar/H2プラズマは、2秒ごとの32パルスでのパルスワイズ(pulse−wise)で適用される。

【0030】

図5で観察されるように、TiN膜の325℃の堆積温度は、体系的に、より大きなEOT値をもたらす。有益なEWF/EOTトレードオフは、以下のシーケンス(図4の2C)で達成されうる。

第1及び第2の層の双方は、390℃で成長した;

Ar/H2プラズマトリートメントは、390℃で行われた;及び

二つのエアブレイク(Ar/H2プラズマトリートメントの前後)。

【0031】

同様の条件で処理されたサンプルの図2と図4との結果(図2の1F 対 図4の2B)には差異が存在することがわかる。これらの変位は、図2と図4の実験の時間間隔によるものである。また、図4の実験のエアブレイク(1−2日)は、図2の実験のエアブレイク(1−2週間)よりも短い。それにも関わらず、各セットの実験では、Ar/H2プラズマへの露出を有する全てのシーケンスは、このような露出を有さないセット(図2の1A、図4の2A及び2E)よりEWFの増加を提供する。

【0032】

図2及び4で説明された実験で用いられた各種の追加プロセス条件は、図6に総括される。TBTDETは、第三級ブチルイミド トリス(ジメチルアミノ)タンタル、Ta[N(C2H5)2]3[=NC(CH3)3]であることがわかる。異なる温度及びわずかな(又は全く無い)エアブレイクにおいて、所望の大きなEWFは、各種トリートメントパラメータを調整することにより達成されてもよいと考えられる。プロセスパラメータのいくつかの例は、1)下部TiN層厚さの変更、2)熱のみのトリートメント(プラズマ無し)を含む、プラズマ電力及び時間の変更、3)リアクタ内のO2,N2及びH2量の変更を含むように変更されうるが、これに限定されない。上述した実験では、EWF/EOT近似曲線が観察され、高いEWFが高いEOT値で観察される。一方、いくつかの用途では、低いEOT値での高いEWFを達成することが望まれる。上記のパラメータのバリエーションは、高いEWF及び低いEOT間での有利なトレードオフを可能にしうる。

【0033】

理論による制限無しでは、エアブレイクと水素含有ガスへの露出との組み合わせは、EWFにも影響しうると考えられる。例えば、エアブレイクの後に、Ar/H2プラズマトリートメント、別のエアブレイクが続き、グレインサイズ/モフォロジー及び/又は金属含有スタックのO及びN量が変化し、その結果、スタックのEWF(例えば、TiNスタック)は増加しうる。さらに、エアブレイクにより、第1の金属層を水素含有ガス又は水素含有プラズマに露出する工程時に、酸素又は水素含有不純物(例えば、O2又はH2O)が存在するようになる。これらの不純物は、所望のスタック特性を達成する役割を果たしてもよい。

【0034】

例えば、理論による制限を求めること無しでは、EWFのいくつかの増加は、第1の金属層とそれに続く金属層との間の界面でのH−Oダイポールの形成の結果であってもよいと考えられる。低い濃度の酸素が提供されてもよく、低い濃度の酸素は、リアクタ及び/又は第1の金属層の残りの酸素の存在から生じうる、又は、水素ラジカル又はプラズマトリートメントの前、最中、又は後の金属層の酸素への意図的な露出から生じうる。酸素は、水素トリートメントの前及び/又は後のエアブレイクから生じうる。好ましくは、酸素濃度は、十分に低いレベルで維持されて、金属層の参加が制限され、これは、所望されないEOTの増加をもたらしうる。

【0035】

図7では、プラズマトリートメント時のVpp(ピーク間電圧、peak−to−peak Voltage)は、より決定的な要因であり、EWFとの相関よりもプラズマ電力のほうが好ましい、つまり、より高いEWFがより高いVppのために得られる、ことが示される。さらなる結果は、390℃で堆積されたTiNについて図8に示される。2nm厚さの第1のTiN膜は堆積され、その後、32パルスのプラズマ露出は、図8に示すようなVpp及びパルス期間で適用され、その後、10nm厚さの第2のTiN膜は堆積される。エアブレイクは、水素プラズマトリートメントの前後に適用される。水素プラズマトリートメントは、0.5Torrでの水素/Ar混合物が適用される。図8からは、高いVpp及び/又は長いパルス期間は高いEWFをもたらすことが観察されうる。いくつかの実施形態では、Vppは、約110V以上、約130V以上、約160V以上、又は約200V以上でありうる。いくつかの実施形態では、励起された水素種を露出する期間は、約2秒以上、約4秒以上、又は約2−4秒でありうる。リファレンスとして、プラズマに露出せずに形成されたTiNは、上述したように、約4.7又は4.73の低いEWFを有する。

【0036】

図1b−1cを再度参照すると、いくつかの実施形態では、第1及び第2の層の堆積により形成された金属材料は、電極54として用いられてもよいことがわかる。よって、いくつかの実施形態では、第1及び第2の層の堆積は、誘電体材料で形成されたスペーサにより規定される狭トレンチで行われてもよく、金属は、続いて、ゲート電極54により規定される開口に堆積されてもよい。

【0037】

CMOSプロセスでの金属電極スタックの堆積のいくつかの例は、以下の図9a−12を参照して提供される。同一のハッチング及び網掛けは、同一の層を示す。プロセスフローは、高い仕事関数を有するPMOS金属電極及び低い仕事関数を有するNMOS金属電極の堆積を含む。以下で説明する金属は、例示であり、他の金属も用いることができる。例えば、各種の他の金属は、本明細書で説明したように、TiNの代わりに用いられてもよい。

【0038】

(実施例1)

実施例1は、図9a−9cを参照して説明する。ゲート誘電体は、HfO2を含んでもよい。PMOS金属電極は、下部から上部へ向かって、2nmTiN層、1nmTaCN層、4nmTiN層、5nmTiAl層、及び充填金属の層の堆積により形成される。NMOS金属電極は、下部から上部へ向かって、2nmTiN層、1nmTaCN層、5nmTiAl層、及び充填金属の層の堆積により形成される。TiAlは、NMOSについての低い仕事関数を提供する。PMOSスタックでは、しかし、TiAl層は、HfO2/金属電極界面から離れており、HfO2/金属電極界面での仕事関数の影響は制限されている。PMOSスタックでのAr/H*でのトリートメント(H*はプラズマでの水素ラジカルのような励起された水素含有種を示す)は、プラズマエンハンスド堆積プロセスがTaCN層(図9c)又はTaCN層堆積の後に(図9d)の形成に用いられた場合のTaCN層堆積時に、TaCN層堆積の前に適用されてもよい。

【0039】

図9aのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.水素含有ガスでの第1のTiN層のトリートメント;

3.サーマルプロセスによるTaCN層の堆積及び第2のTiN層の堆積;

4.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;及び

5.TiAl層の堆積及び金属を充填。

【0040】

図9bのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.NMOSデバイスの保護層(例えば、フォトレジスト又はSiO2層)を形成するためのリソグラフィ及びエッチング;

3.水素含有ガスでのTiN層のトリートメント;

4.保護層の除去;

5.サーマルプロセスによるTaCN層の堆積及び第2のTiN層の堆積;

6.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;及び

7.TiAl層の堆積及び金属を充填。

【0041】

図9cのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.水素含有プラズマエンハンスドプロセスによるTaCN層の堆積;

3.第2のTiN層の堆積;

4.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;及び

5.TiAl層の堆積及び金属を充填。

【0042】

図9dのスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層及びTaCN層の堆積;

2.NMOSデバイスの保護層(例えば、フォトレジスト又はSiO2層)を形成するためのリソグラフィ及びエッチング;

3.水素含有ガスでのトリートメント;

4.保護層の除去;

5.第2のTiN層の堆積;

6.NMOSデバイスから第2のTiN層をTaCN層のエッチストップと共に除去するためのリソグラフィ及びエッチング;

7.(残りのTaCN層の厚さを削減するための追加エッチング);

8.TiAl層(nEWF)の堆積及び金属層の前に薄いバリア金属層(例えば、TiN層)を堆積し、追加で金属を充填する。

【0043】

(実施例2)

実施例2は、図10を参照して説明する。ゲート誘電体層は、HfO2を含んでもよい。PMOS金属電極は、2nmTiN層の堆積、水素含有ガスによるTiN層のトリートメント、4nmTiN層の堆積、及び充填金属の堆積により形成される。NMOS金属電極は、2nmの第1のTiN層、5nmのTiAl層、4nmのTiN層、及び充填金属層を含む。

図10のスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層及びTiAl層の堆積;

2.NMOSデバイスの保護層(例えば、フォトレジスト又はSiO2層)を形成するためのリソグラフィ及びエッチング;

3.PMOSデバイスからTiAl層をTiN層のエッチストップと共に除去;

4.水素含有ガスでのトリートメント;

5.保護層の除去;及び

6.第2のTiN層の堆積及び金属を充填。

【0044】

(実施例3)

実施例3は、図11を参照して説明する。PMOS電極は、2nmのTiN層の堆積、水素含有ガスによるTiN層のトリートメント、5nmTaC層の堆積、及び充填金属の堆積により形成される。NMOSスタックは、5nmのTaC層及び充填金属の層を含んでもよい。TaC層は、また、NMOSデバイスにとって好ましい、低い仕事関数を提供し、TiAlに相当する。しかし、TaCはALDにより堆積されうるのに対して、TiAlは通常PVDプロセスにより堆積される点で有利である。

図11のスタックは、以下のプロセスフローを用いて製造されうる。

1.第1のTiN層の堆積;

2.水素含有ガスでのトリートメント;

3.NMOSデバイスからTiNをHfO2のエッチストップと共に除去するためのリソグラフィ及びエッチング(追加でSiO2ハードマスク);

4.(SiO2ハードマスクを適用可能な場合には、追加でハードマスクの除去);

5.NMOSデバイスのEWFを設定するためにTaC層を堆積;及び

6.充填金属を堆積。

【0045】

(実施例4)

実施例4は、図12を参照して説明する。PMOS金属電極は、5nmのTaC層の堆積、水素含有ガスでのトリートメント、及び充填金属の堆積により形成される。NMOS金属電極は、5nmのTaC層及び充填金属を含み、NMOS金属電極での唯一の差異は、水素含有ガスでのトリートメントを行わないことである。水素含有ガスでのトリートメントのみで、TaC層の仕事関数は、十分に変化し、PMOS及びNMOSデバイスのための適切な仕事関数を達成しうることを意図する。

図12のスタックは、以下のプロセスフローを用いて製造されうる。

1.(nEWFを有する)TaC層の堆積;

2.NMOSデバイスを保護層(例えば、フォトレジスト又はSiO2層)と共にマスクするためのリソグラフィ及びエッチング;

3.PMOSデバイスのためのEWFを調整するために水素含有ガスでのトリートメント;

4.NMOSデバイスから保護層の除去;及び

5.充填金属を堆積。

【0046】

図1から図4の全ての実施例に対して、図9a−12に示すように、例えば、2nmのTiN層のような薄いバリア層は、充填金属層の堆積前に追加で堆積されてもよい。理論により制限されず、このようなバリア層は、充填金属からの不純物の不拡散(in−diffusion)に対する仕事関数が変化しやすい(sensitive)層を保護しうることが考えられる。

【0047】

本明細書に記載されたプロセスは、PMOS及びNMOSデバイスの有効仕事関数を同時に調整するために用いられてもよい。また、異なる仕事関数を有する異なるデバイスのグループが形成されてもよい。異なる仕事関数は、トランジスタデバイスのための異なる閾値電圧を提供しうることがわかる。したがって、いくつかの実施形態では、高速及び高電力消費をもたらす低いVt(Vt=閾値電圧)を有するデバイスのグループ、中程度の速度及び中程度の電力消費をもたらす中程度のVtを有するデバイスのグループ、及び低速及び低電力消費をもたらす高いVtを有するデバイスのグループを形成することが可能であり、全てのグループはプロセスフローにより同一基板に形成される。異なるグループは、本明細書で説明したプロセスに係る異なる水素トリートメントに露出されてもよく、又は本明細書で説明したプロセスに係る異なるスタックは、各グループのために形成されてもよい。例えば、各種グループのための電極層は、同時に堆積されてもよく、一又はそれ以上のグループは、保護層で保護される一方で、一又はそれ以上の他のグループは、本明細書で説明したように、水素含有ガスでのトリートメントに露出されてもよい。したがって、露出したグループは、保護され、保護層は、一又はそれ以上の他のグループから除去され、これらの他のグループは、水素含有ガスでトリートメントされることができる。このプロセスは、全てのグループが、所望の水素含有ガスに露出されるまで繰り返されてもよい。各グループに対する露出パラメータは、変化するため、異なる閾値電圧を異なるグループのための実現することが可能となる。

【0048】

いくつかの他の実施では、異なるグループのための電極スタックは、別々に形成される。各スタックの形成時に水素含有ガスへの露出に対する異なる条件を提供することにより、異なる閾値電圧は提供される。

【0049】

当業者にとっては明白となるように、様々な省略、追加および修正を、本発明の範囲から逸脱することなく、上記の方法に対して行うことができる。すべてのかかる修正、および変更が、添付の特許請求の範囲によって定義されるように、本発明の範囲内に含まれることを意図する。

【特許請求の範囲】

【請求項1】

半導体処理方法であって、基板にゲート電極を形成する工程を含み、

前記基板にゲート電極を形成する工程は、

ゲート誘電体を含む基板を反応チャンバ内に提供する工程と、

前記基板をプラズマ又はプラズマ発生ラジカルに露出せずに、前記ゲート誘電体に遷移金属化合物を含む第1の層を堆積する工程と、

前記第1の層を水素含有ガスに露出する工程と、

その後、遷移金属化合物を含む第2の層を堆積する工程と、を含む、半導体処理方法。

【請求項2】

前記第1の層の厚さは、約5nm以下である請求項1に記載の方法。

【請求項3】

前記ゲート電極及び前記ゲート誘電体は、ゲートスタックを構成し、前記ゲートスタックの前記ゲート電極の仕事関数は、約4.85eV以上である請求項1に記載の方法。

【請求項4】

前記仕事関数は、約5.0eV以上である請求項3に記載の方法。

【請求項5】

前記水素含有ガスは、励起された水素含有種を含む請求項1に記載の方法。

【請求項6】

前記励起された水素含有種は、水素ラジカルを含む請求項5に記載の方法。

【請求項7】

前記励起された水素含有種は、水素含有プラズマの一つである請求項5に記載の方法。

【請求項8】

前記水素含有プラズマを形成するプラズマ電力は、約175W以上である請求項7に記載の方法。

【請求項9】

前記励起された水素含有種を発生するプラズマ電力は、約2秒以上のパルスである請求項7に記載の方法。

【請求項10】

前記励起された水素含有種を発生するピーク間電圧は、約130V以上である請求項7に記載の方法。

【請求項11】

前記ピーク間電圧は、約160V以上である請求項10に記載の方法。

【請求項12】

前記第1の層を水素含有ガスに露出する工程は、プラズマ‐エンハンスド原子層堆積により膜を堆積する工程を含む請求項7に記載の方法。

【請求項13】

プラズマ‐エンハンスド原子層堆積により堆積される前記膜は、タンタル含有膜である請求項12に記載の方法。

【請求項14】

前記第1の層は、原子層堆積により堆積される請求項1に記載の方法。

【請求項15】

前記第2の層は、プラズマ‐エンハンスド原子層堆積により堆積される請求項14に記載の方法。

【請求項16】

前記第2の層は、原子層堆積により堆積される請求項1に記載の方法。

【請求項17】

前記第1の層を堆積する工程と前記第1の層を露出する工程との間、又は前記第1の層を露出する工程と前記第2の層を堆積する工程との間に、前記基板を酸素含有ガスに露出する工程をさらに含む請求項1に記載の方法。

【請求項18】

前記基板を酸素含有ガスに露出する工程は、前記基板を前記反応チャンバから搬出し、前記基板をクリーンルームエアに露出する工程を含む請求項17に記載の方法。

【請求項19】

前記第1の層を堆積する工程と前記第1の層を露出する工程との間、及び前記第1の層を露出する工程と前記第2の層を堆積する工程との間に、前記基板を酸素含有ガスに露出する工程をさらに含む請求項1に記載の方法。

【請求項20】

前記ゲート電極を形成する工程は、前記第1及び第2の層を誘電体材料により規定されるトレンチに堆積する工程を含む請求項1に記載の方法。

【請求項21】

前記ゲート電極を形成する工程は、PMOSトランジスタの前記ゲート電極を形成する工程を含む請求項20に記載の方法。

【請求項22】

前記ゲート電極を形成する工程は、前記トレンチの開口を規定し、前記開口を金属で充填する工程をさらに含む請求項20に記載の方法。

【請求項23】

前記基板は、前記第1の層を堆積する工程と前記開口を充填する工程との間で約420℃未満の温度で維持される請求項22に記載の方法。

【請求項24】

前記第1の層及び前記第2の層の一方又は双方は、複数の金属サブレイヤーを含むラミネート層である請求項1に記載の方法。

【請求項25】

半導体処理方法であって、金属電極を堆積する工程を含み、

前記金属電極を堆積する工程は、

誘電体層に金属材料を堆積する工程であって、前記金属材料を堆積する前駆体がプラズマ活性化されていない、工程と、

励起された水素含有種に前記金属材料を露出する工程と、

その後、前記金属材料を露出する工程の後に、前記金属材料にさらなる金属材料を堆積する工程と、を含む半導体処理方法。

【請求項26】

前記さらなる金属材料を堆積する前駆体は、プラズマ活性化されていない請求項25に記載の方法。

【請求項27】

前記金属電極を堆積する工程は、約420℃未満で行われる請求項25に記載の方法。

【請求項28】

前記金属材料は、遷移金属化合物である請求項25に記載の方法。

【請求項29】

前記遷移金属化合物は、窒化金属、炭化金属、又は窒炭化金属である請求項28に記載の方法。

【請求項30】

前記遷移金属化合物は、炭化タンタル、窒炭化タンタル、窒化タンタル、炭化チタニウム、窒炭化チタニウム、窒化チタニウムからなる群から選択される請求項29に記載の方法。

【請求項31】

前記金属材料を堆積する工程は、実質的に均質な金属を形成する請求項25に記載の方法。

【請求項32】

前記金属材料を堆積する工程は、異なる材料のサブレイヤーを含むラミネート層を形成する請求項25に記載の方法。

【請求項33】

前記金属材料を堆積する工程及び前記さらなる金属層を堆積する工程は、同一材料を堆積する工程を含む請求項25に記載の方法。

【請求項34】

前記金属材料を堆積する工程は、約1−3nmの厚さを有する層を形成する請求項25に記載の方法。

【請求項35】

前記金属電極は、ゲートスタックの一部を構成し、前記ゲートスタックの前記金属電極の仕事関数は、プラズマトリートメントなしで行われる同等の処理と比較して、約0.15eV以上増加する請求項34に記載の方法。

【請求項1】

半導体処理方法であって、基板にゲート電極を形成する工程を含み、

前記基板にゲート電極を形成する工程は、

ゲート誘電体を含む基板を反応チャンバ内に提供する工程と、

前記基板をプラズマ又はプラズマ発生ラジカルに露出せずに、前記ゲート誘電体に遷移金属化合物を含む第1の層を堆積する工程と、

前記第1の層を水素含有ガスに露出する工程と、

その後、遷移金属化合物を含む第2の層を堆積する工程と、を含む、半導体処理方法。

【請求項2】

前記第1の層の厚さは、約5nm以下である請求項1に記載の方法。

【請求項3】

前記ゲート電極及び前記ゲート誘電体は、ゲートスタックを構成し、前記ゲートスタックの前記ゲート電極の仕事関数は、約4.85eV以上である請求項1に記載の方法。

【請求項4】

前記仕事関数は、約5.0eV以上である請求項3に記載の方法。

【請求項5】

前記水素含有ガスは、励起された水素含有種を含む請求項1に記載の方法。

【請求項6】

前記励起された水素含有種は、水素ラジカルを含む請求項5に記載の方法。

【請求項7】

前記励起された水素含有種は、水素含有プラズマの一つである請求項5に記載の方法。

【請求項8】

前記水素含有プラズマを形成するプラズマ電力は、約175W以上である請求項7に記載の方法。

【請求項9】

前記励起された水素含有種を発生するプラズマ電力は、約2秒以上のパルスである請求項7に記載の方法。

【請求項10】

前記励起された水素含有種を発生するピーク間電圧は、約130V以上である請求項7に記載の方法。

【請求項11】

前記ピーク間電圧は、約160V以上である請求項10に記載の方法。

【請求項12】

前記第1の層を水素含有ガスに露出する工程は、プラズマ‐エンハンスド原子層堆積により膜を堆積する工程を含む請求項7に記載の方法。

【請求項13】

プラズマ‐エンハンスド原子層堆積により堆積される前記膜は、タンタル含有膜である請求項12に記載の方法。

【請求項14】

前記第1の層は、原子層堆積により堆積される請求項1に記載の方法。

【請求項15】

前記第2の層は、プラズマ‐エンハンスド原子層堆積により堆積される請求項14に記載の方法。

【請求項16】

前記第2の層は、原子層堆積により堆積される請求項1に記載の方法。

【請求項17】

前記第1の層を堆積する工程と前記第1の層を露出する工程との間、又は前記第1の層を露出する工程と前記第2の層を堆積する工程との間に、前記基板を酸素含有ガスに露出する工程をさらに含む請求項1に記載の方法。

【請求項18】

前記基板を酸素含有ガスに露出する工程は、前記基板を前記反応チャンバから搬出し、前記基板をクリーンルームエアに露出する工程を含む請求項17に記載の方法。

【請求項19】

前記第1の層を堆積する工程と前記第1の層を露出する工程との間、及び前記第1の層を露出する工程と前記第2の層を堆積する工程との間に、前記基板を酸素含有ガスに露出する工程をさらに含む請求項1に記載の方法。

【請求項20】

前記ゲート電極を形成する工程は、前記第1及び第2の層を誘電体材料により規定されるトレンチに堆積する工程を含む請求項1に記載の方法。

【請求項21】

前記ゲート電極を形成する工程は、PMOSトランジスタの前記ゲート電極を形成する工程を含む請求項20に記載の方法。

【請求項22】

前記ゲート電極を形成する工程は、前記トレンチの開口を規定し、前記開口を金属で充填する工程をさらに含む請求項20に記載の方法。

【請求項23】

前記基板は、前記第1の層を堆積する工程と前記開口を充填する工程との間で約420℃未満の温度で維持される請求項22に記載の方法。

【請求項24】

前記第1の層及び前記第2の層の一方又は双方は、複数の金属サブレイヤーを含むラミネート層である請求項1に記載の方法。

【請求項25】

半導体処理方法であって、金属電極を堆積する工程を含み、

前記金属電極を堆積する工程は、

誘電体層に金属材料を堆積する工程であって、前記金属材料を堆積する前駆体がプラズマ活性化されていない、工程と、

励起された水素含有種に前記金属材料を露出する工程と、

その後、前記金属材料を露出する工程の後に、前記金属材料にさらなる金属材料を堆積する工程と、を含む半導体処理方法。

【請求項26】

前記さらなる金属材料を堆積する前駆体は、プラズマ活性化されていない請求項25に記載の方法。

【請求項27】

前記金属電極を堆積する工程は、約420℃未満で行われる請求項25に記載の方法。

【請求項28】

前記金属材料は、遷移金属化合物である請求項25に記載の方法。

【請求項29】

前記遷移金属化合物は、窒化金属、炭化金属、又は窒炭化金属である請求項28に記載の方法。

【請求項30】

前記遷移金属化合物は、炭化タンタル、窒炭化タンタル、窒化タンタル、炭化チタニウム、窒炭化チタニウム、窒化チタニウムからなる群から選択される請求項29に記載の方法。

【請求項31】

前記金属材料を堆積する工程は、実質的に均質な金属を形成する請求項25に記載の方法。

【請求項32】

前記金属材料を堆積する工程は、異なる材料のサブレイヤーを含むラミネート層を形成する請求項25に記載の方法。

【請求項33】

前記金属材料を堆積する工程及び前記さらなる金属層を堆積する工程は、同一材料を堆積する工程を含む請求項25に記載の方法。

【請求項34】

前記金属材料を堆積する工程は、約1−3nmの厚さを有する層を形成する請求項25に記載の方法。

【請求項35】

前記金属電極は、ゲートスタックの一部を構成し、前記ゲートスタックの前記金属電極の仕事関数は、プラズマトリートメントなしで行われる同等の処理と比較して、約0.15eV以上増加する請求項34に記載の方法。

【図1a】

【図1b】

【図1c】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9a】

【図9b】

【図9c】

【図9d】

【図10】

【図11】

【図12】

【図1b】

【図1c】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9a】

【図9b】

【図9c】

【図9d】

【図10】

【図11】

【図12】

【公開番号】特開2012−253352(P2012−253352A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2012−125885(P2012−125885)

【出願日】平成24年6月1日(2012.6.1)

【出願人】(512144771)エーエスエム アイピー ホールディング ビー.ブイ. (1)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成24年6月1日(2012.6.1)

【出願人】(512144771)エーエスエム アイピー ホールディング ビー.ブイ. (1)

【Fターム(参考)】

[ Back to top ]