TFTアレイ検査装置

【課題】TFTアレイ検査装置において、基板内で絶縁破壊(ESD)を生じさせることなく、基板に帯電した電荷を放電する。

【解決手段】プローバーを基板に配置し、プローバーを介して検査信号を基板に供給し、基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、TFTアレイ検査時にプローバーを基板に配置した際に、基板をプローバーを介して接地された高抵抗の放電用抵抗に接続することによって、基板に帯電する電荷をプローバーおよび放電用抵抗を介して放電させる。基板に帯電する電荷を、基板からプローバーを介して放電用抵抗に導くことによって、TFTアレイ検査装置内において格別な機構を設けることなく基板に帯電する電荷を放電することができる。

【解決手段】プローバーを基板に配置し、プローバーを介して検査信号を基板に供給し、基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、TFTアレイ検査時にプローバーを基板に配置した際に、基板をプローバーを介して接地された高抵抗の放電用抵抗に接続することによって、基板に帯電する電荷をプローバーおよび放電用抵抗を介して放電させる。基板に帯電する電荷を、基板からプローバーを介して放電用抵抗に導くことによって、TFTアレイ検査装置内において格別な機構を設けることなく基板に帯電する電荷を放電することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶基板等のTFT基板のアレイを検査するTFTアレイ検査装置に関し、特に、基板の帯電を除電する機構を有するTFTアレイ検査装置に関する。

【背景技術】

【0002】

液晶アレイ検査装置等のTFTアレイ検査装置において、液晶基板等の基板上を撮像して得られる撮像画像として、光学的に撮像して得られる光学撮像画像、あるいは、電子ビームやイオンビーム等の荷電ビームを基板上で二次元的に走査して得られる走査画像を用いることができる。

【0003】

TFTディスプレイ装置に用いるTFTアレイ基板の製造工程では、製造されたTFTアレイ基板が正しく駆動するかの検査が行われる(特許文献1,2)。

【0004】

例えば、検査対象である基板のTFTアレイに検査信号を印加してTFTアレイに付随した透明電極を所定電位状態とし、基板上に電子ビームやイオンビーム等の荷電ビームを二次元的に照射して走査し、このビーム走査で得られる走査画像に基づいてTFTアレイを検査するTFTアレイ検査装置が知られている。TFTアレイ検査では、例えば、電子線の照射によって放出される二次電子をフォトマルチプライヤなどによって電気信号に変換して検出し、この検出信号の信号強度に基づいてアレイ欠陥を判定している。

【0005】

基板のTFTアレイとピクセルは対応して形成されており、TFTアレイに駆動信号を印加することによって特定のピクセルを駆動することができる。TFTアレイ検査において、一般に、TFTアレイに所定パターンの駆動信号を印加し、基板内に形成されたパネルの各ピクセルを所定パターンで駆動し、これらのピクセルに電子線を照射し、照射点から放出される二次電子を検出する。この電子線照射をパネル内で走査して行うことによって、パネル内の各ピクセルから検出信号を取得している。

【0006】

TFTアレイの欠陥は、例えば、取得した検出信号の信号強度を、所定パターンの駆動信号で駆動した際に正常なTFTアレイから得られる検出信号の信号強度と比較することによって検出することができる。

【0007】

基板不良として、プロセスに起因する不良の他、静電気に起因する不良が指摘されている(例えば、特許文献3参照)。

【0008】

基板の製造ライン上において基板を搬送する際に、接触や摩擦等の種々の要因によって静電気が発生して帯電する場合がある。基板に対する各種処理工程において帯電した基板が処理装置と接触すると、基板と処理装置との間の電位差によって過剰電流が流れ、基板上に形成あるいは装着された電子部品が絶縁破壊(ESD)される場合がある。

【0009】

このような絶縁破壊を防止する方法として、搬送路上にイオナイザ(帯電中和装置)を配置し、搬送される基板にイオナイザで生成したイオンを放射することによって、基板に帯電する電荷を除電することが提案されている(例えば、特許文献4,5参照)。

【0010】

また、装置内に収納された基板と装置とが接触する箇所に絶縁処理を施すことによって放電の発生を抑制することも行われている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2004−271516号公報

【特許文献2】特開2004−309488号公報

【特許文献3】特開2000−206177号公報(段落[0003],段落[0010],段落[0013])

【特許文献4】特開2001−60609号公報

【特許文献5】特開2002−232189号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

絶縁破壊を防ぐ方法として、上記したイオナイザ(帯電中和装置)を用いる方法では、除電に時間を要するという問題があり、除電時間を十分にとることができない場合には除電が不十分となり、搬送先の装置内において絶縁破壊が発生するという問題が生じる。基板をインラインで製造する場合には、製品のスループットを高めるためにライン上に設けられた各処理工程での処理時間を短縮することが求められているため、イオナイザによる除電は最適とは言えない場合がある。

【0013】

基板上に形成されたTFTアレイを検査するTFTアレイ検査工程を含むライン処理においても、全体の処理時間の短縮要求から搬送に要する時間についても短縮することが求められる。そのため、イオナイザによる除電の時間を十分にとることができず、除電を十分に行うことができない。

【0014】

また、装置内において絶縁体によって放電を防ぐ処置が考えられる。この処置では、基板が帯電した状態のままで処理が行われ、その後、帯電したまま装置から搬送されることになるため、後工程において絶縁破壊が発生するおそれがあるという問題がある。

【0015】

基板を接地させることによって、基板に帯電した電荷を放電させることができる。しかしながら、基板を接地させることによって基板の帯電電荷を短時間で放電させると、基板内の電位が不均一となり基板内に電位差が生じることになる。この電位差が絶縁破壊電圧を超えると、放電現象と同様に絶縁破壊が発生する。

【0016】

そこで、本発明は上記課題を解決して、TFTアレイ検査装置において、基板内で絶縁破壊を生じさせることなく、基板に帯電した電荷を放電することを目的とする。

【0017】

また、基板内で絶縁破壊を生じさせることなく、かつ、短時間で基板に帯電した電荷を放電することを目的とし、また、後工程において絶縁破壊が発生することを防ぐことを目的とする。

【課題を解決するための手段】

【0018】

本願発明は、プローバーを基板に載置し、プローバーを介して検査信号を基板に供給し、基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、TFTアレイ検査時にプローバーを基板に載置した際に、基板をプローバーを介して高い電気抵抗の放電用抵抗に接続し、この放電用抵抗を介して接地することによって、基板の帯電電荷の放電速度を抑制した放電させる。

【0019】

基板に帯電する電荷を、基板からプローバーを介して放電用抵抗に導くことによって、TFTアレイ検査装置内において格別な機構を設けることなく基板に帯電する電荷を放電することができる。

【0020】

また、高い電気抵抗の放電用抵抗を介して接地することによって、放電時に基板内に生じる電位差を低減させて、発生した電位差が絶縁破壊電圧を超えないようにすることで絶縁破壊の発生を抑制することができる。

【0021】

本願発明のTFTアレイ検査装置は、基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、基板検査を行うための検査信号を出力する基板検査信号部と、基板にコンタクトピンを電気的な接触させ、検査信号を基板に印加するプローバーと、基板検査信号部が出力する検査信号をプローバーに供給する給電部と、基板に帯電する電荷をプローバーを介して接地に放電する放電部とを備える。

【0022】

本発明の放電部は、コンタクトピンとアースとの間を高い電気抵抗で接続する放電用抵抗を備える。

【0023】

TFTアレイ検査装置は、基板上に形成されたTFTアレイを検査する際に、プローバーを基板に配置して、プローバーから基板に検査信号を印加する。本発明のTFTアレイ検査装置は、プローバーを基板に配置してコンタクトピンを基板の電極に電気的に接触させ、給電部が基板検査信号部から入力した検査信号を、コンタクトピンと基板の電極の電気的接触を通して基板に供給する。

【0024】

本発明のプローバーは、検査信号の供給に先立って、基板に帯電する電荷を、コンタクトピンと基板の電極との電気的接触を通して基板から放電部に導く。放電部は、プローバーを介して導かれた電荷を、放電用抵抗を通して接地に放電する。放電用抵抗は高い電気抵抗を有しているため、放電時に流れる電流値は低い値に抑制され、基板内に生じる電位差は低減される。

【0025】

基板内に生じる電位差を低減することによって、基板内の電位差が絶縁破壊電圧を越えることによる絶縁破壊の発生を抑制する。

【0026】

本願発明のTFTアレイ検査装置は、プローバーを介して基板に検査信号を供給すると共に、プローバーを介して基板の帯電を放電する。この放電電流が基板検査信号部に流入し、絶縁破壊によって基板検査信号部内の信号発生回路等が破損することを避けるために、プローバーへの検査信号の供給とプローバーを介して行う帯電電荷の放電とを分離して行う構成を備える。

【0027】

本願発明のTFTアレイ検査装置は、プローバーへの検査信号の供給とプローバーを介して行う帯電電荷の放電とを分離して行う構成として2つの形態を備える。

【0028】

本願発明のTFTアレイ検査装置の第1の形態は、プローバーの給電ピンを、放電用抵抗と基板検査信号部との間で切り替えて接続する切り替え回路を備える。

【0029】

本発明の切り替え回路は、プローバーの給電ピンを放電用抵抗に切り替える動作によって、基板に帯電する電荷を放電用抵抗を介して接地に放電する。一方、本発明の切り替え回路は、プローバーの給電ピンを基板検査信号部に切り替える動作によって、検査用信号を給電ピンおよびコンタクトピンを介して基板に供給する。

【0030】

本発明の切り替え回路は、はじめに放電用抵抗側に接続を切り替えておくことによって、基板に帯電する電荷を放電し、放電が完了した後、基板検査信号部側に接続を切り替えることによって、プローバーに検査信号を供給する。

【0031】

本発明の切り替え回路において、放電用抵抗側への接続に続いて基板検査信号部側への接続を行う接続の動作は、複数の形態で行うことができる。

【0032】

接続動作を定める一形態は、切り替え回路において、給電ピンとの接続を放電用抵抗から基板検査信号部へ切り替える動作を、基板の帯電電荷の放電が放電用抵抗を介して開始した後、所定時間が経過した時点で行う。この動作によって、はじめに基板からの帯電電荷の放電を行い、次にプローバーに検査信号を供給する。

【0033】

基板の帯電電荷の放電が放電用抵抗を介して開始した後、所定時間が経過した時点を定める形態は、タイマーによって経過時間を計時して定める形態、あるいは、TFTアレイ検査装置において予め定められた制御プログラムに基づいてデフォルトの時間経過により定める形態とすることができる。

【0034】

タイマーによる経過時間の計時によって切り替え時点を定める形態では、切り替え回路によって放電と検査信号の供給の切り替えを行うTFTアレイ検査装置において、給電部は、プローバーに設けたプローバー側給電部と、基板を載置するステージに設けたステージ側給電部とを備え、放電部は切り替え信号を出力するタイマーを備える。タイマーは、プローバー側給電部とステージ側給電部との接触に基づいて計時を開始し、予め定められた所定時間が経過した後に切り替え信号を出力する。

【0035】

上記した給電部および放電部を備える構成において、プローバーが基板に載置されたことを、プローバー側給電部とステージ側給電部との接触に基づいて検出し、タイマーはこの接触検出に基づいて計時を開始し、予め設定された時間が経過した時点で、切り替え信号を出力する。

【0036】

切り替え回路は、タイマーが出力する切り替信号に基づいて、給電ピンとの接続を放電用抵抗から基板検査信号部へ切り替える動作を行う。

【0037】

制御プログラムに基づいてデフォルトの時間経過により定める形態では、基板の検査を行うメインチャンバへ基板を搬送する工程、メインチャンバ内に配置された基板にプローバーを配置する工程、放電工程、検査信号を供給して基板検査を行う工程等の各工程を行うプログラムにおいて、基板配置工程の終了した後、基板の放電に要する時間に所定の余裕時間を加味した時間を検査信号の供給時点として設定する。

【0038】

本願発明のTFTアレイ検査装置の第2の形態は、第1の形態の切り替え回路を用いることなく、コンタクトピンと放電用抵抗との接続と、給電ピンと基板検査信号部との接続との接続を、プローバーの基板側への移動に伴って、時間差を伴って順に行うことによって、プローバーを介して行う帯電電荷の放電と、プローバーを介して行う検査信号の供給とを分離して行う。

【0039】

第2の形態において、放電部は、放電用抵抗の一端を接地し、他端をコンタクトピンと給電ピンとの間に接続する。この放電用抵抗の接続によってコンタクトピンと放電用抵抗とを接続する第1の接続回路と、コンタクトピンと給電ピンと基板検査信号部とを接続する第2の接続回路とを備える。

【0040】

第1の接続回路と第2の接続回路の各接続は、プローバーの移動に伴って順次行う。第1の接続回路は、基板に帯電する電荷を、コンタクトピンから放電用抵抗を介して接地に放電し、第2の接続回路は、検査用信号を、給電ピンおよびコンタクトピンから基板に供給する。

【0041】

また、給電部は、プローバーに設けたプローバー側給電部と、基板を載置するステージに設けたステージ側給電部とを有する。プローバー側給電部はコンタクトピンと接続された給電ピンを備え、ステージ側給電部は給電ピンと電気的に接触するための電極を備える。プローバーの移動に伴って、コンタクトピンと基板側の電極との電気的接触を、給電ピンとステージ側給電部との電極との電気的接触よりも先行させるように、給電ピンおよびコンタクトピンと配置する。この配置により、プローバーが基板方向に移動すると、コンタクトピンと基板側の電極とが先に電気的に接触し、第1の接続回路の接続によってコンタクトピンと放電用抵抗とを接続し、基板に帯電する電荷を放電用抵抗を介して接地に放電する。

【0042】

さらに、プローバーが基板方向に移動すると、給電ピンとステージ側給電部の電極とが電気的に接触し、第2の接続回路によってコンタクトピンと基板検査信号部とを接続し、検査用信号を基板に供給する。

【0043】

前記した給電ピンとコンタクトピンの配置は、例えば、コンタクトピンの長さを給電ピンの長さよりも長く設定することで実現することができる。なお、給電ピンおよびコンタクトピンは、各ピンをスプリング等の弾性部材によって弾性的に保持することによって、コンタクトピンは電極に接触した後、所定のストローク分だけ押し込まれるため、プローバーの移動に伴って、給電ピンが電極を押圧することによる支障を解消することができる。

【0044】

第2の形態によれば、プローバーと基板とが接触する時間を、タイマーやプログラムによって定める構成を不要とすることができる。

【0045】

さらに、本願発明のTFTアレイ検査装置が備えるステージは、ステージ用放電抵抗を介して接地する構成とすることができる。ステージ用放電用抵抗を介して接地することによって、ステージに帯電する電荷が放電した際に、このステージ上に載置される基板に発生する絶縁破壊を防ぐ。

【0046】

さらに、本願発明のTFTアレイ検査装置が備える基板搬送装置は、基板を載置する搬送用パレットを備え、この搬送用パレットは基板を載置する側に絶縁体を有し、絶縁体を介して基板と接触する構成とすることができる。搬送用パレットと基板との間に絶縁体を設けることによって、基板に帯電する電荷が搬送用パレットを介して放電しないようにし、搬送パレットに載置された基板に発生する絶縁破壊を防ぐ。

【発明の効果】

【0047】

本発明によれば、TFTアレイ検査装置において、基板内で絶縁破壊を生じさせることなく、基板に帯電した電荷を放電することができる。

【0048】

また、本発明によれば、基板内で絶縁破壊を生じさせることなく、かつ、短時間で基板に帯電した電荷を放電することができ、また、後工程において絶縁破壊が発生することを防ぐことができる。

【図面の簡単な説明】

【0049】

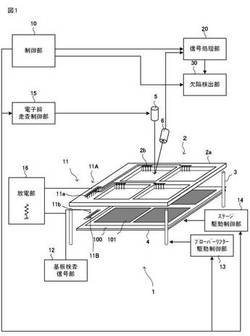

【図1】本発明のTFTアレイ検査装置の構成を説明するための図である。

【図2】本発明のTFTアレイ検査装置の第1の形態を説明するための概略図である。

【図3】本発明のTFTアレイ検査装置の第1の形態のプローバー、給電部、放電部の構成を説明するための概略図である。

【図4】本発明のTFTアレイ検査装置の第1の形態の動作例を説明するためのフローチャートである。

【図5】本発明のTFTアレイ検査装置の第1の形態の動作例を説明するための動作説明図である。

【図6】本発明のTFTアレイ検査装置の第2の形態を説明するための概略図である。

【図7】本発明のTFTアレイ検査装置の第2の形態のプローバー、給電部、放電部の構成を説明するための概略図である。

【図8】本発明のTFTアレイ検査装置の第2の形態の動作例を説明するためのフローチャートである。

【図9】本発明のTFTアレイ検査装置の第2の形態の動作例を説明するための動作説明図である。

【発明を実施するための形態】

【0050】

以下、本発明の実施の形態について図を参照しながら詳細に説明する。以下では、図1を用いて本発明のTFTアレイ検査装置の構成を説明し、本発明の第1の形態に対応する実施例を図2〜図5を用いて説明し、本発明の第2の形態に対応する実施例を図6〜図9を用いて説明する。

【0051】

はじめに、図1を用いて本発明のTFTアレイ検査装置の一構成例を説明する。なお、図1はTFTアレイ検査装置の内、主に基板検査を行う構成について示している。図1に示す構成例では、液晶基板等のTFT基板に電子線を照射し、TFT基板から放出される二次電子を検出し、二次電子の検出信号から信号画像を形成し、この信号画像に基づいて欠陥検出を行う構成例を示している。本発明は、検査対象の基板は液晶基板に限らず、また、基板走査は電子線に限らずイオンビーム等の荷電ビームとすることができる。また、検出信号は照射する荷電ビームに依存し、二次電子に限られるものではない。

【0052】

図1において、TFTアレイ検査装置1は、液晶基板等の基板100を載置すると共にXY方向に移動自在とするステージ4と、基板100上に形成されたパネル101のアレイ(図示していない)に検査信号を印加するプローバー2と、プローバー2のプローバーフレーム2aを上下方向に昇降駆動するプローバーリフター3と、ステージ4の上方位置に配置した電子銃5と、基板100のパネル101のピクセル(図示していない)から放出される二次電子を検出する検出器6とを備える。電子銃5および検出器6は複数の組みを設けることができる。検査信号は、基板検査信号部12で生成され、プローバー2を介して基板100のパネル101に供給される。

【0053】

基板検査信号部12からプローバー2への検査信号の供給は、給電部11を介して行われる。給電部11は、プローバー2側に設けたプローバー側給電部11Aとステージ4側に設けたステージ側給電部11Bとによって構成される。

【0054】

プローバー側給電部11Aは給電ピン11aを備え、プローバーフレーム2aに設けられる。給電ピン11aは、プローバーフレーム2aに配設された配線2cを通してコンタクトピン2bに接続される。コンタクトピン2bは、プローバー2の移動によって基板100に設けられた電極と電気的に接触し、検査信号を基板100の各パネル101に供給する。

【0055】

ステージ側給電部11Bは電極11bを備え、ステージ4あるいはTFTアレイ検査装置1の固定側に設けられる。電極11bは、基板検査信号部12と直接あるいは間接に接続されており、プローバー2をステージ4側に移動させ、給電ピン11aを電極11bに電気的に接触させることによって、基板検査信号部12からプローバー2へ検査信号を供給する。なお、図1には給電ピン11aおよび電極11bは図示していない。

【0056】

本発明のTFTアレイ検査装置1は、基板100に帯電する電荷を放電する放電部16を備える。放電部16は一端を接地した放電用抵抗16aを備え、放電用抵抗16aを通して基板100に帯電する電荷を放電する。

【0057】

放電用抵抗16aの他端は、プローバーフレーム2aに配設された配線2cあるいは給電部11に接続され、コンタクトピン2bが基板100の電極100a(図示していない)に接触した際に、電極100a、コンタクトピン2b、配線2c、および放電用抵抗16aをつなぐ放電回路が形成され、基板100の帯電電荷は放電回路を通して接地に放電される。

【0058】

放電用抵抗16aは高い電気抵抗を有しており、電荷が流れる際に放電用抵抗16aの両端に電圧降下が発生する。放電用抵抗16aの一端は接地しているため、放電用抵抗16aの他端側には電圧降下分の電圧が発生し、プローバー2を介して接続される基板100の電位は、放電用抵抗16aの電圧降下分だけ高くなる。この電位の発生によって、基板100内に発生する電位差は短絡した場合の電位差と比較して小さくなる。これによって、基板100内の電位差を、絶縁破壊が発生する電位差よりも下げることができる。

【0059】

放電部16とプローバーフレーム2aの配線2cとを接続する構成は、給電部11を介して接続する構成とする他に、給電部11を介することなく直接に接続する構成とすることができる。図1では、2つの構成を同一の図面に示しているが、何れか一方の構成によって、放電部16とプローバーフレーム2aの配線2cとの接続を行う。

【0060】

給電部11を介して接続する構成では、コンタクトピン2bおよび給電ピン11aは、基板100に検査信号を供給する給電回路を構成すると共に、基板100に帯電する電荷を放電用抵抗を介して接地に放電する放電回路を構成することになる。

【0061】

第1の形態では、図2〜図5を用いて給電部11を介して接続する構成について説明し、第2の形態では、図6〜図9を用いて給電部11を介することなく直接に接続する構成について説明する。

【0062】

ステージ駆動制御部14はステージ4の駆動を制御し、電子線走査制御部15は電子銃5が照射する電子線の照射方向を制御して、基板100上の電子線の走査を制御する。信号処理部20は、検出器6が検出する二次電子の検出信号を信号処理し信号画像を形成する。得られた信号画像の信号強度や検出位置は欠陥検出部30に送られ、欠陥位置や欠陥種の判定が行われる。欠陥検出部30は、信号処理部20から送られた信号画像の信号強度に基づいてピクセルの欠陥を検出し、検出位置によって欠陥ピクセルおよび対応する欠陥アレイを検出する。

【0063】

なお、ピクセルおよびアレイは基板のパネルに形成され、各ピクセルはアレイに対して電圧を印加することによって駆動されるため、ピクセルの欠陥検出は、そのピクセルに対するアレイ検査に対応している。

【0064】

ステージ4は、基板100を載置するとともに、ステージ駆動制御部14によってX軸方向およびY軸方向に移動自在であり、また、電子銃5から照射される電子線は電子線走査制御部15によってX軸方向あるいはY軸方向に振らせることができる。ステージ駆動制御部14および電子線走査制御部15は、単独あるいは協働動作によって電子線を基板100上で走査させ、基板100のパネル101の各ピクセルに照射させることができる。

【0065】

プローバーリフター駆動制御部13は、プローバーリフター3を駆動制御して、プローバーフレーム2aを上下方向に昇降駆動する。プローバーリフター3が上昇駆動するとプローバーフレーム2aは上方に移動して基板100から離れ、コンタクトピン2bおよび給電ピン11aの各端子は、それぞれが対向する電極との電気的な接続が解かれる。一方、プローバーリフター3が下降駆動するとプローバーフレーム2aは下方に移動して基板100に近づき、コンタクトピン2bおよび給電ピン11aの各端子はそれぞれが対向する電極と電気的に接触する。

【0066】

プローバーリフター駆動制御部13,ステージ駆動制御部14,電子線走査制御部15,信号処理部20、欠陥検出部30の各部の駆動動作は制御部10によって制御される。また、制御部10は、アレイ検査装置1の全体の動作を含む制御を行う機能を有し、これらの制御を行うCPU、およびCPUを制御するプログラムを記憶するメモリ等によって構成することができる。

【0067】

[第1の形態]

次に、本願発明のTFTアレイ検査装置の第1の形態について説明する。図2は第1の形態を説明するための概略図であり、図3は第1の形態のプローバー、給電部、放電部の構成を説明するための概略図であり、図4,5は第1の形態の動作例を説明するためのフローチャートおよび動作説明図である。

【0068】

図2において、TFTアレイ検査装置1は、基板100を検査するメインチャンバ1A、基板100をメインチャンバ1Aとの間で搬送する搬送チャンバ1B、およびメインチャンバ1Aと搬送チャンバ1Bとの間を密封自在に開閉するゲートドア1Cを備える。

【0069】

搬送チャンバ1B内には、基板100を載置した状態で搬送する搬送部17を備える。搬送部17は、基板100を搬送するパレット17a、およびパレット17a上に設けられた絶縁体17bを備え、パレット17aと載置する基板100との間に絶縁体17bを設けることによって、基板100に帯電する電荷の放電を防ぎ、絶縁破壊の発生を防ぐ構成としている。

【0070】

メインチャンバ1A内には、基板100を載置するステージ4と、基板100に検査信号を供給するプローバー2を備える。ステージ4は、X方向あるいはY方向に移動する第1のステージ4aおよび第2のステージ4bを備える。第1のステージ4aと第2のステージ4bとの間には絶縁物4cを設け、基板100を載置する側の第1のステージ4aはステージ用放電抵抗4dを介して接地されている。第1のステージ4aは絶縁物4cによって絶縁することによって基板100からの帯電電荷の放電を防いでいる。

【0071】

また、第1のステージ4aはステージ用放電抵抗4dを介して接地する構成とする。この構成とすることで、基板100の撓みによってステージ4aと接触し、接触部位から放電が発生して部分的に絶縁破壊を生じさせるような電位差が発生する事態が生じたとしても、放電時の放電速度を低下させることによって基板100内の電位差を低減して絶縁破壊の発生を抑制する。

【0072】

プローバー2は、プローバーフレーム2aを有し、基板100の電極100aと電気的に接触するコンタクトピン2bと、検査信号の供給を受ける給電ピン11aを備える。プローバー2側とステージ4側は、検査信号の供給を受けるための構成として給電部11を備える。給電部11は、プローバー2側の構成として給電ピン11aを有するプローバー側給電部11Aを備え、ステージ4側の構成として電極11bを有するステージ側給電部11Bを備える。

【0073】

第1の形態では、検査信号の供給と帯電電荷の放電とを給電部11を介して行うと共に、切り替え部19によって検査信号の供給と帯電電荷の放電とを切り替える。

【0074】

切り替え部19は、通常は放電部16側に接続しておき、検査時において放電が終了した後、基板検査信号部12側に切り替える。

【0075】

放電時には、切り替え部19は放電部16側に接続されているため、基板100に帯電する電荷は、コンタクトピン2b、配線2c、給電部11、および切り替え部19を介して放電部16に導かれ、放電部16の放電用抵抗16aを通して接地される。

【0076】

一方、検査時には、切り替え部19は放電部16を切り離して給電部11に接続を切り替えることによって、基板検査信号部12からの検査信号は、切り替え部19,給電部11、配線2c、およびコンタクトピン2bを介して基板100に供給される。

【0077】

切り替え部19は切り替え回路19aとタイマー19bを備え、切り替え回路19aはタイマー19bの切り替え信号に基づいて放電部16から基板検査信号部12に接続を切り替える。タイマー19bは、プローバー2が基板100に載置されてから所定時間が経過した時点で切り替え信号を出力する。所定時間は、基板100に帯電する電荷が放電用抵抗16aを通して接地に放電されるに要する時間に応じて定めることができ、一例として2秒程度に設定される。

【0078】

給電部11は、プローバー側給電部11Aとステージ側給電部11Bを備え、プローバー2が基板100上に載置した際に、プローバー側給電部11Aの給電ピン11aとステージ側給電部11B側の電極11bとが電気的に接触することによって、プローバー2と切り替え部19との間を接続する回路を形成する。

【0079】

タイマー19bの計時の開始は、例えば、プローバー側給電部11Aとステージ側給電部11Bとの接触を検出することによって行うことができる。

【0080】

切り替え回路19aの接続切替は、タイマーによる計時時間によって行う他、制御プリグラムに基づいて行う形態とすることもできる。

【0081】

制御部10は、メインチャンバへ基板を搬送する工程、メインチャンバ内に配置された基板にプローバーを配置する工程、放電工程、検査信号を供給して基板検査を行う工程等の各工程を行う制御プログラムを格納し、この制御プログラムに従って各工程を行う。各工程処理において、基板配置工程が終了した後、基板の放電の要する時間に所定の余裕時間を加味した時間を予め設定しておき、この設定時点を検査信号の供給時点として設定することで、デフォルトの時間経過により切り替え回路の接続切替を行う。

【0082】

図3は、第1の形態が備えるプローバー2、給電部11、切り替え部19、および放電部16の構成例を示している。

【0083】

プローバー2は、基板100の電極100aと電気的に接触するコンタクトピン2bと、給電部11において電極11bと電気的に接触する給電ピン11aと、コンタクトピン2bと給電ピン11aとを接続するプローバーフレーム2aに配設された配線2cとを備える。給電ピン11aはプローバー側給電部11Aを構成し、電極11bはステージ側給電部11Bを構成している。

【0084】

切り替え部19が備える切り替え回路19aの一端には、ステージ側給電部11Bの電極11bが接続され、他方に切り替え端子には基板検査信号部12と放電部16とが接続され、通常は放電部16側に接続し、タイマー19bの切り替え信号に応じて基板検査信号部12側に接続が切り替えられる。

【0085】

タイマー19bの計時の開始は、プローバー2が基板100に載置された時点で行われ、予め定められた時間が経過した時点で切り替え信号を出力する。

【0086】

プローバー2が基板100に載置された時点の検出は、例えば、プローバー2側に設けたピン18aとステージ側に設けたセンサ18bからなる載置検出部18によって行うことができる。プローバー2が基板100に載置されると、センサ18bはピン18aの近接あるいは接触したことを検出して検出信号をタイマー19bに出力する。タイマー19bは、検出信号を受けて計時を開始する。

【0087】

切り替え部19が放電部16側に切り替えられているときには、基板100の電極100aから、コンタクトピン2b、配線2c、給電ピン11a、電極11bを通って放電用抵抗16aにつながる放電回路が形成され、基板100の帯電電荷はこの放電回路を介して接地に放電される。

【0088】

一方、切り替え部19が基板検査信号部12側に切り替えられているときには、基板検査信号部12から、電極11b、給電ピン11a、配線2c、コンタクトピン2bを通って100の電極100aにつながる給電回路が形成され、検査信号はこの給電回路を通って基板100の各パネルに供給される。

【0089】

本願発明のTFTアレイ検査装置の第1の形態の動作例について、図4のフローチャートおよび動作説明図を用いて説明する。

【0090】

切り替え回路19aは放電用抵抗16a側に接続を切り替え、ステージ側給電部11Bの電極11bと放電用抵抗16aとを接続する(S1)。ステージ4上に基板100を搬送して載置した後(S2)、プローバー2を基板100に移動する。図5(a)はプローバー2を基板100に載置する前の状態を示している。この状態では、切り替え回路19aは放電用抵抗16a側に接続を切り替えられている(S3)。

【0091】

プローバー2の移動によって、プローバー2のコンタクトピン2bは基板100の電極100aに接触し、プローバー側給電部11Aの給電ピン11aはステージ側給電部11Bの電極11bに接触する。これによって、電極100aからコンタクトピン2b、配線2c、給電ピン11a、電極11b、および放電用抵抗16aを介して接地に接続される放電回路が形成される。図5(b)は、プローバー2が基板100に載置された状態を示している(S4)。

【0092】

この放電回路の形成によって、基板100に帯電した電荷は放電用抵抗16aを介して接地に放電される。放電用抵抗16aは例えば、100MΩ程度の高い電気抵抗とすることによって、放電速度を抑えると共に、コンタクトピン2bが接触する基板100の電位降下を抑え、基板100内に絶縁破壊を生じさせるような大きな電位差が発生しないようにする(S5)。

【0093】

プローバー2が基板100に載置され、コンタクトピン2bが電極100aに接触し、給電ピン11aが電極11bに接触したことを検出し、タイマー19bの計時を開始する。プローバー2が基板100に載置されたことの検出は、例えば、載置検出部18においてセンサ18bがピン18aの移動を検出することで行うことができる。前記検出は、載置検出部18によらず他の検出手段を用いることができる。例えば、給電ピン11aと電極11bとの接触を検出し、この検出信号を用いる構成、プローバーフレーム2aとステージ4との距離を検出し、この距離に基づいて検出する構成等としても良い(S6)。

【0094】

タイマー19bの計時時間があらかじめ定めておいた所定時間を経過した時点で、切り替え回路19aに接続を切り替える切り替え信号を出力する。所定時間は、基板の帯電電荷が放電用抵抗を介して放電されるに要する放電時間を予め想定しておき、この放電時間に基づいて定めることができる。切り替え回路19aの接続を切り替えるタイミングを、放電が終了する時点より後とすることによって、放電電流が基板検査信号部12に流入して基板検査信号部12が電気的に破壊されることを防ぐことができる(S7)。

【0095】

切り替え回路19aは、タイマー19bからの切り替え信号を受けて、放電用抵抗16aから基板検査信号部12に接続を切り替える。図5(c)は切り替え回路19aを放電用抵抗16aから基板検査信号部12に接続を切り替えた状態を示している。(S8)。

【0096】

基板検査信号部12に接続を切り替えることによって、基板検査信号部12から電極11b、給電ピン11a、配線2c、コンタクトピン2bを介して基板100の電極100aに接続される給電回路が形成され、基板検査信号部12は形成された給電回路を通して検査信号を基板100の各パネルに給電する(S9)。

【0097】

検査信号を基板のパネルに給電した状態において、電子線等を走査して検出信号を検出する(S10)。

【0098】

[第2の形態]

次に、本願発明のTFTアレイ検査装置の第2の形態について説明する。図6は第2の形態を説明するための概略図であり、図7は第2の形態のプローバー、給電部、放電部の構成を説明するための概略図であり、図8,9は第2の形態の動作例を説明するためのフローチャートおよび動作説明図である。

【0099】

図6において、TFTアレイ検査装置1は、図2に示した第1の形態と同様に、基板100を検査するメインチャンバ1A、基板100をメインチャンバ1Aとの間で搬送する搬送チャンバ1B、およびメインチャンバ1Aと搬送チャンバ1Bとの間を密封自在に開閉するゲートドア1Cを備える。

【0100】

搬送チャンバ1B内には、基板100を載置した状態で搬送する搬送部17を備える。搬送部17は、基板100を搬送するパレット17a、およびパレット17a上に設けられた絶縁体17bを備え、パレット17aと載置する基板100との間の絶縁体17bを設けることによって、基板100に帯電する電荷の放電を防ぎ、絶縁破壊の発生を防ぐ構成としている。

【0101】

メインチャンバ1A内には、基板100を載置するステージ4と、基板100に検査信号を供給するプローバー2を備える。ステージ4は、X方向あるいはY方向に移動する第1のステージ4aおよび第2のステージ4bを備える。第1のステージ4aと第2のステージ4bとの間には絶縁物4cを設け、基板100を載置する側の第1のステージ4aはステージ用放電抵抗4dを介して接地されている。第1のステージ4aは絶縁物4cによって絶縁することによって基板100からの帯電電荷の放電を防いでいる。

【0102】

また、第1のステージ4aはステージ用放電抵抗4dを介して接地する構成とする。この構成とすることで、基板100の撓みによってステージ4aと接触し、接触部位から放電が発生して部分的に絶縁破壊を生じさせるような電位差が発生する事態が生じたとしても、放電時の放電速度を低下させることによって基板100内の電位差を低減して絶縁破壊の発生を抑制する。

【0103】

プローバー2は、プローバーフレーム2aを有し、基板100の電極100aと電気的に接触するコンタクトピン2bと、検査信号の供給を受ける給電ピン11aを備える。プローバー2側とステージ4側は、検査信号の供給を受けるための構成として給電部11を備える。給電部11は、プローバー2側の構成として給電ピン11aからなるプローバー側給電部11Aを備え、ステージ4側の構成として電極11bからなるステージ側給電部11Bを備える。

【0104】

第2の形態では、給電部11を介して検査信号を供給し、プローバー2を介して帯電電荷を放電する構成であり、プローバー2の基板100への移動に伴って、はじめにプローバー2を介して基板の帯電電荷を放電用抵抗16aを通して接地に放電し、次に、検査信号を給電部11およびプローバー2を介して基板に供給する。

【0105】

帯電電荷の放電と検査信号の供給の切り替えは、プローバー2の基板100への移動に伴って、はじめにプローバー2のコンタクトピン2bを基板100の電極100aに電気的に接触させて放電回路を形成し、次に、プローバー2の給電ピン11aを給電部11の電極11bに電気的に接触させて給電回路を形成することで行う。

【0106】

放電時には、コンタクトピン2bは基板100の電極100aに電気的に接触するが、給電ピン11aは電極11bに電気的に接触していないため、基板100に帯電する電荷は、コンタクトピン2b、配線2c、および放電部16を介して接地される放電回路が形成され、帯電電荷は放電部16の放電用抵抗16aを通して放電される。

【0107】

さらに、プローバー2が基板100側に移動して、給電ピン11aが電極11bに電気的に接触すると、基板検査信号部12から電極11b、給電ピン11a、配線2c、およびコンタクトピン2bへの給電回路が形成され、基板検査信号部12からの検査信号は、給電部11、配線2c、およびコンタクトピン2bを介して基板100の各パネルに供給される。

【0108】

なお、配線2cには放電用抵抗16aが接続されているため、給電ピン11aが電極11bと電気的に接続した場合には、基板検査信号部12から出力された検査信号は、コンタクトピン2bと電極100aとの接続を通して基板100に供給される他に、配線2cを介して放電用抵抗16aにも流れる経路が考えられる。しかしながら、放電用抵抗16aの電気抵抗は、コンタクトピン2bおよび電極100aを介して形成される回路中の電気抵抗よりも十分に高くすることによって、放電用抵抗16aに流れる経路は実質的に絶縁された状態と見なすことができ、基板検査信号は基板100に供給されるとして扱うことができる。

【0109】

帯電電荷の放電と検査信号の供給との切り替えは、コンタクトピン2bが基板100の電極100aに電気的に接触するタイミングと、給電部11において給電ピン11aが電極11bに電気的に接触するタイミングとの時間差によって行われる。コンタクトピン2bが給電ピン11aよりも先に電極に接触させる構成として、例えば、コンタクトピン2bと給電ピン11aのピンの長さ、および基板100の電極100aとステージ側給電部11Bの電極11bの、プローバー2の移動方向における位置関係によって、コンタクトピン2bが給電ピン11aよりも先に電極に接触するように設定する。

【0110】

コンタクトピン2bが電極100aに接触した後、プローバー2がさらに基板方向に移動して給電ピン11aが電極11bに接触するまで、および接触した状態においても、コンタクトピン2bは電極100aと接触した状態を保持する。

【0111】

ここで、コンタクトピン2bをスプリング等によって弾性的に保持する構成として接触状態を保持すると共に、先端が電極100aに当接したコンタクトピン2bがプローバー2の移動に伴って湾曲あるいは破損しないようにすることができる。

【0112】

制御部10は、メインチャンバへ基板を搬送する工程、メインチャンバ内に配置された基板にプローバーを配置する工程、放電工程、検査信号を供給して基板検査を行う工程等の各工程を行う制御プログラムを格納し、この制御プログラムに従って各工程を行う。

【0113】

図7は、第2の形態が備えるプローバー2、給電部11、および放電部16の構成例を示している。

【0114】

プローバー2は、基板100の電極100aと電気的に接触するコンタクトピン2bと、給電部11において電極11bと電気的に接触する給電ピン11aと、コンタクトピン2bと給電ピン11aとを接続するプローバーフレーム2aに配設された配線2cとを備える。給電ピン11aはプローバー側給電部11Aを構成し、電極11bはステージ側給電部11Bを構成している。

【0115】

コンタクトピン2bと給電ピン11aとを接続する各配線2cには放電部16の放電用抵抗16aが接続され、放電用抵抗16aの他端は接地されている。プローバー2を基板100に載置して、コンタクトピン2bを基板100の電極100aに電気的に接触させると、電極100aから、コンタクトピン2b、配線2c、および放電用抵抗16aを介して接地される放電回路が形成される。

【0116】

一方、電極11bには基板検査信号部12が接続されている。プローバー2を基板100に載置して、給電ピン11aを電極11bに電気的に接触させると、基板検査信号部12から、電極11b、給電ピン11a、配線2c、コンタクトピン2b、および電極100aを介して基板100のパネルにつながる給電回路が形成される。

【0117】

したがって、放電時には、基板100の帯電電荷は、基板100の電極100aからコンタクトピン2b、配線2cを通って放電用抵抗16aにつながる放電回路を介して接地に放電される。

【0118】

一方、検査信号の供給時には、検査信号は、基板検査信号部12から電極11b、給電ピン11a、配線2c、コンタクトピン2bを通って100の電極100aにつながる給電回路を通って基板100の各パネルに供給される。

【0119】

本願発明のTFTアレイ検査装置の第2の形態の動作例について、図8のフローチャートおよび動作説明図を用いて説明する。

【0120】

ステージ4上に基板100を搬送して載置した後(S11)、プローバー2を基板100に移動する。図9(a)はプローバー2を基板100に載置する前の状態を示している (S12)。

【0121】

プローバー2の移動によって、プローバー2のコンタクトピン2bは基板100の電極100aに接触する。これによって、電極100aからコンタクトピン2b、配線2c、および放電用抵抗16aを介して接地に接続される放電回路が形成される。図9(b)は、プローバー2が基板100に載置された状態を示している(S13)。

【0122】

この放電回路の形成によって、基板100に帯電した電荷は放電用抵抗16aを介して接地に放電される。放電用抵抗16aは例えば、100MΩ程度の高い電気抵抗とすることによって、放電速度を抑えると共に、コンタクトピン2bが接触する基板100の電位降下を抑え、基板100内に絶縁破壊を生じさせるような大きな電位差が発生しないようにする(S14)。

【0123】

プローバー2を基板100側に更に移動させ(S15)、給電ピン11aをステージ側給電部11Bの電極11bに接触させる(S16)。これによって、基板検査信号部12から電極11b、給電ピン11a、配線2c、コンタクトピン2bを介して基板100の電極100aに接続される給電回路が形成され、基板検査信号部12は形成された給電回路を通して検査信号を基板100の各パネルに給電する(S17)。

【0124】

検査信号を基板のパネルに給電した状態において、電子線等を走査して検出信号を検出する(S18)。

【産業上の利用可能性】

【0125】

本発明は、TFT基板は液晶基板や有機ELとすることができ、液晶基板や有機ELを形成する成膜装置の他、種々の半導体基板を形成する成膜装置に適用することができる。

【符号の説明】

【0126】

1 TFTアレイ検査装置

1A メインチャンバ

1B 搬送チャンバ

1C ゲートドア

2 プローバー

2a プローバーフレーム

2b コンタクトピン

2c 配線

3 プローバーリフター

4 ステージ

4a 第1のステージ

4b 第2のステージ

4c 絶縁物

4d ステージ用放電抵抗

5 電子銃

6 検出器

10 制御部

11 給電部

11A プローバー側給電部

11B ステージ側給電部

11a 給電ピン

11b 電極

12 基板検査信号部

13 プローバーリフター駆動制御部

14 ステージ駆動制御部

15 電子線走査制御部

16 放電部

16a 放電用抵抗

17 搬送部

17a パレット

17b 絶縁体

18 載置検出部

18a ピン

18b センサ

19 切り替え部

19a 切り替え回路

19b タイマー

20 信号処理部

30 欠陥検出部

100 基板

100a 電極

101 パネル

【技術分野】

【0001】

本発明は、液晶基板等のTFT基板のアレイを検査するTFTアレイ検査装置に関し、特に、基板の帯電を除電する機構を有するTFTアレイ検査装置に関する。

【背景技術】

【0002】

液晶アレイ検査装置等のTFTアレイ検査装置において、液晶基板等の基板上を撮像して得られる撮像画像として、光学的に撮像して得られる光学撮像画像、あるいは、電子ビームやイオンビーム等の荷電ビームを基板上で二次元的に走査して得られる走査画像を用いることができる。

【0003】

TFTディスプレイ装置に用いるTFTアレイ基板の製造工程では、製造されたTFTアレイ基板が正しく駆動するかの検査が行われる(特許文献1,2)。

【0004】

例えば、検査対象である基板のTFTアレイに検査信号を印加してTFTアレイに付随した透明電極を所定電位状態とし、基板上に電子ビームやイオンビーム等の荷電ビームを二次元的に照射して走査し、このビーム走査で得られる走査画像に基づいてTFTアレイを検査するTFTアレイ検査装置が知られている。TFTアレイ検査では、例えば、電子線の照射によって放出される二次電子をフォトマルチプライヤなどによって電気信号に変換して検出し、この検出信号の信号強度に基づいてアレイ欠陥を判定している。

【0005】

基板のTFTアレイとピクセルは対応して形成されており、TFTアレイに駆動信号を印加することによって特定のピクセルを駆動することができる。TFTアレイ検査において、一般に、TFTアレイに所定パターンの駆動信号を印加し、基板内に形成されたパネルの各ピクセルを所定パターンで駆動し、これらのピクセルに電子線を照射し、照射点から放出される二次電子を検出する。この電子線照射をパネル内で走査して行うことによって、パネル内の各ピクセルから検出信号を取得している。

【0006】

TFTアレイの欠陥は、例えば、取得した検出信号の信号強度を、所定パターンの駆動信号で駆動した際に正常なTFTアレイから得られる検出信号の信号強度と比較することによって検出することができる。

【0007】

基板不良として、プロセスに起因する不良の他、静電気に起因する不良が指摘されている(例えば、特許文献3参照)。

【0008】

基板の製造ライン上において基板を搬送する際に、接触や摩擦等の種々の要因によって静電気が発生して帯電する場合がある。基板に対する各種処理工程において帯電した基板が処理装置と接触すると、基板と処理装置との間の電位差によって過剰電流が流れ、基板上に形成あるいは装着された電子部品が絶縁破壊(ESD)される場合がある。

【0009】

このような絶縁破壊を防止する方法として、搬送路上にイオナイザ(帯電中和装置)を配置し、搬送される基板にイオナイザで生成したイオンを放射することによって、基板に帯電する電荷を除電することが提案されている(例えば、特許文献4,5参照)。

【0010】

また、装置内に収納された基板と装置とが接触する箇所に絶縁処理を施すことによって放電の発生を抑制することも行われている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2004−271516号公報

【特許文献2】特開2004−309488号公報

【特許文献3】特開2000−206177号公報(段落[0003],段落[0010],段落[0013])

【特許文献4】特開2001−60609号公報

【特許文献5】特開2002−232189号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

絶縁破壊を防ぐ方法として、上記したイオナイザ(帯電中和装置)を用いる方法では、除電に時間を要するという問題があり、除電時間を十分にとることができない場合には除電が不十分となり、搬送先の装置内において絶縁破壊が発生するという問題が生じる。基板をインラインで製造する場合には、製品のスループットを高めるためにライン上に設けられた各処理工程での処理時間を短縮することが求められているため、イオナイザによる除電は最適とは言えない場合がある。

【0013】

基板上に形成されたTFTアレイを検査するTFTアレイ検査工程を含むライン処理においても、全体の処理時間の短縮要求から搬送に要する時間についても短縮することが求められる。そのため、イオナイザによる除電の時間を十分にとることができず、除電を十分に行うことができない。

【0014】

また、装置内において絶縁体によって放電を防ぐ処置が考えられる。この処置では、基板が帯電した状態のままで処理が行われ、その後、帯電したまま装置から搬送されることになるため、後工程において絶縁破壊が発生するおそれがあるという問題がある。

【0015】

基板を接地させることによって、基板に帯電した電荷を放電させることができる。しかしながら、基板を接地させることによって基板の帯電電荷を短時間で放電させると、基板内の電位が不均一となり基板内に電位差が生じることになる。この電位差が絶縁破壊電圧を超えると、放電現象と同様に絶縁破壊が発生する。

【0016】

そこで、本発明は上記課題を解決して、TFTアレイ検査装置において、基板内で絶縁破壊を生じさせることなく、基板に帯電した電荷を放電することを目的とする。

【0017】

また、基板内で絶縁破壊を生じさせることなく、かつ、短時間で基板に帯電した電荷を放電することを目的とし、また、後工程において絶縁破壊が発生することを防ぐことを目的とする。

【課題を解決するための手段】

【0018】

本願発明は、プローバーを基板に載置し、プローバーを介して検査信号を基板に供給し、基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、TFTアレイ検査時にプローバーを基板に載置した際に、基板をプローバーを介して高い電気抵抗の放電用抵抗に接続し、この放電用抵抗を介して接地することによって、基板の帯電電荷の放電速度を抑制した放電させる。

【0019】

基板に帯電する電荷を、基板からプローバーを介して放電用抵抗に導くことによって、TFTアレイ検査装置内において格別な機構を設けることなく基板に帯電する電荷を放電することができる。

【0020】

また、高い電気抵抗の放電用抵抗を介して接地することによって、放電時に基板内に生じる電位差を低減させて、発生した電位差が絶縁破壊電圧を超えないようにすることで絶縁破壊の発生を抑制することができる。

【0021】

本願発明のTFTアレイ検査装置は、基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、基板検査を行うための検査信号を出力する基板検査信号部と、基板にコンタクトピンを電気的な接触させ、検査信号を基板に印加するプローバーと、基板検査信号部が出力する検査信号をプローバーに供給する給電部と、基板に帯電する電荷をプローバーを介して接地に放電する放電部とを備える。

【0022】

本発明の放電部は、コンタクトピンとアースとの間を高い電気抵抗で接続する放電用抵抗を備える。

【0023】

TFTアレイ検査装置は、基板上に形成されたTFTアレイを検査する際に、プローバーを基板に配置して、プローバーから基板に検査信号を印加する。本発明のTFTアレイ検査装置は、プローバーを基板に配置してコンタクトピンを基板の電極に電気的に接触させ、給電部が基板検査信号部から入力した検査信号を、コンタクトピンと基板の電極の電気的接触を通して基板に供給する。

【0024】

本発明のプローバーは、検査信号の供給に先立って、基板に帯電する電荷を、コンタクトピンと基板の電極との電気的接触を通して基板から放電部に導く。放電部は、プローバーを介して導かれた電荷を、放電用抵抗を通して接地に放電する。放電用抵抗は高い電気抵抗を有しているため、放電時に流れる電流値は低い値に抑制され、基板内に生じる電位差は低減される。

【0025】

基板内に生じる電位差を低減することによって、基板内の電位差が絶縁破壊電圧を越えることによる絶縁破壊の発生を抑制する。

【0026】

本願発明のTFTアレイ検査装置は、プローバーを介して基板に検査信号を供給すると共に、プローバーを介して基板の帯電を放電する。この放電電流が基板検査信号部に流入し、絶縁破壊によって基板検査信号部内の信号発生回路等が破損することを避けるために、プローバーへの検査信号の供給とプローバーを介して行う帯電電荷の放電とを分離して行う構成を備える。

【0027】

本願発明のTFTアレイ検査装置は、プローバーへの検査信号の供給とプローバーを介して行う帯電電荷の放電とを分離して行う構成として2つの形態を備える。

【0028】

本願発明のTFTアレイ検査装置の第1の形態は、プローバーの給電ピンを、放電用抵抗と基板検査信号部との間で切り替えて接続する切り替え回路を備える。

【0029】

本発明の切り替え回路は、プローバーの給電ピンを放電用抵抗に切り替える動作によって、基板に帯電する電荷を放電用抵抗を介して接地に放電する。一方、本発明の切り替え回路は、プローバーの給電ピンを基板検査信号部に切り替える動作によって、検査用信号を給電ピンおよびコンタクトピンを介して基板に供給する。

【0030】

本発明の切り替え回路は、はじめに放電用抵抗側に接続を切り替えておくことによって、基板に帯電する電荷を放電し、放電が完了した後、基板検査信号部側に接続を切り替えることによって、プローバーに検査信号を供給する。

【0031】

本発明の切り替え回路において、放電用抵抗側への接続に続いて基板検査信号部側への接続を行う接続の動作は、複数の形態で行うことができる。

【0032】

接続動作を定める一形態は、切り替え回路において、給電ピンとの接続を放電用抵抗から基板検査信号部へ切り替える動作を、基板の帯電電荷の放電が放電用抵抗を介して開始した後、所定時間が経過した時点で行う。この動作によって、はじめに基板からの帯電電荷の放電を行い、次にプローバーに検査信号を供給する。

【0033】

基板の帯電電荷の放電が放電用抵抗を介して開始した後、所定時間が経過した時点を定める形態は、タイマーによって経過時間を計時して定める形態、あるいは、TFTアレイ検査装置において予め定められた制御プログラムに基づいてデフォルトの時間経過により定める形態とすることができる。

【0034】

タイマーによる経過時間の計時によって切り替え時点を定める形態では、切り替え回路によって放電と検査信号の供給の切り替えを行うTFTアレイ検査装置において、給電部は、プローバーに設けたプローバー側給電部と、基板を載置するステージに設けたステージ側給電部とを備え、放電部は切り替え信号を出力するタイマーを備える。タイマーは、プローバー側給電部とステージ側給電部との接触に基づいて計時を開始し、予め定められた所定時間が経過した後に切り替え信号を出力する。

【0035】

上記した給電部および放電部を備える構成において、プローバーが基板に載置されたことを、プローバー側給電部とステージ側給電部との接触に基づいて検出し、タイマーはこの接触検出に基づいて計時を開始し、予め設定された時間が経過した時点で、切り替え信号を出力する。

【0036】

切り替え回路は、タイマーが出力する切り替信号に基づいて、給電ピンとの接続を放電用抵抗から基板検査信号部へ切り替える動作を行う。

【0037】

制御プログラムに基づいてデフォルトの時間経過により定める形態では、基板の検査を行うメインチャンバへ基板を搬送する工程、メインチャンバ内に配置された基板にプローバーを配置する工程、放電工程、検査信号を供給して基板検査を行う工程等の各工程を行うプログラムにおいて、基板配置工程の終了した後、基板の放電に要する時間に所定の余裕時間を加味した時間を検査信号の供給時点として設定する。

【0038】

本願発明のTFTアレイ検査装置の第2の形態は、第1の形態の切り替え回路を用いることなく、コンタクトピンと放電用抵抗との接続と、給電ピンと基板検査信号部との接続との接続を、プローバーの基板側への移動に伴って、時間差を伴って順に行うことによって、プローバーを介して行う帯電電荷の放電と、プローバーを介して行う検査信号の供給とを分離して行う。

【0039】

第2の形態において、放電部は、放電用抵抗の一端を接地し、他端をコンタクトピンと給電ピンとの間に接続する。この放電用抵抗の接続によってコンタクトピンと放電用抵抗とを接続する第1の接続回路と、コンタクトピンと給電ピンと基板検査信号部とを接続する第2の接続回路とを備える。

【0040】

第1の接続回路と第2の接続回路の各接続は、プローバーの移動に伴って順次行う。第1の接続回路は、基板に帯電する電荷を、コンタクトピンから放電用抵抗を介して接地に放電し、第2の接続回路は、検査用信号を、給電ピンおよびコンタクトピンから基板に供給する。

【0041】

また、給電部は、プローバーに設けたプローバー側給電部と、基板を載置するステージに設けたステージ側給電部とを有する。プローバー側給電部はコンタクトピンと接続された給電ピンを備え、ステージ側給電部は給電ピンと電気的に接触するための電極を備える。プローバーの移動に伴って、コンタクトピンと基板側の電極との電気的接触を、給電ピンとステージ側給電部との電極との電気的接触よりも先行させるように、給電ピンおよびコンタクトピンと配置する。この配置により、プローバーが基板方向に移動すると、コンタクトピンと基板側の電極とが先に電気的に接触し、第1の接続回路の接続によってコンタクトピンと放電用抵抗とを接続し、基板に帯電する電荷を放電用抵抗を介して接地に放電する。

【0042】

さらに、プローバーが基板方向に移動すると、給電ピンとステージ側給電部の電極とが電気的に接触し、第2の接続回路によってコンタクトピンと基板検査信号部とを接続し、検査用信号を基板に供給する。

【0043】

前記した給電ピンとコンタクトピンの配置は、例えば、コンタクトピンの長さを給電ピンの長さよりも長く設定することで実現することができる。なお、給電ピンおよびコンタクトピンは、各ピンをスプリング等の弾性部材によって弾性的に保持することによって、コンタクトピンは電極に接触した後、所定のストローク分だけ押し込まれるため、プローバーの移動に伴って、給電ピンが電極を押圧することによる支障を解消することができる。

【0044】

第2の形態によれば、プローバーと基板とが接触する時間を、タイマーやプログラムによって定める構成を不要とすることができる。

【0045】

さらに、本願発明のTFTアレイ検査装置が備えるステージは、ステージ用放電抵抗を介して接地する構成とすることができる。ステージ用放電用抵抗を介して接地することによって、ステージに帯電する電荷が放電した際に、このステージ上に載置される基板に発生する絶縁破壊を防ぐ。

【0046】

さらに、本願発明のTFTアレイ検査装置が備える基板搬送装置は、基板を載置する搬送用パレットを備え、この搬送用パレットは基板を載置する側に絶縁体を有し、絶縁体を介して基板と接触する構成とすることができる。搬送用パレットと基板との間に絶縁体を設けることによって、基板に帯電する電荷が搬送用パレットを介して放電しないようにし、搬送パレットに載置された基板に発生する絶縁破壊を防ぐ。

【発明の効果】

【0047】

本発明によれば、TFTアレイ検査装置において、基板内で絶縁破壊を生じさせることなく、基板に帯電した電荷を放電することができる。

【0048】

また、本発明によれば、基板内で絶縁破壊を生じさせることなく、かつ、短時間で基板に帯電した電荷を放電することができ、また、後工程において絶縁破壊が発生することを防ぐことができる。

【図面の簡単な説明】

【0049】

【図1】本発明のTFTアレイ検査装置の構成を説明するための図である。

【図2】本発明のTFTアレイ検査装置の第1の形態を説明するための概略図である。

【図3】本発明のTFTアレイ検査装置の第1の形態のプローバー、給電部、放電部の構成を説明するための概略図である。

【図4】本発明のTFTアレイ検査装置の第1の形態の動作例を説明するためのフローチャートである。

【図5】本発明のTFTアレイ検査装置の第1の形態の動作例を説明するための動作説明図である。

【図6】本発明のTFTアレイ検査装置の第2の形態を説明するための概略図である。

【図7】本発明のTFTアレイ検査装置の第2の形態のプローバー、給電部、放電部の構成を説明するための概略図である。

【図8】本発明のTFTアレイ検査装置の第2の形態の動作例を説明するためのフローチャートである。

【図9】本発明のTFTアレイ検査装置の第2の形態の動作例を説明するための動作説明図である。

【発明を実施するための形態】

【0050】

以下、本発明の実施の形態について図を参照しながら詳細に説明する。以下では、図1を用いて本発明のTFTアレイ検査装置の構成を説明し、本発明の第1の形態に対応する実施例を図2〜図5を用いて説明し、本発明の第2の形態に対応する実施例を図6〜図9を用いて説明する。

【0051】

はじめに、図1を用いて本発明のTFTアレイ検査装置の一構成例を説明する。なお、図1はTFTアレイ検査装置の内、主に基板検査を行う構成について示している。図1に示す構成例では、液晶基板等のTFT基板に電子線を照射し、TFT基板から放出される二次電子を検出し、二次電子の検出信号から信号画像を形成し、この信号画像に基づいて欠陥検出を行う構成例を示している。本発明は、検査対象の基板は液晶基板に限らず、また、基板走査は電子線に限らずイオンビーム等の荷電ビームとすることができる。また、検出信号は照射する荷電ビームに依存し、二次電子に限られるものではない。

【0052】

図1において、TFTアレイ検査装置1は、液晶基板等の基板100を載置すると共にXY方向に移動自在とするステージ4と、基板100上に形成されたパネル101のアレイ(図示していない)に検査信号を印加するプローバー2と、プローバー2のプローバーフレーム2aを上下方向に昇降駆動するプローバーリフター3と、ステージ4の上方位置に配置した電子銃5と、基板100のパネル101のピクセル(図示していない)から放出される二次電子を検出する検出器6とを備える。電子銃5および検出器6は複数の組みを設けることができる。検査信号は、基板検査信号部12で生成され、プローバー2を介して基板100のパネル101に供給される。

【0053】

基板検査信号部12からプローバー2への検査信号の供給は、給電部11を介して行われる。給電部11は、プローバー2側に設けたプローバー側給電部11Aとステージ4側に設けたステージ側給電部11Bとによって構成される。

【0054】

プローバー側給電部11Aは給電ピン11aを備え、プローバーフレーム2aに設けられる。給電ピン11aは、プローバーフレーム2aに配設された配線2cを通してコンタクトピン2bに接続される。コンタクトピン2bは、プローバー2の移動によって基板100に設けられた電極と電気的に接触し、検査信号を基板100の各パネル101に供給する。

【0055】

ステージ側給電部11Bは電極11bを備え、ステージ4あるいはTFTアレイ検査装置1の固定側に設けられる。電極11bは、基板検査信号部12と直接あるいは間接に接続されており、プローバー2をステージ4側に移動させ、給電ピン11aを電極11bに電気的に接触させることによって、基板検査信号部12からプローバー2へ検査信号を供給する。なお、図1には給電ピン11aおよび電極11bは図示していない。

【0056】

本発明のTFTアレイ検査装置1は、基板100に帯電する電荷を放電する放電部16を備える。放電部16は一端を接地した放電用抵抗16aを備え、放電用抵抗16aを通して基板100に帯電する電荷を放電する。

【0057】

放電用抵抗16aの他端は、プローバーフレーム2aに配設された配線2cあるいは給電部11に接続され、コンタクトピン2bが基板100の電極100a(図示していない)に接触した際に、電極100a、コンタクトピン2b、配線2c、および放電用抵抗16aをつなぐ放電回路が形成され、基板100の帯電電荷は放電回路を通して接地に放電される。

【0058】

放電用抵抗16aは高い電気抵抗を有しており、電荷が流れる際に放電用抵抗16aの両端に電圧降下が発生する。放電用抵抗16aの一端は接地しているため、放電用抵抗16aの他端側には電圧降下分の電圧が発生し、プローバー2を介して接続される基板100の電位は、放電用抵抗16aの電圧降下分だけ高くなる。この電位の発生によって、基板100内に発生する電位差は短絡した場合の電位差と比較して小さくなる。これによって、基板100内の電位差を、絶縁破壊が発生する電位差よりも下げることができる。

【0059】

放電部16とプローバーフレーム2aの配線2cとを接続する構成は、給電部11を介して接続する構成とする他に、給電部11を介することなく直接に接続する構成とすることができる。図1では、2つの構成を同一の図面に示しているが、何れか一方の構成によって、放電部16とプローバーフレーム2aの配線2cとの接続を行う。

【0060】

給電部11を介して接続する構成では、コンタクトピン2bおよび給電ピン11aは、基板100に検査信号を供給する給電回路を構成すると共に、基板100に帯電する電荷を放電用抵抗を介して接地に放電する放電回路を構成することになる。

【0061】

第1の形態では、図2〜図5を用いて給電部11を介して接続する構成について説明し、第2の形態では、図6〜図9を用いて給電部11を介することなく直接に接続する構成について説明する。

【0062】

ステージ駆動制御部14はステージ4の駆動を制御し、電子線走査制御部15は電子銃5が照射する電子線の照射方向を制御して、基板100上の電子線の走査を制御する。信号処理部20は、検出器6が検出する二次電子の検出信号を信号処理し信号画像を形成する。得られた信号画像の信号強度や検出位置は欠陥検出部30に送られ、欠陥位置や欠陥種の判定が行われる。欠陥検出部30は、信号処理部20から送られた信号画像の信号強度に基づいてピクセルの欠陥を検出し、検出位置によって欠陥ピクセルおよび対応する欠陥アレイを検出する。

【0063】

なお、ピクセルおよびアレイは基板のパネルに形成され、各ピクセルはアレイに対して電圧を印加することによって駆動されるため、ピクセルの欠陥検出は、そのピクセルに対するアレイ検査に対応している。

【0064】

ステージ4は、基板100を載置するとともに、ステージ駆動制御部14によってX軸方向およびY軸方向に移動自在であり、また、電子銃5から照射される電子線は電子線走査制御部15によってX軸方向あるいはY軸方向に振らせることができる。ステージ駆動制御部14および電子線走査制御部15は、単独あるいは協働動作によって電子線を基板100上で走査させ、基板100のパネル101の各ピクセルに照射させることができる。

【0065】

プローバーリフター駆動制御部13は、プローバーリフター3を駆動制御して、プローバーフレーム2aを上下方向に昇降駆動する。プローバーリフター3が上昇駆動するとプローバーフレーム2aは上方に移動して基板100から離れ、コンタクトピン2bおよび給電ピン11aの各端子は、それぞれが対向する電極との電気的な接続が解かれる。一方、プローバーリフター3が下降駆動するとプローバーフレーム2aは下方に移動して基板100に近づき、コンタクトピン2bおよび給電ピン11aの各端子はそれぞれが対向する電極と電気的に接触する。

【0066】

プローバーリフター駆動制御部13,ステージ駆動制御部14,電子線走査制御部15,信号処理部20、欠陥検出部30の各部の駆動動作は制御部10によって制御される。また、制御部10は、アレイ検査装置1の全体の動作を含む制御を行う機能を有し、これらの制御を行うCPU、およびCPUを制御するプログラムを記憶するメモリ等によって構成することができる。

【0067】

[第1の形態]

次に、本願発明のTFTアレイ検査装置の第1の形態について説明する。図2は第1の形態を説明するための概略図であり、図3は第1の形態のプローバー、給電部、放電部の構成を説明するための概略図であり、図4,5は第1の形態の動作例を説明するためのフローチャートおよび動作説明図である。

【0068】

図2において、TFTアレイ検査装置1は、基板100を検査するメインチャンバ1A、基板100をメインチャンバ1Aとの間で搬送する搬送チャンバ1B、およびメインチャンバ1Aと搬送チャンバ1Bとの間を密封自在に開閉するゲートドア1Cを備える。

【0069】

搬送チャンバ1B内には、基板100を載置した状態で搬送する搬送部17を備える。搬送部17は、基板100を搬送するパレット17a、およびパレット17a上に設けられた絶縁体17bを備え、パレット17aと載置する基板100との間に絶縁体17bを設けることによって、基板100に帯電する電荷の放電を防ぎ、絶縁破壊の発生を防ぐ構成としている。

【0070】

メインチャンバ1A内には、基板100を載置するステージ4と、基板100に検査信号を供給するプローバー2を備える。ステージ4は、X方向あるいはY方向に移動する第1のステージ4aおよび第2のステージ4bを備える。第1のステージ4aと第2のステージ4bとの間には絶縁物4cを設け、基板100を載置する側の第1のステージ4aはステージ用放電抵抗4dを介して接地されている。第1のステージ4aは絶縁物4cによって絶縁することによって基板100からの帯電電荷の放電を防いでいる。

【0071】

また、第1のステージ4aはステージ用放電抵抗4dを介して接地する構成とする。この構成とすることで、基板100の撓みによってステージ4aと接触し、接触部位から放電が発生して部分的に絶縁破壊を生じさせるような電位差が発生する事態が生じたとしても、放電時の放電速度を低下させることによって基板100内の電位差を低減して絶縁破壊の発生を抑制する。

【0072】

プローバー2は、プローバーフレーム2aを有し、基板100の電極100aと電気的に接触するコンタクトピン2bと、検査信号の供給を受ける給電ピン11aを備える。プローバー2側とステージ4側は、検査信号の供給を受けるための構成として給電部11を備える。給電部11は、プローバー2側の構成として給電ピン11aを有するプローバー側給電部11Aを備え、ステージ4側の構成として電極11bを有するステージ側給電部11Bを備える。

【0073】

第1の形態では、検査信号の供給と帯電電荷の放電とを給電部11を介して行うと共に、切り替え部19によって検査信号の供給と帯電電荷の放電とを切り替える。

【0074】

切り替え部19は、通常は放電部16側に接続しておき、検査時において放電が終了した後、基板検査信号部12側に切り替える。

【0075】

放電時には、切り替え部19は放電部16側に接続されているため、基板100に帯電する電荷は、コンタクトピン2b、配線2c、給電部11、および切り替え部19を介して放電部16に導かれ、放電部16の放電用抵抗16aを通して接地される。

【0076】

一方、検査時には、切り替え部19は放電部16を切り離して給電部11に接続を切り替えることによって、基板検査信号部12からの検査信号は、切り替え部19,給電部11、配線2c、およびコンタクトピン2bを介して基板100に供給される。

【0077】

切り替え部19は切り替え回路19aとタイマー19bを備え、切り替え回路19aはタイマー19bの切り替え信号に基づいて放電部16から基板検査信号部12に接続を切り替える。タイマー19bは、プローバー2が基板100に載置されてから所定時間が経過した時点で切り替え信号を出力する。所定時間は、基板100に帯電する電荷が放電用抵抗16aを通して接地に放電されるに要する時間に応じて定めることができ、一例として2秒程度に設定される。

【0078】

給電部11は、プローバー側給電部11Aとステージ側給電部11Bを備え、プローバー2が基板100上に載置した際に、プローバー側給電部11Aの給電ピン11aとステージ側給電部11B側の電極11bとが電気的に接触することによって、プローバー2と切り替え部19との間を接続する回路を形成する。

【0079】

タイマー19bの計時の開始は、例えば、プローバー側給電部11Aとステージ側給電部11Bとの接触を検出することによって行うことができる。

【0080】

切り替え回路19aの接続切替は、タイマーによる計時時間によって行う他、制御プリグラムに基づいて行う形態とすることもできる。

【0081】

制御部10は、メインチャンバへ基板を搬送する工程、メインチャンバ内に配置された基板にプローバーを配置する工程、放電工程、検査信号を供給して基板検査を行う工程等の各工程を行う制御プログラムを格納し、この制御プログラムに従って各工程を行う。各工程処理において、基板配置工程が終了した後、基板の放電の要する時間に所定の余裕時間を加味した時間を予め設定しておき、この設定時点を検査信号の供給時点として設定することで、デフォルトの時間経過により切り替え回路の接続切替を行う。

【0082】

図3は、第1の形態が備えるプローバー2、給電部11、切り替え部19、および放電部16の構成例を示している。

【0083】

プローバー2は、基板100の電極100aと電気的に接触するコンタクトピン2bと、給電部11において電極11bと電気的に接触する給電ピン11aと、コンタクトピン2bと給電ピン11aとを接続するプローバーフレーム2aに配設された配線2cとを備える。給電ピン11aはプローバー側給電部11Aを構成し、電極11bはステージ側給電部11Bを構成している。

【0084】

切り替え部19が備える切り替え回路19aの一端には、ステージ側給電部11Bの電極11bが接続され、他方に切り替え端子には基板検査信号部12と放電部16とが接続され、通常は放電部16側に接続し、タイマー19bの切り替え信号に応じて基板検査信号部12側に接続が切り替えられる。

【0085】

タイマー19bの計時の開始は、プローバー2が基板100に載置された時点で行われ、予め定められた時間が経過した時点で切り替え信号を出力する。

【0086】

プローバー2が基板100に載置された時点の検出は、例えば、プローバー2側に設けたピン18aとステージ側に設けたセンサ18bからなる載置検出部18によって行うことができる。プローバー2が基板100に載置されると、センサ18bはピン18aの近接あるいは接触したことを検出して検出信号をタイマー19bに出力する。タイマー19bは、検出信号を受けて計時を開始する。

【0087】

切り替え部19が放電部16側に切り替えられているときには、基板100の電極100aから、コンタクトピン2b、配線2c、給電ピン11a、電極11bを通って放電用抵抗16aにつながる放電回路が形成され、基板100の帯電電荷はこの放電回路を介して接地に放電される。

【0088】

一方、切り替え部19が基板検査信号部12側に切り替えられているときには、基板検査信号部12から、電極11b、給電ピン11a、配線2c、コンタクトピン2bを通って100の電極100aにつながる給電回路が形成され、検査信号はこの給電回路を通って基板100の各パネルに供給される。

【0089】

本願発明のTFTアレイ検査装置の第1の形態の動作例について、図4のフローチャートおよび動作説明図を用いて説明する。

【0090】

切り替え回路19aは放電用抵抗16a側に接続を切り替え、ステージ側給電部11Bの電極11bと放電用抵抗16aとを接続する(S1)。ステージ4上に基板100を搬送して載置した後(S2)、プローバー2を基板100に移動する。図5(a)はプローバー2を基板100に載置する前の状態を示している。この状態では、切り替え回路19aは放電用抵抗16a側に接続を切り替えられている(S3)。

【0091】

プローバー2の移動によって、プローバー2のコンタクトピン2bは基板100の電極100aに接触し、プローバー側給電部11Aの給電ピン11aはステージ側給電部11Bの電極11bに接触する。これによって、電極100aからコンタクトピン2b、配線2c、給電ピン11a、電極11b、および放電用抵抗16aを介して接地に接続される放電回路が形成される。図5(b)は、プローバー2が基板100に載置された状態を示している(S4)。

【0092】

この放電回路の形成によって、基板100に帯電した電荷は放電用抵抗16aを介して接地に放電される。放電用抵抗16aは例えば、100MΩ程度の高い電気抵抗とすることによって、放電速度を抑えると共に、コンタクトピン2bが接触する基板100の電位降下を抑え、基板100内に絶縁破壊を生じさせるような大きな電位差が発生しないようにする(S5)。

【0093】

プローバー2が基板100に載置され、コンタクトピン2bが電極100aに接触し、給電ピン11aが電極11bに接触したことを検出し、タイマー19bの計時を開始する。プローバー2が基板100に載置されたことの検出は、例えば、載置検出部18においてセンサ18bがピン18aの移動を検出することで行うことができる。前記検出は、載置検出部18によらず他の検出手段を用いることができる。例えば、給電ピン11aと電極11bとの接触を検出し、この検出信号を用いる構成、プローバーフレーム2aとステージ4との距離を検出し、この距離に基づいて検出する構成等としても良い(S6)。

【0094】

タイマー19bの計時時間があらかじめ定めておいた所定時間を経過した時点で、切り替え回路19aに接続を切り替える切り替え信号を出力する。所定時間は、基板の帯電電荷が放電用抵抗を介して放電されるに要する放電時間を予め想定しておき、この放電時間に基づいて定めることができる。切り替え回路19aの接続を切り替えるタイミングを、放電が終了する時点より後とすることによって、放電電流が基板検査信号部12に流入して基板検査信号部12が電気的に破壊されることを防ぐことができる(S7)。

【0095】

切り替え回路19aは、タイマー19bからの切り替え信号を受けて、放電用抵抗16aから基板検査信号部12に接続を切り替える。図5(c)は切り替え回路19aを放電用抵抗16aから基板検査信号部12に接続を切り替えた状態を示している。(S8)。

【0096】

基板検査信号部12に接続を切り替えることによって、基板検査信号部12から電極11b、給電ピン11a、配線2c、コンタクトピン2bを介して基板100の電極100aに接続される給電回路が形成され、基板検査信号部12は形成された給電回路を通して検査信号を基板100の各パネルに給電する(S9)。

【0097】

検査信号を基板のパネルに給電した状態において、電子線等を走査して検出信号を検出する(S10)。

【0098】

[第2の形態]

次に、本願発明のTFTアレイ検査装置の第2の形態について説明する。図6は第2の形態を説明するための概略図であり、図7は第2の形態のプローバー、給電部、放電部の構成を説明するための概略図であり、図8,9は第2の形態の動作例を説明するためのフローチャートおよび動作説明図である。

【0099】

図6において、TFTアレイ検査装置1は、図2に示した第1の形態と同様に、基板100を検査するメインチャンバ1A、基板100をメインチャンバ1Aとの間で搬送する搬送チャンバ1B、およびメインチャンバ1Aと搬送チャンバ1Bとの間を密封自在に開閉するゲートドア1Cを備える。

【0100】

搬送チャンバ1B内には、基板100を載置した状態で搬送する搬送部17を備える。搬送部17は、基板100を搬送するパレット17a、およびパレット17a上に設けられた絶縁体17bを備え、パレット17aと載置する基板100との間の絶縁体17bを設けることによって、基板100に帯電する電荷の放電を防ぎ、絶縁破壊の発生を防ぐ構成としている。

【0101】

メインチャンバ1A内には、基板100を載置するステージ4と、基板100に検査信号を供給するプローバー2を備える。ステージ4は、X方向あるいはY方向に移動する第1のステージ4aおよび第2のステージ4bを備える。第1のステージ4aと第2のステージ4bとの間には絶縁物4cを設け、基板100を載置する側の第1のステージ4aはステージ用放電抵抗4dを介して接地されている。第1のステージ4aは絶縁物4cによって絶縁することによって基板100からの帯電電荷の放電を防いでいる。

【0102】

また、第1のステージ4aはステージ用放電抵抗4dを介して接地する構成とする。この構成とすることで、基板100の撓みによってステージ4aと接触し、接触部位から放電が発生して部分的に絶縁破壊を生じさせるような電位差が発生する事態が生じたとしても、放電時の放電速度を低下させることによって基板100内の電位差を低減して絶縁破壊の発生を抑制する。

【0103】

プローバー2は、プローバーフレーム2aを有し、基板100の電極100aと電気的に接触するコンタクトピン2bと、検査信号の供給を受ける給電ピン11aを備える。プローバー2側とステージ4側は、検査信号の供給を受けるための構成として給電部11を備える。給電部11は、プローバー2側の構成として給電ピン11aからなるプローバー側給電部11Aを備え、ステージ4側の構成として電極11bからなるステージ側給電部11Bを備える。

【0104】

第2の形態では、給電部11を介して検査信号を供給し、プローバー2を介して帯電電荷を放電する構成であり、プローバー2の基板100への移動に伴って、はじめにプローバー2を介して基板の帯電電荷を放電用抵抗16aを通して接地に放電し、次に、検査信号を給電部11およびプローバー2を介して基板に供給する。

【0105】

帯電電荷の放電と検査信号の供給の切り替えは、プローバー2の基板100への移動に伴って、はじめにプローバー2のコンタクトピン2bを基板100の電極100aに電気的に接触させて放電回路を形成し、次に、プローバー2の給電ピン11aを給電部11の電極11bに電気的に接触させて給電回路を形成することで行う。

【0106】

放電時には、コンタクトピン2bは基板100の電極100aに電気的に接触するが、給電ピン11aは電極11bに電気的に接触していないため、基板100に帯電する電荷は、コンタクトピン2b、配線2c、および放電部16を介して接地される放電回路が形成され、帯電電荷は放電部16の放電用抵抗16aを通して放電される。

【0107】

さらに、プローバー2が基板100側に移動して、給電ピン11aが電極11bに電気的に接触すると、基板検査信号部12から電極11b、給電ピン11a、配線2c、およびコンタクトピン2bへの給電回路が形成され、基板検査信号部12からの検査信号は、給電部11、配線2c、およびコンタクトピン2bを介して基板100の各パネルに供給される。

【0108】

なお、配線2cには放電用抵抗16aが接続されているため、給電ピン11aが電極11bと電気的に接続した場合には、基板検査信号部12から出力された検査信号は、コンタクトピン2bと電極100aとの接続を通して基板100に供給される他に、配線2cを介して放電用抵抗16aにも流れる経路が考えられる。しかしながら、放電用抵抗16aの電気抵抗は、コンタクトピン2bおよび電極100aを介して形成される回路中の電気抵抗よりも十分に高くすることによって、放電用抵抗16aに流れる経路は実質的に絶縁された状態と見なすことができ、基板検査信号は基板100に供給されるとして扱うことができる。

【0109】

帯電電荷の放電と検査信号の供給との切り替えは、コンタクトピン2bが基板100の電極100aに電気的に接触するタイミングと、給電部11において給電ピン11aが電極11bに電気的に接触するタイミングとの時間差によって行われる。コンタクトピン2bが給電ピン11aよりも先に電極に接触させる構成として、例えば、コンタクトピン2bと給電ピン11aのピンの長さ、および基板100の電極100aとステージ側給電部11Bの電極11bの、プローバー2の移動方向における位置関係によって、コンタクトピン2bが給電ピン11aよりも先に電極に接触するように設定する。

【0110】

コンタクトピン2bが電極100aに接触した後、プローバー2がさらに基板方向に移動して給電ピン11aが電極11bに接触するまで、および接触した状態においても、コンタクトピン2bは電極100aと接触した状態を保持する。

【0111】

ここで、コンタクトピン2bをスプリング等によって弾性的に保持する構成として接触状態を保持すると共に、先端が電極100aに当接したコンタクトピン2bがプローバー2の移動に伴って湾曲あるいは破損しないようにすることができる。

【0112】

制御部10は、メインチャンバへ基板を搬送する工程、メインチャンバ内に配置された基板にプローバーを配置する工程、放電工程、検査信号を供給して基板検査を行う工程等の各工程を行う制御プログラムを格納し、この制御プログラムに従って各工程を行う。

【0113】

図7は、第2の形態が備えるプローバー2、給電部11、および放電部16の構成例を示している。

【0114】

プローバー2は、基板100の電極100aと電気的に接触するコンタクトピン2bと、給電部11において電極11bと電気的に接触する給電ピン11aと、コンタクトピン2bと給電ピン11aとを接続するプローバーフレーム2aに配設された配線2cとを備える。給電ピン11aはプローバー側給電部11Aを構成し、電極11bはステージ側給電部11Bを構成している。

【0115】

コンタクトピン2bと給電ピン11aとを接続する各配線2cには放電部16の放電用抵抗16aが接続され、放電用抵抗16aの他端は接地されている。プローバー2を基板100に載置して、コンタクトピン2bを基板100の電極100aに電気的に接触させると、電極100aから、コンタクトピン2b、配線2c、および放電用抵抗16aを介して接地される放電回路が形成される。

【0116】

一方、電極11bには基板検査信号部12が接続されている。プローバー2を基板100に載置して、給電ピン11aを電極11bに電気的に接触させると、基板検査信号部12から、電極11b、給電ピン11a、配線2c、コンタクトピン2b、および電極100aを介して基板100のパネルにつながる給電回路が形成される。

【0117】

したがって、放電時には、基板100の帯電電荷は、基板100の電極100aからコンタクトピン2b、配線2cを通って放電用抵抗16aにつながる放電回路を介して接地に放電される。

【0118】

一方、検査信号の供給時には、検査信号は、基板検査信号部12から電極11b、給電ピン11a、配線2c、コンタクトピン2bを通って100の電極100aにつながる給電回路を通って基板100の各パネルに供給される。

【0119】

本願発明のTFTアレイ検査装置の第2の形態の動作例について、図8のフローチャートおよび動作説明図を用いて説明する。

【0120】

ステージ4上に基板100を搬送して載置した後(S11)、プローバー2を基板100に移動する。図9(a)はプローバー2を基板100に載置する前の状態を示している (S12)。

【0121】

プローバー2の移動によって、プローバー2のコンタクトピン2bは基板100の電極100aに接触する。これによって、電極100aからコンタクトピン2b、配線2c、および放電用抵抗16aを介して接地に接続される放電回路が形成される。図9(b)は、プローバー2が基板100に載置された状態を示している(S13)。

【0122】

この放電回路の形成によって、基板100に帯電した電荷は放電用抵抗16aを介して接地に放電される。放電用抵抗16aは例えば、100MΩ程度の高い電気抵抗とすることによって、放電速度を抑えると共に、コンタクトピン2bが接触する基板100の電位降下を抑え、基板100内に絶縁破壊を生じさせるような大きな電位差が発生しないようにする(S14)。

【0123】

プローバー2を基板100側に更に移動させ(S15)、給電ピン11aをステージ側給電部11Bの電極11bに接触させる(S16)。これによって、基板検査信号部12から電極11b、給電ピン11a、配線2c、コンタクトピン2bを介して基板100の電極100aに接続される給電回路が形成され、基板検査信号部12は形成された給電回路を通して検査信号を基板100の各パネルに給電する(S17)。

【0124】

検査信号を基板のパネルに給電した状態において、電子線等を走査して検出信号を検出する(S18)。

【産業上の利用可能性】

【0125】

本発明は、TFT基板は液晶基板や有機ELとすることができ、液晶基板や有機ELを形成する成膜装置の他、種々の半導体基板を形成する成膜装置に適用することができる。

【符号の説明】

【0126】

1 TFTアレイ検査装置

1A メインチャンバ

1B 搬送チャンバ

1C ゲートドア

2 プローバー

2a プローバーフレーム

2b コンタクトピン

2c 配線

3 プローバーリフター

4 ステージ

4a 第1のステージ

4b 第2のステージ

4c 絶縁物

4d ステージ用放電抵抗

5 電子銃

6 検出器

10 制御部

11 給電部

11A プローバー側給電部

11B ステージ側給電部

11a 給電ピン

11b 電極

12 基板検査信号部

13 プローバーリフター駆動制御部

14 ステージ駆動制御部

15 電子線走査制御部

16 放電部

16a 放電用抵抗

17 搬送部

17a パレット

17b 絶縁体

18 載置検出部

18a ピン

18b センサ

19 切り替え部

19a 切り替え回路

19b タイマー

20 信号処理部

30 欠陥検出部

100 基板

100a 電極

101 パネル

【特許請求の範囲】

【請求項1】

基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、

基板検査を行うための検査信号を出力する基板検査信号部と、

前記基板にコンタクトピンを電気的な接触させ、前記検査信号を基板に印加するプローバーと、

前記基板検査信号部が出力する検査信号を前記プローバーに供給する給電部と、

前記基板に帯電する電荷を前記プローバーを介して接地に放電する放電部とを備え、

前記放電部は、前記コンタクトピンと前記アースとの間を高抵抗で接続する放電用抵抗を備えることを特徴とする、TFTアレイ検査装置。

【請求項2】

前記放電部は、

前記コンタクトピンとの接続を、前記放電用抵抗と前記基板検査信号部との間で切り替える切り替え回路を備え、

前記切り替え回路が前記コンタクトピンと前記放電用抵抗とを接続する切り替え状態であるとき、前記基板に帯電する電荷を前記放電用抵抗を介して接地に放電し、

前記切り替え回路が前記コンタクトピンと前記基板検査信号部とを接続する切り替え状態であるとき、前記検査用信号を前記コンタクトピンから前記基板に供給することを特徴とする、請求項1に記載のTFTアレイ検査装置。

【請求項3】

前記切り替え回路は、

前記コンタクトピンとの接続を前記放電用抵抗から前記基板検査信号部へ切り替える動作を、前記電荷を前記放電用抵抗を介して行う放電が開始された後、所定時間を経過した後に行うことを特徴とする、請求項2に記載のTFTアレイ検査装置。

【請求項4】

前記給電部は、

前記プローバーに設けたプローバー側給電部と、前記基板を載置するステージに設けたステージ側給電部とを有し、

前記放電部は、前記プローバー側給電部と前記ステージ側給電部との接触に基づいて計時を開始し、予め定められた所定時間が経過した後に切り替え信号を出力するタイマーを有し、

前記切り替え回路は、前記タイマーが出力する切り替信号に基づいて、前記コンタクトピンとの接続を前記放電用抵抗から前記基板検査信号部へ切り替える動作を行うことを特徴とする、請求項3に記載のTFTアレイ検査装置。

【請求項5】

前記放電部は、

前記放電用抵抗の一端をアースに接続し、他端を前記コンタクトピンと前記給電部との間に接続し、前記接続によって前記コンタクトピンと前記放電用抵抗とを接続する第1の接続回路と、前記コンタクトピンと前記基板検査信号部とを接続する第2の接続回路とを備え、

前記第1の接続回路と前記第2の接続回路の各接続は、プローバーの移動に伴って順次行い、

前記第1の接続回路は、基板に帯電する電荷を、前記コンタクトピンから前記放電用抵抗を介して接地に放電し、

前記第2の接続回路は、検査用信号を、前記コンタクトピンから前記基板に供給することを特徴とする、請求項1に記載のTFTアレイ検査装置。

【請求項6】

前記給電部は、

前記プローバーに設けたプローバー側給電部と、前記基板を載置するステージに設けたステージ側給電部とを有し、

前記プローバー側給電部は前記コンタクトピンと接続された給電ピンを備え、

前記ステージ側給電部は前記給電ピンと電気的に接触するための電極を備え、

前記給電ピンおよび前記コンタクトピンは、

プローバーの移動に伴って、前記コンタクトピンと基板側の電極との電気的接触を、前記給電ピンとステージ側給電部との電極との電気的接触よりも先行させる配置であり、当該配置により前記第1の接続回路と前記第2の接続回路の各接続はプローバーの移動に伴って順次行うことを特徴とする、請求項5に記載のTFTアレイ検査装置。

【請求項7】

前記ステージはステージ用放電抵抗を介して接地することを特徴とする、請求項4又は6に記載のTFTアレイ検査装置。

【請求項8】

前記基板を搬送する基板搬送装置を備え、

前記基板搬送装置は、基板を載置する搬送用パレットを備え、当該搬送用パレットは基板を載置する側に絶縁体を有し、当該絶縁体を介して基板と接触することを特徴とする、請求項1から7の何れか一つに記載のTFTアレイ検査装置。

【請求項1】

基板上に形成されたTFTアレイを検査するTFTアレイ検査装置において、

基板検査を行うための検査信号を出力する基板検査信号部と、

前記基板にコンタクトピンを電気的な接触させ、前記検査信号を基板に印加するプローバーと、

前記基板検査信号部が出力する検査信号を前記プローバーに供給する給電部と、

前記基板に帯電する電荷を前記プローバーを介して接地に放電する放電部とを備え、

前記放電部は、前記コンタクトピンと前記アースとの間を高抵抗で接続する放電用抵抗を備えることを特徴とする、TFTアレイ検査装置。

【請求項2】

前記放電部は、

前記コンタクトピンとの接続を、前記放電用抵抗と前記基板検査信号部との間で切り替える切り替え回路を備え、

前記切り替え回路が前記コンタクトピンと前記放電用抵抗とを接続する切り替え状態であるとき、前記基板に帯電する電荷を前記放電用抵抗を介して接地に放電し、

前記切り替え回路が前記コンタクトピンと前記基板検査信号部とを接続する切り替え状態であるとき、前記検査用信号を前記コンタクトピンから前記基板に供給することを特徴とする、請求項1に記載のTFTアレイ検査装置。

【請求項3】

前記切り替え回路は、

前記コンタクトピンとの接続を前記放電用抵抗から前記基板検査信号部へ切り替える動作を、前記電荷を前記放電用抵抗を介して行う放電が開始された後、所定時間を経過した後に行うことを特徴とする、請求項2に記載のTFTアレイ検査装置。

【請求項4】

前記給電部は、

前記プローバーに設けたプローバー側給電部と、前記基板を載置するステージに設けたステージ側給電部とを有し、

前記放電部は、前記プローバー側給電部と前記ステージ側給電部との接触に基づいて計時を開始し、予め定められた所定時間が経過した後に切り替え信号を出力するタイマーを有し、

前記切り替え回路は、前記タイマーが出力する切り替信号に基づいて、前記コンタクトピンとの接続を前記放電用抵抗から前記基板検査信号部へ切り替える動作を行うことを特徴とする、請求項3に記載のTFTアレイ検査装置。

【請求項5】

前記放電部は、

前記放電用抵抗の一端をアースに接続し、他端を前記コンタクトピンと前記給電部との間に接続し、前記接続によって前記コンタクトピンと前記放電用抵抗とを接続する第1の接続回路と、前記コンタクトピンと前記基板検査信号部とを接続する第2の接続回路とを備え、

前記第1の接続回路と前記第2の接続回路の各接続は、プローバーの移動に伴って順次行い、

前記第1の接続回路は、基板に帯電する電荷を、前記コンタクトピンから前記放電用抵抗を介して接地に放電し、

前記第2の接続回路は、検査用信号を、前記コンタクトピンから前記基板に供給することを特徴とする、請求項1に記載のTFTアレイ検査装置。

【請求項6】

前記給電部は、

前記プローバーに設けたプローバー側給電部と、前記基板を載置するステージに設けたステージ側給電部とを有し、

前記プローバー側給電部は前記コンタクトピンと接続された給電ピンを備え、

前記ステージ側給電部は前記給電ピンと電気的に接触するための電極を備え、

前記給電ピンおよび前記コンタクトピンは、

プローバーの移動に伴って、前記コンタクトピンと基板側の電極との電気的接触を、前記給電ピンとステージ側給電部との電極との電気的接触よりも先行させる配置であり、当該配置により前記第1の接続回路と前記第2の接続回路の各接続はプローバーの移動に伴って順次行うことを特徴とする、請求項5に記載のTFTアレイ検査装置。

【請求項7】

前記ステージはステージ用放電抵抗を介して接地することを特徴とする、請求項4又は6に記載のTFTアレイ検査装置。

【請求項8】

前記基板を搬送する基板搬送装置を備え、

前記基板搬送装置は、基板を載置する搬送用パレットを備え、当該搬送用パレットは基板を載置する側に絶縁体を有し、当該絶縁体を介して基板と接触することを特徴とする、請求項1から7の何れか一つに記載のTFTアレイ検査装置。

【図3】

【図4】

【図7】

【図8】

【図1】

【図2】

【図5】

【図6】

【図9】

【図4】

【図7】

【図8】

【図1】

【図2】

【図5】

【図6】

【図9】

【公開番号】特開2013−96758(P2013−96758A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−237902(P2011−237902)

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000001993)株式会社島津製作所 (3,708)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000001993)株式会社島津製作所 (3,708)

【Fターム(参考)】

[ Back to top ]