しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力素子及びその製造方法に係り、特にしきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法に関する。

【背景技術】

【0002】

高電子移動度トランジスタ(High Electron Mobility Transistor:HEMT)は、電力素子の一つである。高電子移動度トランジスタは、分極率が異なる化合物半導体を含み、チャネル層には、キャリアとして使われる二次元電子ガス(2−Dimensional Electron Gas:2DEG)が形成される。高電子移動度トランジスタにおいて、AlGaNバリヤー層の厚さを厚く形成すれば、チャネル層に二次元電子ガスの濃度を高めることができ、ターンオン時の電流、すなわち、オン電流を増加させることができる。しかし、AlGaNバリヤー層の厚さが厚い場合、ゲートとAlGaNバリヤー層との間に形成されるデプリーション層によるAlGaNバリヤー層のエネルギーバンドの引き上げられる程度が小さい。したがって、ゲート下のチャネル層から二次元電子ガスが完全に除去されず、高電子移動度トランジスタのE・モード(Enhanced mode)の動作が困難である。

【0003】

かかる高電子移動度トランジスタにおいて、ゲート下のAlGaNバリヤー層にリセスを形成して、ゲート下のチャネル層から二次元電子ガスを完全に除去できる。しかし、リセスを形成するためのエッチング過程で、リセス後に、リセス下に残ったAlGaNバリヤー層の厚さが高電子移動度トランジスタごとに変わりうる。これによって、高電子移動度トランジスタごとにターンオンのためのしきい電圧Vthが変わるが、これは、高電子移動度トランジスタの動作の信頼性低下の原因の一つとなる。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の目的は、製品別のしきい電圧の偏差を減らすことができる高電子移動度トランジスタを提供することである。

【0005】

本発明の他の目的は、かかる高電子移動度トランジスタの製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の一実施形態による高電子移動度トランジスタは、化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、前記二次元電子ガスチャネルに対応するように、前記チャネル層上に形成された第1チャネル供給層と、前記チャネル層のデプリーション領域及び前記第1チャネル供給層の一部の領域上に形成されたデプリーション層と、前記第1チャネル供給層上に形成され、前記デプリーション領域を挟んで対向するソース及びドレイン電極と、前記デプリーション層上に形成されたゲート電極と、を備える。

【0007】

かかる高電子移動度トランジスタにおいて、前記第1チャネル供給層より分極率が小さい第2チャネル供給層を、前記チャネル層の前記デプリーション領域及び前記第1チャネル供給層の一部の領域上に備え、前記デプリーション層が、前記第2チャネル供給層上に備えられてもよい。

【0008】

前記ソース及びドレイン電極が、前記デプリーション層と接触または離隔されてもよい。

【0009】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられてもよい。

【0010】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であってもよい。

【0011】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であってもよい。

【0012】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であってもよい。

【0013】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含んでもよい。

【0014】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であってもよい。

【0015】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記第2チャネル供給層の厚さが、5ないし20nmであってもよい。

【0016】

前記ゲート電極が、p−金属または窒化物であってもよい。

【0017】

前記第1及び第2チャネル供給層が、同じ分極率を有してもよい。

【0018】

本発明の一実施形態によるトランジスタは、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、前記デプリーション領域を露出させる開口を限定し、前記二次元電子ガスチャネル上に形成された第1チャネル供給層と、前記第1チャネル供給層及び前記デプリーション領域上に形成されたデプリーション層と、前記第1チャネル供給層上に形成され、互いに離隔したソース及びドレイン電極と、前記デプリーション層上に形成されたゲート電極と、を備え、前記デプリーション層が、窒素(N)を含有し、アルミニウム(Al)、ガリウム(Ga)及びインジウム(In)のうち少なくとも一つを含有する化合物半導体を含む。

【0019】

かかるトランジスタにおいて、前記デプリーション層と前記デプリーション領域との間に、第2チャネル供給層をさらに備えてもよい。

【0020】

前記第2チャネル供給層の分極率が、前記第1チャネル供給層の分極率より小さくてもよい。

【0021】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられてもよい。

【0022】

前記デプリーション層が、p型ドーパントを含んでもよい。

【0023】

前記デプリーション層の分極率が、前記第1チャネル供給層の分極率より小さくてもよい。

【0024】

本発明の他の実施形態による高電子移動度トランジスタは、基板上に形成され、互いに離隔したソース電極、ドレイン電極及びゲート電極と、前記ゲート電極上に形成されたデプリーション層と、前記デプリーション層の少なくとも一部の上に形成された第1チャネル供給層と、前記デプリーション層及び前記第1チャネル供給層上に形成されたチャネル層と、を備え、前記チャネル層が、前記第1チャネル供給層に対応する二次元電子ガスチャネルと、前記デプリーション層に対応するデプリーション領域とを備える。

【0025】

本発明の一実施形態による高電子移動度トランジスタの製造方法は、基板上にチャネル層を形成し、前記チャネル層上に、前記チャネル層より分極率が大きい第1チャネル供給層を形成し、前記第1チャネル供給層の一部を除去して、前記チャネル層の一部を露出させ、前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆うデプリーション層を形成し、前記第1チャネル供給層上に、前記デプリーション層を挟んで対向するソース及びドレイン電極を形成し、前記デプリーション層上にゲート電極を形成する過程を含む。

【0026】

かかる製造方法において、前記デプリーション層を形成する前に、前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆って、前記第1チャネル供給層より分極率が小さい第2チャネル供給層を形成し、前記デプリーション層が、前記第2チャネル供給層上に形成されてもよい。

【0027】

前記ゲート電極と前記デプリーション層との間に、絶縁層を形成してもよい。

【0028】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であってもよい。

【0029】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であってもよい。

【0030】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であってもよい。

【0031】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であってもよい。

【0032】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であってもよい。

【0033】

前記ゲート電極が、p−金属または窒化物であってもよい。

【0034】

前記デプリーション層及び前記第2チャネル形成層とが、エピタキシー法で形成されてもよい。

【0035】

前記ソース及びドレイン電極が、前記デプリーション層と離隔して形成されてもよい。

【0036】

前記デプリーション層を形成する前に、ウェットエッチングにより、前記チャネル層の露出された領域の表面粗度を緩和させてもよい。

【0037】

前記第1及び第2チャネル供給層の分極率が、同じであってもよい。

【発明の効果】

【0038】

本発明の一実施形態による高電子移動度トランジスタにおいて、チャネル層上にチャネル供給層が形成された後、チャネル供給層のゲート電極下に形成された部分は完全に除去される。以後、チャネル供給層が除去されたチャネル層上にエピタキシー法でデプリーション層を直接成長させるか、あるいはチャネル供給層と分極率が同じであるか、または小さい他のチャネル供給層とデプリーション層とを順次に成長させる。

【0039】

ゲート電極下のデプリーション領域上に形成されるデプリーション層、または他のチャネル供給層とデプリーション層とは、エピタキシー法で成長されるので、ゲート電極とチャネル層との間に形成される物質層の厚さを正確に調節できる。これによって、ゲート電極とチャネル層との間に形成される物質層の厚さは、誤差範囲内で高電子移動度トランジスタ別に一定に維持できる。したがって、高電子移動度トランジスタ別にゲートしきい電圧の変化を最小化することができるため、高電子移動度トランジスタの動作信頼性が高くなる。

【0040】

また、他のチャネル供給層は、ゲート電極とドレイン電極との間のチャネル供給層上にも成長されるので、ゲート電極とドレイン電極との間のチャネル供給層の厚さは、ゲート下より厚くなる。これによって、ゲート電極とドレイン電極との間にデプリーション層が存在するとしても、ゲート電極とドレイン電極との間のチャネル層で二次元電子ガス密度は低くならない。

【図面の簡単な説明】

【0041】

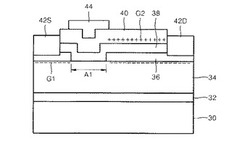

【図1】本発明の一実施形態による高電子移動度トランジスタの断面図である。

【図2A】図1において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図2B】図1において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図2C】図1において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図3】図1において、ゲート電極とデプリーション層との間に絶縁層(ゲート絶縁膜)がさらに備えられた場合を示す断面図である。

【図4】本発明の他の実施形態による高電子移動度トランジスタの断面図である。

【図5】図4において、ゲート電極とデプリーション層との間に絶縁層(ゲート絶縁膜)がさらに備えられた場合を示す断面図である。

【図6】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図7】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図8】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図9】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図10】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図11】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図12】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図13】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図14】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図15】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図16】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図17】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図18】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図19】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図20】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図21】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図22】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図23】本発明の一実施形態による高電子移動度トランジスタを対象として実施したシミュレーションで測定された、ゲート電極とドレイン電極との間の二次元電子ガスと二次元ホールガス密度を示すグラフである。

【図24A】図4において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図24B】図4において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図24C】図4において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図25A】本発明のさらに他の実施形態による高電子移動度トランジスタを示す断面図である。

【図25B】本発明のさらに他の実施形態による高電子移動度トランジスタを示す断面図である。

【図26A】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26B】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26C】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26D】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26E】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26F】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26G】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【発明を実施するための形態】

【0042】

以下、本発明の一実施形態による高電子移動度トランジスタ及びその製造方法を、添付された図面を参照して詳細に説明する。この過程で、図面に示す層や領域の厚さは、明細書の明確性のために誇張されて示されたものである。

【0043】

まず、本発明の一実施形態による高電子移動度トランジスタについて説明する。

【0044】

図1を参照すれば、基板30上にバッファ層32が形成されている。基板30は、例えば、シリコン基板、シリコンカーバイド(SiC)基板、またはアルミニウム酸化物(例えば、Al2O3)基板である。バッファ層32は、化合物半導体層である。例えば、バッファ層32は、GaN層、AlGaN層またはAlGaInN層である。基板30とバッファ層32との間に、シード層がさらに備えられてもよい。この時、シード層は、例えば、AlN層、AlGaN層である。バッファ層32上には、 二次元電子ガスG1を含む物質層34が存在する。物質層34は、化合物半導体層であり、例えば、GaN層である。二次元電子ガスG1は、物質層34の上部面下に位置する。二次元電子ガスG1は、チャネルキャリアとして使われる。このように、物質層34は、チャネルキャリアとして使われる二次元電子ガスG1を含むため、チャネルを含む物質層という意味で、以下でチャネル層34とする。チャネル層34の上部面下の一部の領域A1には、二次元電子ガスが存在しない。この領域A1は、二次元電子ガスが除去された領域であって、以下、デプリーション領域(depletion area)A1とする。チャネル層34上に、第1チャネル供給層36が存在する。第1チャネル供給層36の厚さは、20nm以上であるが、例えば、20nmないし200nmである。第1チャネル供給層36の分極率によって、その厚さは20nm以下であってもよい。第1チャネル供給層36は、化合物半導体層である。第1チャネル供給層36の分極率とバンドギャップとは、チャネル層34より大きい。チャネル層34と第1チャネル供給層36とのかかる差によって、チャネル層34に二次元電子ガスG1が現れる。第1チャネル供給層36の化合物半導体は、AlxGa(1−x−y)InyNである。ここで、xは、0<x≦1、yは、0≦y<1、0<x+y≦1である。例えば、第1チャネル供給層36は、AlN,AlGaN,AlInN及びAlGaInNのうちいずれか一つを含む。第1チャネル供給層36は、二次元電子ガスG1に対応するチャネル層34の上部面上に存在する。チャネル層34のデプリーション領域A1上には、第1チャネル供給層36が存在しない。第1チャネル供給層36上に、チャネル層34のデプリーション領域A1を覆う第2チャネル供給層38が存在する。第2チャネル供給層38は、第1チャネル供給層36の上部面の一部の領域を覆う。第1チャネル供給層36よりは及ぼす影響が少ないが、第2チャネル供給層38は、チャネル層34の二次元電子ガスG1の生成に影響を与える。第2チャネル供給層38の厚さは、20nm以下であるが、例えば、1nmより厚く、20nmより薄い。

【0045】

第1チャネル供給層36上に第2チャネル供給層38が備えられることで、二次元電子ガスG1上に存在するチャネル供給層36及び38の合計の厚さは、デプリーション領域A1上に形成されたチャネル供給層38より厚くなる。デプリーション領域A1の境界での第1チャネル供給層36の段差によって、デプリーション領域A1上で、第2チャネル供給層38は、リセスされた形態となる。かかる第2チャネル供給層38は、化合物半導体層である。第2チャネル供給層38の化合物半導体は、AlxGa(1−x−y)InyNである。ここで、xは、0<x≦1、yは、0≦y<1、0<x+y≦1である。第2チャネル供給層38の分極率は、第1チャネル供給層36より小さい。第1及び第2チャネル供給層36,38の分極率は同じであってもよいが、例えば、第2チャネル供給層38の分極率が第1チャネル供給層36の分極率と同じであってもよい。第1及び第2チャネル供給層36,38は、同じ化合物半導体層であってもよいが、その場合、第1及び第2チャネル供給層36,38の特定の成分、例えば、アルミニウム(Al)またはインジウム(In)の含量は異なる。例えば、第1及び第2チャネル供給層36,38がいずれもAlGaN層である時、第1チャネル供給層36のアルミニウム含量は35%であり、第2チャネル供給層38のアルミニウム含量は20%であり、その逆であってもよい。第1及び第2チャネル供給層36,38は、n型ドーピング物質でドーピングされたものであってもよい。シリコン(Si)がn型ドーピング物質として使われるが、これに制限されない。

【0046】

第2チャネル供給層38上にデプリーション層40が存在する。デプリーション層40は、第2チャネル供給層38のリセスされた部分とその周囲を覆う。二次元電子ガスG1上に存在するチャネル供給層36及び38の合計の厚さは、チャネル層34のデプリーション領域A1上に形成された第2チャネル供給層38より厚い。したがって、デプリーション層40による影響は、デプリーション領域A1に制限されるため、デプリーション層40の存在は、二次元電子ガスG1の密度に影響を与えない。デプリーション層40の厚さは、例えば、5ないし500nmである。

【0047】

第2チャネル供給層38により、チャネル層34のデプリーション領域A1に二次元電子ガスが現れるが、このように表れた二次元電子ガスは、デプリーション層40により除去される。このようにして、デプリーション領域A1には、二次元電子ガスが存在しなくなる。もし存在するとしても、その量は、二次元電子ガスG1と比較して非常に少ないため、その影響は無視してもよい。デプリーション層40は、化合物半導体層または窒化物層である。この時、化合物半導体層は、p型ドーピング物質でドーピングされたものであるが、例えば、GaN層、AlGaN層、AlInN層、AlInGaN層及びInGaN層のうちいずれか一つである。かかる化合物半導体層のうち、InGaN層の場合は、ドーピング物質を含まない。デプリーション層40が窒化物層である場合、デプリーション層40は、例えば、InN層である。この時、InN層は、p型ドーピング物質でドーピングされたものであるが、かかるドーピング物質を含まなくてもよい。マグネシウム(Mg)がp型ドーピング物質として使われるが、これに制限されない。デプリーション層40は、また、p型半導体層または誘電体層を備える。

【0048】

デプリーション層40は、第1チャネル供給層36との分極率の差による二次元ホールガス(2−Dimensional Hole Gas:2DHG)G2を含む。二次元ホールガスG2の形成に、第2チャネル供給層38も影響を与える。二次元ホールガスG2は、第2チャネル供給層38とデプリーション層40との界面近辺に存在する。二次元電子ガスG1を除去する時、二次元ホールガスG2を共に除去すれば、図1の高電子移動度トランジスタの空間電荷は、全体的に中性となる。したがって、図1の高電子移動度トランジスタは、絶縁破壊電圧が非常に高いスーパー接合高電子移動度トランジスタとなる。

【0049】

次いで、第1チャネル供給層36で、第2チャネル供給層38が形成されていない領域上に、ソース電極42Sとドレイン電極42Dとが形成される。ソース電極42Sとドレイン電極42Dとは、デプリーション領域A1を挟んで対向する。チャネル層34のデプリーション領域A1は、ドレイン電極42Dよりソース電極42Sに近い。ソース電極42Sとドレイン電極42Dとは、第2チャネル供給層38及びデプリーション層40に接触する。

【0050】

一方、図示していないが、第1チャネル供給層36から、ソース電極42Sとドレイン電極42Dの下に形成された部分が除去されて、ソース電極42Sとドレイン電極42Dとがチャネル層34上に形成されてもよい。かかる場合は、後述する他の実施形態にも適用される。

【0051】

再び図1を参照すれば、デプリーション層40上にゲート電極44が存在する。ゲート電極44は、チャネル層34のデプリーション領域A1上に位置する。ゲート電極44は、金属ゲートまたは窒化物ゲートである。ゲート44電極が金属ゲートである時、ゲート電極44は、デプリーション層40とオーミックコンタクトをなす第1金属、またはデプリーション層40とショットキーコンタクトをなす第2金属で形成されたものである。第1金属は、仕事関数が4.5eV以上である金属であって、例えば、ニッケル(Ni)、イリジウム(Ir)、白金(Pt)及び金(Au)のうちいずれか一つである。第2金属は、仕事関数が4.5eVより小さい金属であって、例えば、チタン(Ti)、アルミニウム(Al)、ハフニウム(Hf)、タンタル(Ta)及びタングステン(W)のうちいずれか一つである。ゲート電極44が窒化物ゲートである時、ゲート電極44は、遷移金属窒化物で形成されたものである。遷移金属窒化物は、例えば、TiN、TaNまたはWNである。また、ゲート電極44は、導電性不純物を含むポリシリコンまたはゲルマニウム(Ge)で形成されたゲート電極である。

【0052】

一方、図2Aに示すように、デプリーション層40Aは、ソース電極42S及びドレイン電極42Dと離隔される。また、図2Bに示すように、デプリーション層40Bは、ソース電極42Sと離隔され、ドレイン電極42Dとは離隔されなくてもよい。また、図2Cに示すように、デプリーション層40Cは、ドレイン電極42Dと離隔され、ソース電極42Sとは離隔されなくてもよい。ソース電極42Sとドレイン電極42Dとは、少なくとも一つの金属または金属窒化物を含むが、例えば、Au,Ni,Pt,Ti,Al,Pd,Ir,W,Mo,Ta,Cu,TiN,TaN及びWNのうち少なくとも一つを含む。ソース電極42Sとドレイン電極42Dとは、これらに制限されない。

【0053】

また、図3に示すように、ゲート電極44’とデプリーション層40との間には、漏れ電流を防止するための絶縁層46がさらに備えられる。絶縁層46は、シリコン酸化物層または窒化物層である。絶縁層46は、図2Aないし図2Cに示す高電子移動度トランジスタに適用される。

【0054】

図4は、本発明の他の実施形態による高電子移動度トランジスタを示す。図1の場合と異なる部分についてのみ説明する。

【0055】

図4を参照すれば、第1チャネル供給層36の一部の領域上に、チャネル層34のデプリーション領域A1を覆う第2デプリーション層50が備えられている。第2デプリーション層50の厚さは、例えば、1ないし100nmである。第2デプリーション層50は、p型ドーピング物質がドーピングされた化合物半導体層であるが、例えば、p型AlGaN層である。第2デプリーション層50は、また、分極誘発元素の含量が次第に変わる化合物半導体層であるが、例えば、アルミニウム(Al)の含量が下面から上面へ行くほど次第に少なくなって、分極密度が次第に低くなるpドーピング効果を有するAlGaN層である。かかる第2デプリーション層50は、AlGaN層以外にも、AlInN層またはAlInGaN層がある。第2デプリーション層50は、図1の第2チャネル供給層38と同じ位置に備えられる。第1チャネル供給層36の上部面で、第2デプリーション層50が存在しない領域上に、ソース電極42Sとドレイン電極42Dとが存在する。ソース電極42Sとドレイン電極42Dとは、第2デプリーション層50と接触する。第2デプリーション層50上にゲート電極44が存在する。

【0056】

一方、図5に示すように、第2デプリーション層50とゲート電極44’との間に、絶縁層46がさらに備えられる。

【0057】

図24Aに示すように、デプリーション層50Aは、ソース電極42S及びドレイン電極42Dから離隔される。また、図24Bに示すように、デプリーション層50Bは、ソース電極42Sと離隔され、ドレイン電極42Dとは離隔されなくてもよい。また、図24Cに示すように、デプリーション層50Cは、ドレイン電極42Dと離隔され、ソース電極42Sとは離隔されなくてもよい。

【0058】

次いで、図6ないし図11を参照して、本発明の一実施形態による高電子移動度トランジスタの製造方法を説明する。この過程で、図1ないし図5の説明で言及された部材については、同じ参照番号を使用し、関連した説明は省略する。

【0059】

図6を参照すれば、基板30上にバッファ層32を形成する。基板30とバッファ層32との間にシード層(図示せず)を形成する。バッファ層32上にチャネル層34を形成する。チャネル層34は、エピタキシー法を利用して形成する。チャネル層34上に第1チャネル供給層36’を形成する。第1チャネル供給層36’とチャネル層34との分極率の差によって、チャネル層34の上部面下に二次元電子ガスG1が現れる。第1チャネル供給層36’は、エピタキシー法を利用して形成する。第1チャネル供給層36’が、n型ドーピング物質、例えば、シリコン(Si)がドーピングされた物質層である場合、第1チャネル供給層36’を成長させる過程で、n型ドーピング物質を注入させて形成する。この時、第1チャネル供給層36’の成長及びn型ドーピング物質の注入は、イン・シチュ(in−situ)で行う。第1チャネル供給層36’を形成した後、第1チャネル供給層36’の上部面上にマスクM1を形成する。マスクM1は、第1チャネル供給層36’の上部面の一部の領域A2が露出されるように形成する。マスクM1の形成後、第1チャネル供給層36’の上部面の露出された一部の領域A2は、図1のチャネル層34のデプリーション領域A1に対応する。マスクM1を形成した後、第1チャネル供給層36’の上部面の露出された領域A2を除去する。次いで、マスクM1も除去する。

【0060】

このようにして、図7に示すように、チャネル層34の上部面の一部の領域A3が露出される。そして、一部の領域A3を挟んで離隔された第1チャネル供給層36’’が形成される。図6の第1チャネル供給層36’から、チャネル層34の露出された領域A3上に形成された部分が除去されることで、チャネル層34の露出された領域A3から二次元電子ガスG1は除去される。かかるチャネル層34の露出された領域A3は、図1のデプリーション領域A1に該当する。

【0061】

図6の第1チャネル供給層36’の一部の領域A2は、異方性ドライエッチングにより除去されるが、かかるエッチングにより、チャネル層34の上部面の露出された領域A3の表面粗度は大きくなる。したがって、チャネル層34の上部面の露出された領域A3の表面粗度を低めるために、図7の結果物をウェットエッチングする。この時、ウェットエッチングのエッチャントとして、TMAHまたはKOHを使用する。ウェットエッチングにより、チャネル層34の露出された領域A3の表面粗度(rms)は、図6の第1チャネル供給層36’を異方性のドライエッチングする前と類似したレベルに下げることができる。例えば、異方性のドライエッチング前において、チャネル層34の上部面の表面粗度は、約1Åであるが、異方性のドライエッチング後、チャネル層34の上部面の露出された領域A3の表面粗度は、約2Åに大きくなる。しかし、ウェットエッチング後、露出された領域A3の表面粗度は、再び約1Åに低くなる。

【0062】

次いで、図8を参照すれば、ウェットエッチング後、第1チャネル供給層36’’上に、チャネル層34の上部面の露出された領域A3を覆う第2チャネル供給層38’を形成する。第2チャネル供給層38’は、エピタキシー法で形成する。第2チャネル供給層38’は、第1チャネル供給層36’’と同じ組成で形成するが、組成のうち一つの成分の含量は、第1チャネル供給層36’’と異なってもよい。例えば、第2チャネル供給層38’は、第1チャネル供給層36’’と同様に、AlGaN層を成長させて形成するが、Alの含量は、第1チャネル供給層36’’より少なくして形成する。チャネル層34の露出された領域A3と第1チャネル供給層36’’との間には、段差が存在する。かかる段差は、第2チャネル供給層38’にもそのまま転写される。これによって、第2チャネル供給層38’が形成された後、チャネル層34の露出された領域A3上で、第2チャネル供給層38’は、リセスされた形態に形成される。第2チャネル供給層38’が形成された後、チャネル層34の露出された領域A3には、第2チャネル供給層38’とチャネル層34との分極率の差による第2二次元電子ガスG3が現れる。第2二次元電子ガスG3の密度は、第1チャネル供給層36’’により第1チャネル供給層36’’下のチャネル層34に現れる二次元電子ガスG1に比べて低い。

【0063】

次いで、図9を参照すれば、第2チャネル供給層38’上にデプリーション層40’を形成する。デプリーション層40’は、エピタキシー法で形成する。第2チャネル供給層38’のリセスされた形態は、デプリーション層40’にも転写される。これによって、チャネル層34の露出された領域A3上で、デプリーション層40’は、リセスされた形態に形成される。チャネル層34の露出された領域A3に現れる第2二次元電子ガスG3は、デプリーション層40’が形成されるにつれて除去される。

【0064】

デプリーション層40’上にマスクM2を形成する。マスクM2は、チャネル層34のデプリーション領域A3と、その周囲の領域に対応するデプリーション層40’の一部の領域とを覆う。マスクM2により、ソース及びドレイン電極が形成される領域が限定される。

【0065】

図10を参照すれば、マスクM2の周囲のデプリーション層40’及び第2チャネル供給層38’’が順次にエッチングされて、デプリーション層40と第2チャネル供給層38とが形成される。かかるエッチングは、第1チャネル供給層36の上部面が露出されるまで行う。エッチング後、マスクM2を除去する。かかるエッチングにおいて、第1チャネル供給層36の一部がエッチングされてもよい。かかるエッチングにより、第1チャネル供給層36の上部面の第1領域36Aと第2領域36Bとが露出される。第1及び第2領域36A,36Bは離隔されており、チャネル層34のデプリーション領域A3を挟んで対向する。第2領域36Bより第1領域36Aがデプリーション領域A3に近い。第1領域36A上には、図11に示すように、ソース電極42Sを形成し、第2領域36B上には、ドレイン電極42Dを形成する。かかるソース及びドレイン電極42S,42Dは、図10の結果からマスクM2を除去する前に、第1及び第2領域36A,36BとマスクM2上に電極物質層(図示せず)を形成した後、マスクM2を除去するリフトオフ方式により形成する。

【0066】

図11を参照すれば、ソース電極42Sとドレイン電極42Dとは、第2チャネル供給層38及びデプリーション層40と接触する。

【0067】

一方、図10の第1チャネル供給層36の上部面が露出されるエッチングにおいて、エッチングは、チャネル層34が露出されるまで行ってもよい。この場合、ソース電極42Sとドレイン電極42Dとは、チャネル層34上に形成されてもよい。

【0068】

図12を参照すれば、デプリーション層40上にゲート電極44を形成する。ゲート電極44とデプリーション層40との間に、絶縁層(ゲート絶縁膜)(図示せず)をさらに形成してもよい。

【0069】

次いで、図2Aに示す高電子移動度トランジスタの製造方法を、図13ないし図18を参照して説明する。図6ないし図12を参照して説明した製造方法と異なる部分についてのみ説明する。

【0070】

図13を参照すれば、基板30上にバッファ層32、チャネル層34、第1チャネル供給層36及び第2チャネル供給層38を形成する過程は、図6ないし図8で説明した過程と同じである。

【0071】

第2チャネル供給層38上に、第2チャネル供給層38のリセス部分とその周囲の一部とを覆うデプリーション層40Aを形成する。この時、デプリーション層40Aが覆う第2チャネル供給層38の面積は、図10でデプリーション層40が覆う第2チャネル供給層38の面積より小さい。換言すれば、図13のデプリーション層40Aのサイズは、図10のデプリーション層40のサイズより小さい。

【0072】

図14を参照すれば、第2チャネル供給層38上に、デプリーション層40Aを覆い、その周囲の第2チャネル供給層38の一部も覆うマスクM3を形成する。次いで、マスクM3の周囲の第2チャネル供給層38をエッチングして、図15に示すように、第1チャネル供給層36を露出させる。第1チャネル供給層36が露出された後、第1チャネル供給層36の露出された部分は、一定の厚さ範囲内でさらにエッチングされる。

【0073】

図16を参照すれば、第1チャネル供給層36の露出された領域上に導電層42を形成する。導電層42は、ソース及びドレイン電極42S,42Dを形成する物質である。導電層42は、マスクM3上にも形成される。導電層42を形成した後、マスクM3を除去する。マスクM3を除去する過程で、導電層42のマスクM3上に形成された部分も除去される。マスクM3が除去された後、デプリーション層40Aの両側に残った導電層42は、図17に示すように、ソース電極42S及びドレイン電極42Dとして使われる。図16において、デプリーション層40Aと導電層42とは、マスクM3により離隔された状態となる。したがって、マスクM3が除去された後、デプリーション層40A、ソース及びドレイン電極42S,42Dは、図17に示すように離隔された状態となる。マスクM3を除去した後、図18に示すように、デプリーション層40A上にゲート電極44を形成する。

【0074】

次いで、図4に示す高電子移動度トランジスタの製造方法を、図19ないし図22を参照して説明する。前述した製造方法と異なる部分についてのみ説明する。

【0075】

図19を参照すれば、第1チャネル供給層36上に、チャネル層34の上部面の露出された領域A3を覆う第2デプリーション層50’を形成する。第2デプリーション層50’は、エピタキシー法で形成する。第2デプリーション層50’において、チャネル層34の露出された領域A3上に形成された部分は、第1チャネル供給層36の段差によってリセスされた形態となる。第2デプリーション層50’上にマスクM4を形成する。マスクM4は、第2デプリーション層50’のリセスされた部分とその周囲とを覆って、第2デプリーション層50’でソース及びドレイン電極が形成される領域を限定する。このようにマスクM4を形成した後、図20に示すように、マスクM4の周囲の第2デプリーション層50の露出された部分をエッチングする。このエッチングは、第1チャネル供給層36が露出されるまで行う。

【0076】

図21を参照すれば、エッチングにより露出された第1チャネル供給層36の領域上に導電層42を形成する。導電層42は、マスクM4上にも形成される。導電層42の形成後にマスクM4を除去すれば、マスクM4上に形成された導電層42は、マスクM4と共に除去される。このようにして、導電層42は、第1チャネル供給層36上にのみ残る。第2デプリーション層50の両側の第1チャネル供給層36上に残った導電層42は、図22に示すように、ソース電極42S及びドレイン電極42Dとして使われる。第1チャネル供給層36上に残った導電層42は、第2デプリーション層50の側面と接触する。

【0077】

マスクM4を除去した後、図22に示すように、第2デプリーション層50上にゲート電極44を形成する。

【0078】

一方、図20において、マスクM4を除去した後、第2デプリーション層50を覆う他のマスクを形成した後で後続工程を進めるが、このようにすることで、ソース及びドレイン電極42S,42Dと第2デプリーション層50とが離隔される高電子移動度トランジスタを形成できる。

【0079】

図23は、チャネル層34がGaN層、第1チャネル供給層36がAl35GaN層(15nm)(または、Al20GaN層(15nm))、第2チャネル供給層38がAl20GaN層(15nm)(または、Al35GaN層(15nm))、デプリーション層40がp−GaN層である時、測定したゲート電極44とソース及びドレイン電極42S,42Dとの間の二次元電子ガスG1と二次元ホールガスG2の密度に対するシミュレーション結果を表す。

【0080】

図23において、第1ピークP1は、二次元電子ガス密度を表し、第2ピークP2は、二次元ホールガス密度を表す。

【0081】

図23を参照すれば、第1及び第2チャネル供給層36,38の組成が同じである時、各層の成分比が異なる場合でも、二次元電子ガスと二次元ホールガスとの密度は、1018/cm3以上の高さがあるということが分かる。したがって、第1及び第2チャネル供給層36,38の組成が同じである場合にも、各層の成分比を異ならせれば、ゲート電極44とドレイン電極42Dとの間のチャネル層34で、二次元電子ガス密度は高く維持でき、ゲート電極44とドレイン電極42Dとの間のデプリーション層40で、二次元ホールガス密度も高く維持できるということが分かる。

【0082】

図25Aは、本発明のさらに他の実施形態による高電子移動度トランジスタを示す。

【0083】

図25Aを参照すれば、高電子移動度トランジスタは、基板105上に離隔して形成されたソース電極110、ゲート電極112及びドレイン電極114を備える。デプリーション層104が、ゲート電極112上に形成されている。第1チャネル供給層103が、デプリーション層104の側面上に存在する。チャネル層102とパッシベーション層101とが、第1チャネル供給層103とデプリーション層104上に形成されている。

【0084】

図25Aに示すように、第1チャネル層102は、デプリーション層104との界面にデプリーション領域A1を備え、二次元電子ガスを含む第1チャネル供給層103との界面に領域G1を備える。

【0085】

図25Bは、本発明のさらに他の実施形態による高電子移動度トランジスタを示す。図25Aに示す高電子移動度トランジスタと異なる部分についてのみ説明する。

【0086】

図25Bに示すように、デプリーション層104の代わりに、デプリーション層107と第1チャネル供給層103との間に第2チャネル供給層106を備える。

【0087】

図26Aないし図26Gは、本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す。

【0088】

図26Aを参照すれば、電極層116が基板105上に形成される。基板105は、例えば、シリコン基板、シリコンカーバイド(SiC)基板、またはアルミニウム酸化物基板(例えば、Al2O3)である。しかし、基板105は、かかる基板に限定されない。電極層116は、金属または金属窒化物を含む。図26Bに示すように、電極層116は、ソース電極110、ゲート電極112及びドレイン電極114にパターニングされる。図26Cに示すように、デプリーション層104’は、ソース電極110、ゲート電極112及びドレイン電極114上に形成される。デプリーション層104’は、図4で説明したデプリーション層50と同じ物質を含むが、かかる物質に制限されない。

【0089】

次いで、図26Dに示すように、ソース電極110、ゲート電極112及びドレイン電極114上に形成されたデプリーション層104’をエッチバックして、デプリーション層104を形成する。図26Eに示すように、第1チャネル供給層103’がデプリーション層104上に形成される。第1チャネル供給層103’は、図4で説明した第1チャネル供給層36と同じ物質を含むが、かかる物質に制限されない。図26Fに示すように、第1チャネル供給層103’をエッチバックすることで、第1チャネル供給層103が形成される。第1チャネル供給層103は、デプリーション層104を部分的に露出させてもよい。

【0090】

次いで、図26Gに示すように、チャネル層102及びパッシベーション層101が、第1チャネル供給層103上に順次に形成される。チャネル層102は、図4で説明したチャネル層34と同じ物質を含むが、かかる物質に制限されない。パッシベーション層101は、絶縁物質または絶縁ポリマー物質を含むが、かかる物質に限定されない。この時、絶縁物質は、シリコン酸化物のような酸化物である。

【0091】

図26Aないし図26Gは、デプリーション層104を備える高電子移動度トランジスタを形成する方法の一例を示すが、デプリーション層104を形成する代わりに、図25Bに示すように、デプリーション層107が第2チャネル供給層106上に形成されてもよい。

【0092】

図25Bを参照すれば、第2チャネル供給層106及びデプリーション層107は、それぞれ図1で説明した第2チャネル供給層38及びデプリーション層40と同じ物質を含んでもよい。

【0093】

前述の説明で多くの事項が具体的に記載されているが、それらは、発明の範囲を限定するというより、望ましい実施形態の例示として解釈されねばならない。したがって、本発明の範囲は、説明された実施形態により決まるものではなく、特許請求の範囲に記載された技術的思想により決まらねばならない。

【産業上の利用可能性】

【0094】

本発明は、高周波素子関連の技術分野に適用可能である。

【符号の説明】

【0095】

30 基板

32 バッファ層

34 チャネル層

36 第1チャネル供給層

38 第2チャネル供給層

40,40A,40B,40C デプリーション層

42D ドレイン電極

42S ソース電極

44 ゲート電極

A1 デプリーション領域

G1 二次元電子ガス

G2 二次元ホールガス

【技術分野】

【0001】

本発明は、電力素子及びその製造方法に係り、特にしきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法に関する。

【背景技術】

【0002】

高電子移動度トランジスタ(High Electron Mobility Transistor:HEMT)は、電力素子の一つである。高電子移動度トランジスタは、分極率が異なる化合物半導体を含み、チャネル層には、キャリアとして使われる二次元電子ガス(2−Dimensional Electron Gas:2DEG)が形成される。高電子移動度トランジスタにおいて、AlGaNバリヤー層の厚さを厚く形成すれば、チャネル層に二次元電子ガスの濃度を高めることができ、ターンオン時の電流、すなわち、オン電流を増加させることができる。しかし、AlGaNバリヤー層の厚さが厚い場合、ゲートとAlGaNバリヤー層との間に形成されるデプリーション層によるAlGaNバリヤー層のエネルギーバンドの引き上げられる程度が小さい。したがって、ゲート下のチャネル層から二次元電子ガスが完全に除去されず、高電子移動度トランジスタのE・モード(Enhanced mode)の動作が困難である。

【0003】

かかる高電子移動度トランジスタにおいて、ゲート下のAlGaNバリヤー層にリセスを形成して、ゲート下のチャネル層から二次元電子ガスを完全に除去できる。しかし、リセスを形成するためのエッチング過程で、リセス後に、リセス下に残ったAlGaNバリヤー層の厚さが高電子移動度トランジスタごとに変わりうる。これによって、高電子移動度トランジスタごとにターンオンのためのしきい電圧Vthが変わるが、これは、高電子移動度トランジスタの動作の信頼性低下の原因の一つとなる。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の目的は、製品別のしきい電圧の偏差を減らすことができる高電子移動度トランジスタを提供することである。

【0005】

本発明の他の目的は、かかる高電子移動度トランジスタの製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の一実施形態による高電子移動度トランジスタは、化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、前記二次元電子ガスチャネルに対応するように、前記チャネル層上に形成された第1チャネル供給層と、前記チャネル層のデプリーション領域及び前記第1チャネル供給層の一部の領域上に形成されたデプリーション層と、前記第1チャネル供給層上に形成され、前記デプリーション領域を挟んで対向するソース及びドレイン電極と、前記デプリーション層上に形成されたゲート電極と、を備える。

【0007】

かかる高電子移動度トランジスタにおいて、前記第1チャネル供給層より分極率が小さい第2チャネル供給層を、前記チャネル層の前記デプリーション領域及び前記第1チャネル供給層の一部の領域上に備え、前記デプリーション層が、前記第2チャネル供給層上に備えられてもよい。

【0008】

前記ソース及びドレイン電極が、前記デプリーション層と接触または離隔されてもよい。

【0009】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられてもよい。

【0010】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であってもよい。

【0011】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であってもよい。

【0012】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であってもよい。

【0013】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含んでもよい。

【0014】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であってもよい。

【0015】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記第2チャネル供給層の厚さが、5ないし20nmであってもよい。

【0016】

前記ゲート電極が、p−金属または窒化物であってもよい。

【0017】

前記第1及び第2チャネル供給層が、同じ分極率を有してもよい。

【0018】

本発明の一実施形態によるトランジスタは、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、前記デプリーション領域を露出させる開口を限定し、前記二次元電子ガスチャネル上に形成された第1チャネル供給層と、前記第1チャネル供給層及び前記デプリーション領域上に形成されたデプリーション層と、前記第1チャネル供給層上に形成され、互いに離隔したソース及びドレイン電極と、前記デプリーション層上に形成されたゲート電極と、を備え、前記デプリーション層が、窒素(N)を含有し、アルミニウム(Al)、ガリウム(Ga)及びインジウム(In)のうち少なくとも一つを含有する化合物半導体を含む。

【0019】

かかるトランジスタにおいて、前記デプリーション層と前記デプリーション領域との間に、第2チャネル供給層をさらに備えてもよい。

【0020】

前記第2チャネル供給層の分極率が、前記第1チャネル供給層の分極率より小さくてもよい。

【0021】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられてもよい。

【0022】

前記デプリーション層が、p型ドーパントを含んでもよい。

【0023】

前記デプリーション層の分極率が、前記第1チャネル供給層の分極率より小さくてもよい。

【0024】

本発明の他の実施形態による高電子移動度トランジスタは、基板上に形成され、互いに離隔したソース電極、ドレイン電極及びゲート電極と、前記ゲート電極上に形成されたデプリーション層と、前記デプリーション層の少なくとも一部の上に形成された第1チャネル供給層と、前記デプリーション層及び前記第1チャネル供給層上に形成されたチャネル層と、を備え、前記チャネル層が、前記第1チャネル供給層に対応する二次元電子ガスチャネルと、前記デプリーション層に対応するデプリーション領域とを備える。

【0025】

本発明の一実施形態による高電子移動度トランジスタの製造方法は、基板上にチャネル層を形成し、前記チャネル層上に、前記チャネル層より分極率が大きい第1チャネル供給層を形成し、前記第1チャネル供給層の一部を除去して、前記チャネル層の一部を露出させ、前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆うデプリーション層を形成し、前記第1チャネル供給層上に、前記デプリーション層を挟んで対向するソース及びドレイン電極を形成し、前記デプリーション層上にゲート電極を形成する過程を含む。

【0026】

かかる製造方法において、前記デプリーション層を形成する前に、前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆って、前記第1チャネル供給層より分極率が小さい第2チャネル供給層を形成し、前記デプリーション層が、前記第2チャネル供給層上に形成されてもよい。

【0027】

前記ゲート電極と前記デプリーション層との間に、絶縁層を形成してもよい。

【0028】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であってもよい。

【0029】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であってもよい。

【0030】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であってもよい。

【0031】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であってもよい。

【0032】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であってもよい。

【0033】

前記ゲート電極が、p−金属または窒化物であってもよい。

【0034】

前記デプリーション層及び前記第2チャネル形成層とが、エピタキシー法で形成されてもよい。

【0035】

前記ソース及びドレイン電極が、前記デプリーション層と離隔して形成されてもよい。

【0036】

前記デプリーション層を形成する前に、ウェットエッチングにより、前記チャネル層の露出された領域の表面粗度を緩和させてもよい。

【0037】

前記第1及び第2チャネル供給層の分極率が、同じであってもよい。

【発明の効果】

【0038】

本発明の一実施形態による高電子移動度トランジスタにおいて、チャネル層上にチャネル供給層が形成された後、チャネル供給層のゲート電極下に形成された部分は完全に除去される。以後、チャネル供給層が除去されたチャネル層上にエピタキシー法でデプリーション層を直接成長させるか、あるいはチャネル供給層と分極率が同じであるか、または小さい他のチャネル供給層とデプリーション層とを順次に成長させる。

【0039】

ゲート電極下のデプリーション領域上に形成されるデプリーション層、または他のチャネル供給層とデプリーション層とは、エピタキシー法で成長されるので、ゲート電極とチャネル層との間に形成される物質層の厚さを正確に調節できる。これによって、ゲート電極とチャネル層との間に形成される物質層の厚さは、誤差範囲内で高電子移動度トランジスタ別に一定に維持できる。したがって、高電子移動度トランジスタ別にゲートしきい電圧の変化を最小化することができるため、高電子移動度トランジスタの動作信頼性が高くなる。

【0040】

また、他のチャネル供給層は、ゲート電極とドレイン電極との間のチャネル供給層上にも成長されるので、ゲート電極とドレイン電極との間のチャネル供給層の厚さは、ゲート下より厚くなる。これによって、ゲート電極とドレイン電極との間にデプリーション層が存在するとしても、ゲート電極とドレイン電極との間のチャネル層で二次元電子ガス密度は低くならない。

【図面の簡単な説明】

【0041】

【図1】本発明の一実施形態による高電子移動度トランジスタの断面図である。

【図2A】図1において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図2B】図1において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図2C】図1において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図3】図1において、ゲート電極とデプリーション層との間に絶縁層(ゲート絶縁膜)がさらに備えられた場合を示す断面図である。

【図4】本発明の他の実施形態による高電子移動度トランジスタの断面図である。

【図5】図4において、ゲート電極とデプリーション層との間に絶縁層(ゲート絶縁膜)がさらに備えられた場合を示す断面図である。

【図6】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図7】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図8】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図9】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図10】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図11】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図12】本発明の一実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図13】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図14】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図15】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図16】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図17】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図18】本発明の他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図19】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図20】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図21】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図22】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図23】本発明の一実施形態による高電子移動度トランジスタを対象として実施したシミュレーションで測定された、ゲート電極とドレイン電極との間の二次元電子ガスと二次元ホールガス密度を示すグラフである。

【図24A】図4において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図24B】図4において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図24C】図4において、デプリーション層がソース及びドレイン電極のうち少なくとも一つと離隔された場合を示す断面図である。

【図25A】本発明のさらに他の実施形態による高電子移動度トランジスタを示す断面図である。

【図25B】本発明のさらに他の実施形態による高電子移動度トランジスタを示す断面図である。

【図26A】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26B】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26C】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26D】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26E】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26F】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【図26G】本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す断面図である。

【発明を実施するための形態】

【0042】

以下、本発明の一実施形態による高電子移動度トランジスタ及びその製造方法を、添付された図面を参照して詳細に説明する。この過程で、図面に示す層や領域の厚さは、明細書の明確性のために誇張されて示されたものである。

【0043】

まず、本発明の一実施形態による高電子移動度トランジスタについて説明する。

【0044】

図1を参照すれば、基板30上にバッファ層32が形成されている。基板30は、例えば、シリコン基板、シリコンカーバイド(SiC)基板、またはアルミニウム酸化物(例えば、Al2O3)基板である。バッファ層32は、化合物半導体層である。例えば、バッファ層32は、GaN層、AlGaN層またはAlGaInN層である。基板30とバッファ層32との間に、シード層がさらに備えられてもよい。この時、シード層は、例えば、AlN層、AlGaN層である。バッファ層32上には、 二次元電子ガスG1を含む物質層34が存在する。物質層34は、化合物半導体層であり、例えば、GaN層である。二次元電子ガスG1は、物質層34の上部面下に位置する。二次元電子ガスG1は、チャネルキャリアとして使われる。このように、物質層34は、チャネルキャリアとして使われる二次元電子ガスG1を含むため、チャネルを含む物質層という意味で、以下でチャネル層34とする。チャネル層34の上部面下の一部の領域A1には、二次元電子ガスが存在しない。この領域A1は、二次元電子ガスが除去された領域であって、以下、デプリーション領域(depletion area)A1とする。チャネル層34上に、第1チャネル供給層36が存在する。第1チャネル供給層36の厚さは、20nm以上であるが、例えば、20nmないし200nmである。第1チャネル供給層36の分極率によって、その厚さは20nm以下であってもよい。第1チャネル供給層36は、化合物半導体層である。第1チャネル供給層36の分極率とバンドギャップとは、チャネル層34より大きい。チャネル層34と第1チャネル供給層36とのかかる差によって、チャネル層34に二次元電子ガスG1が現れる。第1チャネル供給層36の化合物半導体は、AlxGa(1−x−y)InyNである。ここで、xは、0<x≦1、yは、0≦y<1、0<x+y≦1である。例えば、第1チャネル供給層36は、AlN,AlGaN,AlInN及びAlGaInNのうちいずれか一つを含む。第1チャネル供給層36は、二次元電子ガスG1に対応するチャネル層34の上部面上に存在する。チャネル層34のデプリーション領域A1上には、第1チャネル供給層36が存在しない。第1チャネル供給層36上に、チャネル層34のデプリーション領域A1を覆う第2チャネル供給層38が存在する。第2チャネル供給層38は、第1チャネル供給層36の上部面の一部の領域を覆う。第1チャネル供給層36よりは及ぼす影響が少ないが、第2チャネル供給層38は、チャネル層34の二次元電子ガスG1の生成に影響を与える。第2チャネル供給層38の厚さは、20nm以下であるが、例えば、1nmより厚く、20nmより薄い。

【0045】

第1チャネル供給層36上に第2チャネル供給層38が備えられることで、二次元電子ガスG1上に存在するチャネル供給層36及び38の合計の厚さは、デプリーション領域A1上に形成されたチャネル供給層38より厚くなる。デプリーション領域A1の境界での第1チャネル供給層36の段差によって、デプリーション領域A1上で、第2チャネル供給層38は、リセスされた形態となる。かかる第2チャネル供給層38は、化合物半導体層である。第2チャネル供給層38の化合物半導体は、AlxGa(1−x−y)InyNである。ここで、xは、0<x≦1、yは、0≦y<1、0<x+y≦1である。第2チャネル供給層38の分極率は、第1チャネル供給層36より小さい。第1及び第2チャネル供給層36,38の分極率は同じであってもよいが、例えば、第2チャネル供給層38の分極率が第1チャネル供給層36の分極率と同じであってもよい。第1及び第2チャネル供給層36,38は、同じ化合物半導体層であってもよいが、その場合、第1及び第2チャネル供給層36,38の特定の成分、例えば、アルミニウム(Al)またはインジウム(In)の含量は異なる。例えば、第1及び第2チャネル供給層36,38がいずれもAlGaN層である時、第1チャネル供給層36のアルミニウム含量は35%であり、第2チャネル供給層38のアルミニウム含量は20%であり、その逆であってもよい。第1及び第2チャネル供給層36,38は、n型ドーピング物質でドーピングされたものであってもよい。シリコン(Si)がn型ドーピング物質として使われるが、これに制限されない。

【0046】

第2チャネル供給層38上にデプリーション層40が存在する。デプリーション層40は、第2チャネル供給層38のリセスされた部分とその周囲を覆う。二次元電子ガスG1上に存在するチャネル供給層36及び38の合計の厚さは、チャネル層34のデプリーション領域A1上に形成された第2チャネル供給層38より厚い。したがって、デプリーション層40による影響は、デプリーション領域A1に制限されるため、デプリーション層40の存在は、二次元電子ガスG1の密度に影響を与えない。デプリーション層40の厚さは、例えば、5ないし500nmである。

【0047】

第2チャネル供給層38により、チャネル層34のデプリーション領域A1に二次元電子ガスが現れるが、このように表れた二次元電子ガスは、デプリーション層40により除去される。このようにして、デプリーション領域A1には、二次元電子ガスが存在しなくなる。もし存在するとしても、その量は、二次元電子ガスG1と比較して非常に少ないため、その影響は無視してもよい。デプリーション層40は、化合物半導体層または窒化物層である。この時、化合物半導体層は、p型ドーピング物質でドーピングされたものであるが、例えば、GaN層、AlGaN層、AlInN層、AlInGaN層及びInGaN層のうちいずれか一つである。かかる化合物半導体層のうち、InGaN層の場合は、ドーピング物質を含まない。デプリーション層40が窒化物層である場合、デプリーション層40は、例えば、InN層である。この時、InN層は、p型ドーピング物質でドーピングされたものであるが、かかるドーピング物質を含まなくてもよい。マグネシウム(Mg)がp型ドーピング物質として使われるが、これに制限されない。デプリーション層40は、また、p型半導体層または誘電体層を備える。

【0048】

デプリーション層40は、第1チャネル供給層36との分極率の差による二次元ホールガス(2−Dimensional Hole Gas:2DHG)G2を含む。二次元ホールガスG2の形成に、第2チャネル供給層38も影響を与える。二次元ホールガスG2は、第2チャネル供給層38とデプリーション層40との界面近辺に存在する。二次元電子ガスG1を除去する時、二次元ホールガスG2を共に除去すれば、図1の高電子移動度トランジスタの空間電荷は、全体的に中性となる。したがって、図1の高電子移動度トランジスタは、絶縁破壊電圧が非常に高いスーパー接合高電子移動度トランジスタとなる。

【0049】

次いで、第1チャネル供給層36で、第2チャネル供給層38が形成されていない領域上に、ソース電極42Sとドレイン電極42Dとが形成される。ソース電極42Sとドレイン電極42Dとは、デプリーション領域A1を挟んで対向する。チャネル層34のデプリーション領域A1は、ドレイン電極42Dよりソース電極42Sに近い。ソース電極42Sとドレイン電極42Dとは、第2チャネル供給層38及びデプリーション層40に接触する。

【0050】

一方、図示していないが、第1チャネル供給層36から、ソース電極42Sとドレイン電極42Dの下に形成された部分が除去されて、ソース電極42Sとドレイン電極42Dとがチャネル層34上に形成されてもよい。かかる場合は、後述する他の実施形態にも適用される。

【0051】

再び図1を参照すれば、デプリーション層40上にゲート電極44が存在する。ゲート電極44は、チャネル層34のデプリーション領域A1上に位置する。ゲート電極44は、金属ゲートまたは窒化物ゲートである。ゲート44電極が金属ゲートである時、ゲート電極44は、デプリーション層40とオーミックコンタクトをなす第1金属、またはデプリーション層40とショットキーコンタクトをなす第2金属で形成されたものである。第1金属は、仕事関数が4.5eV以上である金属であって、例えば、ニッケル(Ni)、イリジウム(Ir)、白金(Pt)及び金(Au)のうちいずれか一つである。第2金属は、仕事関数が4.5eVより小さい金属であって、例えば、チタン(Ti)、アルミニウム(Al)、ハフニウム(Hf)、タンタル(Ta)及びタングステン(W)のうちいずれか一つである。ゲート電極44が窒化物ゲートである時、ゲート電極44は、遷移金属窒化物で形成されたものである。遷移金属窒化物は、例えば、TiN、TaNまたはWNである。また、ゲート電極44は、導電性不純物を含むポリシリコンまたはゲルマニウム(Ge)で形成されたゲート電極である。

【0052】

一方、図2Aに示すように、デプリーション層40Aは、ソース電極42S及びドレイン電極42Dと離隔される。また、図2Bに示すように、デプリーション層40Bは、ソース電極42Sと離隔され、ドレイン電極42Dとは離隔されなくてもよい。また、図2Cに示すように、デプリーション層40Cは、ドレイン電極42Dと離隔され、ソース電極42Sとは離隔されなくてもよい。ソース電極42Sとドレイン電極42Dとは、少なくとも一つの金属または金属窒化物を含むが、例えば、Au,Ni,Pt,Ti,Al,Pd,Ir,W,Mo,Ta,Cu,TiN,TaN及びWNのうち少なくとも一つを含む。ソース電極42Sとドレイン電極42Dとは、これらに制限されない。

【0053】

また、図3に示すように、ゲート電極44’とデプリーション層40との間には、漏れ電流を防止するための絶縁層46がさらに備えられる。絶縁層46は、シリコン酸化物層または窒化物層である。絶縁層46は、図2Aないし図2Cに示す高電子移動度トランジスタに適用される。

【0054】

図4は、本発明の他の実施形態による高電子移動度トランジスタを示す。図1の場合と異なる部分についてのみ説明する。

【0055】

図4を参照すれば、第1チャネル供給層36の一部の領域上に、チャネル層34のデプリーション領域A1を覆う第2デプリーション層50が備えられている。第2デプリーション層50の厚さは、例えば、1ないし100nmである。第2デプリーション層50は、p型ドーピング物質がドーピングされた化合物半導体層であるが、例えば、p型AlGaN層である。第2デプリーション層50は、また、分極誘発元素の含量が次第に変わる化合物半導体層であるが、例えば、アルミニウム(Al)の含量が下面から上面へ行くほど次第に少なくなって、分極密度が次第に低くなるpドーピング効果を有するAlGaN層である。かかる第2デプリーション層50は、AlGaN層以外にも、AlInN層またはAlInGaN層がある。第2デプリーション層50は、図1の第2チャネル供給層38と同じ位置に備えられる。第1チャネル供給層36の上部面で、第2デプリーション層50が存在しない領域上に、ソース電極42Sとドレイン電極42Dとが存在する。ソース電極42Sとドレイン電極42Dとは、第2デプリーション層50と接触する。第2デプリーション層50上にゲート電極44が存在する。

【0056】

一方、図5に示すように、第2デプリーション層50とゲート電極44’との間に、絶縁層46がさらに備えられる。

【0057】

図24Aに示すように、デプリーション層50Aは、ソース電極42S及びドレイン電極42Dから離隔される。また、図24Bに示すように、デプリーション層50Bは、ソース電極42Sと離隔され、ドレイン電極42Dとは離隔されなくてもよい。また、図24Cに示すように、デプリーション層50Cは、ドレイン電極42Dと離隔され、ソース電極42Sとは離隔されなくてもよい。

【0058】

次いで、図6ないし図11を参照して、本発明の一実施形態による高電子移動度トランジスタの製造方法を説明する。この過程で、図1ないし図5の説明で言及された部材については、同じ参照番号を使用し、関連した説明は省略する。

【0059】

図6を参照すれば、基板30上にバッファ層32を形成する。基板30とバッファ層32との間にシード層(図示せず)を形成する。バッファ層32上にチャネル層34を形成する。チャネル層34は、エピタキシー法を利用して形成する。チャネル層34上に第1チャネル供給層36’を形成する。第1チャネル供給層36’とチャネル層34との分極率の差によって、チャネル層34の上部面下に二次元電子ガスG1が現れる。第1チャネル供給層36’は、エピタキシー法を利用して形成する。第1チャネル供給層36’が、n型ドーピング物質、例えば、シリコン(Si)がドーピングされた物質層である場合、第1チャネル供給層36’を成長させる過程で、n型ドーピング物質を注入させて形成する。この時、第1チャネル供給層36’の成長及びn型ドーピング物質の注入は、イン・シチュ(in−situ)で行う。第1チャネル供給層36’を形成した後、第1チャネル供給層36’の上部面上にマスクM1を形成する。マスクM1は、第1チャネル供給層36’の上部面の一部の領域A2が露出されるように形成する。マスクM1の形成後、第1チャネル供給層36’の上部面の露出された一部の領域A2は、図1のチャネル層34のデプリーション領域A1に対応する。マスクM1を形成した後、第1チャネル供給層36’の上部面の露出された領域A2を除去する。次いで、マスクM1も除去する。

【0060】

このようにして、図7に示すように、チャネル層34の上部面の一部の領域A3が露出される。そして、一部の領域A3を挟んで離隔された第1チャネル供給層36’’が形成される。図6の第1チャネル供給層36’から、チャネル層34の露出された領域A3上に形成された部分が除去されることで、チャネル層34の露出された領域A3から二次元電子ガスG1は除去される。かかるチャネル層34の露出された領域A3は、図1のデプリーション領域A1に該当する。

【0061】

図6の第1チャネル供給層36’の一部の領域A2は、異方性ドライエッチングにより除去されるが、かかるエッチングにより、チャネル層34の上部面の露出された領域A3の表面粗度は大きくなる。したがって、チャネル層34の上部面の露出された領域A3の表面粗度を低めるために、図7の結果物をウェットエッチングする。この時、ウェットエッチングのエッチャントとして、TMAHまたはKOHを使用する。ウェットエッチングにより、チャネル層34の露出された領域A3の表面粗度(rms)は、図6の第1チャネル供給層36’を異方性のドライエッチングする前と類似したレベルに下げることができる。例えば、異方性のドライエッチング前において、チャネル層34の上部面の表面粗度は、約1Åであるが、異方性のドライエッチング後、チャネル層34の上部面の露出された領域A3の表面粗度は、約2Åに大きくなる。しかし、ウェットエッチング後、露出された領域A3の表面粗度は、再び約1Åに低くなる。

【0062】

次いで、図8を参照すれば、ウェットエッチング後、第1チャネル供給層36’’上に、チャネル層34の上部面の露出された領域A3を覆う第2チャネル供給層38’を形成する。第2チャネル供給層38’は、エピタキシー法で形成する。第2チャネル供給層38’は、第1チャネル供給層36’’と同じ組成で形成するが、組成のうち一つの成分の含量は、第1チャネル供給層36’’と異なってもよい。例えば、第2チャネル供給層38’は、第1チャネル供給層36’’と同様に、AlGaN層を成長させて形成するが、Alの含量は、第1チャネル供給層36’’より少なくして形成する。チャネル層34の露出された領域A3と第1チャネル供給層36’’との間には、段差が存在する。かかる段差は、第2チャネル供給層38’にもそのまま転写される。これによって、第2チャネル供給層38’が形成された後、チャネル層34の露出された領域A3上で、第2チャネル供給層38’は、リセスされた形態に形成される。第2チャネル供給層38’が形成された後、チャネル層34の露出された領域A3には、第2チャネル供給層38’とチャネル層34との分極率の差による第2二次元電子ガスG3が現れる。第2二次元電子ガスG3の密度は、第1チャネル供給層36’’により第1チャネル供給層36’’下のチャネル層34に現れる二次元電子ガスG1に比べて低い。

【0063】

次いで、図9を参照すれば、第2チャネル供給層38’上にデプリーション層40’を形成する。デプリーション層40’は、エピタキシー法で形成する。第2チャネル供給層38’のリセスされた形態は、デプリーション層40’にも転写される。これによって、チャネル層34の露出された領域A3上で、デプリーション層40’は、リセスされた形態に形成される。チャネル層34の露出された領域A3に現れる第2二次元電子ガスG3は、デプリーション層40’が形成されるにつれて除去される。

【0064】

デプリーション層40’上にマスクM2を形成する。マスクM2は、チャネル層34のデプリーション領域A3と、その周囲の領域に対応するデプリーション層40’の一部の領域とを覆う。マスクM2により、ソース及びドレイン電極が形成される領域が限定される。

【0065】

図10を参照すれば、マスクM2の周囲のデプリーション層40’及び第2チャネル供給層38’’が順次にエッチングされて、デプリーション層40と第2チャネル供給層38とが形成される。かかるエッチングは、第1チャネル供給層36の上部面が露出されるまで行う。エッチング後、マスクM2を除去する。かかるエッチングにおいて、第1チャネル供給層36の一部がエッチングされてもよい。かかるエッチングにより、第1チャネル供給層36の上部面の第1領域36Aと第2領域36Bとが露出される。第1及び第2領域36A,36Bは離隔されており、チャネル層34のデプリーション領域A3を挟んで対向する。第2領域36Bより第1領域36Aがデプリーション領域A3に近い。第1領域36A上には、図11に示すように、ソース電極42Sを形成し、第2領域36B上には、ドレイン電極42Dを形成する。かかるソース及びドレイン電極42S,42Dは、図10の結果からマスクM2を除去する前に、第1及び第2領域36A,36BとマスクM2上に電極物質層(図示せず)を形成した後、マスクM2を除去するリフトオフ方式により形成する。

【0066】

図11を参照すれば、ソース電極42Sとドレイン電極42Dとは、第2チャネル供給層38及びデプリーション層40と接触する。

【0067】

一方、図10の第1チャネル供給層36の上部面が露出されるエッチングにおいて、エッチングは、チャネル層34が露出されるまで行ってもよい。この場合、ソース電極42Sとドレイン電極42Dとは、チャネル層34上に形成されてもよい。

【0068】

図12を参照すれば、デプリーション層40上にゲート電極44を形成する。ゲート電極44とデプリーション層40との間に、絶縁層(ゲート絶縁膜)(図示せず)をさらに形成してもよい。

【0069】

次いで、図2Aに示す高電子移動度トランジスタの製造方法を、図13ないし図18を参照して説明する。図6ないし図12を参照して説明した製造方法と異なる部分についてのみ説明する。

【0070】

図13を参照すれば、基板30上にバッファ層32、チャネル層34、第1チャネル供給層36及び第2チャネル供給層38を形成する過程は、図6ないし図8で説明した過程と同じである。

【0071】

第2チャネル供給層38上に、第2チャネル供給層38のリセス部分とその周囲の一部とを覆うデプリーション層40Aを形成する。この時、デプリーション層40Aが覆う第2チャネル供給層38の面積は、図10でデプリーション層40が覆う第2チャネル供給層38の面積より小さい。換言すれば、図13のデプリーション層40Aのサイズは、図10のデプリーション層40のサイズより小さい。

【0072】

図14を参照すれば、第2チャネル供給層38上に、デプリーション層40Aを覆い、その周囲の第2チャネル供給層38の一部も覆うマスクM3を形成する。次いで、マスクM3の周囲の第2チャネル供給層38をエッチングして、図15に示すように、第1チャネル供給層36を露出させる。第1チャネル供給層36が露出された後、第1チャネル供給層36の露出された部分は、一定の厚さ範囲内でさらにエッチングされる。

【0073】

図16を参照すれば、第1チャネル供給層36の露出された領域上に導電層42を形成する。導電層42は、ソース及びドレイン電極42S,42Dを形成する物質である。導電層42は、マスクM3上にも形成される。導電層42を形成した後、マスクM3を除去する。マスクM3を除去する過程で、導電層42のマスクM3上に形成された部分も除去される。マスクM3が除去された後、デプリーション層40Aの両側に残った導電層42は、図17に示すように、ソース電極42S及びドレイン電極42Dとして使われる。図16において、デプリーション層40Aと導電層42とは、マスクM3により離隔された状態となる。したがって、マスクM3が除去された後、デプリーション層40A、ソース及びドレイン電極42S,42Dは、図17に示すように離隔された状態となる。マスクM3を除去した後、図18に示すように、デプリーション層40A上にゲート電極44を形成する。

【0074】

次いで、図4に示す高電子移動度トランジスタの製造方法を、図19ないし図22を参照して説明する。前述した製造方法と異なる部分についてのみ説明する。

【0075】

図19を参照すれば、第1チャネル供給層36上に、チャネル層34の上部面の露出された領域A3を覆う第2デプリーション層50’を形成する。第2デプリーション層50’は、エピタキシー法で形成する。第2デプリーション層50’において、チャネル層34の露出された領域A3上に形成された部分は、第1チャネル供給層36の段差によってリセスされた形態となる。第2デプリーション層50’上にマスクM4を形成する。マスクM4は、第2デプリーション層50’のリセスされた部分とその周囲とを覆って、第2デプリーション層50’でソース及びドレイン電極が形成される領域を限定する。このようにマスクM4を形成した後、図20に示すように、マスクM4の周囲の第2デプリーション層50の露出された部分をエッチングする。このエッチングは、第1チャネル供給層36が露出されるまで行う。

【0076】

図21を参照すれば、エッチングにより露出された第1チャネル供給層36の領域上に導電層42を形成する。導電層42は、マスクM4上にも形成される。導電層42の形成後にマスクM4を除去すれば、マスクM4上に形成された導電層42は、マスクM4と共に除去される。このようにして、導電層42は、第1チャネル供給層36上にのみ残る。第2デプリーション層50の両側の第1チャネル供給層36上に残った導電層42は、図22に示すように、ソース電極42S及びドレイン電極42Dとして使われる。第1チャネル供給層36上に残った導電層42は、第2デプリーション層50の側面と接触する。

【0077】

マスクM4を除去した後、図22に示すように、第2デプリーション層50上にゲート電極44を形成する。

【0078】

一方、図20において、マスクM4を除去した後、第2デプリーション層50を覆う他のマスクを形成した後で後続工程を進めるが、このようにすることで、ソース及びドレイン電極42S,42Dと第2デプリーション層50とが離隔される高電子移動度トランジスタを形成できる。

【0079】

図23は、チャネル層34がGaN層、第1チャネル供給層36がAl35GaN層(15nm)(または、Al20GaN層(15nm))、第2チャネル供給層38がAl20GaN層(15nm)(または、Al35GaN層(15nm))、デプリーション層40がp−GaN層である時、測定したゲート電極44とソース及びドレイン電極42S,42Dとの間の二次元電子ガスG1と二次元ホールガスG2の密度に対するシミュレーション結果を表す。

【0080】

図23において、第1ピークP1は、二次元電子ガス密度を表し、第2ピークP2は、二次元ホールガス密度を表す。

【0081】

図23を参照すれば、第1及び第2チャネル供給層36,38の組成が同じである時、各層の成分比が異なる場合でも、二次元電子ガスと二次元ホールガスとの密度は、1018/cm3以上の高さがあるということが分かる。したがって、第1及び第2チャネル供給層36,38の組成が同じである場合にも、各層の成分比を異ならせれば、ゲート電極44とドレイン電極42Dとの間のチャネル層34で、二次元電子ガス密度は高く維持でき、ゲート電極44とドレイン電極42Dとの間のデプリーション層40で、二次元ホールガス密度も高く維持できるということが分かる。

【0082】

図25Aは、本発明のさらに他の実施形態による高電子移動度トランジスタを示す。

【0083】

図25Aを参照すれば、高電子移動度トランジスタは、基板105上に離隔して形成されたソース電極110、ゲート電極112及びドレイン電極114を備える。デプリーション層104が、ゲート電極112上に形成されている。第1チャネル供給層103が、デプリーション層104の側面上に存在する。チャネル層102とパッシベーション層101とが、第1チャネル供給層103とデプリーション層104上に形成されている。

【0084】

図25Aに示すように、第1チャネル層102は、デプリーション層104との界面にデプリーション領域A1を備え、二次元電子ガスを含む第1チャネル供給層103との界面に領域G1を備える。

【0085】

図25Bは、本発明のさらに他の実施形態による高電子移動度トランジスタを示す。図25Aに示す高電子移動度トランジスタと異なる部分についてのみ説明する。

【0086】

図25Bに示すように、デプリーション層104の代わりに、デプリーション層107と第1チャネル供給層103との間に第2チャネル供給層106を備える。

【0087】

図26Aないし図26Gは、本発明のさらに他の実施形態による高電子移動度トランジスタの製造方法を段階別に示す。

【0088】

図26Aを参照すれば、電極層116が基板105上に形成される。基板105は、例えば、シリコン基板、シリコンカーバイド(SiC)基板、またはアルミニウム酸化物基板(例えば、Al2O3)である。しかし、基板105は、かかる基板に限定されない。電極層116は、金属または金属窒化物を含む。図26Bに示すように、電極層116は、ソース電極110、ゲート電極112及びドレイン電極114にパターニングされる。図26Cに示すように、デプリーション層104’は、ソース電極110、ゲート電極112及びドレイン電極114上に形成される。デプリーション層104’は、図4で説明したデプリーション層50と同じ物質を含むが、かかる物質に制限されない。

【0089】

次いで、図26Dに示すように、ソース電極110、ゲート電極112及びドレイン電極114上に形成されたデプリーション層104’をエッチバックして、デプリーション層104を形成する。図26Eに示すように、第1チャネル供給層103’がデプリーション層104上に形成される。第1チャネル供給層103’は、図4で説明した第1チャネル供給層36と同じ物質を含むが、かかる物質に制限されない。図26Fに示すように、第1チャネル供給層103’をエッチバックすることで、第1チャネル供給層103が形成される。第1チャネル供給層103は、デプリーション層104を部分的に露出させてもよい。

【0090】

次いで、図26Gに示すように、チャネル層102及びパッシベーション層101が、第1チャネル供給層103上に順次に形成される。チャネル層102は、図4で説明したチャネル層34と同じ物質を含むが、かかる物質に制限されない。パッシベーション層101は、絶縁物質または絶縁ポリマー物質を含むが、かかる物質に限定されない。この時、絶縁物質は、シリコン酸化物のような酸化物である。

【0091】

図26Aないし図26Gは、デプリーション層104を備える高電子移動度トランジスタを形成する方法の一例を示すが、デプリーション層104を形成する代わりに、図25Bに示すように、デプリーション層107が第2チャネル供給層106上に形成されてもよい。

【0092】

図25Bを参照すれば、第2チャネル供給層106及びデプリーション層107は、それぞれ図1で説明した第2チャネル供給層38及びデプリーション層40と同じ物質を含んでもよい。

【0093】

前述の説明で多くの事項が具体的に記載されているが、それらは、発明の範囲を限定するというより、望ましい実施形態の例示として解釈されねばならない。したがって、本発明の範囲は、説明された実施形態により決まるものではなく、特許請求の範囲に記載された技術的思想により決まらねばならない。

【産業上の利用可能性】

【0094】

本発明は、高周波素子関連の技術分野に適用可能である。

【符号の説明】

【0095】

30 基板

32 バッファ層

34 チャネル層

36 第1チャネル供給層

38 第2チャネル供給層

40,40A,40B,40C デプリーション層

42D ドレイン電極

42S ソース電極

44 ゲート電極

A1 デプリーション領域

G1 二次元電子ガス

G2 二次元ホールガス

【特許請求の範囲】

【請求項1】

化合物半導体を含む基板と、

前記基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、

前記二次元電子ガスチャネルに対応するように、前記チャネル層上に形成された第1チャネル供給層と、

前記チャネル層の前記デプリーション領域及び前記第1チャネル供給層の一部の領域上に形成されたデプリーション層と、

前記第1チャネル供給層及び前記チャネル層のうちいずれか一つの上に形成され、前記デプリーション領域を挟んで対向するソース及びドレイン電極と、

前記デプリーション層上に形成されたゲート電極と、を備えることを特徴とする、高電子移動度トランジスタ。

【請求項2】

前記第1チャネル供給層より分極率が小さい第2チャネル供給層を、前記チャネル層の前記デプリーション領域及び前記第1チャネル供給層の一部の領域上に備え、前記デプリーション層が、前記第2チャネル供給層上に備えられることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項3】

前記ソース及びドレイン電極が、前記デプリーション層と接触または離隔することを特徴とする、請求項1または2に記載の高電子移動度トランジスタ。

【請求項4】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられることを特徴とする、請求項1または2に記載の高電子移動度トランジスタ。

【請求項5】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項6】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項7】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項8】

前記第1チャネル供給層の厚さが、20nmないし200nmであることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項9】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項10】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であることを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項11】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記第2チャネル供給層の厚さが、5ないし20nmであることを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項12】

前記ゲート電極が、p−金属または窒化物であることを特徴とする、請求項1または2に記載の高電子移動度トランジスタ。

【請求項13】

前記第1及び第2チャネル供給層が、同じ分極率を有することを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項14】

二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、

前記デプリーション領域を露出させる開口を限定し、前記二次元電子ガスチャネル上に形成された第1チャネル供給層と、

前記第1チャネル供給層及び前記デプリーション領域上に形成されたデプリーション層と、

前記第1チャネル供給層上に形成され、互いに離隔されたソース及びドレイン電極と、

前記デプリーション層上に形成されたゲート電極と、を備え、

前記デプリーション層が、窒素(N)を含有し、アルミニウム(Al)、ガリウム(Ga)及びインジウム(In)のうち少なくとも一つを含有する化合物半導体を含むことを特徴とする、トランジスタ。

【請求項15】

前記デプリーション層と前記デプリーション領域との間に、第2チャネル供給層をさらに備えることを特徴とする、請求項14に記載のトランジスタ。

【請求項16】

前記第2チャネル供給層の分極率が、前記第1チャネル供給層の分極率より小さいことを特徴とする、請求項15に記載のトランジスタ。

【請求項17】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられることを特徴とする、請求項14に記載のトランジスタ。

【請求項18】

前記デプリーション層が、p型ドーパントを含むことを特徴とする、請求項14に記載のトランジスタ。

【請求項19】

前記デプリーション層の分極率が、前記第1チャネル供給層の分極率より小さいことを特徴とする、請求項14に記載のトランジスタ。

【請求項20】

基板と、

前記基板上に形成され、互いに離隔されたソース電極、ドレイン電極及びゲート電極と、

前記ゲート電極上に形成されたデプリーション層と、

前記デプリーション層の少なくとも一部の上に形成された第1チャネル供給層と、

前記デプリーション層及び前記第1チャネル供給層上に形成されたチャネル層と、を備え、

前記チャネル層が、前記第1チャネル供給層に対応する二次元電子ガスチャネルと、前記デプリーション層に対応するデプリーション領域とを備えることを特徴とする、高電子移動度トランジスタ。

【請求項21】

基板上にチャネル層を形成するステップと、

前記チャネル層上に、前記チャネル層より分極率が大きい第1チャネル供給層を形成するステップと、

前記第1チャネル供給層の一部を除去して、前記チャネル層の一部を露出させるステップと、

前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆うデプリーション層を形成するステップと、

前記第1チャネル供給層上に、前記デプリーション層を挟んで対向するソース及びドレイン電極を形成するステップと、

前記デプリーション層上にゲート電極を形成するステップと、を含むことを特徴とする、高電子移動度トランジスタの製造方法。

【請求項22】

前記デプリーション層を形成する前に、前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆って、前記第1チャネル供給層より分極率が小さい第2チャネル供給層を形成し、前記デプリーション層が、前記第2チャネル供給層上に形成されることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項23】

前記ゲート電極と前記デプリーション層との間に、絶縁層を形成するステップをさらに含むことを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項24】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項25】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項26】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項27】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記デプリーション層の厚さが、5ないし20nmであることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項28】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項29】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項30】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記第2チャネル供給層の厚さが、5ないし20nmであることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項31】

前記ゲート電極が、p−金属または窒化物であることを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項32】

前記デプリーション層が、エピタキシー法で形成されることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項33】

前記第2チャネル供給層及び前記デプリーション層が、エピタキシー法で形成されることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項34】

前記ソース及びドレイン電極が、前記デプリーション層と離隔して形成されることを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項35】

前記デプリーション層を形成する前に、前記チャネル層の露出された領域の表面粗度を緩和させることを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項36】

前記チャネル層の露出された領域をウェットエッチングして、前記表面粗度を緩和させることを特徴とする、請求項35に記載の高電子移動度トランジスタの製造方法。

【請求項37】

前記第1及び第2チャネル供給層の分極率が、同じであることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項1】

化合物半導体を含む基板と、

前記基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、

前記二次元電子ガスチャネルに対応するように、前記チャネル層上に形成された第1チャネル供給層と、

前記チャネル層の前記デプリーション領域及び前記第1チャネル供給層の一部の領域上に形成されたデプリーション層と、

前記第1チャネル供給層及び前記チャネル層のうちいずれか一つの上に形成され、前記デプリーション領域を挟んで対向するソース及びドレイン電極と、

前記デプリーション層上に形成されたゲート電極と、を備えることを特徴とする、高電子移動度トランジスタ。

【請求項2】

前記第1チャネル供給層より分極率が小さい第2チャネル供給層を、前記チャネル層の前記デプリーション領域及び前記第1チャネル供給層の一部の領域上に備え、前記デプリーション層が、前記第2チャネル供給層上に備えられることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項3】

前記ソース及びドレイン電極が、前記デプリーション層と接触または離隔することを特徴とする、請求項1または2に記載の高電子移動度トランジスタ。

【請求項4】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられることを特徴とする、請求項1または2に記載の高電子移動度トランジスタ。

【請求項5】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項6】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項7】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項8】

前記第1チャネル供給層の厚さが、20nmないし200nmであることを特徴とする、請求項1に記載の高電子移動度トランジスタ。

【請求項9】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項10】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であることを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項11】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記第2チャネル供給層の厚さが、5ないし20nmであることを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項12】

前記ゲート電極が、p−金属または窒化物であることを特徴とする、請求項1または2に記載の高電子移動度トランジスタ。

【請求項13】

前記第1及び第2チャネル供給層が、同じ分極率を有することを特徴とする、請求項2に記載の高電子移動度トランジスタ。

【請求項14】

二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、

前記デプリーション領域を露出させる開口を限定し、前記二次元電子ガスチャネル上に形成された第1チャネル供給層と、

前記第1チャネル供給層及び前記デプリーション領域上に形成されたデプリーション層と、

前記第1チャネル供給層上に形成され、互いに離隔されたソース及びドレイン電極と、

前記デプリーション層上に形成されたゲート電極と、を備え、

前記デプリーション層が、窒素(N)を含有し、アルミニウム(Al)、ガリウム(Ga)及びインジウム(In)のうち少なくとも一つを含有する化合物半導体を含むことを特徴とする、トランジスタ。

【請求項15】

前記デプリーション層と前記デプリーション領域との間に、第2チャネル供給層をさらに備えることを特徴とする、請求項14に記載のトランジスタ。

【請求項16】

前記第2チャネル供給層の分極率が、前記第1チャネル供給層の分極率より小さいことを特徴とする、請求項15に記載のトランジスタ。

【請求項17】

前記ゲート電極と前記デプリーション層との間に、絶縁層がさらに備えられることを特徴とする、請求項14に記載のトランジスタ。

【請求項18】

前記デプリーション層が、p型ドーパントを含むことを特徴とする、請求項14に記載のトランジスタ。

【請求項19】

前記デプリーション層の分極率が、前記第1チャネル供給層の分極率より小さいことを特徴とする、請求項14に記載のトランジスタ。

【請求項20】

基板と、

前記基板上に形成され、互いに離隔されたソース電極、ドレイン電極及びゲート電極と、

前記ゲート電極上に形成されたデプリーション層と、

前記デプリーション層の少なくとも一部の上に形成された第1チャネル供給層と、

前記デプリーション層及び前記第1チャネル供給層上に形成されたチャネル層と、を備え、

前記チャネル層が、前記第1チャネル供給層に対応する二次元電子ガスチャネルと、前記デプリーション層に対応するデプリーション領域とを備えることを特徴とする、高電子移動度トランジスタ。

【請求項21】

基板上にチャネル層を形成するステップと、

前記チャネル層上に、前記チャネル層より分極率が大きい第1チャネル供給層を形成するステップと、

前記第1チャネル供給層の一部を除去して、前記チャネル層の一部を露出させるステップと、

前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆うデプリーション層を形成するステップと、

前記第1チャネル供給層上に、前記デプリーション層を挟んで対向するソース及びドレイン電極を形成するステップと、

前記デプリーション層上にゲート電極を形成するステップと、を含むことを特徴とする、高電子移動度トランジスタの製造方法。

【請求項22】

前記デプリーション層を形成する前に、前記第1チャネル供給層上に、前記チャネル層の露出された領域を覆って、前記第1チャネル供給層より分極率が小さい第2チャネル供給層を形成し、前記デプリーション層が、前記第2チャネル供給層上に形成されることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項23】

前記ゲート電極と前記デプリーション層との間に、絶縁層を形成するステップをさらに含むことを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項24】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、p型ドーピング物質でドーピングされた化合物半導体層であることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項25】

前記デプリーション層が、分極率が前記第1チャネル供給層より小さく、分極誘発主成分の含量が厚さによって変わる化合物半導体層であることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項26】

前記第1チャネル供給層が、n型ドーピング物質でドーピングされたものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項27】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記デプリーション層の厚さが、5ないし20nmであることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項28】

前記デプリーション層が、p型ドーピング物質がドーピングされるか、またはドーピングされていないものであって、Al,Ga及びInのうち少なくとも一つを含む窒化物層であることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項29】

前記第1及び第2チャネル供給層が、組成が同じであり、組成比が異なる化合物半導体層であることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項30】

前記第1チャネル供給層の厚さが、20nmないし200nmであり、前記第2チャネル供給層の厚さが、5ないし20nmであることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項31】

前記ゲート電極が、p−金属または窒化物であることを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項32】

前記デプリーション層が、エピタキシー法で形成されることを特徴とする、請求項21に記載の高電子移動度トランジスタの製造方法。

【請求項33】

前記第2チャネル供給層及び前記デプリーション層が、エピタキシー法で形成されることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【請求項34】

前記ソース及びドレイン電極が、前記デプリーション層と離隔して形成されることを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項35】

前記デプリーション層を形成する前に、前記チャネル層の露出された領域の表面粗度を緩和させることを特徴とする、請求項21または22に記載の高電子移動度トランジスタの製造方法。

【請求項36】

前記チャネル層の露出された領域をウェットエッチングして、前記表面粗度を緩和させることを特徴とする、請求項35に記載の高電子移動度トランジスタの製造方法。

【請求項37】

前記第1及び第2チャネル供給層の分極率が、同じであることを特徴とする、請求項22に記載の高電子移動度トランジスタの製造方法。

【図1】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図24A】

【図24B】

【図24C】

【図25A】

【図25B】

【図26A】

【図26B】

【図26C】

【図26D】

【図26E】

【図26F】

【図26G】

【図23】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図24A】

【図24B】

【図24C】

【図25A】

【図25B】

【図26A】

【図26B】

【図26C】

【図26D】

【図26E】

【図26F】

【図26G】

【図23】

【公開番号】特開2013−89973(P2013−89973A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2012−231776(P2012−231776)

【出願日】平成24年10月19日(2012.10.19)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成24年10月19日(2012.10.19)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]