アイソレータ用回路基板、アイソレータおよびそれらの製造方法

【課題】コイルの設計の自由度の向上および小型化が可能でかつ容易に製造可能なアイソレータ用回路基板およびアイソレータならびにそれらの製造方法を提供することである。

【解決手段】回路基板10の上面にコイルCAが形成される。回路基板10の下面にコイルCBおよび配線パターンPBが形成される。回路基板20の上面にコイルCCが形成される。回路基板20の下面にコイルCDおよび配線パターンPDが形成される。複数のコイルCA,CB,CC、CDが互いに重なるように回路基板10,20が配置される。コイルCA,CB,CC,CDが送信チップ40および受信チップ50に重なるように回路基板10,20が送信チップ40上、受信チップ50上およびリードフレーム30上に配置される。

【解決手段】回路基板10の上面にコイルCAが形成される。回路基板10の下面にコイルCBおよび配線パターンPBが形成される。回路基板20の上面にコイルCCが形成される。回路基板20の下面にコイルCDおよび配線パターンPDが形成される。複数のコイルCA,CB,CC、CDが互いに重なるように回路基板10,20が配置される。コイルCA,CB,CC,CDが送信チップ40および受信チップ50に重なるように回路基板10,20が送信チップ40上、受信チップ50上およびリードフレーム30上に配置される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アイソレータ用回路基板、アイソレータ、アイソレータ用回路基板の製造方法およびアイソレータの製造方法に関する。

【背景技術】

【0002】

従来より、入力信号と出力信号との分離のために、アイソレータが用いられる(例えば特許文献1および2参照)。特許文献1および2に記載されたアイソレータでは、アイソレータ用回路基板に複数のコイルが形成されるとともにアイソレータ用回路基板の複数のコイルとは異なる領域上に受信チップおよび送信チップが実装されている。アイソレータ用回路基板の複数のコイルは、複数のワイヤを用いて受信チップおよび送信チップに接続される。

【0003】

近年、MEMS(Micro Electro Mechanical Systems)技術を用いたアイソレータが開発されている。このアイソレータでは、複数のコイルがチップ(以下、コイルチップと呼ぶ)上にMEMS技術により微細に形成される。コイルチップは、受信チップおよび送信チップとともにリードフレーム上に配置される。コイルチップは、ワイヤにより受信チップおよび送信チップに接続される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−61236号公報

【特許文献2】特開2010−74621号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記の従来のアイソレータ用回路基板に形成されるコイルの寸法に制限はない。しかしながら、アイソレータ用回路基板のコイルとは異なる領域に受信チップおよび送信チップを実装するために、アイソレータ用回路基板の面積が大きくなる。それにより、アイソレータの全体の大きさが大きくなる。

【0006】

一方、MEMS技術によれば、コイルチップを小型化することが可能となる。それにより、アイソレータを小型化することができる。しかしながら、MEMS技術により形成されるコイルチップには、寸法上の制約がある。例えば、コイルチップに形成されるコイルの線幅および線間隔を大きくすることは困難である。そのため、コイルの抵抗を十分に小さくすることが困難である。

【0007】

また、従来のアイソレータ用回路基板を用いたアイソレータおよびMEMS技術を用いたアイソレータにおいては、コイルを受信チップおよび送信チップに接続するためにワイヤボンディングが必要となる。そのため、製造工程が煩雑となる。

【0008】

本発明の目的は、コイルの設計の自由度の向上および小型化が可能でかつ容易に製造可能なアイソレータ用回路基板およびアイソレータならびにそれらの製造方法を提供することである。

【課題を解決するための手段】

【0009】

(1)第1の発明に係るアイソレータ用回路基板は、第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板であって、第1の回路基板と、第2の回路基板とを備え、第1の回路基板は、第1のコイルと、第1のコイルに電気的に接続される第1の接続部とを含み、第2の回路基板は、第2のコイルと、第2のコイルに電気的に接続される第2の接続部とを含み、第1および第2の接続部は、第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板が配置されるとともに第1および第2のコイルに重なるように第1および第2の電子部品が配置された場合に、第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられるものである。

【0010】

そのアイソレータ用回路基板をアイソレータに用いた場合、アイソレータ用回路基板の第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板を配置するとともに、第1および第2のコイルに重なるように第1および第2の電子部品を配置することにより、第1の回路基板の第1の接続部を第1の電子部品の端子に接続し、第2の回路基板の第2の接続部を第2の電子部品の端子に接続することができる。

【0011】

このように、第1および第2のコイルに重なるように第1および第2の電子部品を配置することができるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【0012】

(2)アイソレータはリードフレームをさらに有し、第1の回路基板は、第1の配線パターンと、第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、第2の回路基板は、第2の配線パターンと、第2の配線パターンに電気的に接続される第4の接続部とをさらに含み、第3および第4の接続部は、リードフレーム上に第1および第2の電子部品が配置された場合に、リードフレームに接触可能な位置に設けられてもよい。

【0013】

この場合、リードフレーム上に第1および第2の電子部品を配置することにより、第3および第4の接続部をリードフレームに接続することができる。したがって、ワイヤボンディングを用いることなく第1の回路基板の第1の配線パターンおよび第2の回路基板の第2の配線パターンをリードフレームに電気的に接続することができる。その結果、リードフレームを有する小型のアイソレータを容易に製造することが可能となる。

【0014】

(3)第3の接続部は、第1の電子部品の厚み方向において第1の接続部よりも大きな高さを有し、第4の接続部は、第2の電子部品の厚み方向において第2の接続部よりも大きな高さを有してもよい。

【0015】

この場合、第1および第2の回路基板とリードフレームとの間に第1および第2の電子部品を配置した状態で、第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子に容易に接続するとともに第1および第2の回路基板の第3および第4の接続部をリードフレームに容易に接続することができる。

【0016】

(4)第1の回路基板は、一主面および他主面を有する第1の絶縁層と、第1の絶縁層の他主面に設けられ、第1のコイルの少なくとも一部分を構成する第1の導体層と、第1の導体層を覆うように第1の絶縁層の他主面上に形成される第1の被覆層とを含み、第2の回路基板は、一主面および他主面を有する第2の絶縁層と、第2の絶縁層の一主面に設けられ、第2のコイルの少なくとも一部分を構成する第2の導体層と、第2の導体層を覆うように第2の絶縁層の一主面上に形成される第2の被覆層とを含んでもよい。

【0017】

この場合、第1の回路基板の第1のコイルが第1の被覆層で被覆されるとともに第2の回路基板の第2のコイルが第2の被覆層で被覆される。それにより、第1のコイルと第2のコイルとの間の絶縁性が十分に確保される。

【0018】

(5)第1および第2の回路基板は、第1の絶縁層の他主面が第2の絶縁層の一主面に向き合うように重ねられ、第1および第3の接続部は、第1の絶縁層の他主面上の第1の被覆層上に設けられ、第2および第4の接続部は、第2の絶縁層の他主面上に設けられてもよい。

【0019】

この場合、第1の回路基板の第1のコイルと第2の回路基板の第2のコイルとを第1および第2の被覆層を挟んで対向させることができる。それにより、第1のコイルと第2のコイルとの間隔を小さくすることができる。その結果、アイソレータ用回路基板の面積を増加させることなく、第1および第2のコイルのインダクタンスを大きくすることが可能となる。

【0020】

(6)第1の回路基板は、第1の絶縁層の一主面に設けられ、第1のコイルの他の部分を構成する第3の導体層と、第3の導体層を覆うように第1の絶縁層の一主面上に形成される第3の被覆層とをさらに含み、第2の回路基板は、第2の絶縁層の他主面に設けられ、第2のコイルの他の部分を構成する第4の導体層と、第4の導体層を覆うように第2の絶縁層の他主面上に形成される第4の被覆層とを含んでもよい。

【0021】

この場合、第1のコイルが第1の回路基板の両面に形成され、第2のコイルが第2の回路基板の両面に形成される。それにより、第1および第2の回路基板の面積を増加させることなく、第1および第2のコイルの巻き数を増加させることができる。その結果、アイソレータ用回路基板の面積を増加させることなく、第1および第2のコイルのインダクタンスを大きくすることが可能となる。

【0022】

(7)第2の発明に係るアイソレータは、アイソレータ用回路基板と、第1および第2の電子部品とを備え、アイソレータ用回路基板は、第1の回路基板と、第2の回路基板とを備え、第1の回路基板は、第1のコイルと、第1のコイルに電気的に接続される第1の接続部とを含み、第2の回路基板は、第2のコイルと、第2のコイルに電気的に接続される第2の接続部とを含み、アイソレータ用回路基板の第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板が配置されるとともに、第1および第2のコイルに重なるように第1および第2の電子部品が配置され、第1の回路基板の第1の接続部が第1の電子部品の端子に接続され、第2の回路基板の第2の接続部が第2の電子部品の端子に接続されるものである。

【0023】

そのアイソレータにおいては、第1および第2のコイルに重なるように第1および第2の電子部品が配置されるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【0024】

(8)アイソレータは、リードフレームをさらに有し、第1の回路基板は、第1の配線パターンと、第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、第2の回路基板は、第2の配線パターンとをさらに含み、リードフレーム上に第1および第2の電子部品が配置され、第3および第4の接続部がリードフレームに接続されてもよい。

【0025】

この場合、リードフレーム上に第1および第2の電子部品が配置され、第3および第4の接続部がリードフレームに接続される。したがって、ワイヤボンディングを用いることなく第1の回路基板の第1の配線パターンおよび第2の回路基板の第2の配線パターンをリードフレームに電気的に接続することができる。その結果、リードフレームを有する小型のアイソレータを容易に製造することが可能となる。

【0026】

(9)第3の発明に係るアイソレータ用回路基板の製造方法は、第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板の製造方法であって、第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程とを備え、第1および第2の接続部は、第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板が配置されるとともに第1および第2のコイルに重なるように第1および第2の電子部品が配置された場合に、第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられるものである。

【0027】

その方法により製造されたアイソレータ用回路基板をアイソレータの製造に用いる場合、アイソレータ用回路基板の第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板を配置するとともに、第1および第2のコイルに重なるように第1および第2の電子部品を配置する。それにより、第1の回路基板の第1の接続部を第1の電子部品の端子に接続し、第2の回路基板の第2の接続部を第2の電子部品の端子に接続することができる。

【0028】

このように、第1および第2のコイルに重なるように第1および第2の電子部品を配置することができるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【0029】

(10)第4の発明に係るアイソレータの製造方法は、第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程と、第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板を配置するとともに第1および第2のコイルに重なるように第1および第2の電子部品を配置し、第1および第2の接続部をそれぞれ第1および第2の電子部品の端子に接続する工程とを含むものである。

【0030】

そのアイソレータの製造方法によれば、第1および第2のコイルに重なるように第1および第2の電子部品が配置されるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【発明の効果】

【0031】

本発明によれば、コイルの設計の自由度が向上するとともに、アイソレータの小型化が可能でかつアイソレータを容易に製造することが可能となる。

【図面の簡単な説明】

【0032】

【図1】本発明の一実施の形態に係るアイソレータの断面図である。

【図2】図1のアイソレータに用いられるアイソレータ用回路基板の平面図である。

【図3】アイソレータ用回路基板を構成する一方の回路基板の上面図である。

【図4】図3の回路基板の下面図である。

【図5】アイソレータ用回路基板を構成する他方の回路基板の上面図である。

【図6】図5の回路基板の下面図である。

【図7】図1のアイソレータに用いられるリードフレームの平面図である。

【図8】アイソレータ用回路基板を構成する回路基板の製造工程を示す断面図である。

【図9】アイソレータ用回路基板を用いたアイソレータの製造方法を示す断面図である。

【図10】本発明の他の実施の形態に係るアイソレータの断面図である。

【図11】本発明のさらに他の実施の形態に係るアイソレータの断面図である。

【図12】比較例のアイソレータの平面図である。

【発明を実施するための形態】

【0033】

以下、本発明の実施の形態に係るアイソレータ用回路基板、アイソレータおよびそれらの製造方法について図面を参照しながら説明する。

【0034】

(1)構成

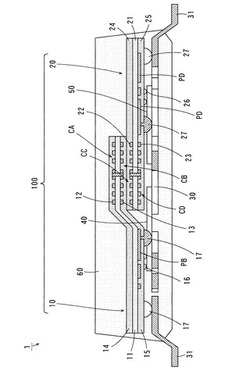

図1は本発明の一実施の形態に係るアイソレータの断面図であり、図2は図1のアイソレータに用いられるアイソレータ用回路基板の平面図である。

【0035】

図1に示すように、アイソレータ1は、アイソレータ用回路基板100、リードフレーム30、送信チップ40、受信チップ50およびパッケージ60により構成される。アイソレータ用回路基板100は、フレキシブル配線回路基板(以下、回路基板と呼ぶ)10,20からなる。

【0036】

回路基板10は、例えばポリイミドからなるベース絶縁層11を有する。ベース絶縁層11の上面には、所定のパターンを有する導体層12が形成される。導体層12によりコイルCAが構成される。ベース絶縁層11の下面には、所定のパターンを有する導体層13が形成される。導体層13によりコイルCBおよび配線パターンPB(図2参照)が構成される。導体層12,13は例えば銅からなる。コイルCA,CBは互いに重なる位置に形成される。導体層12を覆うようにベース絶縁層11の上面上に例えばポリイミドからなるカバー絶縁層14が形成される。導体層13を覆うようにベース絶縁層11の下面上に例えばポリイミドからなるカバー絶縁層15が形成される。

【0037】

回路基板20は、例えばポリイミドからなるベース絶縁層21を有する。ベース絶縁層21の上面には、所定のパターンを有する導体層22が形成される。導体層22によりコイルCCが構成される。ベース絶縁層21の下面には、所定のパターンを有する導体層23が形成される。導体層23によりコイルCDおよび配線パターンPD(図2参照)が構成される。導体層22,23は例えば銅からなる。コイルCC,CDは互いに重なる位置に形成される。導体層22を覆うようにベース絶縁層21の上面上に例えばポリイミドからなるカバー絶縁層24が形成される。導体層23を覆うようにベース絶縁層21の下面上に例えばポリイミドからなるカバー絶縁層25が形成される。

【0038】

回路基板10のカバー絶縁層15の下面には、複数の半田バンプ16,17が設けられる。回路基板20のカバー絶縁層25の下面には、複数の半田バンプ26,27が設けられる。半田バンプ17,27の高さは、半田バンプ16,26の高さよりも、送信チップ40および受信チップ50の厚み分小さい。

【0039】

リードフレーム30上に送信チップ40および受信チップ50が配置される。リードフレーム30は、後述する複数の部分により構成されるともに、複数の外部端子31を有する。複数のコイルCA,CB,CC,CDが互いに重なるように回路基板10,20が配置される。また、コイルCA,CB,CC,CDが送信チップ40および受信チップ50に重なるように回路基板10,20が送信チップ40上、受信チップ50上およびリードフレーム30上に配置される。半田バンプ16は送信チップ40の上面の端子に接合され、半田バンプ26は受信チップ50の上面の端子に接合される。半田バンプ17,27はリードフレーム30の上面に接合される。この状態でリードフレーム30の外部端子31を除く部分、送信チップ40、受信チップ50およびアイソレータ用回路基板100が封止樹脂からなるパッケージ60に収容される。

【0040】

図3はアイソレータ用回路基板100を構成する一方の回路基板10の上面図である。図4は図3の回路基板10の下面図である。図3および図4では、カバー絶縁層14,15の図示が省略されている。

【0041】

図3に示すように、回路基板10のベース絶縁層11(図1参照)の上面上には、複数(本例では2つ)のコイルCAが設けられる。図4に示すように、回路基板10のベース絶縁層11(図1参照)の下面上には、複数(本例では2つ)のコイルCBおよび複数の配線パターンPBが設けられる。コイルCAとコイルCBとは互いに重なるように配置される。

【0042】

上面のコイルCAの中心の端部は接続層18を通して下面のコイルCBの中心の端部に接続される。それにより、コイルCAとコイルCBとが直列に接続される。また、コイルCAとコイルCBとは、上面側から見て逆向きの渦巻き状に延びる。それにより、コイルCAおよびコイルCBに同じ向きに電流が流れる。

【0043】

上面の複数のコイルCAの外側の端部にはそれぞれ端子部TAが設けられる。ベース絶縁層11の下面には、上面の端子部TAに重なるように端子部TBが設けられる。上面の端子部TAと下面の端子部TBとは接続層18(図3)を通して接続される。下面の複数のコイルCBの端部にはそれぞれ端子部TBが形成される。

【0044】

複数の端子部TBおよび配線パターンPBの一端部には、それぞれ半田バンプ16が形成される。複数の半田バンプ16は、送信チップ40の上面の複数の端子に接触可能な位置に設けられる。複数の配線パターンPBの他端部には、矩形のパッドが形成され、そのパッドにそれぞれ半田バンプ17が形成される。複数の半田バンプ17は、後述するリードフレーム30の各部分に接触可能な位置に設けられる。

【0045】

図5はアイソレータ用回路基板100を構成する他方の回路基板20の上面図である。図6は図5の回路基板20の下面図である。図5および図6では、カバー絶縁層24,25の図示が省略されている。

【0046】

図5に示すように、回路基板20のベース絶縁層21(図1参照)の上面上には、複数(本例では2つ)のコイルCCが設けられる。図6に示すように、回路基板20のベース絶縁層21(図1参照)の下面上には、複数(本例では2つ)のコイルCDおよび複数の配線パターンPDが設けられる。コイルCCとコイルCDとは互いに重なるように配置される。

【0047】

上面のコイルCCの中心の端部は接続層28を通して下面のコイルCDの中心の端部に接続される。上面のコイルCCの中心の端部は接続層28を通して下面のコイルCDの中心の端部に接続される。それにより、コイルCCとコイルCDとが直列に接続される。また、コイルCCとコイルCDとは、上面側から見て逆向きの渦巻き状に延びる。それにより、コイルCCおよびコイルCDに同じ向きに電流が流れる。

【0048】

上面の複数のコイルCCの外側の端部にはそれぞれ端子部TCが設けられる。ベース絶縁層21の下面には、上面の端子部TCに重なるように端子部TDが設けられる。上面の端子部TCと下面の端子部TDとは接続層28(図5)を通して接続される。下面の複数のコイルCDの端部にはそれぞれ端子部TDが形成される。

【0049】

複数の端子部TDおよび配線パターンPDの一端部には、それぞれ半田バンプ26が形成される。複数の半田バンプ26は、受信チップ50の上面の複数の端子に接触可能な位置に設けられる。複数の配線パターンPDの他端部には、矩形のパッドが形成され、そのパッドにそれぞれ半田バンプ27が形成される。複数の半田バンプ27は、後述するリードフレーム30の各部分に接触可能な位置に設けられる。

【0050】

回路基板10のコイルCA,CBにより第1のコイルが構成され、回路基板20のコイルCC,CDにより第2のコイルが構成される。第1のコイルと第2のコイルとによりトランスが構成される。

【0051】

図7は図1のアイソレータ1に用いられるリードフレーム30の平面図である。図7においては、リードフレーム30の外部端子31の図示が省略されている。

【0052】

リードフレーム30は、銅、アルミニウムまたはステンレス等の金属材料からなり、複数のリード部32および支持部34,35により構成される。各リード部32には、回路基板10の半田バンプ17または回路基板20の半田バンプ27が接合される。支持部34には送信チップ40が取り付けられる。支持部35には受信チップ50が取り付けられる。

【0053】

図3および図4に示す送信チップ40の複数の端子は、回路基板10の半田バンプ16、配線パターンPBおよび半田バンプ17を通して図7のリードフレーム30の複数のリード部32にそれぞれ接続される。また、図5および図6に示す受信チップ50の複数の端子は、回路基板20の半田バンプ26、配線パターンPDおよび半田バンプ27を通して図7のリードフレーム30の複数のリード部32にそれぞれ接続される。

【0054】

コイルCA,CB,CC,CDを構成する線路の厚み(導体層12,13,22,23の厚み)は、例えば5μm以上35μm以下であり、9μm以上18μm以下であることが好ましい。コイルCA,CB,CC,CDを構成する線路の幅は、例えば30μm以上150μm以下であり、50μm以上100μm以下であることが好ましい。また、コイルCA,CB,CC.CDを構成する線路の間隔は、例えば30μm以上150μm以下であり、50μm以上100μm以下であることが好ましい。

【0055】

ベース絶縁層11,21の厚みは、例えば5μm以上150μm以下であり、25μm以上100μm以下であることが好ましい。カバー絶縁層14,15,24,25の厚みは、例えば5μm以上150μm以下であり、25μm以上100μm以下であることが好ましい。

【0056】

半田バンプ16,26の直径は、例えば30μm以上100μm以下であり、50μm以上75μm以下であることが好ましい。半田バンプ17,27の直径は、例えば100μm以上500μm以下であり、150μm以上350μm以下であることが好ましい。

【0057】

ベース絶縁層11,21およびカバー絶縁層14,15,24,25の材料として、ポリイミドの代わりに、液晶ポリマーまたはポリエステル等を用いることができる。また、導体層12,13,22,23の材料として、銅の代わりに、金(Au)、アルミニウム等の他の金属、または銅合金、アルミニウム合金等の合金を用いることができる。

【0058】

(2)製造方法

次に、本実施の形態に係るアイソレータ用回路基板100およびそれを用いたアイソレータ1の製造方法の一例について説明する。

【0059】

図8はアイソレータ用回路基板100を構成する回路基板10の製造工程を示す断面図である。図9はアイソレータ用回路基板100を用いたアイソレータ1の製造方法を示す断面図である。

【0060】

まず、図8(a)に示すように、ポリイミドからなるベース絶縁層11の上面および下面に銅からなる導体層12,13が積層された三層基材を用意する。

【0061】

次に、図8(b)に示すように、導体層12をエッチングすることによりベース絶縁層11の上面にサブトラクティブ法によりコイルCAおよび端子部TA(図3参照)を形成する。また、導体層13をエッチングすることによりベース絶縁層11の下面にサブトラクティブ法によりコイルCB、配線パターンPBおよび端子部TB(図4参照)を形成する。

【0062】

次に、図8(c)に示すように、レーザ加工により導体層12、ベース絶縁層11および導体層13に貫通孔THを形成する。レーザ加工の代わりにドリル加工等の他の方法により貫通孔THを形成してもよい。貫通孔THは、図3および図4のコイルCA,CBの中心の端部とコイルCA,CBの外側の端部に形成される。

【0063】

さらに、図8(d)に示すように、導体層12上、貫通孔THの内面上および導体層13上に金属めっきにより接続層18を形成する。本例では、銅めっきにより接続層18を形成する。

【0064】

次に、図8(e)に示すように、コイルCAを覆うようにベース絶縁層11の上面上にカバー絶縁層14を形成する。また、コイルCBおよび配線パターンPBを覆うようにベース絶縁層11の下面上にカバー絶縁層15を形成する。

【0065】

その後、図8(f)に示すように、図4の半田バンプ16,17が形成されるべきカバー絶縁層15の位置にレーザ加工により貫通孔VHを形成する。次いで、貫通孔VHの形成時に発生したスミア(残渣)を除去する。

【0066】

次に、図8(g)に示すように、回路基板10のカバー絶縁層15の貫通孔VHの位置に半田ペーストを用いた印刷法より半田バンプ16,17を形成する。

【0067】

図8と同様の方法で回路基板20を製造する。このようにして、回路基板10および回路基板20からなるアイソレータ用回路基板100が製造される。

【0068】

次に、図9に示すように、リードフレーム30上に送信チップ40および受信チップ50を配置する。さらに、コイルCA,CBとコイルCC,CDとが重なるように回路基板10のカバー絶縁層15と回路基板20のカバー絶縁層24とを接着剤で接着する。接着された回路基板10,20を送信チップ40および受信チップ50上に配置する。その後、図1に示すように、外部端子31を除くリードフレーム30の領域、送信チップ40、受信チップ50およびアイソレータ用回路基板100を封止樹脂からなるパッケージ60に収容する。

【0069】

(3)効果

本実施の形態に係るアイソレータ用回路基板100によれば、コイルCA,CB,CC,CDに重なるように送信チップ40および受信チップ50を配置することができるので、回路基板10,20の面積を大きくすることなくコイルCA,CB,CC,CDが形成される領域を十分に広く確保することができる。それにより、コイルCA,CB,CC,CDの設計の自由度を向上させることができる。その結果、コイルCA,CB,CC,CDのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板100の面積を小さくすることができるので、アイソレータ1の小型化が可能となる。さらに、ワイヤボンディングを用いることなく回路基板10,20の半田バンプ16,26を送信チップ40および受信チップ50の端子にそれぞれ接合することができる。また、コイルCA,CB,CC,CDを作製するためにMEMS技術を用いる必要がない。それにより、アイソレータ1を容易に製造することが可能となる。

【0070】

また、リードフレーム30上に送信チップ40および受信チップ50を配置することにより、半田バンプ17.27をリードフレーム30に接合することができる。したがって、ワイヤボンディングを用いることなく回路基板10の配線パターンPBおよび回路基板20の配線パターンPDをリードフレーム30に電気的に接続することができる。その結果、外部端子31を有する小型のアイソレータ1を容易に製造することが可能となる。

【0071】

さらに、半田バンプ17,27は送信チップ40および受信チップ50の厚み方向において半田バンプ16,26よりも大きな高さを有するので、回路基板10,20とリードフレーム30との間に送信チップ40および受信チップ50を配置した状態で、回路基板10,20の半田バンプ16,26を送信チップ40および受信チップ50の端子に容易に接合するとともに回路基板10,20の半田バンプ17,27をリードフレーム30に容易に接合することができる。

【0072】

また、コイルCA,CBが回路基板10の両面に形成され、コイルCC,CDが回路基板20の両面に形成されるので、回路基板10,20の面積を増加させることなく、コイルCA,CBからなる第1のコイルの巻き数およびコイルCC,CDからなる第2のコイルの巻き数を増加させることができる。その結果、アイソレータ用回路基板100の面積を増加させることなく、第1および第2のコイルのインダクタンスを大きくすることが可能となる。

【0073】

(4)他の実施の形態

図10は本発明の他の実施の形態に係るアイソレータ1の断面図である。図10のアイソレータ1が図1のアイソレータ1と異なるのは、次の点である。

【0074】

アイソレータ用回路基板100を構成する回路基板10のベース絶縁層11の上面にコイルCAおよびカバー絶縁層14が設けられず、ベース絶縁層11の下面にコイルCB、配線パターンPBおよびカバー絶縁層15が設けられる。また、回路基板20のベース絶縁層21の上面にコイルCCおよびカバー絶縁層24が設けられ、ベース絶縁層21の下面にコイルCDが設けられず、ベース絶縁層21の下面には配線パターンPBおよびカバー絶縁層15のみが設けられる。

【0075】

本実施の形態に係るアイソレータ1では、第1のコイルがコイルCBからなり、第2のコイルがコイルCCからなる。この場合、回路基板10の製造のために二層基板を用いることができる。

【0076】

図11は本発明のさらに他の実施の形態に係るアイソレータ1の断面図である。図11のアイソレータ1が図1のアイソレータ1と異なるのは、次の点である。

【0077】

アイソレータ用回路基板100を構成する回路基板10のベース絶縁層11の上面にコイルCAおよびカバー絶縁層14が設けられず、ベース絶縁層11の下面にコイルCB、配線パターンPBおよびカバー絶縁層15が設けられる。回路基板20の構成は、図1の回路基板20の構成と同様である。

【0078】

本実施の形態に係るアイソレータ1では、第1のコイルがコイルCBからなり、第2のコイルがコイルCC,CDからなる。この場合、回路基板10の製造のために二層基板を用いることができる。また、コイルCBからなる第1のコイルの巻き数をコイルCC,CDからなる第2のコイルの巻き数の約半分にすることができる。それにより、アイソレータ1において変圧を容易に行うことができる。

【0079】

(5)実施例

本実施例では、図8および図9の製造方法により図1のアイソレータ1を作製し、MEMS技術により製造された比較例のアイソレータに対する特性の比較を行った。

【0080】

図12は比較例のアイソレータの平面図である。図12のアイソレータ1Aにおいて、リードフレーム300は、複数のリード部310および支持部320により構成される。支持部320には、コイルチップ100、送信チップ400および受信チップ500が取り付けられる。コイルチップ100は絶縁層110を有する。絶縁層100には、MEMS技術によりコイルC1,C2,C3,C4が形成される。コイルチップ100の複数の端子は、送信チップ400の端子および受信チップ500の端子にワイヤWLにより接続される。また、送信チップ400の端子および受信チップ500の端子は、リード部310および支持部320にワイヤWLにより接続される。

【0081】

比較例のアイソレータ1Aでは、コイルC1,C2,C3,C4を構成する線路の幅は2μmであり、コイルC1,C2,C3,C4を構成する線路間の間隔は5μmであり、コイルC1,C2,C3,C4を構成する線路の厚み(高さ)は9μmであり、絶縁層110の厚みは16μmである。各コイルC1,C2,C3,C4の巻き数は14である。各コイルC1,C2,C3,C4の外径は0.24mmであり、各コイルC1,C2,C3,C4の内径は0.14mmである。各コイルC1,C2,C3,C4の線路の長さは20mmである。各コイルC1,C2,C3,C4の抵抗値は19.11Ωである。各コイルC1,C2,C3,C4のインダクタンスは105.5nHである。

【0082】

また、比較例のアイソレータ1Aの外部端子を除く短辺の寸法L1は12.0mmであり、長辺の寸法L2は11.0mmである。

【0083】

実施例のアイソレータ1については、各コイルCA,CB,CC,CDのインダクタンスが比較例とほぼ同じになるように、コイルCA,CB,CC,CD、ベース絶縁層11,21およびカバー絶縁層14,15,24,25の寸法を設計した。

【0084】

実施例のアイソレータ1では、コイルCA,CB,CC,CDを構成する線路の幅は67μmであり、コイルCA,CB,CC,CDを構成する線路間の間隔は67μmであり、コイルCA,CB,CC,CDを構成する線路の厚みは12μmであり、ベース絶縁層11,21およびカバー絶縁層14,15,24,25の各々の厚みは25μmである。各コイルCA,CB,CC,CDの巻き数は5.8である。各コイルCA,CB,CC,CDの外径は2.0mmであり、各コイルCA,CB,CC,CDの内径は0.8mmである。各コイルCA,CB,CC,CDの線路の長さは50mmである。各コイルCA,CB,CC,CDの抵抗値は1.07Ωである。各コイルCA,CB,CC,CDのインダクタンスは105.6nHである。

【0085】

また、実施例のアイソレータ1の外部端子31を除く短辺の寸法LA(図2参照)は11.0mmであり、長辺の寸法LB(図2参照)は10.0mmである。

【0086】

実施例のアイソレータ1および比較例のアイソレータ1Aの各部の寸法および特性を表1に示す。

【0087】

【表1】

【0088】

このように、実施例のアイソレータ1では、コイルCA,CB,CC,CDのインダクタンスを比較例のコイルC1,C2,C3,C4のインダクタンスと同じにした場合に、コイルCA,CB,CC,CDの抵抗値が比較例のコイルC1,C2,C3,C4の抵抗値に比べて約18分の1と大幅に低減される。

【0089】

したがって、上記実施の形態に係るアイソレータ1においては、コイルCA,CB,CC,CDの寸法の設計によりコイルCA,CB,CC,CDのインダクタンスの増加およびコイルCA,CB,CC,CDの抵抗値の減少が可能となる。

【0090】

(6)請求項の各構成要素と実施の形態の各部との対応関係

以下、請求項の各構成要素と実施の形態の各部との対応の例について説明するが、本発明は下記の例に限定されない。

【0091】

上記実施の形態では、回路基板10が第1の回路基板の例であり、回路基板20が第2の回路基板の例であり、コイルCA,CBが第1のコイルの例であり、コイルCC,CDが第2のコイルの例であり、配線パターンPBが第1の配線パターンの例であり、配線パターンPDが第2の配線パターンの例であり、半田バンプ16が第1の接続部の例であり、半田バンプ26が第2の接続部の例であり、半田バンプ17が第3の接続部の例であり、半田バンプ27が第4の接続部の例であり、リードフレーム30がリードフレームの例であり、送信チップ40が第1の電子部品の例であり、受信チップ50が第2の電子部品の例である。

【0092】

また、コイルCBが第1のコイルの一部分の例であり、コイルCAが第1のコイルの他の部分の例であり、コイルCCが第2のコイルの一部分の例であり、コイルCDが第2のコイルの他の部分の例であり、ベース絶縁層11が第1の絶縁層の例であり、導体層13が第1の導体層の例であり、カバー絶縁層15が第1の被覆層の例であり、ベース絶縁層21が第2の絶縁層の例であり、導体層22が第2の導体層の例であり、カバー絶縁層24が第2の被覆層の例であり、導体層12が第3の導体層の例であり、導体層23が第4の導体層の例である。

【0093】

さらに、ベース絶縁層11の上面が第1の絶縁層の一主面の例であり、ベース絶縁層11の下面が第1の絶縁層の他主面の例であり、ベース絶縁層21の上面が第2の絶縁層の一主面であり、ベース絶縁層21の下面が第2の絶縁層の他主面の例である。

【0094】

請求項の各構成要素として、請求項に記載されている構成または機能を有する他の種々の要素を用いることもできる。

【産業上の利用可能性】

【0095】

本発明は、種々の電気機器または電子機器等に有効に利用することができる。

【符号の説明】

【0096】

1 アイソレータ

10,20 回路基板

11,21 ベース絶縁層

12,13,22,23 導体層

14,15,24,25 カバー絶縁層

16,17,26,27 半田バンプ

18,28 接続層

30 リードフレーム

31 外部端子

32 リード部

34,35 支持部

40 送信チップ

50 受信チップ

60 パッケージ

100 アイソレータ用回路基板

PB,PD 配線パターン

CA,CB,CC,CD コイル

TA,TB,TC 端子部

TH,VH 貫通孔

【技術分野】

【0001】

本発明は、アイソレータ用回路基板、アイソレータ、アイソレータ用回路基板の製造方法およびアイソレータの製造方法に関する。

【背景技術】

【0002】

従来より、入力信号と出力信号との分離のために、アイソレータが用いられる(例えば特許文献1および2参照)。特許文献1および2に記載されたアイソレータでは、アイソレータ用回路基板に複数のコイルが形成されるとともにアイソレータ用回路基板の複数のコイルとは異なる領域上に受信チップおよび送信チップが実装されている。アイソレータ用回路基板の複数のコイルは、複数のワイヤを用いて受信チップおよび送信チップに接続される。

【0003】

近年、MEMS(Micro Electro Mechanical Systems)技術を用いたアイソレータが開発されている。このアイソレータでは、複数のコイルがチップ(以下、コイルチップと呼ぶ)上にMEMS技術により微細に形成される。コイルチップは、受信チップおよび送信チップとともにリードフレーム上に配置される。コイルチップは、ワイヤにより受信チップおよび送信チップに接続される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−61236号公報

【特許文献2】特開2010−74621号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記の従来のアイソレータ用回路基板に形成されるコイルの寸法に制限はない。しかしながら、アイソレータ用回路基板のコイルとは異なる領域に受信チップおよび送信チップを実装するために、アイソレータ用回路基板の面積が大きくなる。それにより、アイソレータの全体の大きさが大きくなる。

【0006】

一方、MEMS技術によれば、コイルチップを小型化することが可能となる。それにより、アイソレータを小型化することができる。しかしながら、MEMS技術により形成されるコイルチップには、寸法上の制約がある。例えば、コイルチップに形成されるコイルの線幅および線間隔を大きくすることは困難である。そのため、コイルの抵抗を十分に小さくすることが困難である。

【0007】

また、従来のアイソレータ用回路基板を用いたアイソレータおよびMEMS技術を用いたアイソレータにおいては、コイルを受信チップおよび送信チップに接続するためにワイヤボンディングが必要となる。そのため、製造工程が煩雑となる。

【0008】

本発明の目的は、コイルの設計の自由度の向上および小型化が可能でかつ容易に製造可能なアイソレータ用回路基板およびアイソレータならびにそれらの製造方法を提供することである。

【課題を解決するための手段】

【0009】

(1)第1の発明に係るアイソレータ用回路基板は、第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板であって、第1の回路基板と、第2の回路基板とを備え、第1の回路基板は、第1のコイルと、第1のコイルに電気的に接続される第1の接続部とを含み、第2の回路基板は、第2のコイルと、第2のコイルに電気的に接続される第2の接続部とを含み、第1および第2の接続部は、第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板が配置されるとともに第1および第2のコイルに重なるように第1および第2の電子部品が配置された場合に、第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられるものである。

【0010】

そのアイソレータ用回路基板をアイソレータに用いた場合、アイソレータ用回路基板の第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板を配置するとともに、第1および第2のコイルに重なるように第1および第2の電子部品を配置することにより、第1の回路基板の第1の接続部を第1の電子部品の端子に接続し、第2の回路基板の第2の接続部を第2の電子部品の端子に接続することができる。

【0011】

このように、第1および第2のコイルに重なるように第1および第2の電子部品を配置することができるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【0012】

(2)アイソレータはリードフレームをさらに有し、第1の回路基板は、第1の配線パターンと、第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、第2の回路基板は、第2の配線パターンと、第2の配線パターンに電気的に接続される第4の接続部とをさらに含み、第3および第4の接続部は、リードフレーム上に第1および第2の電子部品が配置された場合に、リードフレームに接触可能な位置に設けられてもよい。

【0013】

この場合、リードフレーム上に第1および第2の電子部品を配置することにより、第3および第4の接続部をリードフレームに接続することができる。したがって、ワイヤボンディングを用いることなく第1の回路基板の第1の配線パターンおよび第2の回路基板の第2の配線パターンをリードフレームに電気的に接続することができる。その結果、リードフレームを有する小型のアイソレータを容易に製造することが可能となる。

【0014】

(3)第3の接続部は、第1の電子部品の厚み方向において第1の接続部よりも大きな高さを有し、第4の接続部は、第2の電子部品の厚み方向において第2の接続部よりも大きな高さを有してもよい。

【0015】

この場合、第1および第2の回路基板とリードフレームとの間に第1および第2の電子部品を配置した状態で、第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子に容易に接続するとともに第1および第2の回路基板の第3および第4の接続部をリードフレームに容易に接続することができる。

【0016】

(4)第1の回路基板は、一主面および他主面を有する第1の絶縁層と、第1の絶縁層の他主面に設けられ、第1のコイルの少なくとも一部分を構成する第1の導体層と、第1の導体層を覆うように第1の絶縁層の他主面上に形成される第1の被覆層とを含み、第2の回路基板は、一主面および他主面を有する第2の絶縁層と、第2の絶縁層の一主面に設けられ、第2のコイルの少なくとも一部分を構成する第2の導体層と、第2の導体層を覆うように第2の絶縁層の一主面上に形成される第2の被覆層とを含んでもよい。

【0017】

この場合、第1の回路基板の第1のコイルが第1の被覆層で被覆されるとともに第2の回路基板の第2のコイルが第2の被覆層で被覆される。それにより、第1のコイルと第2のコイルとの間の絶縁性が十分に確保される。

【0018】

(5)第1および第2の回路基板は、第1の絶縁層の他主面が第2の絶縁層の一主面に向き合うように重ねられ、第1および第3の接続部は、第1の絶縁層の他主面上の第1の被覆層上に設けられ、第2および第4の接続部は、第2の絶縁層の他主面上に設けられてもよい。

【0019】

この場合、第1の回路基板の第1のコイルと第2の回路基板の第2のコイルとを第1および第2の被覆層を挟んで対向させることができる。それにより、第1のコイルと第2のコイルとの間隔を小さくすることができる。その結果、アイソレータ用回路基板の面積を増加させることなく、第1および第2のコイルのインダクタンスを大きくすることが可能となる。

【0020】

(6)第1の回路基板は、第1の絶縁層の一主面に設けられ、第1のコイルの他の部分を構成する第3の導体層と、第3の導体層を覆うように第1の絶縁層の一主面上に形成される第3の被覆層とをさらに含み、第2の回路基板は、第2の絶縁層の他主面に設けられ、第2のコイルの他の部分を構成する第4の導体層と、第4の導体層を覆うように第2の絶縁層の他主面上に形成される第4の被覆層とを含んでもよい。

【0021】

この場合、第1のコイルが第1の回路基板の両面に形成され、第2のコイルが第2の回路基板の両面に形成される。それにより、第1および第2の回路基板の面積を増加させることなく、第1および第2のコイルの巻き数を増加させることができる。その結果、アイソレータ用回路基板の面積を増加させることなく、第1および第2のコイルのインダクタンスを大きくすることが可能となる。

【0022】

(7)第2の発明に係るアイソレータは、アイソレータ用回路基板と、第1および第2の電子部品とを備え、アイソレータ用回路基板は、第1の回路基板と、第2の回路基板とを備え、第1の回路基板は、第1のコイルと、第1のコイルに電気的に接続される第1の接続部とを含み、第2の回路基板は、第2のコイルと、第2のコイルに電気的に接続される第2の接続部とを含み、アイソレータ用回路基板の第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板が配置されるとともに、第1および第2のコイルに重なるように第1および第2の電子部品が配置され、第1の回路基板の第1の接続部が第1の電子部品の端子に接続され、第2の回路基板の第2の接続部が第2の電子部品の端子に接続されるものである。

【0023】

そのアイソレータにおいては、第1および第2のコイルに重なるように第1および第2の電子部品が配置されるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【0024】

(8)アイソレータは、リードフレームをさらに有し、第1の回路基板は、第1の配線パターンと、第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、第2の回路基板は、第2の配線パターンとをさらに含み、リードフレーム上に第1および第2の電子部品が配置され、第3および第4の接続部がリードフレームに接続されてもよい。

【0025】

この場合、リードフレーム上に第1および第2の電子部品が配置され、第3および第4の接続部がリードフレームに接続される。したがって、ワイヤボンディングを用いることなく第1の回路基板の第1の配線パターンおよび第2の回路基板の第2の配線パターンをリードフレームに電気的に接続することができる。その結果、リードフレームを有する小型のアイソレータを容易に製造することが可能となる。

【0026】

(9)第3の発明に係るアイソレータ用回路基板の製造方法は、第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板の製造方法であって、第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程とを備え、第1および第2の接続部は、第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板が配置されるとともに第1および第2のコイルに重なるように第1および第2の電子部品が配置された場合に、第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられるものである。

【0027】

その方法により製造されたアイソレータ用回路基板をアイソレータの製造に用いる場合、アイソレータ用回路基板の第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板を配置するとともに、第1および第2のコイルに重なるように第1および第2の電子部品を配置する。それにより、第1の回路基板の第1の接続部を第1の電子部品の端子に接続し、第2の回路基板の第2の接続部を第2の電子部品の端子に接続することができる。

【0028】

このように、第1および第2のコイルに重なるように第1および第2の電子部品を配置することができるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【0029】

(10)第4の発明に係るアイソレータの製造方法は、第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程と、第1のコイルと第2のコイルとが互いに重なるように第1および第2の回路基板を配置するとともに第1および第2のコイルに重なるように第1および第2の電子部品を配置し、第1および第2の接続部をそれぞれ第1および第2の電子部品の端子に接続する工程とを含むものである。

【0030】

そのアイソレータの製造方法によれば、第1および第2のコイルに重なるように第1および第2の電子部品が配置されるので、第1および第2の回路基板の面積を大きくすることなく第1および第2のコイルが形成される領域を十分に広く確保することができる。それにより、コイルの設計の自由度を向上させることができる。その結果、第1および第2のコイルのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板の面積を小さくすることができるので、アイソレータの小型化が可能となる。さらに、ワイヤボンディングを用いることなく第1および第2の回路基板の第1および第2の接続部を第1および第2の電子部品の端子にそれぞれ接続することができる。それにより、アイソレータを容易に製造することが可能となる。

【発明の効果】

【0031】

本発明によれば、コイルの設計の自由度が向上するとともに、アイソレータの小型化が可能でかつアイソレータを容易に製造することが可能となる。

【図面の簡単な説明】

【0032】

【図1】本発明の一実施の形態に係るアイソレータの断面図である。

【図2】図1のアイソレータに用いられるアイソレータ用回路基板の平面図である。

【図3】アイソレータ用回路基板を構成する一方の回路基板の上面図である。

【図4】図3の回路基板の下面図である。

【図5】アイソレータ用回路基板を構成する他方の回路基板の上面図である。

【図6】図5の回路基板の下面図である。

【図7】図1のアイソレータに用いられるリードフレームの平面図である。

【図8】アイソレータ用回路基板を構成する回路基板の製造工程を示す断面図である。

【図9】アイソレータ用回路基板を用いたアイソレータの製造方法を示す断面図である。

【図10】本発明の他の実施の形態に係るアイソレータの断面図である。

【図11】本発明のさらに他の実施の形態に係るアイソレータの断面図である。

【図12】比較例のアイソレータの平面図である。

【発明を実施するための形態】

【0033】

以下、本発明の実施の形態に係るアイソレータ用回路基板、アイソレータおよびそれらの製造方法について図面を参照しながら説明する。

【0034】

(1)構成

図1は本発明の一実施の形態に係るアイソレータの断面図であり、図2は図1のアイソレータに用いられるアイソレータ用回路基板の平面図である。

【0035】

図1に示すように、アイソレータ1は、アイソレータ用回路基板100、リードフレーム30、送信チップ40、受信チップ50およびパッケージ60により構成される。アイソレータ用回路基板100は、フレキシブル配線回路基板(以下、回路基板と呼ぶ)10,20からなる。

【0036】

回路基板10は、例えばポリイミドからなるベース絶縁層11を有する。ベース絶縁層11の上面には、所定のパターンを有する導体層12が形成される。導体層12によりコイルCAが構成される。ベース絶縁層11の下面には、所定のパターンを有する導体層13が形成される。導体層13によりコイルCBおよび配線パターンPB(図2参照)が構成される。導体層12,13は例えば銅からなる。コイルCA,CBは互いに重なる位置に形成される。導体層12を覆うようにベース絶縁層11の上面上に例えばポリイミドからなるカバー絶縁層14が形成される。導体層13を覆うようにベース絶縁層11の下面上に例えばポリイミドからなるカバー絶縁層15が形成される。

【0037】

回路基板20は、例えばポリイミドからなるベース絶縁層21を有する。ベース絶縁層21の上面には、所定のパターンを有する導体層22が形成される。導体層22によりコイルCCが構成される。ベース絶縁層21の下面には、所定のパターンを有する導体層23が形成される。導体層23によりコイルCDおよび配線パターンPD(図2参照)が構成される。導体層22,23は例えば銅からなる。コイルCC,CDは互いに重なる位置に形成される。導体層22を覆うようにベース絶縁層21の上面上に例えばポリイミドからなるカバー絶縁層24が形成される。導体層23を覆うようにベース絶縁層21の下面上に例えばポリイミドからなるカバー絶縁層25が形成される。

【0038】

回路基板10のカバー絶縁層15の下面には、複数の半田バンプ16,17が設けられる。回路基板20のカバー絶縁層25の下面には、複数の半田バンプ26,27が設けられる。半田バンプ17,27の高さは、半田バンプ16,26の高さよりも、送信チップ40および受信チップ50の厚み分小さい。

【0039】

リードフレーム30上に送信チップ40および受信チップ50が配置される。リードフレーム30は、後述する複数の部分により構成されるともに、複数の外部端子31を有する。複数のコイルCA,CB,CC,CDが互いに重なるように回路基板10,20が配置される。また、コイルCA,CB,CC,CDが送信チップ40および受信チップ50に重なるように回路基板10,20が送信チップ40上、受信チップ50上およびリードフレーム30上に配置される。半田バンプ16は送信チップ40の上面の端子に接合され、半田バンプ26は受信チップ50の上面の端子に接合される。半田バンプ17,27はリードフレーム30の上面に接合される。この状態でリードフレーム30の外部端子31を除く部分、送信チップ40、受信チップ50およびアイソレータ用回路基板100が封止樹脂からなるパッケージ60に収容される。

【0040】

図3はアイソレータ用回路基板100を構成する一方の回路基板10の上面図である。図4は図3の回路基板10の下面図である。図3および図4では、カバー絶縁層14,15の図示が省略されている。

【0041】

図3に示すように、回路基板10のベース絶縁層11(図1参照)の上面上には、複数(本例では2つ)のコイルCAが設けられる。図4に示すように、回路基板10のベース絶縁層11(図1参照)の下面上には、複数(本例では2つ)のコイルCBおよび複数の配線パターンPBが設けられる。コイルCAとコイルCBとは互いに重なるように配置される。

【0042】

上面のコイルCAの中心の端部は接続層18を通して下面のコイルCBの中心の端部に接続される。それにより、コイルCAとコイルCBとが直列に接続される。また、コイルCAとコイルCBとは、上面側から見て逆向きの渦巻き状に延びる。それにより、コイルCAおよびコイルCBに同じ向きに電流が流れる。

【0043】

上面の複数のコイルCAの外側の端部にはそれぞれ端子部TAが設けられる。ベース絶縁層11の下面には、上面の端子部TAに重なるように端子部TBが設けられる。上面の端子部TAと下面の端子部TBとは接続層18(図3)を通して接続される。下面の複数のコイルCBの端部にはそれぞれ端子部TBが形成される。

【0044】

複数の端子部TBおよび配線パターンPBの一端部には、それぞれ半田バンプ16が形成される。複数の半田バンプ16は、送信チップ40の上面の複数の端子に接触可能な位置に設けられる。複数の配線パターンPBの他端部には、矩形のパッドが形成され、そのパッドにそれぞれ半田バンプ17が形成される。複数の半田バンプ17は、後述するリードフレーム30の各部分に接触可能な位置に設けられる。

【0045】

図5はアイソレータ用回路基板100を構成する他方の回路基板20の上面図である。図6は図5の回路基板20の下面図である。図5および図6では、カバー絶縁層24,25の図示が省略されている。

【0046】

図5に示すように、回路基板20のベース絶縁層21(図1参照)の上面上には、複数(本例では2つ)のコイルCCが設けられる。図6に示すように、回路基板20のベース絶縁層21(図1参照)の下面上には、複数(本例では2つ)のコイルCDおよび複数の配線パターンPDが設けられる。コイルCCとコイルCDとは互いに重なるように配置される。

【0047】

上面のコイルCCの中心の端部は接続層28を通して下面のコイルCDの中心の端部に接続される。上面のコイルCCの中心の端部は接続層28を通して下面のコイルCDの中心の端部に接続される。それにより、コイルCCとコイルCDとが直列に接続される。また、コイルCCとコイルCDとは、上面側から見て逆向きの渦巻き状に延びる。それにより、コイルCCおよびコイルCDに同じ向きに電流が流れる。

【0048】

上面の複数のコイルCCの外側の端部にはそれぞれ端子部TCが設けられる。ベース絶縁層21の下面には、上面の端子部TCに重なるように端子部TDが設けられる。上面の端子部TCと下面の端子部TDとは接続層28(図5)を通して接続される。下面の複数のコイルCDの端部にはそれぞれ端子部TDが形成される。

【0049】

複数の端子部TDおよび配線パターンPDの一端部には、それぞれ半田バンプ26が形成される。複数の半田バンプ26は、受信チップ50の上面の複数の端子に接触可能な位置に設けられる。複数の配線パターンPDの他端部には、矩形のパッドが形成され、そのパッドにそれぞれ半田バンプ27が形成される。複数の半田バンプ27は、後述するリードフレーム30の各部分に接触可能な位置に設けられる。

【0050】

回路基板10のコイルCA,CBにより第1のコイルが構成され、回路基板20のコイルCC,CDにより第2のコイルが構成される。第1のコイルと第2のコイルとによりトランスが構成される。

【0051】

図7は図1のアイソレータ1に用いられるリードフレーム30の平面図である。図7においては、リードフレーム30の外部端子31の図示が省略されている。

【0052】

リードフレーム30は、銅、アルミニウムまたはステンレス等の金属材料からなり、複数のリード部32および支持部34,35により構成される。各リード部32には、回路基板10の半田バンプ17または回路基板20の半田バンプ27が接合される。支持部34には送信チップ40が取り付けられる。支持部35には受信チップ50が取り付けられる。

【0053】

図3および図4に示す送信チップ40の複数の端子は、回路基板10の半田バンプ16、配線パターンPBおよび半田バンプ17を通して図7のリードフレーム30の複数のリード部32にそれぞれ接続される。また、図5および図6に示す受信チップ50の複数の端子は、回路基板20の半田バンプ26、配線パターンPDおよび半田バンプ27を通して図7のリードフレーム30の複数のリード部32にそれぞれ接続される。

【0054】

コイルCA,CB,CC,CDを構成する線路の厚み(導体層12,13,22,23の厚み)は、例えば5μm以上35μm以下であり、9μm以上18μm以下であることが好ましい。コイルCA,CB,CC,CDを構成する線路の幅は、例えば30μm以上150μm以下であり、50μm以上100μm以下であることが好ましい。また、コイルCA,CB,CC.CDを構成する線路の間隔は、例えば30μm以上150μm以下であり、50μm以上100μm以下であることが好ましい。

【0055】

ベース絶縁層11,21の厚みは、例えば5μm以上150μm以下であり、25μm以上100μm以下であることが好ましい。カバー絶縁層14,15,24,25の厚みは、例えば5μm以上150μm以下であり、25μm以上100μm以下であることが好ましい。

【0056】

半田バンプ16,26の直径は、例えば30μm以上100μm以下であり、50μm以上75μm以下であることが好ましい。半田バンプ17,27の直径は、例えば100μm以上500μm以下であり、150μm以上350μm以下であることが好ましい。

【0057】

ベース絶縁層11,21およびカバー絶縁層14,15,24,25の材料として、ポリイミドの代わりに、液晶ポリマーまたはポリエステル等を用いることができる。また、導体層12,13,22,23の材料として、銅の代わりに、金(Au)、アルミニウム等の他の金属、または銅合金、アルミニウム合金等の合金を用いることができる。

【0058】

(2)製造方法

次に、本実施の形態に係るアイソレータ用回路基板100およびそれを用いたアイソレータ1の製造方法の一例について説明する。

【0059】

図8はアイソレータ用回路基板100を構成する回路基板10の製造工程を示す断面図である。図9はアイソレータ用回路基板100を用いたアイソレータ1の製造方法を示す断面図である。

【0060】

まず、図8(a)に示すように、ポリイミドからなるベース絶縁層11の上面および下面に銅からなる導体層12,13が積層された三層基材を用意する。

【0061】

次に、図8(b)に示すように、導体層12をエッチングすることによりベース絶縁層11の上面にサブトラクティブ法によりコイルCAおよび端子部TA(図3参照)を形成する。また、導体層13をエッチングすることによりベース絶縁層11の下面にサブトラクティブ法によりコイルCB、配線パターンPBおよび端子部TB(図4参照)を形成する。

【0062】

次に、図8(c)に示すように、レーザ加工により導体層12、ベース絶縁層11および導体層13に貫通孔THを形成する。レーザ加工の代わりにドリル加工等の他の方法により貫通孔THを形成してもよい。貫通孔THは、図3および図4のコイルCA,CBの中心の端部とコイルCA,CBの外側の端部に形成される。

【0063】

さらに、図8(d)に示すように、導体層12上、貫通孔THの内面上および導体層13上に金属めっきにより接続層18を形成する。本例では、銅めっきにより接続層18を形成する。

【0064】

次に、図8(e)に示すように、コイルCAを覆うようにベース絶縁層11の上面上にカバー絶縁層14を形成する。また、コイルCBおよび配線パターンPBを覆うようにベース絶縁層11の下面上にカバー絶縁層15を形成する。

【0065】

その後、図8(f)に示すように、図4の半田バンプ16,17が形成されるべきカバー絶縁層15の位置にレーザ加工により貫通孔VHを形成する。次いで、貫通孔VHの形成時に発生したスミア(残渣)を除去する。

【0066】

次に、図8(g)に示すように、回路基板10のカバー絶縁層15の貫通孔VHの位置に半田ペーストを用いた印刷法より半田バンプ16,17を形成する。

【0067】

図8と同様の方法で回路基板20を製造する。このようにして、回路基板10および回路基板20からなるアイソレータ用回路基板100が製造される。

【0068】

次に、図9に示すように、リードフレーム30上に送信チップ40および受信チップ50を配置する。さらに、コイルCA,CBとコイルCC,CDとが重なるように回路基板10のカバー絶縁層15と回路基板20のカバー絶縁層24とを接着剤で接着する。接着された回路基板10,20を送信チップ40および受信チップ50上に配置する。その後、図1に示すように、外部端子31を除くリードフレーム30の領域、送信チップ40、受信チップ50およびアイソレータ用回路基板100を封止樹脂からなるパッケージ60に収容する。

【0069】

(3)効果

本実施の形態に係るアイソレータ用回路基板100によれば、コイルCA,CB,CC,CDに重なるように送信チップ40および受信チップ50を配置することができるので、回路基板10,20の面積を大きくすることなくコイルCA,CB,CC,CDが形成される領域を十分に広く確保することができる。それにより、コイルCA,CB,CC,CDの設計の自由度を向上させることができる。その結果、コイルCA,CB,CC,CDのインダクタンスの増加または抵抗の減少が可能となる。また、アイソレータ用回路基板100の面積を小さくすることができるので、アイソレータ1の小型化が可能となる。さらに、ワイヤボンディングを用いることなく回路基板10,20の半田バンプ16,26を送信チップ40および受信チップ50の端子にそれぞれ接合することができる。また、コイルCA,CB,CC,CDを作製するためにMEMS技術を用いる必要がない。それにより、アイソレータ1を容易に製造することが可能となる。

【0070】

また、リードフレーム30上に送信チップ40および受信チップ50を配置することにより、半田バンプ17.27をリードフレーム30に接合することができる。したがって、ワイヤボンディングを用いることなく回路基板10の配線パターンPBおよび回路基板20の配線パターンPDをリードフレーム30に電気的に接続することができる。その結果、外部端子31を有する小型のアイソレータ1を容易に製造することが可能となる。

【0071】

さらに、半田バンプ17,27は送信チップ40および受信チップ50の厚み方向において半田バンプ16,26よりも大きな高さを有するので、回路基板10,20とリードフレーム30との間に送信チップ40および受信チップ50を配置した状態で、回路基板10,20の半田バンプ16,26を送信チップ40および受信チップ50の端子に容易に接合するとともに回路基板10,20の半田バンプ17,27をリードフレーム30に容易に接合することができる。

【0072】

また、コイルCA,CBが回路基板10の両面に形成され、コイルCC,CDが回路基板20の両面に形成されるので、回路基板10,20の面積を増加させることなく、コイルCA,CBからなる第1のコイルの巻き数およびコイルCC,CDからなる第2のコイルの巻き数を増加させることができる。その結果、アイソレータ用回路基板100の面積を増加させることなく、第1および第2のコイルのインダクタンスを大きくすることが可能となる。

【0073】

(4)他の実施の形態

図10は本発明の他の実施の形態に係るアイソレータ1の断面図である。図10のアイソレータ1が図1のアイソレータ1と異なるのは、次の点である。

【0074】

アイソレータ用回路基板100を構成する回路基板10のベース絶縁層11の上面にコイルCAおよびカバー絶縁層14が設けられず、ベース絶縁層11の下面にコイルCB、配線パターンPBおよびカバー絶縁層15が設けられる。また、回路基板20のベース絶縁層21の上面にコイルCCおよびカバー絶縁層24が設けられ、ベース絶縁層21の下面にコイルCDが設けられず、ベース絶縁層21の下面には配線パターンPBおよびカバー絶縁層15のみが設けられる。

【0075】

本実施の形態に係るアイソレータ1では、第1のコイルがコイルCBからなり、第2のコイルがコイルCCからなる。この場合、回路基板10の製造のために二層基板を用いることができる。

【0076】

図11は本発明のさらに他の実施の形態に係るアイソレータ1の断面図である。図11のアイソレータ1が図1のアイソレータ1と異なるのは、次の点である。

【0077】

アイソレータ用回路基板100を構成する回路基板10のベース絶縁層11の上面にコイルCAおよびカバー絶縁層14が設けられず、ベース絶縁層11の下面にコイルCB、配線パターンPBおよびカバー絶縁層15が設けられる。回路基板20の構成は、図1の回路基板20の構成と同様である。

【0078】

本実施の形態に係るアイソレータ1では、第1のコイルがコイルCBからなり、第2のコイルがコイルCC,CDからなる。この場合、回路基板10の製造のために二層基板を用いることができる。また、コイルCBからなる第1のコイルの巻き数をコイルCC,CDからなる第2のコイルの巻き数の約半分にすることができる。それにより、アイソレータ1において変圧を容易に行うことができる。

【0079】

(5)実施例

本実施例では、図8および図9の製造方法により図1のアイソレータ1を作製し、MEMS技術により製造された比較例のアイソレータに対する特性の比較を行った。

【0080】

図12は比較例のアイソレータの平面図である。図12のアイソレータ1Aにおいて、リードフレーム300は、複数のリード部310および支持部320により構成される。支持部320には、コイルチップ100、送信チップ400および受信チップ500が取り付けられる。コイルチップ100は絶縁層110を有する。絶縁層100には、MEMS技術によりコイルC1,C2,C3,C4が形成される。コイルチップ100の複数の端子は、送信チップ400の端子および受信チップ500の端子にワイヤWLにより接続される。また、送信チップ400の端子および受信チップ500の端子は、リード部310および支持部320にワイヤWLにより接続される。

【0081】

比較例のアイソレータ1Aでは、コイルC1,C2,C3,C4を構成する線路の幅は2μmであり、コイルC1,C2,C3,C4を構成する線路間の間隔は5μmであり、コイルC1,C2,C3,C4を構成する線路の厚み(高さ)は9μmであり、絶縁層110の厚みは16μmである。各コイルC1,C2,C3,C4の巻き数は14である。各コイルC1,C2,C3,C4の外径は0.24mmであり、各コイルC1,C2,C3,C4の内径は0.14mmである。各コイルC1,C2,C3,C4の線路の長さは20mmである。各コイルC1,C2,C3,C4の抵抗値は19.11Ωである。各コイルC1,C2,C3,C4のインダクタンスは105.5nHである。

【0082】

また、比較例のアイソレータ1Aの外部端子を除く短辺の寸法L1は12.0mmであり、長辺の寸法L2は11.0mmである。

【0083】

実施例のアイソレータ1については、各コイルCA,CB,CC,CDのインダクタンスが比較例とほぼ同じになるように、コイルCA,CB,CC,CD、ベース絶縁層11,21およびカバー絶縁層14,15,24,25の寸法を設計した。

【0084】

実施例のアイソレータ1では、コイルCA,CB,CC,CDを構成する線路の幅は67μmであり、コイルCA,CB,CC,CDを構成する線路間の間隔は67μmであり、コイルCA,CB,CC,CDを構成する線路の厚みは12μmであり、ベース絶縁層11,21およびカバー絶縁層14,15,24,25の各々の厚みは25μmである。各コイルCA,CB,CC,CDの巻き数は5.8である。各コイルCA,CB,CC,CDの外径は2.0mmであり、各コイルCA,CB,CC,CDの内径は0.8mmである。各コイルCA,CB,CC,CDの線路の長さは50mmである。各コイルCA,CB,CC,CDの抵抗値は1.07Ωである。各コイルCA,CB,CC,CDのインダクタンスは105.6nHである。

【0085】

また、実施例のアイソレータ1の外部端子31を除く短辺の寸法LA(図2参照)は11.0mmであり、長辺の寸法LB(図2参照)は10.0mmである。

【0086】

実施例のアイソレータ1および比較例のアイソレータ1Aの各部の寸法および特性を表1に示す。

【0087】

【表1】

【0088】

このように、実施例のアイソレータ1では、コイルCA,CB,CC,CDのインダクタンスを比較例のコイルC1,C2,C3,C4のインダクタンスと同じにした場合に、コイルCA,CB,CC,CDの抵抗値が比較例のコイルC1,C2,C3,C4の抵抗値に比べて約18分の1と大幅に低減される。

【0089】

したがって、上記実施の形態に係るアイソレータ1においては、コイルCA,CB,CC,CDの寸法の設計によりコイルCA,CB,CC,CDのインダクタンスの増加およびコイルCA,CB,CC,CDの抵抗値の減少が可能となる。

【0090】

(6)請求項の各構成要素と実施の形態の各部との対応関係

以下、請求項の各構成要素と実施の形態の各部との対応の例について説明するが、本発明は下記の例に限定されない。

【0091】

上記実施の形態では、回路基板10が第1の回路基板の例であり、回路基板20が第2の回路基板の例であり、コイルCA,CBが第1のコイルの例であり、コイルCC,CDが第2のコイルの例であり、配線パターンPBが第1の配線パターンの例であり、配線パターンPDが第2の配線パターンの例であり、半田バンプ16が第1の接続部の例であり、半田バンプ26が第2の接続部の例であり、半田バンプ17が第3の接続部の例であり、半田バンプ27が第4の接続部の例であり、リードフレーム30がリードフレームの例であり、送信チップ40が第1の電子部品の例であり、受信チップ50が第2の電子部品の例である。

【0092】

また、コイルCBが第1のコイルの一部分の例であり、コイルCAが第1のコイルの他の部分の例であり、コイルCCが第2のコイルの一部分の例であり、コイルCDが第2のコイルの他の部分の例であり、ベース絶縁層11が第1の絶縁層の例であり、導体層13が第1の導体層の例であり、カバー絶縁層15が第1の被覆層の例であり、ベース絶縁層21が第2の絶縁層の例であり、導体層22が第2の導体層の例であり、カバー絶縁層24が第2の被覆層の例であり、導体層12が第3の導体層の例であり、導体層23が第4の導体層の例である。

【0093】

さらに、ベース絶縁層11の上面が第1の絶縁層の一主面の例であり、ベース絶縁層11の下面が第1の絶縁層の他主面の例であり、ベース絶縁層21の上面が第2の絶縁層の一主面であり、ベース絶縁層21の下面が第2の絶縁層の他主面の例である。

【0094】

請求項の各構成要素として、請求項に記載されている構成または機能を有する他の種々の要素を用いることもできる。

【産業上の利用可能性】

【0095】

本発明は、種々の電気機器または電子機器等に有効に利用することができる。

【符号の説明】

【0096】

1 アイソレータ

10,20 回路基板

11,21 ベース絶縁層

12,13,22,23 導体層

14,15,24,25 カバー絶縁層

16,17,26,27 半田バンプ

18,28 接続層

30 リードフレーム

31 外部端子

32 リード部

34,35 支持部

40 送信チップ

50 受信チップ

60 パッケージ

100 アイソレータ用回路基板

PB,PD 配線パターン

CA,CB,CC,CD コイル

TA,TB,TC 端子部

TH,VH 貫通孔

【特許請求の範囲】

【請求項1】

第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板であって、

第1の回路基板と、

第2の回路基板とを備え、

前記第1の回路基板は、

第1のコイルと、

前記第1のコイルに電気的に接続される第1の接続部とを含み、

前記第2の回路基板は、

第2のコイルと、

前記第2のコイルに電気的に接続される第2の接続部とを含み、

前記第1および第2の接続部は、前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板が配置されるとともに前記第1および第2のコイルに重なるように前記第1および第2の電子部品が配置された場合に、前記第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられることを特徴とするアイソレータ用回路基板。

【請求項2】

前記アイソレータはリードフレームをさらに有し、

前記第1の回路基板は、

第1の配線パターンと、

前記第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、

前記第2の回路基板は、

第2の配線パターンとをさらに含み、

前記第2の配線パターンに電気的に接続される第4の接続部とをさらに含み、

前記第3および第4の接続部は、前記リードフレーム上に前記第1および第2の電子部品が配置された場合に、前記リードフレームに接触可能な位置に設けられることを特徴とする請求項1記載のアイソレータ用回路基板。

【請求項3】

前記第3の接続部は、前記第1の電子部品の厚み方向において前記第1の接続部よりも大きな高さを有し、前記第4の接続部は、前記第2の電子部品の厚み方向において前記第2の接続部よりも大きな高さを有することを特徴とする請求項2記載のアイソレータ用回路基板。

【請求項4】

前記第1の回路基板は、

一主面および他主面を有する第1の絶縁層と、

前記第1の絶縁層の前記他主面に設けられ、前記第1のコイルの少なくとも一部分を構成する第1の導体層と、

前記第1の導体層を覆うように前記第1の絶縁層の前記他主面上に形成される第1の被覆層とを含み、

前記第2の回路基板は、

一主面および他主面を有する第2の絶縁層と、

前記第2の絶縁層の前記一主面に設けられ、前記第2のコイルの少なくとも一部分を構成する第2の導体層と、

前記第2の導体層を覆うように前記第2の絶縁層の前記一主面上に形成される第2の被覆層とを含むことを特徴とする請求項3記載のアイソレータ用回路基板。

【請求項5】

前記第1および第2の回路基板は、前記第1の絶縁層の前記他主面が前記第2の絶縁層の前記一主面に向き合うように重ねられ、

前記第1および第3の接続部は、前記第1の絶縁層の前記他主面上の前記第1の被覆層上に設けられ、

前記第2および第4の接続部は、前記第2の絶縁層の前記他主面上に設けられることを特徴とする請求項4記載のアイソレータ用回路基板。

【請求項6】

前記第1の回路基板は、

前記第1の絶縁層の前記一主面に設けられ、前記第1のコイルの他の部分を構成する第3の導体層と、

前記第3の導体層を覆うように前記第1の絶縁層の前記一主面上に形成される第3の被覆層とをさらに含み、

前記第2の回路基板は、

前記第2の絶縁層の前記他主面に設けられ、前記第2のコイルの他の部分を構成する第4の導体層と、

前記第4の導体層を覆うように前記第2の絶縁層の前記他主面上に形成される第4の被覆層とを含むことを特徴とする請求項5記載のアイソレータ用回路基板。

【請求項7】

アイソレータ用回路基板と、

第1および第2の電子部品とを備え、

前記アイソレータ用回路基板は、

第1の回路基板と、

第2の回路基板とを備え、

前記第1の回路基板は、

第1のコイルと、

前記第1のコイルに電気的に接続される第1の接続部とを含み、

前記第2の回路基板は、

第2のコイルと、

前記第2のコイルに電気的に接続される第2の接続部とを含み、

前記アイソレータ用回路基板の前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板が配置されるとともに、前記第1および第2のコイルに重なるように前記第1および第2の電子部品が配置され、前記第1の回路基板の前記第1の接続部が前記第1の電子部品の端子に接続され、前記第2の回路基板の前記第2の接続部が前記第2の電子部品の端子に接続されることを特徴とするアイソレータ。

【請求項8】

リードフレームをさらに有し、

前記第1の回路基板は、

第1の配線パターンと、

前記第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、

前記第2の回路基板は、

第2の配線パターンとをさらに含み、

前記リードフレーム上に前記第1および第2の電子部品が配置され、前記第3および第4の接続部が前記リードフレームに接続されることを特徴とするアイソレータ。

【請求項9】

第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板の製造方法であって、

第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、

第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程とを備え、

前記第1および第2の接続部は、前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板が配置されるとともに前記第1および第2のコイルに重なるように前記第1および第2の電子部品が配置された場合に、前記第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられることを特徴とするアイソレータ用回路基板の製造方法。

【請求項10】

第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、

第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程と、

前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板を配置するとともに前記第1および第2のコイルに重なるように前記第1および第2の電子部品を配置し、前記第1および第2の接続部をそれぞれ前記第1および第2の電子部品の端子に接続する工程とを含むことを特徴とするアイソレータの製造方法。

【請求項1】

第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板であって、

第1の回路基板と、

第2の回路基板とを備え、

前記第1の回路基板は、

第1のコイルと、

前記第1のコイルに電気的に接続される第1の接続部とを含み、

前記第2の回路基板は、

第2のコイルと、

前記第2のコイルに電気的に接続される第2の接続部とを含み、

前記第1および第2の接続部は、前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板が配置されるとともに前記第1および第2のコイルに重なるように前記第1および第2の電子部品が配置された場合に、前記第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられることを特徴とするアイソレータ用回路基板。

【請求項2】

前記アイソレータはリードフレームをさらに有し、

前記第1の回路基板は、

第1の配線パターンと、

前記第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、

前記第2の回路基板は、

第2の配線パターンとをさらに含み、

前記第2の配線パターンに電気的に接続される第4の接続部とをさらに含み、

前記第3および第4の接続部は、前記リードフレーム上に前記第1および第2の電子部品が配置された場合に、前記リードフレームに接触可能な位置に設けられることを特徴とする請求項1記載のアイソレータ用回路基板。

【請求項3】

前記第3の接続部は、前記第1の電子部品の厚み方向において前記第1の接続部よりも大きな高さを有し、前記第4の接続部は、前記第2の電子部品の厚み方向において前記第2の接続部よりも大きな高さを有することを特徴とする請求項2記載のアイソレータ用回路基板。

【請求項4】

前記第1の回路基板は、

一主面および他主面を有する第1の絶縁層と、

前記第1の絶縁層の前記他主面に設けられ、前記第1のコイルの少なくとも一部分を構成する第1の導体層と、

前記第1の導体層を覆うように前記第1の絶縁層の前記他主面上に形成される第1の被覆層とを含み、

前記第2の回路基板は、

一主面および他主面を有する第2の絶縁層と、

前記第2の絶縁層の前記一主面に設けられ、前記第2のコイルの少なくとも一部分を構成する第2の導体層と、

前記第2の導体層を覆うように前記第2の絶縁層の前記一主面上に形成される第2の被覆層とを含むことを特徴とする請求項3記載のアイソレータ用回路基板。

【請求項5】

前記第1および第2の回路基板は、前記第1の絶縁層の前記他主面が前記第2の絶縁層の前記一主面に向き合うように重ねられ、

前記第1および第3の接続部は、前記第1の絶縁層の前記他主面上の前記第1の被覆層上に設けられ、

前記第2および第4の接続部は、前記第2の絶縁層の前記他主面上に設けられることを特徴とする請求項4記載のアイソレータ用回路基板。

【請求項6】

前記第1の回路基板は、

前記第1の絶縁層の前記一主面に設けられ、前記第1のコイルの他の部分を構成する第3の導体層と、

前記第3の導体層を覆うように前記第1の絶縁層の前記一主面上に形成される第3の被覆層とをさらに含み、

前記第2の回路基板は、

前記第2の絶縁層の前記他主面に設けられ、前記第2のコイルの他の部分を構成する第4の導体層と、

前記第4の導体層を覆うように前記第2の絶縁層の前記他主面上に形成される第4の被覆層とを含むことを特徴とする請求項5記載のアイソレータ用回路基板。

【請求項7】

アイソレータ用回路基板と、

第1および第2の電子部品とを備え、

前記アイソレータ用回路基板は、

第1の回路基板と、

第2の回路基板とを備え、

前記第1の回路基板は、

第1のコイルと、

前記第1のコイルに電気的に接続される第1の接続部とを含み、

前記第2の回路基板は、

第2のコイルと、

前記第2のコイルに電気的に接続される第2の接続部とを含み、

前記アイソレータ用回路基板の前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板が配置されるとともに、前記第1および第2のコイルに重なるように前記第1および第2の電子部品が配置され、前記第1の回路基板の前記第1の接続部が前記第1の電子部品の端子に接続され、前記第2の回路基板の前記第2の接続部が前記第2の電子部品の端子に接続されることを特徴とするアイソレータ。

【請求項8】

リードフレームをさらに有し、

前記第1の回路基板は、

第1の配線パターンと、

前記第1の配線パターンに電気的に接続される第3の接続部とをさらに含み、

前記第2の回路基板は、

第2の配線パターンとをさらに含み、

前記リードフレーム上に前記第1および第2の電子部品が配置され、前記第3および第4の接続部が前記リードフレームに接続されることを特徴とするアイソレータ。

【請求項9】

第1および第2の電子部品を有するアイソレータに用いられるアイソレータ用回路基板の製造方法であって、

第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、

第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程とを備え、

前記第1および第2の接続部は、前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板が配置されるとともに前記第1および第2のコイルに重なるように前記第1および第2の電子部品が配置された場合に、前記第1および第2の電子部品の端子にそれぞれ接触可能な位置に設けられることを特徴とするアイソレータ用回路基板の製造方法。

【請求項10】

第1のコイルおよびその第1のコイルに電気的に接続される第1の接続部を有する第1の回路基板を作製する工程と、

第2のコイルおよびその第2のコイルに電気的に接続される第2の接続部を有する第2の回路基板を作製する工程と、

前記第1のコイルと前記第2のコイルとが互いに重なるように前記第1および第2の回路基板を配置するとともに前記第1および第2のコイルに重なるように前記第1および第2の電子部品を配置し、前記第1および第2の接続部をそれぞれ前記第1および第2の電子部品の端子に接続する工程とを含むことを特徴とするアイソレータの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−182740(P2012−182740A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−45542(P2011−45542)

【出願日】平成23年3月2日(2011.3.2)

【出願人】(000003964)日東電工株式会社 (5,557)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年3月2日(2011.3.2)

【出願人】(000003964)日東電工株式会社 (5,557)

【Fターム(参考)】

[ Back to top ]