アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はフラクショナルN−PLLシンセサイザ、特に、アキュムレータを用いてフラクショナル分周数を制御するアキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法に関する。

【背景技術】

【0002】

フラクショナルN−PLLシンセサイザは、電圧制御発振器(以下VCO)の出力を分周する帰還分周数が、小数分周であることを特徴とするPLLである。ここで一般的なフラクショナルN−PLLシンセサイザの一例を図12に示す。

図12において、フラクショナルN−PLLシンセサイザ1200は、参照信号と帰還信号との位相差を検出する位相検出器1211、その次段のチャージポンプ1212、更に次段のローパスフィルタ(以下LPF)1213、その次段のVCO1214、VCO1214の出力を分周するフラクショナル分周器1215、および、デルタシグマ変調器1220から構成され、デルタシグマ型フラクショナルN−PLLシンセサイザと称される。

【0003】

位相検出器1211は参照信号とフラクショナル分周器1215の出力である帰還信号との位相差を検出し、チャージポンプ1212に出力する。チャージポンプ1212は位相差に応じた電荷量をLPF1213に出力する。

VCO1214はLPF1213の出力に応じて出力周波数を変化させる。フラクショナル分周器1215はVCO1214の出力信号を既定の分周比で分周して位相検出器1211に出力する。

【0004】

デルタシグマ変調器1220は、帰還分周数の分子と分母の設定値により、フラクショナル分周器1215における分周数を、N分周およびN+1分周の何れかとするように時間的に切り替える。

例えば、参照信号の周波数をFref、帰還分周数を、N+NUM/DEN(N、NUM、DENはそれぞれ整数)とおくと、VCO1214の出力信号の発振周波数Fvcoは、

Fvco=Fref×(N+NUM/DEN)………(1)

と表される。

【0005】

式(1)を変形すると、

Fvco=Fref×{(NUM/DEN)×(N+1)+(1−NUM/DEN)×N}………………………………………………………………………(2)

が得られ、N分周、N+1分周を式(2)に従った時間割合で分周数を切り替えることによって、フラクショナル分周器1215は小数分周数を実現している。

【0006】

また、デルタシグマ変調を用いることによって、非周期的に帰還分周数を切り替えるため、切り替える周期に応じた固有のスプリアスであるフラクショナルスプリアスが生じ難いという利点がある。

しかしながら、図12を参照して説明した上記方式では、フラクショナルスプリアスをデルタシグマ変調器1220で高周波数側にノイズシェープしているため、PLLを構成するLPF1213でそのノイズ成分を除去する必要が生じる。従って、このデルタシグマ型フラクショナルN−PLLシンセサイザではLPFのカットオフ周波数の低域化を要するという問題があった。

【0007】

PLLを構成するLPFは、PLLの構成要素であるLPFやVCOからみるとハイパスフィルタ(以下HPF)として機能している。従って、LPFやVCOの構成要素から生じた低周波のノイズ成分は、このLPFによって除去される。このため、LPFのカットオフ周波数が高いほど、低周波のノイズ成分を効率良く除去することが可能である。

上述の事情により、デルタシグマ型フラクショナルN−PLLシンセサイザでは、PLLを構成するLPFやVCOから生じる低周波のノイズを十分に除去することができず、結果的にフラクショナルN−PLLシンセサイザの出力信号の性能(ジッタ)が劣化してしまうという課題を残している。

【0008】

図13は、図12とは異なる従来例としてアキュムレータを用いた方式によるフラクショナルN−PLLシンセサイザを表す図である。

図13において、フラクショナルN−PLLシンセサイザ1300は、参照信号と帰還信号との位相差を検出する位相検出器1311、その次段のチャージポンプ1312、更に次段のローパスフィルタ(以下LPF)1313、その次段のVCO1314、VCO1314の出力を分周するフラクショナル分周器1315、および、フラクショナル分周器1315の分周数を周期的に切り替えるアキュムレータ1320から構成され、アキュムレータ型フラクショナルN−PLLと称される。

【0009】

アキュムレータ型フラクショナルN−PLLでは、アキュムレータ1320の出力によってフラクショナル分周器1315の分周数を周期的に切り替えることにより小数分周数を実現する方式を採っている。この方式では、図12の方式におけるようなデルタシグマ変調器を持たないため高周波域のノイズを除去する必要がなく、LPFのカットオフ周波数を高く出来る。従って、PLLを構成するLPFやVCOから生じる低周波のノイズを十分に除去することができ、出力信号の性能(ジッタ)を向上させることができるという点で優れる。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】S.E.Meninger and M.H.Perrott,“ A 1MHz Bandwidth 3.6−GHz 0.18um CMOS Fractional−N Synthesizer Utilizing a Hybrid PFD/DAC structure for Reduced Broadband Phase Noise、 ”IEEE J.Solid-state Circuits, vol.41、pp.966-980、April 2006.

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、図13を参照して説明した従来のアキュムレータ型フラクショナルN−PLLシンセサイザでは、フラクショナル分周器の分周数を周期的に切り替えるため、切り替える周期に応じたフラクショナルスプリアスが生じてしまうという課題があった。

本願発明は上述のような状況に鑑みてなされたものであり、フラクショナルスプリアスの少ないアキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記課題を解決するために、ここに、次に列挙するような技術を提案する。

(1)発振出力信号の帰還路に介挿されたフラクショナル分周器の分周数をアキュムレータの出力によって周期的に切り替えることにより小数分周数の帰還信号を得るアキュムレータ型フラクショナルN−PLLシンセサイザであって、

前記フラクショナル分周器からの帰還信号が一方の入力端に供給される位相検出器と、

前記アキュムレータからの誤差信号に基づいて既定の参照信号に位相調整を施した位相調整信号を前記位相検出器の他方の入力端に供給する位相調整回路と、

を備えることを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザ。

【0013】

(2)前記位相調整回路は、

入力された前記参照信号を遅延させた信号を出力する遅延回路と、

前記参照信号と前記遅延回路から出力される遅延信号とによって前記位相調整信号を生成する位相シフト回路と、

を備えることを特徴とする(1)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(3)前記遅延回路は、自己への入力信号を前記発振出力信号の周期分だけ遅延させることを特徴とする(2)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【0014】

(4)前記遅延回路は、前記発振器を構成する遅延素子と同じ構成を持つことを特徴とする(3)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(5)前記位相シフト回路は、前記参照信号と前記遅延回路から出力される遅延信号とが供給されるようになされ、前記アキュムレータからの誤差信号に基づいて該供給された前記参照信号に対して位相シフトを施すことによって前記位相調整信号を生成することを特徴とする(2)乃至(4)の何れか一に記載のフラクショナルN−PLL。

【0015】

(6)前記遅延回路は、前記発振器の出力周期に対しMを自然数としてその1/M、2/M、…、(M−1)/M倍遅延させた複数の出力信号を前記位相シフト回路に供給することを特徴とする(2)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(7)前記位相シフト回路は、前記遅延回路から供給される複数の遅延信号のうちの一の遅延信号を前記誤差信号に基づいて選択し出力することを特徴とする(6)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【0016】

(8)前記位相シフト回路は、前記遅延回路から供給された前記複数の遅延信号について隣接する遅延信号間での補間をとった複数の信号のうちの一の信号を前記誤差信号に基づいて選択し出力することを特徴とする(6)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(9)アキュムレータからの誤差信号に基づいて参照信号の位相を制御することを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザの制御方法。

【発明の効果】

【0017】

本発明によれば、フラクショナルスプリアスの少ないアキュムレータ型フラクショナルN−PLLシンセサイザを実現することができる。

【図面の簡単な説明】

【0018】

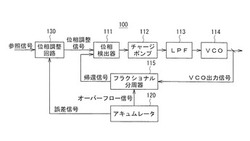

【図1】本発明の実施の形態であるアキュムレータ型フラクショナルN−PLLシンセサイザを表すブロック図である。

【図2】図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用されるアキュムレータを例示するブロック図である。

【図3】図2のアキュムレータの出力を時系列に沿って周期毎に表す図である。

【図4】図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相調整回路の入出力に関係する各信号を表すタイミングチャートである。

【図5】図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相検出器への入出力に関係する各信号を表すタイミングチャートである。

【図6】図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路の一例を表すブロック図である。

【図7】図6の位相調整回路に適用される位相シフト回路を例示するブロック図である。

【図8】図6の位相調整回路に適用される遅延回路を例示するブロック図である。

【図9】図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路の他の例を表すブロック図である。

【図10】図9の位相調整回路に適用される位相シフト回路(選択回路)を例示するブロック図である。

【図11】図9の位相調整回路に適用される遅延回路を例示するブロック図である。

【図12】一般的なデルタシグマ型フラクショナルN−PLLシンセサイザを表すブロック図である。

【図13】従来のアキュムレータ型フラクショナルN−PLLシンセサイザを表すブロック図である。

【発明を実施するための形態】

【0019】

以下に、本発明の実施の形態について詳述することにより本発明を明らかにする。

図1は本発明の実施形態であるアキュムレータ型フラクショナルN−PLLシンセサイザを表すブロック図である。

図1において、アキュムレータ型フラクショナルN−PLLシンセサイザ100は、位相検出器111、チャージポンプ112、LPF113、VCO114、フラクショナル分周器115、および、アキュムレータ120を有し、更に、アキュムレータ120の出力によって制御される位相調整回路130が図示のように位相検出器111の前段に介挿されて構成されている。

【0020】

アキュムレータ型フラクショナルN−PLLシンセサイザ100は、参照信号と帰還信号との位相差を検出する位相検出器111、その次段のチャージポンプ112、更に次段のLPF113、その次段のVCO114、VCO114の出力を分周するフラクショナル分周器115、および、アキュムレータ120を有し、これらは、図13を参照して既述のフラクショナルN−PLLシンセサイザ1300における、位相検出器1311、チャージポンプ1312、LPF1313、VCO1314、フラクショナル分周器1315、および、アキュムレータ1320に上述の順に逐次対応している。

そして、本例のアキュムレータ型フラクショナルN−PLLシンセサイザ100では、詳細を後述するように、位相検出器111に入力される参照信号に位相調整が施されるように構成され、その位相調整にアキュムレータ120からの誤差信号を用いる点を一つの特徴としている。

【0021】

次に、図面を参照して、アキュムレータ120、フラクショナル分周器115、および位相調整回路130について説明する。

図2は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザ100に適用されるアキュムレータ120を例示するブロック図である。

図2において、アキュムレータ120は、分子/分母で表される小数値と、誤差信号とを、加算器121を用いて加算する。加算器121の次段の飽和処理回路122では、加算信号ADDが1より大か小かを判断し、1より小さければ、一方の出力ER=ADDとし、且つ、他方の出力CA=0とする出力を発し、1と同じもしくは大きければ、一方の出力ER=ADD−1とし、且つ、他方の出力CA=1とする出力を発する。

【0022】

図3は、図2のアキュムレータ120の出力を時系列に沿って周期毎に表す図である。即ち、図3には、アキュムレータ120が出力する各信号の時間サイクルが列記されている。

図3より容易に理解される通り、オーバーフロー信号は、00010001・・と周期的に信号を出力する。これにより、分周数を22232223・・・と切り替えて、入力されたクロックのエッジを9発カウントする間に、4回のクロックエッジを作り出す。これにより9/4の小数分周を実現する。そして、アキュムレータ120から出力されるオーバーフローする以前の積算情報は、誤差信号として、1/4、2/4、3/4、0、1/4、2/4、3/4、0・・・と出力される。

【0023】

一方、位相調整回路130では、アキュムレータ120が出力する上述のような誤差信号と既定の参照信号とに基づいて、図4のように位相を調整した信号を作り出し、この信号を位相検出器111に出力する。

図4は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相調整回路130の入出力に関係する各信号を表すタイミングチャートである。尚、位相調整回路130の構成例については、図6を参照して後述する。

【0024】

図4を既述の図3と対照して容易に理解される通り、VCO114の出力の1周期毎に、デジタル信号である誤差信号が1/4周期ずつ遅延した状態を表す値をとる。即ち、図3を参照して既述の通り、その遅延が、1周期を単位として、その1/4、2/4、3/4、0、1/4、2/4、3/4、0・・・となる如く出力される。そして、誤差信号によって表されるその遅延が3/4→0/4となるタイミングで自己の周期が半周期遅延する位相調整信号が出力される。

【0025】

そして、位相検出器111では、図3および図4を参照して説明した位相調整信号(位相調整された参照信号)とフラクショナル分周器115の出力である帰還信号とに基づいて、位相検出出力を得る。

図5は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相検出器111への入出力に関係する各信号を表すタイミングチャートである。

【0026】

図5を参照して理解される通り、PLLのロック状態でも参照信号と帰還信号との二つの信号には位相の誤差が周期的に生じる。これがフラクショナルスプリアスの原因となる。位相の誤差量は、VCO114の出力信号の1周期を単位として、その、1/4、2/4、3/4、0、1/4、2/4、3/4、0・・・となる。

図4を参照して既述のとおり、この位相の誤差量に対応するデジタル信号である誤差信号に基づいて、位相調整された参照信号である位相調整信号が出力される。

【0027】

図1の実施形態では、上述のようにして、フラクショナル分周器115から出力される周期的なクロックのエッジのずれをあらかじめ予測し、位相調整回路130で参照信号のエッジ(即ち、位相)を調整するため、当該フラクショナルN−PLL100が位相をロックした状態では、位相検出器111に入力される2つの信号の間に位相差が生じない。従って、ロック状態ではチャージポンプ112からLPF113に電荷を出力しないため、VCO114の入力電圧が周期的に変動することがない。よって、従来のアキュムレータ型フラクショナルN−PLLの課題であったフラクショナルスプリアスを大幅に低減することができる。

【0028】

このため、本実施の形態におけるアキュムレータ型フラクショナルN−PLLシンセサイザでは、フラクショナルスプリアスを生じさせるチャージポンプからの周期的な電荷出力を、新たに保有する別のチャージポンプの出力によってキャンセルするといった別の手法との比較においても、そもそも位相検出器111の入力に位相差を生じさせないようにしているために、VCO114の入力電圧が周期的に変動することがなく、フラクショナルスプリアスの低減効果がより顕著である。

【0029】

また、図1の実施形態では、図12を参照して既述のデルタシグマ型フラクショナルN−PLLシンセサイザとの比較においては、フラクショナルスプリアス自体の低減をはかっている点が特徴的である。従って、デルタシグマ型フラクショナルN−PLLシンセサイザでは必要であったLPFのカットオフ周波数の低帯域化が不要となるため、LPFやVCOを構成する要素から生じた低周波のノイズ成分を効率よく除去することが可能であり、当該フラクショナルN−PLLシンセサイザとしての出力信号の性能(ジッタ)を向上させることが可能である。

【0030】

更に、一般的なデルタシグマ型フラクショナルN−PLLシンセサイザでは、フラクショナル分周をする際の分母の値を固定値にする必要があり、周波数誤差を伴わずに任意の周波数を作り出すことができないという問題があった。これに対し、本実施の形態では、アキュムレータ型フラクショナルN−PLLシンセサイザの方式を採ることを特徴としており、そのため周波数誤差を伴わずに任意の周波数を作り出すことができるという優れた特徴をも併せ持つ。

【0031】

図6は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路130の一例を表すブロック図である。

図6の位相調整回路130は、遅延回路131と位相シフト回路132とが図示のように接続されて構成されている。この位相調整回路130では、入力された参照信号は、遅延回路131によって、ある遅延量を持った遅延信号となって出力される。遅延信号と参照信号との位相差は、一定値であることが望ましい。フラクショナル分周器115によって、VCO114の出力信号がN分周もしくはN+1分周されるので、参照信号と帰還信号の位相差は、既述の図5におけるように最大でもVCO114の発振周期を超えることはない。しかしながら、遅延信号と参照信号の位相差が、VCO114の発振周期と同一であることはより望ましい。

【0032】

尚、ここではフラクショナル分周器115として、N分周もしくはN+1分周を行なうデュアルモジュラス周波数分周器を例示したが、この例によらず、N分周とN+2分周等種々の仕様を採ることができる。N分周とN+2分周の仕様とする場合は、遅延信号と参照信号の位相差はVCO115の発振周期の2倍と同一であることがより望ましい。

図6の位相調整回路130における上述の遅延回路131の次段に設けられた位相シフト回路132では、遅延回路131の出力である遅延信号、既述の参照信号、および、アキュムレータ120から供給される誤差信号に基づいて、出力信号たる位相調整信号を生成する。

【0033】

次に、図6および既述の図4を併せ参照して、位相シフト回路132について更に説明する。位相シフト回路132は、その両入力である参照信号と遅延信号との立ち上がりエッジ間を位相シフトすることによって位相調整回路130の出力たる位相調整信号を生成する。例えば、アキュムレータ120からの誤差信号がVCO114の出力信号の1周期を単位として、その、1/4の場合、参照信号と誤差信号の立ち上がりエッジ間のちょうど上述の1/4の位置に位相調整信号の立ち上がりエッジを生成する。次のステップで誤差信号が2/4の場合、参照信号と誤差信号の立ち上がりエッジ間のちょうど真ん中の位置に位相調整信号の立ち上がりエッジを生成する。

【0034】

図7は、図6の位相調整回路に適用される位相シフト回路を例示するブロック図である。

図7において、位相シフト回路132は、トランスコンダクタンス値が電流によって可変のトランスコンダクタンスアンプ2個(1321a、1321b)とコンパレータ1322を備えて構成されている。参照信号と遅延信号は、あらかじめCML(カレントモードロジック)の差動信号に変換されている。誤差信号を元に、それぞれのトランスコンダクタンス値をコントロールする。例えば誤差信号が上述の如く1/4の場合、参照信号側と遅延信号側のトランスコンダクタンス値の比を1:3にすることによって所望の位相シフト量を得ることができる。尚、位相シフト回路の構成は図7に例示したものに限定されることはない。

【0035】

上述の実施の形態では、位相調整回路130を帰還信号側ではなく、参照信号側に設けていることを特徴としている。従って、図7の位相シフト回路132に入力される信号には周波数変調がかかっていないため、この位相シフト回路1320における設計上の制約が緩和されるだけでなく、精度よく位相調整ができるという点も一つの特徴である。

【0036】

図8は、図6の位相調整回路に適用される遅延回路を例示するブロック図である。

次に、図8を参照して遅延回路131について説明する。図8の例では、VCO114の構成が遅延素子が3段縦続接続されたリングオシレータ構成を成している。また遅延素子の電源は、発振周波数を制御するために可変となっている。遅延回路131は、VCO114を構成する遅延素子を6段縦続接続した構成と採っており、電源も共通としている。上述のように構成することにより、遅延回路131の遅延量は、VCO114の発振周期に精度よく合致した特性を呈する。

【0037】

なお、VCO114の構成は図8の例に限られたものではなく、上述のようなリングオシレータの態様を採るに替えて、マルチバイブレータにより構成する態様を採ってもよい。また、リングオシレータの態様を採る場合においても、遅延素子の段数は3段に限定されるものではない。また遅延素子の構成として、例えば、遅延素子の負荷容量を制御して発振周波数をコントロールする態様を採ってもよい。その場合は、遅延回路の各遅延素子も同量の負荷容量とすることによって所要の特性を得ることができる。

【0038】

図9は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路の他の例を表すブロック図である。

図9の位相調整回路130aは、遅延回路131aと(選択回路)132aとが図示のように接続されて構成されている。この位相調整回路130aにおける、既述の図6における位相調整回路130との相違点は、遅延量がそれぞれ異なる複数(n)の出力(DCLK[M−n])を得るように構成された遅延回路131aを適用している点である。

【0039】

即ち、VCO114の出力周期に対しMを自然数としてその1/M倍、2/M倍・・・(M−1)/M倍の各出力を得るように構成されている点である。そして、複数の遅延出力信号を前記位相シフト回路に供給する。尚、出力周期の1/M倍は、例えば図8を参照して既述のような遅延回路を用いれば、容易に実現することができる。

図9の位相調整回路130aにおける位相シフト回路132aは、図10に示すような選択回路を適用して実現できる。

【0040】

図10は、図9の位相調整回路130aに適用される位相シフト回路132aとしての選択回路を例示するブロック図である。

図10の選択回路では、既述の誤差信号に応じて選択的に一のスイッチ素子がオンとなるように制御可能な複数のスイッチ素子が並置され、何れか一のオンになった素子によって当該素子に対応する信号を選択的に出力する構成を採る。

【0041】

例えば遅延回路131aから、VCO114の出力周期の1/4倍、2/4倍、3/4倍の遅延量を持った遅延信号が入力されていれば、誤差信号として1/4、2/4、3/4が入力されたときには、その複数の遅延信号のうちの一つを選択するだけで、所望の位相調整信号を得られる。よって、本実施の形態は非常に少ない素子数の構成で位相シフト回路を構成できるという点が一つの特徴である。

遅延量と誤差信号が同一とならない場合でも、両者が近似した値となるような遅延量を選択すればよい。その場合は、フラクショナルスプリアスを完全に消去することはできないが、遅延量の刻み幅をある程度細かくとっておけば、実用上十分なフラクショナルスプリアス低減効果を奏し得る。

【0042】

図11は、図9の位相調整回路に適用される遅延回路を例示するブロック図である。

図11に例示された遅延回路131aでは、遅延量を細密な分解能で選択可能な構成を採っている。即ち、並置された複数の選択スイッチのうち隣接する選択スイッチを同時にONにすることによって、各選択スイッチに対応して供給される遅延量が漸次異なる複数の遅延信号について、隣接する遅延信号間でそれらの補間をとり、両者の中間に該当する位相の信号を生成する。これにより、遅延量の刻み幅が、遅延回路で生成されたものの1/2となるような細密な分解能での遅延量の選択が可能となる。

【0043】

尚、隣接する遅延信号間でそれらの補間をとる方法は、図11に例示されたような簡便な方法に限らず、たとえば図8を参照して既述のような所望の遅延量を得るような手法を採ってもよい。その場合は、フラクショナルスプリアスを一層低減することができる。

以上を通して理解されるとおり、図1乃至図11を参照して説明した技術は、アキュムレータからの誤差信号に基づいて参照信号の位相を制御することを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザの制御方法の技術思想であると観念することができる。

【符号の説明】

【0044】

100……………………………アキュムレータ型フラクショナルN−PLLシンセサイザ

111、1211、1311…位相検出器

112、1212、1312…チャージポンプ

113、1213、1313…LPF

114、1214、1314…VCO

115、1215、1315…フラクショナル分周器

120、1220、1320…アキュムレータ

121……………………………加算器

122……………………………飽和処理回路

130、130a………………位相調整回路

131、131a………………遅延回路

132、132a………………位相シフト回路

1300 …………………………フラクショナルN−PLLシンセサイザ

1321a、1321b………トランスコンダクタンスアンプ

1322 …………………………コンパレータ

【技術分野】

【0001】

本発明はフラクショナルN−PLLシンセサイザ、特に、アキュムレータを用いてフラクショナル分周数を制御するアキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法に関する。

【背景技術】

【0002】

フラクショナルN−PLLシンセサイザは、電圧制御発振器(以下VCO)の出力を分周する帰還分周数が、小数分周であることを特徴とするPLLである。ここで一般的なフラクショナルN−PLLシンセサイザの一例を図12に示す。

図12において、フラクショナルN−PLLシンセサイザ1200は、参照信号と帰還信号との位相差を検出する位相検出器1211、その次段のチャージポンプ1212、更に次段のローパスフィルタ(以下LPF)1213、その次段のVCO1214、VCO1214の出力を分周するフラクショナル分周器1215、および、デルタシグマ変調器1220から構成され、デルタシグマ型フラクショナルN−PLLシンセサイザと称される。

【0003】

位相検出器1211は参照信号とフラクショナル分周器1215の出力である帰還信号との位相差を検出し、チャージポンプ1212に出力する。チャージポンプ1212は位相差に応じた電荷量をLPF1213に出力する。

VCO1214はLPF1213の出力に応じて出力周波数を変化させる。フラクショナル分周器1215はVCO1214の出力信号を既定の分周比で分周して位相検出器1211に出力する。

【0004】

デルタシグマ変調器1220は、帰還分周数の分子と分母の設定値により、フラクショナル分周器1215における分周数を、N分周およびN+1分周の何れかとするように時間的に切り替える。

例えば、参照信号の周波数をFref、帰還分周数を、N+NUM/DEN(N、NUM、DENはそれぞれ整数)とおくと、VCO1214の出力信号の発振周波数Fvcoは、

Fvco=Fref×(N+NUM/DEN)………(1)

と表される。

【0005】

式(1)を変形すると、

Fvco=Fref×{(NUM/DEN)×(N+1)+(1−NUM/DEN)×N}………………………………………………………………………(2)

が得られ、N分周、N+1分周を式(2)に従った時間割合で分周数を切り替えることによって、フラクショナル分周器1215は小数分周数を実現している。

【0006】

また、デルタシグマ変調を用いることによって、非周期的に帰還分周数を切り替えるため、切り替える周期に応じた固有のスプリアスであるフラクショナルスプリアスが生じ難いという利点がある。

しかしながら、図12を参照して説明した上記方式では、フラクショナルスプリアスをデルタシグマ変調器1220で高周波数側にノイズシェープしているため、PLLを構成するLPF1213でそのノイズ成分を除去する必要が生じる。従って、このデルタシグマ型フラクショナルN−PLLシンセサイザではLPFのカットオフ周波数の低域化を要するという問題があった。

【0007】

PLLを構成するLPFは、PLLの構成要素であるLPFやVCOからみるとハイパスフィルタ(以下HPF)として機能している。従って、LPFやVCOの構成要素から生じた低周波のノイズ成分は、このLPFによって除去される。このため、LPFのカットオフ周波数が高いほど、低周波のノイズ成分を効率良く除去することが可能である。

上述の事情により、デルタシグマ型フラクショナルN−PLLシンセサイザでは、PLLを構成するLPFやVCOから生じる低周波のノイズを十分に除去することができず、結果的にフラクショナルN−PLLシンセサイザの出力信号の性能(ジッタ)が劣化してしまうという課題を残している。

【0008】

図13は、図12とは異なる従来例としてアキュムレータを用いた方式によるフラクショナルN−PLLシンセサイザを表す図である。

図13において、フラクショナルN−PLLシンセサイザ1300は、参照信号と帰還信号との位相差を検出する位相検出器1311、その次段のチャージポンプ1312、更に次段のローパスフィルタ(以下LPF)1313、その次段のVCO1314、VCO1314の出力を分周するフラクショナル分周器1315、および、フラクショナル分周器1315の分周数を周期的に切り替えるアキュムレータ1320から構成され、アキュムレータ型フラクショナルN−PLLと称される。

【0009】

アキュムレータ型フラクショナルN−PLLでは、アキュムレータ1320の出力によってフラクショナル分周器1315の分周数を周期的に切り替えることにより小数分周数を実現する方式を採っている。この方式では、図12の方式におけるようなデルタシグマ変調器を持たないため高周波域のノイズを除去する必要がなく、LPFのカットオフ周波数を高く出来る。従って、PLLを構成するLPFやVCOから生じる低周波のノイズを十分に除去することができ、出力信号の性能(ジッタ)を向上させることができるという点で優れる。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】S.E.Meninger and M.H.Perrott,“ A 1MHz Bandwidth 3.6−GHz 0.18um CMOS Fractional−N Synthesizer Utilizing a Hybrid PFD/DAC structure for Reduced Broadband Phase Noise、 ”IEEE J.Solid-state Circuits, vol.41、pp.966-980、April 2006.

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、図13を参照して説明した従来のアキュムレータ型フラクショナルN−PLLシンセサイザでは、フラクショナル分周器の分周数を周期的に切り替えるため、切り替える周期に応じたフラクショナルスプリアスが生じてしまうという課題があった。

本願発明は上述のような状況に鑑みてなされたものであり、フラクショナルスプリアスの少ないアキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記課題を解決するために、ここに、次に列挙するような技術を提案する。

(1)発振出力信号の帰還路に介挿されたフラクショナル分周器の分周数をアキュムレータの出力によって周期的に切り替えることにより小数分周数の帰還信号を得るアキュムレータ型フラクショナルN−PLLシンセサイザであって、

前記フラクショナル分周器からの帰還信号が一方の入力端に供給される位相検出器と、

前記アキュムレータからの誤差信号に基づいて既定の参照信号に位相調整を施した位相調整信号を前記位相検出器の他方の入力端に供給する位相調整回路と、

を備えることを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザ。

【0013】

(2)前記位相調整回路は、

入力された前記参照信号を遅延させた信号を出力する遅延回路と、

前記参照信号と前記遅延回路から出力される遅延信号とによって前記位相調整信号を生成する位相シフト回路と、

を備えることを特徴とする(1)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(3)前記遅延回路は、自己への入力信号を前記発振出力信号の周期分だけ遅延させることを特徴とする(2)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【0014】

(4)前記遅延回路は、前記発振器を構成する遅延素子と同じ構成を持つことを特徴とする(3)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(5)前記位相シフト回路は、前記参照信号と前記遅延回路から出力される遅延信号とが供給されるようになされ、前記アキュムレータからの誤差信号に基づいて該供給された前記参照信号に対して位相シフトを施すことによって前記位相調整信号を生成することを特徴とする(2)乃至(4)の何れか一に記載のフラクショナルN−PLL。

【0015】

(6)前記遅延回路は、前記発振器の出力周期に対しMを自然数としてその1/M、2/M、…、(M−1)/M倍遅延させた複数の出力信号を前記位相シフト回路に供給することを特徴とする(2)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(7)前記位相シフト回路は、前記遅延回路から供給される複数の遅延信号のうちの一の遅延信号を前記誤差信号に基づいて選択し出力することを特徴とする(6)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【0016】

(8)前記位相シフト回路は、前記遅延回路から供給された前記複数の遅延信号について隣接する遅延信号間での補間をとった複数の信号のうちの一の信号を前記誤差信号に基づいて選択し出力することを特徴とする(6)のアキュムレータ型フラクショナルN−PLLシンセサイザ。

(9)アキュムレータからの誤差信号に基づいて参照信号の位相を制御することを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザの制御方法。

【発明の効果】

【0017】

本発明によれば、フラクショナルスプリアスの少ないアキュムレータ型フラクショナルN−PLLシンセサイザを実現することができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施の形態であるアキュムレータ型フラクショナルN−PLLシンセサイザを表すブロック図である。

【図2】図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用されるアキュムレータを例示するブロック図である。

【図3】図2のアキュムレータの出力を時系列に沿って周期毎に表す図である。

【図4】図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相調整回路の入出力に関係する各信号を表すタイミングチャートである。

【図5】図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相検出器への入出力に関係する各信号を表すタイミングチャートである。

【図6】図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路の一例を表すブロック図である。

【図7】図6の位相調整回路に適用される位相シフト回路を例示するブロック図である。

【図8】図6の位相調整回路に適用される遅延回路を例示するブロック図である。

【図9】図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路の他の例を表すブロック図である。

【図10】図9の位相調整回路に適用される位相シフト回路(選択回路)を例示するブロック図である。

【図11】図9の位相調整回路に適用される遅延回路を例示するブロック図である。

【図12】一般的なデルタシグマ型フラクショナルN−PLLシンセサイザを表すブロック図である。

【図13】従来のアキュムレータ型フラクショナルN−PLLシンセサイザを表すブロック図である。

【発明を実施するための形態】

【0019】

以下に、本発明の実施の形態について詳述することにより本発明を明らかにする。

図1は本発明の実施形態であるアキュムレータ型フラクショナルN−PLLシンセサイザを表すブロック図である。

図1において、アキュムレータ型フラクショナルN−PLLシンセサイザ100は、位相検出器111、チャージポンプ112、LPF113、VCO114、フラクショナル分周器115、および、アキュムレータ120を有し、更に、アキュムレータ120の出力によって制御される位相調整回路130が図示のように位相検出器111の前段に介挿されて構成されている。

【0020】

アキュムレータ型フラクショナルN−PLLシンセサイザ100は、参照信号と帰還信号との位相差を検出する位相検出器111、その次段のチャージポンプ112、更に次段のLPF113、その次段のVCO114、VCO114の出力を分周するフラクショナル分周器115、および、アキュムレータ120を有し、これらは、図13を参照して既述のフラクショナルN−PLLシンセサイザ1300における、位相検出器1311、チャージポンプ1312、LPF1313、VCO1314、フラクショナル分周器1315、および、アキュムレータ1320に上述の順に逐次対応している。

そして、本例のアキュムレータ型フラクショナルN−PLLシンセサイザ100では、詳細を後述するように、位相検出器111に入力される参照信号に位相調整が施されるように構成され、その位相調整にアキュムレータ120からの誤差信号を用いる点を一つの特徴としている。

【0021】

次に、図面を参照して、アキュムレータ120、フラクショナル分周器115、および位相調整回路130について説明する。

図2は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザ100に適用されるアキュムレータ120を例示するブロック図である。

図2において、アキュムレータ120は、分子/分母で表される小数値と、誤差信号とを、加算器121を用いて加算する。加算器121の次段の飽和処理回路122では、加算信号ADDが1より大か小かを判断し、1より小さければ、一方の出力ER=ADDとし、且つ、他方の出力CA=0とする出力を発し、1と同じもしくは大きければ、一方の出力ER=ADD−1とし、且つ、他方の出力CA=1とする出力を発する。

【0022】

図3は、図2のアキュムレータ120の出力を時系列に沿って周期毎に表す図である。即ち、図3には、アキュムレータ120が出力する各信号の時間サイクルが列記されている。

図3より容易に理解される通り、オーバーフロー信号は、00010001・・と周期的に信号を出力する。これにより、分周数を22232223・・・と切り替えて、入力されたクロックのエッジを9発カウントする間に、4回のクロックエッジを作り出す。これにより9/4の小数分周を実現する。そして、アキュムレータ120から出力されるオーバーフローする以前の積算情報は、誤差信号として、1/4、2/4、3/4、0、1/4、2/4、3/4、0・・・と出力される。

【0023】

一方、位相調整回路130では、アキュムレータ120が出力する上述のような誤差信号と既定の参照信号とに基づいて、図4のように位相を調整した信号を作り出し、この信号を位相検出器111に出力する。

図4は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相調整回路130の入出力に関係する各信号を表すタイミングチャートである。尚、位相調整回路130の構成例については、図6を参照して後述する。

【0024】

図4を既述の図3と対照して容易に理解される通り、VCO114の出力の1周期毎に、デジタル信号である誤差信号が1/4周期ずつ遅延した状態を表す値をとる。即ち、図3を参照して既述の通り、その遅延が、1周期を単位として、その1/4、2/4、3/4、0、1/4、2/4、3/4、0・・・となる如く出力される。そして、誤差信号によって表されるその遅延が3/4→0/4となるタイミングで自己の周期が半周期遅延する位相調整信号が出力される。

【0025】

そして、位相検出器111では、図3および図4を参照して説明した位相調整信号(位相調整された参照信号)とフラクショナル分周器115の出力である帰還信号とに基づいて、位相検出出力を得る。

図5は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザにおける位相検出器111への入出力に関係する各信号を表すタイミングチャートである。

【0026】

図5を参照して理解される通り、PLLのロック状態でも参照信号と帰還信号との二つの信号には位相の誤差が周期的に生じる。これがフラクショナルスプリアスの原因となる。位相の誤差量は、VCO114の出力信号の1周期を単位として、その、1/4、2/4、3/4、0、1/4、2/4、3/4、0・・・となる。

図4を参照して既述のとおり、この位相の誤差量に対応するデジタル信号である誤差信号に基づいて、位相調整された参照信号である位相調整信号が出力される。

【0027】

図1の実施形態では、上述のようにして、フラクショナル分周器115から出力される周期的なクロックのエッジのずれをあらかじめ予測し、位相調整回路130で参照信号のエッジ(即ち、位相)を調整するため、当該フラクショナルN−PLL100が位相をロックした状態では、位相検出器111に入力される2つの信号の間に位相差が生じない。従って、ロック状態ではチャージポンプ112からLPF113に電荷を出力しないため、VCO114の入力電圧が周期的に変動することがない。よって、従来のアキュムレータ型フラクショナルN−PLLの課題であったフラクショナルスプリアスを大幅に低減することができる。

【0028】

このため、本実施の形態におけるアキュムレータ型フラクショナルN−PLLシンセサイザでは、フラクショナルスプリアスを生じさせるチャージポンプからの周期的な電荷出力を、新たに保有する別のチャージポンプの出力によってキャンセルするといった別の手法との比較においても、そもそも位相検出器111の入力に位相差を生じさせないようにしているために、VCO114の入力電圧が周期的に変動することがなく、フラクショナルスプリアスの低減効果がより顕著である。

【0029】

また、図1の実施形態では、図12を参照して既述のデルタシグマ型フラクショナルN−PLLシンセサイザとの比較においては、フラクショナルスプリアス自体の低減をはかっている点が特徴的である。従って、デルタシグマ型フラクショナルN−PLLシンセサイザでは必要であったLPFのカットオフ周波数の低帯域化が不要となるため、LPFやVCOを構成する要素から生じた低周波のノイズ成分を効率よく除去することが可能であり、当該フラクショナルN−PLLシンセサイザとしての出力信号の性能(ジッタ)を向上させることが可能である。

【0030】

更に、一般的なデルタシグマ型フラクショナルN−PLLシンセサイザでは、フラクショナル分周をする際の分母の値を固定値にする必要があり、周波数誤差を伴わずに任意の周波数を作り出すことができないという問題があった。これに対し、本実施の形態では、アキュムレータ型フラクショナルN−PLLシンセサイザの方式を採ることを特徴としており、そのため周波数誤差を伴わずに任意の周波数を作り出すことができるという優れた特徴をも併せ持つ。

【0031】

図6は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路130の一例を表すブロック図である。

図6の位相調整回路130は、遅延回路131と位相シフト回路132とが図示のように接続されて構成されている。この位相調整回路130では、入力された参照信号は、遅延回路131によって、ある遅延量を持った遅延信号となって出力される。遅延信号と参照信号との位相差は、一定値であることが望ましい。フラクショナル分周器115によって、VCO114の出力信号がN分周もしくはN+1分周されるので、参照信号と帰還信号の位相差は、既述の図5におけるように最大でもVCO114の発振周期を超えることはない。しかしながら、遅延信号と参照信号の位相差が、VCO114の発振周期と同一であることはより望ましい。

【0032】

尚、ここではフラクショナル分周器115として、N分周もしくはN+1分周を行なうデュアルモジュラス周波数分周器を例示したが、この例によらず、N分周とN+2分周等種々の仕様を採ることができる。N分周とN+2分周の仕様とする場合は、遅延信号と参照信号の位相差はVCO115の発振周期の2倍と同一であることがより望ましい。

図6の位相調整回路130における上述の遅延回路131の次段に設けられた位相シフト回路132では、遅延回路131の出力である遅延信号、既述の参照信号、および、アキュムレータ120から供給される誤差信号に基づいて、出力信号たる位相調整信号を生成する。

【0033】

次に、図6および既述の図4を併せ参照して、位相シフト回路132について更に説明する。位相シフト回路132は、その両入力である参照信号と遅延信号との立ち上がりエッジ間を位相シフトすることによって位相調整回路130の出力たる位相調整信号を生成する。例えば、アキュムレータ120からの誤差信号がVCO114の出力信号の1周期を単位として、その、1/4の場合、参照信号と誤差信号の立ち上がりエッジ間のちょうど上述の1/4の位置に位相調整信号の立ち上がりエッジを生成する。次のステップで誤差信号が2/4の場合、参照信号と誤差信号の立ち上がりエッジ間のちょうど真ん中の位置に位相調整信号の立ち上がりエッジを生成する。

【0034】

図7は、図6の位相調整回路に適用される位相シフト回路を例示するブロック図である。

図7において、位相シフト回路132は、トランスコンダクタンス値が電流によって可変のトランスコンダクタンスアンプ2個(1321a、1321b)とコンパレータ1322を備えて構成されている。参照信号と遅延信号は、あらかじめCML(カレントモードロジック)の差動信号に変換されている。誤差信号を元に、それぞれのトランスコンダクタンス値をコントロールする。例えば誤差信号が上述の如く1/4の場合、参照信号側と遅延信号側のトランスコンダクタンス値の比を1:3にすることによって所望の位相シフト量を得ることができる。尚、位相シフト回路の構成は図7に例示したものに限定されることはない。

【0035】

上述の実施の形態では、位相調整回路130を帰還信号側ではなく、参照信号側に設けていることを特徴としている。従って、図7の位相シフト回路132に入力される信号には周波数変調がかかっていないため、この位相シフト回路1320における設計上の制約が緩和されるだけでなく、精度よく位相調整ができるという点も一つの特徴である。

【0036】

図8は、図6の位相調整回路に適用される遅延回路を例示するブロック図である。

次に、図8を参照して遅延回路131について説明する。図8の例では、VCO114の構成が遅延素子が3段縦続接続されたリングオシレータ構成を成している。また遅延素子の電源は、発振周波数を制御するために可変となっている。遅延回路131は、VCO114を構成する遅延素子を6段縦続接続した構成と採っており、電源も共通としている。上述のように構成することにより、遅延回路131の遅延量は、VCO114の発振周期に精度よく合致した特性を呈する。

【0037】

なお、VCO114の構成は図8の例に限られたものではなく、上述のようなリングオシレータの態様を採るに替えて、マルチバイブレータにより構成する態様を採ってもよい。また、リングオシレータの態様を採る場合においても、遅延素子の段数は3段に限定されるものではない。また遅延素子の構成として、例えば、遅延素子の負荷容量を制御して発振周波数をコントロールする態様を採ってもよい。その場合は、遅延回路の各遅延素子も同量の負荷容量とすることによって所要の特性を得ることができる。

【0038】

図9は、図1のアキュムレータ型フラクショナルN−PLLシンセサイザに適用される位相調整回路の他の例を表すブロック図である。

図9の位相調整回路130aは、遅延回路131aと(選択回路)132aとが図示のように接続されて構成されている。この位相調整回路130aにおける、既述の図6における位相調整回路130との相違点は、遅延量がそれぞれ異なる複数(n)の出力(DCLK[M−n])を得るように構成された遅延回路131aを適用している点である。

【0039】

即ち、VCO114の出力周期に対しMを自然数としてその1/M倍、2/M倍・・・(M−1)/M倍の各出力を得るように構成されている点である。そして、複数の遅延出力信号を前記位相シフト回路に供給する。尚、出力周期の1/M倍は、例えば図8を参照して既述のような遅延回路を用いれば、容易に実現することができる。

図9の位相調整回路130aにおける位相シフト回路132aは、図10に示すような選択回路を適用して実現できる。

【0040】

図10は、図9の位相調整回路130aに適用される位相シフト回路132aとしての選択回路を例示するブロック図である。

図10の選択回路では、既述の誤差信号に応じて選択的に一のスイッチ素子がオンとなるように制御可能な複数のスイッチ素子が並置され、何れか一のオンになった素子によって当該素子に対応する信号を選択的に出力する構成を採る。

【0041】

例えば遅延回路131aから、VCO114の出力周期の1/4倍、2/4倍、3/4倍の遅延量を持った遅延信号が入力されていれば、誤差信号として1/4、2/4、3/4が入力されたときには、その複数の遅延信号のうちの一つを選択するだけで、所望の位相調整信号を得られる。よって、本実施の形態は非常に少ない素子数の構成で位相シフト回路を構成できるという点が一つの特徴である。

遅延量と誤差信号が同一とならない場合でも、両者が近似した値となるような遅延量を選択すればよい。その場合は、フラクショナルスプリアスを完全に消去することはできないが、遅延量の刻み幅をある程度細かくとっておけば、実用上十分なフラクショナルスプリアス低減効果を奏し得る。

【0042】

図11は、図9の位相調整回路に適用される遅延回路を例示するブロック図である。

図11に例示された遅延回路131aでは、遅延量を細密な分解能で選択可能な構成を採っている。即ち、並置された複数の選択スイッチのうち隣接する選択スイッチを同時にONにすることによって、各選択スイッチに対応して供給される遅延量が漸次異なる複数の遅延信号について、隣接する遅延信号間でそれらの補間をとり、両者の中間に該当する位相の信号を生成する。これにより、遅延量の刻み幅が、遅延回路で生成されたものの1/2となるような細密な分解能での遅延量の選択が可能となる。

【0043】

尚、隣接する遅延信号間でそれらの補間をとる方法は、図11に例示されたような簡便な方法に限らず、たとえば図8を参照して既述のような所望の遅延量を得るような手法を採ってもよい。その場合は、フラクショナルスプリアスを一層低減することができる。

以上を通して理解されるとおり、図1乃至図11を参照して説明した技術は、アキュムレータからの誤差信号に基づいて参照信号の位相を制御することを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザの制御方法の技術思想であると観念することができる。

【符号の説明】

【0044】

100……………………………アキュムレータ型フラクショナルN−PLLシンセサイザ

111、1211、1311…位相検出器

112、1212、1312…チャージポンプ

113、1213、1313…LPF

114、1214、1314…VCO

115、1215、1315…フラクショナル分周器

120、1220、1320…アキュムレータ

121……………………………加算器

122……………………………飽和処理回路

130、130a………………位相調整回路

131、131a………………遅延回路

132、132a………………位相シフト回路

1300 …………………………フラクショナルN−PLLシンセサイザ

1321a、1321b………トランスコンダクタンスアンプ

1322 …………………………コンパレータ

【特許請求の範囲】

【請求項1】

発振出力信号の帰還路に介挿されたフラクショナル分周器の分周数をアキュムレータの出力によって周期的に切り替えることにより小数分周数の帰還信号を得るアキュムレータ型フラクショナルN−PLLシンセサイザであって、

前記フラクショナル分周器からの帰還信号が一方の入力端に供給される位相検出器と、

前記アキュムレータからの誤差信号に基づいて既定の参照信号に位相調整を施した位相調整信号を前記位相検出器の他方の入力端に供給する位相調整回路と、

を備えることを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項2】

前記位相調整回路は、

入力された前記参照信号を遅延させた信号を出力する遅延回路と、

前記参照信号と前記遅延回路から出力される遅延信号とによって前記位相調整信号を生成する位相シフト回路と、

を備えることを特徴とする請求項1に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項3】

前記遅延回路は、自己への入力信号を前記発振出力信号の周期分だけ遅延させることを特徴とする請求項2に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項4】

前記遅延回路は、前記発振出力信号を生成する発振器を構成する遅延素子と同じ構成を持つことを特徴とする請求項3に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項5】

前記位相シフト回路は、前記参照信号と前記遅延回路から出力される遅延信号とが供給されるようになされ、前記アキュムレータからの誤差信号に基づいて該供給された前記参照信号に対して位相シフトを施すことによって前記位相調整信号を生成することを特徴とする請求項2乃至請求項4の何れか一項に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項6】

前記遅延回路は、前記発振出力信号の出力周期に対しMを自然数としてその1/M、2/M、…、(M−1)/M倍遅延させた複数の出力信号を前記位相シフト回路に供給することを特徴とする請求項2に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項7】

前記位相シフト回路は、前記遅延回路から供給される複数の遅延信号のうちの一の遅延信号を前記誤差信号に基づいて選択し出力することを特徴とする請求項6に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項8】

前記位相シフト回路は、前記遅延回路から供給された前記複数の遅延信号について隣接する遅延信号間での補間をとった複数の信号のうちの一の信号を前記誤差信号に基づいて選択し出力することを特徴とする請求項6に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項9】

アキュムレータからの誤差信号に基づいて参照信号の位相を制御することを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザの制御方法。

【請求項1】

発振出力信号の帰還路に介挿されたフラクショナル分周器の分周数をアキュムレータの出力によって周期的に切り替えることにより小数分周数の帰還信号を得るアキュムレータ型フラクショナルN−PLLシンセサイザであって、

前記フラクショナル分周器からの帰還信号が一方の入力端に供給される位相検出器と、

前記アキュムレータからの誤差信号に基づいて既定の参照信号に位相調整を施した位相調整信号を前記位相検出器の他方の入力端に供給する位相調整回路と、

を備えることを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項2】

前記位相調整回路は、

入力された前記参照信号を遅延させた信号を出力する遅延回路と、

前記参照信号と前記遅延回路から出力される遅延信号とによって前記位相調整信号を生成する位相シフト回路と、

を備えることを特徴とする請求項1に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項3】

前記遅延回路は、自己への入力信号を前記発振出力信号の周期分だけ遅延させることを特徴とする請求項2に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項4】

前記遅延回路は、前記発振出力信号を生成する発振器を構成する遅延素子と同じ構成を持つことを特徴とする請求項3に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項5】

前記位相シフト回路は、前記参照信号と前記遅延回路から出力される遅延信号とが供給されるようになされ、前記アキュムレータからの誤差信号に基づいて該供給された前記参照信号に対して位相シフトを施すことによって前記位相調整信号を生成することを特徴とする請求項2乃至請求項4の何れか一項に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項6】

前記遅延回路は、前記発振出力信号の出力周期に対しMを自然数としてその1/M、2/M、…、(M−1)/M倍遅延させた複数の出力信号を前記位相シフト回路に供給することを特徴とする請求項2に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項7】

前記位相シフト回路は、前記遅延回路から供給される複数の遅延信号のうちの一の遅延信号を前記誤差信号に基づいて選択し出力することを特徴とする請求項6に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項8】

前記位相シフト回路は、前記遅延回路から供給された前記複数の遅延信号について隣接する遅延信号間での補間をとった複数の信号のうちの一の信号を前記誤差信号に基づいて選択し出力することを特徴とする請求項6に記載のアキュムレータ型フラクショナルN−PLLシンセサイザ。

【請求項9】

アキュムレータからの誤差信号に基づいて参照信号の位相を制御することを特徴とするアキュムレータ型フラクショナルN−PLLシンセサイザの制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−204883(P2012−204883A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−65009(P2011−65009)

【出願日】平成23年3月23日(2011.3.23)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月23日(2011.3.23)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

[ Back to top ]