アクティブインダクタ回路、発振器、及び、フィルタ回路

【課題】 外部接続用の2端子の各入力インピーダンスが等しく差動回路に適用した場合の波形歪を抑制でき、小面積化、低消費電力化の図れるアクティブインダクタ回路を提供する。

【解決手段】 相互コンダクタンスの極性の異なる第1電圧制御電流源回路5A〜5Dと第2電圧制御電流源回路6A〜6Dの一方の入力と他方の出力、他方の入力と一方の出力

を互いに接続した能動回路1A〜1Dの4つを循環的に接続し、各能動回路の4つの接続点の対向する1対間にキャパシタ4を接続し、他の対向する1対を外部接続用の端子対Nx1,Nx2として構成する。

【解決手段】 相互コンダクタンスの極性の異なる第1電圧制御電流源回路5A〜5Dと第2電圧制御電流源回路6A〜6Dの一方の入力と他方の出力、他方の入力と一方の出力

を互いに接続した能動回路1A〜1Dの4つを循環的に接続し、各能動回路の4つの接続点の対向する1対間にキャパシタ4を接続し、他の対向する1対を外部接続用の端子対Nx1,Nx2として構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アクティブインダクタ回路に関し、更に、アクティブインダクタ回路を使用した発振器、並びに、フィルタ回路に関する。

【背景技術】

【0002】

インダクタは、無線受信器用の局部発信器やフィルタ回路等に広く用いられる。しかし、一例として図12に示すような、集積回路(IC)上に金属薄膜配線を矩形または円形の螺旋状に旋回させて形成した受動素子としてのオンチップインダクタは、チップ上に占める面積が非常に大きくなる傾向がある。このため、小面積化のため、MOSトランジスタ等の能動素子で構成されるOTA(Operational Transconductance Amplifier)等の電圧制御電流源回路を用いてインダクタの機能を模擬した回路(アクティブインダクタ回路)を実現する試みが多数なされている(例えば、下記の非特許文献1のFig.3(d)及び(e)等参照)。

【0003】

図13は、2つの電圧制御電流源41、42と1個のキャパシタ43からなるアクティブインダクタ回路の一例を示す。図13のアクティブインダクタ回路のインピーダンス値Zinは、下記の数1で与えられ、そのインダクタンス値(L=Zin/s)は、電圧制御電流源41、42の相互コンダクタンス(gm1,gm2)、または、キャパシタ43のキャパシタンス値(電気容量)C0を調整して制御可能である。

【0004】

[数1]

Zin=sC0/(|gm1|×|gm2|)=sL

【0005】

ここで、電圧制御電流源41、42は、夫々非反転入力端子と反転入力端子を備え、非反転入力端子と反転入力端子間の入力電圧が相互コンダクタンスgm1,gm2によって出力電流に変換される差動入力型の電圧制御電流源回路であり、電圧制御電流源41の入力電圧は非反転入力端子に入力され、電圧制御電流源42の入力電圧は反転入力端子に入力されているので、夫々の出力電流の方向を同じとすれば、各相互コンダクタンスgm1,gm2の極性が相互に正負逆極性となっていると看做すことができる。

【0006】

また、図13に示すアクティブインダクタ回路は、1つの端子と接地電位間のインダクタを模擬する回路であり、任意の2端子間に挿入して使用するアクティブインダクタ回路としては適合しない。そこで、図14に、任意の2端子間に挿入して使用可能なアクティブインダクタ回路の一例として、3つの差動入力型の電圧制御電流源51〜53と1個のキャパシタ54からなるアクティブインダクタ回路を示す。図14のアクティブインダクタ回路のインピーダンスZinは、下記の数2で与えられ、そのインダクタンス値(L=Zin/s)は、電圧制御電流源81〜83の相互コンダクタンス(|gm1|=|gm2|=|gm3|=gm)、または、キャパシタ54のキャパシタンス値(電気容量)C0を調整して制御可能である。

【0007】

[数2]

Zin=sC0/gm2=sL

【0008】

【非特許文献1】Randall L.Geiger and Edger Sanchez−Sinencio,“Active Filter Design Using Operational Transconductance Amplifiers:A Tutorial”,IEEE Circuits and devices Magazine,1985

【発明の開示】

【発明が解決しようとする課題】

【0009】

アクティブインダクタ回路は、受動型と比較してチップ占有面積を小さくできる反面、電圧制御電流源部に定常的に電流を流す必要があるため消費電力が増大し、回路内で発生する雑音も問題となる。

【0010】

アクティブインダクタ回路を利用した電圧制御発振器やフィルタ回路等では、その発生する雑音が課題となる。電流を流すことで雑音発生を抑制することは可能だが、低消費電力化のためには、回路の工夫で雑音を低減することが求められる。

【0011】

図14に示すアクティブインダクタ回路は、構造的には、図13に示すアクティブインダクタ回路の入力端子の極性が相互に反転した2つを組み合わせ、出力端子が同じキャパシタに接続してなる図15に示すアクティブインダクタ回路に対して、2つの電圧制御電流源55,56(図15参照)を1つの電圧制御電流源(図14の電圧制御電流源51)に置換したものである。図14に示すアクティブインダクタ回路は、他の2つの電圧制御電流源52,53の相互コンダクタンスgm2,gm3が必ずしも等価である必要はなく、回路構成上等価でない場合には、入力端子V1と出力端子V2が非対称となる場合もある。また、図15に示すアクティブインダクタ回路は、差動入力型の電圧制御電流源を用いたが、図16に示すように、これを単一入力(シングルエンド)の回路構成とすると、入力端子V1側に入力端子が接続する電圧制御電流源61と出力端子V2側に入力端子が接続する電圧制御電流源64が同じ回路構成とはならず、また、入力端子V1側に出力端子が接続する電圧制御電流源62と出力端子V2側に出力端子が接続する電圧制御電流源63が同じ回路構成とはならないので、入力端子V1と出力端子V2から回路側を見た入力インピーダンスが一致せずに非対称となる。

【0012】

斯かる非対称なアクティブインダクタ回路を用いて差動回路の電圧制御発振器やフィルタ回路を構成する場合、差動回路の差動端子対間に図14に示すアクティブインダクタ回路の入力端子V1と出力端子V2を夫々接続すると、入力端子V1と出力端子V2から回路側を見た入力インピーダンスが異なるため、差動回路による平衡動作が阻害され、差動回路の波形歪の原因となり、所期の電圧制御発振器やフィルタ回路の性能が低下する。

【0013】

また、図14に示すアクティブインダクタ回路を集積回路として構成する場合、キャパシタ84が必要となる。集積回路内に構成するキャパシタ構造、例えば、MIM(Metal−Insulator−Metal)構造やMOM(Metal−Oxide−Metal)構造のキャパシタは、集積回路チップ上においてアクティブインダクタ回路の大部分を占める。集積回路の製造コスト削減のためにはキャパシタの小面積化が必要であり、キャパシタの電気容量の削減は小面積化には効果的である。

【0014】

本発明は、上記問題点に鑑みてなされたものであり、その目的は、第1に、外部接続用の2端子の各入力インピーダンスが等しく差動回路に適用した場合の波形歪を抑制でき、第2に、従来回路に比べて使用するキャパシタの電気容量を低減して小面積化が図れ、第3に低消費電力化の図れるアクティブインダクタ回路を提供する点にある。

【課題を解決するための手段】

【0015】

上記目的を達成するための本発明に係るアクティブインダクタ回路は、夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、キャパシタとを備えてなるアクティブインダクタ回路であって、少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、前記第1、第2、第3及び第4能動回路の夫々が、入力電圧が第1相互コンダクタンスによって出力電流に変換される第1電圧制御電流源回路と、入力電圧が前記第1相互コンダクタンスと極性の異なる第2相互コンダクタンスによって出力電流に変換される第2電圧制御電流源回路と、第1端子と、第2端子を備え、前記第1電圧制御電流源回路の入力端子と前記第2電圧制御電流源回路の出力端子を前記第1端子と接続し、前記第1電圧制御電流源回路の出力端子と前記第2電圧制御電流源回路の入力端子を前記第2端子と接続して構成され、前記第1能動回路の前記第2端子と、前記第2能動回路の前記第1端子を接続し、前記第2能動回路の前記第2端子と、前記第3能動回路の前記第1端子を接続し、前記第3能動回路の前記第2端子と、前記第4能動回路の前記第1端子を接続し、前記第4能動回路の前記第2端子と、前記第1能動回路の前記第1端子を接続し、前記第1能動回路の前記第2端子と、前記キャパシタの一方端を接続し、前記第3能動回路の前記第2端子と、前記キャパシタの他方端を接続し、前記第1能動回路の前記第1端子と前記第3能動回路の前記第1端子を外部接続用の端子対とすることを第1の特徴とする。

【0016】

上記第1の特徴のアクティブインダクタ回路によれば、外部接続用の端子の一方が、第1能動回路の第1端子と第4能動回路の第2端子の接続点で、外部接続用の端子の他方が、第3能動回路の第1端子と第2能動回路の第2端子の接続点であり、また、第1能動回路と第3能動回路が同じ回路で、第2能動回路と第4能動回路が同じ回路であるので、外部接続用の端子対から見て対称な回路構成となり、外部接続用の各端子のインピーダンスが等価となり、差動回路に適用した場合に波形歪を抑制できる。また、第1能動回路の第2端子と第2能動回路の第1端子を接続した中間点にキャパシタの一方端を接続し、キャパシタの他方端を接地電位等の固定電位に接続し、第1能動回路の第1端子と第2能動回路の第2端子を外部接続用の端子対とする従来の回路構成(図15参照)と比較して、同じインダクタンス値を得るためのキャパシタの電気容量が4分の1で済むため、アクティブインダクタ回路の小面積化が図れる。

【0017】

更に、第1、第2、第3及び第4能動回路が循環的に接続する構成となっているため、後述するように、各能動回路に回路構成によっては、1つの能動回路の第2端子に接続するバイアス電流回路と、次段の能動回路の第1端子に接続するバイアス電流回路の各バイアス電流が相殺できるため、低消費電流化に適した回路構成となっている。

【0018】

本発明に係るアクティブインダクタ回路は、上記第1の特徴に加えて、更に、前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々非反転入力端子と反転入力端子を備え、前記非反転入力端子と前記反転入力端子間の入力電圧が相互コンダクタンスによって出力電流に変換される差動入力型の電圧制御電流源回路で構成され、前記第1電圧制御電流源回路が、前記反転入力端子が接地され、前記非反転入力端子が入力端子となる非反転増幅器として構成され、前記第2電圧制御電流源回路が、前記非反転入力端子が接地され、前記反転入力端子が入力端子となる反転増幅器として構成されていることを第2の特徴とする。

【0019】

本発明に係るアクティブインダクタ回路は、上記第2の特徴に加えて、更に、前記第1能動回路の前記第1電圧制御電流源回路と前記第2能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第1端子と、前記反転入力端子が前記第2能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、前記第3能動回路の前記第1電圧制御電流源回路と前記第4能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第3能動回路の前記第1端子と、前記反転入力端子が前記第4能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを第3の特徴とする。

【0020】

本発明に係るアクティブインダクタ回路は、上記第2または第3の特徴に加えて、更に、前記第1能動回路の前記第2電圧制御電流源回路と前記第4能動回路の前記第1電圧制御電流源回路が合体して、前記反転入力端子が前記第1能動回路の前記第2端子と、前記非反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、前記第2能動回路の前記第1電圧制御電流源回路と前記第3能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第2端子と、前記反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを第4の特徴とする。

【0021】

上記第2乃至第4の特徴のアクティブインダクタ回路によれば、各能動回路において、第1電圧制御電流源回路と第2電圧制御電流源回路を同じ差動入力型の電圧制御電流源回路で構成して、上記第1の特徴のアクティブインダクタ回路を実現でき、その作用効果を奏することができる。更に、第3または第4の特徴のアクティブインダクタ回路のように、一部の差動入力型の電圧制御電流源回路を合体して、各能動回路の回路構成を更に簡素化でき、その結果、低消費電流化及び小面積化を図ることができる。

【0022】

本発明に係るアクティブインダクタ回路は、上記第1の特徴に加えて、更に、前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々単一の入力端子と単一の出力端子を備え、前記第1電圧制御電流源回路が非反転増幅器として、前記第2電圧制御電流源回路が反転増幅器として構成されていることを第5の特徴とする。

【0023】

上記第5の特徴のアクティブインダクタ回路によれば、各能動回路の第1及び第2電圧制御電流源回路を、差動入力型の電圧制御電流源回路より少ないトランジスタ数で構成でき、各能動回路の低消費電流化を更に図ることができる。

【0024】

更に、第1及び第2電圧制御電流源回路の入力電圧によって制御される各出力電流の向きが、相互コンダクタンスの極性の違いによって反転するため、各出力端子に流れるバイアス電流も第1及び第2電圧制御電流源回路間で相互に逆方向となる。従って、第1、第2、第3及び第4能動回路が循環的に接続する構成となっているため、1つの能動回路の第2端子に接続する第1電圧制御電流源回路のバイアス電流回路と、次段の能動回路の第1端子に接続する第2電圧制御電流源回路のバイアス電流回路の各バイアス電流を相殺してバイアス電流回路を省略できる、低消費電流化に適した回路構成とすることができる。

【0025】

本発明に係るアクティブインダクタ回路は、上記何れかの特徴に加えて、更に、前記キャパシタが、電気容量が前記キャパシタの2倍の第1キャパシタと第2キャパシタの直列回路で構成され、前記第2キャパシタの一方端と前記第1キャパシタの他方端が相互に接続する中間接続点が、所定の固定電位に接続されていることを第6の特徴とする。

【0026】

上記第6の特徴のアクティブインダクタ回路によれば、キャパシタの電気容量は従来と同じになってしまうものの、外部接続用の各端子のインピーダンスが等価となり、差動回路に適用した場合に波形歪を抑制できる効果は、上記第1乃至第5の各特徴のアクティブインダクタ回路と同様に奏することができる。

【0027】

本発明に係るアクティブインダクタ回路は、更に、夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、2つのキャパシタとを備えてなるアクティブインダクタ回路であって、

少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、

前記第1、第2、第3及び第4能動回路の夫々が、非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路で構成される第1電圧制御電流源回路と第2電圧制御電流源回路と、第1非反転端子と、第1反転端子と、第2非反転端子と、第2反転端子を備え、前記第1電圧制御電流源回路の前記非反転入力端子と前記第2電圧制御電流源回路の前記非反転出力端子が、前記第1非反転端子と接続し、前記第1電圧制御電流源回路の前記反転入力端子と前記第2電圧制御電流源回路の前記反転出力端子が、前記第1反転端子と接続し、前記第2電圧制御電流源回路の前記反転入力端子と前記第1電圧制御電流源回路の前記非反転出力端子が、前記第2非反転端子と接続し、前記第2電圧制御電流源回路の前記非反転入力端子と前記第1電圧制御電流源回路の前記反転出力端子が、前記第2反転端子と接続して構成され、

前記第1能動回路の前記第2非反転端子と前記第2反転端子が、前記第2能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第2能動回路の前記第2非反転端子と前記第2反転端子が、前記第3能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第3能動回路の前記第2非反転端子と前記第2反転端子が、前記第4能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第4能動回路の前記第2非反転端子と前記第2反転端子が、前記第1能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第1能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2非反転端子間に、前記2つキャパシタの一方を接続し、前記第3能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2反転端子間に、前記2つキャパシタの他方を接続し、前記第1能動回路の前記第1非反転端子または前記第1反転端子、及び、前記第3能動回路の前記第1非反転端子または前記第1反転端子を外部接続用の端子対とすることを第7の特徴とする。

【0028】

上記第7の特徴のアクティブインダクタ回路は、上記第2の特徴のアクティブインダクタ回路の各能動回路の差動入力型の電圧制御電流源回路で構成された第1及び第2電圧制御電流源回路を、夫々全差動型の電圧制御電流源回路で構成し直したもので、各能動回路において、第1電圧制御電流源回路の反転出力端子を同じ能動回路の第2電圧制御電流源回路の接地されていた非反転入力端子と次段の能動回路の第1電圧制御電流源回路の接地されていた反転入力端子に夫々接続し、第2電圧制御電流源回路の反転出力端子を同じ能動回路の第1電圧制御電流源回路の接地されていた反転入力端子に接続するという各電圧制御電流源回路の反転出力端子に対する接続を追加する調整を行ったものと等価である。また、キャパシタは、上記第2の特徴のアクティブインダクタ回路では、第1能動回路の第2端子(第2非反転端子に相当)と第3能動回路の第2端子(第2非反転端子に相当)間に1つのキャパシタを設けていたが、上記第7の特徴のアクティブインダクタ回路では、第1能動回路の第2非反転端子と第2反転端子間、または、第1能動回路と第3能動回路の第2非反転端子間に、2つキャパシタの一方を接続し、第3能動回路の第2非反転端子と第2反転端子間、または、第1能動回路と第3能動回路の第2反転端子間に、2つキャパシタの他方を接続する調整を行っている。従って、基本的な回路機能及び奏する作用効果を上記第1及び第2のアクティブインダクタ回路と同じであるが、差動出力を差動入力側に帰還させる構成であるため、同じトランジスタ回路を用いて実効的に大きな相互コンダクタンスが得られるため、更なる低消費電力化、及び、全差動型の電圧制御電流源回路を使用しているため、差動回路に適用した場合の整合性がより完全となり、波形歪をより良く抑制できる。尚、上記第7の特徴のアクティブインダクタ回路は、上記第4の特徴のアクティブインダクタ回路を2組重ね合わせた回路構成とも等価となっている。

【0029】

本発明に係るアクティブインダクタ回路は、上記何れかの特徴に加えて、更に、前記第1、第2、第3及び第4能動回路、並びに、前記キャパシタが、同一基板上に、半導体集積回路として構成されていることを第8の特徴とする。

【0030】

上記第8の特徴のアクティブインダクタ回路によれば、各段の能動回路を、相互間の必要な整合性を維持して形成できるので、アクティブインダクタ回路の高性能化を図ることができ、更に、回路の小面積化及び小部品点数化が図れる。

【0031】

本発明に係る発振器は、上記何れかの特徴のアクティブインダクタ回路と、前記アクティブインダクタ回路の前記外部接続用の端子対間に接続する電気容量が固定または可変のキャパシタと、2つのMOSトランジスタを備え、前記アクティブインダクタ回路の前記外部接続用の端子対の一方に、前記2つのMOSトランジスタの一方のドレインと他方のゲートが夫々接続し、前記アクティブインダクタ回路の前記外部接続用の端子対の他方に、前記2つのMOSトランジスタの他方のドレインと一方のゲートが夫々接続し、前記2つのMOSトランジスタの各ソースが、共通の固定電位または電流源に接続して構成されていることを特徴とする。

【0032】

上記特徴の発振器によれば、使用するアクティブインダクタ回路の作用効果、つまり、低波形歪、低消費電力、小面積の発振器が実現できる。また、使用するアクティブインダクタ回路の各電圧制御電流源回路の相互コンダクタンスを調整することで、或いは、電気容量が可変のキャパシタを使用している場合には、当該キャパシタの電気容量を調整することで、発振器の発振周波数を所望の発振周波数に調整可能である。

【0033】

本発明に係るフィルタ回路は、上記何れかの特徴のアクティブインダクタ回路と、前記アクティブインダクタ回路の前記外部接続用の端子対間に並列に接続するキャパシタ及び抵抗と、非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路と、を備えてなり、前記電圧制御電流源回路の前記非反転出力端子と反転出力端子に、前記アクティブインダクタ回路の前記外部接続用の端子対の一方端子と他方端子が各別に接続して構成されていることを特徴とする。

【0034】

上記特徴のフィルタ回路によれば、使用するアクティブインダクタ回路の作用効果、つまり、低波形歪、低消費電力、小面積のフィルタ回路が実現できる。また、使用するアクティブインダクタ回路の各電圧制御電流源回路の相互コンダクタンスを調整することで、フィルタ回路のカットオフ周波数を所望のカットオフ周波数に調整可能である。

【発明を実施するための最良の形態】

【0035】

次に、本発明に係るアクティブインダクタ回路(以下、適宜「本発明回路」と称す)、及び、本発明回路を適用した発振器及びフィルタ回路について、図面を参照して説明する。

【0036】

〈第1実施形態〉

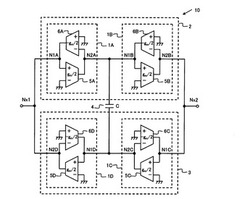

先ず、本発明回路の基本的な回路構成について説明する。基本的な回路構成の本発明回路10は、図1に示すように、4つの能動回路1(第1能動回路1A,第2能動回路1B,第3能動回路1C,第4能動回路1D)の夫々が、他の能動回路及び外部回路との接続用に、2つの端子(第1端子N1と第2端子N2)を有し、第1能動回路1Aの第2端子N2Aと第2能動回路1Bの第1端子N1Bを接続し、第2能動回路1Bの第2端子N2Bと第3能動回路1Cの第1端子N1Cを接続し、第3能動回路1Cの第2端子N2Cと第4能動回路1Dの第1端子N1Dを接続し、第4能動回路1Dの第2端子N2Dと第1能動回路1Aの第1端子N1Aを接続して、4つの能動回路1A,1B,1C,1Dを循環的に接続して構成される。

【0037】

また、電気容量Cのキャパシタ4が、第1能動回路1Aの第2端子N2Aと第3能動回路1Cの第2端子N2Cの間に接続され、第1能動回路1Aの第1端子N1Aと第3能動回路1Cの第1端子N1Cが、夫々外部接続用の端子対Nx1,Nx2となっている。

【0038】

本実施形態では、4つの能動回路1A,1B,1C,1D、及び、キャパシタ4は、同一基板上に、半導体集積回路として構成されている。

【0039】

本実施形態では、4つの能動回路1A,1B,1C,1Dの夫々は、2種類の電圧制御電流源回路5,6(第1電圧制御電流源回路5A〜5D 、第2電圧制御電流源回路6A〜6D)で構成され、夫々が、非反転入力端子IPと反転入力端子INを備え、非反転入力端子IPと反転入力端子IN間の入力電圧(VIP−VIN)が相互コンダクタンスgm/2によって出力電流Ioutに変換される差動入力型の電圧制御電流源回路で構成された相互コンダクタンスが可変なOTAである。

【0040】

各能動回路1A,1B,1C,1Dにおいて、第1電圧制御電流源回路5A〜5Dは、反転入力端子INが接地され、非反転入力端子IPが入力端子となる非反転増幅器として構成され、第2電圧制御電流源回路6A〜6Dは、非反転入力端子IPが接地され、反転入力端子INが入力端子となる反転増幅器として構成され、第1電圧制御電流源回路5A〜5Dの出力端子が、第2電圧制御電流源回路6A〜6Dの反転入力端子INに接続し、第2電圧制御電流源回路6A〜6Dの出力端子が、第1電圧制御電流源回路5A〜5Dの非反転入力端子IPに接続している。

【0041】

第1及び第2電圧制御電流源回路5,6を構成する差動入力型の電圧制御電流源回路は、例えば、図2(A)に示すようなCMOS型の差動増幅器で構成され、その小信号等価回路は、図2(B)のように表される。ここで、出力電流Ioutの向きは、出力端子から外部に向って流れる電流を正電流とし、入力電圧(VIP−VIN)の増加に対してIoutが増加する場合の相互コンダクタンスgm/2を正として、逆の場合を負とする。本実施形態では、相互コンダクタンスgm/2の極性は、入力端子として使用する入力端子IP,INによって切り替えている。

【0042】

尚、差動入力型の電圧制御電流源回路5,6は、図2(A)の回路構成に限定されるものではない。尚、図中のMOSFETのシンボルは、ソース端子からゲート端子に向けて矢印のあるのがPチャネル型MOSFET(PMOS)で、ゲート端子からソース端子に向けて矢印のあるのがNチャネル型MOSFET(NMOS)であり、図2(A)に示す差動増幅器では、PMOSによるカレントミラー回路に、非反転入力端子IPと反転入力端子INが夫々ゲート端子に接続するNMOSとバイアス電流源を備えた構成となっている。

【0043】

図1の上側の第1及び第2能動回路1A,1Bで構成されるアクティブインダクタ回路2は、回路構成上、図15に示す従来のアクティブインダクタ回路の相互コンダクタンスgmとキャパシタの電気容量C0を夫々半分にした構成となっており、数2より、インダクタンス値L1/2は、従来のアクティブインダクタ回路の2倍となる。図1の下側の第3及び第4能動回路1C,1Dで構成されるアクティブインダクタ回路3は、上側のアクティブインダクタ回路2を左右反転させた構成で、上側のアクティブインダクタ回路2と等価であるので、そのインダクタンス値L1/2は同じである。

【0044】

図1に示す本発明回路10は、上下2つのインダクタンス値L1/2のアクティブインダクタ回路2,3を並列に接続したものであるので、そのインダクタンス値Lは、インダクタンス値L1/2の半分となり、図15に示す従来のアクティブインダクタ回路と同じである。しかし、キャパシタ4は、図3に示すように、従来のアクティブインダクタ回路の電気容量C0を半分にしたものを、第1能動回路1Aの第2端子N2Aと第3能動回路1Cの第2端子N2Cの間に2個直列にして接続したものと等価であるので、電気容量Cは、従来回路の電気容量C0の4分の1(C=C0/4)となる。つまり、図3において、2つのキャパシタ4a,4bの直列回路の両端電位は、中間点のバイアス電位(例えば、接地電位)を中心に平衡動作をする。そのため、2つのキャパシタ4a,4bを1つのキャパシタ4に置き換えることで電気容量を各キャパシタ4a,4bの半分で同等の特性を実現できる。

【0045】

また、各能動回路の差動入力型の電圧制御電流源回路5,6の相互コンダクタンスは従来回路の半分であるため、図15に示す従来のアクティブインダクタ回路と比較して、個々の能動回路を構成するトランジスタサイズは半分であるが、アクティブインダクタ回路2,3が上下2段に並列に接続されているので、合計での回路規模は、従来のアクティブインダクタ回路は略同じである。つまり、4つの能動回路1A,1B,1C,1Dの全体での消費電力は、図15に示す2つの能動回路で構成された従来のアクティブインダクタ回路の消費電力と同じになっている。

【0046】

従って、図1に示す本発明回路10は、図15に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路10側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制される。

【0047】

次に、図1に示す基本回路構成の本発明回路10からの第1の変形構成例について説明する。図4に示す第1の変形構成の本発明回路11では、上側のアクティブインダクタ回路2aが、本発明回路10の第1能動回路1Aの第1電圧制御電流源回路5Aと第2能動回路1Bの第2電圧制御電流源回路6Bが合体して、非反転入力端子IPが第1能動回路1Aの第1端子N1Aと、反転入力端子NPが第2能動回路1Bの第2端子N2Bと夫々接続する1つの差動入力型の電圧制御電流源回路7Aに置換されている。また、第3能動回路1Cの第1電圧制御電流源回路5Cと第4能動回路1Dの第2電圧制御電流源回路6Dが合体して、非反転入力端子IPが第3能動回路1Cの第1端子N1Cと、反転入力端子INが第4能動回路1Dの第2端子N2Dと夫々接続する1つの差動入力型の電圧制御電流源回路7Cで構成されている。本発明回路10と本発明回路11は、消費電力を除いて回路動作上、等価である。

【0048】

図4に示す本発明回路11では、上下夫々のアクティブインダクタ回路2a,3aにおいて、差動入力型の電圧制御電流源回路5B,5D,6A,6C,7A,7Cの個数が、図1に示す基本回路構成の本発明回路10の総数8から上下で1ずつ減少して、総数6に減少しているので、上下夫々のアクティブインダクタ回路2a,3aの占める面積が、図1に示す本発明回路10の4分の3に小面積化しており、低消費電力化が図られている。

【0049】

尚、図4に示す本発明回路11の上下夫々のアクティブインダクタ回路2a,3aは、回路構成上、図15に示す従来のアクティブインダクタ回路の相互コンダクタンスgmとキャパシタの電気容量C0を夫々半分にした構成となっており、数2より、インダクタンス値L1/2は、従来のアクティブインダクタ回路の2倍となる。図4の下側のアクティブインダクタ回路3aは、上側のアクティブインダクタ回路2aを左右反転させた構成で、上側のアクティブインダクタ回路2aと等価であるので、そのインダクタンス値L1/2は同じである。

【0050】

図4に示す本発明回路11は、上下2つのインダクタンス値L1/2のアクティブインダクタ回路2a,3aを並列に接続したものであるので、そのインダクタンス値Lは、インダクタンス値L1/2の半分となり、図14に示す従来のアクティブインダクタ回路と同じである。しかし、キャパシタ4は、従来のアクティブインダクタ回路の電気容量C0を半分にしたものを、第1能動回路1Aの第2端子N2Aと第3能動回路1Cの第2端子N2Cの間に2個直列にして接続したものと等価であるので、電気容量Cは、従来回路の電気容量C0の4分の1(C=C0/4)となる。

【0051】

また、差動入力型の電圧制御電流源回路5B,5D,6A,6C,7A,7Cの個々の相互コンダクタンスは従来回路の半分であるため、図14に示す従来のアクティブインダクタ回路と比較して、個々の能動回路を構成するトランジスタサイズは半分であるが、アクティブインダクタ回路2a,3aが上下2段に並列に接続されているので、合計での回路規模は、従来のアクティブインダクタ回路は略同じである。つまり、4つの能動回路1A,1B,1C,1Dの全体での消費電力は、図14に示す2つの能動回路で構成された従来のアクティブインダクタ回路の消費電力と同じになっている。

【0052】

従って、図4に示す本発明回路11は、図14に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路11側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制される。

【0053】

次に、図1に示す基本回路構成の本発明回路10からの第2の変形構成例について説明する。図5に示す第2の変形構成の本発明回路12は、図4に示す本発明回路11をベースに更なる回路変形を施したもので、本発明回路10〜12は、消費電力を除いて回路動作上、相互に等価である。

【0054】

図5に示す第2の変形構成の本発明回路12では、本発明回路11の上側のアクティブインダクタ回路2aの第1能動回路1Aの第2電圧制御電流源回路6Aと下側のアクティブインダクタ回路3aの第4能動回路1Dの第1電圧制御電流源回路5Dが合体して、反転入力端子INが第1能動回路1Aの第2端子N2Aと、非反転入力端子INが第3能動回路1Cの第2端子N2Cと夫々接続する1つの差動入力型の電圧制御電流源回路7Dで構成され、本発明回路11の上側のアクティブインダクタ回路2aの第2能動回路1Bの第1電圧制御電流源回路5Bと下側のアクティブインダクタ回路3aの第3能動回路1Cの第2電圧制御電流源回路6Cが合体して、非反転入力端子IPが第1能動回路1Aの第2端子N2Aと、反転入力端子INが第3能動回路1Cの第2端子N2Cと夫々接続する1つの差動入力型の電圧制御電流源回路7Bで構成されている。

【0055】

図5に示す本発明回路12では、差動入力型の電圧制御電流源回路7A〜7Dの個数が、図4に示す本発明回路11の総数6から更に2減少して、総数4に減少しているので、電圧制御電流源回路7A〜7Dの占める面積が、図4に示す本発明回路11の3分の2に、図1に示す基本回路構成の本発明回路10の半分に小面積化しており、低消費電力化が図られている。

【0056】

尚、図5に示す本発明回路12は、図1に示す基本回路構成の本発明回路10及び図4に示す本発明回路11からの等価回路変換により構成されているので、そのインダクタンス値Lは、本発明回路10及び本発明回路11と同じである。また、キャパシタ4の電気容量Cも、従来回路の電気容量C0の4分の1(C=C0/4)となっている。

【0057】

また、各差動入力型の電圧制御電流源回路7A〜7Dの相互コンダクタンスは従来回路の半分であるため、図14に示す従来のアクティブインダクタ回路と比較して、電圧制御電流源回路7A〜7Dの総数は3分の4倍に増加しているが、個々の能動回路を構成するトランジスタサイズは半分であるので、合計での回路規模は、従来のアクティブインダクタ回路の3分の2となっている。つまり、4つの電圧制御電流源回路7A〜7Dの全体での消費電力は、図14に示す3つの電圧制御電流源回路で構成された従来のアクティブインダクタ回路の消費電力の3分の2に減少する。

【0058】

従って、図5に示す本発明回路12は、図14に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、差動入力型の電圧制御電流源回路7A〜7Dの回路規模も3分の2に縮小されて小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路12側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制され、更に、低消費電力化が図られている。

【0059】

〈第2実施形態〉

次に、本発明回路の第2実施形態について図6を参照して説明する。図6に示すように、第2実施形態に本発明回路13は、4つの能動回路14(第1能動回路14A、第2能動回路14B、第3能動回路14C、及び、第4能動回路14D)の夫々が、他の能動回路及び外部回路との接続用に、4つの端子(第1非反転端子N1p、第1反転端子N1nと、第2非反転端子N2p、第2反転端子N2n)を有し、第1能動回路14Aの第2非反転端子N2p及び第2反転端子N2nと、第2能動回路14Bの第1非反転端子N1p及び第1反転端子N1nを各別に接続し、第2能動回路14Bの第2非反転端子N2p及び第2反転端子N2nと、第3能動回路14Cの第1非反転端子N1p及び第1反転端子N1nを各別に接続し、第3能動回路14Cの第2非反転端子N2p及び第2反転端子N2nと、第4能動回路14Dの第1非反転端子N1p及び第1反転端子N1nを各別に接続し、第4能動回路14Dの第2非反転端子N2p及び第2反転端子N2nと第1能動回路14Aの第1非反転端子N1p及び第1反転端子N1nを各別に接続して、4つの能動回路14A,14B,14C,14Dを循環的に接続して構成される。

【0060】

また、電気容量Cの2つのキャパシタ15,16が、第1能動回路14Aの第2非反転端子N2pと第2反転端子N2n間と、第3能動回路14Cの第2非反転端子N2pと第2反転端子N2n間に夫々接続され、第1能動回路14Aの第1非反転端子N1pまたは第1反転端子N1n、及び、第3能動回路14Cの第1非反転端子N1pまたは第1反転端子N1nが、夫々外部接続用の端子対Nx1,Nx2となっている。尚、キャパシタ15,16の電気容量Cは、第1実施形態の各本発明回路10〜12のキャパシタ4の電気容量Cと同じ値であり、得られるインダクタンス値も、第1実施形態の各本発明回路10〜12と同じである。

【0061】

本実施形態では、4つの能動回路14A,14B,14C,14Dの夫々は、2種類の電圧制御電流源回路8,9(第1電圧制御電流源回路8A〜8D、第2電圧制御電流源回路9A〜9D)で構成され、夫々が、非反転入力端子IP、反転入力端子IN、非反転出力端子OP、反転出力端子ONを備え、非反転入力端子IPと反転入力端子IN間の入力電圧(VIP−VIN)が、相互コンダクタンスgm/2によって非反転出力端子OPの非反転出力電流Ioutに変換され、相互コンダクタンス−gm/2によって反転出力端子ONの反転出力電流−Ioutに変換される全差動型の電圧制御電流源回路で構成された相互コンダクタンスが可変なOTAである。

【0062】

各能動回路14A,14B,14C,14Dにおいて、第1電圧制御電流源回路8A〜8Dの非反転入力端子IPと第2電圧制御電流源回路9A〜9Dの非反転出力端子OPが、第1非反転端子N1pと接続し、第1電圧制御電流源回路8A〜8Dの反転入力端子INと第2電圧制御電流源回路9A〜9Dの反転出力端子ONが、第1反転端子N1nと接続し、第2電圧制御電流源回路9A〜9Dの反転入力端子INと第1電圧制御電流源回路8A〜8Dの非反転出力端子OPが、第2非反転端子N2pと接続し、第2電圧制御電流源回路9A〜9Dの非反転入力端子IPと第1電圧制御電流源回路8A〜8Dの反転出力ON端子が、第2反転端子N2nと接続している。

【0063】

第1及び第2電圧制御電流源回路8,9を構成する全差動型の電圧制御電流源回路は、例えば、図7(A)に示すようなCMOS型の差動増幅器で構成され、その小信号等価回路は、図7(B)のように表される。尚、全差動型の電圧制御電流源回路8,9は、図7(A)の回路構成に限定されるものではない。

【0064】

第2実施形態に本発明回路13は、図1に示す本発明回路10の各能動回路1A,1B,1C,1Dの差動入力型の電圧制御電流源回路で構成された第1及び第2電圧制御電流源回路5,6を、夫々全差動型の電圧制御電流源回路8,9で構成し直したもので、各能動回路14A,14B,14C,14Dにおいて、第1電圧制御電流源回路8の反転出力端子ONを同じ能動回路の第2電圧制御電流源回路9の非反転入力端子IPと次段の能動回路の第1電圧制御電流源回路8の反転入力端子INに夫々接続し、第2電圧制御電流源回路9の反転出力端子ONを同じ能動回路の第1電圧制御電流源回路8の反転入力端子IPに接続するという各電圧制御電流源回路8,9の反転出力端子ONに対する接続を追加している。各電圧制御電流源回路8,9の非反転出力端子OPに対する接続は、図1に示す本発明回路10の第1及び第2電圧制御電流源回路5,6の出力端子の接続と同じである。

【0065】

第2実施形態の本発明回路13は、図5に示す本発明回路12を2組重ね合わせた回路構成とも等価となっており、以上の説明より、基本的な回路機能及び奏する作用効果は、第1実施形態の本発明回路10〜12と同じであるが、差動出力を差動入力側に帰還させる構成であるため、同じトランジスタ回路を用いて実効的に大きな相互コンダクタンスが得られるため、更なる低消費電力化、及び、全差動型の電圧制御電流源回路を使用しているため、差動回路に適用した場合の整合性がより完全となり、波形歪をより良く抑制できる。

【0066】

尚、図6に示す本発明回路13は、2つのキャパシタ15,16が、第1能動回路14Aの第2非反転端子N2pと第2反転端子N2n間と、第3能動回路14Cの第2非反転端子N2pと第2反転端子N2n間に夫々接続する構成としたが、これに代えて、第1能動回路14Aと第3能動回路14Cの第2非反転端子N2p間と、第1能動回路14Aと第3能動回路14Cの第2反転端子N2n間に夫々接続する構成としても構わない。

【0067】

〈第3実施形態〉

次に、本発明回路の第3実施形態について図8を参照して説明する。第3実施形態の本発明回路17は、図8に示すように、第1実施形態の本発明回路10と同様に、4つの能動回路18(第1能動回路18A,第2能動回路18B,第3能動回路18C,第4能動回路18D)の夫々が、他の能動回路及び外部回路との接続用に、2つの端子(第1端子N1と第2端子N2)を有し、第1能動回路18Aの第2端子N2Aと第2能動回路18Bの第1端子N1Bを接続し、第2能動回路18Bの第2端子N2Bと第3能動回路18Cの第1端子N1Cを接続し、第3能動回路18Cの第2端子N2Cと第4能動回路18Dの第1端子N1Dを接続し、第4能動回路18Dの第2端子N2Dと第1能動回路18Aの第1端子N1Aを接続して、4つの能動回路18A,18B,18C,18Dを循環的に接続して構成される。

【0068】

また、電気容量Cのキャパシタ19が、第1能動回路18Aの第2端子N2Aと第3能動回路18Cの第2端子N2Cの間に接続され、第1能動回路18Aの第1端子N1Aと第3能動回路18Cの第1端子N1Cが、夫々外部接続用の端子対Nx1,Nx2となっている。キャパシタ19の電気容量Cは、第1実施形態の本発明回路10〜12のキャパシタ4の電気容量Cと同じであり、得られるインダクタンス値も第1実施形態と同じである。

【0069】

本実施形態では、4つの能動回路18A,18B,18C,18Dの夫々は、2種類のシングルエンド型の電圧制御電流源回路20,21(第1電圧制御電流源回路20A〜20D、第2電圧制御電流源回路21A〜21D)で構成されている。第1電圧制御電流源回路20A〜20Dは、単一の入力端子と単一の出力端子を備え、入力電圧が相互コンダクタンスgm/2によって出力電流Ioutに変換される非反転増幅器として機能し、第2電圧制御電流源回路21A〜21Dは、単一の入力端子と単一の出力端子を備え、入力電圧が、第1電圧制御電流源回路20A〜20Dの相互コンダクタンスgm/2とは逆極性の相互コンダクタンス−gm/2によって出力電流Ioutに変換される反転増幅器として機能する。

【0070】

各能動回路18A,18B,18C,18Dにおいて、第1電圧制御電流源回路20A〜20Dの出力端子OUT1が、第2電圧制御電流源回路21A〜21Dの入力端子IN2と接続し、第2電圧制御電流源回路21A〜21Dの出力端子OUT2が、第1電圧制御電流源回路20A〜20Dの入力端子IN1と接続している。

【0071】

第1電圧制御電流源回路20は、例えば、図9(A)に示すようなPMOSのカレントミラー回路とNMOSの入力トランジスタとバイアス電流源で構成され、第2電圧制御電流源回路21は、例えば、図9(B)に示すようなNMOSの入力トランジスタとバイアス電流源で構成される。尚、第1及び第2電圧制御電流源回路20,21は、図9(A)、(B)に示す回路構成に限定されるものではない。

【0072】

本実施形態では、第1電圧制御電流源回路20のバイアス電流源は、出力端子OUT1と接地電位間に設けられ、第2電圧制御電流源回路21のバイアス電流源は、出力端子OUT2と電源電位間に設けられ、各出力端子OUT1,OUT2への各バイアス電流の方向が逆になっている。また、上述のように、1つの能動回路の第1電圧制御電流源回路20の出力端子OUT1と次段の能動回路の第2電圧制御電流源回路21の出力端子OUT2が相互に接続する構成となっているため、第1電圧制御電流源回路20と第2電圧制御電流源回路21の各バイアス電流が相殺され、夫々のバイアス電流源または何れか一方のバイアス電流源を省略することができ、回路構成の簡素化並びに低消費電力化が図られる。

【0073】

また、図8に示す本発明回路17は、図16に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路17側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制される。

【0074】

〈第4実施形態〉

次に、上記第1乃至第3実施形態で説明した本発明回路10〜13、17を適用した本発明に係る発振器について図10を参照して説明する。

【0075】

図10に示すように、本発明に係る発振器22は、本発明回路10〜13、17の何れかと、外部接続用の端子対Nx1,Nx2間に接続する電気容量が可変のキャパシタ23と発振振幅調整用の抵抗24、及び、2つのMOSトランジスタ25,26を備え、外部接続用の端子Nx1に、MOSトランジスタ25のドレインとMOSトランジスタ26のゲートが夫々接続し、外部接続用の端子Nx2に、MOSトランジスタ26のドレインとMOSトランジスタ25のゲートが夫々接続し、2つのMOSトランジスタ25,26の各ソースが、電流調整用の電流源27に接続して構成されている。尚、図10に示す回路構成から、電流源27を省略して、2つのMOSトランジスタ25,26の各ソースを固定電位(例えば、接地電位)に直接接続しても構わない。

【0076】

図10に示す発振器22の発振周波数は、本発明回路10〜13、17の何れかのインダクタンス値、または、キャパシタ23の電気容量値で決定するため、発振周波数を可変とするには、インダクタンス値または電気容量値の何れか一方を可変とすれば良い。キャパシタ23を電気容量の調整には、バラクタダイオード等を用いることで実現できる。また、キャパシタ23を電気容量が固定のキャパシタに置き換えた場合には、本発明回路10〜13、17の何れかのインダクタンス値を、本発明回路を構成する電圧制御電流源回路の相互コンダクタンスを可変として調整すれば良い。

【0077】

〈第5実施形態〉

次に、上記第1乃至第3実施形態で説明した本発明回路10〜13、17を適用した本発明に係るフィルタ回路について図11を参照して説明する。尚、図11に示す回路例では、バンドパスフィルタについて例示する。

【0078】

図11に示すように、本発明に係るフィルタ回路28は、本発明回路10〜13、17の何れかと、外部接続用の端子対Nx1,Nx2間に接続する電気容量が可変のキャパシタ29と発振振幅調整用の抵抗30、及び、入力電圧を増幅する全差動型の電圧制御電流源回路31を備え、電圧制御電流源回路31の非反転出力端子と反転出力端子に、本発明回路10〜13、17の何れかの外部接続用の端子対Nx1,Nx2の一方端子と他方端子が各別に接続して構成されている。電圧制御電流源回路31は、一例として、第2実施形態の本発明回路13で使用される電圧制御電流源回路8,9と同様の回路構成の差動増幅器で構成できる。

【0079】

図11に示すフィルタ回路28のバンドパスフィルタの中心周波数は、本発明回路10〜13、17の何れかのインダクタンス値、または、キャパシタ29の電気容量値で決定するため、発振周波数を可変とするには、インダクタンス値または電気容量値の何れか一方を可変とすれば良い。キャパシタ29を電気容量の調整には、バラクタダイオード等を用いることで実現できる。また、キャパシタ29を電気容量が固定のキャパシタに置き換えた場合には、本発明回路10〜13、17の何れかのインダクタンス値を、本発明回路を構成する電圧制御電流源回路の相互コンダクタンスを可変として調整すれば良い。

【0080】

〈別実施形態〉

〈1〉上記各実施形態において、本発明回路、並びに、本発明回路を用いた発振器、フィルタ回路は、同一基板上に、半導体集積回路として構成される場合を想定して詳細に説明したが、必ずしも半導体集積回路として構成されなくても構わない。

【0081】

〈2〉上記第1乃至第3実施形態において、図2(A)にCMOS回路で構成された差動入力型の電圧制御電流源回路の一例を示し、図7(A)にCMOS回路で構成された全差動型の電圧制御電流源回路の一例を示し、図9(A)及び(B)に、CMOS回路及びNMOSトランジスタで構成した単一入力/単一出力型(シングルエンド型)の電圧制御電流源回路の一例を示したが、各電圧制御電流源回路は、使用するトランジスタやバイアス電流回路の構成等は、図2(A)、図7(A)及び図9に示した回路構成に限定されるものではない。例えば、使用するトランジスタはバイポーラトランジスタであってもよい。

【0082】

〈3〉上記第4及び第5実施形態では、本発明回路の応用例として、図10に示す発振器、図11に示すバンドパスフィルタ回路を例示したが、本発明回路の応用例は、これらの発振器、バンドパスフィルタ回路に限定されるものではない。

【0083】

更に、本発明回路を応用した電圧制御発振器やフィルタ回路を無線または有線通信機器に搭載することにより、波形歪や機器の出力雑音を抑えることができ、受信感度の改善に繋がる。具体的には、テレビ受像機、携帯電話、無線・有線通信機器等の性能の向上が図れる。

【産業上の利用可能性】

【0084】

本発明は、アクティブインダクタ回路に利用可能であり、例えば、半導体集積回路内に形成した電圧制御発振器やフィルタ回路に好適に用いられ、更に、これらの電圧制御発振器やフィルタ回路を搭載する通信機器に応用できる。

【図面の簡単な説明】

【0085】

【図1】本発明に係るアクティブインダクタ回路の第1実施形態における差動入力型の電圧制御電流源を用いた回路構成例を示す回路図

【図2】図1に示す本発明に係るアクティブインダクタ回路に使用される差動入力型の電圧制御電流源の回路構成例、及び、その小信号等価回路を示す回路図

【図3】図1に示す本発明に係るアクティブインダクタ回路のキャパシタを2つのキャパシタの直列回路で構成した別実施形態を示す回路図

【図4】図1に示す本発明に係るアクティブインダクタ回路の第1の変形構成例を示す回路図

【図5】図1に示す本発明に係るアクティブインダクタ回路の第2の変形構成例を示す回路図

【図6】本発明に係るアクティブインダクタ回路の第2実施形態における全差動型の電圧制御電流源を用いた回路構成例を示す回路図

【図7】図6に示す本発明に係るアクティブインダクタ回路に使用される全差動型の電圧制御電流源の回路構成例、及び、その小信号等価回路を示す回路図

【図8】本発明に係るアクティブインダクタ回路の第3実施形態におけるシングルエンド型の電圧制御電流源を用いた回路構成例を示す回路図

【図9】図8に示す本発明に係るアクティブインダクタ回路に使用される2種類のシングルエンド型の電圧制御電流源の回路構成例を示す回路図

【図10】本発明に係る発振器の一実施形態における回路構成例を示す回路図

【図11】本発明に係るフィルタ回路の一実施形態における回路構成例を示す回路図

【図12】受動素子としてのオンチップインダクタの構成例を模式的に示す図

【図13】2つの差動入力型の電圧制御電流源を用いた従来のアクティブインダクタ回路の一例を示す回路図

【図14】3つの差動入力型の電圧制御電流源を用いた2端子型の従来のアクティブインダクタ回路の一例を示す回路図

【図15】4つの差動入力型の電圧制御電流源を用いた2端子型の従来のアクティブインダクタ回路の一例を示す回路図

【図16】4つのシングルエンド型の電圧制御電流源を用いた2端子型の従来のアクティブインダクタ回路の一例を示す回路図

【符号の説明】

【0086】

1、14、18: 能動回路

1A、14A、18A: 第1能動回路

1B、14B、18B: 第2能動回路

1C、14C、18C: 第3能動回路

1D、14D、18D: 第4能動回路

2、2a: 第1及び第2能動回路で構成されるアクティブインダクタ回路

3、3a: 第3及び第4能動回路で構成されるアクティブインダクタ回路

4、4a、4b、15、16、19: キャパシタ

5、6: 差動入力型の電圧制御電流源回路

5A〜5D: 第1電圧制御電流源回路

6A〜6D: 第2電圧制御電流源回路

7A〜7D: 合体後の差動入力型の電圧制御電流源回路

8、9: 全差動型の電圧制御電流源回路

8A〜8D: 第1電圧制御電流源回路

9A〜9D: 第2電圧制御電流源回路

10〜13、17: 本発明に係るアクティブインダクタ回路

20、21: 全差動型の電圧制御電流源回路

20A〜20D: 第1電圧制御電流源回路

21A〜21D: 第2電圧制御電流源回路

22: 本発明に係る発振器

23: 可変キャパシタ

24: 抵抗

25,26: MOSトランジスタ

27: 電流源

28: 本発明に係るフィルタ回路

29: 可変キャパシタ

30: 抵抗

31: 全差動型の電圧制御電流源回路

IP: 非反転入力端子

IN: 反転入力端子

IN1、IN2: シングルエンド型の電圧制御電流源回路の入力端子

OP: 非反転出力端子

ON: 反転出力端子

OUT1、OUT2: シングルエンド型の電圧制御電流源回路の出力端子

N1: 能動回路の第1端子

N1p: 能動回路の第1非反転端子

N1n: 能動回路の第1反転端子

N2: 能動回路の第2端子

N2p: 能動回路の第2非反転端子

N2n: 能動回路の第2反転端子

N1A: 第1能動回路の第1端子

N2A: 第1能動回路の第2端子

N1B: 第2能動回路の第1端子

N2B: 第2能動回路の第2端子

N1C: 第3能動回路の第1端子

N2C: 第3能動回路の第2端子

N1D: 第4能動回路の第1端子

N2D: 第5能動回路の第2端子

Nx1、Nx2: 本発明回路の外部接続用の端子対

VDD: 電源電位

VGP: ゲートバイアス電位

【技術分野】

【0001】

本発明は、アクティブインダクタ回路に関し、更に、アクティブインダクタ回路を使用した発振器、並びに、フィルタ回路に関する。

【背景技術】

【0002】

インダクタは、無線受信器用の局部発信器やフィルタ回路等に広く用いられる。しかし、一例として図12に示すような、集積回路(IC)上に金属薄膜配線を矩形または円形の螺旋状に旋回させて形成した受動素子としてのオンチップインダクタは、チップ上に占める面積が非常に大きくなる傾向がある。このため、小面積化のため、MOSトランジスタ等の能動素子で構成されるOTA(Operational Transconductance Amplifier)等の電圧制御電流源回路を用いてインダクタの機能を模擬した回路(アクティブインダクタ回路)を実現する試みが多数なされている(例えば、下記の非特許文献1のFig.3(d)及び(e)等参照)。

【0003】

図13は、2つの電圧制御電流源41、42と1個のキャパシタ43からなるアクティブインダクタ回路の一例を示す。図13のアクティブインダクタ回路のインピーダンス値Zinは、下記の数1で与えられ、そのインダクタンス値(L=Zin/s)は、電圧制御電流源41、42の相互コンダクタンス(gm1,gm2)、または、キャパシタ43のキャパシタンス値(電気容量)C0を調整して制御可能である。

【0004】

[数1]

Zin=sC0/(|gm1|×|gm2|)=sL

【0005】

ここで、電圧制御電流源41、42は、夫々非反転入力端子と反転入力端子を備え、非反転入力端子と反転入力端子間の入力電圧が相互コンダクタンスgm1,gm2によって出力電流に変換される差動入力型の電圧制御電流源回路であり、電圧制御電流源41の入力電圧は非反転入力端子に入力され、電圧制御電流源42の入力電圧は反転入力端子に入力されているので、夫々の出力電流の方向を同じとすれば、各相互コンダクタンスgm1,gm2の極性が相互に正負逆極性となっていると看做すことができる。

【0006】

また、図13に示すアクティブインダクタ回路は、1つの端子と接地電位間のインダクタを模擬する回路であり、任意の2端子間に挿入して使用するアクティブインダクタ回路としては適合しない。そこで、図14に、任意の2端子間に挿入して使用可能なアクティブインダクタ回路の一例として、3つの差動入力型の電圧制御電流源51〜53と1個のキャパシタ54からなるアクティブインダクタ回路を示す。図14のアクティブインダクタ回路のインピーダンスZinは、下記の数2で与えられ、そのインダクタンス値(L=Zin/s)は、電圧制御電流源81〜83の相互コンダクタンス(|gm1|=|gm2|=|gm3|=gm)、または、キャパシタ54のキャパシタンス値(電気容量)C0を調整して制御可能である。

【0007】

[数2]

Zin=sC0/gm2=sL

【0008】

【非特許文献1】Randall L.Geiger and Edger Sanchez−Sinencio,“Active Filter Design Using Operational Transconductance Amplifiers:A Tutorial”,IEEE Circuits and devices Magazine,1985

【発明の開示】

【発明が解決しようとする課題】

【0009】

アクティブインダクタ回路は、受動型と比較してチップ占有面積を小さくできる反面、電圧制御電流源部に定常的に電流を流す必要があるため消費電力が増大し、回路内で発生する雑音も問題となる。

【0010】

アクティブインダクタ回路を利用した電圧制御発振器やフィルタ回路等では、その発生する雑音が課題となる。電流を流すことで雑音発生を抑制することは可能だが、低消費電力化のためには、回路の工夫で雑音を低減することが求められる。

【0011】

図14に示すアクティブインダクタ回路は、構造的には、図13に示すアクティブインダクタ回路の入力端子の極性が相互に反転した2つを組み合わせ、出力端子が同じキャパシタに接続してなる図15に示すアクティブインダクタ回路に対して、2つの電圧制御電流源55,56(図15参照)を1つの電圧制御電流源(図14の電圧制御電流源51)に置換したものである。図14に示すアクティブインダクタ回路は、他の2つの電圧制御電流源52,53の相互コンダクタンスgm2,gm3が必ずしも等価である必要はなく、回路構成上等価でない場合には、入力端子V1と出力端子V2が非対称となる場合もある。また、図15に示すアクティブインダクタ回路は、差動入力型の電圧制御電流源を用いたが、図16に示すように、これを単一入力(シングルエンド)の回路構成とすると、入力端子V1側に入力端子が接続する電圧制御電流源61と出力端子V2側に入力端子が接続する電圧制御電流源64が同じ回路構成とはならず、また、入力端子V1側に出力端子が接続する電圧制御電流源62と出力端子V2側に出力端子が接続する電圧制御電流源63が同じ回路構成とはならないので、入力端子V1と出力端子V2から回路側を見た入力インピーダンスが一致せずに非対称となる。

【0012】

斯かる非対称なアクティブインダクタ回路を用いて差動回路の電圧制御発振器やフィルタ回路を構成する場合、差動回路の差動端子対間に図14に示すアクティブインダクタ回路の入力端子V1と出力端子V2を夫々接続すると、入力端子V1と出力端子V2から回路側を見た入力インピーダンスが異なるため、差動回路による平衡動作が阻害され、差動回路の波形歪の原因となり、所期の電圧制御発振器やフィルタ回路の性能が低下する。

【0013】

また、図14に示すアクティブインダクタ回路を集積回路として構成する場合、キャパシタ84が必要となる。集積回路内に構成するキャパシタ構造、例えば、MIM(Metal−Insulator−Metal)構造やMOM(Metal−Oxide−Metal)構造のキャパシタは、集積回路チップ上においてアクティブインダクタ回路の大部分を占める。集積回路の製造コスト削減のためにはキャパシタの小面積化が必要であり、キャパシタの電気容量の削減は小面積化には効果的である。

【0014】

本発明は、上記問題点に鑑みてなされたものであり、その目的は、第1に、外部接続用の2端子の各入力インピーダンスが等しく差動回路に適用した場合の波形歪を抑制でき、第2に、従来回路に比べて使用するキャパシタの電気容量を低減して小面積化が図れ、第3に低消費電力化の図れるアクティブインダクタ回路を提供する点にある。

【課題を解決するための手段】

【0015】

上記目的を達成するための本発明に係るアクティブインダクタ回路は、夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、キャパシタとを備えてなるアクティブインダクタ回路であって、少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、前記第1、第2、第3及び第4能動回路の夫々が、入力電圧が第1相互コンダクタンスによって出力電流に変換される第1電圧制御電流源回路と、入力電圧が前記第1相互コンダクタンスと極性の異なる第2相互コンダクタンスによって出力電流に変換される第2電圧制御電流源回路と、第1端子と、第2端子を備え、前記第1電圧制御電流源回路の入力端子と前記第2電圧制御電流源回路の出力端子を前記第1端子と接続し、前記第1電圧制御電流源回路の出力端子と前記第2電圧制御電流源回路の入力端子を前記第2端子と接続して構成され、前記第1能動回路の前記第2端子と、前記第2能動回路の前記第1端子を接続し、前記第2能動回路の前記第2端子と、前記第3能動回路の前記第1端子を接続し、前記第3能動回路の前記第2端子と、前記第4能動回路の前記第1端子を接続し、前記第4能動回路の前記第2端子と、前記第1能動回路の前記第1端子を接続し、前記第1能動回路の前記第2端子と、前記キャパシタの一方端を接続し、前記第3能動回路の前記第2端子と、前記キャパシタの他方端を接続し、前記第1能動回路の前記第1端子と前記第3能動回路の前記第1端子を外部接続用の端子対とすることを第1の特徴とする。

【0016】

上記第1の特徴のアクティブインダクタ回路によれば、外部接続用の端子の一方が、第1能動回路の第1端子と第4能動回路の第2端子の接続点で、外部接続用の端子の他方が、第3能動回路の第1端子と第2能動回路の第2端子の接続点であり、また、第1能動回路と第3能動回路が同じ回路で、第2能動回路と第4能動回路が同じ回路であるので、外部接続用の端子対から見て対称な回路構成となり、外部接続用の各端子のインピーダンスが等価となり、差動回路に適用した場合に波形歪を抑制できる。また、第1能動回路の第2端子と第2能動回路の第1端子を接続した中間点にキャパシタの一方端を接続し、キャパシタの他方端を接地電位等の固定電位に接続し、第1能動回路の第1端子と第2能動回路の第2端子を外部接続用の端子対とする従来の回路構成(図15参照)と比較して、同じインダクタンス値を得るためのキャパシタの電気容量が4分の1で済むため、アクティブインダクタ回路の小面積化が図れる。

【0017】

更に、第1、第2、第3及び第4能動回路が循環的に接続する構成となっているため、後述するように、各能動回路に回路構成によっては、1つの能動回路の第2端子に接続するバイアス電流回路と、次段の能動回路の第1端子に接続するバイアス電流回路の各バイアス電流が相殺できるため、低消費電流化に適した回路構成となっている。

【0018】

本発明に係るアクティブインダクタ回路は、上記第1の特徴に加えて、更に、前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々非反転入力端子と反転入力端子を備え、前記非反転入力端子と前記反転入力端子間の入力電圧が相互コンダクタンスによって出力電流に変換される差動入力型の電圧制御電流源回路で構成され、前記第1電圧制御電流源回路が、前記反転入力端子が接地され、前記非反転入力端子が入力端子となる非反転増幅器として構成され、前記第2電圧制御電流源回路が、前記非反転入力端子が接地され、前記反転入力端子が入力端子となる反転増幅器として構成されていることを第2の特徴とする。

【0019】

本発明に係るアクティブインダクタ回路は、上記第2の特徴に加えて、更に、前記第1能動回路の前記第1電圧制御電流源回路と前記第2能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第1端子と、前記反転入力端子が前記第2能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、前記第3能動回路の前記第1電圧制御電流源回路と前記第4能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第3能動回路の前記第1端子と、前記反転入力端子が前記第4能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを第3の特徴とする。

【0020】

本発明に係るアクティブインダクタ回路は、上記第2または第3の特徴に加えて、更に、前記第1能動回路の前記第2電圧制御電流源回路と前記第4能動回路の前記第1電圧制御電流源回路が合体して、前記反転入力端子が前記第1能動回路の前記第2端子と、前記非反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、前記第2能動回路の前記第1電圧制御電流源回路と前記第3能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第2端子と、前記反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを第4の特徴とする。

【0021】

上記第2乃至第4の特徴のアクティブインダクタ回路によれば、各能動回路において、第1電圧制御電流源回路と第2電圧制御電流源回路を同じ差動入力型の電圧制御電流源回路で構成して、上記第1の特徴のアクティブインダクタ回路を実現でき、その作用効果を奏することができる。更に、第3または第4の特徴のアクティブインダクタ回路のように、一部の差動入力型の電圧制御電流源回路を合体して、各能動回路の回路構成を更に簡素化でき、その結果、低消費電流化及び小面積化を図ることができる。

【0022】

本発明に係るアクティブインダクタ回路は、上記第1の特徴に加えて、更に、前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々単一の入力端子と単一の出力端子を備え、前記第1電圧制御電流源回路が非反転増幅器として、前記第2電圧制御電流源回路が反転増幅器として構成されていることを第5の特徴とする。

【0023】

上記第5の特徴のアクティブインダクタ回路によれば、各能動回路の第1及び第2電圧制御電流源回路を、差動入力型の電圧制御電流源回路より少ないトランジスタ数で構成でき、各能動回路の低消費電流化を更に図ることができる。

【0024】

更に、第1及び第2電圧制御電流源回路の入力電圧によって制御される各出力電流の向きが、相互コンダクタンスの極性の違いによって反転するため、各出力端子に流れるバイアス電流も第1及び第2電圧制御電流源回路間で相互に逆方向となる。従って、第1、第2、第3及び第4能動回路が循環的に接続する構成となっているため、1つの能動回路の第2端子に接続する第1電圧制御電流源回路のバイアス電流回路と、次段の能動回路の第1端子に接続する第2電圧制御電流源回路のバイアス電流回路の各バイアス電流を相殺してバイアス電流回路を省略できる、低消費電流化に適した回路構成とすることができる。

【0025】

本発明に係るアクティブインダクタ回路は、上記何れかの特徴に加えて、更に、前記キャパシタが、電気容量が前記キャパシタの2倍の第1キャパシタと第2キャパシタの直列回路で構成され、前記第2キャパシタの一方端と前記第1キャパシタの他方端が相互に接続する中間接続点が、所定の固定電位に接続されていることを第6の特徴とする。

【0026】

上記第6の特徴のアクティブインダクタ回路によれば、キャパシタの電気容量は従来と同じになってしまうものの、外部接続用の各端子のインピーダンスが等価となり、差動回路に適用した場合に波形歪を抑制できる効果は、上記第1乃至第5の各特徴のアクティブインダクタ回路と同様に奏することができる。

【0027】

本発明に係るアクティブインダクタ回路は、更に、夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、2つのキャパシタとを備えてなるアクティブインダクタ回路であって、

少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、

前記第1、第2、第3及び第4能動回路の夫々が、非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路で構成される第1電圧制御電流源回路と第2電圧制御電流源回路と、第1非反転端子と、第1反転端子と、第2非反転端子と、第2反転端子を備え、前記第1電圧制御電流源回路の前記非反転入力端子と前記第2電圧制御電流源回路の前記非反転出力端子が、前記第1非反転端子と接続し、前記第1電圧制御電流源回路の前記反転入力端子と前記第2電圧制御電流源回路の前記反転出力端子が、前記第1反転端子と接続し、前記第2電圧制御電流源回路の前記反転入力端子と前記第1電圧制御電流源回路の前記非反転出力端子が、前記第2非反転端子と接続し、前記第2電圧制御電流源回路の前記非反転入力端子と前記第1電圧制御電流源回路の前記反転出力端子が、前記第2反転端子と接続して構成され、

前記第1能動回路の前記第2非反転端子と前記第2反転端子が、前記第2能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第2能動回路の前記第2非反転端子と前記第2反転端子が、前記第3能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第3能動回路の前記第2非反転端子と前記第2反転端子が、前記第4能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第4能動回路の前記第2非反転端子と前記第2反転端子が、前記第1能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、前記第1能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2非反転端子間に、前記2つキャパシタの一方を接続し、前記第3能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2反転端子間に、前記2つキャパシタの他方を接続し、前記第1能動回路の前記第1非反転端子または前記第1反転端子、及び、前記第3能動回路の前記第1非反転端子または前記第1反転端子を外部接続用の端子対とすることを第7の特徴とする。

【0028】

上記第7の特徴のアクティブインダクタ回路は、上記第2の特徴のアクティブインダクタ回路の各能動回路の差動入力型の電圧制御電流源回路で構成された第1及び第2電圧制御電流源回路を、夫々全差動型の電圧制御電流源回路で構成し直したもので、各能動回路において、第1電圧制御電流源回路の反転出力端子を同じ能動回路の第2電圧制御電流源回路の接地されていた非反転入力端子と次段の能動回路の第1電圧制御電流源回路の接地されていた反転入力端子に夫々接続し、第2電圧制御電流源回路の反転出力端子を同じ能動回路の第1電圧制御電流源回路の接地されていた反転入力端子に接続するという各電圧制御電流源回路の反転出力端子に対する接続を追加する調整を行ったものと等価である。また、キャパシタは、上記第2の特徴のアクティブインダクタ回路では、第1能動回路の第2端子(第2非反転端子に相当)と第3能動回路の第2端子(第2非反転端子に相当)間に1つのキャパシタを設けていたが、上記第7の特徴のアクティブインダクタ回路では、第1能動回路の第2非反転端子と第2反転端子間、または、第1能動回路と第3能動回路の第2非反転端子間に、2つキャパシタの一方を接続し、第3能動回路の第2非反転端子と第2反転端子間、または、第1能動回路と第3能動回路の第2反転端子間に、2つキャパシタの他方を接続する調整を行っている。従って、基本的な回路機能及び奏する作用効果を上記第1及び第2のアクティブインダクタ回路と同じであるが、差動出力を差動入力側に帰還させる構成であるため、同じトランジスタ回路を用いて実効的に大きな相互コンダクタンスが得られるため、更なる低消費電力化、及び、全差動型の電圧制御電流源回路を使用しているため、差動回路に適用した場合の整合性がより完全となり、波形歪をより良く抑制できる。尚、上記第7の特徴のアクティブインダクタ回路は、上記第4の特徴のアクティブインダクタ回路を2組重ね合わせた回路構成とも等価となっている。

【0029】

本発明に係るアクティブインダクタ回路は、上記何れかの特徴に加えて、更に、前記第1、第2、第3及び第4能動回路、並びに、前記キャパシタが、同一基板上に、半導体集積回路として構成されていることを第8の特徴とする。

【0030】

上記第8の特徴のアクティブインダクタ回路によれば、各段の能動回路を、相互間の必要な整合性を維持して形成できるので、アクティブインダクタ回路の高性能化を図ることができ、更に、回路の小面積化及び小部品点数化が図れる。

【0031】

本発明に係る発振器は、上記何れかの特徴のアクティブインダクタ回路と、前記アクティブインダクタ回路の前記外部接続用の端子対間に接続する電気容量が固定または可変のキャパシタと、2つのMOSトランジスタを備え、前記アクティブインダクタ回路の前記外部接続用の端子対の一方に、前記2つのMOSトランジスタの一方のドレインと他方のゲートが夫々接続し、前記アクティブインダクタ回路の前記外部接続用の端子対の他方に、前記2つのMOSトランジスタの他方のドレインと一方のゲートが夫々接続し、前記2つのMOSトランジスタの各ソースが、共通の固定電位または電流源に接続して構成されていることを特徴とする。

【0032】

上記特徴の発振器によれば、使用するアクティブインダクタ回路の作用効果、つまり、低波形歪、低消費電力、小面積の発振器が実現できる。また、使用するアクティブインダクタ回路の各電圧制御電流源回路の相互コンダクタンスを調整することで、或いは、電気容量が可変のキャパシタを使用している場合には、当該キャパシタの電気容量を調整することで、発振器の発振周波数を所望の発振周波数に調整可能である。

【0033】

本発明に係るフィルタ回路は、上記何れかの特徴のアクティブインダクタ回路と、前記アクティブインダクタ回路の前記外部接続用の端子対間に並列に接続するキャパシタ及び抵抗と、非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路と、を備えてなり、前記電圧制御電流源回路の前記非反転出力端子と反転出力端子に、前記アクティブインダクタ回路の前記外部接続用の端子対の一方端子と他方端子が各別に接続して構成されていることを特徴とする。

【0034】

上記特徴のフィルタ回路によれば、使用するアクティブインダクタ回路の作用効果、つまり、低波形歪、低消費電力、小面積のフィルタ回路が実現できる。また、使用するアクティブインダクタ回路の各電圧制御電流源回路の相互コンダクタンスを調整することで、フィルタ回路のカットオフ周波数を所望のカットオフ周波数に調整可能である。

【発明を実施するための最良の形態】

【0035】

次に、本発明に係るアクティブインダクタ回路(以下、適宜「本発明回路」と称す)、及び、本発明回路を適用した発振器及びフィルタ回路について、図面を参照して説明する。

【0036】

〈第1実施形態〉

先ず、本発明回路の基本的な回路構成について説明する。基本的な回路構成の本発明回路10は、図1に示すように、4つの能動回路1(第1能動回路1A,第2能動回路1B,第3能動回路1C,第4能動回路1D)の夫々が、他の能動回路及び外部回路との接続用に、2つの端子(第1端子N1と第2端子N2)を有し、第1能動回路1Aの第2端子N2Aと第2能動回路1Bの第1端子N1Bを接続し、第2能動回路1Bの第2端子N2Bと第3能動回路1Cの第1端子N1Cを接続し、第3能動回路1Cの第2端子N2Cと第4能動回路1Dの第1端子N1Dを接続し、第4能動回路1Dの第2端子N2Dと第1能動回路1Aの第1端子N1Aを接続して、4つの能動回路1A,1B,1C,1Dを循環的に接続して構成される。

【0037】

また、電気容量Cのキャパシタ4が、第1能動回路1Aの第2端子N2Aと第3能動回路1Cの第2端子N2Cの間に接続され、第1能動回路1Aの第1端子N1Aと第3能動回路1Cの第1端子N1Cが、夫々外部接続用の端子対Nx1,Nx2となっている。

【0038】

本実施形態では、4つの能動回路1A,1B,1C,1D、及び、キャパシタ4は、同一基板上に、半導体集積回路として構成されている。

【0039】

本実施形態では、4つの能動回路1A,1B,1C,1Dの夫々は、2種類の電圧制御電流源回路5,6(第1電圧制御電流源回路5A〜5D 、第2電圧制御電流源回路6A〜6D)で構成され、夫々が、非反転入力端子IPと反転入力端子INを備え、非反転入力端子IPと反転入力端子IN間の入力電圧(VIP−VIN)が相互コンダクタンスgm/2によって出力電流Ioutに変換される差動入力型の電圧制御電流源回路で構成された相互コンダクタンスが可変なOTAである。

【0040】

各能動回路1A,1B,1C,1Dにおいて、第1電圧制御電流源回路5A〜5Dは、反転入力端子INが接地され、非反転入力端子IPが入力端子となる非反転増幅器として構成され、第2電圧制御電流源回路6A〜6Dは、非反転入力端子IPが接地され、反転入力端子INが入力端子となる反転増幅器として構成され、第1電圧制御電流源回路5A〜5Dの出力端子が、第2電圧制御電流源回路6A〜6Dの反転入力端子INに接続し、第2電圧制御電流源回路6A〜6Dの出力端子が、第1電圧制御電流源回路5A〜5Dの非反転入力端子IPに接続している。

【0041】

第1及び第2電圧制御電流源回路5,6を構成する差動入力型の電圧制御電流源回路は、例えば、図2(A)に示すようなCMOS型の差動増幅器で構成され、その小信号等価回路は、図2(B)のように表される。ここで、出力電流Ioutの向きは、出力端子から外部に向って流れる電流を正電流とし、入力電圧(VIP−VIN)の増加に対してIoutが増加する場合の相互コンダクタンスgm/2を正として、逆の場合を負とする。本実施形態では、相互コンダクタンスgm/2の極性は、入力端子として使用する入力端子IP,INによって切り替えている。

【0042】

尚、差動入力型の電圧制御電流源回路5,6は、図2(A)の回路構成に限定されるものではない。尚、図中のMOSFETのシンボルは、ソース端子からゲート端子に向けて矢印のあるのがPチャネル型MOSFET(PMOS)で、ゲート端子からソース端子に向けて矢印のあるのがNチャネル型MOSFET(NMOS)であり、図2(A)に示す差動増幅器では、PMOSによるカレントミラー回路に、非反転入力端子IPと反転入力端子INが夫々ゲート端子に接続するNMOSとバイアス電流源を備えた構成となっている。

【0043】

図1の上側の第1及び第2能動回路1A,1Bで構成されるアクティブインダクタ回路2は、回路構成上、図15に示す従来のアクティブインダクタ回路の相互コンダクタンスgmとキャパシタの電気容量C0を夫々半分にした構成となっており、数2より、インダクタンス値L1/2は、従来のアクティブインダクタ回路の2倍となる。図1の下側の第3及び第4能動回路1C,1Dで構成されるアクティブインダクタ回路3は、上側のアクティブインダクタ回路2を左右反転させた構成で、上側のアクティブインダクタ回路2と等価であるので、そのインダクタンス値L1/2は同じである。

【0044】

図1に示す本発明回路10は、上下2つのインダクタンス値L1/2のアクティブインダクタ回路2,3を並列に接続したものであるので、そのインダクタンス値Lは、インダクタンス値L1/2の半分となり、図15に示す従来のアクティブインダクタ回路と同じである。しかし、キャパシタ4は、図3に示すように、従来のアクティブインダクタ回路の電気容量C0を半分にしたものを、第1能動回路1Aの第2端子N2Aと第3能動回路1Cの第2端子N2Cの間に2個直列にして接続したものと等価であるので、電気容量Cは、従来回路の電気容量C0の4分の1(C=C0/4)となる。つまり、図3において、2つのキャパシタ4a,4bの直列回路の両端電位は、中間点のバイアス電位(例えば、接地電位)を中心に平衡動作をする。そのため、2つのキャパシタ4a,4bを1つのキャパシタ4に置き換えることで電気容量を各キャパシタ4a,4bの半分で同等の特性を実現できる。

【0045】

また、各能動回路の差動入力型の電圧制御電流源回路5,6の相互コンダクタンスは従来回路の半分であるため、図15に示す従来のアクティブインダクタ回路と比較して、個々の能動回路を構成するトランジスタサイズは半分であるが、アクティブインダクタ回路2,3が上下2段に並列に接続されているので、合計での回路規模は、従来のアクティブインダクタ回路は略同じである。つまり、4つの能動回路1A,1B,1C,1Dの全体での消費電力は、図15に示す2つの能動回路で構成された従来のアクティブインダクタ回路の消費電力と同じになっている。

【0046】

従って、図1に示す本発明回路10は、図15に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路10側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制される。

【0047】

次に、図1に示す基本回路構成の本発明回路10からの第1の変形構成例について説明する。図4に示す第1の変形構成の本発明回路11では、上側のアクティブインダクタ回路2aが、本発明回路10の第1能動回路1Aの第1電圧制御電流源回路5Aと第2能動回路1Bの第2電圧制御電流源回路6Bが合体して、非反転入力端子IPが第1能動回路1Aの第1端子N1Aと、反転入力端子NPが第2能動回路1Bの第2端子N2Bと夫々接続する1つの差動入力型の電圧制御電流源回路7Aに置換されている。また、第3能動回路1Cの第1電圧制御電流源回路5Cと第4能動回路1Dの第2電圧制御電流源回路6Dが合体して、非反転入力端子IPが第3能動回路1Cの第1端子N1Cと、反転入力端子INが第4能動回路1Dの第2端子N2Dと夫々接続する1つの差動入力型の電圧制御電流源回路7Cで構成されている。本発明回路10と本発明回路11は、消費電力を除いて回路動作上、等価である。

【0048】

図4に示す本発明回路11では、上下夫々のアクティブインダクタ回路2a,3aにおいて、差動入力型の電圧制御電流源回路5B,5D,6A,6C,7A,7Cの個数が、図1に示す基本回路構成の本発明回路10の総数8から上下で1ずつ減少して、総数6に減少しているので、上下夫々のアクティブインダクタ回路2a,3aの占める面積が、図1に示す本発明回路10の4分の3に小面積化しており、低消費電力化が図られている。

【0049】

尚、図4に示す本発明回路11の上下夫々のアクティブインダクタ回路2a,3aは、回路構成上、図15に示す従来のアクティブインダクタ回路の相互コンダクタンスgmとキャパシタの電気容量C0を夫々半分にした構成となっており、数2より、インダクタンス値L1/2は、従来のアクティブインダクタ回路の2倍となる。図4の下側のアクティブインダクタ回路3aは、上側のアクティブインダクタ回路2aを左右反転させた構成で、上側のアクティブインダクタ回路2aと等価であるので、そのインダクタンス値L1/2は同じである。

【0050】

図4に示す本発明回路11は、上下2つのインダクタンス値L1/2のアクティブインダクタ回路2a,3aを並列に接続したものであるので、そのインダクタンス値Lは、インダクタンス値L1/2の半分となり、図14に示す従来のアクティブインダクタ回路と同じである。しかし、キャパシタ4は、従来のアクティブインダクタ回路の電気容量C0を半分にしたものを、第1能動回路1Aの第2端子N2Aと第3能動回路1Cの第2端子N2Cの間に2個直列にして接続したものと等価であるので、電気容量Cは、従来回路の電気容量C0の4分の1(C=C0/4)となる。

【0051】

また、差動入力型の電圧制御電流源回路5B,5D,6A,6C,7A,7Cの個々の相互コンダクタンスは従来回路の半分であるため、図14に示す従来のアクティブインダクタ回路と比較して、個々の能動回路を構成するトランジスタサイズは半分であるが、アクティブインダクタ回路2a,3aが上下2段に並列に接続されているので、合計での回路規模は、従来のアクティブインダクタ回路は略同じである。つまり、4つの能動回路1A,1B,1C,1Dの全体での消費電力は、図14に示す2つの能動回路で構成された従来のアクティブインダクタ回路の消費電力と同じになっている。

【0052】

従って、図4に示す本発明回路11は、図14に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路11側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制される。

【0053】

次に、図1に示す基本回路構成の本発明回路10からの第2の変形構成例について説明する。図5に示す第2の変形構成の本発明回路12は、図4に示す本発明回路11をベースに更なる回路変形を施したもので、本発明回路10〜12は、消費電力を除いて回路動作上、相互に等価である。

【0054】

図5に示す第2の変形構成の本発明回路12では、本発明回路11の上側のアクティブインダクタ回路2aの第1能動回路1Aの第2電圧制御電流源回路6Aと下側のアクティブインダクタ回路3aの第4能動回路1Dの第1電圧制御電流源回路5Dが合体して、反転入力端子INが第1能動回路1Aの第2端子N2Aと、非反転入力端子INが第3能動回路1Cの第2端子N2Cと夫々接続する1つの差動入力型の電圧制御電流源回路7Dで構成され、本発明回路11の上側のアクティブインダクタ回路2aの第2能動回路1Bの第1電圧制御電流源回路5Bと下側のアクティブインダクタ回路3aの第3能動回路1Cの第2電圧制御電流源回路6Cが合体して、非反転入力端子IPが第1能動回路1Aの第2端子N2Aと、反転入力端子INが第3能動回路1Cの第2端子N2Cと夫々接続する1つの差動入力型の電圧制御電流源回路7Bで構成されている。

【0055】

図5に示す本発明回路12では、差動入力型の電圧制御電流源回路7A〜7Dの個数が、図4に示す本発明回路11の総数6から更に2減少して、総数4に減少しているので、電圧制御電流源回路7A〜7Dの占める面積が、図4に示す本発明回路11の3分の2に、図1に示す基本回路構成の本発明回路10の半分に小面積化しており、低消費電力化が図られている。

【0056】

尚、図5に示す本発明回路12は、図1に示す基本回路構成の本発明回路10及び図4に示す本発明回路11からの等価回路変換により構成されているので、そのインダクタンス値Lは、本発明回路10及び本発明回路11と同じである。また、キャパシタ4の電気容量Cも、従来回路の電気容量C0の4分の1(C=C0/4)となっている。

【0057】

また、各差動入力型の電圧制御電流源回路7A〜7Dの相互コンダクタンスは従来回路の半分であるため、図14に示す従来のアクティブインダクタ回路と比較して、電圧制御電流源回路7A〜7Dの総数は3分の4倍に増加しているが、個々の能動回路を構成するトランジスタサイズは半分であるので、合計での回路規模は、従来のアクティブインダクタ回路の3分の2となっている。つまり、4つの電圧制御電流源回路7A〜7Dの全体での消費電力は、図14に示す3つの電圧制御電流源回路で構成された従来のアクティブインダクタ回路の消費電力の3分の2に減少する。

【0058】

従って、図5に示す本発明回路12は、図14に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、差動入力型の電圧制御電流源回路7A〜7Dの回路規模も3分の2に縮小されて小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路12側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制され、更に、低消費電力化が図られている。

【0059】

〈第2実施形態〉

次に、本発明回路の第2実施形態について図6を参照して説明する。図6に示すように、第2実施形態に本発明回路13は、4つの能動回路14(第1能動回路14A、第2能動回路14B、第3能動回路14C、及び、第4能動回路14D)の夫々が、他の能動回路及び外部回路との接続用に、4つの端子(第1非反転端子N1p、第1反転端子N1nと、第2非反転端子N2p、第2反転端子N2n)を有し、第1能動回路14Aの第2非反転端子N2p及び第2反転端子N2nと、第2能動回路14Bの第1非反転端子N1p及び第1反転端子N1nを各別に接続し、第2能動回路14Bの第2非反転端子N2p及び第2反転端子N2nと、第3能動回路14Cの第1非反転端子N1p及び第1反転端子N1nを各別に接続し、第3能動回路14Cの第2非反転端子N2p及び第2反転端子N2nと、第4能動回路14Dの第1非反転端子N1p及び第1反転端子N1nを各別に接続し、第4能動回路14Dの第2非反転端子N2p及び第2反転端子N2nと第1能動回路14Aの第1非反転端子N1p及び第1反転端子N1nを各別に接続して、4つの能動回路14A,14B,14C,14Dを循環的に接続して構成される。

【0060】

また、電気容量Cの2つのキャパシタ15,16が、第1能動回路14Aの第2非反転端子N2pと第2反転端子N2n間と、第3能動回路14Cの第2非反転端子N2pと第2反転端子N2n間に夫々接続され、第1能動回路14Aの第1非反転端子N1pまたは第1反転端子N1n、及び、第3能動回路14Cの第1非反転端子N1pまたは第1反転端子N1nが、夫々外部接続用の端子対Nx1,Nx2となっている。尚、キャパシタ15,16の電気容量Cは、第1実施形態の各本発明回路10〜12のキャパシタ4の電気容量Cと同じ値であり、得られるインダクタンス値も、第1実施形態の各本発明回路10〜12と同じである。

【0061】

本実施形態では、4つの能動回路14A,14B,14C,14Dの夫々は、2種類の電圧制御電流源回路8,9(第1電圧制御電流源回路8A〜8D、第2電圧制御電流源回路9A〜9D)で構成され、夫々が、非反転入力端子IP、反転入力端子IN、非反転出力端子OP、反転出力端子ONを備え、非反転入力端子IPと反転入力端子IN間の入力電圧(VIP−VIN)が、相互コンダクタンスgm/2によって非反転出力端子OPの非反転出力電流Ioutに変換され、相互コンダクタンス−gm/2によって反転出力端子ONの反転出力電流−Ioutに変換される全差動型の電圧制御電流源回路で構成された相互コンダクタンスが可変なOTAである。

【0062】

各能動回路14A,14B,14C,14Dにおいて、第1電圧制御電流源回路8A〜8Dの非反転入力端子IPと第2電圧制御電流源回路9A〜9Dの非反転出力端子OPが、第1非反転端子N1pと接続し、第1電圧制御電流源回路8A〜8Dの反転入力端子INと第2電圧制御電流源回路9A〜9Dの反転出力端子ONが、第1反転端子N1nと接続し、第2電圧制御電流源回路9A〜9Dの反転入力端子INと第1電圧制御電流源回路8A〜8Dの非反転出力端子OPが、第2非反転端子N2pと接続し、第2電圧制御電流源回路9A〜9Dの非反転入力端子IPと第1電圧制御電流源回路8A〜8Dの反転出力ON端子が、第2反転端子N2nと接続している。

【0063】

第1及び第2電圧制御電流源回路8,9を構成する全差動型の電圧制御電流源回路は、例えば、図7(A)に示すようなCMOS型の差動増幅器で構成され、その小信号等価回路は、図7(B)のように表される。尚、全差動型の電圧制御電流源回路8,9は、図7(A)の回路構成に限定されるものではない。

【0064】

第2実施形態に本発明回路13は、図1に示す本発明回路10の各能動回路1A,1B,1C,1Dの差動入力型の電圧制御電流源回路で構成された第1及び第2電圧制御電流源回路5,6を、夫々全差動型の電圧制御電流源回路8,9で構成し直したもので、各能動回路14A,14B,14C,14Dにおいて、第1電圧制御電流源回路8の反転出力端子ONを同じ能動回路の第2電圧制御電流源回路9の非反転入力端子IPと次段の能動回路の第1電圧制御電流源回路8の反転入力端子INに夫々接続し、第2電圧制御電流源回路9の反転出力端子ONを同じ能動回路の第1電圧制御電流源回路8の反転入力端子IPに接続するという各電圧制御電流源回路8,9の反転出力端子ONに対する接続を追加している。各電圧制御電流源回路8,9の非反転出力端子OPに対する接続は、図1に示す本発明回路10の第1及び第2電圧制御電流源回路5,6の出力端子の接続と同じである。

【0065】

第2実施形態の本発明回路13は、図5に示す本発明回路12を2組重ね合わせた回路構成とも等価となっており、以上の説明より、基本的な回路機能及び奏する作用効果は、第1実施形態の本発明回路10〜12と同じであるが、差動出力を差動入力側に帰還させる構成であるため、同じトランジスタ回路を用いて実効的に大きな相互コンダクタンスが得られるため、更なる低消費電力化、及び、全差動型の電圧制御電流源回路を使用しているため、差動回路に適用した場合の整合性がより完全となり、波形歪をより良く抑制できる。

【0066】

尚、図6に示す本発明回路13は、2つのキャパシタ15,16が、第1能動回路14Aの第2非反転端子N2pと第2反転端子N2n間と、第3能動回路14Cの第2非反転端子N2pと第2反転端子N2n間に夫々接続する構成としたが、これに代えて、第1能動回路14Aと第3能動回路14Cの第2非反転端子N2p間と、第1能動回路14Aと第3能動回路14Cの第2反転端子N2n間に夫々接続する構成としても構わない。

【0067】

〈第3実施形態〉

次に、本発明回路の第3実施形態について図8を参照して説明する。第3実施形態の本発明回路17は、図8に示すように、第1実施形態の本発明回路10と同様に、4つの能動回路18(第1能動回路18A,第2能動回路18B,第3能動回路18C,第4能動回路18D)の夫々が、他の能動回路及び外部回路との接続用に、2つの端子(第1端子N1と第2端子N2)を有し、第1能動回路18Aの第2端子N2Aと第2能動回路18Bの第1端子N1Bを接続し、第2能動回路18Bの第2端子N2Bと第3能動回路18Cの第1端子N1Cを接続し、第3能動回路18Cの第2端子N2Cと第4能動回路18Dの第1端子N1Dを接続し、第4能動回路18Dの第2端子N2Dと第1能動回路18Aの第1端子N1Aを接続して、4つの能動回路18A,18B,18C,18Dを循環的に接続して構成される。

【0068】

また、電気容量Cのキャパシタ19が、第1能動回路18Aの第2端子N2Aと第3能動回路18Cの第2端子N2Cの間に接続され、第1能動回路18Aの第1端子N1Aと第3能動回路18Cの第1端子N1Cが、夫々外部接続用の端子対Nx1,Nx2となっている。キャパシタ19の電気容量Cは、第1実施形態の本発明回路10〜12のキャパシタ4の電気容量Cと同じであり、得られるインダクタンス値も第1実施形態と同じである。

【0069】

本実施形態では、4つの能動回路18A,18B,18C,18Dの夫々は、2種類のシングルエンド型の電圧制御電流源回路20,21(第1電圧制御電流源回路20A〜20D、第2電圧制御電流源回路21A〜21D)で構成されている。第1電圧制御電流源回路20A〜20Dは、単一の入力端子と単一の出力端子を備え、入力電圧が相互コンダクタンスgm/2によって出力電流Ioutに変換される非反転増幅器として機能し、第2電圧制御電流源回路21A〜21Dは、単一の入力端子と単一の出力端子を備え、入力電圧が、第1電圧制御電流源回路20A〜20Dの相互コンダクタンスgm/2とは逆極性の相互コンダクタンス−gm/2によって出力電流Ioutに変換される反転増幅器として機能する。

【0070】

各能動回路18A,18B,18C,18Dにおいて、第1電圧制御電流源回路20A〜20Dの出力端子OUT1が、第2電圧制御電流源回路21A〜21Dの入力端子IN2と接続し、第2電圧制御電流源回路21A〜21Dの出力端子OUT2が、第1電圧制御電流源回路20A〜20Dの入力端子IN1と接続している。

【0071】

第1電圧制御電流源回路20は、例えば、図9(A)に示すようなPMOSのカレントミラー回路とNMOSの入力トランジスタとバイアス電流源で構成され、第2電圧制御電流源回路21は、例えば、図9(B)に示すようなNMOSの入力トランジスタとバイアス電流源で構成される。尚、第1及び第2電圧制御電流源回路20,21は、図9(A)、(B)に示す回路構成に限定されるものではない。

【0072】

本実施形態では、第1電圧制御電流源回路20のバイアス電流源は、出力端子OUT1と接地電位間に設けられ、第2電圧制御電流源回路21のバイアス電流源は、出力端子OUT2と電源電位間に設けられ、各出力端子OUT1,OUT2への各バイアス電流の方向が逆になっている。また、上述のように、1つの能動回路の第1電圧制御電流源回路20の出力端子OUT1と次段の能動回路の第2電圧制御電流源回路21の出力端子OUT2が相互に接続する構成となっているため、第1電圧制御電流源回路20と第2電圧制御電流源回路21の各バイアス電流が相殺され、夫々のバイアス電流源または何れか一方のバイアス電流源を省略することができ、回路構成の簡素化並びに低消費電力化が図られる。

【0073】

また、図8に示す本発明回路17は、図16に示す従来のアクティブインダクタ回路と比較すると、キャパシタ4の面積が4分の1に低減され、小面積化が図られているとともに、外部接続用の端子Nx1,Nx2から本発明回路17側を見た夫々の入力インピーダンスが対称な回路構成によって等しくなっており、後述する差動回路に使用した場合に、入力インピーダンスの非平衡状態に起因する波形歪が抑制される。

【0074】

〈第4実施形態〉

次に、上記第1乃至第3実施形態で説明した本発明回路10〜13、17を適用した本発明に係る発振器について図10を参照して説明する。

【0075】

図10に示すように、本発明に係る発振器22は、本発明回路10〜13、17の何れかと、外部接続用の端子対Nx1,Nx2間に接続する電気容量が可変のキャパシタ23と発振振幅調整用の抵抗24、及び、2つのMOSトランジスタ25,26を備え、外部接続用の端子Nx1に、MOSトランジスタ25のドレインとMOSトランジスタ26のゲートが夫々接続し、外部接続用の端子Nx2に、MOSトランジスタ26のドレインとMOSトランジスタ25のゲートが夫々接続し、2つのMOSトランジスタ25,26の各ソースが、電流調整用の電流源27に接続して構成されている。尚、図10に示す回路構成から、電流源27を省略して、2つのMOSトランジスタ25,26の各ソースを固定電位(例えば、接地電位)に直接接続しても構わない。

【0076】

図10に示す発振器22の発振周波数は、本発明回路10〜13、17の何れかのインダクタンス値、または、キャパシタ23の電気容量値で決定するため、発振周波数を可変とするには、インダクタンス値または電気容量値の何れか一方を可変とすれば良い。キャパシタ23を電気容量の調整には、バラクタダイオード等を用いることで実現できる。また、キャパシタ23を電気容量が固定のキャパシタに置き換えた場合には、本発明回路10〜13、17の何れかのインダクタンス値を、本発明回路を構成する電圧制御電流源回路の相互コンダクタンスを可変として調整すれば良い。

【0077】

〈第5実施形態〉

次に、上記第1乃至第3実施形態で説明した本発明回路10〜13、17を適用した本発明に係るフィルタ回路について図11を参照して説明する。尚、図11に示す回路例では、バンドパスフィルタについて例示する。

【0078】

図11に示すように、本発明に係るフィルタ回路28は、本発明回路10〜13、17の何れかと、外部接続用の端子対Nx1,Nx2間に接続する電気容量が可変のキャパシタ29と発振振幅調整用の抵抗30、及び、入力電圧を増幅する全差動型の電圧制御電流源回路31を備え、電圧制御電流源回路31の非反転出力端子と反転出力端子に、本発明回路10〜13、17の何れかの外部接続用の端子対Nx1,Nx2の一方端子と他方端子が各別に接続して構成されている。電圧制御電流源回路31は、一例として、第2実施形態の本発明回路13で使用される電圧制御電流源回路8,9と同様の回路構成の差動増幅器で構成できる。

【0079】

図11に示すフィルタ回路28のバンドパスフィルタの中心周波数は、本発明回路10〜13、17の何れかのインダクタンス値、または、キャパシタ29の電気容量値で決定するため、発振周波数を可変とするには、インダクタンス値または電気容量値の何れか一方を可変とすれば良い。キャパシタ29を電気容量の調整には、バラクタダイオード等を用いることで実現できる。また、キャパシタ29を電気容量が固定のキャパシタに置き換えた場合には、本発明回路10〜13、17の何れかのインダクタンス値を、本発明回路を構成する電圧制御電流源回路の相互コンダクタンスを可変として調整すれば良い。

【0080】

〈別実施形態〉

〈1〉上記各実施形態において、本発明回路、並びに、本発明回路を用いた発振器、フィルタ回路は、同一基板上に、半導体集積回路として構成される場合を想定して詳細に説明したが、必ずしも半導体集積回路として構成されなくても構わない。

【0081】

〈2〉上記第1乃至第3実施形態において、図2(A)にCMOS回路で構成された差動入力型の電圧制御電流源回路の一例を示し、図7(A)にCMOS回路で構成された全差動型の電圧制御電流源回路の一例を示し、図9(A)及び(B)に、CMOS回路及びNMOSトランジスタで構成した単一入力/単一出力型(シングルエンド型)の電圧制御電流源回路の一例を示したが、各電圧制御電流源回路は、使用するトランジスタやバイアス電流回路の構成等は、図2(A)、図7(A)及び図9に示した回路構成に限定されるものではない。例えば、使用するトランジスタはバイポーラトランジスタであってもよい。

【0082】

〈3〉上記第4及び第5実施形態では、本発明回路の応用例として、図10に示す発振器、図11に示すバンドパスフィルタ回路を例示したが、本発明回路の応用例は、これらの発振器、バンドパスフィルタ回路に限定されるものではない。

【0083】

更に、本発明回路を応用した電圧制御発振器やフィルタ回路を無線または有線通信機器に搭載することにより、波形歪や機器の出力雑音を抑えることができ、受信感度の改善に繋がる。具体的には、テレビ受像機、携帯電話、無線・有線通信機器等の性能の向上が図れる。

【産業上の利用可能性】

【0084】

本発明は、アクティブインダクタ回路に利用可能であり、例えば、半導体集積回路内に形成した電圧制御発振器やフィルタ回路に好適に用いられ、更に、これらの電圧制御発振器やフィルタ回路を搭載する通信機器に応用できる。

【図面の簡単な説明】

【0085】

【図1】本発明に係るアクティブインダクタ回路の第1実施形態における差動入力型の電圧制御電流源を用いた回路構成例を示す回路図

【図2】図1に示す本発明に係るアクティブインダクタ回路に使用される差動入力型の電圧制御電流源の回路構成例、及び、その小信号等価回路を示す回路図

【図3】図1に示す本発明に係るアクティブインダクタ回路のキャパシタを2つのキャパシタの直列回路で構成した別実施形態を示す回路図

【図4】図1に示す本発明に係るアクティブインダクタ回路の第1の変形構成例を示す回路図

【図5】図1に示す本発明に係るアクティブインダクタ回路の第2の変形構成例を示す回路図

【図6】本発明に係るアクティブインダクタ回路の第2実施形態における全差動型の電圧制御電流源を用いた回路構成例を示す回路図

【図7】図6に示す本発明に係るアクティブインダクタ回路に使用される全差動型の電圧制御電流源の回路構成例、及び、その小信号等価回路を示す回路図

【図8】本発明に係るアクティブインダクタ回路の第3実施形態におけるシングルエンド型の電圧制御電流源を用いた回路構成例を示す回路図

【図9】図8に示す本発明に係るアクティブインダクタ回路に使用される2種類のシングルエンド型の電圧制御電流源の回路構成例を示す回路図

【図10】本発明に係る発振器の一実施形態における回路構成例を示す回路図

【図11】本発明に係るフィルタ回路の一実施形態における回路構成例を示す回路図

【図12】受動素子としてのオンチップインダクタの構成例を模式的に示す図

【図13】2つの差動入力型の電圧制御電流源を用いた従来のアクティブインダクタ回路の一例を示す回路図

【図14】3つの差動入力型の電圧制御電流源を用いた2端子型の従来のアクティブインダクタ回路の一例を示す回路図

【図15】4つの差動入力型の電圧制御電流源を用いた2端子型の従来のアクティブインダクタ回路の一例を示す回路図

【図16】4つのシングルエンド型の電圧制御電流源を用いた2端子型の従来のアクティブインダクタ回路の一例を示す回路図

【符号の説明】

【0086】

1、14、18: 能動回路

1A、14A、18A: 第1能動回路

1B、14B、18B: 第2能動回路

1C、14C、18C: 第3能動回路

1D、14D、18D: 第4能動回路

2、2a: 第1及び第2能動回路で構成されるアクティブインダクタ回路

3、3a: 第3及び第4能動回路で構成されるアクティブインダクタ回路

4、4a、4b、15、16、19: キャパシタ

5、6: 差動入力型の電圧制御電流源回路

5A〜5D: 第1電圧制御電流源回路

6A〜6D: 第2電圧制御電流源回路

7A〜7D: 合体後の差動入力型の電圧制御電流源回路

8、9: 全差動型の電圧制御電流源回路

8A〜8D: 第1電圧制御電流源回路

9A〜9D: 第2電圧制御電流源回路

10〜13、17: 本発明に係るアクティブインダクタ回路

20、21: 全差動型の電圧制御電流源回路

20A〜20D: 第1電圧制御電流源回路

21A〜21D: 第2電圧制御電流源回路

22: 本発明に係る発振器

23: 可変キャパシタ

24: 抵抗

25,26: MOSトランジスタ

27: 電流源

28: 本発明に係るフィルタ回路

29: 可変キャパシタ

30: 抵抗

31: 全差動型の電圧制御電流源回路

IP: 非反転入力端子

IN: 反転入力端子

IN1、IN2: シングルエンド型の電圧制御電流源回路の入力端子

OP: 非反転出力端子

ON: 反転出力端子

OUT1、OUT2: シングルエンド型の電圧制御電流源回路の出力端子

N1: 能動回路の第1端子

N1p: 能動回路の第1非反転端子

N1n: 能動回路の第1反転端子

N2: 能動回路の第2端子

N2p: 能動回路の第2非反転端子

N2n: 能動回路の第2反転端子

N1A: 第1能動回路の第1端子

N2A: 第1能動回路の第2端子

N1B: 第2能動回路の第1端子

N2B: 第2能動回路の第2端子

N1C: 第3能動回路の第1端子

N2C: 第3能動回路の第2端子

N1D: 第4能動回路の第1端子

N2D: 第5能動回路の第2端子

Nx1、Nx2: 本発明回路の外部接続用の端子対

VDD: 電源電位

VGP: ゲートバイアス電位

【特許請求の範囲】

【請求項1】

夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、キャパシタとを備えてなるアクティブインダクタ回路であって、

少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、

前記第1、第2、第3及び第4能動回路の夫々が、

入力電圧が第1相互コンダクタンスによって出力電流に変換される第1電圧制御電流源回路と、入力電圧が前記第1相互コンダクタンスと極性の異なる第2相互コンダクタンスによって出力電流に変換される第2電圧制御電流源回路と、第1端子と、第2端子を備え、前記第1電圧制御電流源回路の入力端子と前記第2電圧制御電流源回路の出力端子を前記第1端子と接続し、前記第1電圧制御電流源回路の出力端子と前記第2電圧制御電流源回路の入力端子を前記第2端子と接続して構成され、

前記第1能動回路の前記第2端子と、前記第2能動回路の前記第1端子を接続し、

前記第2能動回路の前記第2端子と、前記第3能動回路の前記第1端子を接続し、

前記第3能動回路の前記第2端子と、前記第4能動回路の前記第1端子を接続し、

前記第4能動回路の前記第2端子と、前記第1能動回路の前記第1端子を接続し、

前記第1能動回路の前記第2端子と、前記キャパシタの一方端を接続し、

前記第3能動回路の前記第2端子と、前記キャパシタの他方端を接続し、

前記第1能動回路の前記第1端子と前記第3能動回路の前記第1端子を外部接続用の端子対とすることを特徴とするアクティブインダクタ回路。

【請求項2】

前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々非反転入力端子と反転入力端子を備え、前記非反転入力端子と前記反転入力端子間の入力電圧が相互コンダクタンスによって出力電流に変換される差動入力型の電圧制御電流源回路で構成され、

前記第1電圧制御電流源回路が、前記反転入力端子が接地され、前記非反転入力端子が入力端子となる非反転増幅器として構成され、

前記第2電圧制御電流源回路が、前記非反転入力端子が接地され、前記反転入力端子が入力端子となる反転増幅器として構成されていることを特徴とする請求項1に記載のアクティブインダクタ回路。

【請求項3】

前記第1能動回路の前記第1電圧制御電流源回路と前記第2能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第1端子と、前記反転入力端子が前記第2能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、

前記第3能動回路の前記第1電圧制御電流源回路と前記第4能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第3能動回路の前記第1端子と、前記反転入力端子が前記第4能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを特徴とする請求項2に記載のアクティブインダクタ回路。

【請求項4】

前記第1能動回路の前記第2電圧制御電流源回路と前記第4能動回路の前記第1電圧制御電流源回路が合体して、前記反転入力端子が前記第1能動回路の前記第2端子と、前記非反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、

前記第2能動回路の前記第1電圧制御電流源回路と前記第3能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第2端子と、前記反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを特徴とする請求項2または3に記載のアクティブインダクタ回路。

【請求項5】

前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々単一の入力端子と単一の出力端子を備え、前記第1電圧制御電流源回路が非反転増幅器として、前記第2電圧制御電流源回路が反転増幅器として構成されていることを特徴とする請求項1に記載のアクティブインダクタ回路。

【請求項6】

前記キャパシタが、電気容量が前記キャパシタの2倍の第1キャパシタと第2キャパシタの直列回路で構成され、前記第2キャパシタの一方端と前記第1キャパシタの他方端が相互に接続する中間接続点が、所定の固定電位に接続されていることを特徴とする請求項1〜5の何れか1項に記載のアクティブインダクタ回路。

【請求項7】

夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、2つのキャパシタとを備えてなるアクティブインダクタ回路であって、

少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、

前記第1、第2、第3及び第4能動回路の夫々が、

非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路で構成される第1電圧制御電流源回路と第2電圧制御電流源回路と、第1非反転端子と、第1反転端子と、第2非反転端子と、第2反転端子を備え、

前記第1電圧制御電流源回路の前記非反転入力端子と前記第2電圧制御電流源回路の前記非反転出力端子が、前記第1非反転端子と接続し、

前記第1電圧制御電流源回路の前記反転入力端子と前記第2電圧制御電流源回路の前記反転出力端子が、前記第1反転端子と接続し、

前記第2電圧制御電流源回路の前記反転入力端子と前記第1電圧制御電流源回路の前記非反転出力端子が、前記第2非反転端子と接続し、

前記第2電圧制御電流源回路の前記非反転入力端子と前記第1電圧制御電流源回路の前記反転出力端子が、前記第2反転端子と接続して構成され、

前記第1能動回路の前記第2非反転端子と前記第2反転端子が、前記第2能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第2能動回路の前記第2非反転端子と前記第2反転端子が、前記第3能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第3能動回路の前記第2非反転端子と前記第2反転端子が、前記第4能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第4能動回路の前記第2非反転端子と前記第2反転端子が、前記第1能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第1能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2非反転端子間に、前記2つキャパシタの一方を接続し、

前記第3能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2反転端子間に、前記2つキャパシタの他方を接続し、

前記第1能動回路の前記第1非反転端子または前記第1反転端子、及び、前記第3能動回路の前記第1非反転端子または前記第1反転端子を外部接続用の端子対とすることを特徴とするアクティブインダクタ回路。

【請求項8】

前記第1、第2、第3及び第4能動回路、並びに、前記キャパシタが、同一基板上に、半導体集積回路として構成されていることを特徴とする請求項1〜7の何れか1項に記載のアクティブインダクタ回路。

【請求項9】

請求項1〜8の何れか1項に記載のアクティブインダクタ回路と、前記アクティブインダクタ回路の前記外部接続用の端子対間に接続する電気容量が固定または可変のキャパシタと、2つのMOSトランジスタを備え、

前記アクティブインダクタ回路の前記外部接続用の端子対の一方に、前記2つのMOSトランジスタの一方のドレインと他方のゲートが夫々接続し、

前記アクティブインダクタ回路の前記外部接続用の端子対の他方に、前記2つのMOSトランジスタの他方のドレインと一方のゲートが夫々接続し、

前記2つのMOSトランジスタの各ソースが、共通の固定電位または電流源に接続して構成されていることを特徴とする発振器。

【請求項10】

請求項1〜8の何れか1項に記載のアクティブインダクタ回路と、

前記アクティブインダクタ回路の前記外部接続用の端子対間に並列に接続するキャパシタ及び抵抗と、

非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路と、を備えてなり、

前記電圧制御電流源回路の前記非反転出力端子と反転出力端子に、前記アクティブインダクタ回路の前記外部接続用の端子対の一方端子と他方端子が各別に接続して構成されていることを特徴とするフィルタ回路。

【請求項1】

夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、キャパシタとを備えてなるアクティブインダクタ回路であって、

少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、

前記第1、第2、第3及び第4能動回路の夫々が、

入力電圧が第1相互コンダクタンスによって出力電流に変換される第1電圧制御電流源回路と、入力電圧が前記第1相互コンダクタンスと極性の異なる第2相互コンダクタンスによって出力電流に変換される第2電圧制御電流源回路と、第1端子と、第2端子を備え、前記第1電圧制御電流源回路の入力端子と前記第2電圧制御電流源回路の出力端子を前記第1端子と接続し、前記第1電圧制御電流源回路の出力端子と前記第2電圧制御電流源回路の入力端子を前記第2端子と接続して構成され、

前記第1能動回路の前記第2端子と、前記第2能動回路の前記第1端子を接続し、

前記第2能動回路の前記第2端子と、前記第3能動回路の前記第1端子を接続し、

前記第3能動回路の前記第2端子と、前記第4能動回路の前記第1端子を接続し、

前記第4能動回路の前記第2端子と、前記第1能動回路の前記第1端子を接続し、

前記第1能動回路の前記第2端子と、前記キャパシタの一方端を接続し、

前記第3能動回路の前記第2端子と、前記キャパシタの他方端を接続し、

前記第1能動回路の前記第1端子と前記第3能動回路の前記第1端子を外部接続用の端子対とすることを特徴とするアクティブインダクタ回路。

【請求項2】

前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々非反転入力端子と反転入力端子を備え、前記非反転入力端子と前記反転入力端子間の入力電圧が相互コンダクタンスによって出力電流に変換される差動入力型の電圧制御電流源回路で構成され、

前記第1電圧制御電流源回路が、前記反転入力端子が接地され、前記非反転入力端子が入力端子となる非反転増幅器として構成され、

前記第2電圧制御電流源回路が、前記非反転入力端子が接地され、前記反転入力端子が入力端子となる反転増幅器として構成されていることを特徴とする請求項1に記載のアクティブインダクタ回路。

【請求項3】

前記第1能動回路の前記第1電圧制御電流源回路と前記第2能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第1端子と、前記反転入力端子が前記第2能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、

前記第3能動回路の前記第1電圧制御電流源回路と前記第4能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第3能動回路の前記第1端子と、前記反転入力端子が前記第4能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを特徴とする請求項2に記載のアクティブインダクタ回路。

【請求項4】

前記第1能動回路の前記第2電圧制御電流源回路と前記第4能動回路の前記第1電圧制御電流源回路が合体して、前記反転入力端子が前記第1能動回路の前記第2端子と、前記非反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成され、

前記第2能動回路の前記第1電圧制御電流源回路と前記第3能動回路の前記第2電圧制御電流源回路が合体して、前記非反転入力端子が前記第1能動回路の前記第2端子と、前記反転入力端子が前記第3能動回路の前記第2端子と夫々接続する1つの前記差動入力型の電圧制御電流源回路で構成されていることを特徴とする請求項2または3に記載のアクティブインダクタ回路。

【請求項5】

前記第1電圧制御電流源回路と前記第2電圧制御電流源回路が、夫々単一の入力端子と単一の出力端子を備え、前記第1電圧制御電流源回路が非反転増幅器として、前記第2電圧制御電流源回路が反転増幅器として構成されていることを特徴とする請求項1に記載のアクティブインダクタ回路。

【請求項6】

前記キャパシタが、電気容量が前記キャパシタの2倍の第1キャパシタと第2キャパシタの直列回路で構成され、前記第2キャパシタの一方端と前記第1キャパシタの他方端が相互に接続する中間接続点が、所定の固定電位に接続されていることを特徴とする請求項1〜5の何れか1項に記載のアクティブインダクタ回路。

【請求項7】

夫々がトランジスタを備えて構成される第1能動回路、第2能動回路、第3能動回路、及び、第4能動回路と、2つのキャパシタとを備えてなるアクティブインダクタ回路であって、

少なくとも、前記第1能動回路と前記第3能動回路が同じ回路で、前記第2能動回路と前記第4能動回路が同じ回路であって、

前記第1、第2、第3及び第4能動回路の夫々が、

非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路で構成される第1電圧制御電流源回路と第2電圧制御電流源回路と、第1非反転端子と、第1反転端子と、第2非反転端子と、第2反転端子を備え、

前記第1電圧制御電流源回路の前記非反転入力端子と前記第2電圧制御電流源回路の前記非反転出力端子が、前記第1非反転端子と接続し、

前記第1電圧制御電流源回路の前記反転入力端子と前記第2電圧制御電流源回路の前記反転出力端子が、前記第1反転端子と接続し、

前記第2電圧制御電流源回路の前記反転入力端子と前記第1電圧制御電流源回路の前記非反転出力端子が、前記第2非反転端子と接続し、

前記第2電圧制御電流源回路の前記非反転入力端子と前記第1電圧制御電流源回路の前記反転出力端子が、前記第2反転端子と接続して構成され、

前記第1能動回路の前記第2非反転端子と前記第2反転端子が、前記第2能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第2能動回路の前記第2非反転端子と前記第2反転端子が、前記第3能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第3能動回路の前記第2非反転端子と前記第2反転端子が、前記第4能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第4能動回路の前記第2非反転端子と前記第2反転端子が、前記第1能動回路の前記第1非反転端子と前記第1反転端子と夫々接続し、

前記第1能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2非反転端子間に、前記2つキャパシタの一方を接続し、

前記第3能動回路の前記第2非反転端子と前記第2反転端子間、または、前記第1能動回路と前記第3能動回路の前記第2反転端子間に、前記2つキャパシタの他方を接続し、

前記第1能動回路の前記第1非反転端子または前記第1反転端子、及び、前記第3能動回路の前記第1非反転端子または前記第1反転端子を外部接続用の端子対とすることを特徴とするアクティブインダクタ回路。

【請求項8】

前記第1、第2、第3及び第4能動回路、並びに、前記キャパシタが、同一基板上に、半導体集積回路として構成されていることを特徴とする請求項1〜7の何れか1項に記載のアクティブインダクタ回路。

【請求項9】

請求項1〜8の何れか1項に記載のアクティブインダクタ回路と、前記アクティブインダクタ回路の前記外部接続用の端子対間に接続する電気容量が固定または可変のキャパシタと、2つのMOSトランジスタを備え、

前記アクティブインダクタ回路の前記外部接続用の端子対の一方に、前記2つのMOSトランジスタの一方のドレインと他方のゲートが夫々接続し、

前記アクティブインダクタ回路の前記外部接続用の端子対の他方に、前記2つのMOSトランジスタの他方のドレインと一方のゲートが夫々接続し、

前記2つのMOSトランジスタの各ソースが、共通の固定電位または電流源に接続して構成されていることを特徴とする発振器。

【請求項10】

請求項1〜8の何れか1項に記載のアクティブインダクタ回路と、

前記アクティブインダクタ回路の前記外部接続用の端子対間に並列に接続するキャパシタ及び抵抗と、

非反転入力端子と反転入力端子間の入力電圧が正負両方の相互コンダクタンスによって非反転出力端子の非反転出力電流と反転出力端子の反転出力電流に各別に変換される全差動型の電圧制御電流源回路と、を備えてなり、

前記電圧制御電流源回路の前記非反転出力端子と反転出力端子に、前記アクティブインダクタ回路の前記外部接続用の端子対の一方端子と他方端子が各別に接続して構成されていることを特徴とするフィルタ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2008−294578(P2008−294578A)

【公開日】平成20年12月4日(2008.12.4)

【国際特許分類】

【出願番号】特願2007−135800(P2007−135800)

【出願日】平成19年5月22日(2007.5.22)

【出願人】(000005049)シャープ株式会社 (33,933)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

【公開日】平成20年12月4日(2008.12.4)

【国際特許分類】

【出願日】平成19年5月22日(2007.5.22)

【出願人】(000005049)シャープ株式会社 (33,933)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

[ Back to top ]