アクティブマトリクス型表示装置およびカメラ

【課題】電源線とデータ線との交差部の寄生容量を低減させて表示品質を向上させる。

【解決手段】表示素子とアクティブ素子とを備えた画素101が2次元に配列され、一方向に延在する複数のデータ信号線102、他方向に延在する複数の電源線103を有するアクティブマトリクス型表示装置において、データ信号線102と電源線103との交差部で電源線の線幅が交差部以外の位置の線幅よりも短くなるようにする、又はデータ信号線と電源線との交差部で電源線を分岐させ、分岐した複数の分岐部の各幅の合計が交差部以外の位置の線幅よりも短くなるようにする。

【解決手段】表示素子とアクティブ素子とを備えた画素101が2次元に配列され、一方向に延在する複数のデータ信号線102、他方向に延在する複数の電源線103を有するアクティブマトリクス型表示装置において、データ信号線102と電源線103との交差部で電源線の線幅が交差部以外の位置の線幅よりも短くなるようにする、又はデータ信号線と電源線との交差部で電源線を分岐させ、分岐した複数の分岐部の各幅の合計が交差部以外の位置の線幅よりも短くなるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はアクティブマトリクス型表示装置およびカメラに係わり、特に表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置およびカメラに関するものである。

【背景技術】

【0002】

近年、エレクトロルミネッセンス(EL)素子が画像表示素子として画像表示パネルに応用されている(以後、ELパネルと称する)。

【0003】

EL素子は電流駆動型素子であり、その発光制御方法には電圧設定方式と電流設定方式がある。

【0004】

特許文献1に記載されているような電圧設定方式の画素回路の構成を図10に示す。回路構成は次のようになっている。電圧データV(data)はデータ信号線102を介してトランジスタM1のドレインに入力され、トランジスタM3のドレインがEL素子の電流注入端子と接続されている。また制御信号が行制御線104、105を介して各々トランジスタM1のゲート、トランジスタM3のゲートに入力される。容量C1は一端が電源に接続され他端がトランジスタM2のゲートとトランジスタM1のソースに接続される。トランジスタM2のソースは電源(Vcc)と接続され、トランジスタM2のドレインはトランジスタM3のソースと各々接続される。トランジスタM3は瞬間的に過大な電流がEL素子に流れないために設けられており、点順次動作を行う場合はトランジスタM3を必要としない。また、特許文献1の図2では、信号線駆動回路から有機EL素子列に沿って配置される複数のデータ線は列方向に配列された一定の線幅を有する電源線と交差した平面構造が示されている。

【0005】

次に特許文献2に記載されているような電流設定方式の画素回路の構成を図11に示す。

【0006】

電流データI(data)はデータ信号線102を介してトランジスタM3のソースに入力され、トランジスタM3のゲートとトランジスタM4のゲートは共通の制御線105に接続される。トランジスタM4のソースはトランジスタM3のドレインとトランジスタM2のドレイン、トランジスタM1のドレインと接続される。トランジスタM4のドレインはEL素子の電流注入端子と接続されている。また、トランジスタM1のゲートは一端が電源線103に接続された容量C1の他端と、トランジスタM2のソースと接続され、トランジスタM2のゲートは制御線104、トランジスタM1のソースは電源線103に接続されている。

【0007】

なお、本発明に関連する技術としては、特許文献3に、液晶表示装置において、ゲート配線とソース配線の交差部容量を低減するために、ゲート配線とソース配線の少なくとも一方の幅を交差部以外より細くすることの記載がある(特許文献3の図2等)。また、特許文献4には、補助容量配線を走査配線に沿って延長することの記載がある(特許文献4の図1(a)等)

【特許文献1】特開2003−228299号公報

【特許文献2】米国特許第6373454号明細書

【特許文献3】特開平5−061069号公報

【特許文献4】特開2001−092378号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上記ELパネルの画素回路部において、例えば、特許文献1の図2に示されるように、データ信号を選択画素に供給する複数の信号線(データ線)と前記データ線と垂直方向に延在する電源線(Vdd)が交差する構造をとっている。その場合、データ線と電源線の交差部において交差数分の寄生容量が発生していた。その結果、選択画素回路に正確なデータ信号を安定して書き込むことが十分にできず表示品質を悪化させている課題があった。

【0009】

本発明は上記課題を鑑みてなされたものであり、ELパネルの画素回路部におけるデータ線と電源線の交差部に発生する寄生容量を低減させ、選択画素に正確な信号を安定して書き込むことを可能にして表示品質を向上させた表示装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明は前記課題を下記の手段によって解決したものである。

【0011】

本発明のアクティブマトリクス型表示装置は、表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線の線幅が前記交差部以外の位置の線幅よりも短いことを特徴とする。

【0012】

本発明のアクティブマトリクス型表示装置は、表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線は分岐しており、分岐した複数の分岐部の各幅の合計が前記交差部以外の位置の線幅よりも短いことを特徴とする。

【発明の効果】

【0013】

本発明によれば、電源線とデータ線の寄生容量の影響を抑え、電源の信頼性を確保して画素回路部へのデータの書き込み動作を安定化させることができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

[実施形態1]

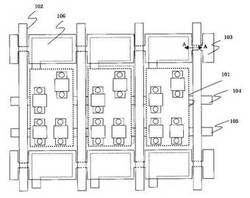

図1は本発明の第1実施形態に係わる電流設定方式の画素回路の、電流データが供給される行方向に延在した複数のデータ線と、各画素回路に電源を供給する電源線の一部の平面構造図である。画素回路の構成は図11に示した構成と同じである。図2は図1のA−A断面図である。

【0015】

図1において、101は図11に示すような電流設定方式の画素回路部であり、102はデータ線、103は電源線、104及び105は行制御線を示す。電源線103において線幅をデータ線102との交差部で交差部以外の他の位置の線幅より短くした構造となっている。この構造により電源線103とデータ線102の交差部に発生する寄生容量を低減している。こうすることで、選択画素への電流データI(data)の書き込み動作を安定化させることができる。特に、黒レベルを表示するための微小電流(黒電流)を正確に書き込むことが可能となる。線幅が短い部分は図1では電源線103の中心に配置しているが、この位置は任意に配置することができる。

【0016】

なお、電源線はデータ線に対して基本的には並行に配することも可能であるが、以下に説明するように、電源線はデータ線に対して垂直に配することが望ましい。

【0017】

電源線は、各画素を構成するEL素子の駆動電流の総和電流を流すため、低抵抗となるように他の配線と比較して線幅を太くすることが求められる。図1及び図2に示すように、その構成レイアウトにおいて、高精細な画素を形成するために、各画素回路に有する容量C1(図11に図示)は、電源線103とオーバーラップするように電極106が設けられることで、形成される。また、画素回路領域101(1画素)内にトランジスタ4つが配置される。ここで、電源線をデータ線と並行に配置すると、データ線間に容量C1と4つのトランジスタとをデータ線の並び方向に並べて配置する必要が生じ、高精細な画素形成において不利になる。そのため、電源線はデータ線に対して垂直方向に延在させるレイアウトが望ましい。

【0018】

図2において、107は基板、108、109は絶縁層である。電極106はポリシリコン領域によって形成され、配線層(電極層)の順番は上から、データ線、電源線、容量電極(一端)となっている。図1では交差部の寄生容量がより少なくなるように、電源線103と平行となるように交差部での電源線の幅を短くしているが、適宜、交差部での電源線の形状は変更してもよい。

【0019】

次に上記画素回路を2次元状に配置したELパネルの回路構成を図3に示す。R(赤)G(緑)B(青)入力映像信号10(以下、入力映像信号)がELパネルの水平画素数の3倍数設けられた列制御回路1に入力される。その後、水平制御信号11aは入力回路6に入力され水平制御信号11を出力して水平シフトレジスタ3に入力される。

【0020】

補助列制御信号13aは入力回路8を介して補助列制御信号13を出力しゲート回路4及び16に入力される。水平シフトレジスタ3の各列に対応した出力端子に出力された水平サンプリング信号群17はゲート回路16から出力される制御信号21が入力されたゲート回路15に入力され、そこで変換された水平サンプリング信号群18が列制御回路1に入力される。列制御回路1はゲート回路4から出力される制御信号19が入力されている。垂直制御信号12aは入力回路7に入力され垂直制御信号12を出力して垂直シフトレジスタ5に入力され、走査信号が行制御線104、105に入力される。

【0021】

列制御回路1からのデータ信号はデータ線102を介して各画素回路に入力される。列制御回路1の1例を図5に示す。入力映像信号(Video)はトランジスタM11のソース及びトランジスタM12のソースに入力され、トランジスタM11のゲート、トランジスタM12のゲートは各々水平サンプリング信号SPa、SPbが入力される。トランジスタM11のドレインはトランジスタM13のソースと一端がGNDに接地された容量C11とに接続される。トランジスタM13のゲートは制御信号P1に接続される。またトランジスタM12のドレインはトランジスタM14のソースと一端がGNDに接地された容量C12とに接続される。トランジスタM14のゲートは制御信号P2に接続される。トランジスタM13のドレインとトランジスタM14のドレインはトランジスタM15のゲートに接続される。トランジスタM15のソースはGNDに接地され、ドレインから電流データI(data)が出力される。

【0022】

以上、本実施形態では電流設定方式の画素回路を有する表示パネルについて説明をしたが、電圧設定方式の例えば図10のような画素回路を有する表示パネルにおいても上述したように電源線幅をデータ線との交差部において短くすることも可能である。そして、選択画素への電圧データV(data)の書き込み動作を安定化させる同様な効果を得ることができる。図4は電流設定方式の画素回路を2次元状に配置したELパネルの回路構成を示す図である。図3の回路構成と異なるのは、入力回路8、ゲート回路4、ゲート回路15、ゲート回路16が設けられておらず、水平シフトレジスタ3が列制御回路22に接続されていることである。

【0023】

ここで、列制御回路22では図6に示すように水平サンプリング信号SPがトランジスタM0のゲートに接続され、トランジスタM0のソースに入力映像信号(Video)が入力される。トランジスタM0のドレインのドレインの出力から列制御信号14の電圧データV(data)が出力される。

[実施形態2]

図7はELパネルの画素部における実施形態2の平面構造図であり、図8は図7のB−B断面図である。101は例えば図10や図11に示すような画素回路部であり、102はデータ線、103は電源線、104及び105は行制御線を示す。図8において、107は基板、108、109は絶縁層である。

【0024】

実施形態1との相違は、電源線103においてデータ線102との交差部で2本に分岐した構造である点である。電源線幅を短くすると、過電流などによって配線が切断されやすくなる場合がある。本実施形態では、電源線の幅を短くするデータ線との交差部において2本に分岐することによって電源線の信頼性を向上させた構造としている。そして、電源線とデータ線との交差部で、電源線の線幅は交差部以外の位置の線幅よりも短くなっており、実施形態1と同様な効果を得ることができる。なお、本実施形態では電源線103とデータ線102との交差部で2本に分岐した構造を示したが、3本以上に分岐した構造でもよく本実施形態と同様な効果を得ることができる。

【0025】

なお、実施形態1及び2において、図10に示した画素回路及び図11に示した画素回路は図10のトランジスタM2、図11のトランジスタM1の導電型を反対導電型にして用いても良い(図10のトランジスタM2及び図11のトランジスタM1はpMOSトランジスタとなっているが、nMOSトランジスタに変えてもよい。他のトランジスタはスイッチングトランジスタとして動作するので、基本的には導電型を問わない。)。この場合、EL素子のアノード、カソードは逆になり、アノードにVccが接続され、電源線の電圧はVccではなく、GNDとなる。

【0026】

なお交差部の分岐は図7の構成に限定されず、分岐した複数の分岐部の各幅(L1、L2)の合計(L1+L2)が交差部以外の位置の線幅(L)よりも短くなるようになっていればよく((L1+L2)<L)(図7の構成もこの関係を満たしている)、図12に示したように、電源線103の両端に分岐させることも可能である。

[実施形態3]

上述した実施形態1及び実施形態2において電子機器に用いた例について説明する。

【0027】

図10はデジタルスチルカメラの一例のブロック図である。図中、29はシステム全体、23は被写体を撮像する撮影部、24は映像信号処理回路、25は表示パネル、26はメモリ、27はCPU、28は操作部を示す。撮像部23で撮影した映像または、メモリ26に記録された映像を、映像信号処理回路24で信号処理し、表示パネル25で見ることができる。CPU27では、操作部28からの入力によって、撮影部23、メモリ26、映像信号処理回路24などを制御して、状況に適した撮影、記録、再生、表示を行う。

【0028】

表示パネル25として上述した実施形態におけるELパネルを用いた場合、電源線とデータ線の寄生容量を抑制し、画素部へのデータ書き込み動作を安定させることによって高品質な表示パネルを提供できる。また、表示パネルはこの他にもデジタルビデオカメラ、PDA、携帯電話等の各種電子機器の表示部、テレビ等の表示装置として利用できる。

【0029】

なお、本発明は上記実施形態に限定されるものではなく、電源線はデータ線と同様に寄生容量を発生する他の配線においてでもよい。また、上記実施形態で示したEL表示装置だけでなく液晶表示装置などのアクティブマトリクス型表示装置にも適用可能である。液晶表示装置において、液晶と並列に接続される補助容量は画素選択スイッチが非選択時に液晶を駆動する電圧を十分に保持できる容量を形成するため、電源線は他の配線よりも線幅を太くして液晶を安定に駆動できる容量を形成することが求められる。そのため、液晶表示装置においても、電源線をデータ線との交差部で、電源線の線幅を交差部以外の位置の線幅よりも短くする、又は電源線を分岐し、分岐した複数の分岐部の各幅の合計を交差部以外の位置の線幅よりも短くする。

【産業上の利用可能性】

【0030】

本発明はEL表示装置や液晶表示装置等のアクティブ表示装置を用いたデジタルスチルカメラ、デジタルビデオカメラ、PDA、携帯電話、テレビ等に用いることができる。

【図面の簡単な説明】

【0031】

【図1】本発明の実施形態1の画素回路部の平面構造図である。

【図2】図1のA−A断面を示す断面図である。

【図3】電流設定方式によるELパネルの回路構成図である。

【図4】電圧設定方式によるELパネルの回路構成図である。

【図5】電流設定方式によるELパネルの列制御回路構成図である。

【図6】電圧設定方式によるELパネルの列制御回路構成図である。

【図7】本発明の実施形態2の画素回路部の平面構造図である。

【図8】図7のB−B断面を示す断面図である。

【図9】実施形態を利用した表示装置のブロック図である。

【図10】電圧設定方式によるELパネルの画素回路の構成図である。

【図11】電流設定方式によるELパネルの画素回路の構成図である。

【図12】交差部の変形例を示す平面図である。

【符号の説明】

【0032】

1 列制御回路

2 画素回路

3 列シフトレジスタ

4 ゲート回路

5 行シフトレジスタ

6、7,8 入力回路

9 画像表示部

10 映像信号線

11 水平走査制御信号

12 垂直走査制御信号

13 副制御信号

15 水平サンプリング信号ゲート回路

16 ゲート回路

17 水平サンプリング信号

18 水平サンプリング信号

19 制御信号

21 制御信号

22 列制御回路

23 撮影部

24 映像信号処理回路

25 表示パネル

26 メモリ

27 CPU

28 操作部

29 システム

101 画素回路

102 データ線

103 電源線

104、105 行制御線

C1 容量

V(data) 電圧データ信号

I(data) 電流データ信号

M0、M1〜M4、M11〜M15 トランジスタ

【技術分野】

【0001】

本発明はアクティブマトリクス型表示装置およびカメラに係わり、特に表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置およびカメラに関するものである。

【背景技術】

【0002】

近年、エレクトロルミネッセンス(EL)素子が画像表示素子として画像表示パネルに応用されている(以後、ELパネルと称する)。

【0003】

EL素子は電流駆動型素子であり、その発光制御方法には電圧設定方式と電流設定方式がある。

【0004】

特許文献1に記載されているような電圧設定方式の画素回路の構成を図10に示す。回路構成は次のようになっている。電圧データV(data)はデータ信号線102を介してトランジスタM1のドレインに入力され、トランジスタM3のドレインがEL素子の電流注入端子と接続されている。また制御信号が行制御線104、105を介して各々トランジスタM1のゲート、トランジスタM3のゲートに入力される。容量C1は一端が電源に接続され他端がトランジスタM2のゲートとトランジスタM1のソースに接続される。トランジスタM2のソースは電源(Vcc)と接続され、トランジスタM2のドレインはトランジスタM3のソースと各々接続される。トランジスタM3は瞬間的に過大な電流がEL素子に流れないために設けられており、点順次動作を行う場合はトランジスタM3を必要としない。また、特許文献1の図2では、信号線駆動回路から有機EL素子列に沿って配置される複数のデータ線は列方向に配列された一定の線幅を有する電源線と交差した平面構造が示されている。

【0005】

次に特許文献2に記載されているような電流設定方式の画素回路の構成を図11に示す。

【0006】

電流データI(data)はデータ信号線102を介してトランジスタM3のソースに入力され、トランジスタM3のゲートとトランジスタM4のゲートは共通の制御線105に接続される。トランジスタM4のソースはトランジスタM3のドレインとトランジスタM2のドレイン、トランジスタM1のドレインと接続される。トランジスタM4のドレインはEL素子の電流注入端子と接続されている。また、トランジスタM1のゲートは一端が電源線103に接続された容量C1の他端と、トランジスタM2のソースと接続され、トランジスタM2のゲートは制御線104、トランジスタM1のソースは電源線103に接続されている。

【0007】

なお、本発明に関連する技術としては、特許文献3に、液晶表示装置において、ゲート配線とソース配線の交差部容量を低減するために、ゲート配線とソース配線の少なくとも一方の幅を交差部以外より細くすることの記載がある(特許文献3の図2等)。また、特許文献4には、補助容量配線を走査配線に沿って延長することの記載がある(特許文献4の図1(a)等)

【特許文献1】特開2003−228299号公報

【特許文献2】米国特許第6373454号明細書

【特許文献3】特開平5−061069号公報

【特許文献4】特開2001−092378号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上記ELパネルの画素回路部において、例えば、特許文献1の図2に示されるように、データ信号を選択画素に供給する複数の信号線(データ線)と前記データ線と垂直方向に延在する電源線(Vdd)が交差する構造をとっている。その場合、データ線と電源線の交差部において交差数分の寄生容量が発生していた。その結果、選択画素回路に正確なデータ信号を安定して書き込むことが十分にできず表示品質を悪化させている課題があった。

【0009】

本発明は上記課題を鑑みてなされたものであり、ELパネルの画素回路部におけるデータ線と電源線の交差部に発生する寄生容量を低減させ、選択画素に正確な信号を安定して書き込むことを可能にして表示品質を向上させた表示装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明は前記課題を下記の手段によって解決したものである。

【0011】

本発明のアクティブマトリクス型表示装置は、表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線の線幅が前記交差部以外の位置の線幅よりも短いことを特徴とする。

【0012】

本発明のアクティブマトリクス型表示装置は、表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線は分岐しており、分岐した複数の分岐部の各幅の合計が前記交差部以外の位置の線幅よりも短いことを特徴とする。

【発明の効果】

【0013】

本発明によれば、電源線とデータ線の寄生容量の影響を抑え、電源の信頼性を確保して画素回路部へのデータの書き込み動作を安定化させることができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

[実施形態1]

図1は本発明の第1実施形態に係わる電流設定方式の画素回路の、電流データが供給される行方向に延在した複数のデータ線と、各画素回路に電源を供給する電源線の一部の平面構造図である。画素回路の構成は図11に示した構成と同じである。図2は図1のA−A断面図である。

【0015】

図1において、101は図11に示すような電流設定方式の画素回路部であり、102はデータ線、103は電源線、104及び105は行制御線を示す。電源線103において線幅をデータ線102との交差部で交差部以外の他の位置の線幅より短くした構造となっている。この構造により電源線103とデータ線102の交差部に発生する寄生容量を低減している。こうすることで、選択画素への電流データI(data)の書き込み動作を安定化させることができる。特に、黒レベルを表示するための微小電流(黒電流)を正確に書き込むことが可能となる。線幅が短い部分は図1では電源線103の中心に配置しているが、この位置は任意に配置することができる。

【0016】

なお、電源線はデータ線に対して基本的には並行に配することも可能であるが、以下に説明するように、電源線はデータ線に対して垂直に配することが望ましい。

【0017】

電源線は、各画素を構成するEL素子の駆動電流の総和電流を流すため、低抵抗となるように他の配線と比較して線幅を太くすることが求められる。図1及び図2に示すように、その構成レイアウトにおいて、高精細な画素を形成するために、各画素回路に有する容量C1(図11に図示)は、電源線103とオーバーラップするように電極106が設けられることで、形成される。また、画素回路領域101(1画素)内にトランジスタ4つが配置される。ここで、電源線をデータ線と並行に配置すると、データ線間に容量C1と4つのトランジスタとをデータ線の並び方向に並べて配置する必要が生じ、高精細な画素形成において不利になる。そのため、電源線はデータ線に対して垂直方向に延在させるレイアウトが望ましい。

【0018】

図2において、107は基板、108、109は絶縁層である。電極106はポリシリコン領域によって形成され、配線層(電極層)の順番は上から、データ線、電源線、容量電極(一端)となっている。図1では交差部の寄生容量がより少なくなるように、電源線103と平行となるように交差部での電源線の幅を短くしているが、適宜、交差部での電源線の形状は変更してもよい。

【0019】

次に上記画素回路を2次元状に配置したELパネルの回路構成を図3に示す。R(赤)G(緑)B(青)入力映像信号10(以下、入力映像信号)がELパネルの水平画素数の3倍数設けられた列制御回路1に入力される。その後、水平制御信号11aは入力回路6に入力され水平制御信号11を出力して水平シフトレジスタ3に入力される。

【0020】

補助列制御信号13aは入力回路8を介して補助列制御信号13を出力しゲート回路4及び16に入力される。水平シフトレジスタ3の各列に対応した出力端子に出力された水平サンプリング信号群17はゲート回路16から出力される制御信号21が入力されたゲート回路15に入力され、そこで変換された水平サンプリング信号群18が列制御回路1に入力される。列制御回路1はゲート回路4から出力される制御信号19が入力されている。垂直制御信号12aは入力回路7に入力され垂直制御信号12を出力して垂直シフトレジスタ5に入力され、走査信号が行制御線104、105に入力される。

【0021】

列制御回路1からのデータ信号はデータ線102を介して各画素回路に入力される。列制御回路1の1例を図5に示す。入力映像信号(Video)はトランジスタM11のソース及びトランジスタM12のソースに入力され、トランジスタM11のゲート、トランジスタM12のゲートは各々水平サンプリング信号SPa、SPbが入力される。トランジスタM11のドレインはトランジスタM13のソースと一端がGNDに接地された容量C11とに接続される。トランジスタM13のゲートは制御信号P1に接続される。またトランジスタM12のドレインはトランジスタM14のソースと一端がGNDに接地された容量C12とに接続される。トランジスタM14のゲートは制御信号P2に接続される。トランジスタM13のドレインとトランジスタM14のドレインはトランジスタM15のゲートに接続される。トランジスタM15のソースはGNDに接地され、ドレインから電流データI(data)が出力される。

【0022】

以上、本実施形態では電流設定方式の画素回路を有する表示パネルについて説明をしたが、電圧設定方式の例えば図10のような画素回路を有する表示パネルにおいても上述したように電源線幅をデータ線との交差部において短くすることも可能である。そして、選択画素への電圧データV(data)の書き込み動作を安定化させる同様な効果を得ることができる。図4は電流設定方式の画素回路を2次元状に配置したELパネルの回路構成を示す図である。図3の回路構成と異なるのは、入力回路8、ゲート回路4、ゲート回路15、ゲート回路16が設けられておらず、水平シフトレジスタ3が列制御回路22に接続されていることである。

【0023】

ここで、列制御回路22では図6に示すように水平サンプリング信号SPがトランジスタM0のゲートに接続され、トランジスタM0のソースに入力映像信号(Video)が入力される。トランジスタM0のドレインのドレインの出力から列制御信号14の電圧データV(data)が出力される。

[実施形態2]

図7はELパネルの画素部における実施形態2の平面構造図であり、図8は図7のB−B断面図である。101は例えば図10や図11に示すような画素回路部であり、102はデータ線、103は電源線、104及び105は行制御線を示す。図8において、107は基板、108、109は絶縁層である。

【0024】

実施形態1との相違は、電源線103においてデータ線102との交差部で2本に分岐した構造である点である。電源線幅を短くすると、過電流などによって配線が切断されやすくなる場合がある。本実施形態では、電源線の幅を短くするデータ線との交差部において2本に分岐することによって電源線の信頼性を向上させた構造としている。そして、電源線とデータ線との交差部で、電源線の線幅は交差部以外の位置の線幅よりも短くなっており、実施形態1と同様な効果を得ることができる。なお、本実施形態では電源線103とデータ線102との交差部で2本に分岐した構造を示したが、3本以上に分岐した構造でもよく本実施形態と同様な効果を得ることができる。

【0025】

なお、実施形態1及び2において、図10に示した画素回路及び図11に示した画素回路は図10のトランジスタM2、図11のトランジスタM1の導電型を反対導電型にして用いても良い(図10のトランジスタM2及び図11のトランジスタM1はpMOSトランジスタとなっているが、nMOSトランジスタに変えてもよい。他のトランジスタはスイッチングトランジスタとして動作するので、基本的には導電型を問わない。)。この場合、EL素子のアノード、カソードは逆になり、アノードにVccが接続され、電源線の電圧はVccではなく、GNDとなる。

【0026】

なお交差部の分岐は図7の構成に限定されず、分岐した複数の分岐部の各幅(L1、L2)の合計(L1+L2)が交差部以外の位置の線幅(L)よりも短くなるようになっていればよく((L1+L2)<L)(図7の構成もこの関係を満たしている)、図12に示したように、電源線103の両端に分岐させることも可能である。

[実施形態3]

上述した実施形態1及び実施形態2において電子機器に用いた例について説明する。

【0027】

図10はデジタルスチルカメラの一例のブロック図である。図中、29はシステム全体、23は被写体を撮像する撮影部、24は映像信号処理回路、25は表示パネル、26はメモリ、27はCPU、28は操作部を示す。撮像部23で撮影した映像または、メモリ26に記録された映像を、映像信号処理回路24で信号処理し、表示パネル25で見ることができる。CPU27では、操作部28からの入力によって、撮影部23、メモリ26、映像信号処理回路24などを制御して、状況に適した撮影、記録、再生、表示を行う。

【0028】

表示パネル25として上述した実施形態におけるELパネルを用いた場合、電源線とデータ線の寄生容量を抑制し、画素部へのデータ書き込み動作を安定させることによって高品質な表示パネルを提供できる。また、表示パネルはこの他にもデジタルビデオカメラ、PDA、携帯電話等の各種電子機器の表示部、テレビ等の表示装置として利用できる。

【0029】

なお、本発明は上記実施形態に限定されるものではなく、電源線はデータ線と同様に寄生容量を発生する他の配線においてでもよい。また、上記実施形態で示したEL表示装置だけでなく液晶表示装置などのアクティブマトリクス型表示装置にも適用可能である。液晶表示装置において、液晶と並列に接続される補助容量は画素選択スイッチが非選択時に液晶を駆動する電圧を十分に保持できる容量を形成するため、電源線は他の配線よりも線幅を太くして液晶を安定に駆動できる容量を形成することが求められる。そのため、液晶表示装置においても、電源線をデータ線との交差部で、電源線の線幅を交差部以外の位置の線幅よりも短くする、又は電源線を分岐し、分岐した複数の分岐部の各幅の合計を交差部以外の位置の線幅よりも短くする。

【産業上の利用可能性】

【0030】

本発明はEL表示装置や液晶表示装置等のアクティブ表示装置を用いたデジタルスチルカメラ、デジタルビデオカメラ、PDA、携帯電話、テレビ等に用いることができる。

【図面の簡単な説明】

【0031】

【図1】本発明の実施形態1の画素回路部の平面構造図である。

【図2】図1のA−A断面を示す断面図である。

【図3】電流設定方式によるELパネルの回路構成図である。

【図4】電圧設定方式によるELパネルの回路構成図である。

【図5】電流設定方式によるELパネルの列制御回路構成図である。

【図6】電圧設定方式によるELパネルの列制御回路構成図である。

【図7】本発明の実施形態2の画素回路部の平面構造図である。

【図8】図7のB−B断面を示す断面図である。

【図9】実施形態を利用した表示装置のブロック図である。

【図10】電圧設定方式によるELパネルの画素回路の構成図である。

【図11】電流設定方式によるELパネルの画素回路の構成図である。

【図12】交差部の変形例を示す平面図である。

【符号の説明】

【0032】

1 列制御回路

2 画素回路

3 列シフトレジスタ

4 ゲート回路

5 行シフトレジスタ

6、7,8 入力回路

9 画像表示部

10 映像信号線

11 水平走査制御信号

12 垂直走査制御信号

13 副制御信号

15 水平サンプリング信号ゲート回路

16 ゲート回路

17 水平サンプリング信号

18 水平サンプリング信号

19 制御信号

21 制御信号

22 列制御回路

23 撮影部

24 映像信号処理回路

25 表示パネル

26 メモリ

27 CPU

28 操作部

29 システム

101 画素回路

102 データ線

103 電源線

104、105 行制御線

C1 容量

V(data) 電圧データ信号

I(data) 電流データ信号

M0、M1〜M4、M11〜M15 トランジスタ

【特許請求の範囲】

【請求項1】

表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線の線幅が前記交差部以外の位置の線幅よりも短いことを特徴とするアクティブマトリクス型表示装置。

【請求項2】

前記交差部で前記電源線が分岐していることを特徴とする請求項1に記載のアクティブマトリクス型表示装置。

【請求項3】

表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線は分岐しており、分岐した複数の分岐部の各幅の合計が前記交差部以外の位置の線幅よりも短いことを特徴とするアクティブマトリクス型表示装置。

【請求項4】

前記データ信号線に加えられるデータ信号は電流信号であることを特徴とする請求項1から3のいずれか1項に記載のアクティブマトリクス型表示装置。

【請求項5】

前記データ信号線に加えられるデータ信号は電圧信号であることを特徴とする請求項1から3のいずれか1項に記載のアクティブマトリクス型表示装置。

【請求項6】

前記表示素子はエレクトロルミネッセンス(EL)素子であることを特徴とする請求項1から5のいずれか1項に記載のアクティブマトリクス型表示装置。

【請求項7】

請求項1から6のいずれか1項に記載のアクティブマトリクス型表示装置と、被写体を撮像する撮像部と、前記撮像部で撮像された信号を処理する映像信号処理部と、を備え、前記映像信号処理部で信号処理された映像信号を前記アクティブマトリクス型表示装置で表示してなるカメラ。

【請求項1】

表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線の線幅が前記交差部以外の位置の線幅よりも短いことを特徴とするアクティブマトリクス型表示装置。

【請求項2】

前記交差部で前記電源線が分岐していることを特徴とする請求項1に記載のアクティブマトリクス型表示装置。

【請求項3】

表示素子とアクティブ素子とを備えた画素が2次元に配列され、一方向に延在する複数のデータ信号線、他方向に延在する複数の電源線を有するアクティブマトリクス型表示装置において、

前記データ信号線と前記電源線との交差部で前記電源線は分岐しており、分岐した複数の分岐部の各幅の合計が前記交差部以外の位置の線幅よりも短いことを特徴とするアクティブマトリクス型表示装置。

【請求項4】

前記データ信号線に加えられるデータ信号は電流信号であることを特徴とする請求項1から3のいずれか1項に記載のアクティブマトリクス型表示装置。

【請求項5】

前記データ信号線に加えられるデータ信号は電圧信号であることを特徴とする請求項1から3のいずれか1項に記載のアクティブマトリクス型表示装置。

【請求項6】

前記表示素子はエレクトロルミネッセンス(EL)素子であることを特徴とする請求項1から5のいずれか1項に記載のアクティブマトリクス型表示装置。

【請求項7】

請求項1から6のいずれか1項に記載のアクティブマトリクス型表示装置と、被写体を撮像する撮像部と、前記撮像部で撮像された信号を処理する映像信号処理部と、を備え、前記映像信号処理部で信号処理された映像信号を前記アクティブマトリクス型表示装置で表示してなるカメラ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2007−121629(P2007−121629A)

【公開日】平成19年5月17日(2007.5.17)

【国際特許分類】

【出願番号】特願2005−312786(P2005−312786)

【出願日】平成17年10月27日(2005.10.27)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成19年5月17日(2007.5.17)

【国際特許分類】

【出願日】平成17年10月27日(2005.10.27)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]