アクティブマトリクス基板、ディスプレイパネル、表示装置およびトランジスタ素子

【課題】アクティブマトリクス基板の開口率を向上させる。

【解決手段】複数のトランジスタ素子を備えたアクティブマトリクス基板101Aであって、可視光を透過させることが可能な基板10と、基板上に形成され、亜鉛錫酸化物から構成される導電体材料よりなり、可視光を透過させることが可能な配線(LG、LD、LP、L1、L2等)であってトランジスタ素子における電極として機能している、配線と、基板の垂直方向からみて配線の少なくとも一部と重なり、配線よりもキャリア濃度が低く、亜鉛錫酸化物から構成される半導体材料よりなり、かつ可視光を透過させることが可能な半導体層44と、配線および半導体層の少なくとも一部を覆い、可視光を透過させることが可能な絶縁膜(40、50)と、を備えることを特徴とするアクティブマトリクス基板。

【解決手段】複数のトランジスタ素子を備えたアクティブマトリクス基板101Aであって、可視光を透過させることが可能な基板10と、基板上に形成され、亜鉛錫酸化物から構成される導電体材料よりなり、可視光を透過させることが可能な配線(LG、LD、LP、L1、L2等)であってトランジスタ素子における電極として機能している、配線と、基板の垂直方向からみて配線の少なくとも一部と重なり、配線よりもキャリア濃度が低く、亜鉛錫酸化物から構成される半導体材料よりなり、かつ可視光を透過させることが可能な半導体層44と、配線および半導体層の少なくとも一部を覆い、可視光を透過させることが可能な絶縁膜(40、50)と、を備えることを特徴とするアクティブマトリクス基板。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法に関し、トランジスタ素子、特に薄膜トランジスタ(Thin Film Transistor:TFT)素子を含むアクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法に関する。

【背景技術】

【0002】

近年、低消費電力化、低駆動電圧化および省スペース化などが可能であることから、液晶ディスプレイ(Liquid Crystal Display:LCD)装置や有機EL(Electro Luminescence)ディスプレイ装置などに代表されるフラットパネルディスプレイ(Flat Panel Display:FPD)装置の開発が盛んに行なわれている。

【0003】

FPD装置において、例えば液晶ディスプレイ装置や有機ELディスプレイ装置などの駆動方式には、大きく分けてスタティック駆動方式とダイナミック駆動方式とがあるが、その中でもダイナミック駆動方式に分類されるアクティブマトリクス駆動方式は、画素間のクロストークを低減し、より明瞭な映像再生が可能なことから注目されている。

【0004】

アクティブマトリクス駆動方式を実現する際には、一般的に、1つ以上のスイッチング素子や容量素子などを画素ごとに備えた、いわゆるアレイ基板と称される回路基板が用いられる。本説明では、これをアクティブマトリクス基板と呼ぶ。

【0005】

例えば液晶ディスプレイ装置の場合、アクティブマトリクス基板と対向基板との間に液晶素子が設けられる。ここで、装置内の光源より発した光は、アクティブマトリクス基板と液晶素子と対向基板とを介して視認されることになるが、この際、液晶素子に適宜電圧を与えてこれの分子配列を制御することで映像としての色調、階調などが表現される。

【0006】

また、例えば有機ELディスプレイ装置の場合、アクティブマトリクス基板の主面における一方の面側に画素ごとの有機発光ダイオードが設けられる。ここで、有機発光ダイオードからの光は、アクティブマトリクス基板を介して(裏面発光型/ボトムエミッションタイプ)、または、アクティブマトリクス基板を介さずに(上面発光型/トップエミッションタイプ)視認されることになるが、この際、有機発光ダイオードに流れる電流量を制御することで映像としての色調、階調が表現される。

【0007】

以上のような構成から、アクティブマトリクス基板は、液晶ディスプレイ装置や有機ELディスプレイ装置などのFPDにおけるパネル部分の厚さを決定する重要なファクタとなっている。そこで、このアクティブマトリクス基板におけるスイッチング素子には、パネル部分の薄型化を意識して、通常、トランジスタ素子、特にTFT素子などの薄膜素子が用いられる。

【0008】

このような中、電極材料や半導体材料や絶縁膜材料などの開発により、透明なTFTを形成することが可能となってきた(例えば以下に示す非特許文献1参照)。

【先行技術文献】

【非特許文献】

【0009】

【非特許文献1】神谷利夫ら、“アモルファス酸化物半導体の設計と高性能フレキシブル薄膜トランジスタの室温形成”、第19回先端技術大賞応募論文、[online]、[平成20年4月9日検索]、インターネット<URL:http://www.fbi-award.jp/sentan/jusyou/2005/toko canon.pdf>

【発明の概要】

【発明が解決しようとする課題】

【0010】

ここで、液晶ディスプレイ装置や有機ELディスプレイ装置などの性能を決める一つのファクタとして、アクティブマトリクス基板の開口率が存在する。この開口率は、より高密度化や高いコントラスト比および輝度などを実現するための重要なファクタであり、開口率が大きければ大きいほど、高集積化や高コントラスト比や高輝度などを実現することが可能となる。

【0011】

しかしながら、上記従来の技術では、アクティブマトリクス基板におけるトランジスタ素子の透明化は可能なものの、配線部分の透明化を実現するには至っていない。配線には、液晶ディスプレイ装置や有機ELディスプレイ装置などの消費電力や駆動電圧の低減を実現するためにある程度大きな断面積が要求される。このため、配線部分が透明でないことは、従来のアクティブマトリクス基板における開口率の向上に制限を与えていた。

【0012】

そこで本発明は、上記の問題に鑑みてなされたものであり、開口率を向上することができるアクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

かかる目的を達成するために、本発明によるアクティブマトリクス基板は、複数のトランジスタ素子を備えたアクティブマトリクス基板であって、可視光を透過させることが可能な基板と、前記基板上に形成され、可視光を透過させることが可能な配線と、前記基板の垂直方向からみて前記配線の少なくとも一部と重なり、かつ可視光を透過させることが可能な半導体層と、前記配線および半導体層の少なくとも一部を覆い、可視光を透過させることが可能な絶縁膜と、を備えることを特徴としている。

【0014】

上記した本発明によるアクティブマトリクス基板は、前記配線が、主配線と、該主配線から分岐されてなり、該主配線と前記トランジスタ素子とを接続する副配線と、を含むことを特徴としている。

【0015】

上記した本発明によるアクティブマトリクス基板は、前記配線が、無機酸化物導電体材料よりなることを特徴としている。

【0016】

上記した本発明によるアクティブマトリクス基板は、前記半導体層が、無機酸化物半導体材料よりなることを特徴としている。

【0017】

上記した本発明によるアクティブマトリクス基板は、前記配線が、亜鉛錫酸化物またはインジウム含有酸化物から構成される導電体材料よりなり、前記半導体層が、前記配線よりもキャリア濃度が低く、亜鉛錫酸化物またはインジウム含有酸化物から構成される半導体材料よりなることを特徴としている。

【0018】

上記した本発明によるアクティブマトリクス基板は、前記配線の一部が、前記トランジスタ素子における電極として機能していることを特徴としている。

【0019】

上記した本発明によるアクティブマトリクス基板は、前記配線の一部が、前記トランジスタ素子におけるゲート電極、ソース電極およびドレイン電極として機能し、前記絶縁膜の一部が、前記トランジスタ素子におけるゲート絶縁膜として機能することを特徴としている。

【0020】

上記した本発明によるアクティブマトリクス基板は、第1および第2トランジスタならびにキャパシタを備え、前記配線が、1つ以上の走査線の少なくとも一部と、1つ以上のデータ線の少なくとも一部と、1つ以上の駆動線の少なくとも一部と、を構成し、前記第1トランジスタが、制御端子が前記走査線に接続され、入力端子が前記データ線に接続されており、前記第2トランジスタが、制御端子が前記第1トランジスタの出力端子に接続され、入力端子が前記駆動線に接続されており、前記キャパシタが、一方の電極が前記駆動線に接続され、他方の端子が前記第2トランジスタの制御端子に接続されていることを特徴としている。

【0021】

上記した本発明によるアクティブマトリクス基板は、第1トランジスタおよびキャパシタを備え、前記配線が、1つ以上の走査線の少なくとも一部と、1つ以上のデータ線の少なくとも一部と、1つ以上の容量線の少なくとも一部と、を構成し、前記第1トランジスタが、制御端子が前記走査線に接続され、入力端子が前記データ線に接続されており、前記キャパシタが、一方の端子が前記トランジスタの出力端子に接続されていることを特徴としている。

【0022】

また、本発明によるディスプレイパネルは、上記した本発明によるアクティブマトリクス基板と、前記アクティブマトリクス基板上に形成され、可視光を透過することが可能な第1電極と、前記第1電極上に形成された有機膜と、前記有機膜上に形成された第2電極と、を備えたことを特徴としている。

【0023】

上記した本発明によるディスプレイパネルは、前記第2電極が、可視光を透過することが可能であることを特徴としている。

【0024】

上記した本発明によるディスプレイパネルは、前記第2電極に電気的に接続された補助電極を備えたことを特徴としている。

【0025】

上記した本発明によるディスプレイパネルは、前記補助電極が、可視光を透過することが可能であることを特徴としている。

【0026】

上記した本発明によるディスプレイパネルは、前記有機膜に対して上層および/または下層に形成されたフィルタ膜を備えたことを特徴としている。

【0027】

また、本発明によるディスプレイパネルは、上記した本発明によるアクティブマトリクス基板と、可視光を透過することが可能な対向基板と、液晶層と、該液晶層をサンドウィッチする2つの配向膜と、前記液晶層と前記2つの配向膜とよりなる積層体をサンドウィッチする画素電極および共通電極と、を含む液晶素子と、を備え、前記画素電極および共通電極が、可視光を透過することが可能であり、前記画素電極が、前記アクティブマトリクス基板における前記配線と電気的に接続され、前記液晶素子が、前記アクティブマトリクス基板と前記対向基板とでサンドウィッチされていることを特徴としている。

【0028】

上記した本発明によるディスプレイパネルは、前記アクティブマトリクス基板と前記液晶素子と前記対向基板とよりなる積層体をサンドウィッチする2つの偏光板を備えたことを特徴としている。

【0029】

上記した本発明によるディスプレイパネルは、前記共通電極上に形成された遮光膜と、少なくとも前記共通電極上に形成され、所定帯域の波長を透過させるフィルタ膜と、を備えたことを特徴としている。

【0030】

また、本発明による表示装置は、上記した本発明によるディスプレイパネルを備えたことを特徴としている。

【0031】

また、本発明によるアクティブマトリクス基板の製造方法は、可視光を透過させることが可能な基板上に、トランジスタ素子を構成する電極を一部に含み、可視光を透過させることが可能な第1配線を形成する第1配線形成工程と、前記基板上に、前記第1配線の少なくとも一部を覆い、前記トランジスタ素子を構成する絶縁膜を一部に含み、可視光を透過させることが可能な第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜上に、前記トランジスタ素子を構成する電極を一部に含み、可視光を透過させることが可能な第2配線を形成する第2配線形成工程と、前記第1絶縁膜上に、前記第2配線の少なくとも一部を覆い、可視光を透過させることが可能な半導体層を形成する半導体層形成工程と、前記第1絶縁膜上に、前記半導体層および前記第2配線の少なくとも一部を覆い、可視光を透過させることが可能な第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴としている。

【0032】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記第2配線を、無機酸化物導電体材料を用いて形成することを特徴としている。

【0033】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記半導体層を、無機酸化物半導体材料を用いて形成することを特徴としている。

【0034】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記第2配線を、亜鉛錫酸化物またはインジウム含有酸化物から構成される導電体材料を用いて形成し、前記半導体層を、前記配線よりもキャリア濃度を低くすることのできる亜鉛錫酸化物またはインジウム含有酸化物から構成される半導体材料を用いて形成することを特徴としている。

【0035】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記半導体層形成工程においては、前記第1絶縁膜上に前記第2配線を覆う半導体膜を形成し、該半導体膜を前記第2配線が露出しないようにエッチングすることで、前記半導体層を形成することを特徴としている。

【0036】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記第1配線形成工程、前記第1絶縁膜形成工程、前記第2配線形成工程、前記半導体層形成工程および前記第2絶縁膜形成工程のうち少なくとも一つの工程においては、印刷法またはインクジェットプリンティング法を用いて、前記第1配線、前記第1絶縁膜、前記第2配線、前記半導体層または前記第2絶縁膜を形成することを特徴としている。

【発明の効果】

【0037】

本発明によれば、アクティブマトリクス基板における配線が可視光に対して透明であるため、アクティブマトリクス基板の開口率を大幅に向上させることが可能となる。また、同様の理由により、本発明によれば、開口率が大幅に向上されたアクティブマトリクス基板を製造することが可能となる。さらに、このような本発明によるアクティブマトリクス基板を用いることで、開口率が大幅に向上されたディスプレイパネルおよび表示装置を実現することが可能となる。

【図面の簡単な説明】

【0038】

【図1】本発明の実施の形態1による有機ELディスプレイ装置の概略構成を示すブロック図である。

【図2】本発明の実施の形態1による各画素の概略回路構成を示す模式図である。

【図3】本発明の実施の形態1による各画素におけるアクティブマトリクス基板のレイアウト構造を説明するための概略平面図である。

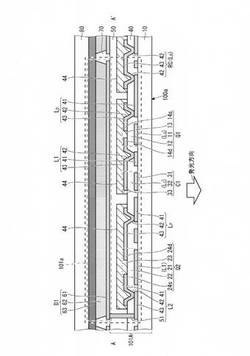

【図4】本発明の実施の形態1による各画素における層構造を説明するための概略断面図である。

【図5−1】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その1)。

【図5−2】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その2)。

【図5−3】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その3)。

【図5−4】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その4)。

【図5−5】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その5)。

【図5−6】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その6)。

【図5−7】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その7)。

【図5−8】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その8)。

【図5−9】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その9)。

【図5−10】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その10)。

【図6】本発明の実施の形態2による各画素における層構造を説明するための概略断面図である。

【図7】本発明の実施の形態3による液晶ディスプレイ装置の概略構成を示すブロック図である。

【図8】本発明の実施の形態3による各画素の概略回路構成を示す模式図である。

【図9】本発明の実施の形態3による各画素におけるアクティブマトリクス基板のレイアウト構造を説明するための概略平面図である。

【図10】本発明の実施の形態3による各画素における層構造を説明するための概略断面図である。

【図11−1】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その1)。

【図11−2】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その2)。

【図12−1】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その3)。

【図12−2】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その4)。

【図12−3】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その5)。

【図12−4】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その6)。

【図12−5】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その7)。

【図12−6】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その8)。

【図13】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その9)。

【発明を実施するための形態】

【0039】

以下、本発明を実施するための最良の形態を図面を参照して詳細に説明する。なお、以下の実施の形態により本発明が限定されるものではない。また、以下の説明において、各図は本発明の内容を理解でき得る程度に形状、大きさ、および位置関係を概略的に示してあるに過ぎず、従って、本発明は各図で例示された形状、大きさ、および位置関係のみに限定されるものではない。さらに、各図では、構成の明瞭化のため、断面におけるハッチングの一部が省略されている。さらにまた、後述において例示する数値は、本発明の好適な例に過ぎず、従って、本発明は例示された数値に限定されるものではない。

【0040】

<実施の形態1>

まず、本発明の実施の形態1による表示装置として、有機ELディスプレイ装置100を例に挙げて説明する。図1は、有機ELディスプレイ装置100の概略構成を示すブロック図である。なお、本実施の形態では、発光素子(例えば図4における有機発光ダイオードD1参照)からの光を素子基板(例えば図4におけるアクティブマトリクス基板101A参照)を介してこれの下面(例えば図4における下面100a参照)から外部へ出力することが可能な、いわゆる裏面発光型(ボトムエミッションタイプ)の有機ELディスプレイ装置100を例に挙げる。

【0041】

(全体構成)

図1に示すように、有機ELディスプレイ装置100は、2次元マトリクス状に配列された画素(PX)101aを含むディスプレイパネル101と、これに接続された走査駆動部103、データ駆動部104、容量線駆動部105および駆動信号生成部106と、各部を制御するための信号制御部102と、を備える。なお、ディスプレイパネル101は、赤(R)、緑(G)および青(B)の三原色それぞれについての画素101aを備える。

【0042】

ここで、ディスプレイパネル101は、走査駆動部103に接続され、それぞれ走査信号を伝達する走査線LG1〜LGn(以下、任意の走査線をLGとする)と、データ駆動部104に接続され、それぞれデータ信号を伝達するデータ線LD1〜LDm(以下、任意のデータ線をLDとする)と、容量線駆動部105に接続され、それぞれ容量線駆動信号を伝達する容量線LC1〜LCm(以下、任意の容量線をLCとする)と、駆動信号生成部106に接続され、それぞれ駆動信号を伝達する駆動線LP1〜LPm(以下、任意の駆動線をLPとする)と、を含む。

【0043】

各走査線LG1〜LGnは図面中略行方向に延伸しており、各データ線LD1〜LDmは図面中略列方向に延伸している。したがって、走査線LG1〜LGnとデータ線LD1〜LDmとは、2次元マトリクス状に交差する。各画素101aは、この2次元マトリクスにおける交差部分にそれぞれ配置され、対応する走査線LGおよびデータ線LDに接続される。また、各容量線LC1〜LCmはデータ線LD1〜LDmと略平行に延伸しており、各交差部分に配置された画素101aに接続される。同様に、各駆動線LP1〜LPmは、データ線LD1〜LDmと略平行に延伸しており、各交差部分に配置された画素101aに接続される。本実施の形態では、走査線LGとデータ線LDと容量線LCと駆動線LPとのそれぞれにおいて、相互に交差するように行列方向に延伸する配線部分を主配線とし、この主配線から分岐して各画素101aにおけるスイッチングトランジスタQ1や駆動トランジスタQ2やキャパシタC1(例えば図2参照)等の素子に接続する配線部分を副配線とする。また、各素子間を接続する配線(L1,L2等)を副配線とする。

【0044】

信号制御部102は、外部から入力されたビデオ信号R,G,Bおよびその表示を制御するための入力制御信号(データイネーブル信号DE,水平同期信号Hsync,垂直同期信号Vsync,メインクロックMCLKなど)に基づき、映像再生を制御するための走査制御信号CONT1、データ制御信号CONT2、容量線制御信号CONT3、発光制御信号CONT4およびビデオデータ信号DAT等を生成する。

【0045】

生成された走査制御信号CONT1は、走査駆動部103に入力される。走査制御信号CONT1は、後述するゲートオン電圧Vonの出力開始を指示する垂直同期開始信号やゲートオン電圧Vonの出力タイミングを制御するゲートクロック信号やゲートオン電圧Vonの出力期間を制御する出力イネーブル信号などを含む。また、走査駆動部103には、各画素101aに含まれるスイッチングトランジスタQ1(図2参照)をオン・オフさせるためのゲートオン電圧Vonおよびゲートオフ電圧Voffも入力される。走査駆動部103は、走査制御信号CONT1に従ってゲートオン電圧Vonおよびゲートオフ電圧Voffから走査信号を生成し、これを走査線LGに入力する。

【0046】

また、データ制御信号CONT2およびビデオデータ信号DATは、データ駆動部104に入力される。データ制御信号CONT2は、ビデオデータ信号DATの入力開始を指示する水平同期開始信号やデータ線LDにデータ信号を入力するためのロード信号などを含む。データ駆動部104は、データ制御信号CONT2に従って、受信したビデオデータ信号DATをラッチさせた後、適宜、ビデオデータ信号DATに対応したデータ信号を生成して、これをデータ線LDに入力する。

【0047】

また、容量線制御信号CONT3は、容量線駆動部105に入力される。容量線制御信号CONT3は、容量線LC駆動用の容量線駆動信号を生成するための信号である。容量線駆動部105は、容量線制御信号CONT3に従って容量線LCを駆動するための容量線駆動信号を生成し、これを容量線LCに入力する。

【0048】

また、発光制御信号CONT4は、駆動信号生成部106に入力される。発光制御信号CONT4は、有機発光ダイオードD1(図2参照)駆動用の駆動信号を生成するための信号である。駆動信号生成部106は、発光制御信号CONT4に従って有機発光ダイオードD1を発光/非発光させるための駆動信号を生成し、これを駆動線LPに入力する。

【0049】

なお、駆動信号は、後述する有機発光ダイオードD1のアノードに入力される。また、有機発光ダイオードD1のカソードには共通電圧Vcomが入力される(図2参照)。そこで、本実施の形態では、有機発光ダイオードD1を発光させる期間の駆動信号の電圧レベルを共通電圧Vcomの電圧レベルよりも高くし、それ以外の期間における駆動信号の電圧レベルを共通電圧Vcomと同じかそれよりも低くすることで、有機発光ダイオードD1の発光/非発光を制御する。ここで、共通電圧Vcomは、例えば接地電位とすることができる。また、駆動線LPの代りに電源線を用いてもよい。この場合、駆動信号生成部106は省略され、電源線に電源電圧が印加される。

【0050】

(画素構成)

次に、図2を用いて各画素101aの概略構成およびその動作を説明する。なお、以下の説明は、R,G,Bのうち何れの画素101aについても同様である。

【0051】

図2は、画素101aの概略回路構成を示す模式図である。図2に示すように、画素101aは、スイッチングトランジスタQ1と、駆動トランジスタQ2と、キャパシタC1と、有機発光ダイオードD1と、を含む。

【0052】

スイッチングトランジスタQ1は例えばn型のTFTであり、そのソースSは例えばノードN4においてデータ線LDの主配線から分岐する副配線に接続され、ドレインDはノードN1を含む配線L1を介して駆動トランジスタQ2のゲートGに接続される。また、スイッチングトランジスタQ1のゲートGは、例えばノードN3において走査線LGの主配線から分岐する副配線に接続される。したがって、スイッチングトランジスタQ1は、走査信号の電圧レベルVg(走査制御電圧)に従ってデータ線LDおよびノードN1間を導通/遮断する。

【0053】

配線L1には、例えばノードN1において分岐する配線部分(これも配線L1に含む)を介してキャパシタC1の一方の端子が接続される。キャパシタC1の他方の端子は、例えばノードN5において容量線LCの主配線から分岐する副配線に接続される。容量線LCには、上述した容量線駆動部105から容量線駆動信号が与えられる。この容量線駆動信号の電圧レベルVc(容量線駆動電圧)は、例えば接地電位とすることができる。言い換えれば、容量線LCは、接地線とすることができる。この場合、容量線駆動部105を省略することができる。

【0054】

ここで、走査線LGに入力された走査信号の電圧レベルVg(走査制御電圧)がハイレベルになると、スイッチングトランジスタQ1がオン状態となり、当該スイッチングトランジスタQ1を介して駆動トランジスタQ2のゲートGにデータ信号の電圧レベルVd(データ駆動電圧)に応じた電荷が注入される。この結果、駆動トランジスタQ2がオン状態となり、ノードN3および有機発光ダイオードD1間が導通する。

【0055】

ここで、キャパシタC1は、走査線LGの電圧レベルVgがローレベルとなってスイッチングトランジスタQ1が完全にオフ状態となった後から次に電圧レベルVgがハイレベルになってスイッチングトランジスタQ1がオン状態となると共に次のデータ信号が入力されるまでの間、駆動トランジスタQ2におけるゲートGの電位を維持する働きをする。すなわち、キャパシタC1は、所定の期間、データ線LDに入力されたデータを保持する。

【0056】

駆動トランジスタQ2は例えばn型のTFTであり、そのドレインDは例えばノードN6において駆動線LPの主配線から分岐する副配線に接続され、ソースSはノードN2を介して有機発光ダイオードD1のアノードに接続される。なお、有機発光ダイオードD1のカソードには、共通電圧Vcom(例えば接地電位GND)が印加される。したがって、駆動トランジスタQ2がオン状態となり、アノードに電源電圧VDDが印加されると、有機発光ダイオードD1に電流Iが流れるため、有機発光ダイオードD1が電流Iの電流量に応じた輝度で発光する。一方、駆動トランジスタQ2がオフ状態の際には有機発光ダイオードD1には電流が流れないため、発光は生じない。

【0057】

次に、図3および図4を用いて、各画素101aのレイアウト構造および層構造を詳細に説明する。図3は、画素101aにおけるアクティブマトリクス基板101A(例えば図4参照)のレイアウト構造を説明するための概略平面図である。また、図4は、画素101aの層構造を説明するための概略断面図である。なお、図3では、説明の簡略化のため、透明基板10、層間絶縁膜40および50などの構成(例えば図4参照)を省略する。また、図4には、図3のA−A’断面に対応する面における画素101aの概略層構造を示す。さらに、以下の説明では、説明の明確化のため、同一レイヤにおける同種の膜に同一の符号を付す。

【0058】

図3または図4に示すように、画素101aは、アレイ基板としてのアクティブマトリクス基板101A(例えば図4参照)と、アクティブマトリクス基板101A上の有機発光ダイオードD1(例えば図4参照)と、を備える。アクティブマトリクス基板101Aは、例えば、走査線LGと、データ線LDと、容量線LCと、駆動線LPと、配線L1およびL2と、スイッチングトランジスタQ1と、駆動トランジスタQ2と、キャパシタC1と、を含む。有機発光ダイオードD1は、アノード電極61およびカソード電極63にサンドウィッチされた有機膜62を含み、例えば配線L2を介して駆動トランジスタQ2のソース電極24sに接続される。なお、有機発光ダイオードD1に対して光の取り出し側にカラーフィルタを設けてもよい。

【0059】

走査線LGは、例えば、透明基板10上の第1配線レイヤ41から構成される(例えば図3参照)。データ線LD、容量線LCおよび駆動線LPは、それぞれ例えば、透明基板10上の第1配線レイヤ41および層間絶縁膜40上の第2配線レイヤ43と、層間絶縁膜40に形成されたコンタクト内のコンタクト内配線42と、隣接する画素101a間における第1配線レイヤ41を接続するためのコンタクト内配線42および第2配線レイヤ43よりなる立体配線RCと、から構成される。配線L1およびL2は、それぞれ例えば、透明基板10上の第1配線レイヤ41および層間絶縁膜40上の第2配線レイヤ43と、層間絶縁膜40に形成されたコンタクトホール内のコンタクト内配線42と、から構成される。また、配線L2には、例えば、駆動トランジスタQ2のソース電極24sに接続された第1配線レイヤ41を有機発光ダイオードD1のアノード電極61へ電気的に接続するためのコンタクトプラグ51も含まれる。さらに、図2に示す各ノードN1〜N6は、それぞれ例えば図3に示す各位置に定義することができる。

【0060】

第1配線レイヤ41において、略行方向または略列方向に延伸する部分は、それぞれ走査線LG、データ線LD、容量線LCまたは駆動線LPにおける主配線部分に相当する。また、主配線部分から分岐して当該主配線と各画素101aにおける素子(Q1、Q2、C1等)とを接続するための副配線部分に相当する。

【0061】

コンタクト内配線42および第2配線レイヤ43は、例えばデータ線LD、容量線LCまたは駆動線LPを層間絶縁膜40上に導くための配線、または、各配線(LD、LC、LP等)と略垂直方向に延伸する走査線LGを跨いで各配線(LD、LC、LP等)における主配線間を電気的に接続させるための立体配線RCである。なお、本実施の形態では、コンタクト内配線42および第2配線レイヤ43において、各配線(LD、LC、LP等)を層間絶縁膜40上に導く部分は副配線部分に含まれ、走査線LGを跨ぐための部分は主配線部分に含まれる。

【0062】

このように、層間絶縁膜40(例えば図4参照)内に形成されたコンタクト内配線42を用いて層間絶縁膜40下の第1配線レイヤ41と層間絶縁膜40上の第2配線レイヤ43とを電気的に接続することで、各信号線(LG、LD、LC、LP等)を立体交差させることが可能になる。これにより、各配線(LG、LD、LC、LP等)の多くの領域を単一の層(本実施の形態で透明基板10上の層)に形成することが可能となるため、アクティブマトリクス基板101Aにおける層構造の簡略化や配線レイアウトの明確化などが可能になると共に、上層に形成する膜上面の平坦性を高めることが可能となる。

【0063】

また、透明基板10上において、各種配線(LG、LD、LC、LP、L1、L2等)および各種素子(Q1、Q2、C1等)が形成されない領域には、例えば第1配線レイヤ41の一部が冗長された冗長配線41a(例えば図3参照)が形成されることで、透明基板10上に形成される層上面の平坦性が向上されている。

【0064】

スイッチングトランジスタQ1は、例えば、透明基板10上のゲート電極11と、ゲート電極11を覆うゲート絶縁膜12と、ゲート絶縁膜12上におけるソース電極14sおよびドレイン電極14dと、ソース電極14sおよびドレイン電極14d間におけるゲート絶縁膜12上の透明半導体層13と、よりなる、いわゆるボトムゲート構造の薄膜トランジスタ(TFT)である(例えば図4参照)。

【0065】

ゲート電極11には、例えば走査線LGを構成する第1配線レイヤ41の一部を使用することができる。ゲート絶縁膜12には、例えば層間絶縁膜40の一部を使用することができる。透明半導体層13には、例えば透明半導体層44の一部を使用することができる。ソース電極14sには、例えばデータ線LDの一部を構成する第2配線レイヤ43の一部を使用することができる。ドレイン電極14dには、例えば配線L1の一部を構成する第2配線レイヤ43の一部を使用することができる。ただし、本発明はこれに限定されず、例えば、ゲート電極11に第2配線レイヤ43の一部を使用し、ソース電極14sおよびドレイン電極14dにそれぞれ第1配線レイヤ41の一部を使用した、いわゆるトップゲート構造の薄膜トランジスタ(TFT)としてもよい。

【0066】

同様に、駆動トランジスタQ2は、例えば、透明電極10上のゲート電極21と、ゲート電極21を覆うゲート絶縁膜22と、ゲート絶縁膜22上におけるソース電極24sおよびドレイン電極24dと、ドレイン電極24dおよびソース電極24s間におけるゲート絶縁膜22上の透明半導体層23と、よりなる、いわゆるボトムゲート構造の薄膜トランジスタ(TFT)である(例えば図4参照)。

【0067】

ゲート電極21には、例えば配線L1の一部を構成する第1配線レイヤ41の一部を使用することができる。ゲート絶縁膜22には、例えば層間絶縁膜40の一部を使用することができる。透明半導体層23には、例えば透明半導体層44の一部を使用することができる。ドレイン電極24dには、例えば駆動線LPの一部を構成する第2配線レイヤ43の一部を使用することができる。ソース電極24sには、例えば配線L2の一部を構成する第2配線レイヤ43の一部を使用することができる。ただし、本発明はこれに限定されず、例えば、ゲート電極21に第2配線レイヤ43の一部を使用し、ドレイン電極24dおよびソース電極24sにそれぞれ第1配線レイヤ41の一部を使用した、いわゆるトップゲート構造のTFTとしてもよい。

【0068】

なお、本実施の形態によるアクティブマトリクス基板101Aは、トランジスタ素子としてのTFTを備える、いわゆるアレイ基板と称されるものである。

【0069】

キャパシタC1は、例えば、透明基板10上の下部電極31と、下部電極31上の上部電極33と、下部電極31および上部電極33間の容量絶縁膜32と、よりなる(例えば図4参照)。下部電極31には、例えば容量線LCの一部を構成する第1配線レイヤ41の一部を使用することができる。容量絶縁膜32には、例えば層間絶縁膜40の一部を使用することができる。上部電極33には、例えば駆動線LPを構成する第2配線レイヤ43の一部を使用することができる。

【0070】

また、アクティブマトリクス基板101A上の有機発光ダイオードD1は、例えば、アノード電極61と、アノード電極61上の有機膜62と、有機膜62上のカソード電極63と、よりなる(例えば図4参照)。なお、有機発光ダイオードD1に対して光を取り出す側の層には、カラーフィルタや波長シフタなどの色変換膜を配置しても良い。

【0071】

隣接する画素101a間には、例えば、アノード電極61と有機膜62とを画素ごとに区画するための隔壁70が形成される(例えば図4参照)。層間絶縁膜50上には、有機発光ダイオードD1および下層の各素子ならびに各配線を保護するためのパッシベーション膜80が形成される(例えば図4参照)。

【0072】

ここで、透明基板10には、ガラス基板を用いることができる。ただし、これに限定されず、例えばガラス基板や石英基板やプラスチック基板など、種々の透明な絶縁性基板を用いることができる。また、透明基板10としてフレキシブルな基板を用いることで、フレキシブルな有機ELディスプレイ装置100を実現することも可能である。なお、本発明において透明とは、少なくとも可視光の帯域に含まれる波長の光に対して透明または半透明であることを意味する。

【0073】

第1配線レイヤ41、コンタクト内配線42および第2配線レイヤ43、ならびに、コンタクトプラグ51は、亜鉛錫酸化物(Zinc Tin Oxide:ZTO)を主成分とした導電体材料を用いて形成される。ただし、これに限定されず、例えばインジウム含有酸化物(Indium Tin Oxide:ITO、Indium Zinc Oxide:IZOなど)やその他の無機酸化物導電体材料、あるいは、有機物材料などで、透明導電性膜を得ることのできる導電体材料を用いて形成することもできる。なお、ZTO材料は、例えば、Zn(モル)よりもSn(モル)の量を多くすることにより(例えば、Zn:Snのモル比が1:2など)、導電体材料としての使用が可能である。また、導電体材料としてのITOは通常In:Snのモル比が0.9:0.1程度、導電体材料としてのIZOは通常In:Znのモル比が0.9:0.1程度である。

【0074】

特に、ZTO導電性膜は、アモルファスな膜として形成することが可能なため、フレキシブルな第1配線レイヤ41、第2配線レイヤ43、コンタクト内配線42およびコンタクトプラグ51を実現することが可能であるという利点を備える。さらに、アモルファスなZTO導電性膜は、低温形成することが可能であるため、例えばプラスチック基板などの高温耐性の低い基板を透明基板10として用いた場合でも、容易に形成することが可能であるという利点も備える。これらのことから、ZTO導電性膜を用いて第1配線レイヤ41、第2配線レイヤ43、コンタクト内配線42およびコンタクトプラグ51を形成することは、フレキシブルな有機ELディスプレイ装置100を形成する際に好適であると言える。

【0075】

層間絶縁膜40および50には、例えばSOG(Spin ON Glass)や酸化シリコン(SiO2)や窒化シリコン(SiNX)などのシリコン系絶縁物やアルミナ(Al2O3)等のアルミニウム酸化物やハフニア(HfO2)等のハフニウム酸化物やイットリア(Y2O3)などのイットリウム酸化物やLa2O3等のランタン酸化物など、あるいは、透明な感光性樹脂などのような塗布プロセスによる成膜が可能な絶縁物よりなる透明な絶縁性単層膜、または、これらを1つ以上含む透明な絶縁性多層膜を用いることができる。本実施の形態では、層間絶縁膜40を例えばアルミナ(Al2O3)膜とハフニア(HfO2)膜とを含む多層構造の絶縁膜で形成し、層間絶縁膜50を例えば感光性樹脂よりなる単層構造の絶縁膜で形成する。なお、本実施の形態において、層間絶縁膜40および50は、各層間を絶縁するための絶縁膜として機能するほか、各層の平坦性を確保するための平坦化膜としても機能することができる。

【0076】

層間絶縁膜40上には、第2配線レイヤ43およびコンタクト内配線42を覆うように透明半導体層44が形成される。透明半導体層44は、後述する製造工程における例えばエッチング工程時に下層に位置する第2配線レイヤ43やコンタクト内配線42などが受けるプロセスダメージを低減するための保護膜として機能する。本実施の形態では、透明半導体層44の例として、前記の導電体材料(ZTO導電体材料、インジウム含有酸化物導電体材料)よりなる配線よりも、キャリア濃度を低くすることのできる半導体材料で、ZTOまたはインジウム含有酸化物から構成される半導体材料よりなる透明半導体層を用いる。なお、ZTO材料は、例えば、Sn(モル)よりもZn(モル)の量を多くすることにより(例えば、Zn:Snのモル比が2:1など)、半導体材料としての使用が可能である。また、このZTO半導体層の成膜時には、雰囲気の酸素濃度を増やすなどして、半導体層のキャリア濃度を低くする調整を行うことができる。また、上述した第1配線レイヤ41等と同様に、ZTO透明半導体層も、アモルファスな膜として形成できることから、フレキシブルな透明半導体層44を実現することが可能となり、フレキシブルな有機ELディスプレイ装置100を形成する際に好適である。また、本発明はこのようなZTO半導体材料に限定されず、インジウム含有酸化物半導体材料(例えば、In:Znのモル比が4:6のIZOなど)などの透明無機酸化物半導体材料や、この他、ペンタセンやテトラベンゾポルフィリンの前駆体などを含む透明有機半導体材料など、種々の透明半導体材料を用いて形成することができる。

【0077】

なお、本実施の形態では、透明半導体層44を形成する導電体材料の主成分と、各素子においてこの透明電極と接触する電極部分を形成する導電体材料の主成分と、に同種の材料を用いる。したがって、本実施の形態では、ソース電極14sおよびドレイン電極14dならびにソース電極24sおよびドレイン電極24dを含む第2配線レイヤ43がZTOを主成分とするZTO導電性膜で形成され、透明半導体層44がZTOを主成分とし、キャリア濃度が第2配線レイヤ43のそれよりも低いZTO半導体膜で形成される。このように、両者を同種の材料で形成することで、例えばスイッチングトランジスタQ1におけるソース電極14sまたはドレイン電極14dと透明半導体層13とをオーミック接触させることが可能となる。同様に、駆動トランジスタQ2におけるドレイン電極24dまたはソース電極24sと透明半導体層23とをオーミック接触させることが可能となる。これにより、各TFT素子(Q1,Q2など)における抵抗成分が低減されるため、各TFT素子の駆動電力を低減することが可能となり、結果的に有機ELディスプレイ装置100の消費電力を低減することが可能となる。

【0078】

隔壁70は、例えば感光性樹脂よりなる単層構造の絶縁膜で形成することができる。ただし、これに限定されず、例えばSOGやSiO2SiNXなどのシリコン系絶縁物やAl2O3等のアルミニウム酸化物やHfO2等のハフニウム酸化物やY2O3などのイットリウム酸化物やLa2O3等のランタン酸化物など、あるいは、透明な感光性樹脂などのような塗布プロセスによる成膜が可能な絶縁物よりなる透明な絶縁性単層膜、または、これらを1つ以上含む透明な絶縁性多層膜を用いることができる。

【0079】

また、スイッチングトランジスタQ1、駆動トランジスタQ2およびキャパシタC1は、上述した第1配線レイヤ41、第2配線レイヤ43および層間絶縁膜40の一部を使用して構成することが可能であるため、その材料も上述したものと同様とすることができる。ただし、各電極上にこれを低抵抗化するための透明な導電性膜を形成するなど、適宜変形することも可能である。

【0080】

また、有機発光ダイオードD1において、有機膜62は、例えば、正孔注入層、正孔輸送層、有機発光層、電子輸送層、電子注入層および正孔障壁層を含んだ多層構造の積層膜である。有機膜62において、有機発光層のホスト材料には、ポリフルオレン、その誘導体および共重合体、ポリアリーレン、その誘導体および共重合体、ポリアリーレンビニレン、その誘導体および共重合体やポリアリールアミン、その誘導体および共重合体などのような高分子材料や、その他、蛍光性もしくは燐光性の種々の低分子発光材料または高分子材料など、正孔輸送層等との組合せやターゲット波長等に応じて種々の発光材料を用いることができる。

【0081】

光取出し側に配置されるアノード電極61には、例えばZTOやITOなどのような酸化物導電体材料、あるいは、銀(Ag)やアルミニウム(Al)などの金属材料よりなる透明単層膜、もしくは、これらを含む多層構造の透明積層膜を用いることができる。なお、金属材料を用いた場合、これを含む層は、光を透過させる程度の薄い膜とされる。本実施の形態では、ZTO/Ag/ZTOの積層膜を用い、その中のAg膜を光が透過する程度の薄膜で形成した場合を例に挙げる。さらに、カソード電極63には、例えば銀(Ag)やアルミニウム(Al)やマグネシウム(Mg)などのような高い導電性と反射率とを兼ね備えた金属あるいは合金などの導電体材料を用いて得ることができる。本実施の形態では、MgとAgとの合金膜を用いた場合を例に挙げる。

【0082】

パッシベーション膜80は、例えばCVD法で成膜されたSiO2膜やSiNx膜等の多層膜を用いて形成することが可能である。本実施の形態では、SiO2膜やSiNx膜の多層膜を使用した場合を例に挙げる。

【0083】

以上から明らかなように、本実施の形態による有機ELディスプレイ装置100は、有機膜62に対して光取出し側である下面100a側に位置する層のすべてが光を透過する透明膜あるいは半透明膜で形成されているため、光取出し面である下面100aの全領域が開口された、いわゆる全開口型の有機ELディスプレイ装置100を実現することが可能となる。

【0084】

(製造方法)

次に、本実施の形態による有機ELディスプレイ装置100の製造方法を、図面を参照して詳細に説明する。図5−1から図5−10は、本実施の形態による有機ELディスプレイ装置100におけるディスプレイパネル101の製造方法を示すプロセス断面図である。なお、図5−1から図5−10では、図4に示すA−A’断面と対応する断面を示す。

【0085】

本製造方法では、まず、透明基板10を準備し、該基板の厚み方向(基板に対して垂直方向)と垂直な面である2つの主面のうち一方の主面(以下、これを上面とする)上に、例えばスパッタリング法、CVD(Chemical Vapor Deposition)法または真空蒸着法などを用いてZTOを堆積することで、透明なアモルファス状のZTO導電性膜を形成する。続いて、例えばフォトリソ法を用いて当該ZTO導電性膜をパターニングすることで、図5−1に示すように、透明基板10上に、ゲート電極11および21、下部電極31、第1配線レイヤ41ならびに冗長配線41a(図3参照)等を形成する(第1配線形成工程)。ただし、これに限定されず、例えばゾル・ゲル法を使用した印刷技術やインクジェットプリンティング技術などのような塗布プロセス技術などを用いてゲート電極11および21、下部電極31、第1配線レイヤ41ならびに冗長配線41a等を形成しても良い。

【0086】

次に、各電極および配線(11、21、31、41、41a等)が形成された透明基板10上面上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてアルミナ(Al2O3)とハフニア(HfO2)とを順次堆積することで、透明な絶縁性積層膜よりなる層間絶縁膜40を形成する(第1層間絶縁膜形成工程)。続いて、例えばフォトリソ法を用いて当該層間絶縁膜40をパターニングすることで、図5−2に示すように、層間絶縁膜40内に、第1配線レイヤ41の一部を露出させるコンタクトホールap1およびap2を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてコンタクトホールap1およびap2を備えた層間絶縁膜40を形成しても良い。なお、本工程で形成された層間絶縁膜40の内、少なくともゲート電極11上の層間絶縁膜40は、スイッチングトランジスタQ1のゲート絶縁膜12として機能し、少なくともゲート電極21上の層間絶縁膜40は、駆動トランジスタQ2のゲート絶縁膜22として機能し、少なくとも下部電極31上の層間絶縁膜40は、キャパシタC1の容量絶縁膜32として機能する。さらに、コンタクトホールap2は、後の工程において第1配線レイヤ41と電気的に接続されたコンタクトプラグ51の一部を形成するためのコンタクトホールである。

【0087】

次に、コンタクトホールap1およびap2が形成された層間絶縁膜40上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOを堆積することで、透明なアモルファス状のZTO導電性膜を形成する。この際、コンタクトホールap2内にZTO導電性膜が形成されてもよい。続いて、例えばフォトリソ法を用いて当該ZTO導電性膜をパターニングすることで、図5−3に示すように、層間絶縁膜40上に、ソース電極14sおよびドレイン電極14d、ドレイン電極24dおよびソース電極24s、上部電極33、ならびに第2配線レイヤ43等を形成すると共に、層間絶縁膜40のコンタクトホールap1内に第1配線レイヤ41と電気的に接続されたコンタクト内配線42を形成する(第2配線形成工程)。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてソース電極14sおよびドレイン電極14d、ドレイン電極24d、ソース電極24s、上部電極33、コンタクト内配線42および第2配線レイヤ43を形成しても良い。なお、この工程では、コンタクトホールap2内のZTO導電性膜が完全に除去されなくともよい。

【0088】

次に、各電極および配線(14s、14d、24d、24s、33、42、43等)が形成された層間絶縁膜40上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOを堆積することで、キャリア濃度が、ZTO導電性膜のそれよりも低いZTO半導体膜を形成する(半導体層形成工程)。この際、コンタクトホールap2内にZTO半導体膜が形成されてもよい。なお、上述したように、ZnとSnのモル比を制御することなどにより、ZTO半導体膜は、そのキャリア濃度が第1配線レイヤ41や第2配線レイヤ43等を構成するZTO導電性膜よりも低い、透明な半導体膜とすることが可能である。続いて、例えばフォトリソ法を用いて当該ZTO半導体膜をパターニングすることで、図5−4に示すように、層間絶縁膜40上に、各電極および配線(14s、14d、24d、24s、33、42、43等)を覆う透明半導体層44を形成する。この際、コンタクトホールap2内のZTO半導体膜が完全に除去される程度にオーバエッチングされることが好ましい。なお、形成された透明半導体層44の内、少なくともソース電極14sおよびドレイン電極14d間の透明半導体層44は、スイッチングトランジスタQ1のチャネル形成層として機能する透明半導体層13として機能し、少なくともドレイン電極24dおよびソース電極24s間の透明半導体層44は、駆動トランジスタQ2のチャネル形成層として機能する透明半導体層23として機能する。

【0089】

ここで本実施の形態では、透明半導体層44と第2配線レイヤ43およびコンタクト内配線42とが同種の材料を用いて形成されているため、透明半導体層44と第2配線レイヤ43等とのエッチングにおける選択比を得ることは困難である。そこで本実施の形態のように、パターニング後の透明半導体層44が第2配線レイヤ43およびコンタクト内配線42を覆うように構成することで、エッチング中に第2配線レイヤ43およびコンタクト内配線42がエッチング雰囲気中に曝されることが無いため、第2配線レイヤ43等との選択比を考慮することなく、透明半導体層44をパターニングすることが可能となる。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて透明半導体層44を形成しても良い。この場合、形成した透明半導体層をエッチングなどによりパターニングする必要が無くなるため、透明半導体層44は必ずしも第2配線レイヤ43およびコンタクト内配線42を覆っていなくとも良い。

【0090】

以上のように透明半導体層(13、23、44等)を形成すると、次に、透明半導体層(13、23、44等)が形成された層間絶縁膜40上に、例えば感光性レジスト液をスピン塗布し、これを露光および現像することで、図5−5に示すように、層間絶縁膜40のコンタクトホールap2と連続するコンタクトホールap3を備え、透明な感光性樹脂よりなる層間絶縁膜50を形成する(第2層間絶縁膜形成工程)。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてコンタクトホールap3を備えた層間絶縁膜50を形成しても良い。

【0091】

次に、コンタクトホールap3が形成された層間絶縁膜50上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOを堆積することで、図5−6に示すように、少なくとも層間絶縁膜50のコンタクトホールap3内および層間絶縁膜40のコンタクトホールap2内に第1配線レイヤ41と電気的に接続された透明なアモルファス状のコンタクトプラグ51を形成する。なお、この際に形成される層間絶縁膜50上の不要なZTO導電性膜は、例えばエッチバックなどの技術などを用いて除去される。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて層間絶縁膜40および50内にコンタクトプラグ51を形成しても良い。

【0092】

これまでに説明した工程を経ることで、本実施の形態では、いわゆるアレイ基板としてのアクティブマトリクス基板101Aが製造される。

【0093】

次に、アクティブマトリクス基板101A上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOとAgとZTOとを順次堆積することで、コンタクトプラグ51と電気的な接点を備える透明なZTO/Ag/ZTO積層膜を形成する。続いて、例えばフォトリソ法を用いて当該ZTO/Ag/ZTO積層膜をパターニングすることで、図5−7に示すように、層間絶縁膜50上に、コンタクトプラグ51と電気的に接続されたアノード電極61を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてアノード電極61を形成しても良い。

【0094】

次に、アノード電極61が形成されたアクティブマトリクス基板101A上に、例えば感光性レジスト液をスピン塗布し、これを露光および現像することで、図5−8に示すように、アクティブマトリクス基板101A上の各画素101aを区画する領域に、透明な感光性樹脂よりなる隔壁70を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて隔壁70を形成しても良い。

【0095】

次に、少なくともアノード電極61上に、例えば既存の成膜技術を用いて正孔注入層、正孔輸送層、有機発光層、電子輸送層、電子注入層および正孔障壁層を順次積層形成することで、図5−9に示すように、有機膜62を隔壁70により区画されたアノード電極61上に形成する。なお、有機膜62において、例えば正孔注入層と正孔輸送層と電子輸送層と電子注入層と正孔障壁層とは、例えば高分子ポリマー溶液を使用した印刷技術やインクジェットプリンティング技術などのような塗布プロセスを用いて形成することが可能である。ただし、これに限定されず、例えば真空蒸着法に代表されるシャドウマスク蒸着法や転写法に代表されるレーザー熱転写法(LITI法)、レーザー再蒸着法(RIST法、LIPS法)などを用いて正孔注入層、正孔輸送層、有機発光層、電子輸送層、電子注入層および正孔障壁層を順次成膜することで、画素101aに応じた有機膜62を形成しても良い。また、アノード電極61に例えばITO/PEDOT(3,4−エチレンジオキシチオフェン):PSS(Polystyrenesulfonate)などのような無機酸化物導電性膜と導電性高分子ポリマー膜との積層膜を用いた場合、有機膜62を下層から例えば正孔注入層/有機発光層/電子注入層の積層膜とすることが可能である。

【0096】

次に、有機膜62および隔壁70が形成されたアクティブマトリクス基板101A上全体に、例えば真空蒸着法などを用いてMgとAgとの合金材料を堆積することで、導電性を有する合金膜を形成する。この時、シャドウマスク法を用いて所望の領域以外に余分な合金膜が蒸着されることを防止することで、図5−10に示すように、少なくとも画素(101a)の配列領域全体にカソード電極63を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてカソード電極63を形成しても良い。

【0097】

次に、隔壁70により区画されたアノード電極61および有機膜62とカソード電極63とよりなる有機発光ダイオードD1が形成されたアクティブマトリクス基板101A上面全体に、CVD法などを用いてSiO2およびSiNxの多層膜を形成することにより、下層の各素子(Q1、Q2、C1、D1等)および配線(LG、LD、LP、L1、L2等)を保護するパッシベーション膜80を形成する。そして、最後にその上面である基板101Aとは反対側に基板を貼り付けて封止したり、もしくは、スパッタリング法やCVD法により膜を形成して封止を行う。以上の工程を経ることで、図4に示す層構造を備えた画素101aを含むディスプレイパネル101が製造される。このとき、基板101Aとは反対側の基板は、ガラス、PET等に代表される透明ポリマーフィルム、スパッタリング法やCVD法などでフィルムのバリア性を高めるために有機膜と無機膜とを交互に積層した封止膜などが挙げられる。

【0098】

その後、以上のように製造したディスプレイパネル101を、信号制御部102や走査駆動部103やデータ駆動部104や容量線駆動部105や駆動信号生成部106やその他の部品が搭載された筐体に取り付けることで、本実施の形態による有機ELディスプレイ装置100が製造される。

【0099】

なお、以上の製造工程には、基板を洗浄する工程等が適宜含まれるが、ここでは説明の簡略化のためにこれらの工程を省略する。

【0100】

以上で説明したように、本実施の形態による有機ELディスプレイ装置100は、有機膜62に対して光取出し側である下面100a側にある層すべてが光を透過する膜より構成されているため、光取出し面が全て開口された、いわゆる全開口の裏面発光型有機ELディスプレイ装置100が実現できる。

【0101】

また、このように光取出し面全てが開口された構成とすることで、発光素子(本実施の形態では有機発光ダイオードD1)の配置を自由に設計することが可能となるため、設計自由度の大きな有機ELディスプレイ装置100を実現することが可能となる。

【0102】

さらに、本実施の形態による製造方法では、製造過程においてコンタクト内配線42および第2配線レイヤ43等が透明半導体層44で覆われているため、後のエッチング工程などにおける各配線(42,43など)が受けるプロセスダメージを低減することが可能となる。

【0103】

さらにまた、上記した実施の形態において、有機ELディスプレイ装置100を構成する各層をフレキシブルな材料を用いて形成していてもよい。

【0104】

なお、上記した本発明の実施の形態1では、発光層(本実施の形態では有機膜62)が有機材料で形成された有機ELディスプレイ装置100を例に挙げて説明したが、本発明はこれに限定されず、例えば発光層が無機材料で形成された無機ELディスプレイ装置とすることも可能である。

【0105】

<実施の形態2>

次に、本発明の実施の形態2による表示装置として、有機ELディスプレイ装置を例に挙げて説明する。なお、本実施の形態では、発光素子(例えば図6における有機発光ダイオードD2参照)からの光をディスプレイパネル101の上面(例えば図6における上面200a参照)および下面(例えば図6における下面100a参照)の両方から外部へ出力することが可能な有機ELディスプレイ装置を例に挙げる。すなわち、本実施の形態による有機ELディスプレイ装置は、上面発光型(トップエミッションタイプ)と裏面発光型との両方を兼ね備えた、いわゆる両面発光型の有機ELディスプレイ装置である。また、以下の説明において、本発明の実施の形態1と同様の構成については、説明の明確化のために、同一の符号を付し、その詳細な説明を省略する。

【0106】

本実施の形態による有機ELディスプレイ装置の概略ブロック構成は、図1に示す有機ELディスプレイ装置100の概略ブロック構成と同様である。ただし、本実施の形態では、図1における画素101aが画素201aに置き換えられる。また、画素201aの概略回路構成は、図2に示す画素101aの概略回路構成と同様である。ただし、本実施の形態では、図2における有機発光ダイオードD1が有機発光ダイオードD2に置き換えられる。

【0107】

(画素構成)

次に、各画素201aのレイアウト構造および層構造を詳細に説明する。本実施の形態による画素201aにおけるアクティブマトリクス基板101Aのレイアウト構造は、図3に示す画素101aのレイアウト構造と同様である。ただし、本実施の形態による画素201aの概略層構造は、図6に示すものとなる。なお、図6は、図4と同様に、図3のA−A’断面に対応する面における画素201aの概略断面図である。

【0108】

図6と図4とを比較すると明らかなように、本実施の形態による有機ELディスプレイ装置は、本発明の実施の形態1による有機ELディスプレイ装置100と同様の構成において、カソード電極63(例えば図4参照)が透明な電極材料で形成されたカソード電極65に置き換えられると共に、カソード電極65上に有機発光ダイオードD2におけるカソードの抵抗値を低減するための補助電極66が設けられている。

【0109】

カソード電極65は、例えばアノード電極61と同様に、可視光を透過可能な電極材料を用いて形成することができる。この電極材料には、例えばZTOやITOなどのような酸化物導電体材料、あるいは、銀(Ag)やアルミニウム(Al)などの金属材料よりなる透明単層膜、もしくは、これらを含む多層構造の透明積層膜を用いることができる。なお、金属材料を用いた場合、これを含む層は、光を透過させる程度の薄い半透過膜とされる。本実施の形態では、MgとAg合金膜を用い、光が透過する程度の薄膜で形成した場合を例に挙げて説明する。このように、本発明の実施の形態1によるボトムエミッション型の構成に加えて、カソード電極65を透明な電極で構成することで、ディスプレイパネル101の下面100aおよび上面200aの両方から光を取り出すことが可能な、いわゆる両面発光型の有機ELディスプレイ装置を実現することが可能となる。

【0110】

また、カソード電極65上の補助電極66は、例えばアクティブマトリクス基板101A上の各画素201aを区画する領域(例えば隔壁70上方)に形成される。この補助電極材料には、例えばZTOやITOなどのような無機酸化物導電体材料、あるいは、銀(Ag)やアルミニウム(Al)などの金属材料よりなる単層膜、もしくは、これらを含む多層構造の積層膜を用いることができる。ただし、本実施の形態のように補助電極66を各画素201aの各領域上に配置する場合、補助電極66は必ずしも透明な電極材料を用いて形成される必要は無く、例えばAlやAgなどの高い導電性を備えた材料で形成することも可能である。本実施の形態では、ZTOよりなる導電性単層膜を用いて補助電極66を形成した場合を例に挙げて説明する。このように、有機発光ダイオードD2におけるカソードの抵抗値を低減する補助電極66を設けることで、有機発光ダイオードD2の駆動電圧を低減することが可能となるため、結果的に有機ELディスプレイ装置の消費電力を低減することが可能となる。また、補助電極66の材料に透明電極材料を用いているため、下面100aだけでなく、上面200a全体も開口された、いわゆる両面全開口型の有機ELディスプレイ装置を実現することが可能となる。

【0111】

(製造方法)

また、本実施の形態による有機ELディスプレイ装置の製造方法は、本発明の実施の形態1による有機ELディスプレイ装置100の製造方法と同様の製造方法において、図5−10に示すカソード電極63の形成工程が、透明なカソード電極65の形成工程になると共に、カソード電極65上に補助電極66を形成する工程が加わる。なお、他の製造工程は、本発明の実施の形態1において図5−1から図5−10および図4を用いて説明した工程と同様であるため、ここでは詳細な説明を省略する。

【0112】

カソード電極65の形成工程では、図5−1から図5−9を用いて製造したアクティブマトリクス基板101A上全体に、例えば真空蒸着法などを用いてMgとAgの合金薄膜を堆積することで、カソード電極65を形成する。このとき、シャドウマスク法を用いることで、所望の領域全体にカソード電極65を形成する。

【0113】

また、補助電極66の形成工程では、上記工程のようにカソード電極65を形成した後、少なくともカソード電極65上に、例えばシャドウマスク法を用いたスパッタリング法、CVD法または真空蒸着法などを用いてZTOやITO等の酸化物導電材料やAg、Al、Cu等の低抵抗率の金属を堆積することで、例えばカソード電極65上面における隔壁70上方の領域に補助電極66を形成する。

【0114】

その後、本発明の実施の形態1と同様に、パッシベーション膜80を形成した後、製造されたディスプレイパネル101を、信号制御部102や走査駆動部103やデータ駆動部104や容量線駆動部105や駆動信号生成部106やその他の部品が搭載された筐体に取り付けることで、本実施の形態による有機ELディスプレイ装置が製造される。

【0115】

なお、以上の製造工程には、基板を洗浄する工程等が適宜含まれるが、ここでは説明の簡略化のためにこれらの工程を省略する。

【0116】

以上で説明したように、本実施の形態による有機ELディスプレイ装置は、有機膜62に対して光取出し側である上面200a側および下面100a側にある層すべてが光を透過する膜より構成されているため、光取出し面が全て開口された、いわゆる全開口の両面発光型有機ELディスプレイ装置が実現できる。

【0117】

また、このように光取出し面全てが開口された構成とすることで、発光素子(本実施の形態では有機発光ダイオードD2)の配置を自由に設計することが可能となるため、設計自由度の大きな有機ELディスプレイ装置を実現することが可能となる。さらに、本実施の形態による有機ELディスプレイ装置は、カソード電極65の抵抗値を低減するための補助電極66を備えているため、有機発光ダイオードD2の駆動電圧を低減することが可能となり、結果、有機ELディスプレイ装置の消費電力を低減することが可能となる。さらにまた、本実施の形態による有機ELディスプレイ装置は、例えば、車両におけるウィンドウやガラス窓やガラス製水槽などのような透明な面に貼り付けて使用するディスプレイとしてなど、種々の目的で使用することが可能である。

【0118】

さらに、本実施の形態による製造方法では、本発明の実施の形態1と同様に、製造過程においてコンタクト内配線42および第2配線レイヤ43等が透明半導体層44で覆われているため、後のエッチング工程などにおける各配線(42,43など)が受けるプロセスダメージを低減することが可能となる。

【0119】

さらにまた、上記した実施の形態において、本発明の実施の形態1と同様に、有機ELディスプレイ装置100を構成する各層をフレキシブルな材料を用いて形成していてもよい。

【0120】

なお、本実施の形態は、本発明の実施の形態1と同様に、例えば発光層が無機材料で形成された無機ELディスプレイ装置とすることも可能である。また、本実施の形態では、一方の光取出し側である上下何れかの側の層に例えば反射膜(リフレクタ)を設けることで、輝度などが向上された、上面発光型もしくは裏面発光型の有機ELディスプレイ装置を実現することもできる。

【0121】

<実施の形態3>

次に、本発明の実施の形態3による表示装置として、液晶ディスプレイ装置300を例に挙げて説明する。図7は、液晶ディスプレイ装置300の概略構成を示すブロック図である。なお、本実施の形態では、いわゆるバックライトと呼ばれる光源(例えば図10における光源350参照)と液晶素子(例えば図10における液晶素子E31参照)との間に素子基板(例えば図10におけるアクティブマトリクス基板301A参照)が介在する構成の液晶ディスプレイ装置300を例に挙げる。また、本実施の形態において、本発明の実施の形態1または2と同様の構成については、同一の符号を付すことで、その詳細な説明を省略する。

【0122】

(全体構成)

図7に示すように、液晶ディスプレイ装置300は、2次元マトリクス状に配列された画素(PX)301aを含むディスプレイパネル301と、これに接続された走査駆動部103、データ駆動部104および容量線駆動部105と、各部を制御するための信号制御部102と、を備える。なお、ディスプレイパネル301は、赤(R)、緑(G)および青(B)の三原色それぞれについての画素301aを備える。

【0123】

ここで、信号制御部102、走査駆動部103、データ駆動部104および容量線駆動部105の構成は、本発明の実施の形態1と同様である。また、走査制御信号CONT1、データ制御信号CONT2、容量線制御信号CONT3およびビデオデータ信号DATについても、適宜、液晶素子の駆動方式に適合した信号として生成され、出力される。ただし、本実施の形態においては、駆動線LP、駆動信号生成部106および発光制御信号CONT4を省略することができる。

【0124】

また、ディスプレイパネル301は、走査線LGとデータ線LDと容量線LCとに接続される。なお、本実施の形態では、走査線LGとデータ線LDと容量線LCとのそれぞれにおいて、相互に交差するように延伸する配線部分を主配線とし、この主配線から分岐して各画素301aにおけるスイッチングトランジスタQ31や蓄積キャパシタC31(例えば図8参照)に接続する配線を副配線とする。また、各素子間を接続する配線部分を副配線とする。また、他の構成は、本発明の実施の形態1と同様であるため、ここでは詳細な説明を省略する。

【0125】

(画素構成)

次に、図8を用いて各画素301aの概略構成およびその動作を説明する。なお、以下の説明は、R,G,Bのうち何れの画素301aについても同様である。

【0126】

図8は、画素301aの概略回路構成を示す模式図である。図8に示すように、画素301aは、スイッチングトランジスタQ31と、蓄積キャパシタC31と、液晶素子E31と、を含む。

【0127】

スイッチングトランジスタQ31は例えばn型のTFTであり、そのソースSは例えばノードN34においてデータ線LDの主配線から分岐する副配線に接続され、ドレインDはノードN31を含む配線L31に接続される。また、スイッチングトランジスタQ31のゲートGは、例えばノードN33において走査線LGの主配線から分岐する副配線に接続される。したがって、スイッチングトランジスタQ31は、走査信号の電圧レベルVg(走査制御電圧)に従ってデータ線LDおよびノードN31間を導通/遮断する。

【0128】

配線L31には、例えばノードN31において分岐する配線部分(これも配線L31に含む)を介して蓄積キャパシタC31の一方の端子が接続される。また、蓄積キャパシタC31の他方の端子は、例えばノードN35において容量線LCの主配線から分岐する副配線に接続される。容量線LCには、本発明の実施の形態1と同様に、容量線駆動部105から出力された容量線駆動信号が与えられる。この容量線駆動信号の電圧レベルVc(容量線駆動電圧)は、例えば接地電位とすることができる。例えば、液晶素子Cpx(E31)と同じ共通電極であるGND(Vcom)端子に接続される。言い換えれば、容量線LCは、接地線とすることができる。この場合、容量線駆動部105を省略することができる。

【0129】

また、配線L31には、液晶素子E31の一方の電極(例えば図10における画素電極311参照)も接続される。液晶素子E31の他方の電極は、共通電極(例えば図10における共通電極313参照)である。したがって、液晶素子E31は、回路上、いわゆる液晶キャパシタCpxとして機能する。この共通電極313には、図7または図8に示すように、共通電圧Vcomが印加される。以上の接続関係から、蓄積キャパシタC31と液晶素子E31とは、スイッチングトランジスタQ31の出力端子に並列に接続された負荷容量として機能する。なお、共通電圧Vcomは、例えば接地電位GNDとすることができる。

【0130】

ここで、走査線LGに入力された走査信号の電圧レベルVg(走査制御電圧)がハイレベルになると、スイッチングトランジスタQ31がオン状態となり、当該スイッチングトランジスタQ31を介して液晶素子E31の画素電極311(例えば図10参照)に電荷が注入される。この結果、画素電極311の電位がデータ信号の電圧レベルVdとなり、共通電極313(例えば図10参照)との間に電位差(Vd−Vcom)が生じて液晶素子E31の分子配列が変化する。

【0131】

ここで、蓄積キャパシタC31は、走査線LGの電圧レベルVgがローレベルとなってスイッチングトランジスタQ31が完全にオフ状態となった後から次に電圧レベルVgがハイレベルになってスイッチングトランジスタQ31がオン状態となると共に次のデータ信号が入力されるまでの間、画素電極311の電位を維持するための働きをする。すなわち、蓄積キャパシタC31は、所定の期間、データ線LDに入力されたデータ信号SDを保持する。

【0132】

なお、本実施の形態では、例えば、データ線LDに入力されるデータ信号の極性と容量線LCに入力される容量線駆動信号の電位とが所定期間ごとに反転される、いわゆる反転駆動方式を採用しても良い。反転駆動方式としては、ドット反転駆動方式やライン反転駆動方式などが存在するが、いずれの反転駆動方式を採用することも可能である。

【0133】

次に、図9および図10を用いて、各画素301aのレイアウト構造および層構造を詳細に説明する。図9は、画素301aにおけるアクティブマトリクス基板301A(例えば図10参照)のレイアウト構造を説明するための概略平面図である。また、図10は、画素301aの層構造を説明するための概略断面図である。なお、図9では、説明の簡略化のため、透明基板10、層間絶縁膜40および50、ならびに、対向基板302Aなどの構成(例えば図10参照)を省略する。また、図10には、図9のB−B’断面に対応する面における画素301aの概略層構造を示す。

【0134】

図9または図10に示すように、画素301aは、アレイ基板としてのアクティブマトリクス基板301A(例えば図10参照)と、これと対向する対向基板302A(例えば図10参照)と、アクティブマトリクス基板301Aと対向基板302Aとの間に配置された液晶素子E31(例えば図10参照)と、を備える。アクティブマトリクス基板301Aは、例えば走査線LGと、データ線LDと、容量線LCと、配線L31と、スイッチングトランジスタQ31と、蓄積キャパシタC31と、を含む。対向基板302Aには、不要な光の漏れを防止するためのブラックマトリクスとしての遮光膜321と、画素301aごとに適切な帯域の波長を透過させるためのカラーフィルタ64と、を備える。液晶素子E31は、液晶層312をサンドウィッチする画素電極311および共通電極313とこれらをさらにサンドウィッチする配向膜314および315とを含み、例えば配線L31を介してスイッチングトランジスタQ31および蓄積キャパシタC31に接続されるようにアクティブマトリクス基板301A上に配置される。なお、対向基板302Aは、アクティブマトリクス基板301Aと共に、液晶素子E31をサンドウィッチするように配置される。さらに、アクティブマトリクス基板301Aと液晶素子E31と対向基板302Aとで形成される積層構造体は、例えば所定方向に振動している光のみを透過させるための偏光板330および340でサンドウィッチされる。

【0135】

走査線LG、データ線LD、容量線LCおよび配線L31は、本発明の実施の形態1と同様に、それぞれ例えば、第1配線レイヤ41、コンタクト内配線42、第2配線レイヤ43およびコンタクトプラグ51のうち少なくとも一部で形成されている。スイッチングトランジスタQ31は、走査線LGを構成する第1配線レイヤ41の一部であるゲート電極15と、層間絶縁膜40の一部であるゲート絶縁膜16と、データ線LDの一部を構成する第2配線レイヤ43の一部であるソース電極18sと、配線L31の一部を構成する第2配線レイヤ43の一部であるドレイン電極18dと、透明半導体層44の一部である透明半導体層17と、よりなる。さらに、蓄積キャパシタC31は、配線L31を構成する第1配線レイヤ41の一部である下部電極35と、層間絶縁膜40の一部である容量絶縁膜36と、容量線LCを構成する第2配線レイヤ43の一部である上部電極37と、よりなる。さらにまた、図8に示す各ノードN31、N33〜N35は、それぞれ例えば図9に示す各位置に定義することができる。

【0136】

また、本実施の形態によるスイッチングトランジスタQ31は、本発明の実施の形態1におけるスイッチングトランジスタQ1と同様に、いわゆるボトムゲート構造のTFTであるが、本発明はこれに限定されず、例えばトップゲート構造のTFTとしてもよい。さらに、本実施の形態によるアクティブマトリクス基板301Aは、本発明の実施の形態1によるアクティブマトリクス基板101Aと同様に、いわゆるアレイ基板と称されるものである。

【0137】

透明基板10上において、各種配線(LG、LD、LC、L31等)および各種素子(Q31、C31等)が形成されない領域には、本発明の実施の形態1と同様に、例えば第1配線レイヤ41の一部が冗長された冗長配線41a(例えば図9参照)が形成されることで、透明基板10上に形成される層上面の平坦性が向上されている。さらに、本実施の形態において、透明半導体層44は、各素子(例えばスイッチングトランジスタQ31)のチャネル層としてだけでなく、下層に位置する第2配線レイヤ43やコンタクト内配線42などが受けるプロセスダメージを低減するための保護膜として機能する。

【0138】

また、上記の構成を備えたアクティブマトリクス基板301A上の液晶素子E31は、例えば、画素電極311と、画素電極311上の液晶層312と、液晶層312上の共通電極313と、液晶層312を上下からサンドウィッチする配向膜314および315と、よりなる(例えば図10参照)。なお、液晶素子E31において、液晶層312の上部に略三角形状の誘電体突起316を設けても良い(例えば図10参照)。また、液晶素子E31に対して光を取り出す側には、光源350からの不要な光の漏れを防止するためのブラックマトリクスや、カラーフィルタまたは波長シフタなどの色変換膜を配置することも可能である。本実施の形態では、共通電極313と対向基板302Aとの間にブラックマトリクスとしての遮光膜321およびカラーフィルタ64を配置した場合を例に挙げる。

【0139】

また、アクティブマトリクス基板301Aおよび対向基板302Aのさらに外側には、これらをサンドウィッチする偏光板330および340が設けられる。また、光源350は、例えばアクティブマトリクス基板301A下に配置される。したがって、光源350からの光は、偏光板330、アクティブマトリクス基板301A、液晶素子E31、カラーフィルタ64、対向基板302Aおよび偏光板340を介して、ディスプレイパネル301の光取出し面である上面300aから外部へ出力される。

【0140】

ここで、第1配線レイヤ41、層間絶縁膜40、透明半導体層44および第2配線レイヤ43は、本発明の実施の形態1と同様の材料を用いて形成することができる。したがって、スイッチングトランジスタQ31および蓄積キャパシタC31も、上記と同様の材料を用いて形成することができる。また、透明基板10、コンタクト内配線42、コンタクトプラグ51および層間絶縁膜50も、本発明の実施の形態1と同様の材料を用いて形成することができる。

【0141】

カラーフィルタ64には、R,G,Bそれぞれの画素301aに応じて適切な帯域の波長を透過させるように所定の顔料が混合された感光性樹脂など、種々のフィルタ材料を用いて形成することが可能である。本実施の形態では、それぞれの画素301aに応じて所定の顔料が混合された透明感光性樹脂を用いて形成した場合を例に挙げる。

【0142】

アクティブマトリクス基板301A上の液晶素子E31において、液晶層312の母材には、例えば、エステル系、ビフェニル系、フェニルシクロヘキサン系、シクロヘキサン系、フェニルビリジミン系、または、ジオキサン系の材料など、種々の材料を用いることが可能である。液晶層312は、上記のような母材に、目的に応じた材料を混合することで形成される。

【0143】

画素電極311には、例えばZTOやITOなどのような酸化物導電体材料を用いることができる。本実施の形態では、ZTOの透明導電膜を用いた場合を例に挙げて説明する。さらに、共通電極313には、画素電極311と同様に、例えばZTOやITOなどのような酸化物導電体材料を用いることができる。本実施の形態では、ZTOの透明導電膜を用いた場合を例に挙げて説明する。

【0144】

配向膜314および315は、それぞれ、液晶層312の分子配列を一定方向へ整列させるための膜であり、液晶層312に使用した材料に応じて、適宜、例えばポリイミドなどの材料により形成される。

【0145】

誘電体突起316は、液晶層312にバイアス電圧を印加した際の液晶分子の配列方向を制御するためのものであり、例えば画素電極311の中央部と液晶層312を挟んで対向するように液晶層312上面から内部へ向けて突出して設けられている。このような誘電体突起316は、例えば感光性樹脂などの誘電体材料を用いて形成することができる。

【0146】

遮光膜321は、例えばクロム(Cr)などのような金属膜やカーボンブラックに代表される遮光性分散顔料が分散されたブラックレジストのような感光性レジスト膜を用いて形成することができる。本実施の形態では、Crを用いて形成した場合を例に挙げる。

【0147】

スペーサ317は、アクティブマトリクス基板301Aと対向基板302Aとの間における液晶が封止されるスペースを確保するための部材であり、例えば感光性樹脂などを用いて構成することができる。ただし、これに限定されるものではない。

【0148】

また、偏光板330および340は、光の進行方向に垂直であって特定の方向に強く振動する光を透過させるためのフィルタであり、例えばヨウ素(I)を吸着させたポリビニルアルコール(PVA)などの膜を用いて形成することができる。ただし、これに限定されるものではない。

【0149】

また、対向基板302Aは、例えば透明基板320よりなる。この透明基板320には、例えばガラス基板や石英基板やプラスチック基板など、種々の透明な絶縁性基板を用いることができる。なお、透明基板320としてフレキシブルな基板を用いてもよい。

【0150】

(製造方法)

次に、本実施の形態による液晶ディスプレイ装置300の製造方法を、図面を参照して詳細に説明する。図11−1および図11−2、図12−1から図12−6、ならびに図13は、本発明の実施の形態による液晶ディスプレイ装置300におけるディスプレイパネル301の製造方法を示すプロセス図である。なお、図11−1および図11−2、図12−1から図12−6、ならびに図13では、図9におけるB−B’断面と対応する断面を示す。

【0151】

本製造方法では、まず、本発明の実施の形態1において図5−1から図5−6を用いて説明した各工程と同様の工程を用いることで、スイッチングトランジスタQ31と蓄積キャパシタC31とを含むアクティブマトリクス基板301Aを製造する。

【0152】

次に、アクティブマトリクス基板301A上に、例えばスパッタリング法、CVD法などを用いてZTOを成膜し、コンタクトプラグ51と電気的な接点を備える透明なZTO膜を形成する。続いて、例えばフォトリソ法を用いて当該ZTO膜をパターニングすることで、図11−1に示すように、層間絶縁膜50上に、コンタクトプラグ51と電気的に接続された画素電極311を形成する。ただし、これに限定されず、例えばゾル・ゲル法を使用した印刷技術やインクジェットプリンティング技術などの塗布プロセス技術を用いて画素電極311を形成しても良い。

【0153】

次に、画素電極311が形成されたアクティブマトリクス基板301A上に、例えばポリイミド溶液をスピン塗布し、これを乾燥させて固化した後、例えばラビング法を用いてポリイミド膜を擦ることで、図11−2に示すように、アクティブマトリクス基板301A上に、画素電極311を覆う配向膜314を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて配向膜314を形成し、これをラビング法などで処理しても良い。

【0154】

その後、アクティブマトリクス基板301Aにおける画素301aの配列領域周囲に、液晶材の流れ出しを防止するためのシール材を形成する。なお、必要に応じて、トランスファを塗布するなど、種々の工程を行うことも可能である。

【0155】

また、本製造方法では、対向基板302A用の透明基板320を準備し、該基板の厚み方向と垂直である2つの主面のうち一方の主面(以下、これを上面とする)上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてCrを堆積させることで、遮光性を備えたクロム膜を形成する。続いて、例えばフォトリソ法を用いて当該クロム膜をパターニングすることで、図12−1に示すように、例えばアクティブマトリクス基板301A上の各画素301aを区画する領域に、ブラックマトリクスとしての遮光性を備えた遮光膜321を形成する。ただし、これに限定されず、ブラックレジストおよびフォトリソ法を使用して遮光膜321を形成しても良い。

【0156】

次に、遮光膜321が形成された対向基板302A上に、例えばR,G,Bに応じて所定の顔料が混合された感光性レジスト液をスピン塗布し、これを露光および現像する工程を繰り返すことで、図12−2に示すように、R,G,Bそれぞれの画素301aに応じて、適切な帯域の波長を透過させるカラーフィルタ64を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてR,G,Bそれぞれの画素301aごとにカラーフィルタ64を形成しても良い。なお、隣接するカラーフィルタ64間の境界面下には、例えば遮光膜321が位置する。

【0157】

次に、カラーフィルタ64が形成された対向基板302A上に、例えばスパッタリング法、CVD法などを用いてZTOを成膜することで、透明なZTO膜を形成する。続いて、例えばフォトリソ法を用いて余分なZTO膜を除去することで、図12−3に示すように、少なくとも画素(301a)の配列領域と対向する領域全体に共通電極313を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて共通電極313を形成しても良い。

【0158】

次に、共通電極313が形成された対向基板302A上に、例えばポリイミド溶液をスピン塗布し、これを乾燥させて固化した後、例えばラビング法を用いてポリイミド膜を擦ることで、図12−4に示すように、配向膜315を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて配向膜315を形成し、これをラビング法などで処理しても良い。

【0159】

次に、配向膜315が形成された対向基板302A上に、感光性レジスト液をスピン塗布し、これを露光および現像した後、形成された樹脂膜のコーナ部分を例えばポストベークの温度を上げることで、図12−5に示すように、配向膜315上に三角形状の誘電体突起316を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて所定形状の誘電体突起316を形成しても良いし、フォトリソ法でハーフトーンマスクを用いてパターンを3次元加工しても良い。

【0160】

次に、誘電体突起316が形成された対向基板302A上に、例えば感光性レジスト液をスピン塗布し、これを露光および現像することで、図12−6に示すように、対向基板302A上の各画素301aを区画する領域の少なくとも一部に、感光性樹脂よりなるスペーサ317を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてスペーサ317を形成しても良い。あるいは、球体状のスペーサを散布する方式を用いて液晶層312が封止されるスペースを確保しても良い。

【0161】

以上のように、画素電極311および配向膜314が形成されたアクティブマトリクス基板301Aと、遮光膜321、カラーフィルタ64、共通電極313、配向膜315、誘電体突起316およびスペーサ317が形成された対向基板302Aと、を製造すると、次に、対向基板302Aにおけるシール材で囲まれた領域に液晶を充填した後、図13に示すように、当該アクティブマトリクス基板301Aと対向基板302Aとを貼り合わせることで、アクティブマトリクス基板301Aと対向基板302Aとの間に液晶層312を封止する。

【0162】

次に、例えばヨウ素(I)が吸着されたポリビニルアルコール(PVA)などの偏光板330および340を用意し、これらで液晶層312を封止するアクティブマトリクス基板301Aおよび対向基板302Aをサンドウィッチするように、それぞれを貼り合わせる。これにより、図10に示す層構造を備えた画素301aを含むディスプレイパネル301が製造される。

【0163】

その後、以上のように製造したディスプレイパネル301を、信号制御部102や走査駆動部103やデータ駆動部104や容量線駆動部305やその他の部品が搭載された筐体に取り付けることで、本実施の形態による液晶ディスプレイ装置300が製造される。

【0164】

なお、以上の製造工程には、基板を洗浄する工程等が適宜含まれるが、ここでは説明の簡略化のためにこれらの工程を省略する。

【0165】

以上で説明したように、本実施の形態による液晶ディスプレイ装置300は、ブラックマトリクスとしての遮光膜321以外の層全てが光を透過する膜より構成されているため、液晶ディスプレイ装置300におけるディスプレイパネル301の開口率を大幅に向上することが可能である。なお、遮光膜321は、必要に応じて適宜形成されるものであるため、ブラックマトリクスを必要としない液晶ディスプレイ装置では、全開口型のディスプレイパネルを実現することも可能である。

【0166】

また、このように開口率が向上された構成とすることで、液晶素子E31や光源350の配置自由度が向上するため、設計自由度の大きな液晶ディスプレイ装置300を実現することが可能となる。

【0167】

さらに、本実施の形態による製造方法では、本発明の実施の形態1または2と同様に、製造過程においてコンタクト内配線42および第2配線レイヤ43等が透明半導体層44で覆われているため、後のエッチング工程などにおける各配線(42,43など)が受けるプロセスダメージを低減することが可能となる。

【0168】

なお、上記各実施の形態は本発明を実施するための例にすぎず、本発明はこれらに限定されるものではなく、仕様等に応じて種々変形することは本発明の範囲内であり、更に本発明の範囲内において、他の様々な実施の形態が可能であることは上記記載から自明である。

【符号の説明】

【0169】

10、320 透明基板

11、21、15 ゲート電極

12、22、16 ゲート絶縁膜

13、23、17 透明半導体層

14d、18d、24d ドレイン電極

14s、18s、24s ソース電極

31、35 下部電極

32、36 容量絶縁膜

33、37 上部電極

40、50 層間絶縁膜

41 第1配線レイヤ

41a 冗長配線

42 コンタクト内配線

43 第2配線レイヤ

44 透明半導体層

51 コンタクトプラグ

61 アノード電極

62 有機膜

63、65 カソード電極

64 カラーフィルタ

66 補助電極

70 隔壁

80 パッシベーション膜

100 有機ELディスプレイ装置

100a 下面

101、301 ディスプレイパネル

101A、301A アクティブマトリクス基板

101a、201a、301a 画素

200a、300a 上面

300 液晶ディスプレイ装置

302A 対向基板

311 画素電極

312 液晶層

313 共通電極

314、315 配向膜

316 誘電体突起

317 スペーサ

321 遮光膜

330、340 偏光板

C1 キャパシタ

C31 蓄積キャパシタ

D1、D2 有機発光ダイオード

E31 液晶素子

H1 コンタクト

LD データ線

LG 走査線

LP 駆動線

LC 容量線

L1、L2、L31 配線

Q1、Q31 スイッチングトランジスタ

Q2 駆動トランジスタ

RC 立体配線

【技術分野】

【0001】

本発明は、アクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法に関し、トランジスタ素子、特に薄膜トランジスタ(Thin Film Transistor:TFT)素子を含むアクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法に関する。

【背景技術】

【0002】

近年、低消費電力化、低駆動電圧化および省スペース化などが可能であることから、液晶ディスプレイ(Liquid Crystal Display:LCD)装置や有機EL(Electro Luminescence)ディスプレイ装置などに代表されるフラットパネルディスプレイ(Flat Panel Display:FPD)装置の開発が盛んに行なわれている。

【0003】

FPD装置において、例えば液晶ディスプレイ装置や有機ELディスプレイ装置などの駆動方式には、大きく分けてスタティック駆動方式とダイナミック駆動方式とがあるが、その中でもダイナミック駆動方式に分類されるアクティブマトリクス駆動方式は、画素間のクロストークを低減し、より明瞭な映像再生が可能なことから注目されている。

【0004】

アクティブマトリクス駆動方式を実現する際には、一般的に、1つ以上のスイッチング素子や容量素子などを画素ごとに備えた、いわゆるアレイ基板と称される回路基板が用いられる。本説明では、これをアクティブマトリクス基板と呼ぶ。

【0005】

例えば液晶ディスプレイ装置の場合、アクティブマトリクス基板と対向基板との間に液晶素子が設けられる。ここで、装置内の光源より発した光は、アクティブマトリクス基板と液晶素子と対向基板とを介して視認されることになるが、この際、液晶素子に適宜電圧を与えてこれの分子配列を制御することで映像としての色調、階調などが表現される。

【0006】

また、例えば有機ELディスプレイ装置の場合、アクティブマトリクス基板の主面における一方の面側に画素ごとの有機発光ダイオードが設けられる。ここで、有機発光ダイオードからの光は、アクティブマトリクス基板を介して(裏面発光型/ボトムエミッションタイプ)、または、アクティブマトリクス基板を介さずに(上面発光型/トップエミッションタイプ)視認されることになるが、この際、有機発光ダイオードに流れる電流量を制御することで映像としての色調、階調が表現される。

【0007】

以上のような構成から、アクティブマトリクス基板は、液晶ディスプレイ装置や有機ELディスプレイ装置などのFPDにおけるパネル部分の厚さを決定する重要なファクタとなっている。そこで、このアクティブマトリクス基板におけるスイッチング素子には、パネル部分の薄型化を意識して、通常、トランジスタ素子、特にTFT素子などの薄膜素子が用いられる。

【0008】

このような中、電極材料や半導体材料や絶縁膜材料などの開発により、透明なTFTを形成することが可能となってきた(例えば以下に示す非特許文献1参照)。

【先行技術文献】

【非特許文献】

【0009】

【非特許文献1】神谷利夫ら、“アモルファス酸化物半導体の設計と高性能フレキシブル薄膜トランジスタの室温形成”、第19回先端技術大賞応募論文、[online]、[平成20年4月9日検索]、インターネット<URL:http://www.fbi-award.jp/sentan/jusyou/2005/toko canon.pdf>

【発明の概要】

【発明が解決しようとする課題】

【0010】

ここで、液晶ディスプレイ装置や有機ELディスプレイ装置などの性能を決める一つのファクタとして、アクティブマトリクス基板の開口率が存在する。この開口率は、より高密度化や高いコントラスト比および輝度などを実現するための重要なファクタであり、開口率が大きければ大きいほど、高集積化や高コントラスト比や高輝度などを実現することが可能となる。

【0011】

しかしながら、上記従来の技術では、アクティブマトリクス基板におけるトランジスタ素子の透明化は可能なものの、配線部分の透明化を実現するには至っていない。配線には、液晶ディスプレイ装置や有機ELディスプレイ装置などの消費電力や駆動電圧の低減を実現するためにある程度大きな断面積が要求される。このため、配線部分が透明でないことは、従来のアクティブマトリクス基板における開口率の向上に制限を与えていた。

【0012】

そこで本発明は、上記の問題に鑑みてなされたものであり、開口率を向上することができるアクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

かかる目的を達成するために、本発明によるアクティブマトリクス基板は、複数のトランジスタ素子を備えたアクティブマトリクス基板であって、可視光を透過させることが可能な基板と、前記基板上に形成され、可視光を透過させることが可能な配線と、前記基板の垂直方向からみて前記配線の少なくとも一部と重なり、かつ可視光を透過させることが可能な半導体層と、前記配線および半導体層の少なくとも一部を覆い、可視光を透過させることが可能な絶縁膜と、を備えることを特徴としている。

【0014】

上記した本発明によるアクティブマトリクス基板は、前記配線が、主配線と、該主配線から分岐されてなり、該主配線と前記トランジスタ素子とを接続する副配線と、を含むことを特徴としている。

【0015】

上記した本発明によるアクティブマトリクス基板は、前記配線が、無機酸化物導電体材料よりなることを特徴としている。

【0016】

上記した本発明によるアクティブマトリクス基板は、前記半導体層が、無機酸化物半導体材料よりなることを特徴としている。

【0017】

上記した本発明によるアクティブマトリクス基板は、前記配線が、亜鉛錫酸化物またはインジウム含有酸化物から構成される導電体材料よりなり、前記半導体層が、前記配線よりもキャリア濃度が低く、亜鉛錫酸化物またはインジウム含有酸化物から構成される半導体材料よりなることを特徴としている。

【0018】

上記した本発明によるアクティブマトリクス基板は、前記配線の一部が、前記トランジスタ素子における電極として機能していることを特徴としている。

【0019】

上記した本発明によるアクティブマトリクス基板は、前記配線の一部が、前記トランジスタ素子におけるゲート電極、ソース電極およびドレイン電極として機能し、前記絶縁膜の一部が、前記トランジスタ素子におけるゲート絶縁膜として機能することを特徴としている。

【0020】

上記した本発明によるアクティブマトリクス基板は、第1および第2トランジスタならびにキャパシタを備え、前記配線が、1つ以上の走査線の少なくとも一部と、1つ以上のデータ線の少なくとも一部と、1つ以上の駆動線の少なくとも一部と、を構成し、前記第1トランジスタが、制御端子が前記走査線に接続され、入力端子が前記データ線に接続されており、前記第2トランジスタが、制御端子が前記第1トランジスタの出力端子に接続され、入力端子が前記駆動線に接続されており、前記キャパシタが、一方の電極が前記駆動線に接続され、他方の端子が前記第2トランジスタの制御端子に接続されていることを特徴としている。

【0021】

上記した本発明によるアクティブマトリクス基板は、第1トランジスタおよびキャパシタを備え、前記配線が、1つ以上の走査線の少なくとも一部と、1つ以上のデータ線の少なくとも一部と、1つ以上の容量線の少なくとも一部と、を構成し、前記第1トランジスタが、制御端子が前記走査線に接続され、入力端子が前記データ線に接続されており、前記キャパシタが、一方の端子が前記トランジスタの出力端子に接続されていることを特徴としている。

【0022】

また、本発明によるディスプレイパネルは、上記した本発明によるアクティブマトリクス基板と、前記アクティブマトリクス基板上に形成され、可視光を透過することが可能な第1電極と、前記第1電極上に形成された有機膜と、前記有機膜上に形成された第2電極と、を備えたことを特徴としている。

【0023】

上記した本発明によるディスプレイパネルは、前記第2電極が、可視光を透過することが可能であることを特徴としている。

【0024】

上記した本発明によるディスプレイパネルは、前記第2電極に電気的に接続された補助電極を備えたことを特徴としている。

【0025】

上記した本発明によるディスプレイパネルは、前記補助電極が、可視光を透過することが可能であることを特徴としている。

【0026】

上記した本発明によるディスプレイパネルは、前記有機膜に対して上層および/または下層に形成されたフィルタ膜を備えたことを特徴としている。

【0027】

また、本発明によるディスプレイパネルは、上記した本発明によるアクティブマトリクス基板と、可視光を透過することが可能な対向基板と、液晶層と、該液晶層をサンドウィッチする2つの配向膜と、前記液晶層と前記2つの配向膜とよりなる積層体をサンドウィッチする画素電極および共通電極と、を含む液晶素子と、を備え、前記画素電極および共通電極が、可視光を透過することが可能であり、前記画素電極が、前記アクティブマトリクス基板における前記配線と電気的に接続され、前記液晶素子が、前記アクティブマトリクス基板と前記対向基板とでサンドウィッチされていることを特徴としている。

【0028】

上記した本発明によるディスプレイパネルは、前記アクティブマトリクス基板と前記液晶素子と前記対向基板とよりなる積層体をサンドウィッチする2つの偏光板を備えたことを特徴としている。

【0029】

上記した本発明によるディスプレイパネルは、前記共通電極上に形成された遮光膜と、少なくとも前記共通電極上に形成され、所定帯域の波長を透過させるフィルタ膜と、を備えたことを特徴としている。

【0030】

また、本発明による表示装置は、上記した本発明によるディスプレイパネルを備えたことを特徴としている。

【0031】

また、本発明によるアクティブマトリクス基板の製造方法は、可視光を透過させることが可能な基板上に、トランジスタ素子を構成する電極を一部に含み、可視光を透過させることが可能な第1配線を形成する第1配線形成工程と、前記基板上に、前記第1配線の少なくとも一部を覆い、前記トランジスタ素子を構成する絶縁膜を一部に含み、可視光を透過させることが可能な第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜上に、前記トランジスタ素子を構成する電極を一部に含み、可視光を透過させることが可能な第2配線を形成する第2配線形成工程と、前記第1絶縁膜上に、前記第2配線の少なくとも一部を覆い、可視光を透過させることが可能な半導体層を形成する半導体層形成工程と、前記第1絶縁膜上に、前記半導体層および前記第2配線の少なくとも一部を覆い、可視光を透過させることが可能な第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴としている。

【0032】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記第2配線を、無機酸化物導電体材料を用いて形成することを特徴としている。

【0033】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記半導体層を、無機酸化物半導体材料を用いて形成することを特徴としている。

【0034】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記第2配線を、亜鉛錫酸化物またはインジウム含有酸化物から構成される導電体材料を用いて形成し、前記半導体層を、前記配線よりもキャリア濃度を低くすることのできる亜鉛錫酸化物またはインジウム含有酸化物から構成される半導体材料を用いて形成することを特徴としている。

【0035】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記半導体層形成工程においては、前記第1絶縁膜上に前記第2配線を覆う半導体膜を形成し、該半導体膜を前記第2配線が露出しないようにエッチングすることで、前記半導体層を形成することを特徴としている。

【0036】

上記した本発明によるアクティブマトリクス基板の製造方法は、前記第1配線形成工程、前記第1絶縁膜形成工程、前記第2配線形成工程、前記半導体層形成工程および前記第2絶縁膜形成工程のうち少なくとも一つの工程においては、印刷法またはインクジェットプリンティング法を用いて、前記第1配線、前記第1絶縁膜、前記第2配線、前記半導体層または前記第2絶縁膜を形成することを特徴としている。

【発明の効果】

【0037】

本発明によれば、アクティブマトリクス基板における配線が可視光に対して透明であるため、アクティブマトリクス基板の開口率を大幅に向上させることが可能となる。また、同様の理由により、本発明によれば、開口率が大幅に向上されたアクティブマトリクス基板を製造することが可能となる。さらに、このような本発明によるアクティブマトリクス基板を用いることで、開口率が大幅に向上されたディスプレイパネルおよび表示装置を実現することが可能となる。

【図面の簡単な説明】

【0038】

【図1】本発明の実施の形態1による有機ELディスプレイ装置の概略構成を示すブロック図である。

【図2】本発明の実施の形態1による各画素の概略回路構成を示す模式図である。

【図3】本発明の実施の形態1による各画素におけるアクティブマトリクス基板のレイアウト構造を説明するための概略平面図である。

【図4】本発明の実施の形態1による各画素における層構造を説明するための概略断面図である。

【図5−1】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その1)。

【図5−2】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その2)。

【図5−3】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その3)。

【図5−4】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その4)。

【図5−5】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その5)。

【図5−6】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その6)。

【図5−7】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その7)。

【図5−8】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その8)。

【図5−9】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その9)。

【図5−10】本発明の実施の形態1による有機ELディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その10)。

【図6】本発明の実施の形態2による各画素における層構造を説明するための概略断面図である。

【図7】本発明の実施の形態3による液晶ディスプレイ装置の概略構成を示すブロック図である。

【図8】本発明の実施の形態3による各画素の概略回路構成を示す模式図である。

【図9】本発明の実施の形態3による各画素におけるアクティブマトリクス基板のレイアウト構造を説明するための概略平面図である。

【図10】本発明の実施の形態3による各画素における層構造を説明するための概略断面図である。

【図11−1】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その1)。

【図11−2】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その2)。

【図12−1】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その3)。

【図12−2】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その4)。

【図12−3】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その5)。

【図12−4】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その6)。

【図12−5】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その7)。

【図12−6】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その8)。

【図13】本発明の実施の形態3による液晶ディスプレイ装置におけるディスプレイパネルの製造方法を示すプロセス断面図である(その9)。

【発明を実施するための形態】

【0039】

以下、本発明を実施するための最良の形態を図面を参照して詳細に説明する。なお、以下の実施の形態により本発明が限定されるものではない。また、以下の説明において、各図は本発明の内容を理解でき得る程度に形状、大きさ、および位置関係を概略的に示してあるに過ぎず、従って、本発明は各図で例示された形状、大きさ、および位置関係のみに限定されるものではない。さらに、各図では、構成の明瞭化のため、断面におけるハッチングの一部が省略されている。さらにまた、後述において例示する数値は、本発明の好適な例に過ぎず、従って、本発明は例示された数値に限定されるものではない。

【0040】

<実施の形態1>

まず、本発明の実施の形態1による表示装置として、有機ELディスプレイ装置100を例に挙げて説明する。図1は、有機ELディスプレイ装置100の概略構成を示すブロック図である。なお、本実施の形態では、発光素子(例えば図4における有機発光ダイオードD1参照)からの光を素子基板(例えば図4におけるアクティブマトリクス基板101A参照)を介してこれの下面(例えば図4における下面100a参照)から外部へ出力することが可能な、いわゆる裏面発光型(ボトムエミッションタイプ)の有機ELディスプレイ装置100を例に挙げる。

【0041】

(全体構成)

図1に示すように、有機ELディスプレイ装置100は、2次元マトリクス状に配列された画素(PX)101aを含むディスプレイパネル101と、これに接続された走査駆動部103、データ駆動部104、容量線駆動部105および駆動信号生成部106と、各部を制御するための信号制御部102と、を備える。なお、ディスプレイパネル101は、赤(R)、緑(G)および青(B)の三原色それぞれについての画素101aを備える。

【0042】

ここで、ディスプレイパネル101は、走査駆動部103に接続され、それぞれ走査信号を伝達する走査線LG1〜LGn(以下、任意の走査線をLGとする)と、データ駆動部104に接続され、それぞれデータ信号を伝達するデータ線LD1〜LDm(以下、任意のデータ線をLDとする)と、容量線駆動部105に接続され、それぞれ容量線駆動信号を伝達する容量線LC1〜LCm(以下、任意の容量線をLCとする)と、駆動信号生成部106に接続され、それぞれ駆動信号を伝達する駆動線LP1〜LPm(以下、任意の駆動線をLPとする)と、を含む。

【0043】

各走査線LG1〜LGnは図面中略行方向に延伸しており、各データ線LD1〜LDmは図面中略列方向に延伸している。したがって、走査線LG1〜LGnとデータ線LD1〜LDmとは、2次元マトリクス状に交差する。各画素101aは、この2次元マトリクスにおける交差部分にそれぞれ配置され、対応する走査線LGおよびデータ線LDに接続される。また、各容量線LC1〜LCmはデータ線LD1〜LDmと略平行に延伸しており、各交差部分に配置された画素101aに接続される。同様に、各駆動線LP1〜LPmは、データ線LD1〜LDmと略平行に延伸しており、各交差部分に配置された画素101aに接続される。本実施の形態では、走査線LGとデータ線LDと容量線LCと駆動線LPとのそれぞれにおいて、相互に交差するように行列方向に延伸する配線部分を主配線とし、この主配線から分岐して各画素101aにおけるスイッチングトランジスタQ1や駆動トランジスタQ2やキャパシタC1(例えば図2参照)等の素子に接続する配線部分を副配線とする。また、各素子間を接続する配線(L1,L2等)を副配線とする。

【0044】

信号制御部102は、外部から入力されたビデオ信号R,G,Bおよびその表示を制御するための入力制御信号(データイネーブル信号DE,水平同期信号Hsync,垂直同期信号Vsync,メインクロックMCLKなど)に基づき、映像再生を制御するための走査制御信号CONT1、データ制御信号CONT2、容量線制御信号CONT3、発光制御信号CONT4およびビデオデータ信号DAT等を生成する。

【0045】

生成された走査制御信号CONT1は、走査駆動部103に入力される。走査制御信号CONT1は、後述するゲートオン電圧Vonの出力開始を指示する垂直同期開始信号やゲートオン電圧Vonの出力タイミングを制御するゲートクロック信号やゲートオン電圧Vonの出力期間を制御する出力イネーブル信号などを含む。また、走査駆動部103には、各画素101aに含まれるスイッチングトランジスタQ1(図2参照)をオン・オフさせるためのゲートオン電圧Vonおよびゲートオフ電圧Voffも入力される。走査駆動部103は、走査制御信号CONT1に従ってゲートオン電圧Vonおよびゲートオフ電圧Voffから走査信号を生成し、これを走査線LGに入力する。

【0046】

また、データ制御信号CONT2およびビデオデータ信号DATは、データ駆動部104に入力される。データ制御信号CONT2は、ビデオデータ信号DATの入力開始を指示する水平同期開始信号やデータ線LDにデータ信号を入力するためのロード信号などを含む。データ駆動部104は、データ制御信号CONT2に従って、受信したビデオデータ信号DATをラッチさせた後、適宜、ビデオデータ信号DATに対応したデータ信号を生成して、これをデータ線LDに入力する。

【0047】

また、容量線制御信号CONT3は、容量線駆動部105に入力される。容量線制御信号CONT3は、容量線LC駆動用の容量線駆動信号を生成するための信号である。容量線駆動部105は、容量線制御信号CONT3に従って容量線LCを駆動するための容量線駆動信号を生成し、これを容量線LCに入力する。

【0048】

また、発光制御信号CONT4は、駆動信号生成部106に入力される。発光制御信号CONT4は、有機発光ダイオードD1(図2参照)駆動用の駆動信号を生成するための信号である。駆動信号生成部106は、発光制御信号CONT4に従って有機発光ダイオードD1を発光/非発光させるための駆動信号を生成し、これを駆動線LPに入力する。

【0049】

なお、駆動信号は、後述する有機発光ダイオードD1のアノードに入力される。また、有機発光ダイオードD1のカソードには共通電圧Vcomが入力される(図2参照)。そこで、本実施の形態では、有機発光ダイオードD1を発光させる期間の駆動信号の電圧レベルを共通電圧Vcomの電圧レベルよりも高くし、それ以外の期間における駆動信号の電圧レベルを共通電圧Vcomと同じかそれよりも低くすることで、有機発光ダイオードD1の発光/非発光を制御する。ここで、共通電圧Vcomは、例えば接地電位とすることができる。また、駆動線LPの代りに電源線を用いてもよい。この場合、駆動信号生成部106は省略され、電源線に電源電圧が印加される。

【0050】

(画素構成)

次に、図2を用いて各画素101aの概略構成およびその動作を説明する。なお、以下の説明は、R,G,Bのうち何れの画素101aについても同様である。

【0051】

図2は、画素101aの概略回路構成を示す模式図である。図2に示すように、画素101aは、スイッチングトランジスタQ1と、駆動トランジスタQ2と、キャパシタC1と、有機発光ダイオードD1と、を含む。

【0052】

スイッチングトランジスタQ1は例えばn型のTFTであり、そのソースSは例えばノードN4においてデータ線LDの主配線から分岐する副配線に接続され、ドレインDはノードN1を含む配線L1を介して駆動トランジスタQ2のゲートGに接続される。また、スイッチングトランジスタQ1のゲートGは、例えばノードN3において走査線LGの主配線から分岐する副配線に接続される。したがって、スイッチングトランジスタQ1は、走査信号の電圧レベルVg(走査制御電圧)に従ってデータ線LDおよびノードN1間を導通/遮断する。

【0053】

配線L1には、例えばノードN1において分岐する配線部分(これも配線L1に含む)を介してキャパシタC1の一方の端子が接続される。キャパシタC1の他方の端子は、例えばノードN5において容量線LCの主配線から分岐する副配線に接続される。容量線LCには、上述した容量線駆動部105から容量線駆動信号が与えられる。この容量線駆動信号の電圧レベルVc(容量線駆動電圧)は、例えば接地電位とすることができる。言い換えれば、容量線LCは、接地線とすることができる。この場合、容量線駆動部105を省略することができる。

【0054】

ここで、走査線LGに入力された走査信号の電圧レベルVg(走査制御電圧)がハイレベルになると、スイッチングトランジスタQ1がオン状態となり、当該スイッチングトランジスタQ1を介して駆動トランジスタQ2のゲートGにデータ信号の電圧レベルVd(データ駆動電圧)に応じた電荷が注入される。この結果、駆動トランジスタQ2がオン状態となり、ノードN3および有機発光ダイオードD1間が導通する。

【0055】

ここで、キャパシタC1は、走査線LGの電圧レベルVgがローレベルとなってスイッチングトランジスタQ1が完全にオフ状態となった後から次に電圧レベルVgがハイレベルになってスイッチングトランジスタQ1がオン状態となると共に次のデータ信号が入力されるまでの間、駆動トランジスタQ2におけるゲートGの電位を維持する働きをする。すなわち、キャパシタC1は、所定の期間、データ線LDに入力されたデータを保持する。

【0056】

駆動トランジスタQ2は例えばn型のTFTであり、そのドレインDは例えばノードN6において駆動線LPの主配線から分岐する副配線に接続され、ソースSはノードN2を介して有機発光ダイオードD1のアノードに接続される。なお、有機発光ダイオードD1のカソードには、共通電圧Vcom(例えば接地電位GND)が印加される。したがって、駆動トランジスタQ2がオン状態となり、アノードに電源電圧VDDが印加されると、有機発光ダイオードD1に電流Iが流れるため、有機発光ダイオードD1が電流Iの電流量に応じた輝度で発光する。一方、駆動トランジスタQ2がオフ状態の際には有機発光ダイオードD1には電流が流れないため、発光は生じない。

【0057】

次に、図3および図4を用いて、各画素101aのレイアウト構造および層構造を詳細に説明する。図3は、画素101aにおけるアクティブマトリクス基板101A(例えば図4参照)のレイアウト構造を説明するための概略平面図である。また、図4は、画素101aの層構造を説明するための概略断面図である。なお、図3では、説明の簡略化のため、透明基板10、層間絶縁膜40および50などの構成(例えば図4参照)を省略する。また、図4には、図3のA−A’断面に対応する面における画素101aの概略層構造を示す。さらに、以下の説明では、説明の明確化のため、同一レイヤにおける同種の膜に同一の符号を付す。

【0058】

図3または図4に示すように、画素101aは、アレイ基板としてのアクティブマトリクス基板101A(例えば図4参照)と、アクティブマトリクス基板101A上の有機発光ダイオードD1(例えば図4参照)と、を備える。アクティブマトリクス基板101Aは、例えば、走査線LGと、データ線LDと、容量線LCと、駆動線LPと、配線L1およびL2と、スイッチングトランジスタQ1と、駆動トランジスタQ2と、キャパシタC1と、を含む。有機発光ダイオードD1は、アノード電極61およびカソード電極63にサンドウィッチされた有機膜62を含み、例えば配線L2を介して駆動トランジスタQ2のソース電極24sに接続される。なお、有機発光ダイオードD1に対して光の取り出し側にカラーフィルタを設けてもよい。

【0059】

走査線LGは、例えば、透明基板10上の第1配線レイヤ41から構成される(例えば図3参照)。データ線LD、容量線LCおよび駆動線LPは、それぞれ例えば、透明基板10上の第1配線レイヤ41および層間絶縁膜40上の第2配線レイヤ43と、層間絶縁膜40に形成されたコンタクト内のコンタクト内配線42と、隣接する画素101a間における第1配線レイヤ41を接続するためのコンタクト内配線42および第2配線レイヤ43よりなる立体配線RCと、から構成される。配線L1およびL2は、それぞれ例えば、透明基板10上の第1配線レイヤ41および層間絶縁膜40上の第2配線レイヤ43と、層間絶縁膜40に形成されたコンタクトホール内のコンタクト内配線42と、から構成される。また、配線L2には、例えば、駆動トランジスタQ2のソース電極24sに接続された第1配線レイヤ41を有機発光ダイオードD1のアノード電極61へ電気的に接続するためのコンタクトプラグ51も含まれる。さらに、図2に示す各ノードN1〜N6は、それぞれ例えば図3に示す各位置に定義することができる。

【0060】

第1配線レイヤ41において、略行方向または略列方向に延伸する部分は、それぞれ走査線LG、データ線LD、容量線LCまたは駆動線LPにおける主配線部分に相当する。また、主配線部分から分岐して当該主配線と各画素101aにおける素子(Q1、Q2、C1等)とを接続するための副配線部分に相当する。

【0061】

コンタクト内配線42および第2配線レイヤ43は、例えばデータ線LD、容量線LCまたは駆動線LPを層間絶縁膜40上に導くための配線、または、各配線(LD、LC、LP等)と略垂直方向に延伸する走査線LGを跨いで各配線(LD、LC、LP等)における主配線間を電気的に接続させるための立体配線RCである。なお、本実施の形態では、コンタクト内配線42および第2配線レイヤ43において、各配線(LD、LC、LP等)を層間絶縁膜40上に導く部分は副配線部分に含まれ、走査線LGを跨ぐための部分は主配線部分に含まれる。

【0062】

このように、層間絶縁膜40(例えば図4参照)内に形成されたコンタクト内配線42を用いて層間絶縁膜40下の第1配線レイヤ41と層間絶縁膜40上の第2配線レイヤ43とを電気的に接続することで、各信号線(LG、LD、LC、LP等)を立体交差させることが可能になる。これにより、各配線(LG、LD、LC、LP等)の多くの領域を単一の層(本実施の形態で透明基板10上の層)に形成することが可能となるため、アクティブマトリクス基板101Aにおける層構造の簡略化や配線レイアウトの明確化などが可能になると共に、上層に形成する膜上面の平坦性を高めることが可能となる。

【0063】

また、透明基板10上において、各種配線(LG、LD、LC、LP、L1、L2等)および各種素子(Q1、Q2、C1等)が形成されない領域には、例えば第1配線レイヤ41の一部が冗長された冗長配線41a(例えば図3参照)が形成されることで、透明基板10上に形成される層上面の平坦性が向上されている。

【0064】

スイッチングトランジスタQ1は、例えば、透明基板10上のゲート電極11と、ゲート電極11を覆うゲート絶縁膜12と、ゲート絶縁膜12上におけるソース電極14sおよびドレイン電極14dと、ソース電極14sおよびドレイン電極14d間におけるゲート絶縁膜12上の透明半導体層13と、よりなる、いわゆるボトムゲート構造の薄膜トランジスタ(TFT)である(例えば図4参照)。

【0065】

ゲート電極11には、例えば走査線LGを構成する第1配線レイヤ41の一部を使用することができる。ゲート絶縁膜12には、例えば層間絶縁膜40の一部を使用することができる。透明半導体層13には、例えば透明半導体層44の一部を使用することができる。ソース電極14sには、例えばデータ線LDの一部を構成する第2配線レイヤ43の一部を使用することができる。ドレイン電極14dには、例えば配線L1の一部を構成する第2配線レイヤ43の一部を使用することができる。ただし、本発明はこれに限定されず、例えば、ゲート電極11に第2配線レイヤ43の一部を使用し、ソース電極14sおよびドレイン電極14dにそれぞれ第1配線レイヤ41の一部を使用した、いわゆるトップゲート構造の薄膜トランジスタ(TFT)としてもよい。

【0066】

同様に、駆動トランジスタQ2は、例えば、透明電極10上のゲート電極21と、ゲート電極21を覆うゲート絶縁膜22と、ゲート絶縁膜22上におけるソース電極24sおよびドレイン電極24dと、ドレイン電極24dおよびソース電極24s間におけるゲート絶縁膜22上の透明半導体層23と、よりなる、いわゆるボトムゲート構造の薄膜トランジスタ(TFT)である(例えば図4参照)。

【0067】

ゲート電極21には、例えば配線L1の一部を構成する第1配線レイヤ41の一部を使用することができる。ゲート絶縁膜22には、例えば層間絶縁膜40の一部を使用することができる。透明半導体層23には、例えば透明半導体層44の一部を使用することができる。ドレイン電極24dには、例えば駆動線LPの一部を構成する第2配線レイヤ43の一部を使用することができる。ソース電極24sには、例えば配線L2の一部を構成する第2配線レイヤ43の一部を使用することができる。ただし、本発明はこれに限定されず、例えば、ゲート電極21に第2配線レイヤ43の一部を使用し、ドレイン電極24dおよびソース電極24sにそれぞれ第1配線レイヤ41の一部を使用した、いわゆるトップゲート構造のTFTとしてもよい。

【0068】

なお、本実施の形態によるアクティブマトリクス基板101Aは、トランジスタ素子としてのTFTを備える、いわゆるアレイ基板と称されるものである。

【0069】

キャパシタC1は、例えば、透明基板10上の下部電極31と、下部電極31上の上部電極33と、下部電極31および上部電極33間の容量絶縁膜32と、よりなる(例えば図4参照)。下部電極31には、例えば容量線LCの一部を構成する第1配線レイヤ41の一部を使用することができる。容量絶縁膜32には、例えば層間絶縁膜40の一部を使用することができる。上部電極33には、例えば駆動線LPを構成する第2配線レイヤ43の一部を使用することができる。

【0070】

また、アクティブマトリクス基板101A上の有機発光ダイオードD1は、例えば、アノード電極61と、アノード電極61上の有機膜62と、有機膜62上のカソード電極63と、よりなる(例えば図4参照)。なお、有機発光ダイオードD1に対して光を取り出す側の層には、カラーフィルタや波長シフタなどの色変換膜を配置しても良い。

【0071】

隣接する画素101a間には、例えば、アノード電極61と有機膜62とを画素ごとに区画するための隔壁70が形成される(例えば図4参照)。層間絶縁膜50上には、有機発光ダイオードD1および下層の各素子ならびに各配線を保護するためのパッシベーション膜80が形成される(例えば図4参照)。

【0072】

ここで、透明基板10には、ガラス基板を用いることができる。ただし、これに限定されず、例えばガラス基板や石英基板やプラスチック基板など、種々の透明な絶縁性基板を用いることができる。また、透明基板10としてフレキシブルな基板を用いることで、フレキシブルな有機ELディスプレイ装置100を実現することも可能である。なお、本発明において透明とは、少なくとも可視光の帯域に含まれる波長の光に対して透明または半透明であることを意味する。

【0073】

第1配線レイヤ41、コンタクト内配線42および第2配線レイヤ43、ならびに、コンタクトプラグ51は、亜鉛錫酸化物(Zinc Tin Oxide:ZTO)を主成分とした導電体材料を用いて形成される。ただし、これに限定されず、例えばインジウム含有酸化物(Indium Tin Oxide:ITO、Indium Zinc Oxide:IZOなど)やその他の無機酸化物導電体材料、あるいは、有機物材料などで、透明導電性膜を得ることのできる導電体材料を用いて形成することもできる。なお、ZTO材料は、例えば、Zn(モル)よりもSn(モル)の量を多くすることにより(例えば、Zn:Snのモル比が1:2など)、導電体材料としての使用が可能である。また、導電体材料としてのITOは通常In:Snのモル比が0.9:0.1程度、導電体材料としてのIZOは通常In:Znのモル比が0.9:0.1程度である。

【0074】

特に、ZTO導電性膜は、アモルファスな膜として形成することが可能なため、フレキシブルな第1配線レイヤ41、第2配線レイヤ43、コンタクト内配線42およびコンタクトプラグ51を実現することが可能であるという利点を備える。さらに、アモルファスなZTO導電性膜は、低温形成することが可能であるため、例えばプラスチック基板などの高温耐性の低い基板を透明基板10として用いた場合でも、容易に形成することが可能であるという利点も備える。これらのことから、ZTO導電性膜を用いて第1配線レイヤ41、第2配線レイヤ43、コンタクト内配線42およびコンタクトプラグ51を形成することは、フレキシブルな有機ELディスプレイ装置100を形成する際に好適であると言える。

【0075】

層間絶縁膜40および50には、例えばSOG(Spin ON Glass)や酸化シリコン(SiO2)や窒化シリコン(SiNX)などのシリコン系絶縁物やアルミナ(Al2O3)等のアルミニウム酸化物やハフニア(HfO2)等のハフニウム酸化物やイットリア(Y2O3)などのイットリウム酸化物やLa2O3等のランタン酸化物など、あるいは、透明な感光性樹脂などのような塗布プロセスによる成膜が可能な絶縁物よりなる透明な絶縁性単層膜、または、これらを1つ以上含む透明な絶縁性多層膜を用いることができる。本実施の形態では、層間絶縁膜40を例えばアルミナ(Al2O3)膜とハフニア(HfO2)膜とを含む多層構造の絶縁膜で形成し、層間絶縁膜50を例えば感光性樹脂よりなる単層構造の絶縁膜で形成する。なお、本実施の形態において、層間絶縁膜40および50は、各層間を絶縁するための絶縁膜として機能するほか、各層の平坦性を確保するための平坦化膜としても機能することができる。

【0076】

層間絶縁膜40上には、第2配線レイヤ43およびコンタクト内配線42を覆うように透明半導体層44が形成される。透明半導体層44は、後述する製造工程における例えばエッチング工程時に下層に位置する第2配線レイヤ43やコンタクト内配線42などが受けるプロセスダメージを低減するための保護膜として機能する。本実施の形態では、透明半導体層44の例として、前記の導電体材料(ZTO導電体材料、インジウム含有酸化物導電体材料)よりなる配線よりも、キャリア濃度を低くすることのできる半導体材料で、ZTOまたはインジウム含有酸化物から構成される半導体材料よりなる透明半導体層を用いる。なお、ZTO材料は、例えば、Sn(モル)よりもZn(モル)の量を多くすることにより(例えば、Zn:Snのモル比が2:1など)、半導体材料としての使用が可能である。また、このZTO半導体層の成膜時には、雰囲気の酸素濃度を増やすなどして、半導体層のキャリア濃度を低くする調整を行うことができる。また、上述した第1配線レイヤ41等と同様に、ZTO透明半導体層も、アモルファスな膜として形成できることから、フレキシブルな透明半導体層44を実現することが可能となり、フレキシブルな有機ELディスプレイ装置100を形成する際に好適である。また、本発明はこのようなZTO半導体材料に限定されず、インジウム含有酸化物半導体材料(例えば、In:Znのモル比が4:6のIZOなど)などの透明無機酸化物半導体材料や、この他、ペンタセンやテトラベンゾポルフィリンの前駆体などを含む透明有機半導体材料など、種々の透明半導体材料を用いて形成することができる。

【0077】

なお、本実施の形態では、透明半導体層44を形成する導電体材料の主成分と、各素子においてこの透明電極と接触する電極部分を形成する導電体材料の主成分と、に同種の材料を用いる。したがって、本実施の形態では、ソース電極14sおよびドレイン電極14dならびにソース電極24sおよびドレイン電極24dを含む第2配線レイヤ43がZTOを主成分とするZTO導電性膜で形成され、透明半導体層44がZTOを主成分とし、キャリア濃度が第2配線レイヤ43のそれよりも低いZTO半導体膜で形成される。このように、両者を同種の材料で形成することで、例えばスイッチングトランジスタQ1におけるソース電極14sまたはドレイン電極14dと透明半導体層13とをオーミック接触させることが可能となる。同様に、駆動トランジスタQ2におけるドレイン電極24dまたはソース電極24sと透明半導体層23とをオーミック接触させることが可能となる。これにより、各TFT素子(Q1,Q2など)における抵抗成分が低減されるため、各TFT素子の駆動電力を低減することが可能となり、結果的に有機ELディスプレイ装置100の消費電力を低減することが可能となる。

【0078】

隔壁70は、例えば感光性樹脂よりなる単層構造の絶縁膜で形成することができる。ただし、これに限定されず、例えばSOGやSiO2SiNXなどのシリコン系絶縁物やAl2O3等のアルミニウム酸化物やHfO2等のハフニウム酸化物やY2O3などのイットリウム酸化物やLa2O3等のランタン酸化物など、あるいは、透明な感光性樹脂などのような塗布プロセスによる成膜が可能な絶縁物よりなる透明な絶縁性単層膜、または、これらを1つ以上含む透明な絶縁性多層膜を用いることができる。

【0079】

また、スイッチングトランジスタQ1、駆動トランジスタQ2およびキャパシタC1は、上述した第1配線レイヤ41、第2配線レイヤ43および層間絶縁膜40の一部を使用して構成することが可能であるため、その材料も上述したものと同様とすることができる。ただし、各電極上にこれを低抵抗化するための透明な導電性膜を形成するなど、適宜変形することも可能である。

【0080】

また、有機発光ダイオードD1において、有機膜62は、例えば、正孔注入層、正孔輸送層、有機発光層、電子輸送層、電子注入層および正孔障壁層を含んだ多層構造の積層膜である。有機膜62において、有機発光層のホスト材料には、ポリフルオレン、その誘導体および共重合体、ポリアリーレン、その誘導体および共重合体、ポリアリーレンビニレン、その誘導体および共重合体やポリアリールアミン、その誘導体および共重合体などのような高分子材料や、その他、蛍光性もしくは燐光性の種々の低分子発光材料または高分子材料など、正孔輸送層等との組合せやターゲット波長等に応じて種々の発光材料を用いることができる。

【0081】

光取出し側に配置されるアノード電極61には、例えばZTOやITOなどのような酸化物導電体材料、あるいは、銀(Ag)やアルミニウム(Al)などの金属材料よりなる透明単層膜、もしくは、これらを含む多層構造の透明積層膜を用いることができる。なお、金属材料を用いた場合、これを含む層は、光を透過させる程度の薄い膜とされる。本実施の形態では、ZTO/Ag/ZTOの積層膜を用い、その中のAg膜を光が透過する程度の薄膜で形成した場合を例に挙げる。さらに、カソード電極63には、例えば銀(Ag)やアルミニウム(Al)やマグネシウム(Mg)などのような高い導電性と反射率とを兼ね備えた金属あるいは合金などの導電体材料を用いて得ることができる。本実施の形態では、MgとAgとの合金膜を用いた場合を例に挙げる。

【0082】

パッシベーション膜80は、例えばCVD法で成膜されたSiO2膜やSiNx膜等の多層膜を用いて形成することが可能である。本実施の形態では、SiO2膜やSiNx膜の多層膜を使用した場合を例に挙げる。

【0083】

以上から明らかなように、本実施の形態による有機ELディスプレイ装置100は、有機膜62に対して光取出し側である下面100a側に位置する層のすべてが光を透過する透明膜あるいは半透明膜で形成されているため、光取出し面である下面100aの全領域が開口された、いわゆる全開口型の有機ELディスプレイ装置100を実現することが可能となる。

【0084】

(製造方法)

次に、本実施の形態による有機ELディスプレイ装置100の製造方法を、図面を参照して詳細に説明する。図5−1から図5−10は、本実施の形態による有機ELディスプレイ装置100におけるディスプレイパネル101の製造方法を示すプロセス断面図である。なお、図5−1から図5−10では、図4に示すA−A’断面と対応する断面を示す。

【0085】

本製造方法では、まず、透明基板10を準備し、該基板の厚み方向(基板に対して垂直方向)と垂直な面である2つの主面のうち一方の主面(以下、これを上面とする)上に、例えばスパッタリング法、CVD(Chemical Vapor Deposition)法または真空蒸着法などを用いてZTOを堆積することで、透明なアモルファス状のZTO導電性膜を形成する。続いて、例えばフォトリソ法を用いて当該ZTO導電性膜をパターニングすることで、図5−1に示すように、透明基板10上に、ゲート電極11および21、下部電極31、第1配線レイヤ41ならびに冗長配線41a(図3参照)等を形成する(第1配線形成工程)。ただし、これに限定されず、例えばゾル・ゲル法を使用した印刷技術やインクジェットプリンティング技術などのような塗布プロセス技術などを用いてゲート電極11および21、下部電極31、第1配線レイヤ41ならびに冗長配線41a等を形成しても良い。

【0086】

次に、各電極および配線(11、21、31、41、41a等)が形成された透明基板10上面上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてアルミナ(Al2O3)とハフニア(HfO2)とを順次堆積することで、透明な絶縁性積層膜よりなる層間絶縁膜40を形成する(第1層間絶縁膜形成工程)。続いて、例えばフォトリソ法を用いて当該層間絶縁膜40をパターニングすることで、図5−2に示すように、層間絶縁膜40内に、第1配線レイヤ41の一部を露出させるコンタクトホールap1およびap2を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてコンタクトホールap1およびap2を備えた層間絶縁膜40を形成しても良い。なお、本工程で形成された層間絶縁膜40の内、少なくともゲート電極11上の層間絶縁膜40は、スイッチングトランジスタQ1のゲート絶縁膜12として機能し、少なくともゲート電極21上の層間絶縁膜40は、駆動トランジスタQ2のゲート絶縁膜22として機能し、少なくとも下部電極31上の層間絶縁膜40は、キャパシタC1の容量絶縁膜32として機能する。さらに、コンタクトホールap2は、後の工程において第1配線レイヤ41と電気的に接続されたコンタクトプラグ51の一部を形成するためのコンタクトホールである。

【0087】

次に、コンタクトホールap1およびap2が形成された層間絶縁膜40上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOを堆積することで、透明なアモルファス状のZTO導電性膜を形成する。この際、コンタクトホールap2内にZTO導電性膜が形成されてもよい。続いて、例えばフォトリソ法を用いて当該ZTO導電性膜をパターニングすることで、図5−3に示すように、層間絶縁膜40上に、ソース電極14sおよびドレイン電極14d、ドレイン電極24dおよびソース電極24s、上部電極33、ならびに第2配線レイヤ43等を形成すると共に、層間絶縁膜40のコンタクトホールap1内に第1配線レイヤ41と電気的に接続されたコンタクト内配線42を形成する(第2配線形成工程)。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてソース電極14sおよびドレイン電極14d、ドレイン電極24d、ソース電極24s、上部電極33、コンタクト内配線42および第2配線レイヤ43を形成しても良い。なお、この工程では、コンタクトホールap2内のZTO導電性膜が完全に除去されなくともよい。

【0088】

次に、各電極および配線(14s、14d、24d、24s、33、42、43等)が形成された層間絶縁膜40上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOを堆積することで、キャリア濃度が、ZTO導電性膜のそれよりも低いZTO半導体膜を形成する(半導体層形成工程)。この際、コンタクトホールap2内にZTO半導体膜が形成されてもよい。なお、上述したように、ZnとSnのモル比を制御することなどにより、ZTO半導体膜は、そのキャリア濃度が第1配線レイヤ41や第2配線レイヤ43等を構成するZTO導電性膜よりも低い、透明な半導体膜とすることが可能である。続いて、例えばフォトリソ法を用いて当該ZTO半導体膜をパターニングすることで、図5−4に示すように、層間絶縁膜40上に、各電極および配線(14s、14d、24d、24s、33、42、43等)を覆う透明半導体層44を形成する。この際、コンタクトホールap2内のZTO半導体膜が完全に除去される程度にオーバエッチングされることが好ましい。なお、形成された透明半導体層44の内、少なくともソース電極14sおよびドレイン電極14d間の透明半導体層44は、スイッチングトランジスタQ1のチャネル形成層として機能する透明半導体層13として機能し、少なくともドレイン電極24dおよびソース電極24s間の透明半導体層44は、駆動トランジスタQ2のチャネル形成層として機能する透明半導体層23として機能する。

【0089】

ここで本実施の形態では、透明半導体層44と第2配線レイヤ43およびコンタクト内配線42とが同種の材料を用いて形成されているため、透明半導体層44と第2配線レイヤ43等とのエッチングにおける選択比を得ることは困難である。そこで本実施の形態のように、パターニング後の透明半導体層44が第2配線レイヤ43およびコンタクト内配線42を覆うように構成することで、エッチング中に第2配線レイヤ43およびコンタクト内配線42がエッチング雰囲気中に曝されることが無いため、第2配線レイヤ43等との選択比を考慮することなく、透明半導体層44をパターニングすることが可能となる。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて透明半導体層44を形成しても良い。この場合、形成した透明半導体層をエッチングなどによりパターニングする必要が無くなるため、透明半導体層44は必ずしも第2配線レイヤ43およびコンタクト内配線42を覆っていなくとも良い。

【0090】

以上のように透明半導体層(13、23、44等)を形成すると、次に、透明半導体層(13、23、44等)が形成された層間絶縁膜40上に、例えば感光性レジスト液をスピン塗布し、これを露光および現像することで、図5−5に示すように、層間絶縁膜40のコンタクトホールap2と連続するコンタクトホールap3を備え、透明な感光性樹脂よりなる層間絶縁膜50を形成する(第2層間絶縁膜形成工程)。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてコンタクトホールap3を備えた層間絶縁膜50を形成しても良い。

【0091】

次に、コンタクトホールap3が形成された層間絶縁膜50上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOを堆積することで、図5−6に示すように、少なくとも層間絶縁膜50のコンタクトホールap3内および層間絶縁膜40のコンタクトホールap2内に第1配線レイヤ41と電気的に接続された透明なアモルファス状のコンタクトプラグ51を形成する。なお、この際に形成される層間絶縁膜50上の不要なZTO導電性膜は、例えばエッチバックなどの技術などを用いて除去される。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて層間絶縁膜40および50内にコンタクトプラグ51を形成しても良い。

【0092】

これまでに説明した工程を経ることで、本実施の形態では、いわゆるアレイ基板としてのアクティブマトリクス基板101Aが製造される。

【0093】

次に、アクティブマトリクス基板101A上に、例えばスパッタリング法、CVD法または真空蒸着法などを用いてZTOとAgとZTOとを順次堆積することで、コンタクトプラグ51と電気的な接点を備える透明なZTO/Ag/ZTO積層膜を形成する。続いて、例えばフォトリソ法を用いて当該ZTO/Ag/ZTO積層膜をパターニングすることで、図5−7に示すように、層間絶縁膜50上に、コンタクトプラグ51と電気的に接続されたアノード電極61を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてアノード電極61を形成しても良い。

【0094】

次に、アノード電極61が形成されたアクティブマトリクス基板101A上に、例えば感光性レジスト液をスピン塗布し、これを露光および現像することで、図5−8に示すように、アクティブマトリクス基板101A上の各画素101aを区画する領域に、透明な感光性樹脂よりなる隔壁70を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いて隔壁70を形成しても良い。

【0095】

次に、少なくともアノード電極61上に、例えば既存の成膜技術を用いて正孔注入層、正孔輸送層、有機発光層、電子輸送層、電子注入層および正孔障壁層を順次積層形成することで、図5−9に示すように、有機膜62を隔壁70により区画されたアノード電極61上に形成する。なお、有機膜62において、例えば正孔注入層と正孔輸送層と電子輸送層と電子注入層と正孔障壁層とは、例えば高分子ポリマー溶液を使用した印刷技術やインクジェットプリンティング技術などのような塗布プロセスを用いて形成することが可能である。ただし、これに限定されず、例えば真空蒸着法に代表されるシャドウマスク蒸着法や転写法に代表されるレーザー熱転写法(LITI法)、レーザー再蒸着法(RIST法、LIPS法)などを用いて正孔注入層、正孔輸送層、有機発光層、電子輸送層、電子注入層および正孔障壁層を順次成膜することで、画素101aに応じた有機膜62を形成しても良い。また、アノード電極61に例えばITO/PEDOT(3,4−エチレンジオキシチオフェン):PSS(Polystyrenesulfonate)などのような無機酸化物導電性膜と導電性高分子ポリマー膜との積層膜を用いた場合、有機膜62を下層から例えば正孔注入層/有機発光層/電子注入層の積層膜とすることが可能である。

【0096】

次に、有機膜62および隔壁70が形成されたアクティブマトリクス基板101A上全体に、例えば真空蒸着法などを用いてMgとAgとの合金材料を堆積することで、導電性を有する合金膜を形成する。この時、シャドウマスク法を用いて所望の領域以外に余分な合金膜が蒸着されることを防止することで、図5−10に示すように、少なくとも画素(101a)の配列領域全体にカソード電極63を形成する。ただし、これに限定されず、例えば上述のような塗布プロセス技術などを用いてカソード電極63を形成しても良い。

【0097】

次に、隔壁70により区画されたアノード電極61および有機膜62とカソード電極63とよりなる有機発光ダイオードD1が形成されたアクティブマトリクス基板101A上面全体に、CVD法などを用いてSiO2およびSiNxの多層膜を形成することにより、下層の各素子(Q1、Q2、C1、D1等)および配線(LG、LD、LP、L1、L2等)を保護するパッシベーション膜80を形成する。そして、最後にその上面である基板101Aとは反対側に基板を貼り付けて封止したり、もしくは、スパッタリング法やCVD法により膜を形成して封止を行う。以上の工程を経ることで、図4に示す層構造を備えた画素101aを含むディスプレイパネル101が製造される。このとき、基板101Aとは反対側の基板は、ガラス、PET等に代表される透明ポリマーフィルム、スパッタリング法やCVD法などでフィルムのバリア性を高めるために有機膜と無機膜とを交互に積層した封止膜などが挙げられる。

【0098】

その後、以上のように製造したディスプレイパネル101を、信号制御部102や走査駆動部103やデータ駆動部104や容量線駆動部105や駆動信号生成部106やその他の部品が搭載された筐体に取り付けることで、本実施の形態による有機ELディスプレイ装置100が製造される。

【0099】

なお、以上の製造工程には、基板を洗浄する工程等が適宜含まれるが、ここでは説明の簡略化のためにこれらの工程を省略する。

【0100】

以上で説明したように、本実施の形態による有機ELディスプレイ装置100は、有機膜62に対して光取出し側である下面100a側にある層すべてが光を透過する膜より構成されているため、光取出し面が全て開口された、いわゆる全開口の裏面発光型有機ELディスプレイ装置100が実現できる。

【0101】

また、このように光取出し面全てが開口された構成とすることで、発光素子(本実施の形態では有機発光ダイオードD1)の配置を自由に設計することが可能となるため、設計自由度の大きな有機ELディスプレイ装置100を実現することが可能となる。

【0102】

さらに、本実施の形態による製造方法では、製造過程においてコンタクト内配線42および第2配線レイヤ43等が透明半導体層44で覆われているため、後のエッチング工程などにおける各配線(42,43など)が受けるプロセスダメージを低減することが可能となる。

【0103】

さらにまた、上記した実施の形態において、有機ELディスプレイ装置100を構成する各層をフレキシブルな材料を用いて形成していてもよい。

【0104】

なお、上記した本発明の実施の形態1では、発光層(本実施の形態では有機膜62)が有機材料で形成された有機ELディスプレイ装置100を例に挙げて説明したが、本発明はこれに限定されず、例えば発光層が無機材料で形成された無機ELディスプレイ装置とすることも可能である。

【0105】

<実施の形態2>

次に、本発明の実施の形態2による表示装置として、有機ELディスプレイ装置を例に挙げて説明する。なお、本実施の形態では、発光素子(例えば図6における有機発光ダイオードD2参照)からの光をディスプレイパネル101の上面(例えば図6における上面200a参照)および下面(例えば図6における下面100a参照)の両方から外部へ出力することが可能な有機ELディスプレイ装置を例に挙げる。すなわち、本実施の形態による有機ELディスプレイ装置は、上面発光型(トップエミッションタイプ)と裏面発光型との両方を兼ね備えた、いわゆる両面発光型の有機ELディスプレイ装置である。また、以下の説明において、本発明の実施の形態1と同様の構成については、説明の明確化のために、同一の符号を付し、その詳細な説明を省略する。

【0106】

本実施の形態による有機ELディスプレイ装置の概略ブロック構成は、図1に示す有機ELディスプレイ装置100の概略ブロック構成と同様である。ただし、本実施の形態では、図1における画素101aが画素201aに置き換えられる。また、画素201aの概略回路構成は、図2に示す画素101aの概略回路構成と同様である。ただし、本実施の形態では、図2における有機発光ダイオードD1が有機発光ダイオードD2に置き換えられる。

【0107】

(画素構成)

次に、各画素201aのレイアウト構造および層構造を詳細に説明する。本実施の形態による画素201aにおけるアクティブマトリクス基板101Aのレイアウト構造は、図3に示す画素101aのレイアウト構造と同様である。ただし、本実施の形態による画素201aの概略層構造は、図6に示すものとなる。なお、図6は、図4と同様に、図3のA−A’断面に対応する面における画素201aの概略断面図である。

【0108】

図6と図4とを比較すると明らかなように、本実施の形態による有機ELディスプレイ装置は、本発明の実施の形態1による有機ELディスプレイ装置100と同様の構成において、カソード電極63(例えば図4参照)が透明な電極材料で形成されたカソード電極65に置き換えられると共に、カソード電極65上に有機発光ダイオードD2におけるカソードの抵抗値を低減するための補助電極66が設けられている。

【0109】

カソード電極65は、例えばアノード電極61と同様に、可視光を透過可能な電極材料を用いて形成することができる。この電極材料には、例えばZTOやITOなどのような酸化物導電体材料、あるいは、銀(Ag)やアルミニウム(Al)などの金属材料よりなる透明単層膜、もしくは、これらを含む多層構造の透明積層膜を用いることができる。なお、金属材料を用いた場合、これを含む層は、光を透過させる程度の薄い半透過膜とされる。本実施の形態では、MgとAg合金膜を用い、光が透過する程度の薄膜で形成した場合を例に挙げて説明する。このように、本発明の実施の形態1によるボトムエミッション型の構成に加えて、カソード電極65を透明な電極で構成することで、ディスプレイパネル101の下面100aおよび上面200aの両方から光を取り出すことが可能な、いわゆる両面発光型の有機ELディスプレイ装置を実現することが可能となる。

【0110】

また、カソード電極65上の補助電極66は、例えばアクティブマトリクス基板101A上の各画素201aを区画する領域(例えば隔壁70上方)に形成される。この補助電極材料には、例えばZTOやITOなどのような無機酸化物導電体材料、あるいは、銀(Ag)やアルミニウム(Al)などの金属材料よりなる単層膜、もしくは、これらを含む多層構造の積層膜を用いることができる。ただし、本実施の形態のように補助電極66を各画素201aの各領域上に配置する場合、補助電極66は必ずしも透明な電極材料を用いて形成される必要は無く、例えばAlやAgなどの高い導電性を備えた材料で形成することも可能である。本実施の形態では、ZTOよりなる導電性単層膜を用いて補助電極66を形成した場合を例に挙げて説明する。このように、有機発光ダイオードD2におけるカソードの抵抗値を低減する補助電極66を設けることで、有機発光ダイオードD2の駆動電圧を低減することが可能となるため、結果的に有機ELディスプレイ装置の消費電力を低減することが可能となる。また、補助電極66の材料に透明電極材料を用いているため、下面100aだけでなく、上面200a全体も開口された、いわゆる両面全開口型の有機ELディスプレイ装置を実現することが可能となる。

【0111】

(製造方法)

また、本実施の形態による有機ELディスプレイ装置の製造方法は、本発明の実施の形態1による有機ELディスプレイ装置100の製造方法と同様の製造方法において、図5−10に示すカソード電極63の形成工程が、透明なカソード電極65の形成工程になると共に、カソード電極65上に補助電極66を形成する工程が加わる。なお、他の製造工程は、本発明の実施の形態1において図5−1から図5−10および図4を用いて説明した工程と同様であるため、ここでは詳細な説明を省略する。

【0112】

カソード電極65の形成工程では、図5−1から図5−9を用いて製造したアクティブマトリクス基板101A上全体に、例えば真空蒸着法などを用いてMgとAgの合金薄膜を堆積することで、カソード電極65を形成する。このとき、シャドウマスク法を用いることで、所望の領域全体にカソード電極65を形成する。

【0113】

また、補助電極66の形成工程では、上記工程のようにカソード電極65を形成した後、少なくともカソード電極65上に、例えばシャドウマスク法を用いたスパッタリング法、CVD法または真空蒸着法などを用いてZTOやITO等の酸化物導電材料やAg、Al、Cu等の低抵抗率の金属を堆積することで、例えばカソード電極65上面における隔壁70上方の領域に補助電極66を形成する。

【0114】

その後、本発明の実施の形態1と同様に、パッシベーション膜80を形成した後、製造されたディスプレイパネル101を、信号制御部102や走査駆動部103やデータ駆動部104や容量線駆動部105や駆動信号生成部106やその他の部品が搭載された筐体に取り付けることで、本実施の形態による有機ELディスプレイ装置が製造される。

【0115】

なお、以上の製造工程には、基板を洗浄する工程等が適宜含まれるが、ここでは説明の簡略化のためにこれらの工程を省略する。

【0116】

以上で説明したように、本実施の形態による有機ELディスプレイ装置は、有機膜62に対して光取出し側である上面200a側および下面100a側にある層すべてが光を透過する膜より構成されているため、光取出し面が全て開口された、いわゆる全開口の両面発光型有機ELディスプレイ装置が実現できる。

【0117】

また、このように光取出し面全てが開口された構成とすることで、発光素子(本実施の形態では有機発光ダイオードD2)の配置を自由に設計することが可能となるため、設計自由度の大きな有機ELディスプレイ装置を実現することが可能となる。さらに、本実施の形態による有機ELディスプレイ装置は、カソード電極65の抵抗値を低減するための補助電極66を備えているため、有機発光ダイオードD2の駆動電圧を低減することが可能となり、結果、有機ELディスプレイ装置の消費電力を低減することが可能となる。さらにまた、本実施の形態による有機ELディスプレイ装置は、例えば、車両におけるウィンドウやガラス窓やガラス製水槽などのような透明な面に貼り付けて使用するディスプレイとしてなど、種々の目的で使用することが可能である。

【0118】

さらに、本実施の形態による製造方法では、本発明の実施の形態1と同様に、製造過程においてコンタクト内配線42および第2配線レイヤ43等が透明半導体層44で覆われているため、後のエッチング工程などにおける各配線(42,43など)が受けるプロセスダメージを低減することが可能となる。

【0119】

さらにまた、上記した実施の形態において、本発明の実施の形態1と同様に、有機ELディスプレイ装置100を構成する各層をフレキシブルな材料を用いて形成していてもよい。

【0120】

なお、本実施の形態は、本発明の実施の形態1と同様に、例えば発光層が無機材料で形成された無機ELディスプレイ装置とすることも可能である。また、本実施の形態では、一方の光取出し側である上下何れかの側の層に例えば反射膜(リフレクタ)を設けることで、輝度などが向上された、上面発光型もしくは裏面発光型の有機ELディスプレイ装置を実現することもできる。

【0121】

<実施の形態3>

次に、本発明の実施の形態3による表示装置として、液晶ディスプレイ装置300を例に挙げて説明する。図7は、液晶ディスプレイ装置300の概略構成を示すブロック図である。なお、本実施の形態では、いわゆるバックライトと呼ばれる光源(例えば図10における光源350参照)と液晶素子(例えば図10における液晶素子E31参照)との間に素子基板(例えば図10におけるアクティブマトリクス基板301A参照)が介在する構成の液晶ディスプレイ装置300を例に挙げる。また、本実施の形態において、本発明の実施の形態1または2と同様の構成については、同一の符号を付すことで、その詳細な説明を省略する。

【0122】

(全体構成)

図7に示すように、液晶ディスプレイ装置300は、2次元マトリクス状に配列された画素(PX)301aを含むディスプレイパネル301と、これに接続された走査駆動部103、データ駆動部104および容量線駆動部105と、各部を制御するための信号制御部102と、を備える。なお、ディスプレイパネル301は、赤(R)、緑(G)および青(B)の三原色それぞれについての画素301aを備える。

【0123】

ここで、信号制御部102、走査駆動部103、データ駆動部104および容量線駆動部105の構成は、本発明の実施の形態1と同様である。また、走査制御信号CONT1、データ制御信号CONT2、容量線制御信号CONT3およびビデオデータ信号DATについても、適宜、液晶素子の駆動方式に適合した信号として生成され、出力される。ただし、本実施の形態においては、駆動線LP、駆動信号生成部106および発光制御信号CONT4を省略することができる。

【0124】

また、ディスプレイパネル301は、走査線LGとデータ線LDと容量線LCとに接続される。なお、本実施の形態では、走査線LGとデータ線LDと容量線LCとのそれぞれにおいて、相互に交差するように延伸する配線部分を主配線とし、この主配線から分岐して各画素301aにおけるスイッチングトランジスタQ31や蓄積キャパシタC31(例えば図8参照)に接続する配線を副配線とする。また、各素子間を接続する配線部分を副配線とする。また、他の構成は、本発明の実施の形態1と同様であるため、ここでは詳細な説明を省略する。

【0125】

(画素構成)

次に、図8を用いて各画素301aの概略構成およびその動作を説明する。なお、以下の説明は、R,G,Bのうち何れの画素301aについても同様である。

【0126】

図8は、画素301aの概略回路構成を示す模式図である。図8に示すように、画素301aは、スイッチングトランジスタQ31と、蓄積キャパシタC31と、液晶素子E31と、を含む。

【0127】

スイッチングトランジスタQ31は例えばn型のTFTであり、そのソースSは例えばノードN34においてデータ線LDの主配線から分岐する副配線に接続され、ドレインDはノードN31を含む配線L31に接続される。また、スイッチングトランジスタQ31のゲートGは、例えばノードN33において走査線LGの主配線から分岐する副配線に接続される。したがって、スイッチングトランジスタQ31は、走査信号の電圧レベルVg(走査制御電圧)に従ってデータ線LDおよびノードN31間を導通/遮断する。

【0128】

配線L31には、例えばノードN31において分岐する配線部分(これも配線L31に含む)を介して蓄積キャパシタC31の一方の端子が接続される。また、蓄積キャパシタC31の他方の端子は、例えばノードN35において容量線LCの主配線から分岐する副配線に接続される。容量線LCには、本発明の実施の形態1と同様に、容量線駆動部105から出力された容量線駆動信号が与えられる。この容量線駆動信号の電圧レベルVc(容量線駆動電圧)は、例えば接地電位とすることができる。例えば、液晶素子Cpx(E31)と同じ共通電極であるGND(Vcom)端子に接続される。言い換えれば、容量線LCは、接地線とすることができる。この場合、容量線駆動部105を省略することができる。

【0129】

また、配線L31には、液晶素子E31の一方の電極(例えば図10における画素電極311参照)も接続される。液晶素子E31の他方の電極は、共通電極(例えば図10における共通電極313参照)である。したがって、液晶素子E31は、回路上、いわゆる液晶キャパシタCpxとして機能する。この共通電極313には、図7または図8に示すように、共通電圧Vcomが印加される。以上の接続関係から、蓄積キャパシタC31と液晶素子E31とは、スイッチングトランジスタQ31の出力端子に並列に接続された負荷容量として機能する。なお、共通電圧Vcomは、例えば接地電位GNDとすることができる。

【0130】

ここで、走査線LGに入力された走査信号の電圧レベルVg(走査制御電圧)がハイレベルになると、スイッチングトランジスタQ31がオン状態となり、当該スイッチングトランジスタQ31を介して液晶素子E31の画素電極311(例えば図10参照)に電荷が注入される。この結果、画素電極311の電位がデータ信号の電圧レベルVdとなり、共通電極313(例えば図10参照)との間に電位差(Vd−Vcom)が生じて液晶素子E31の分子配列が変化する。

【0131】

ここで、蓄積キャパシタC31は、走査線LGの電圧レベルVgがローレベルとなってスイッチングトランジスタQ31が完全にオフ状態となった後から次に電圧レベルVgがハイレベルになってスイッチングトランジスタQ31がオン状態となると共に次のデータ信号が入力されるまでの間、画素電極311の電位を維持するための働きをする。すなわち、蓄積キャパシタC31は、所定の期間、データ線LDに入力されたデータ信号SDを保持する。

【0132】

なお、本実施の形態では、例えば、データ線LDに入力されるデータ信号の極性と容量線LCに入力される容量線駆動信号の電位とが所定期間ごとに反転される、いわゆる反転駆動方式を採用しても良い。反転駆動方式としては、ドット反転駆動方式やライン反転駆動方式などが存在するが、いずれの反転駆動方式を採用することも可能である。

【0133】

次に、図9および図10を用いて、各画素301aのレイアウト構造および層構造を詳細に説明する。図9は、画素301aにおけるアクティブマトリクス基板301A(例えば図10参照)のレイアウト構造を説明するための概略平面図である。また、図10は、画素301aの層構造を説明するための概略断面図である。なお、図9では、説明の簡略化のため、透明基板10、層間絶縁膜40および50、ならびに、対向基板302Aなどの構成(例えば図10参照)を省略する。また、図10には、図9のB−B’断面に対応する面における画素301aの概略層構造を示す。

【0134】

図9または図10に示すように、画素301aは、アレイ基板としてのアクティブマトリクス基板301A(例えば図10参照)と、これと対向する対向基板302A(例えば図10参照)と、アクティブマトリクス基板301Aと対向基板302Aとの間に配置された液晶素子E31(例えば図10参照)と、を備える。アクティブマトリクス基板301Aは、例えば走査線LGと、データ線LDと、容量線LCと、配線L31と、スイッチングトランジスタQ31と、蓄積キャパシタC31と、を含む。対向基板302Aには、不要な光の漏れを防止するためのブラックマトリクスとしての遮光膜321と、画素301aごとに適切な帯域の波長を透過させるためのカラーフィルタ64と、を備える。液晶素子E31は、液晶層312をサンドウィッチする画素電極311および共通電極313とこれらをさらにサンドウィッチする配向膜314および315とを含み、例えば配線L31を介してスイッチングトランジスタQ31および蓄積キャパシタC31に接続されるようにアクティブマトリクス基板301A上に配置される。なお、対向基板302Aは、アクティブマトリクス基板301Aと共に、液晶素子E31をサンドウィッチするように配置される。さらに、アクティブマトリクス基板301Aと液晶素子E31と対向基板302Aとで形成される積層構造体は、例えば所定方向に振動している光のみを透過させるための偏光板330および340でサンドウィッチされる。

【0135】

走査線LG、データ線LD、容量線LCおよび配線L31は、本発明の実施の形態1と同様に、それぞれ例えば、第1配線レイヤ41、コンタクト内配線42、第2配線レイヤ43およびコンタクトプラグ51のうち少なくとも一部で形成されている。スイッチングトランジスタQ31は、走査線LGを構成する第1配線レイヤ41の一部であるゲート電極15と、層間絶縁膜40の一部であるゲート絶縁膜16と、データ線LDの一部を構成する第2配線レイヤ43の一部であるソース電極18sと、配線L31の一部を構成する第2配線レイヤ43の一部であるドレイン電極18dと、透明半導体層44の一部である透明半導体層17と、よりなる。さらに、蓄積キャパシタC31は、配線L31を構成する第1配線レイヤ41の一部である下部電極35と、層間絶縁膜40の一部である容量絶縁膜36と、容量線LCを構成する第2配線レイヤ43の一部である上部電極37と、よりなる。さらにまた、図8に示す各ノードN31、N33〜N35は、それぞれ例えば図9に示す各位置に定義することができる。

【0136】

また、本実施の形態によるスイッチングトランジスタQ31は、本発明の実施の形態1におけるスイッチングトランジスタQ1と同様に、いわゆるボトムゲート構造のTFTであるが、本発明はこれに限定されず、例えばトップゲート構造のTFTとしてもよい。さらに、本実施の形態によるアクティブマトリクス基板301Aは、本発明の実施の形態1によるアクティブマトリクス基板101Aと同様に、いわゆるアレイ基板と称されるものである。

【0137】

透明基板10上において、各種配線(LG、LD、LC、L31等)および各種素子(Q31、C31等)が形成されない領域には、本発明の実施の形態1と同様に、例えば第1配線レイヤ41の一部が冗長された冗長配線41a(例えば図9参照)が形成されることで、透明基板10上に形成される層上面の平坦性が向上されている。さらに、本実施の形態において、透明半導体層44は、各素子(例えばスイッチングトランジスタQ31)のチャネル層としてだけでなく、下層に位置する第2配線レイヤ43やコンタクト内配線42などが受けるプロセスダメージを低減するための保護膜として機能する。

【0138】

また、上記の構成を備えたアクティブマトリクス基板301A上の液晶素子E31は、例えば、画素電極311と、画素電極311上の液晶層312と、液晶層312上の共通電極313と、液晶層312を上下からサンドウィッチする配向膜314および315と、よりなる(例えば図10参照)。なお、液晶素子E31において、液晶層312の上部に略三角形状の誘電体突起316を設けても良い(例えば図10参照)。また、液晶素子E31に対して光を取り出す側には、光源350からの不要な光の漏れを防止するためのブラックマトリクスや、カラーフィルタまたは波長シフタなどの色変換膜を配置することも可能である。本実施の形態では、共通電極313と対向基板302Aとの間にブラックマトリクスとしての遮光膜321およびカラーフィルタ64を配置した場合を例に挙げる。

【0139】

また、アクティブマトリクス基板301Aおよび対向基板302Aのさらに外側には、これらをサンドウィッチする偏光板330および340が設けられる。また、光源350は、例えばアクティブマトリクス基板301A下に配置される。したがって、光源350からの光は、偏光板330、アクティブマトリクス基板301A、液晶素子E31、カラーフィルタ64、対向基板302Aおよび偏光板340を介して、ディスプレイパネル301の光取出し面である上面300aから外部へ出力される。

【0140】

ここで、第1配線レイヤ41、層間絶縁膜40、透明半導体層44および第2配線レイヤ43は、本発明の実施の形態1と同様の材料を用いて形成することができる。したがって、スイッチングトランジスタQ31および蓄積キャパシタC31も、上記と同様の材料を用いて形成することができる。また、透明基板10、コンタクト内配線42、コンタクトプラグ51および層間絶縁膜50も、本発明の実施の形態1と同様の材料を用いて形成することができる。

【0141】

カラーフィルタ64には、R,G,Bそれぞれの画素301aに応じて適切な帯域の波長を透過させるように所定の顔料が混合された感光性樹脂など、種々のフィルタ材料を用いて形成することが可能である。本実施の形態では、それぞれの画素301aに応じて所定の顔料が混合された透明感光性樹脂を用いて形成した場合を例に挙げる。

【0142】

アクティブマトリクス基板301A上の液晶素子E31において、液晶層312の母材には、例えば、エステル系、ビフェニル系、フェニルシクロヘキサン系、シクロヘキサン系、フェニルビリジミン系、または、ジオキサン系の材料など、種々の材料を用いることが可能である。液晶層312は、上記のような母材に、目的に応じた材料を混合することで形成される。

【0143】

画素電極311には、例えばZTOやITOなどのような酸化物導電体材料を用いることができる。本実施の形態では、ZTOの透明導電膜を用いた場合を例に挙げて説明する。さらに、共通電極313には、画素電極311と同様に、例えばZTOやITOなどのような酸化物導電体材料を用いることができる。本実施の形態では、ZTOの透明導電膜を用いた場合を例に挙げて説明する。

【0144】

配向膜314および315は、それぞれ、液晶層312の分子配列を一定方向へ整列させるための膜であり、液晶層312に使用した材料に応じて、適宜、例えばポリイミドなどの材料により形成される。

【0145】

誘電体突起316は、液晶層312にバイアス電圧を印加した際の液晶分子の配列方向を制御するためのものであり、例えば画素電極311の中央部と液晶層312を挟んで対向するように液晶層312上面から内部へ向けて突出して設けられている。このような誘電体突起316は、例えば感光性樹脂などの誘電体材料を用いて形成することができる。

【0146】

遮光膜321は、例えばクロム(Cr)などのような金属膜やカーボンブラックに代表される遮光性分散顔料が分散されたブラックレジストのような感光性レジスト膜を用いて形成することができる。本実施の形態では、Crを用いて形成した場合を例に挙げる。

【0147】